(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5435720号

(P5435720)

(45) 発行日 平成26年3月5日(2014.3.5)

(24) 登録日 平成25年12月20日(2013.12.20)

(51) Int.Cl.

F 1

H01L 21/8234 (2006.01)

H01L 27/088 (2006.01)H01L 27/08 102B

H01L 27/08 102C

請求項の数 9 (全 19 頁)

|           |                               |           |                                             |

|-----------|-------------------------------|-----------|---------------------------------------------|

| (21) 出願番号 | 特願2009-289041 (P2009-289041)  | (73) 特許権者 | 000005821<br>パナソニック株式会社<br>大阪府門真市大字門真1006番地 |

| (22) 出願日  | 平成21年12月21日(2009.12.21)       | (74) 代理人  | 110001427<br>特許業務法人前田特許事務所                  |

| (65) 公開番号 | 特開2011-129811 (P2011-129811A) | (72) 発明者  | 樋口 裕一<br>大阪府門真市大字門真1006番地 パナソニック株式会社内       |

| (43) 公開日  | 平成23年6月30日(2011.6.30)         |           |                                             |

| 審査請求日     | 平成23年1月18日(2011.1.18)         | 合議体       |                                             |

| 審判番号      | 不服2013-11156 (P2013-11156/J1) | 審判長       | 池淵 立                                        |

| 審判請求日     | 平成25年6月13日(2013.6.13)         | 審判官       | 恩田 春香                                       |

|           |                               | 審判官       | 藤原 敬士                                       |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、同一の導電型である第1電界効果型トランジスタ及び第2電界効果型トランジスタが形成され、

前記第1電界効果型トランジスタは、

前記基板における第1活性領域上に形成された第1ゲート電極と、

前記第1ゲート電極の側方に形成された堆積絶縁膜からなる第1サイドウォールスペーサーと、

前記第1活性領域における前記第1ゲート電極下方を挟む両側に形成された第1導電型の第1エクステンション領域とを備え、

前記第2電界効果型トランジスタは、

前記基板における第2活性領域上に形成された第2ゲート電極と、

前記第2ゲート電極の側方に形成された堆積絶縁膜からなる第2サイドウォールスペーサーと、

前記第2活性領域における前記第2ゲート電極下方を挟む両側に形成された第1導電型の第2エクステンション領域とを備え、

前記第1サイドウォールスペーサーと、前記第1ゲート電極との間に、堆積絶縁膜からなる第1オフセットスペーサーが設けられ、

前記第2サイドウォールスペーサーと、前記第2ゲート電極との間に、前記第1オフセットスペーサーよりも厚い、堆積絶縁膜からなる第2オフセットスペーサーが設けられ、

10

20

前記第1ゲート電極のゲート長方向の寸法と、前記第2ゲート電極のゲート長方向の寸法とは同一寸法に形成されており、

前記第1電界効果型トランジスタと前記第2電界効果型トランジスタとは、同一不純物濃度のチャネル拡散層を有し、

前記第2電界効果型トランジスタは、前記第1電界効果型トランジスタよりも閾値電圧が高く設定され、

前記第1エクステンション領域と前記第1ゲート電極とが重なるゲート長方向の長さは、前記第2エクステンション領域と前記第2ゲート電極とが重なるゲート長方向の長さよりも長く、

前記第1ゲート電極と前記第1サイドウォールスペーサーとの間の距離は、前記第2ゲート電極と前記第2サイドウォールスペーサーとの間の距離よりも短いことを特徴とする半導体装置。 10

【請求項2】

請求項1の半導体装置において、

前記第1オフセットスペーサー及び前記第2オフセットスペーサーのうちの少なくとも前記第2オフセットスペーサーは、2層以上の積層構造であり、

前記第2オフセットスペーサーの積層数は、前記第1オフセットスペーサーの積層数よりも多いことを特徴とする半導体装置。

【請求項3】

請求項1又は2のいずれか1つの半導体装置において、

前記第1エクステンション領域と前記第1ゲート電極とが重なるゲート長方向の長さは、前記第2エクステンション領域と前記第2ゲート電極とが重なるゲート長方向の長さよりも所定の距離だけ長いことを特徴とする半導体装置。 20

【請求項4】

請求項1～3のいずれか1つの半導体装置において、

前記第1ゲート電極と前記第1サイドウォールスペーサーとの間の距離は、前記第2ゲート電極と前記第2サイドウォールスペーサーとの間の距離よりも所定の距離だけ短いことを特徴とする半導体装置。

【請求項5】

請求項3又は4の半導体装置において、

前記所定の距離は、前記第1電界効果型トランジスタの閾値電圧と前記第2電界効果型トランジスタの閾値電圧との違いによって設定されていることを特徴とする半導体装置。 30

【請求項6】

請求項3～5のいずれか1つの半導体装置において、

前記所定の距離は、2nm以上で且つ4nm以下であることを特徴とする半導体装置。

【請求項7】

請求項1～6のいずれか1つの半導体装置において、

前記第1ゲート電極の下方における前記第1エクステンション領域間の距離は、前記第2ゲート電極の下方における前記第2エクステンション領域間の距離よりも短いことを特徴とする半導体装置。 40

【請求項8】

請求項1～7のいずれか1つの半導体装置において、

前記第1エクステンション領域と前記基板との間に設けられた第2導電型の第1ハローフィールドと、

前記第2エクステンション領域と前記基板との間に設けられた第2導電型の第2ハローフィールドとを更に備えることを特徴とする半導体装置。

【請求項9】

請求項1～8のいずれか1つの半導体装置において、

前記第1活性領域における前記第1ゲート電極から見て前記第1エクステンション領域の外側に形成された第1導電型の第1ソース／ドレイン領域と、 50

前記第2活性領域における前記第2ゲート電極から見て前記第2エクステンション領域の外側に形成された第1導電型の第2ソース／ドレイン領域とを備えることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置とその製造方法に関し、特に、異なる閾値電圧を有する複数の電界効果型トランジスタ(Field Effect Transistor, FET)を備えた半導体装置とその製造方法に関する。

【背景技術】

10

【0002】

近年、半導体装置の高集積化を実現するために、個々の半導体素子の微細化が行なわれてきている。微細化が進むに連れて、異なる閾値電圧を有する複数の電界効果トランジスタ(以下、単にトランジスタと呼ぶことがある)を備える半導体装置(例えばeSRA M(embedded Static Random Access Memory))において、それぞれのトランジスタの閾値電圧を同時に最適化することが困難になってきている。

【0003】

そこで、同一基板上に閾値電圧の異なる複数のトランジスタを含む半導体装置において、それぞれの閾値電圧の調整方法が種々提案されている。その一つについて、以下に説明する。

20

【0004】

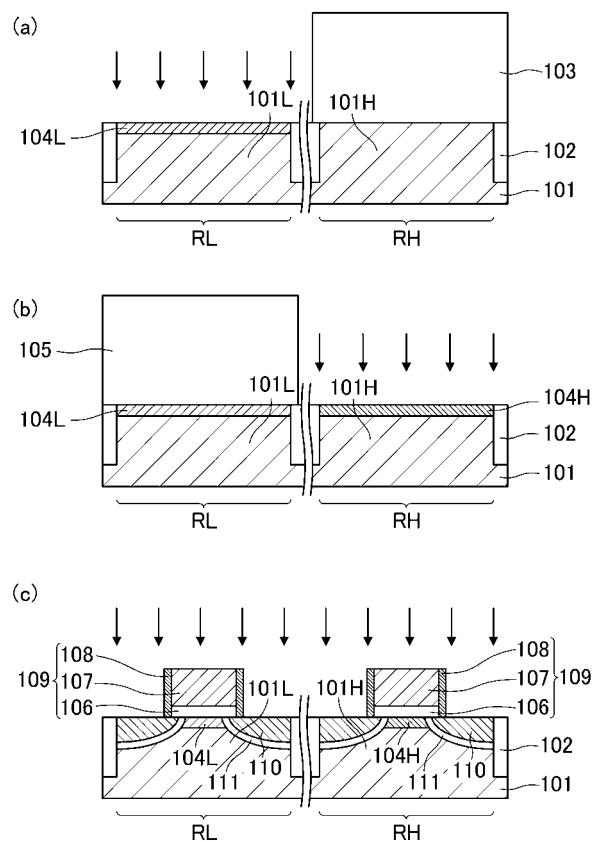

図5(a)～(c)は、互いに閾値電圧の異なる低閾値電圧(Lvt)トランジスタ及び高閾値電圧(Hvt)トランジスタを形成する工程を示す図である。これらの図に示すように、半導体基板101の表面部が素子分離であるSTI(Shallow Trench Isolation)102により区画され、Lvtトランジスタ形成領域RLと、Hvtトランジスタ形成領域RHとが設けられている。

【0005】

まず、図5(a)に示すように、Hvtトランジスタ形成領域RHを覆うレジスト103を形成し、該レジスト103をマスクとしてLvtトランジスタ形成領域RLに対してチャネル注入を行なう。これにより、Lvtトランジスタ形成領域RLの活性領域にチャネル層104Lが形成される。この後、レジスト103を除去する。

30

【0006】

次に、図5(b)に示すように、Lvtトランジスタ形成領域RLを覆うレジスト105を形成し、該レジスト105をマスクとしてHvtトランジスタ形成領域RHに対してチャネル注入を行なう。これにより、Hvtトランジスタ形成領域RHの活性領域にチャネル層104Hが形成される。この後、レジスト105を除去する。

【0007】

図5(b)の工程の後、図5(c)のように、ゲート絶縁膜106、ゲート電極107及びサイドウォールスペーサー108を含むゲート構造109を形成する。更に、ゲート構造109をマスクとして不純物注入を行ない、ゲート構造109の両側にエクステンション領域110及びその下方を覆うハロー領域111とを形成する。図示は省略するが、この後、ソース／ドレイン領域等の形成も行なわれる。

40

【0008】

以上のように、Lvtトランジスタ形成領域RLとHvtトランジスタ形成領域RHとに対して別々にチャネル注入を行なうことにより、それぞれのチャネル層104L及び104Hの不純物の濃度、種類を個別に設定することができる。この結果、Lvtトランジスタ及びHvtトランジスタの両方について、閾値電圧を個別に設定することができる。

【先行技術文献】

【特許文献】

【0009】

50

【特許文献1】特開2007-281027号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、チャネル層の不純物について設定するだけでは、Lvtトランジスタ及びHvtトランジスタのそれぞれの性能向上に限度がある。これに対し、チャネル注入に加えて、エクステンション注入についてもトランジスタの種類毎に個別に行なうことは可能である。しかし、そのためにはマスク工程、注入工程をそれぞれ個別に行なうことを要し、製造工程が長くなってしまう。

【0011】

10

以上に鑑み、本発明の目的は、閾値電圧の異なる複数のトランジスタを備える半導体装置及びその製造方法において、マスク工程の増加を抑えながら、それぞれのトランジスタの性能を向上することである。

【課題を解決するための手段】

【0012】

前記の目的を達成するため、本開示の半導体装置は、基板上に、同一の導電型である第1電界効果型トランジスタ及び第2電界効果型トランジスタが形成され、第1電界効果型トランジスタは、基板における第1活性領域上に形成された第1ゲート電極と、第1ゲート電極の側方に形成された堆積絶縁膜からなる第1サイドウォールスペーサーと、第1活性領域における第1ゲート電極下方を挟む両側に形成された第1導電型の第1エクステンション領域とを備え、第2電界効果型トランジスタは、基板における第2活性領域上に形成された第2ゲート電極と、第2ゲート電極の側方に形成された堆積絶縁膜からなる第2サイドウォールスペーサーと、第2活性領域における第2ゲート電極下方を挟む両側に形成された第1導電型の第2エクステンション領域とを備え、第2電界効果型トランジスタは、第1電界効果型トランジスタよりも閾値電圧が高く、第1エクステンション領域と第1ゲート電極とが重なるゲート長方向の長さは、第2エクステンション領域と第2ゲート電極とが重なるゲート長方向の長さよりも長く、第1ゲート電極と第1サイドウォールスペーサーとの間の距離は、第2ゲート電極と第2サイドウォールスペーサーとの間の距離よりも短い。

20

【0013】

30

このような半導体装置によると、エクステンション領域がゲート電極と重なっている部分のゲート長方向の長さの違いにより、第1電界効果型トランジスタと第2電界効果型トランジスタとでは実効的なゲート長（それぞれゲート電極の両側に設けられているエクステンション領域間の距離）が異なる。このことから、第1電界効果型トランジスタの閾値電圧は、第2電界効果型トランジスタの閾値電圧よりも低くなっている。また、後に説明する通り、共通のマスクを用いた不純物注入によって第1エクステンション領域と第2エクステンション領域を形成することができ、マスク工程の増加を避けることができる。

【0014】

40

尚、第1サイドウォールスペーサーと、第1ゲート電極との間に、第1オフセットスペーサーが設けられ、第2サイドウォールスペーサーと、第2ゲート電極との間に、第1のオフセットスペーサーよりも厚い第2オフセットスペーサー設けられていることが好ましい。

【0015】

ゲート電極とサイドウォールスペーサーとの間の距離の差（第1電界効果型トランジスタにおいて、第2電界効果型トランジスタにおけるよりも短い）を実現するために、このようにしても良い。

【0016】

ここで、記第1オフセットスペーサー及び第2オフセットスペーサーのうちの少なくとも第2オフセットスペーサーは、2層以上の積層構造であり、第2オフセットスペーサーの積層数は、第1オフセットスペーサーの積層数よりも多いことが好ましい。

50

## 【0017】

第2オフセットスペーサーを第1オフセットスペーサーよりも厚くするために、このようにしてもよい。この場合、第1オフセットスペーサーについては単層構造であっても良い。

## 【0018】

また、第1サイドウォールスペーサーは、第1ゲート電極の側壁に接しており、第2サイドウォールスペーサーと、第2ゲート電極との間に、オフセットスペーサーが設けられていることが好ましい。

## 【0019】

ゲート電極とサイドウォールスペーサーとの間の距離の差を実現するために、このようにすることもできる。 10

## 【0020】

また、第1エクステンション領域と第1ゲート電極とが重なるゲート長方向の長さは、第2エクステンション領域と第2ゲート電極とが重なるゲート長方向の長さよりも所定の距離だけ長いことが好ましい。

## 【0021】

また、第1ゲート電極と第1サイドウォールスペーサーとの間の距離は、第2ゲート電極と第2サイドウォールスペーサーとの間の距離よりも所定の距離だけ短いことが好ましい。

## 【0022】

また、所定の距離は、第1電界効果型トランジスタの閾値電圧と第2電界効果型トランジスタの閾値電圧との違いによって設定されていることが好ましい。 20

## 【0023】

それぞれ所定の距離の差により、電界効果型トランジスタ毎に実効的なゲート長の差が生じ、該ゲート長の差に依存して、閾値電圧の差が生じる。よって、望ましい閾値電圧の差に合わせて、前記所定の距離を設定する。

## 【0024】

所定の距離は、2nm以上で且つ4nm以下であってもよい。具体例の1つとして、このようにしても良い。

## 【0025】

また、第1ゲート電極のゲート長方向の寸法と、第2ゲート電極のゲート長方向の寸法とは実質的に同一寸法に形成されていることが好ましい。 30

## 【0026】

ここで、実質的に同一寸法とは、設計寸法が同じであり、製造過程において生じるバラツキは含むことを意味する。

## 【0027】

また、第1ゲート電極の下方における第1エクステンション領域間の距離は、第2ゲート電極の下方における第2エクステンション領域間の距離よりも短いことが好ましい。

## 【0028】

ゲート電極自体の寸法が同じであっても、前記のようなエクステンション領域の構成の違いにより、それぞれの電界効果型トランジスタにおける実効的なゲート長に違いを設けることができる。 40

## 【0029】

また、第1エクステンション領域と基板との間に設けられた第2導電型の第1ハロー領域と、第2エクステンション領域と基板との間に設けられた第2導電型の第2ハロー領域とを更に備えることが好ましい。

## 【0030】

また、第1活性領域における第1ゲート電極から見て第1エクステンション領域の外側に形成された第1導電型の第1ソース／ドレイン領域と、第2活性領域における第2ゲート電極から見て第2エクステンション領域の外側に形成された第2導電型の第2ソース／ 50

ドレイン領域とを備えることが好ましい。

【0031】

半導体装置として、これらの構成要素備えていても良い。

【0032】

次に、前記の目的を達成するため、第1ゲート電極を含む第1電界効果型トランジスタ及び第2ゲート電極を含む第2電界効果型トランジスタを備える本開示の第1の半導体装置の製造方法は、基板における第1活性領域上に第1ゲート電極を形成すると共に、基板における第2活性領域上に第2ゲート電極を形成する工程(a)と、第1ゲート電極の側壁に第1オフセットスペーサーを堆積法を用いて形成すると共に、第2ゲート電極の側壁に、第1オフセットスペーサーよりも厚さの厚い第2オフセットスペーサーを堆積法を用いて形成する工程(b)と、工程(b)の後に、第1ゲート電極及び第1オフセットスペーサーをマスクとして第1活性領域に対して第1の不純物注入を行ない、第1活性領域における第1ゲート電極の両側に第1導電型の第1エクステンション領域を形成すると共に、第2ゲート電極及び第2オフセットスペーサーをマスクとして第2活性領域に対して第1の不純物注入を行ない、第2活性領域における第2ゲート電極の両側に第1導電型の第2エクステンション領域を形成する工程(c)とを備える。

10

【0033】

第1の半導体装置の製造方法において、同じ工程(c)にて不純物注入を行なうため、オフセットスペーサーの端からゲート電極の側にエクステンション領域が延びる距離は、第1電界効果型トランジスタ及び第2電界効果型トランジスタのどちらにおいても同じである。しかし、第1オフセットスペーサーよりも第2オフセットスペーサーの方が厚さが厚いので、第1エクステンション領域と第1ゲート電極とが重なるゲート長方向の長さは、第2エクステンション領域と第2ゲート電極とが重なるゲート長方向の長さよりも長くなる。この結果、第2電界効果型トランジスタの閾値電圧は、第1電界効果型トランジスタの閾値電圧よりも高くなる。

20

【0034】

このように、同じ不純物注入工程を利用し、マスク工程を増加させることなく、閾値電圧の異なる複数の電界効果型トランジスタを形成することができる。

【0035】

尚、第1オフセットスペーサー及び第2オフセットスペーサーのうちの少なくとも第2オフセットスペーサーは、2層以上の積層構造であり、第2オフセットスペーサーの積層数は、第1オフセットスペーサーの積層数よりも多いことが好ましい。

30

【0036】

第2オフセットスペーサーを第1オフセットスペーサーよりも厚くするために、このようにしてもよい。

【0037】

次に、前記目的を達成するため、第1ゲート電極を含む第1電界効果型トランジスタ及び第2ゲート電極を含む第2電界効果型トランジスタを備える本開示の第2の半導体装置の製造方法は、基板における第1活性領域上に第1ゲート電極を形成すると共に、基板における第2活性領域上に第2ゲート電極を形成する工程(a)と、第2ゲート電極の側壁にオフセットスペーサーを堆積法を用いて形成する工程(b)と、工程(b)の後に、第1ゲート電極をマスクとして第1活性領域に対して第1の不純物注入を行ない、第1活性領域における第1ゲート電極の両側に第1導電型の第1エクステンション領域を形成すると共に、第2ゲート電極及びオフセットスペーサーをマスクとして第2活性領域に対して第1の不純物注入を行ない、第2活性領域における第2ゲート電極の両側に第1導電型の第2エクステンション領域を形成する工程(c)とを備え、工程(c)において、第1ゲート電極の側壁にオフセットスペーサーが形成されていない状態で第1の不純物注入を行なう。

40

【0038】

第2の半導体装置の製造方法においても、同じ工程(c)にて不純物注入を行なう。こ

50

ここで、第2ゲート電極の側壁にはオフセットスペーサーが設けられ、第1ゲート電極の側壁にはオフセットスペーサーが設けられないため、第1エクステンション領域と第1ゲート電極とが重なるゲート長方向の長さは、第2エクステンション領域と第2ゲート電極とが重なるゲート長方向の長さよりも長くなる。このように、同じ不純物注入工程を利用し、マスク工程を増加させることなく、閾値電圧の異なる複数の電界効果型トランジスタを形成することができる。

【0039】

また、第1及び第2の半導体装置の製造方法において、工程(c)の後に、第1ゲート電極及び第2ゲート電極の側方にそれぞれ第1サイドウォールスペーサー及び第2サイドウォールスペーサーを形成した後、第1活性領域及び第2活性領域に対して第2の不純物注入を行なうことにより、第1活性領域における第1ゲート電極から見て第1サイドウォールスペーサーの外側に第1導電型の第1ソース／ドレイン領域を形成すると共に、第2活性領域における第2ゲート電極から見て第2サイドウォールスペーサーの外側に第1導電型の第2ソース／ドレイン領域を形成しても良い。10

【0040】

このようにして、第1電界効果型トランジスタ及び第2電界効果型トランジスタについて、ソース／ドレイン領域を形成することができる。

【発明の効果】

【0041】

本開示の半導体装置及びその製造方法によると、同じ不純物注入により、複数の電界効果型トランジスタにおける実効的なゲート長を互いに異なるようにすることができる。このことから、マスク工程の増加を避けながら、互いに異なる閾値電圧を有する複数の電界効果型トランジスタを形成することができる。20

【図面の簡単な説明】

【0042】

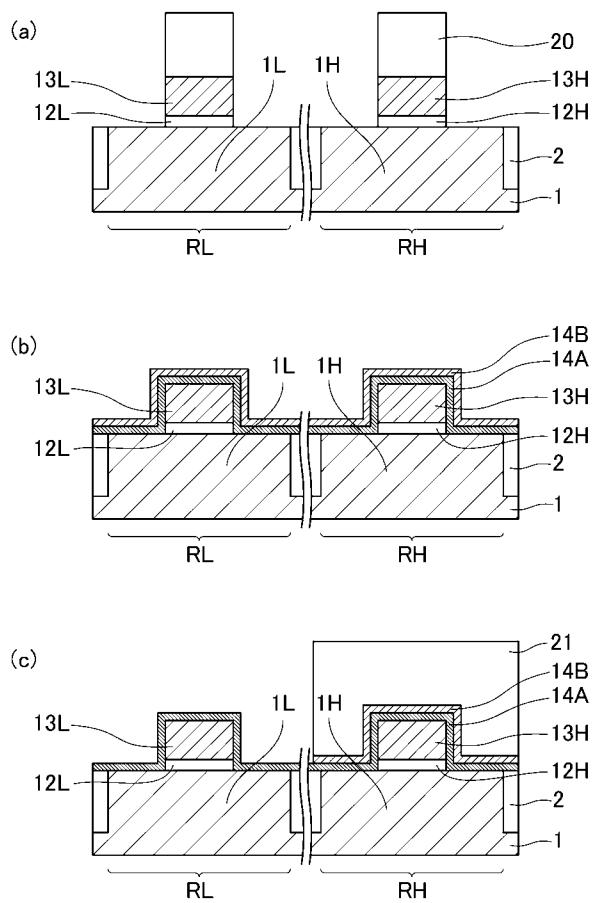

【図1】図1(a)～(c)は、本開示の第1の実施形態に係る例示的半導体装置とその製造方法を模式的に示す図である。

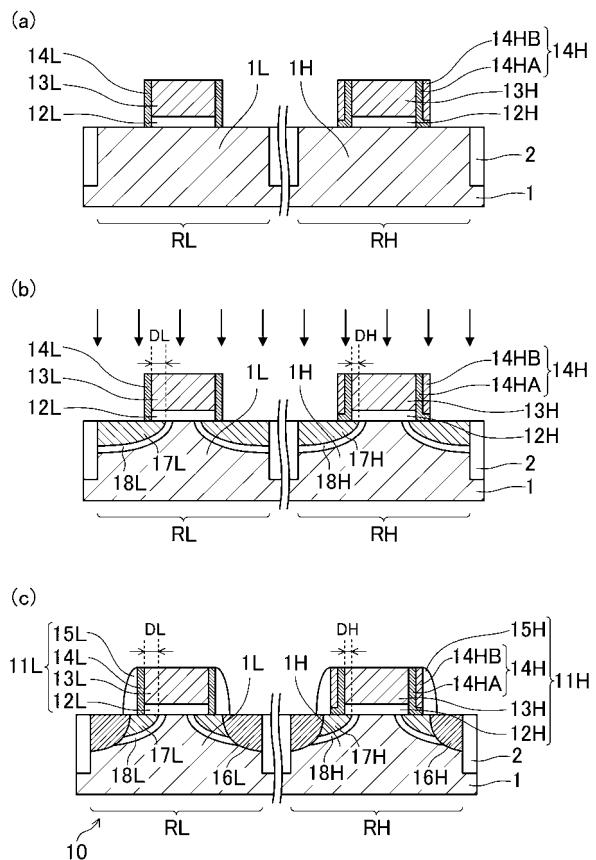

【図2】図2(a)～(c)は、図1(c)に続いて、本開示の第1の実施形態に係る例示的半導体装置とその製造方法を模式的に示す図である。

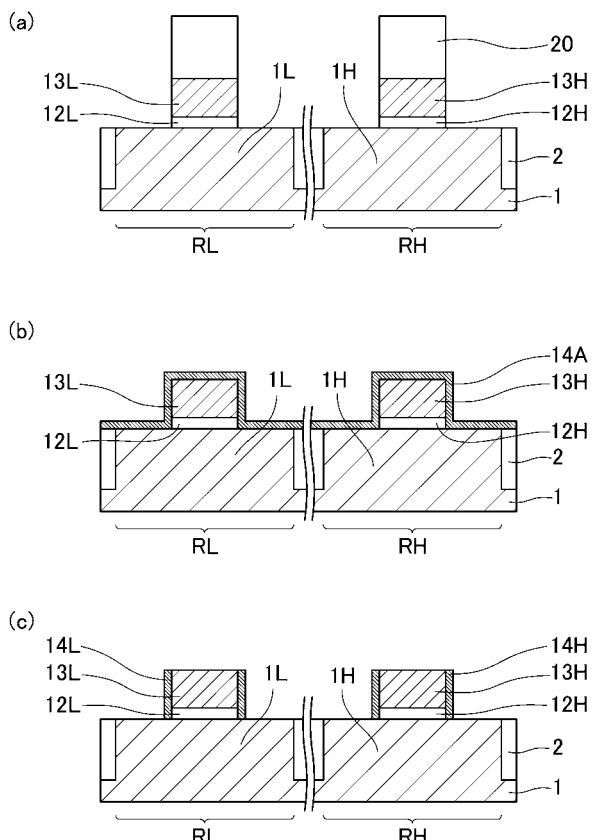

【図3】図3(a)～(c)は、本開示の第2の実施形態に係る例示的半導体装置とその製造方法を模式的に示す図である。30

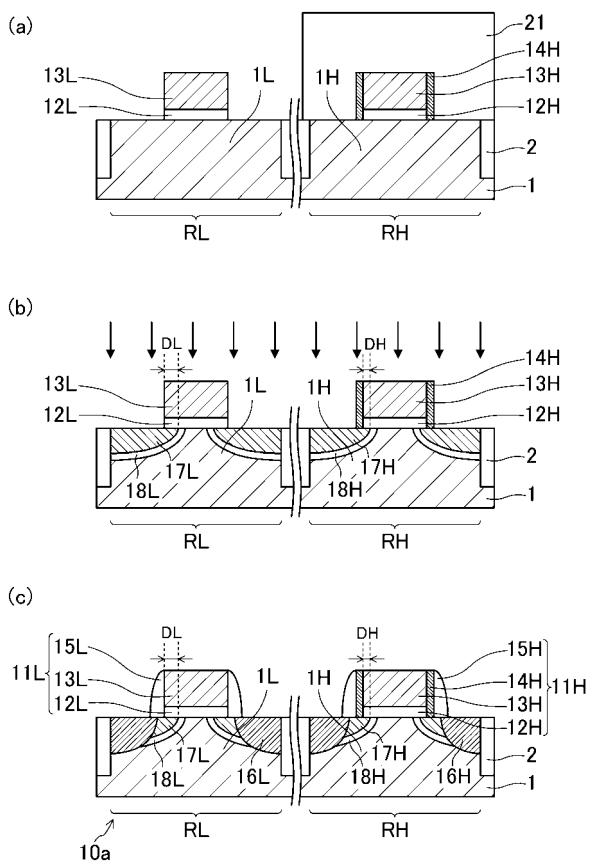

【図4】図4(a)～(c)は、図3(c)に続いて、本開示の第2の実施形態に係る例示的半導体装置とその製造方法を模式的に示す図である。

【図5】図5(a)～(c)は、背景技術の半導体装置の製造方法について示す図である。

。

【発明を実施するための形態】

【0043】

(第1の実施形態)

以下、本発明の第1の実施形態の半導体装置とその製造方法について、図面を参照しながら説明する。40

【0044】

図1(a)～(c)及び図2(a)～(c)は、本実施形態の例示的半導体装置10の構造及びその製造方法について模式的に示す図である。図2(c)に示すように、半導体装置10は、シリコンからなる半導体基板等である基板1を用いて形成されている。基板1の表面部は、例えばLOCOS (Local Oxidation of Silicon) 法やSTI (Shallow Trench Isolation) 法により形成されたシリコン酸化膜からなる素子分離領域2によって基板1からなる活性領域が区画されている。図2(c)には、閾値電圧の低い電界効果型トランジスタ(以下、Lvtトランジスタと呼ぶ)が形成されたLvtトランジスタ領域RLと、Lvtトランジスタに比べて閾値電圧の高い電界効果型トランジスタ(以下、Hvtトランジスタと呼ぶ)が形成されたHvtトランジスタ領域RHとが示されている。50

尚、本実施形態では、Lvtトランジスタ及びHvtトランジスタとして、N型FETを用いて説明する。

【0045】

Lvtトランジスタ領域RLにおいて、P型の基板1における素子分離領域2に囲まれた活性領域1L上に、ゲート絶縁膜12Lを介してゲート電極13Lが形成されている。ゲート電極13Lの側壁には、オフセットスペーサー14Lを介してサイドウォールスペーサー15Lが形成されている。また、活性領域1Lにおけるゲート電極13Lの両側方(サイドウォールスペーサー15Lの外側方)に、N型のソース/ドレイン領域16L(ソース領域及びドレイン領域をまとめてこのように呼ぶ)が形成されている。更に、ソース/ドレイン領域16Lよりも内側(ゲート電極13L側)に、N型のエクステンション領域17Lが、活性領域1Lにおけるゲート電極13L下方のチャネル形成領域を挟んで両側に形成されている。エクステンション領域17Lは、ゲート電極13Lの両側方から一部がゲート電極13Lの下方にまで延びている。エクステンション領域17Lと基板1との間に、エクステンション領域17Lとは導電型が異なるP型のハロー領域18Lが形成されている。ハロー領域18Lは、エクステンション領域17Lの底面及び側面(ソース/ドレイン領域16Lに接続している側面は除く)を覆うように形成されている。10

【0046】

ゲート絶縁膜12L、ゲート電極13L、オフセットスペーサー14L及びサイドウォールスペーサー15Lにより、Lvtトランジスタのゲート構造11Lが構成されている。20

【0047】

次に、Hvtトランジスタ領域RHには、Lvtトランジスタ領域RLのLvtトランジスタと類似した構造のHvtトランジスタが形成されている。具体的に、P型の基板1における素子分離領域2に囲まれた活性領域1H上に、ゲート絶縁膜12Hを介してゲート電極13Hが形成されている。ゲート電極13Hの側壁には、オフセットスペーサー14Hを介してサイドウォールスペーサー15Hが形成されている。また、活性領域1Hにおけるゲート電極13Hの両側方にN型のソース/ドレイン領域16Hが形成され、その内側に一部がゲート電極13Hの下方にまで延びたN型のエクステンション領域17Hが形成されている。エクステンション領域17Hと基板1との間に、エクステンション領域17Hとは導電型が異なるP型のハロー領域18Hが形成されている。ハロー領域18Hは、エクステンション領域17Hの底面及び側面(ソース/ドレイン領域16Hに接続している側面は除く)を覆うように形成されている。30

【0048】

ゲート絶縁膜12H、ゲート電極13H、オフセットスペーサー14H及びサイドウォールスペーサー15Hにより、Hvtトランジスタのゲート構造11Hが構成されている。

【0049】

ここで、Hvtトランジスタにおけるオフセットスペーサー14Hは、ゲート電極13Hの側壁に接する断面形状がL字状の第一層14HAと、該第一層14HAに積層する第二層14HBとからなる2層の積層構造であり、2層合わせた厚さは、Lvtトランジスタにおける一層構造のオフセットスペーサー14Lよりも厚くなっている。40

【0050】

また、Lvtトランジスタにおいてゲート電極13Lの下方に延びている部分のエクステンション領域17Lの長さ(ゲート電極13Lとのオーバーラップ量)をDLとし、Hvtトランジスタにおいてゲート電極13Hの下方に延びている部分のエクステンション領域17Hの長さをDHとすると、DLはDHよりも長い。言い換えると、ゲート電極13Lとエクステンション領域17Lとが重なる長さDLは、ゲート電極13Hとエクステンション領域17Hとが重なる長さDHよりも長い。また、Lvtトランジスタにおけるエクステンション領域17Lは、Hvtトランジスタにおけるエクステンション領域17Hに比べると、よりゲート電極の内側にまで延びていることになる。50

## 【0051】

ここで、ゲート電極13Lのゲート長方向の寸法とゲート電極13Hのゲート長方向の寸法とは、実質的に同一寸法である。実質的に同一寸法とは、設計寸法が同じであり、製造過程において生じるバラツキは含むことを意味する。

## 【0052】

このことから、Lvtトランジスタのゲート電極13L下方におけるエクステンション領域17L間の距離（実効的なゲート長）は、Hvtトランジスタのゲート電極13H下方におけるエクステンション領域17H間の距離よりも短くなっている。

## 【0053】

このようにすることによって、Lvtトランジスタの閾値電圧は、Hvtトランジスタの閾値電圧に比べて低くなっている。 10

## 【0054】

オーバーラップ量DLとオーバーラップ量DHとの違いは、オフセットスペーサー14Lの厚さとオフセットスペーサー14Hの厚さの違いによって実現されている。

## 【0055】

Lvtトランジスタ領域RLに形成されるLvtトランジスタは、オフリーク電流の低減よりも動作の高速性等を重視する（GIDL、BTBT等を無視できる）トランジスタである。そこで、オーバーラップ量DLが十分に長くなるように、オフセットスペーサー14Lは薄く設定され、閾値電圧が低くなっている。

## 【0056】

これに対し、Hvtトランジスタ領域RHに形成されるHvtトランジスタは、Lvtトランジスタに比べてオフリーク電流の低減を重視する（GIDL、BTBT等を無視できない）トランジスタである。そこで、オーバーラップ量DHを（オーバーラップ量DLに比べて）短くするために、オフセットスペーサー14Hがオフセットスペーサー14Lよりも厚く設定されている。但し、エクステンション領域17Hがゲート電極13Hに対してオフセットする（ゲート電極13Hの下方に入り込まない配置になる）ことは無いようとする。 20

## 【0057】

以上のように、オフセットスペーサーの厚さをそれぞれ設定することにより、エクステンション領域とゲート電極とのオーバーラップ量を決定し、それぞれのトランジスタの閾値電圧を設定することができる。 30

## 【0058】

次に、図1(a)～(c)及び図2(a)～(c)を参照して、半導体装置10の製造方法について説明する。

## 【0059】

図1(a)には、ゲート電極の形成まで行なわれた状態が示されている。まず、P型の単結晶シリコンからなる半導体基板、P型ウェル領域が形成された単結晶シリコンからなる半導体基板等であるP型の基板1に、例えばP型不純物であるB（ホウ素）イオン等を注入する。これは、基板1表面のチャネル形成領域に注入するための所定の条件により行なう。その後、熱処理により、P型チャネル拡散層を形成する（図示省略）。 40

## 【0060】

次に、閾値電圧の低い電界効果型トランジスタを形成するLvtトランジスタ領域RLと、閾値電圧の高い電界効果型トランジスタを形成するHvtトランジスタ領域RHとを定めて、基板1のチャネル形成領域を局所的に露出させる。このためには、基板1の表面部にLOCOS法、STI法等による素子分離領域2を形成する。これにより、素子分離領域2によって囲まれた基板1からなる活性領域1L及び活性領域1Hがそれぞれ形成される。

## 【0061】

次に、基板1上を覆うように、ゲート絶縁膜12L及び12Hとなる絶縁膜を形成し、更にその上に、ゲート電極13L及び13Hとなる電極材料層を形成する。 50

## 【0062】

絶縁膜は、 $\text{SiO}_2$ 、 $\text{SiON}$ 、 $\text{HfSiO}$ 、 $\text{HfSiON}$ 、 $\text{HfO}_2$ 等の単層膜又は積層膜とすることができます。形成には、熱酸化法、物理的気相蒸着法（以下、PVD（Physical Vapor Deposition）法と呼ぶ）、化学的気相蒸着法（以下、CVD（Chemical Vapor Deposition）法と呼ぶ）等を用いることができる。

## 【0063】

また、電極材料層は、 $\text{Ta}$ 、 $\text{TaN}$ 、 $\text{Ti}$ 、 $\text{TiN}$ 、 $\text{Al}$ 、 $\text{TiAl}$ 等の金属材料の単層構造又はこれらの積層構造であってもよい。更に、前述のいずれかの金属材料からなる金属層と、該金属層上に形成された $\text{Si}$ 層又は $\text{Si}$ を含む材料からなる $\text{Si}$ 含有層との積層構造であっても良い。これらの層の形成には、PVD法、CVD法、スパッタ法等を用いることができる。10

## 【0064】

次に、電極材料層上にレジスト材料を塗布した後、 $\text{Lvt}$ トランジスタ領域 $\text{RL}$ のゲート電極 $13\text{L}$ 及び $\text{Hvt}$ トランジスタ領域 $\text{RH}$ のゲート電極 $13\text{H}$ の形成位置に対応するようにパターニングして、レジスト $20$ を形成する。続いて、レジスト $20$ をマスクとして前記電極材料層及び絶縁膜をエッチングすることにより、 $\text{Lvt}$ トランジスタ領域 $\text{RL}$ における活性領域 $1\text{L}$ 上にゲート絶縁膜 $12\text{L}$ 及びゲート電極 $13\text{L}$ を形成する一方、 $\text{Hvt}$ トランジスタ領域 $\text{RH}$ における活性領域 $1\text{H}$ 上にゲート絶縁膜 $12\text{H}$ 及びゲート電極 $13\text{H}$ を形成する。この後、レジスト $20$ を除去する。

## 【0065】

次に、図1(b)の工程を行なう。まず、基板 $1$ 上の全面に、ゲート電極 $13\text{L}$ 及び $13\text{H}$ の上面及び側面を覆うように、オフセットスペーサーとなる絶縁膜を形成する。具体例としては、 $\text{SiN}$ 膜からなる絶縁膜 $14\text{A}$ を $2\text{nm} \sim 10\text{nm}$ の膜厚に堆積した後、該絶縁膜 $14\text{A}$ を覆うように、 $\text{SiO}_2$ 膜からなる絶縁膜 $14\text{B}$ を $2\text{nm} \sim 10\text{nm}$ の膜厚に堆積する。形成方法としては、CVD法等を用いればよい。また、ここでは絶縁膜 $14\text{A}$ を $\text{SiN}$ 膜、絶縁膜 $14\text{B}$ を $\text{SiO}_2$ 膜としているが、これらの材料を逆にしても構わない。また、絶縁膜 $14\text{A}$ に対して絶縁膜 $14\text{B}$ を選択的に除去することが可能であれば、それぞれ他の材料を用いることも可能である。20

## 【0066】

次に、図1(c)の工程を行なう。まず、基板 $1$ 上の全面にレジスト材料を塗布し、続いて $\text{Hvt}$ トランジスタ領域 $\text{RH}$ のみがマスクされるようにパターニングして、レジスト $21$ を形成する。その後、レジスト $21$ をマスクとしてウェットエッチングを行ない、 $\text{Lvt}$ トランジスタ領域 $\text{RL}$ における絶縁膜 $14\text{B}$ のみを選択的に除去する。その後、レジスト $21$ を除去する。これにより、活性領域 $1\text{L}$ 上の絶縁膜 $14\text{B}$ は除去されて絶縁膜 $14\text{A}$ のみが残存し、活性領域 $1\text{H}$ 上には絶縁膜 $14\text{A}$ 及び絶縁膜 $14\text{B}$ が共に残存した状態となる。30

## 【0067】

次に、図2(a)に示すように、異方性エッチングを行なって絶縁膜 $14\text{A}$ 及び絶縁膜 $14\text{B}$ を全面エッチバックし、ゲート電極の側壁を覆う部分のみを残して他の部分を除去することにより、オフセットスペーサーを形成する。より具体的に、 $\text{Lvt}$ トランジスタ領域 $\text{RL}$ のゲート電極 $13\text{L}$ の側方に、絶縁膜 $14\text{A}$ から一層構造のオフセットスペーサー $14\text{L}$ を形成する。また、 $\text{Hvt}$ トランジスタ領域 $\text{RH}$ のゲート電極 $13\text{H}$ の側方に、絶縁膜 $14\text{A}$ からなる断面形状が $L$ 字状の第一層 $14\text{HA}$ と、該第一層 $14\text{HA}$ 上に形成された第二層 $14\text{HB}$ とからなる2層構造のオフセットスペーサー $14\text{H}$ を形成する。40

## 【0068】

$\text{Hvt}$ トランジスタ領域 $\text{RH}$ のオフセットスペーサー $14\text{H}$ は、 $\text{Lvt}$ トランジスタ領域 $\text{RL}$ のオフセットスペーサー $14\text{L}$ と同じ絶縁膜 $14\text{A}$ からなる第一層 $14\text{HA}$ に、第二層 $14\text{HB}$ が積層された構造であるから、オフセットスペーサー $14\text{L}$ よりも第二層 $14\text{HB}$ の膜厚分だけ厚さが厚くなっている。

## 【0069】

10

20

30

40

50

次に、図2(b)に示すように、エクステンション領域及びハロー領域の形成を行なう。

【0070】

まず、エクステンション注入として、N型不純物であるAs又はPをイオン注入する。注入の条件としては、例えば、注入イオンがAsの場合、注入エネルギーを2keV、ドーズ量を $1 \sim 2 \times 10^{15} / \text{cm}^2$ 、注入角度を0°。(基板1の正面の法線に対して成す角が0°。)とする。

【0071】

この際、Lvtトランジスタ領域RLにおいては、ゲート電極13Lとオフセットスペーサー14Lとがマスクとなって、活性領域1Lに、N型のエクステンション領域17Lが、ゲート電極13Lの下方にオーバーラップ量DLだけ重なるように形成される。

10

【0072】

また、Hvtトランジスタ領域RHにおいては、ゲート電極13Hと、Lvtトランジスタ領域RLにおけるオフセットスペーサー14Lよりも厚いオフセットスペーサー14Hとがマスクとなって、活性領域1Hに、N型のエクステンション領域17Hが、ゲート電極13Hの下方にオーバーラップ量DHだけ重なるように形成される。

【0073】

オフセットスペーサー14Lの方がオフセットスペーサー14Hよりも厚さが薄いので、Lvtトランジスタ領域RL及びHvtトランジスタ領域RHに対して同様にエクステンション注入を行なったとしても、オーバーラップ量DLがオーバーラップ量DHよりも長くなる。よって、実効的なゲート長に差を設けることを目的として、Lvtトランジスタ領域RL及びHvtトランジスタ領域RHに対して別々にエクステンション注入を行なうことは不要になっている。このことから、マスク工程を増加させることなく、互いに閾値電圧の異なる複数の電界効果型トランジスタを同一基板上に設けることができる。

20

【0074】

この後、エクステンション領域17L及び17Hの下方をそれぞれ覆い、基板1との間に位置するP型のハロー領域18L及び18Hを形成する。このためには、P型不純物としてB、BF<sub>2</sub>又はInをイオン注入する。注入の条件としては、例えば、注入イオンがBの場合、注入エネルギーを5~10keV、ドーズ量を $1 \sim 4 \times 10^{13} / \text{cm}^2$ 、注入角度を15~38°とする。

30

【0075】

ここで、Lvtトランジスタ領域RLのオフセットスペーサー14Lの厚さと、Hvtトランジスタ領域RHのオフセットスペーサー14Hの厚さとの差について説明する。

【0076】

半導体装置10において、閾値電圧の低いLvtトランジスタと、閾値電圧の高いHvtトランジスタとの閾値電圧の差は、Lvtトランジスタ及びHvtトランジスタの実効的なゲート長(ゲート電極下方におけるエクステンション領域間の距離)の違いによって実現する。実効的なゲート長の差は、オーバーラップ量DLとDHとの差によって決まるので、必要なゲート長の差に応じて、オフセットスペーサーの厚さの差を設定する。

【0077】

40

具体的に、閾値電圧の低いLvtトランジスタと、閾値電圧の高いHvtトランジスタとの閾値電圧の差は、例えば、50~100mV程度とすることが望ましい。また、実効的なゲート長が8nm変動すると、閾値電圧は100mV変動するものとする。このような場合、実効的なゲート長に4nm~8nmの差が出るように、オフセットスペーサーの厚さについても、ゲート電極の両側でそれぞれ2nm~4nm(合わせて4nm~8nm)の差を設ける。つまり、Hvtトランジスタ領域RHのオフセットスペーサー14Hについて、Lvtトランジスタ領域RLのオフセットスペーサー14Lに比べ、2nm~4nm厚く設定する。言い換えれば、オフセットスペーサー14Hにおける第二層14HBの膜厚を2nm~4nmにすれば良い。

【0078】

50

これにより、オーバーラップ量 D H は、ゲート電極 13 H の両側において 2 nm ~ 4 nm (オーバーラップ量 D L よりも) 大きくなり、実効的なゲート長の差を 4 nm ~ 8 nm とすることができます。

#### 【 0079 】

尚、以上の数値は、ゲート電極 13 L 及び 13 H 自体のゲート長方向の寸法が 40 nm 程度であるときに望ましい一例であるが、これには限らない。ゲート電極の寸法、各種の不純物領域 (エクステンション領域、ソース / ドレイン領域等) の濃度、望ましい閾値電圧の差等に基づいて設定することができる。

#### 【 0080 】

この後、図 2 (c) に示すように、サイドウォールスペーサーと、ソース / ドレイン領域とを形成する。 10

#### 【 0081 】

まず、ゲート電極 13 L、ゲート電極 13 H 等を覆うように、基板 1 上に、SiO<sub>2</sub> 膜、SiN 膜又は SiON 膜の単層膜、あるいはこれらの積層膜からなる絶縁膜を形成する。次に、該絶縁膜に対して異方性ドライエッチングを行ない、ゲート電極 13 L 及びゲート電極 13 H の側方の部分を残して他の部分を除去する。このようにして、ゲート電極 13 L の側方にオフセットスペーサー 14 L を介してサイドウォールスペーサー 15 L を形成する一方、ゲート電極 13 H の側方にオフセットスペーサー 14 H を介してサイドウォールスペーサー 15 H を形成する。この結果、ゲート電極 13 L とサイドウォールスペーサー 15 L との間の距離は、ゲート電極 13 H とサイドウォールスペーサー 15 H との間の距離よりも短くなる。 20

#### 【 0082 】

これまでの工程により、Lvt トランジスタ領域 RL にはゲート構造 11 L、Hvt トランジスタ領域 RH にはゲート構造 11 H が構成される。

#### 【 0083 】

続いて、ゲート構造 11 L 及びゲート構造 11 H をマスクとして、活性領域 1 L 及び活性領域 1 H に、As 等の N 型不純物をイオン注入することにより、ゲート構造 11 L 及びゲート構造 11 H の両側方にそれぞれ N 型のソース / ドレイン領域 16 L 及び 16 H を形成する。 30

#### 【 0084 】

以上により、同一基板上に Lvt トランジスタと Hvt トランジスタとを備えた半導体装置 10 が形成される。このような製造方法によると、マスク工程を増加させることなく閾値電圧の異なる電界効果型トランジスタを形成することができ、製造工程を短縮することが可能になる。

#### 【 0085 】

尚、オフセットスペーサー 14 H を 2 層構造とすることにより、単層構造のオフセットスペーサー 14 L よりも厚くする例を説明したが、他の方法によって厚さに差を設けても良い。オフセットスペーサー 14 L についても複数層からなる構造として、それよりも多くの積層数からなるオフセットスペーサー 14 H を設けても良い。 40

#### 【 0086 】

また、以上では、二種類の電界効果型トランジスタを形成する例を説明したが、これには限らない。例えば、Lvt トランジスタ及び Hvt トランジスタに加えて、これらの中間の閾値電圧を有する Mvt トランジスタを備えていても良い。この場合、オフセットスペーサー 14 L とオフセットスペーサー 14 H との中間の厚さのオフセットスペーサーを設けるようにする。また、SRAM 用トランジスタ等を備える場合に適用することも可能である。

#### 【 0087 】

##### ( 第 2 の実施形態 )

次に、本発明の第 2 の実施形態の半導体装置とその製造方法について、図面を参照しながら説明する。 50

## 【0088】

図3(a)～(c)及び図4(a)～(c)は、本実施形態の例示的半導体装置10aの構造及びその製造方法について模式的に示す図である。図4(c)に示す半導体装置10aのうち、第1の実施形態の半導体装置10と同様の構成要素については図2(c)と同じ符号を用い、以下には相違点について詳しく説明する。

## 【0089】

図4(c)に示すように、半導体装置10aにおいても、閾値電圧の低いLvtトランジスタの形成されたLvtトランジスタ領域RLと、Lvtトランジスタよりも閾値電圧の高いHvtトランジスタの形成されたHvtトランジスタ領域RHとが設けられている。

10

## 【0090】

Lvtトランジスタ領域RLにおいて、P型の基板1における素子分離領域2に囲まれた活性領域1L上に、ゲート絶縁膜12Lを介してゲート電極13Lが形成されている。ゲート電極13Lの側方には、オフセットスペーサーを介すこと無しに、ゲート電極13Lの側壁にサイドウォールスペーサー15Lが接して形成されている。ゲート絶縁膜12L、ゲート電極13L及びサイドウォールスペーサー15Lにより、Lvtトランジスタ領域RLのゲート構造11Lが構成されている。

## 【0091】

また、ゲート電極13Lの下方にオーバーラップ量DLだけ重なるように、N型のエクステンション領域17Lが形成されている。エクステンション領域17Lよりも外側にN型のソース/ドレイン領域16Lが形成され、また、エクステンション領域17Lと基板1との間に、エクステンション領域17Lの下方を覆うように、P型のハロー領域18Lが形成されている。

20

## 【0092】

次に、Hvtトランジスタ領域RHにおいて、P型の基板1における素子分離領域2に囲まれた活性領域1H上に、ゲート絶縁膜12Hを介してゲート電極13Hが形成されている。ゲート電極13Hの側方には、オフセットスペーサー14Hを介してサイドウォールスペーサー15Hが形成されている。ゲート絶縁膜12H、ゲート電極13H、オフセットスペーサー14H及びサイドウォールスペーサー15Hにより、Hvtトランジスタ領域RHのゲート構造11Hが構成されている。

30

## 【0093】

また、ゲート電極13Hの下方にオーバーラップ量DHだけ重なるように、N型のエクステンション領域17Hが形成されている。エクステンション領域17Hよりも外側にN型のソース/ドレイン領域16Hが形成され、また、エクステンション領域17Hと基板1との間に、エクステンション領域17Hの下方を覆うように、P型のハロー領域18Hが形成されている。

## 【0094】

ここで、Lvtトランジスタにおけるオーバーラップ量DLは、Hvtトランジスタにおけるオーバーラップ量DHよりも長い。このため、Lvtトランジスタのゲート電極13L下方におけるエクステンション領域17L間の距離(実効的なゲート長)は、Hvtトランジスタのゲート電極13H下方におけるエクステンション領域17H間の距離よりも短くなっている。

40

## 【0095】

このようにすることによって、Lvtトランジスタの閾値電圧は、Hvtトランジスタの閾値電圧に比べて低くなっている。

## 【0096】

ここで、オーバーラップ量DLとオーバーラップ量DHとの違いは、Lvtトランジスタにはオフセットスペーサーが設けられず、Hvtトランジスタにはオフセットスペーサー14Hが設けられることにより実現されている。

## 【0097】

50

次に、図3(a)～(c)及び図4(a)～(c)を参照して、半導体装置10aの製造方法について説明する。

【0098】

図3(a)には、ゲート電極の形成まで行なわれた状態が示されている。これは、第1の実施形態において図1(a)を参照して説明したのと同様にして形成すればよい。図3(a)の構成を得た後、レジスト20は除去する。

【0099】

次に、図3(b)に示す通り、ゲート電極13L及びゲート電極13Hの上面及び側面を覆うように、オフセットスペーサーとなる絶縁膜14Aを形成する。例えば、SiN膜、SiO<sub>2</sub>膜等を用い、CVD法により2nm～10nmの膜厚に形成する。

10

【0100】

次に、図3(c)に示す通り、基板1上の全面に、異方性エッチングを行なって絶縁膜14Aを全面エッチバックし、ゲート電極の側壁を覆う部分のみを残して他の部分を除去することにより、オフセットスペーサーを形成する。より具体的に、Hvtトランジスタ領域RHのゲート電極13Hの側壁を覆うオフセットスペーサー14Hを形成する。Lvtトランジスタ領域RLにおいても、ゲート電極13Lの側壁を覆うオフセットスペーサー14Lが形成される。

【0101】

次に、図4(a)に示すように、Lvtトランジスタ領域RLにおけるオフセットスペーサー14Lを除去する。このためには、レジストの塗布を行ない、Hvtトランジスタ領域RHのみを覆うレジスト21としてパターニングする。該レジスト21をマスクとしてウェットエッチングを行ない、Lvtトランジスタ領域RLのオフセットスペーサー14Lを選択的に除去する。この後、レジスト21を除去する。

20

【0102】

次に、図4(b)に示すように、N型のエクステンション領域及びP型のハロー領域の形成を行なう。

【0103】

まず、エクステンション注入として、第1の実施形態にて説明したのと同様の条件により、N型不純物であるAs又はPをイオン注入する。

【0104】

30

この際、Lvtトランジスタ領域RLにおいては、ゲート電極13Lだけがマスクとなって、活性領域1Lにエクステンション領域17Lが形成される。エクステンション領域17Lは、ゲート電極13Lの下方にオーバーラップ量DLだけ重なるように形成される。

【0105】

また、Hvtトランジスタ領域RHにおいては、ゲート電極13Hと、オフセットスペーサー14Hとがマスクとなる。エクステンション領域17Hは、ゲート電極13Hの下方にオーバーラップ量DHだけ重なるように形成される。

【0106】

Hvtトランジスタ領域RHにおいてのみオフセットスペーサー14Hが形成されているので、Lvtトランジスタ領域RL及びHvtトランジスタ領域RHに対して同様にエクステンション注入を行なったとしても、オーバーラップ量DLがオーバーラップ量DHよりも長くなる。よって、個別のマスク工程及び注入工程を要すること無しに、LvtトランジスタとHvtトランジスタとの実効的なゲート長に差を設けることができ、互いに閾値電圧の異なる複数の電界効果型トランジスタを同一基板上に設けることができる。

40

【0107】

この後、エクステンション領域17L及び17Hの下方をそれぞれ覆い、基板1との間に位置するハロー領域18L及び18Hを形成する。このためには、P型不純物としてB、BF<sub>2</sub>又はInをイオン注入する。注入の条件としては、第1の実施形態と同様にしても良い。

50

## 【0108】

ここで、 $H_{vt}$ トランジスタ領域 $R_H$ におけるオフセットスペーサー $14H$ の厚さについては、必要なゲート長の差に応じて設定する。

## 【0109】

例えば、 $L_{vt}$ トランジスタと $H_{vt}$ トランジスタとの望ましい閾値電圧の差が $50 \sim 100 \text{ mV}$ 程度である場合を考える。また、実効的なゲート長の $8 \text{ nm}$ の変動に対して閾値電圧は $100 \text{ mV}$ 変動することが分っているとする。このような場合、 $L_{vt}$ トランジスタと $H_{vt}$ トランジスタとの実効的なゲート長の差が $4 \text{ nm} \sim 8 \text{ nm}$ となればよい。そこで、オフセットスペーサー $14H$ の厚さを $2 \text{ nm} \sim 4 \text{ nm}$ に形成すればよい。

## 【0110】

これにより、オーバーラップ量 $DH$ は、ゲート電極 $13H$ の両側においてそれぞれ $2 \text{ nm} \sim 4 \text{ nm}$ （オーバーラップ量 $DL$ よりも）大きくなり、実効的なゲート長の差を $4 \text{ nm} \sim 8 \text{ nm}$ とすることができます。但し、これらの数値は一例であり、ゲート電極の寸法、各種の不純物領域の濃度、望ましい閾値電圧の差等に基づいて設定することができる。

## 【0111】

次に、図4(c)に示すように、サイドウォールスペーサーと、ソース／ドレイン領域とを形成する。

## 【0112】

まず、ゲート電極 $13L$ 、ゲート電極 $13H$ 等を覆うように、基板1上に絶縁膜を形成し、該絶縁膜に対して異方性ドライエッティングを行なうことにより、ゲート電極 $13L$ 側面に接するサイドウォールスペーサー $15L$ と、ゲート電極 $13H$ 側方にオフセットスペーサー $14H$ を介して形成されるサイドウォールスペーサー $15H$ を得る。

## 【0113】

これまでの工程により、 $L_{vt}$ トランジスタ領域 $R_L$ にはゲート構造 $11L$ 、 $H_{vt}$ トランジスタ領域 $R_H$ にはゲート構造 $11H$ が構成される。

## 【0114】

続いて、ゲート構造 $11L$ 及びゲート構造 $11H$ をマスクとして、活性領域 $1L$ 及び活性領域 $1H$ に、 $As$ 等のN型不純物をイオン注入することにより、ゲート構造 $11L$ 及びゲート構造 $11H$ の両側方にそれぞれN型のソース／ドレイン領域 $16L$ 及び $16H$ を形成する。

## 【0115】

以上により、半導体装置 $10a$ が形成される。このような製造方法によると、マスク工程を増加させることなく閾値電圧の異なる電界効果型トランジスタを形成することができ、製造工程を短縮することができる。

## 【0116】

尚、第1の実施形態及び第2の実施形態を組み合わせて、それぞれ閾値電圧の異なる3種類の電界効果型トランジスタを設けることも可能である。つまり、オフセットスペーサーの有無及び厚さの違いを設定することにより、一度のエクステンション注入によって、ゲート電極とエクステンション領域とのオーバーラップ量を3通り又はそれ以上に設定することができる。

## 【0117】

また、第1及び第2の実施形態のいずれにおいてもNチャネル型のトランジスタを例として説明したが、それぞれの構成をPチャネル型トランジスタに適用することも可能である。

## 【0118】

また、 $L_{vt}$ トランジスタ及び $H_{vt}$ トランジスタについて、チャネル注入を別々に行なっても良い。これにより、チャネル注入に関する工程数は増加するが、閾値電圧の制御性を更に向上することができる。

## 【産業上の利用可能性】

## 【0119】

10

20

30

40

50

本開示の技術によると、製造工程の増加を抑制しながら、互いに閾値電圧の異なる複数の電界効果型トランジスタを備えた半導体装置及びその製造方法を実現することができ、半導体装置の微細化にも対応可能である。

【符号の説明】

【0 1 2 0】

|         |              |    |

|---------|--------------|----|

| 1       | 基板           |    |

| 2       | 素子分離領域       |    |

| 1 0     | 半導体装置        |    |

| 1 0 a   | 半導体装置        |    |

| 1 1 H   | ゲート構造        | 10 |

| 1 1 L   | ゲート構造        |    |

| 1 2 H   | ゲート絶縁膜       |    |

| 1 2 L   | ゲート絶縁膜       |    |

| 1 3 H   | ゲート電極        |    |

| 1 3 L   | ゲート電極        |    |

| 1 4 A   | 絶縁膜          |    |

| 1 4 B   | 絶縁膜          |    |

| 1 4 H   | オフセットスペーサー   |    |

| 1 4 H A | 第一層          |    |

| 1 4 H B | 第二層          | 20 |

| 1 4 L   | オフセットスペーサー   |    |

| 1 5 H   | サイドウォールスペーサー |    |

| 1 5 L   | サイドウォールスペーサー |    |

| 1 6 H   | ソース / ドレイン領域 |    |

| 1 6 L   | ソース / ドレイン領域 |    |

| 1 7 H   | エクステンション領域   |    |

| 1 7 L   | エクステンション領域   |    |

| 1 8 H   | ハロー領域        |    |

| 1 8 L   | ハロー領域        |    |

| 2 0     | レジスト         | 30 |

| 2 1     | レジスト         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開2002-231821(JP,A)

特開2009-277771(JP,A)

特開2004-349372(JP,A)

特開2001-110913(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L27/088

H01L27/092

H01L21/8234

H01L21/8238