(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2021-503119

(P2021-503119A)

(43) 公表日 令和3年2月4日(2021.2.4)

| (51) Int.Cl.           | F 1          | テーマコード (参考) |

|------------------------|--------------|-------------|

| G06F 9/34 (2006.01)    | G06F 9/34    | 5B033       |

| G06F 12/0842 (2016.01) | G06F 12/0842 | 5B205       |

| G06F 12/0875 (2016.01) | G06F 12/0875 | 100         |

審査請求 未請求 予備審査請求 未請求 (全 72 頁)

|                                        |                                                                                                                                                                                                                              |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 特願2020-522939 (P2020-522939) | (71) 出願人 390009531<br>インターナショナル・ビジネス・マシーンズ・コーポレーション<br>INTERNATIONAL BUSINESS MACHINES CORPORATION<br>アメリカ合衆国10504 ニューヨーク<br>州 アーモンク ニュー オーチャード<br>ロード<br>New Orchard Road, Armonk, New York 10504, United States of America |

| (86) (22) 出願日 平成30年11月2日 (2018.11.2)   |                                                                                                                                                                                                                              |

| (85) 翻訳文提出日 令和2年4月23日 (2020.4.23)      |                                                                                                                                                                                                                              |

| (86) 國際出願番号 PCT/IB2018/058616          |                                                                                                                                                                                                                              |

| (87) 國際公開番号 WO2019/097344              |                                                                                                                                                                                                                              |

| (87) 國際公開日 令和1年5月23日 (2019.5.23)       |                                                                                                                                                                                                                              |

| (31) 優先権主張番号 15/812,344                |                                                                                                                                                                                                                              |

| (32) 優先日 平成29年11月14日 (2017.11.14)      |                                                                                                                                                                                                                              |

| (33) 優先権主張国・地域又は機関<br>米国(US)           |                                                                                                                                                                                                                              |

|                                        | (74) 代理人 100108501<br>弁理士 上野 剛史                                                                                                                                                                                              |

最終頁に続く

(54) 【発明の名称】メモリベースの構成状態レジスタを提供するコンピュータ・プログラム、コンピュータ・システム、およびコンピュータ実装方法

## (57) 【要約】

【課題】メモリベースの構成状態レジスタを有するコンピュータ・システムを提供。

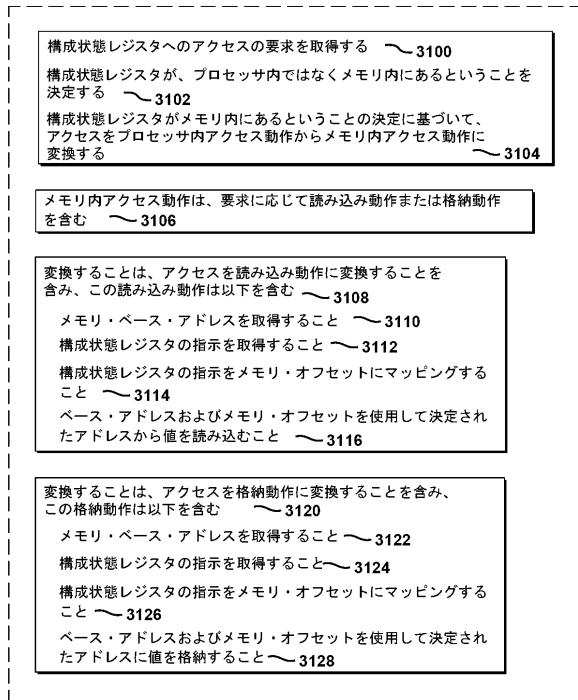

【解決手段】1つまたは複数の構成状態レジスタが、プロセッサ内ではなくメモリ内で提供される。構成状態レジスタへのアクセスの要求が取得される。構成状態レジスタがプロセッサ内ではなくメモリ内にあるということの決定が行われる。構成状態レジスタがメモリ内にあるということの決定に基づいて、アクセスが、プロセッサ内アクセス動作からメモリ内アクセス動作に変換される。例えば、不規則な順序での処理または投機的処理あるいはその両方におけるレジスタの使用を可能にすることによって、処理を容易にする。

【選択図】図6

FIG. 2

**【特許請求の範囲】****【請求項 1】**

コンピューティング環境内の処理を容易にするためのコンピュータ・プログラム製品であって、前記コンピュータ・プログラム製品が、

処理回路によって読み取り可能な、方法を実行するための命令を格納しているコンピュータ可読記憶媒体を備えており、前記方法が、

構成状態レジスタへのアクセスの要求を取得することと、

前記構成状態レジスタがプロセッサ内ではなくメモリ内にあるということを決定することと、

前記構成状態レジスタがメモリ内にあるということの決定に基づいて、前記アクセスを、プロセッサ内アクセス動作からメモリ内アクセス動作に変換することとを含んでいる、コンピュータ・プログラム製品。 10

**【請求項 2】**

前記メモリ内アクセス動作が、前記要求に応じて読み込み動作または格納動作を含んでいる、請求項 1 に記載のコンピュータ・プログラム製品。

**【請求項 3】**

前記変換することが、前記アクセスを読み込み動作に変換することを含んでおり、前記読み込み動作に前記変換することが、

メモリ・ベース・アドレスを取得することと、

前記構成状態レジスタの指示を取得することと、 20

前記構成状態レジスタの前記指示をメモリ・オフセットにマッピングすることと、

前記ベース・アドレスおよび前記メモリ・オフセットを使用して決定されたアドレスから値を読み込むこととを含んでいる、請求項 1 に記載のコンピュータ・プログラム製品。

**【請求項 4】**

前記変換することが、前記アクセスを格納動作に変換することを含んでおり、前記格納動作に前記変換することが、

メモリ・ベース・アドレスを取得することと、

前記構成状態レジスタの指示を取得することと、

前記構成状態レジスタの前記指示をメモリ・オフセットにマッピングすることと、 30

前記ベース・アドレスおよび前記メモリ・オフセットを使用して決定されたアドレスに値を格納することとを含んでいる、請求項 1 に記載のコンピュータ・プログラム製品。

**【請求項 5】**

前記方法が、

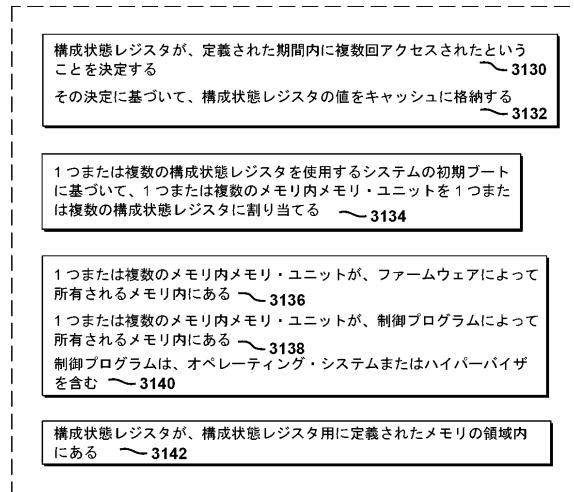

定義された期間内に前記構成状態レジスタが複数回アクセスされたということを決定することと、

前記決定に基づいて、前記構成状態レジスタの値をキャッシュに格納することとをさらに含んでいる、請求項 1 に記載のコンピュータ・プログラム製品。

**【請求項 6】**

前記方法が、1つまたは複数の構成状態レジスタを使用するシステムの初期ブートに基づいて、1つまたは複数のメモリ内メモリ・ユニットを前記1つまたは複数の構成状態レジスタに割り当てるごとをさらに含んでいる、請求項 1 に記載のコンピュータ・プログラム製品。 40

**【請求項 7】**

前記1つまたは複数のメモリ内メモリ・ユニットが、ファームウェアによって所有されるメモリ内にある、請求項 6 に記載のコンピュータ・プログラム製品。

**【請求項 8】**

前記1つまたは複数のメモリ内メモリ・ユニットが、制御プログラムによって所有されるメモリ内にある、請求項 6 に記載のコンピュータ・プログラム製品。

**【請求項 9】**

前記制御プログラムがオペレーティング・システムまたはハイパーバイザを含んでいる 50

、請求項 8 に記載のコンピュータ・プログラム製品。

【請求項 10】

前記構成状態レジスタが、構成状態レジスタ用に定義されたメモリの領域内にある、請求項 1 に記載のコンピュータ・プログラム製品。

【請求項 11】

コンピューティング環境内の処理を容易にするためのコンピュータ・システムであって、前記コンピュータ・システムが、

メモリと、

前記メモリと通信するプロセッサとを備えており、前記コンピュータ・システムが方法を実行するように構成されており、前記方法が、

構成状態レジスタへのアクセスの要求を取得することと、

前記構成状態レジスタがプロセッサ内ではなくメモリ内にあるということを決定することと、

前記構成状態レジスタがメモリ内にあることの決定に基づいて、前記アクセスを、プロセッサ内アクセス動作からメモリ内アクセス動作に変換することとを含んでいる、コンピュータ・システム。

【請求項 12】

前記変換することが、前記アクセスを読み込み動作に変換することを含んでおり、前記読み込み動作に前記変換することが、

メモリ・ベース・アドレスを取得することと、

前記構成状態レジスタの指示を取得することと、

前記構成状態レジスタの前記指示をメモリ・オフセットにマッピングすることと、

前記ベース・アドレスおよび前記メモリ・オフセットを使用して決定されたアドレスから値を読み込むこととを含んでいる、請求項 11 に記載のコンピュータ・システム。

【請求項 13】

前記変換することが、前記アクセスを格納動作に変換することを含んでおり、前記格納動作に前記変換することが、

メモリ・ベース・アドレスを取得することと、

前記構成状態レジスタの指示を取得することと、

前記構成状態レジスタの前記指示をメモリ・オフセットにマッピングすることと、

前記ベース・アドレスおよび前記メモリ・オフセットを使用して決定されたアドレスに値を格納することとを含んでいる、請求項 11 に記載のコンピュータ・システム。

【請求項 14】

前記方法が、

定義された期間内に前記構成状態レジスタが複数回アクセスされたということを決定することと、

前記決定に基づいて、前記構成状態レジスタの値をキャッシュに格納することとをさらに含んでいる、請求項 11 に記載のコンピュータ・システム。

【請求項 15】

前記構成状態レジスタが、構成状態レジスタ用に定義されたメモリの領域内にある、請求項 11 に記載のコンピュータ・システム。

【請求項 16】

コンピューティング環境内の処理を容易にするコンピュータ実装方法であって、前記コンピュータ実装方法が、

プロセッサによって、構成状態レジスタへのアクセスの要求を取得することと、

前記構成状態レジスタがプロセッサ内ではなくメモリ内にあることを決定することと、

前記構成状態レジスタがメモリ内にあることの決定に基づいて、前記アクセスを、プロセッサ内アクセス動作からメモリ内アクセス動作に変換することとを含んでいる、コンピュータ実装方法。

10

20

30

40

50

**【請求項 17】**

前記変換することが、前記アクセスを読み込み動作に変換することを含んでおり、前記読み込み動作に前記変換することが、

メモリ・ベース・アドレスを取得することと、

前記構成状態レジスタの指示を取得することと、

前記構成状態レジスタの前記指示をメモリ・オフセットにマッピングすることと、

前記ベース・アドレスおよび前記メモリ・オフセットを使用して決定されたアドレスから値を読み込むこととを含んでいる、請求項16に記載のコンピュータ実装方法。

**【請求項 18】**

前記変換することが、前記アクセスを格納動作に変換することを含んでおり、前記格納動作に前記変換することが、

メモリ・ベース・アドレスを取得することと、

前記構成状態レジスタの指示を取得することと、

前記構成状態レジスタの前記指示をメモリ・オフセットにマッピングすることと、

前記ベース・アドレスおよび前記メモリ・オフセットを使用して決定されたアドレスに値を格納することとを含んでいる、請求項16に記載のコンピュータ実装方法。

**【請求項 19】**

定義された期間内に前記構成状態レジスタが複数回アクセスされたということを決定することと、

前記決定に基づいて、前記構成状態レジスタの値をキャッシュに格納することとをさらに含んでいる、請求項16に記載のコンピュータ実装方法。

**【請求項 20】**

前記構成状態レジスタが、構成状態レジスタ用に定義されたメモリの領域内にある、請求項16に記載のコンピュータ実装方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

1つまたは複数の態様は、一般に、コンピューティング環境内の処理に関連しており、特に、そのような処理を容易にするコンピュータ・プログラム、コンピュータ・システム、およびコンピュータ実装方法に関連している。なお、「コンピュータ・プログラム」は「コンピュータ・プログラム製品」とも呼ぶ。

**【背景技術】****【0002】**

コンピューティング環境のコンピュータは、コンピュータ内の処理を制御する中央処理装置(CPU: central processing units)またはプロセッサを含んでいる。中央処理装置の動作は、制御レジスタによって制御される。制御レジスタは、例えば、割り込み制御、アドレス指定モードの切り替え、ページング制御、またはコプロセッサ制御、あるいはその組合せなどの、特定のタスクを実行するプロセッサのレジスタである。

**【0003】**

制御レジスタは、プロセッサ・チップの直接上にある半導体素子などの、ラッチとして通常は実装される。一部のコンピュータは、コンピュータのアーキテクチャの実装によって定義されたとおりに、多数の制御レジスタを使用する。したがって、制御レジスタは、チップの面積の増大を表す。

**【0004】**

さらに、一部のコンピュータは、中央処理装置が複数のプロセスまたはスレッドを同時に実行できるマルチスレッドをサポートする。各スレッドは、制御レジスタの別々のセットを使用し、それによってチップ上の制御レジスタの数が増える。

**【0005】**

ラッチベースの制御レジスタの数の増加は、性能、チップ面積、または電力消費、あるいはその組合せに影響を与えることがある。例えば、コンテキスト切り替え時に制御レジ

10

20

30

40

50

スタが切り替えられるため、制御レジスタの数の増加によって、コンテキスト切り替えのコストが増える。さらに、ラッチベースの制御レジスタでは、制御に対する更新がプログラム順序で発生し、このことも性能に影響を与えることがある。

#### 【0006】

異なるアーキテクチャは、制御レジスタについて異なる名前を有することがある。例えば、International Business Machines Corporation(ニューヨーク州アーモンク市)によって提供されるPower Architectureでは、制御レジスタは専用レジスタ(SPR: special purpose register)と呼ばれる。その他のアーキテクチャは、他の名前を使用することがある。本明細書では、制御レジスタの使用は、例えばSPRなどの、他の名前の制御レジスタを含む。

10

#### 【先行技術文献】

#### 【非特許文献】

#### 【0007】

【非特許文献1】“z/Architecture Principles of Operation,” IBM Publication No. SA22-7832-10, March 2015

【非特許文献2】“Power ISA(TM) Version 2.07B,” International Business Machines Corporation, April 9, 2015

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

本発明は、コンピューティング環境内の処理を容易にするためのコンピュータ・プログラム、コンピュータ・システム、およびコンピュータ実装方法を提供する。

20

#### 【課題を解決するための手段】

#### 【0009】

従来技術の欠点が克服され、追加の利点がもたらされるコンピュータ・プログラム製品は、処理回路によって読み取り可能な、方法を実行するための命令を格納しているコンピュータ可読記憶媒体を含む。この方法は、例えば、構成状態レジスタへのアクセスの要求を取得することを含む。構成状態レジスタがプロセッサ内ではなくメモリ内にあることの決定が行われる。構成状態レジスタがメモリ内にあることの決定に基づいて、アクセスが、プロセッサ内アクセス動作からメモリ内アクセス動作に変換される。これは、例えば、不規則な順序での処理または投機的処理あるいはその両方におけるレジスタの使用を可能にすることによって、処理を容易にする。

30

#### 【0010】

例えば、メモリ内アクセス動作は、要求に応じて読み込み動作または格納動作を含む。

#### 【0011】

1つの態様では、この変換は、アクセスを読み込み動作に変換することを含む。読み込み動作に変換することは、メモリ・ベース・アドレスおよび構成状態レジスタの指示を取得することを含む。構成状態レジスタの指示はメモリ・オフセットにマッピングされ、ベース・アドレスおよびメモリ・オフセットを使用して決定されたアドレスから値が読み込まれる。

40

#### 【0012】

別の態様では、この変換は、アクセスを格納動作に変換することを含む。格納動作に変換することは、メモリ・ベース・アドレスおよび構成状態レジスタの指示を取得することを含む。構成状態レジスタの指示はメモリ・オフセットにマッピングされ、ベース・アドレスおよびメモリ・オフセットを使用して決定されたアドレスに値が格納される。

#### 【0013】

さらに別の態様として、定義された期間内に構成状態レジスタが複数回アクセスされたということの決定が行われる。この決定に基づいて、構成状態レジスタの値がキャッシュに格納される。

#### 【0014】

50

1つの実施形態では、1つまたは複数の構成状態レジスタを使用するシステムの初期パートに基づいて、1つまたは複数のメモリ内メモリ・ユニットが1つまたは複数の構成状態レジスタに割り当てられる。

【0015】

1つの例として、1つまたは複数のメモリ内メモリ・ユニットが、ファームウェアによって所有されるメモリ内にある。別の例として、1つまたは複数のメモリ内メモリ・ユニットが、制御プログラムによって所有されるメモリ内にある。制御プログラムは、例えば、オペレーティング・システムまたはハイパーテイプを含む。

【0016】

1つの実施形態では、構成状態レジスタが、構成状態レジスタ用に定義されたメモリの領域内にある。

【0017】

1つまたは複数の態様に関連するコンピュータ実装方法およびシステムも本明細書に記載され、請求される。さらに、1つまたは複数の態様に関連するサービスも本明細書に記載されており、請求されてよい。

【0018】

その他の特徴および長所が、本明細書に記載された技術によって実現される。他の実施形態および態様は、本明細書において詳細に説明され、請求される態様の一部と見なされる。

【0019】

1つまたは複数の態様は、本明細書の最後にある特許請求の範囲において例として具体的に指摘され、明確に請求される。前述の内容、ならびに1つまたは複数の態様の目的、特徴、および長所は、添付の図面と併せて行われる以下の詳細な説明から明らかになる。

【図面の簡単な説明】

【0020】

【図1】本発明の1つまたは複数の態様を組み込んで使用するためのコンピューティング環境の一例を示す図である。

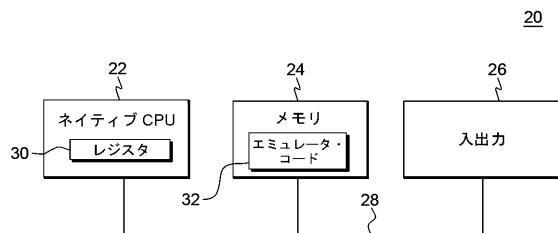

【図2】本発明の1つまたは複数の態様を組み込んで使用するためのコンピューティング環境の別の例を示す図である。

【図3】本発明の1つまたは複数の態様に従って、図1または図2のプロセッサの詳細をさらに示す図である。

【図4】本発明の1つまたは複数の態様に従って使用される命令実行パイプラインの一例の詳細をさらに示す図である。

【図5】本発明の態様に従って、プロセッサの一例の詳細をさらに示す図である。

【図6】本発明の態様に従って、プロセッサ内構成状態レジスタおよびメモリ内構成状態レジスタの一例を示す図である。

【図7】本発明の態様に従って、メモリ内構成状態レジスタを使用することに関連付けられたデコード論理の一例を示す図である。

【図8】本発明の態様に従って、構成状態レジスタ読み込み内部動作の一例を示す図である。

【図9】本発明の態様に従って、構成状態レジスタ格納内部動作の一例を示す図である。

【図10】本発明の態様に従って、メモリ内構成状態レジスタを使用する一例を示す図である。

【図11】本発明の態様に従って、メモリ内構成状態レジスタを使用する別の例を示す図である。

【図12】本発明の態様に従って、構成状態レジスタの書き込み動作の一例を示す図である。

【図13】本発明の態様に従って、構成状態レジスタの読み取り動作の一例を示す図である。

【図14】本発明の態様に従って、構成状態レジスタへの移動または構成状態レジスタか

10

20

30

40

50

らの移動に関連付けられたデコード論理の一実施形態を示す図である。

【図 15】本発明の態様に従って、構成状態レジスタへの移動命令に関連付けられた詳細をさらに示す図である。

【図 16】本発明の態様に従って、構成状態レジスタからの移動命令の詳細をさらに示す図である。

【図 17】本発明の態様に従って、複合構成状態レジスタの読み取り参照に関連付けられた論理の一実施形態を示す図である。

【図 18】本発明の態様に従って、複合構成状態レジスタの書き込み参照に関連付けられた論理の一実施形態を示す図である。

【図 19】本発明の態様に従って、複合構成状態レジスタの一例を示す図である。 10

【図 20】本発明の態様に従って、構成状態レジスタの線形マッピングの一例を示す図である。

【図 21】本発明の態様に従って、構成状態レジスタの線形マッピングの一例を示す図である。

【図 22】本発明の態様に従って、構成状態レジスタの再マッピング・フロー論理の一例を示す図である。

【図 23】複数の構成状態レジスタの格納動作の一例を示す図である。

【図 24】本発明の態様に従って、構成状態レジスター括格納動作の一例を示す図である。 20

【図 25】本発明の態様に従って、構成状態レジスター括読み込み動作の一例を示す図である。

【図 26】本発明の態様に従って、アーキテクチャの構成制御を指定する一例を示す図である。

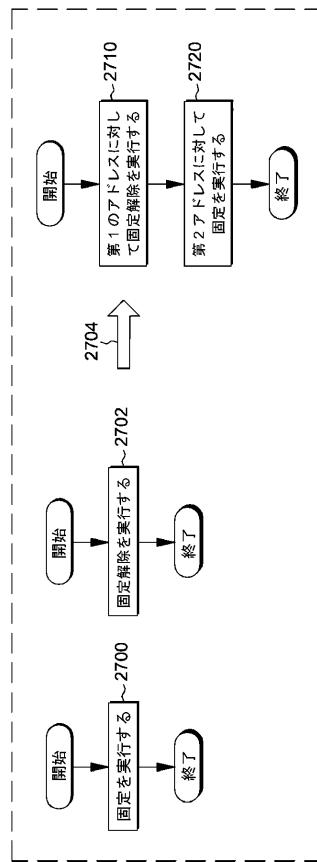

【図 27】本発明の態様に従って、アーキテクチャの構成制御を指定する別の例を示す図である。

【図 28】本発明の態様に従って、コンテキスト切り替えを実行する一例を示す図である。 30

【図 29】本発明の態様に従って、コンテキスト切り替えを実行する別の例を示す図である。

【図 30】本発明の態様に従って、構成状態レジスタへの移動動作に関連付けられたアドレス変換の一実施形態を示す図である。 30

【図 31】本発明の態様に従って、動的アドレス変換を実行する例を示す図である。

【図 32】本発明の態様に従って、動的アドレス変換を実行する例を示す図である。

【図 33】本発明の態様に従って、ページ・テーブル・エントリの一例を示す図である。

【図 34】本発明の態様に従って、特定のコンテキストに関連付けられている特定の構成状態レジスタの一例を示す図である。 40

【図 35】本発明の態様に従って、固定通知をホスト・システムに提供する一実施形態を示す図である。

【図 36】本発明の態様に従って、ページ・テーブル・エントリでの固定動作を指定する一実施形態を示す図である。

【図 37】本発明の態様に従って、ページ・テーブル・エントリでの固定解除動作を指定する一実施形態を示す図である。 40

【図 38】本発明の態様に従って、1回のハイパーバイザの呼び出しで固定動作および固定解除動作を結合する一例を示す図である。

【図 39】本発明の態様に従って、1回の呼び出しに基づいて固定動作および固定解除動作を実行することに関連付けられた詳細をさらに示す図である。

【図 40】本発明の1つまたは複数の態様に従って、データ書き込みのさまざまな例を示す図である。

【図 41】本発明の1つまたは複数の態様に従って、データ書き込みのさまざまな例を示す図である。 50

【図42】本発明の1つまたは複数の態様に従って、データ書き込みのさまざまな例を示す図である。

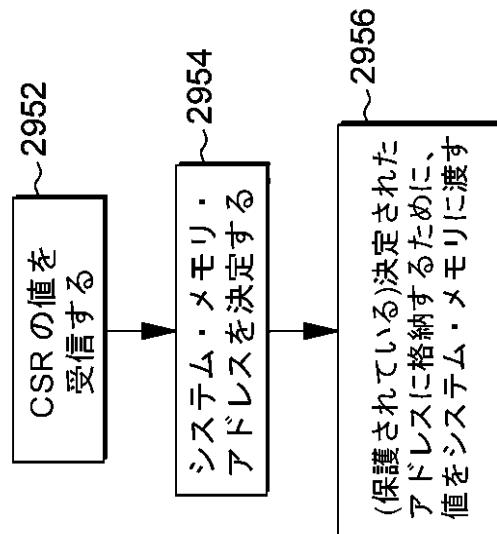

【図43】本発明の1つまたは複数の態様に従って、データ読み取りのさまざまな例を示す図である。

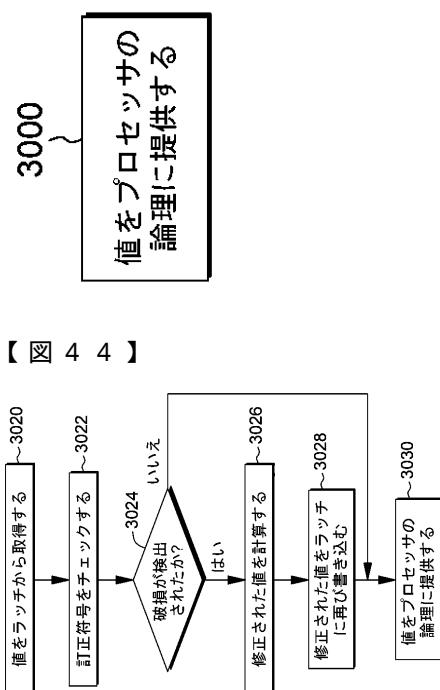

【図44】本発明の1つまたは複数の態様に従って、データ読み取りのさまざまな例を示す図である。

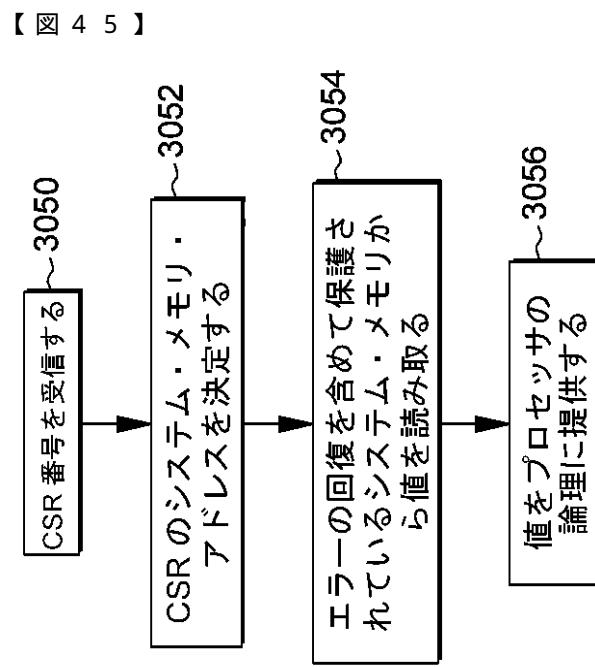

【図45】本発明の1つまたは複数の態様に従って、データ読み取りのさまざまな例を示す図である。

【図46】本発明の態様に従って、コンピューティング環境内の処理を容易にする一実施形態を示す図である。 10

【図47】本発明の態様に従って、コンピューティング環境内の処理を容易にする一実施形態を示す図である。

【図48】本発明の1つまたは複数の態様を組み込んで使用するためのコンピューティング環境の別の例を示す図である。

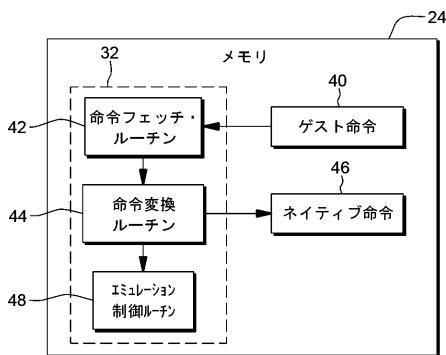

【図49】図48のメモリの詳細をさらに示す図である。

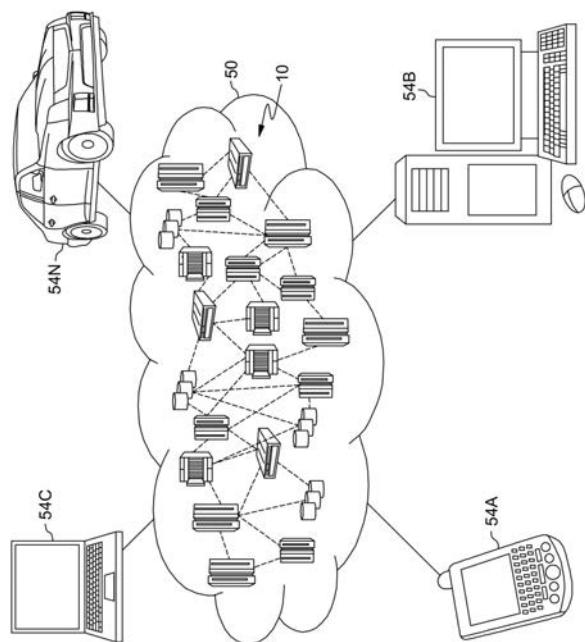

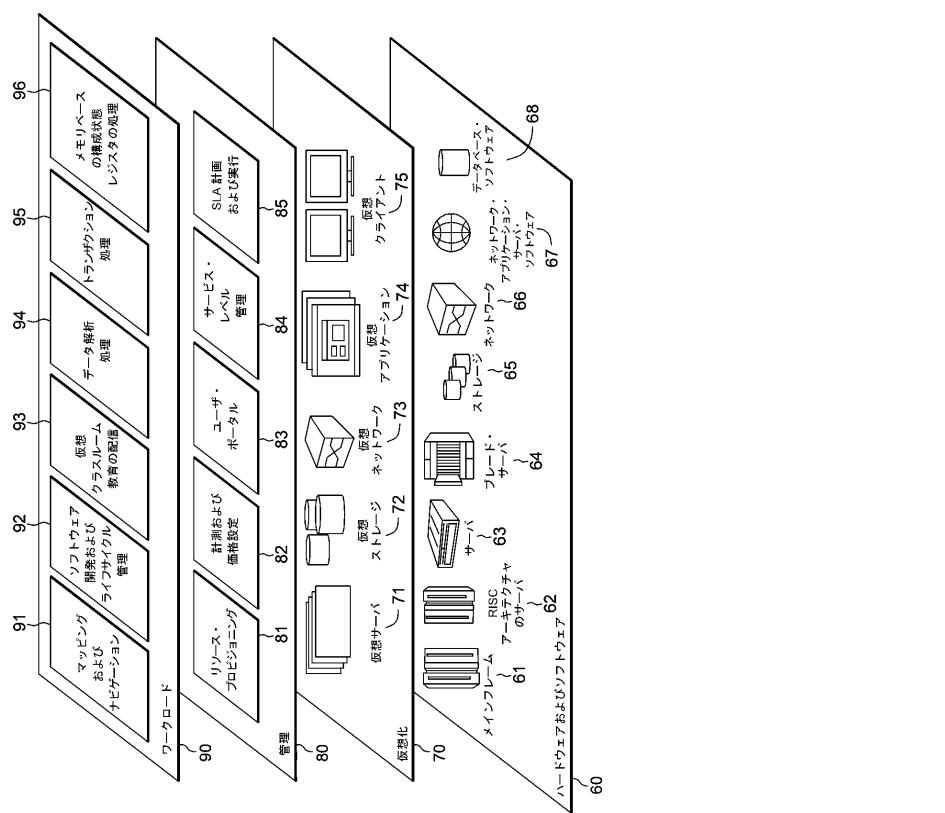

【図50】クラウド・コンピューティング環境の一実施形態を示す図である。

【図51】抽象モデル・レイヤの一例を示す図である。

【発明を実施するための形態】

#### 【0021】

本発明の態様に従って、さまざまな構成状態レジスタが、プロセッサ内ではなくメモリ内で提供される。本明細書において使用されるとき、「構成状態レジスタ」という用語は、制御レジスタ、プログラム状態ワード (P S W : program status word) またはその他のマシン状態レジスタなどのマシン状態レジスタ (M S R : machine state register)、状態レジスタ (例えば、浮動小数点状態制御レジスタ)、専用レジスタ (S P R)、構成レジスタ、または例えば命令の動作を構成するその他のレジスタ、あるいはその組合せを含む。 20

#### 【0022】

選択された構成状態レジスタ (またはさらに別の態様では、その一部) は、メモリ内で提供され、メモリ内でこれらのレジスタは、システム・メモリにマッピングされ、プロセッサに接続されているがプロセッサから離れているメモリ階層に含まれる。メモリ階層は、例えば、読み込み / 格納キュー、1つまたは複数のメモリ・キャッシュ、およびシステム・メモリ (本明細書では、メイン・メモリ、中央記憶装置、ストレージ、主記憶装置、メモリとも呼ばれる) を含む。プロセッサ内ではなくメモリ内に存在することにより、レジスタは、メモリ・アドレスを使用することによってアクセスされ、アクセス要求が、再順序付けされるか、または投機的に処理されてよい。これに対して、プロセッサ内に存在する構成状態レジスタに対するアクセス要求は、不規則な順序では処理されず、投機的にも処理されない。プロセッサ内構成状態レジスタは、例えば直接チップ上で、例えば半導体素子 (ラッチなど) として実装される。「チップ上」は、単一の集積回路に含まれているか、または特定のデバイスと同じ集積回路に含まれている、回路を示すか、またはそのような回路に関連している。 30

#### 【0023】

構成状態レジスタがシステム・メモリに格納されているということに基づいて、構成状態レジスタへの移動命令 (例えば、S P Rへの移動 (m t s p r : move to SPR) 命令) および構成状態レジスタからの移動命令 (例えば、S P Rからの移動 (m f s p r : move from SPR) 命令) などの、特定の命令が、命令デコード論理による読み込み命令または動作および格納命令または動作に置き換えられる。生成された読み込み命令 / 動作および格納命令 / 動作は、格納キューにコミットされ、標準的な読み込み処理および格納処理が実行される。 40

#### 【0024】

1つの例として、構成状態レジスタを含むための記憶領域が、オペレーティング・シス

テムまたはハイパーバイザあるいはその両方によって定義され、メモリベースのレジスタを格納するために確保される。1つの実施形態では、物理メモリ領域がアーキテクチャによって指定される（例えば、物理メモリの最初または最後のnページ）。

#### 【0025】

さらに別の態様では、構成状態レジスタの1つまたは複数の部分がメモリ内に設けられ、一方、構成状態レジスタの1つまたは複数の他の部分がプロセッサ内に設けられる。1つの例では、メモリ内に設けられた部分は、あまり頻繁に使用されない部分である。

#### 【0026】

さらに別の態様では、処理性能を改善するために、通常は一緒に使用される構成状態レジスタ（または少なくともその一部）がメモリ内に一緒に（例えば、単一のキャッシュ・ラインまたは隣接するキャッシュ・ライン内に）配置されるように、構成状態レジスタの再マッピングが提供される。10

#### 【0027】

さらに別の態様では、複数の構成状態レジスタの一括格納または一括読み込みを実行するための命令または動作が提供される。これは、例えば、コンテキスト切り替えを容易にして、その性能を改善するためである。

#### 【0028】

さらに別の1つの態様では、メモリ内のどこに構成状態レジスタが格納されるかを識別するための制御のセットを定義することによって、処理が容易にされ、性能が改善される。20

#### 【0029】

さらに別の態様では、メモリ内構成状態レジスタのメモリ・ポインタを操作することによって、コンテキスト切り替え時の効率が達成される。古い構成データをコピーするのではなく、それらのポインタが操作される。これによって、速度を上げ、コンテキスト切り替え時の複雑さを減らして、コンピューティング環境内の処理を改善する。

#### 【0030】

さらに別の態様では、後で命令の処理において発生する可能性のあるページ・フォールトを防ぐために、ベース・アドレスとして使用されるアドレスを読み込む命令を実行することに基づいて、アドレス変換が自動的に実行される。

#### 【0031】

さらに別の態様では、管理の柔軟性を向上させることによって処理を容易にするために、構成状態レジスタがコンテキストまたはグループ（例えば、ハイパーバイザ、オペレーティング・システム、プロセス、スレッド）別に分離される。30

#### 【0032】

さらに別の態様として、初期化されたメモリ補助の状態のための自動固定の指示が提供される。

#### 【0033】

さらに別の態様では、準仮想化された固定呼び出しを使用して、メモリ・ページの固定が効率的に管理される。

#### 【0034】

さらに別の1つの態様では、システム・メモリがシングル・イベント・アップセットに対して保護される。40

#### 【0035】

本明細書では、さまざまな態様が説明される。さらに、本発明の態様の思想を逸脱することなく、多くの変形が可能である。本明細書に記載された各態様および特徴ならびにその変形を、特に矛盾しない限り、任意の他の態様または特徴と組み合わせができるということに、注意するべきである。

#### 【0036】

本発明の1つまたは複数の態様を組み込んで使用するためのコンピューティング環境の一実施形態が、図1を参照して説明される。1つの例では、コンピューティング環境は、50

International Business Machines Corporation (ニューヨーク州アーモンク市) によって提供される z / Architecture に基づく。z / Architecture の一実施形態は、"z/Architecture Principles of Operation," IBM Publication No. SA22-7832-10, March 2015に記載されており、この文献は本明細書において参照によってその全体が本明細書に組み込まれている。Z / ARCHITECTURE は、International Business Machines Corporation (米国ニューヨーク州アーモンク市) の登録商標である。

#### 【0037】

別の例では、コンピューティング環境は、International Business Machines Corporation (ニューヨーク州アーモンク市) によって提供される Power Architecture に基づく。Power Architecture の一実施形態は、"Power ISA(TM) Version 2.07B," International Business Machines Corporation, April 9, 2015に記載されており、この文献は本明細書において参照によってその全体が本明細書に組み込まれている。POWER ARCHITECTURE は、International Business Machines Corporation (米国ニューヨーク州アーモンク市) の登録商標である。

#### 【0038】

コンピューティング環境は、Intel × 86 アーキテクチャを含むが、これに限定されない、他のアーキテクチャに基づいてもよい。その他の例も存在する。

#### 【0039】

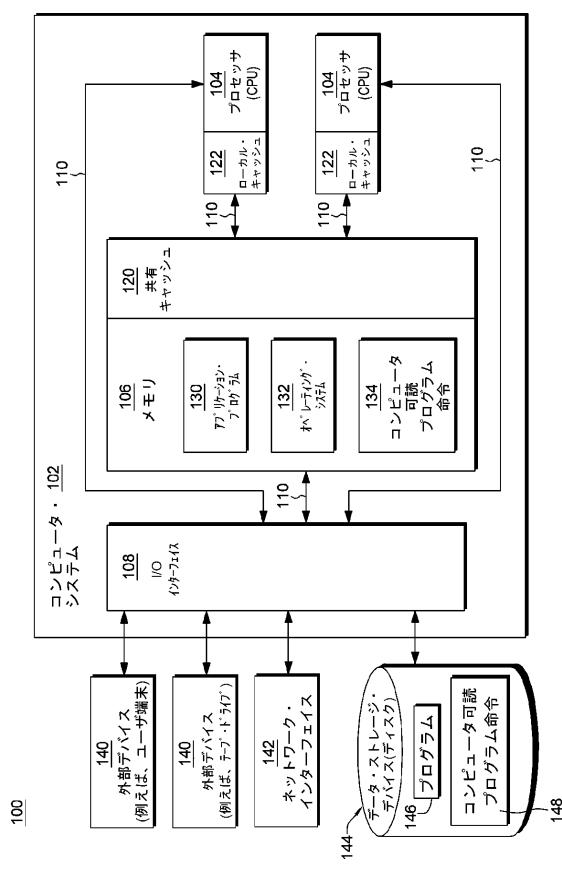

図1に示されているように、コンピューティング環境100は、例えば、汎用コンピューティング・デバイスの形態で示されるコンピュータ・システム102を含んでいる。コンピュータ・システム102は、1つまたは複数のバスまたはその他の接続110あるいはその両方を介して互いに結合された、1つまたは複数のプロセッサまたはプロセッシング・ユニット104（例えば、中央処理装置（CPU））、メモリ106（例えば、システム・メモリ、メイン・メモリ、主記憶装置、中央記憶装置、またはストレージとも呼ばれる）、および1つまたは複数の入出力（I/O：input/output）インターフェイス108を含んでよいが、これらに限定されない。

#### 【0040】

バス110は、メモリ・バスまたはメモリ・コントローラ、ペリフェラル・バス、アクセラレーテッド・グラフィックス・ポート、およびさまざまなバス・アーキテクチャのいずれかを使用するプロセッサまたはローカル・バスを含む、複数の種類のバス構造のいずれかのうちの1つまたは複数を表す。例として、そのようなアーキテクチャは、ISA (Industry Standard Architecture)、MCA (Micro Channel Architecture)、EISA (Enhanced ISA)、VESA (Video Electronics Standards Association) ローカル・バス、およびPCI (Peripheral Component Interconnects) を含むが、これらに限定されない。

#### 【0041】

メモリ106は、例えば、プロセッサ104のローカル・キャッシュ122に結合されてよい、共有キャッシュなどのキャッシュ120を含んでよい。さらに、メモリ106は、1つまたは複数のプログラムまたはアプリケーション130、オペレーティング・システム132、および1つまたは複数のコンピュータ可読プログラム命令134を含んでよい。コンピュータ可読プログラム命令134は、本発明の態様の実施形態の機能を実行するように構成されてよい。

#### 【0042】

コンピュータ・システム102は、例えばI/Oインターフェイス108を介して、1つまたは複数の外部デバイス140、1つまたは複数のネットワーク・インターフェイス142、または1つまたは複数のデータ・ストレージ・デバイス144、あるいはその組合せと通信してもよい。外部デバイスの例としては、ユーザ端末、テープ・ドライブ、ポ

10

20

30

40

50

インティング・デバイス、ディスプレイなどが挙げられる。ネットワーク・インターフェイス 142 は、コンピュータ・システム 102 が、ローカル・エリア・ネットワーク (L A N : local area network)、一般的な広域ネットワーク (W A N : wide area network)、またはパブリック・ネットワーク (例えば、インターネット)、あるいはその組合せなどの 1 つまたは複数のネットワークと通信できるようにし、他のコンピューティング・デバイスまたはシステムとの通信を実現する。

#### 【 0 0 4 3 】

データ・ストレージ・デバイス 144 は、1 つまたは複数のプログラム 146、1 つまたは複数のコンピュータ可読プログラム命令 148、またはデータ、あるいはその組合せなどを格納してよい。コンピュータ可読プログラム命令は、本発明の態様の実施形態の機能を実行するように構成されてよい。

10

#### 【 0 0 4 4 】

コンピュータ・システム 102 は、取り外し可能 / 取り外し不可、揮発性 / 不揮発性のコンピュータ・システム・ストレージ媒体を含むか、またはそのようにコンピュータ・システム・ストレージ媒体に結合されるか、あるいはその両方であってよい。例えば、コンピュータ・システム 102 は、取り外し不可、不揮発性の磁気媒体 (通常は、「ハード・ドライブ」と呼ばれる)、取り外し可能、不揮発性の磁気ディスク (例えば、「フロッピー・ディスク」) に対する読み取りと書き込みを行うための磁気ディスク・ドライブ、あるいは C D - R O M、D V D - R O M、またはその他の光媒体などの取り外し可能、不揮発性の光ディスクに対する読み取りと書き込みを行うための光ディスク・ドライブ、あるいはその組合せを含むか、またはこれらに結合されるか、あるいはその両方であってよい。その他のハードウェア・コンポーネントまたはソフトウェア・コンポーネントあるいはその両方を、コンピュータ・システム 102 と併用できるということが理解されるべきである。その例として、マイクロコード、デバイス・ドライバ、冗長プロセッシング・ユニット、外部ディスク・ドライブ・アレイ、R A I D システム、テープ・ドライブ、およびデータ・アーカイブ・ストレージ・システムなどが挙げられるが、これらに限定されない。

20

#### 【 0 0 4 5 】

コンピュータ・システム 102 は、他の多数の汎用または専用のコンピューティング・システム環境または構成で運用されてよい。コンピュータ・システム 102 での使用に適した周知のコンピューティング・システム、環境、または構成、あるいはその組合せの例としては、パーソナル・コンピュータ (P C : personal computer) システム、サーバ・コンピュータ・システム、シン・クライアント、シック・クライアント、ハンドヘルドまたはラップトップ・デバイス、マイクロプロセッサ・システム、マイクロプロセッサベース・システム、セット・トップ・ボックス、プログラマブル・コンシューマ・エレクトロニクス、ネットワーク P C、マイクロコンピュータ・システム、メインフレーム・コンピュータ・システム、およびこれらのシステムまたはデバイスのいずれかを含む分散クラウド・コンピューティング環境などが挙げられるが、これらに限定されない。

30

#### 【 0 0 4 6 】

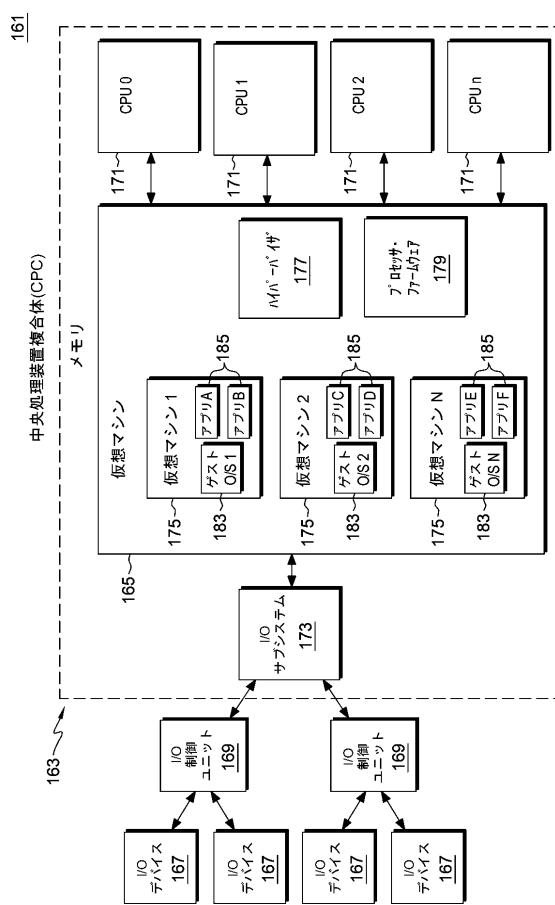

別の実施形態では、コンピューティング環境が仮想マシンをサポートする。そのような環境の一例が、図 2 を参照して説明される。1 つの例では、コンピューティング環境 161 は、仮想マシンをサポートする中央処理装置複合体 (C P C : central processor complex) 163 を含んでいる。C P C 163 は、1 つまたは複数の制御ユニット 169 を介して 1 つまたは複数の入出力 (I / O) デバイス 167 に結合される。中央処理装置複合体 163 は、例えば、1 つまたは複数のプロセッサ (中央処理装置 (C P U : central processing unit) とも呼ばれる) 171 に結合されたメモリ 165 (システム・メモリ、メイン・メモリ、主記憶装置、中央記憶装置、ストレージとも呼ばれる)、および入出力サブシステム 173 を含んでおり、これらの各々が下で説明される。

40

#### 【 0 0 4 7 】

メモリ 165 は、例えば、1 つまたは複数の仮想マシン 175、仮想マシンを管理する

50

仮想マシン・マネージャ（ハイパーバイザ 177など）、およびプロセッサ・ファームウェア 179を含んでいる。ハイパーバイザ 177の1つの例は、International Business Machines Corporation（ニューヨーク州アーモンク市）によって提供される z/VMである。ハイパーバイザは、ホストと呼ばれることがある。さらに、本明細書において使用されるとき、ファームウェアは、例えば、プロセッサのマイクロコードを含む。ファームウェアは、例えば、上位レベルの機械コードの実装において使用される、ハードウェア・レベルの命令またはデータ構造あるいはその両方を含む。1つの実施形態では、ファームウェアは、例えば、信頼できるソフトウェアを含んでいるマイクロコード、または基盤になるハードウェアに固有のマイクロコードとして通常は提供される、システムのハードウェアへのオペレーティング・システムのアクセスを制御する独自のコードを含む。

10

#### 【0048】

CPC の仮想マシンのサポートは、多数の仮想マシン 175 を動作させることができるようにし、各仮想マシン 175 は、異なるプログラム 185 で動作し、Linux などのゲスト・オペレーティング・システム 183 を実行することができる。各仮想マシン 175 は、別々のシステムとして機能することができる。すなわち、各仮想マシンは、独立してリセットされ、ゲスト・オペレーティング・システムを実行し、異なるプログラムで動作することができる。仮想マシン内で実行されるオペレーティング・システムまたはアプリケーション・プログラムは、完全なシステム全体にアクセスできるように見えるが、実際は、その一部のみが利用可能である。

20

#### 【0049】

メモリ 165 は、仮想マシンに割り当て可能な物理プロセッサ・リソースである、プロセッサ（例えば、CPU）171 に結合される。例えば、仮想マシン 175 は、1つまたは複数の論理プロセッサを含み、それらの論理プロセッサの各々は、仮想マシンに動的に割り当てることができる物理プロセッサ・リソース 171 の全部または一部を表す。

#### 【0050】

さらに、メモリ 165 は、I/O サブシステム 173 に結合される。入出力サブシステム 173 は、入出力制御ユニット 169 およびデバイス 167 と主記憶装置 165 の間の情報の流れを管理する。入出力サブシステム 173 は中央処理装置複合体に結合され、この結合において、入出力サブシステム 173 は中央処理装置複合体の一部であるか、または中央処理装置複合体から分離することができる。

30

#### 【0051】

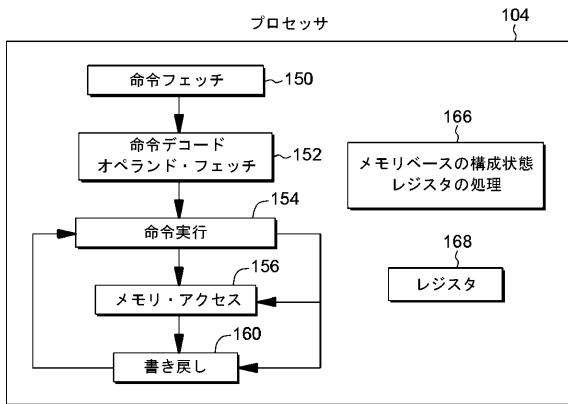

さらに、プロセッサ 104（またはプロセッサ 171）などのプロセッサの一例に関する詳細が、図 3 を参照して説明される。プロセッサ 104（またはプロセッサ 171）などのプロセッサは、命令を実行するために使用される複数の機能コンポーネントを含む。これらの機能コンポーネントは、例えば、実行される命令をフェッチするための命令フェッチ・コンポーネント 150 と、フェッチされた命令をデコードするため、およびデコードされた命令のオペランドを取得するための命令デコード・ユニット 152 と、デコードされた命令を実行するための命令実行コンポーネント 154 と、必要な場合に、命令を実行するためにメモリにアクセスするためのメモリ・アクセス・コンポーネント 156 と、実行された命令の結果を提供するための書き戻しコンポーネント 160 とを含む。これらのコンポーネントのうちの1つまたは複数は、本発明の態様に従って、メモリベースの構成状態レジスタの処理 166 に関連付けられた1つまたは複数の命令または動作あるいはその両方を実行するために使用されてよい。

40

#### 【0052】

プロセッサ 104（またはプロセッサ 171）は、1つの実施形態では、機能コンポーネントのうちの1つまたは複数によって使用される1つまたは複数のレジスタ 168 も含む。プロセッサ 104（またはプロセッサ 171）は、本明細書で提供されている例よりも多いコンポーネント、少ないコンポーネント、またはその他のコンポーネント、あるいはその組合せを含んでよい。

50

## 【0053】

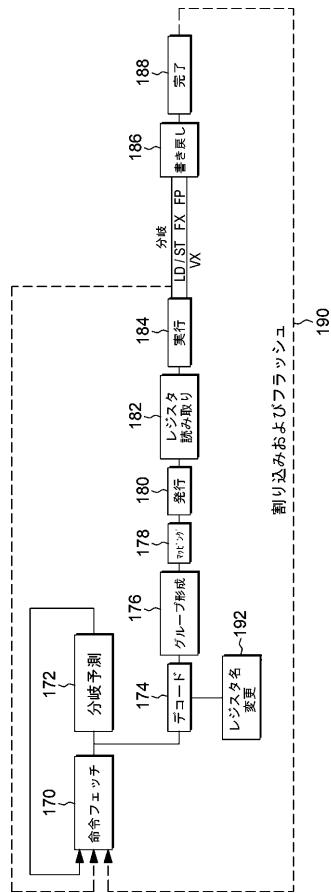

さらに、プロセッサ104またはプロセッサ171などのプロセッサの実行パイプラインに関する詳細が、図4を参照して説明される。本明細書では、パイplineのさまざまな処理段階が図に示されて説明されているが、本発明の態様の思想から逸脱することなく、追加の段階、より少ない段階、またはその他の段階、あるいはその組合せが使用されてよいということが理解されるであろう。

## 【0054】

図4を参照すると、1つの実施形態では、命令が命令キューからフェッチされ(170)、命令の分岐予測172またはデコーディング174あるいはその両方が実行されてよい。デコードされた命令が、一緒に処理される命令のグループ176に追加されてよい。グループ化された命令がマッパー178に提供され、マッパー178が、任意の依存関係を決定し、リソースを割り当て、命令／動作のグループを適切な発行キューにディスパッチする。例えば分岐、読み込み／格納、浮動小数点、固定小数点、ベクトルなどを含む、異なる種類の実行ユニットに対して、1つまたは複数の発行キューが存在する。発行段階180の間に、命令／動作が適切な実行ユニットに発行される。いずれかのレジスタが読み取られて(182)、そのソースを取り出し、実行段階184の間に命令／動作が実行される。示されているように、この実行は、分岐の場合、例えば、読み込み(LD)または格納(ST)、固定小数点演算(FX)、浮動小数点演算(FP)、またはベクトル演算(VX)であってよい。書き戻し段階186の間に、いずれかの結果が適切なレジスタに書き込まれる。その後、命令が完了する(188)。割り込みまたはフラッシュ190が存在する場合、処理が命令フェッチ170に戻ってよい。

10

20

30

## 【0055】

さらに、1つの例では、レジスタの保存／復元において使用されてよいレジスタ名変更ユニット192が、デコード・ユニットに結合される。

## 【0056】

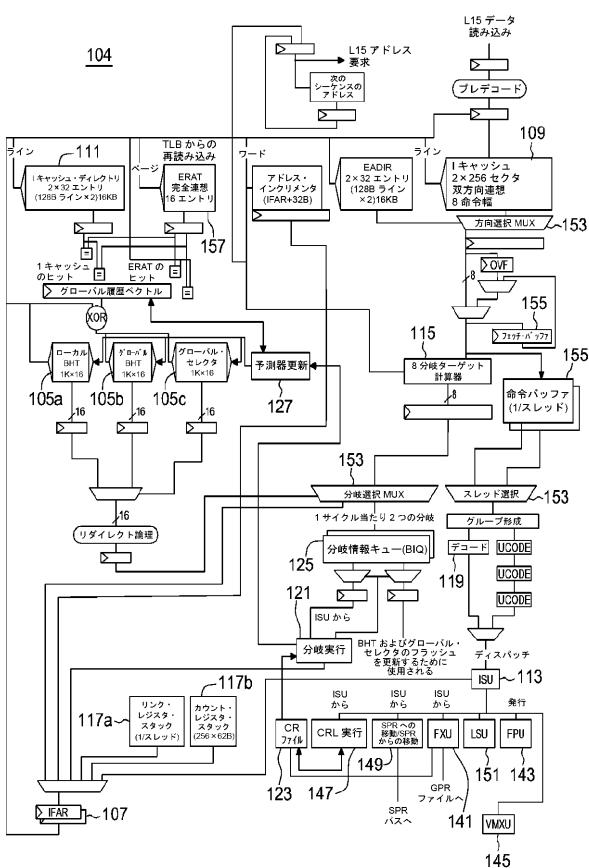

プロセッサに関する他の詳細が、図5を参照して説明される。1つの例では、プロセッサ104(またはプロセッサ171)などのプロセッサは、予測ハードウェア、レジスタ、キャッシュ、デコーダ、命令順序付けユニット、および命令実行ユニットを例として含んでよい、パイpline型プロセッサである。予測ハードウェアは、例えば、ローカル分岐履歴テーブル(BHT:branch history table)105a、グローバル分岐履歴テーブル(BHT)105b、およびグローバル・セレクタ105cを含む。予測ハードウェアは、次の命令フェッチのアドレスを有する命令フェッチ・アドレス・レジスタ(IFAR:instruction fetch address register)107を介してアクセスされる。

30

## 【0057】

同じアドレスが、「フェッチ・グループ」と呼ばれる複数の命令をフェッチしてよい命令キャッシュ109にも提供される。ディレクトリ111が命令キャッシュ109に関連付けられる。

## 【0058】

キャッシュおよび予測ハードウェアは、同じアドレスを使用してほぼ同時にアクセスされる。予測ハードウェアが、フェッチ・グループ内の命令に使用できる予測情報を含んでいる場合、その予測が命令順序付けユニット(ISU:instruction sequencing unit)113に転送され、次に、命令順序付けユニット113が、命令を実行するために実行ユニットに発行する。この予測は、分岐ターゲット計算115および分岐ターゲット予測ハードウェア(リンク・レジスタ予測スタック117aおよびカウント・レジスタ・スタック117bなど)と連動してIFAR107を更新するために使用されてよい。予測情報を使用できないが、1つまたは複数の命令デコーダ119がフェッチ・グループ内で分岐命令を検出した場合、そのフェッチ・グループに関する予測が作成される。予測された分岐が、分岐情報キュー(BIQ:branch information queue)125などの予測ハードウェアに格納され、ISU113に転送される。

40

## 【0059】

50

I S U 1 1 3 によって分岐実行ユニット (B R U : branch execution unit) 1 2 1 に発行された命令に応答して、分岐実行ユニット 1 2 1 が動作する。B R U 1 2 1 は、条件レジスタ (C R : condition register) ファイル 1 2 3 に対する読み取りアクセス権限を有する。さらに分岐実行ユニット 1 2 1 は、分岐スキャン論理 (branch scan logic) によって分岐情報キュー 1 2 5 に格納された情報にアクセスして、分岐予測の成功を決定することができ、マイクロプロセッサによってサポートされる 1 つまたは複数のスレッドに対応する命令フェッチ・アドレス・レジスタ (I F A R) 1 0 7 に、動作可能なように結合される。少なくとも 1 つの実施形態に従って、B I Q エントリが識別子によって (例えば、分岐タグ (B T A G : branch tag) によって) 関連付けられ、識別される。B I Q エントリに関連付けられた分岐が完了したときに、そのことが B I Q エントリにマーク付けされる。B I Q エントリはキュー内で維持され、完了した分岐に関連付けられた情報を含んでいるとしてキュー・エントリがマーク付けされるときに、最も古いキュー・エントリの割り当てが順次解除される。B R U 1 2 1 は、B R U 1 2 1 が分岐予測ミスを発見したときに予測器の更新を引き起こすように、動作可能なようにさらに結合される。

10

## 【0060】

命令が実行されるときに、B R U 1 2 1 が、予測が誤っているかどうかを検出する。予測が誤っている場合は、予測が更新される。この目的のために、プロセッサは予測器更新論理 1 2 7 も含んでいる。予測器更新論理 1 2 7 は、分岐実行ユニット 1 2 1 からの更新指示に応答して、ローカル B H T 1 0 5 a、グローバル B H T 1 0 5 b、およびグローバル・セレクタ 1 0 5 c のうちの 1 つまたは複数に含まれる配列エントリを更新するよう構成される。予測器ハードウェア 1 0 5 a、1 0 5 b、および 1 0 5 c は、命令フェッチおよび予測動作によって使用される、読み取りポートと異なる書き込みポートを有してよく、または単一の読み取り / 書き込みポートが共有されてよい。予測器更新論理 1 2 7 は、リンク・スタック 1 1 7 a およびカウント・レジスタ・スタック 1 1 7 b に動作可能なようにさらに結合されてよい。

20

## 【0061】

ここで条件レジスタ・ファイル (C R F : condition register file) 1 2 3 を参照すると、C R F 1 2 3 は、B R U 1 2 1 によって読み取りアクセス可能であり、固定小数点ユニット (F X U : fixed point unit) 1 4 1、浮動小数点ユニット (F P U : floating point unit) 1 4 3、およびベクトル・マルチメディア拡張ユニット (V M X U : vector multimedia extension unit) 1 4 5 を含むが、これらに限定さない、実行ユニットによって書き込み可能である。条件レジスタ論理 (C R L : condition register logic) 実行ユニット 1 4 7 (C R U とも呼ばれる) および専用レジスタ (S P R : special purpose register) 処理論理 1 4 9 は、条件レジスタ・ファイル (C R F) 1 2 3 に対する読み取りおよび書き込みアクセス権限を有する。C R U 1 4 7 は、C R F ファイル 1 2 3 に格納された条件レジスタに対して論理演算を実行する。F X U 1 4 1 は、C R F 1 2 3 に対して書き込み更新を実行することができる。

30

## 【0062】

プロセッサ 1 0 4 (またはプロセッサ 1 7 1) は、読み込み / 格納ユニット 1 5 1、ならびにさまざまなマルチブレクサ 1 5 3 およびバッファ 1 5 5 に加えて、アドレス変換テーブル 1 5 7 およびその他の回路をさらに含む。

40

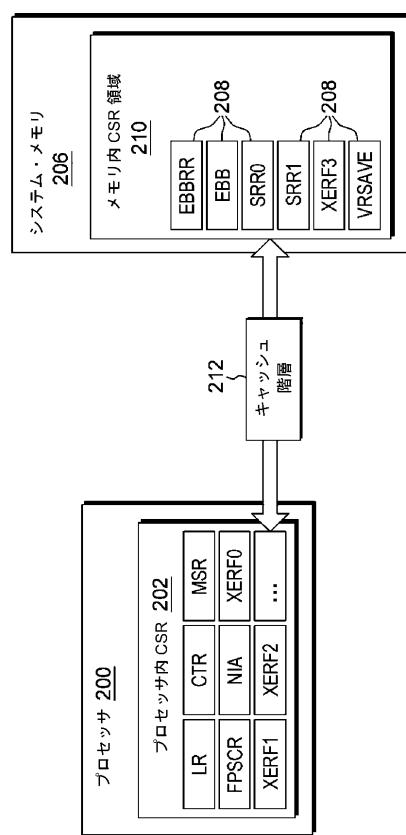

## 【0063】

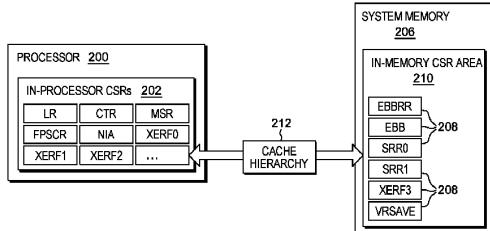

さらに、プロセッサ 1 0 4 またはプロセッサ 1 7 1 などのプロセッサ 2 0 0 によって使用されるさまざまなレジスタに関する詳細が、図 6 を参照して説明される。図に示されているように、プロセッサ 2 0 0 は、複数のプロセッサ内構成状態レジスタ (C S R : configuration state registers) 2 0 2 を含んでいる。例として、プロセッサ内構成状態レジスタは、リンク・レジスタ (L R : link register)、カウンタ・レジスタ (C T R : counter register)、マシン状態レジスタ (M S R)、浮動小数点状態制御レジスタ (F P S C R : floating point status control register)、次命令アドレス (N I A : next instruction address) レジスタ、および 1 つまたは複数の整数例外レジスタ (X E R : e

50

xception register) を含んでいる。さらに、本発明の態様に従って、プロセッサ 200 に結合されたシステム・メモリ 206 は、1つまたは複数のメモリ内構成状態レジスタ 208 を含んでいる。例として、メモリ内構成状態レジスタは、イベントベースの分岐復帰レジスタ (E B B R R : event based branch return registers)、イベントベースの分岐 (E B B : event based branch) レジスタ、状態回復レジスタ (S R R : state restoration registers)、整数例外レジスタ (X E R)、およびベクトル・レジスタ保存 (V R S A V E : vector register save) レジスタを含んでいる。1つの例では、メモリ内構成状態レジスタ 208 は、システム・メモリ 206 のメモリ内構成状態レジスタ領域 210 に格納される。

## 【0064】

10

頻繁にアクセスされる（例えば、連続的に複数回アクセスされる）構成状態レジスタは、プロセッサ 200 およびシステム・メモリ 206 に結合されたキャッシュ階層 212 に移動されてよい。

## 【0065】

1つの態様に従って、メモリ内に移動または配置されている1つまたは複数の構成状態レジスタに基づいて、それらの構成状態レジスタへのプロセッサ内のアクセスが、メモリへのアクセスに置き換えられる。アクセスの種類を決定するデコード論理の一例が、図7を参照して説明される。この処理は、例えばプロセッサのデコード・ユニットまたは別のユニットあるいはその両方によって実行される。

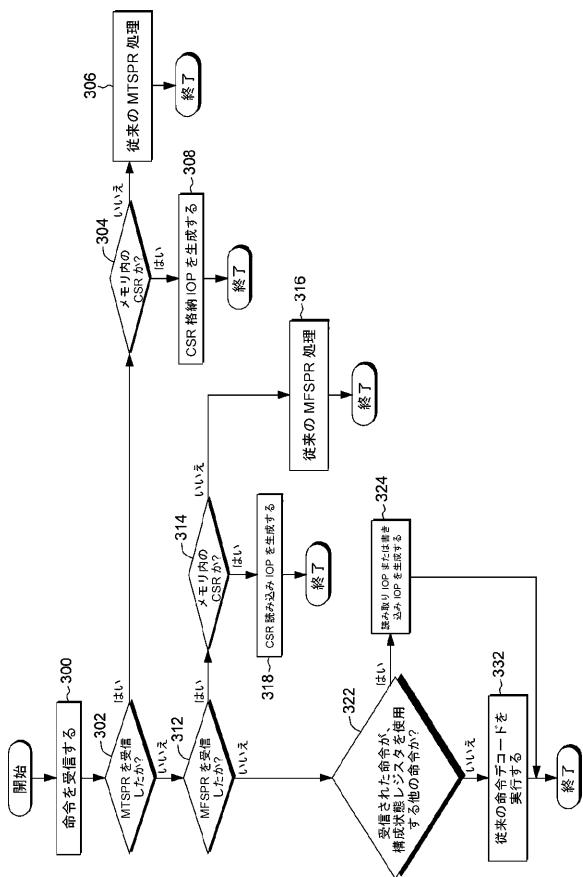

## 【0066】

20

図7を参照すると、最初に命令が受信される（ステップ300）。命令がS P Rへの移動 (m t s p r) 命令などの構成状態レジスタへの移動命令であるかどうかに関する判定が行われる（照会302）。命令が構成状態レジスタへの移動命令である場合、命令内で示された構成状態レジスタがメモリ内構成状態レジスタであるかどうかに関する判定がさらに行われる（照会304）。メモリ内構成状態レジスタでない場合、構成状態レジスタへの移動命令の従来の処理が実行される（ステップ306）。しかし、構成状態レジスタがメモリ内構成状態レジスタである場合、構成状態レジスタをメモリに格納する（例えば、構成状態レジスタの新しい内容をメモリに格納する）ために、構成状態レジスタ格納内部動作が生成される（ステップ308）。

## 【0067】

30

照会302に戻ると、受信された命令が構成状態レジスタへの移動命令でない場合、命令がS P Rからの移動 (m f s p r) 命令などの構成状態レジスタからの移動命令であるかに関する判定がさらに行われる（照会312）。命令が構成状態レジスタからの移動命令である場合、命令内で示された構成状態レジスタがメモリ内であるかどうかに関する判定が行われる（照会314）。メモリ内でない場合、従来の構成状態レジスタからの移動処理が実行される（ステップ316）。メモリ内である場合、レジスタの内容をメモリから取得するために、構成状態レジスタ読み込み内部動作が生成される（ステップ318）。

## 【0068】

照会312に戻ると、受信された命令が構成状態レジスタへの移動命令でも構成状態レジスタからの移動命令でもない場合、受信された命令が、構成状態レジスタを使用する別の命令であるかどうかを判定するための判定がさらに実行されてよい（照会322）。受信された命令が構成状態レジスタを使用する別の命令である場合、命令によって実行されている機能に応じて、読み取りまたは書き込みあるいはその両方の内部動作が生成されてよい（ステップ324）。受信された命令が構成状態レジスタを使用する別の命令でない場合、処理がステップ332に進み、ステップ332で従来の命令デコード処理が実行される。

## 【0069】

本発明の他の態様では、構成状態レジスタを読み込み、構成状態レジスタ値を格納するための内部動作が、命令に対応しないプロセッサの動作を実行することと連動して、例え

40

50

ば、割り込み要求を受信することに応答して例外ハンドラに移行することに応答して、実行される。

#### 【0070】

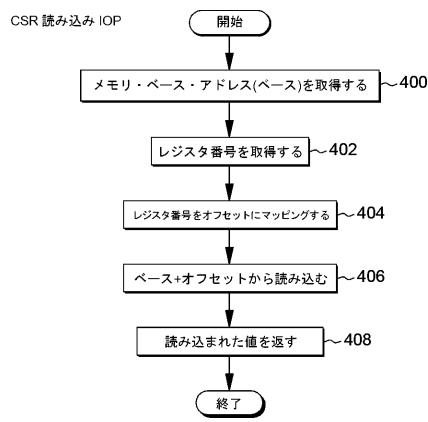

構成状態レジスタ読み込み内部動作に関する詳細が、図8を参照してさらに説明される。この処理は、プロセッサによって実行される。図8を参照すると、最初にメモリ・ベース・アドレス（ベース）が、構成状態レジスタを含んでいるメモリのベース・アドレスであるメモリ・ユニット（例えば、メモリ・ページ）のアドレスを含んでいるレジスタまたは位置（例えば、スレッド制御ベース・レジスタ（TCBR：thread control base register）などのベース・レジスタ）から取得される（ステップ400）。さらに、動作において示されるレジスタ番号が取得される（ステップ402）。そのレジスタ番号が、メモリ内のオフセットにマッピングされる（ステップ404）。例えば、各構成状態レジスタ番号（または別の実施形態では、他の識別情報）が、メモリ内の特定の位置にマッピングされる。その位置は、ベース・アドレスからの特定の数量（例えば、オフセット）である。次に、アドレス（ベース・アドレスにオフセットを加算したアドレス）からの読み込みが実行され（ステップ406）、読み込まれた値が返される（ステップ408）。

10

#### 【0071】

本明細書において使用されるとき、ベースとは、メモリ内構成状態レジスタを含んでいるメモリのベース・アドレスのことを指し、ベース・レジスタとは、ベースを含んでいるレジスタのことを指す。ベース・レジスタの一例はスレッド制御ベース・レジスタ（TCBR）であるが、他の文脈（例えば、オペレーティング・システムなど）では、他のベース・レジスタを使用することがある。

20

#### 【0072】

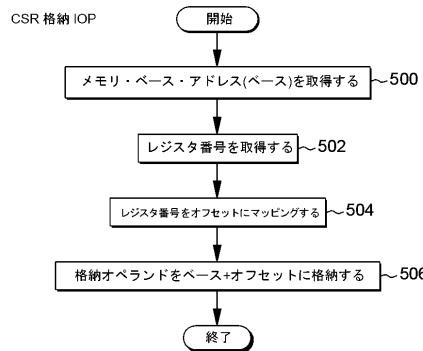

構成状態レジスタ格納内部動作に関する詳細が、図9を参照してさらに説明される。この処理は、プロセッサによって実行される。図9を参照すると、最初にメモリ・ベース・アドレス（ベース）が、例えばベース・レジスタから（例えばTCBRから）取得され（ステップ500）、動作において示されたレジスタ番号も取得される（ステップ502）。レジスタ番号がメモリ内のオフセットにマッピングされ（ステップ504）、格納のオペランド（例えば、レジスタの内容）が、ベース・アドレスにオフセットを加算することによって指定されたアドレスに格納される（ステップ506）。

30

#### 【0073】

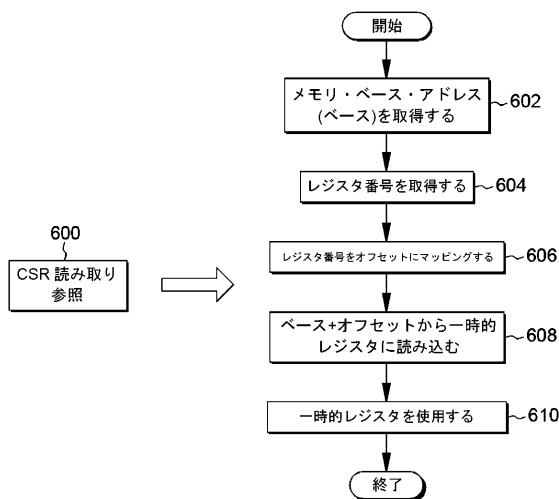

上で示されたように、構成状態レジスタからの移動命令でも構成状態レジスタへの移動命令でもない命令が構成状態レジスタを使用することがある。したがって、そのような命令のうちの1つに関連付けられた処理が、図10を参照して説明される。この処理は、プロセッサによって実行される。図10を参照すると、この実施形態では、構成状態レジスタの読み取り参照を含んでいる命令／動作が取得される（ステップ600）。それに基づいて、命令／動作において示された構成状態レジスタのメモリ・ベース・アドレス（ベース）が、例えばベース・レジスタから（例えばTCBRから）取得され（ステップ602）、命令／動作において示されたレジスタ番号も取得される（ステップ604）。レジスタ番号がメモリ内のオフセットにマッピングされ（ステップ606）、ベースにオフセットを加算することによって指定されたアドレスからの内容が、一時的レジスタに読み込まれる（ステップ608）。次に、一時的レジスタが使用される（ステップ610）。

40

#### 【0074】

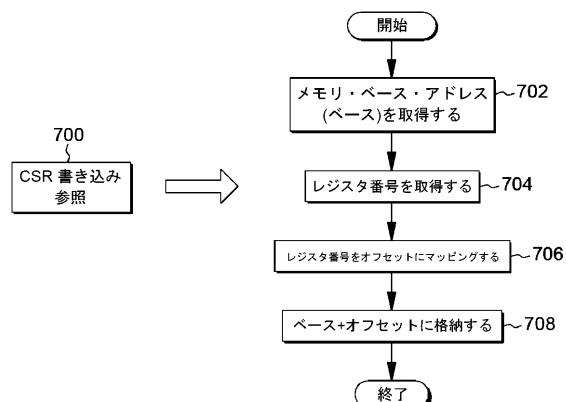

図11を参照して説明されているように、構成状態レジスタの書き込み参照に関して、同様の処理が実行される。この処理は、プロセッサによって実行される。図11を参照すると、1つの例では、構成状態レジスタの書き込み参照が取得される（ステップ700）。それに基づいて、メモリ・ベース・アドレス（ベース）が、例えば、命令／動作で示された構成状態レジスタのベース・レジスタから（例えばTCBRから）取得され（ステップ702）、それに加えて、命令／動作で指定されたベース・レジスタ番号が取得される（ステップ704）。レジスタ番号がオフセットにマッピングされ（ステップ706）、書き込み参照に（例えば、一時的レジスタに）含まれている内容が、ベースにオフセット

50

を加算して指定されたアドレスに格納される（ステップ 708）。

#### 【0075】

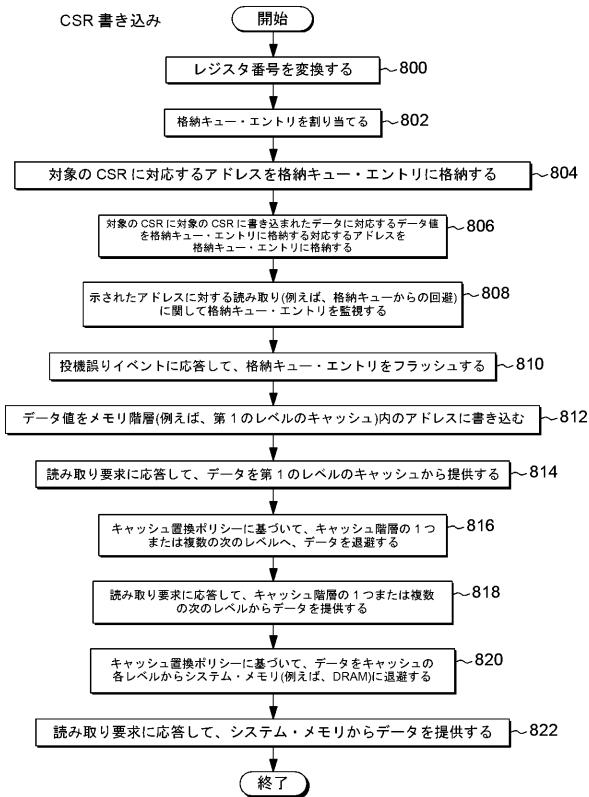

構成状態レジスタの書き込み動作（構成状態レジスタへの移動（例えば、m t s p r）など）の動作可能な実装の考え方に関する詳細が、図12を参照してさらに説明される。この処理は、プロセッサによって実行される。図12を参照すると、1つの例では、動作で指定されたレジスタ番号が変換される（ステップ800）。例えば、レジスタ番号（または他の指示）に対応するか、またはマッピングされたメモリ・アドレスが、（例えば、ルックアップ・テーブルを使用することによって、または計算されて）決定される。さらに、格納キュー・エントリが割り当てられ（ステップ802）、対象の構成状態レジスタに対応するアドレスが格納キュー・エントリに格納される（ステップ804）。さらに、対象の構成状態レジスタに書き込まれたデータに対応する内容（例えば、データ値）が、格納キュー・エントリに書き込まれる（ステップ806）。1つの例では、ステップ804および806は、不規則な順序で実行されてよい。10

#### 【0076】

格納キュー・エントリは、示されたアドレスに対する読み取り（例えば、格納キューからの回避）に関して監視される（ステップ808）。さらに、投機誤りイベントに基づいて、格納キュー・エントリがフラッシュされてよく、投機誤りイベントは、1つの例では、アーキテクチャ的に正しい順序の位置まで発生する可能性がある（ステップ810）。

#### 【0077】

内容（例えば、データ値）が、メモリ階層（例えば、第1のレベルのキャッシュ）内のアドレスに書き込まれる（ステップ812）。読み取り要求に基づいて、第1のレベルのキャッシュからのデータが提供される（ステップ814）。さらに、キャッシュ置換ポリシーに基づいて、第1のレベルのキャッシュからキャッシュ階層の1つまたは複数の次のレベルへ、データが退避される（ステップ816）。読み取り要求に基づいて、キャッシュ階層の1つまたは複数の次のレベルからのデータが提供される（ステップ818）。キャッシュ置換ポリシーに基づいて、キャッシュの各レベルからのデータがシステム・メモリ（例えば、DRAM）に退避される（ステップ820）。読み取り要求に基づいて、システム・メモリからのデータが提供される（ステップ822）。20

#### 【0078】

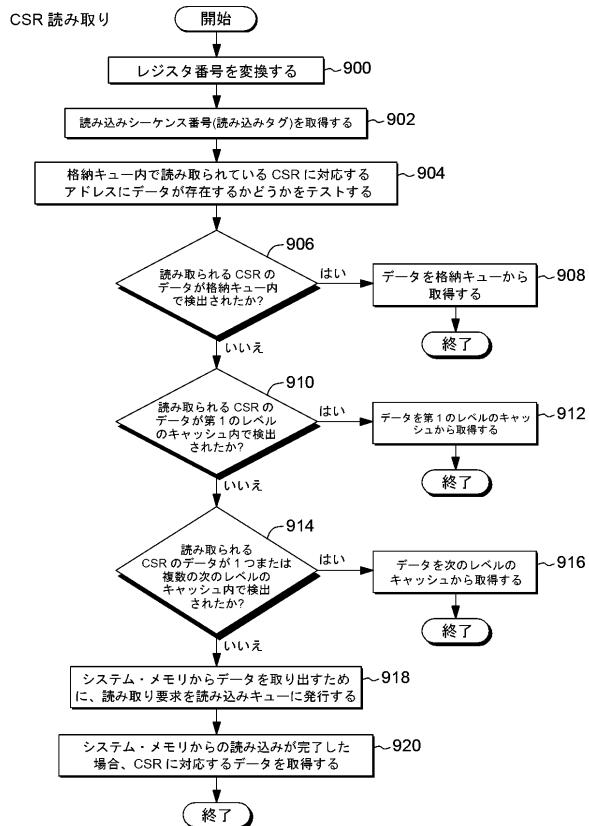

構成状態レジスタの読み取り動作の動作可能な実装の考え方に関する詳細が、図13を参照してさらに説明される。この処理は、プロセッサによって実行される。図13を参照すると、1つの例では、読み取り動作によって指定されたレジスタ番号が、対応するメモリ・アドレスに変換される（ステップ900）。読み込み要求の追跡に使用される読み込みキュー内の位置を示すために使用される読み込みシーケンス番号、および依存関係を追跡する読み込みタグが、取得される（ステップ902）。格納キュー内で読み取られている構成状態レジスタに対応するアドレスにデータが存在する（すなわち、格納キュー内のメモリから読み取られるデータが存在する）かどうかのテストが実行される（ステップ904）。読み取られる構成状態レジスタのデータが格納キュー内で検出された場合（照会906）、格納キューから値が取得され（ステップ908）、処理が完了する。30

#### 【0079】

照会906に戻ると、読み取られる構成状態レジスタのデータが格納キュー内で検出されない場合、読み取られる構成状態レジスタのデータが第1のレベルのキャッシュ内で検出されるかどうかに関する判定がさらに行われる（照会910）。データが第1のレベルのキャッシュ内で検出された場合、第1のレベルのキャッシュから値が取得され（ステップ912）、処理が完了する。40

#### 【0080】

しかし、照会910に戻ると、データが第1のレベルのキャッシュ内で検出されない場合、読み取られる構成状態レジスタのデータが1つまたは複数の次のレベルのキャッシュ内で検出されるかどうかに関する判定がさらに行われる（照会914）。データが1つまたは複数の次のレベルのキャッシュ内で検出された場合、次のレベルのキャッシュからデ

10

20

30

40

50

ータが取得され（ステップ916）、処理が完了する。

【0081】

照会914に戻ると、データが1つまたは複数の次のレベルのキャッシュ内にない場合、システム・メモリからデータを取り出すために、読み取り要求が読み込みキューに発行される（ステップ918）。システム・メモリからの読み込みが完了した場合、構成状態レジスタに対応するデータが取得される（ステップ920）。

【0082】

本発明の態様に従って、ソフトウェアの互換性を実現するために、メモリ内メモリ・ユニット（例えば、ページ）の割り当てが実行される。例えば、プロセッサがレガシー・ハイパーバイザを実行できるようにする、およびハイパーバイザがレガシー・オペレーティング・システムを実行できるようにする、などのために、ファームウェアによって割り当てが実行される。

10

【0083】

1つの例では、システムの初期ブート時に、ファームウェアが、ファームウェアが所有するメモリ内のメモリ内ページをメモリ内構成状態レジスタに割り当てる。1つの例では、ハイパーバイザがメモリ内構成状態レジスタを認識しない場合、ベース・レジスタ（例えば、TCBRなど）へのそれ以上のソフトウェアの参照なしで、ファームウェアが所有するページがシステムの実行全体を通じて使用される。

20

【0084】

そのため、ハイパーバイザは、例えば構成状態レジスタからの移動（例えば、mfspr）を使用してコンテキストを読み取り、例えば構成状態レジスタへの移動（例えば、mtspr）を使用してコンテキストを再読み込みすることによって、コンテキスト切り替えを簡単に実行する。これによって、コンピュータ・システム内の大幅な設計の簡略化および性能優位性を実現する。

20

【0085】

さらに、1つの例では、ハイパーバイザが、メモリによって補助されたページを認識する場合、ハイパーバイザは、補助ページのセットを含むように新しい各パーティションを構成してよい。さらに、オペレーティング・システムがメモリ内構成状態レジスタを認識しない場合、例えばベース・レジスタ（例えば、TCBRなど）へのそれ以上のソフトウェアの参照なしで、ハイパーバイザが所有するページがシステムの実行全体を通じて使用される。ハイパーバイザも認識しない場合、オペレーティング・システムが、ファームウェアが所有するページを使用する。

30

【0086】

そのため、オペレーティング・システムは、例えば構成状態レジスタからの移動（例えば、mfsprなど）を使用してコンテキストを読み取り、例えば構成状態レジスタへの移動（例えば、mtsprなど）を使用してコンテキストを再読み込みすることによって、コンテキスト切り替えを簡単に実行する。これによって、コンピュータ・システム内の大幅な設計の簡略化および性能優位性を実現し、処理を容易にする。

40

【0087】

本明細書において説明されているように、1つまたは複数の態様に従って、選択された構成状態レジスタがシステム・メモリに格納される。したがって、構成状態レジスタへの移動および構成状態レジスタからの移動が、命令デコード論理によって、読み込み命令および格納命令に置き換えられる。そのように生成された読み込みおよび格納は、格納キューにコミットされ、通常の読み込み処理および格納処理が実行される。1つの例では、常に必要ではない構成状態レジスタ（例えば、プログラム・カウンタ（PC：program counter）、データおよびアドレス・ブレーク・ポイント・レジスタ、PSW、浮動小数点制御などのレジスタ以外のレジスタ）は、メモリに格納される構成状態レジスタである。

【0088】

1つの例として、記憶領域が、オペレーティング・システムおよびハイパーバイザによって定義され、メモリベースのレジスタを格納するために確保される。1つの実施形態で

50

は、物理メモリ領域がアーキテクチャによって指定される（例えば、物理メモリの最初または最後の n ページ）。

#### 【0089】

少なくとも 1 つの実施形態では、メモリ内構成状態レジスタが、通常のキャッシュ可能なメモリにマッピングされる。構成状態レジスタが更新される場合、その構成状態レジスタが格納キューに格納される。格納キューは、キュー・メカニズムであるだけでなく、メモリ・アクセスの投機的実行を可能にするために、格納用の位置の名前を変更する方法を効果的に提供する。アドレスの投機的値の複数のバージョンが（キャッシュ内またはシステム・メモリ内の、アーキテクチャ的に正しい順序の位置での信頼できる設計済み値に加えて）、格納キュー内に存在することができる。キャッシュ・エントリは、割り当てられた後に、不規則な順序で更新されてよい。格納は、エントリを格納キューからフラッシュすることによって取り消されてもよい。

10

#### 【0090】

したがって、メモリ内構成状態レジスタは、性能を犠牲にすることなく、格納キューを使用することによって更新し、不規則な順序で読み取ることができ、コア内のラッチベースの構成状態レジスタは、プロセッサ内構成状態レジスタの投機的実行のための手段を実装することが、ほとんどの場合、非常に高価であるため、2 つのシリアルライズおよび順序通りのアクセスによるコストの不利益を強いいる。

20

#### 【0091】

さらに、値が格納キュー内にない場合、頻繁に使用されるメモリ制御（例えば、メモリ内構成状態レジスタ）が、キャッシュ内で検出され、わずか 2 ~ 3 サイクル（第 1 のレベルのキャッシュにアクセスするための時間）で使用可能になることが可能であるため、値の読み取りを、ラッチからよりも効率的に実行することができ、この速度は、プロセッサ内のラッチベースの構成状態レジスタにアクセスするために必要な専用論理よりも非常に高速である。

30

#### 【0092】

1 つの実施形態では、構成状態レジスタを保持するためのページが割り当てられた場合、アーキテクチャは、メモリのオペランドを使用するページへのアクセスを許可しない。これによって、メモリ操作と、構成状態レジスタからの / への移動命令との間の連結を防ぐ。

30

#### 【0093】

本発明のさらに別の態様に従って、構成状態レジスタの 1 つまたは複数の部分がメモリ内に設けられ、一方、構成状態レジスタの 1 つまたは複数の他の部分がプロセッサ内に設けられる。例えば、構成状態レジスタは複数の部分（例えば、フィールド）を含んでよく、それらの部分のうちの例えば頻繁にアクセスされる 1 つまたは複数が、プロセッサ内に残ってよく、例えばあまり使用されない残りの部分が、メモリに移動されてよい。これが、図 14 ~ 図 19 を参照してさらに詳細に説明される。

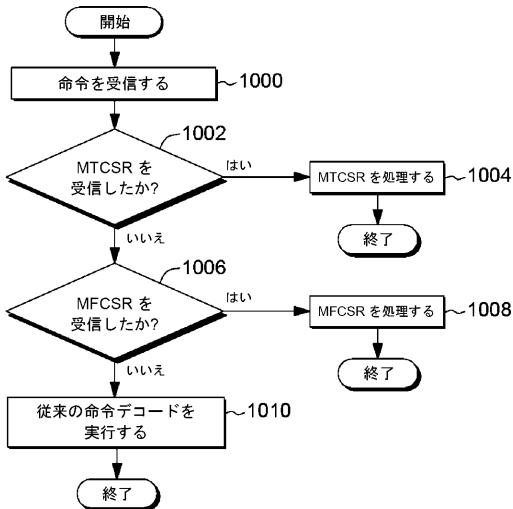

#### 【0094】

最初に図 14 を参照すると、プロセッサ（または別のコンポーネント）のデコード・ユニットが命令を受信する（ステップ 1000）。デコード・ユニット（または別のコンポーネント）によって、命令が SPR への移動 (m t s p r) 命令などの構成状態レジスタへの移動 (m t c s r : move to configuration state register) 命令であるかどうかに関する判定が行われる（照会 1002）。命令が構成状態レジスタへの移動命令である場合、その命令が下で説明されているように処理される（ステップ 1004）。

40

#### 【0095】

照会 1002 に戻ると、命令が構成状態レジスタへの移動命令でない場合、命令が SPR からの移動 (m f s p r) 命令などの構成状態レジスタからの移動 (m f c s r : move from configuration state register) 命令であるかに関する判定がさらに行われる（照会 1006）。命令が構成状態レジスタからの移動命令である場合、その命令が下で説明されているように処理される（ステップ 1008）。照会 1006 に戻ると、命令が構成

50

状態レジスタへの移動命令でも構成状態レジスタからの移動命令でもない場合、従来の命令デコードが実行される（ステップ1010）。

#### 【0096】

さらに別の実施形態では、命令が構成状態レジスタを使用する別の命令であるかどうかに関する他の照会が行われてよく、そのような命令である場合、それらの命令が適切に処理されてよく、その例が本明細書において説明されている。さらに別の実施形態では、命令に対応していない（例えば、例外処理シーケンスを開始している）プロセッサの動作が同様に実行されてよい。

#### 【0097】

構成状態レジスタへの移動命令の処理に関する詳細が、図15を参照してさらに説明される。1つの例では、構成状態レジスタが専用レジスタ（SPR）であってよく、命令がSPRへの移動（m t s p r）命令である。ただし、これは1つの例にすぎない。他の構成状態レジスタが同様に処理されてよい。この論理は、例えばプロセッサのデコード・ユニットなどの、プロセッサによって実行される。他の例では、1つまたは複数の他のコンポーネントがこの論理を実行する。

10

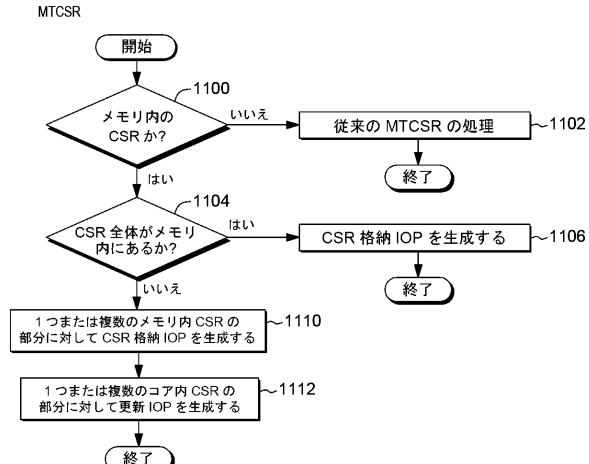

#### 【0098】

図15を参照すると、m t s p r命令などの構成状態レジスタへの移動命令を取得すること（例えば、受信すること、提供されること、選択することなど）に基づいて、命令によって指定された構成状態レジスタ（CSR）の少なくとも一部がメモリ内にあるかどうかに関する判定が行われる（照会1100）。メモリ内がない場合、構成状態レジスタへの移動命令（例えば、m t s p r）の従来の処理が実行される（ステップ1102）。

20

#### 【0099】

照会1100に戻ると、構成状態レジスタの少なくとも一部がメモリ内にある場合、構成状態レジスタ全体がメモリ内にあるかどうかに関する判定がさらに行われる（照会1104）。構成状態レジスタ全体がメモリ内にある場合、構成状態レジスタ格納内部動作が生成される（ステップ1106）。この内部動作に関連する処理の例が、図9を参照して説明されている。

20

#### 【0100】

照会1104に戻ると、構成状態レジスタの1つまたは複数の部分のみがメモリ内にある場合、1つまたは複数のメモリ内構成状態レジスタの部分に対する1つまたは複数の構成状態レジスタ格納動作が生成される（ステップ1110）。さらに、1つまたは複数のコア内構成状態レジスタの部分に対する更新された内部動作が生成される（ステップ1112）。更新された内部動作は、指定されたコア内の部分のデータを含んでいる1つまたは複数の汎用レジスタの内容をコア内構成状態レジスタの適切な部分にコピーする動作を実行する、1つまたは複数の命令、状態マシンなどであってよい。処理が完了する。

30

#### 【0101】

構成状態レジスタからの移動命令の処理に関連付けられた処理に関する詳細が、図16を参照してさらに説明される。1つの例では、構成状態レジスタが専用レジスタ（SPR）であってよく、命令がSPRからの移動（m f s p r）命令である。ただし、これは1つの例にすぎない。他の構成状態レジスタが同様に処理されてよい。この論理は、例えばプロセッサのデコード・ユニットなどの、プロセッサによって実行される。他の例では、1つまたは複数の他のコンポーネントがこの論理を実行する。

40

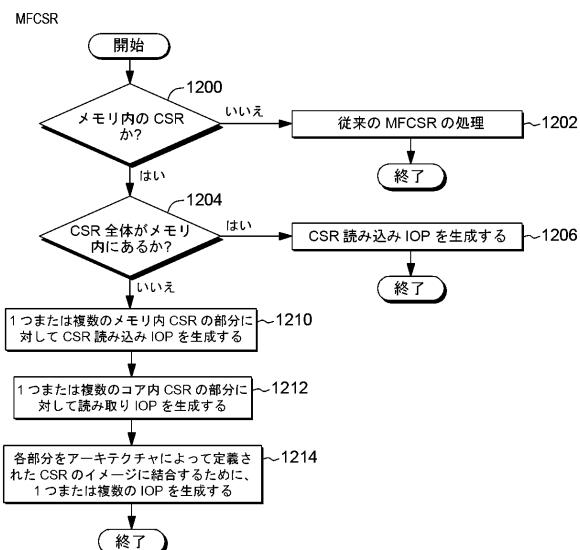

#### 【0102】

図16を参照すると、m f s p r命令などの構成状態レジスタからの移動命令を取得すること（例えば、受信すること、提供すること、選択することなど）に基づいて、構成状態レジスタの少なくとも一部がメモリ内にあるかどうかに関する判定が行われる。メモリ内がない場合、構成状態レジスタからの移動命令に対して従来の処理が実行される（ステップ1202）。

#### 【0103】

照会1200に戻ると、構成状態レジスタの少なくとも一部がメモリ内にある場合、構

50

成状態レジスタ全体がメモリ内にあるかどうかに関する判定がさらに行われる（照会 1204）。構成状態レジスタ全体がメモリ内にある場合、構成状態レジスタ読み込み内部動作が生成される（ステップ 1206）。この動作に関連する処理の例が、図 8 を参照して説明されている。

#### 【0104】

照会 1204 に戻ると、構成状態レジスタの 1 つまたは複数の部分のみがメモリ内にある場合、メモリ内構成状態レジスタの部分のうちの 1 つまたは複数に対する 1 つまたは複数の構成状態レジスタ読み込み内部動作が生成される（ステップ 1210）。さらに、1 つまたは複数のコア内構成状態レジスタの部分に対する 1 つまたは複数の読み込み内部動作が生成される（ステップ 1212）。

10

#### 【0105】

さらに、1 つの実施形態では、メモリ内の部分およびコア内の部分をアーキテクチャによって定義された構成状態レジスタのイメージに結合するために、1 つまたは複数の内部動作が生成される（ステップ 1214）。これは例えば、下で説明されているように、マスク下挿入命令、あるいは OR、AND、もしくは NOT、あるいはその組合せの論理回路を使用することを含んでよい。

#### 【0106】

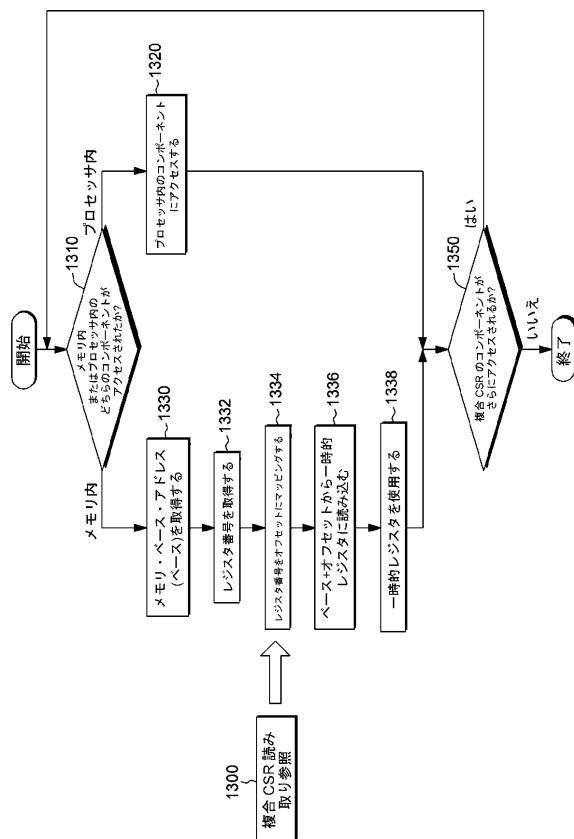

1 つまたは複数の部分がプロセッサ内にあり、1 つまたは複数の部分がメモリ内にある複合構成状態レジスタの使用に関する詳細が、図 17 を参照してさらに説明され、図 17 では読み取り参照が説明される。この論理は、例えばプロセッサのデコード・ユニットなどの、プロセッサによって実行される。他の例では、1 つまたは複数の他のコンポーネントがこの論理を実行する。

20

#### 【0107】

図 17 を参照すると、複合構成状態レジスタの読み取り参照 1300 に基づいて、アクセスされている特定の部分（コンポーネント（例えばフィールド）とも呼ばれる）がメモリ内にあるかプロセッサ内にあるかに関する判定が行われる（照会 1310）。特定の部分がプロセッサ内にある場合、プロセッサ内のコンポーネントがアクセスされ（ステップ 1320）、処理が下で説明されている照会 1350 に進む。しかし、特定のコンポーネントがメモリ内にある場合（照会 1310）、図 10 を参照して説明された処理が実行される。例えば、メモリ・ベース・アドレス（ベース）が取得され（ステップ 1330）、複合構成状態レジスタを参照する命令内で示されたレジスタ番号も取得される（ステップ 1332）。レジスタ番号がオフセットにマッピングされ（ステップ 1334）、アドレス（ベース + オフセット）から一時的レジスタへの読み込みが実行される（ステップ 1336）。次に、一時的レジスタが使用される（ステップ 1338）。その後、またはステップ 1320 の後に、複合構成レジスタの別のコンポーネントがアクセスされるかどうかに関する判定が行われる（照会 1350）。複合構成レジスタの別のコンポーネントがアクセスされる場合は、処理が照会 1310 を続行する。複合構成レジスタの別のコンポーネントがアクセスされない場合は、処理が完了する。

30

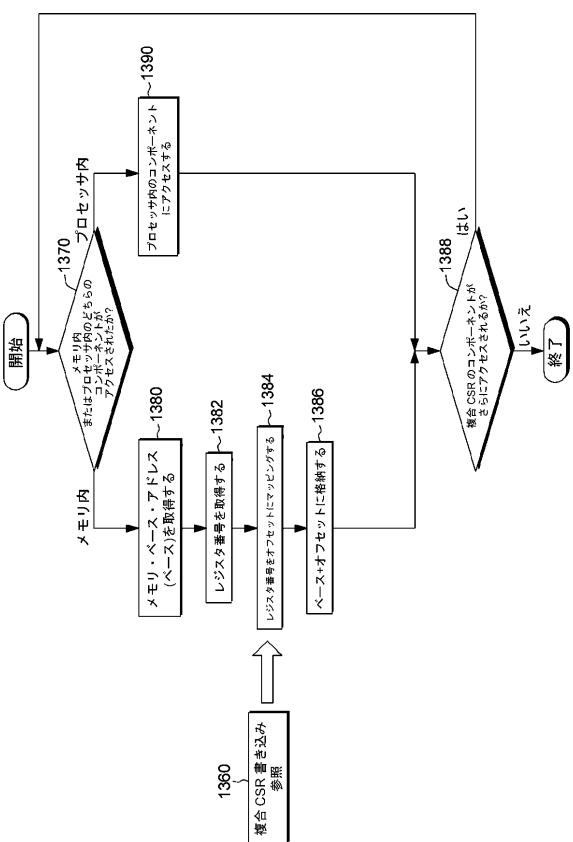

#### 【0108】

1 つまたは複数の部分がプロセッサ内にあり、1 つまたは複数の部分がメモリ内にある複合構成状態レジスタの使用に関する詳細が、図 18 を参照してさらに説明され、図 18 では書き込み参照が説明される。この論理は、例えばプロセッサのデコード・ユニットなどの、プロセッサによって実行される。他の例では、1 つまたは複数の他のコンポーネントがこの論理を実行する。

40

#### 【0109】

図 18 を参照すると、複合構成状態レジスタの書き込み参照 1360 に基づいて、アクセスされている特定の部分（コンポーネント（例えばフィールド）とも呼ばれる）がメモリ内にあるかプロセッサ内にあるかに関する判定が行われる（照会 1370）。特定の部分がプロセッサ内にある場合、プロセッサ内のコンポーネントがアクセスされ（ステップ 1390）、処理が下で説明されている照会 1388 に進む。しかし、特定のコンポーネ

50

ントがメモリ内にある場合(照会1370)、図11を参照して説明された処理が実行される。例えば、メモリ・ベース・アドレス(ベース)が取得され(ステップ1380)、複合構成状態レジスタを参照する命令内で示されたレジスタ番号も取得される(ステップ1382)。レジスタ番号がオフセットにマッピングされ(ステップ1384)、ベース+オフセットによって定義されたアドレスへの格納が実行される(ステップ1386)。その後、またはステップ1390の後に、複合構成レジスタの別のコンポーネントがアクセスされるかどうかに関する判定が行われる(照会1388)。複合構成レジスタの別のコンポーネントがアクセスされる場合は、処理が照会1370を続行する。複合構成レジスタの別のコンポーネントがアクセスされない場合は、処理が完了する。

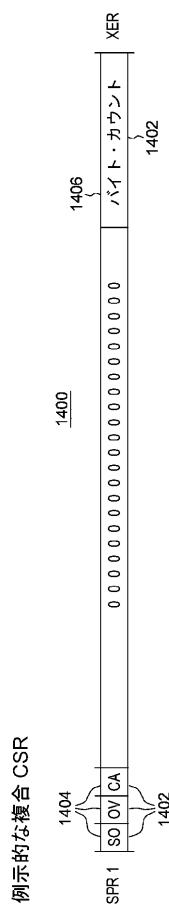

## 【0110】

複合構成状態レジスタの1つの例が、図19に示されている。図に示されているように、この例では、複合構成状態レジスタ1400は、整数例外レジスタ(XER)に対応する専用レジスタ(SPR)1である。このレジスタは、複数のフィールド1402を含んでいる。1つの例では、フィールドのうちの1つまたは複数がプロセッサ内のフィールド1404であり、別のフィールド1406がメモリ内のフィールドである。この特定の例では、Xerf0、1、2(すなわち、XERのフィールド0、1、および2)の名前が、プロセッサ内ではSO(要約オーバーフロー)、OV(オーバーフロー)、およびCA(キャリー)に変更され、この例では名前が変更されないXerf3(XERのフィールド3)は、メモリ内のバイト・カウント・フィールドである。この構成では、複合構成状態レジスタに対してmtrsprおよびmfsprをそれぞれ実行するために、次のIOPシーケンスが生成されて使用されてよい。

10

20

30

40

50

## 【0111】

```

mtrspr_xer      mtxerf2

```

## 【0112】

```

mtxerf0

```

## 【0113】

```

mtxerf1

```

## 【0114】

```

stxerf3

```

## 【0115】

上記では、XERレジスタに対するmtrsprは、汎用レジスタの内容がXERのフィールド2にコピーされる、XERのフィールド2への移動(mtxerf2)、汎用レジスタの内容がXERのフィールド0にコピーされる、XERのフィールド0への移動(mtxerf0)、および汎用レジスタの内容がXERのフィールド1にコピーされる、XERのフィールド1への移動(mtxerf1)を含んでいる。mtrsprは、フィールド3がメモリ内にあるため、格納動作によって実行されるXERのフィールド3への格納(stxerf3)も含んでいる。

## 【0116】

```

mfspr_xer      mfxerf2

```

## 【0117】

```

mfxerf0

```

## 【0118】

または

## 【0119】

```

ldxerf3

```

## 【0120】

または

## 【0121】

```

mfxerf1

```

## 【0122】

または

**【 0 1 2 3 】**

X E R からの移動の場合、プロセッサ内またはメモリ内のいずれかから、フィールドの各々が読み取られ、それらのフィールドが、例えば O R 演算によって結合される。例えば、フィールド 2 およびフィールド 0 の内容が読み取られ、O R 演算が実行されて結果 1 を提供し、次に、（例えば、フィールド 3 がメモリ内にあるため、x e r f 3 読み込み内部動作 ( l d x e r f 3 ) などの読み込みを使用して）フィールド 3 の内容が読み取られ、結果 1 との O R 演算が実行されて結果 2 を生成する。さらに、フィールド 1 の内容が読み取られ、結果 2 との O R 演算が実行されて最終結果を提供し、この最終結果は、プロセッサ内かメモリ内かに関わらず、フィールドを含む X E R のイメージである。

10

**【 0 1 2 4 】**

本明細書において説明されているように、本発明の態様に従って、構成状態レジスタからの移動命令は、プロセッサ内の部分からの移動のシーケンス、およびメモリに格納された部分の読み取りを生成する。メモリ内の部分またはプロセッサ内の部分の読み取りの内容は、例えば、例えば O R 命令のシーケンスを使用して、照合される。さらに、構成状態レジスタへの移動命令は、プロセッサ内の部分への移動のシーケンス、およびメモリに格納された部分の格納を生成する。

**【 0 1 2 5 】**

1つの態様では、メモリが構成状態レジスタに割り当てられた場合、オフセットがアーキテクチャによって指定される（例えば、定義されて外部から見える）か、またはマイクロアーキテクチャによって指定される（定義されるが、外部からは見えない）。例えば、オフセットは、構成状態レジスタ番号（またはその他の指示）から直接導き出されてよい。

20

**【 0 1 2 6 】**

1つの例はマッピングであり、各構成状態レジスタが、対応するオフセット（ダブルワード単位）、すなわち、ベース \* 構成状態レジスタ番号にマッピングされ、構成状態レジスタ 1 が第 1 の位置にあり、構成状態レジスタ 2 が、第 1 の位置に定義されたバイト数（例えば 8 ）を加算した位置にある、などとなる。

**【 0 1 2 7 】**

しかし、構成状態レジスタ番号は連続しておらず、メモリを浪費し、キャッシュ効率を低下させる。したがって、本発明の態様に従う別の実施形態では、メモリ・ページへのオフセットを直接導き出すために構成状態レジスタ番号が使用されず、機能的類似性に基づいて構成状態レジスタにオフセットが割り当てられる。したがって、キャッシュ局所性を向上させるために、共通の動作において一緒に使用される構成状態レジスタが、同じキャッシュ・ラインまたは隣接するキャッシュ・ラインに割り当てられる。例えば、E B B 处理は、例えばレジスタ E B B H R 、 E B B R R 、 B E S C R 、および T A R を使用する。T A R は、他のレジスタに隣接していない。しかし、これらのレジスタは、最終的に同じキャッシュ・ライン内または隣接するキャッシュ・ライン内に存在するように、すべてメモリに割り当てられる。

30

**【 0 1 2 8 】**

線形マッピングの1つの例が、図 2 0 ~ 図 2 1 に示されている。図に示されているように、1つの例では、線形マッピング 1 5 0 0 はスペースである。例えば、1つの例では、1 K 未満の構成状態レジスタがマッピングされたとしても、8 K B ( 2 ページ ) が使用される。さらに、E B B H R 、 E B B R R 、 B E S C R 、および T A R などの共同で使用される構成状態レジスタは、隣接していない。さらに、構成状態レジスタのグループは、同じキャッシュ・ライン（例えば、7 7 9 M M C R 0 、 7 8 0 S I A R 、 7 8 1 S D A R 、 7 8 2 M M C R 1 ）内にあることを保証するために、アライメント境界上にない。さらに、一部の構成状態レジスタは、同じレジスタ（例えば、異なるアクセス許可、サブフィールドなど）を参照することがある。これは、非効率的なキャッシュの使用である。（各活動で1回のキャッシュ・ミスのみが発生することを保証するための）プリフェッチが欠如しており、大きすぎるキャッシュ・フットプリントが存在する（その結果、ヒッ

40

50

ト率を減らすワーキング・セットが増加する）。したがって、本発明の態様に従って、構成状態レジスタは、例えばベース + ( i d x \* 8 ) に格納されない。構成状態レジスタは、例えばベース + 再マッピング [ i d x ] に格納される。

#### 【 0 1 2 9 】

この再マッピングは、キャッシュ・ラインを共有するために、グループが隣接することを保証し、スパース性を除去 / 低減して、より効率的なキャッシュの使用を実現し、複数の名前を処理する。1つの例として、この再マッピングは静的であり、プロセッサの設計で実行され、テーブルなどのデータ構造において提供されるか、または定義された方程式の計算によって提供される。別の例として、この再マッピングは動的であり、使用によって決定される。例えば、レジスタの追跡が、レジスタのセットのうちの複数のレジスタが一緒に使用されることを示した場合、それらのレジスタがグループ化され、互いに隣接して配置される。その他の可能性が存在する。

10

#### 【 0 1 3 0 】

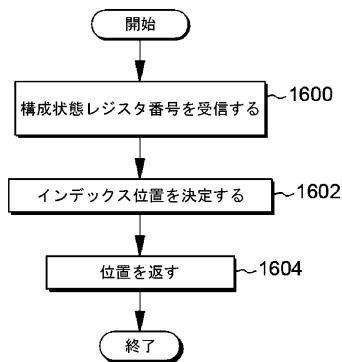

再マッピングの詳細が、図 22 を参照してさらに説明される。この処理は、プロセッサによって実行される。1つの例では、構成状態レジスタ番号がプロセッサによって取得される（ステップ 1600）。構成状態レジスタ番号に基づいて、メモリ・ユニット（例えば、ページ）へのインデックス位置（オフセットとも呼ばれる）が決定される（ステップ 1602）。このインデックス位置は、テーブル検索によって、または計算によって決定されてよい。インデックス位置が要求側（例えば、内部動作）に返される（ステップ 1604）。

20

#### 【 0 1 3 1 】

さらに別の例では、マッピング論理を含んでいる回路が使用される。構成状態レジスタ番号がマッピング論理に入力され、出力はページ・インデックスである。

#### 【 0 1 3 2 】

前述したように、1つの実施形態では、より効率的なキャッシュを可能にするために、一緒に使用される構成状態レジスタが互いに近接して配置されるように、アーキテクチャで定義された構成状態レジスタ番号が再マッピングされる。これによって、構成状態レジスタに使用されるキャッシュ・ラインの数を減らし、キャッシュの使用に関して、他のプログラムとの競合を少なくする。さらに、これによって、特定の構成状態レジスタと共にキャッシュ・ラインが読み込まれ、その値のキャッシュ・ミスに対してペナルティが支払われた後に、その構成状態レジスタと連動して使用されてもよい他の構成状態レジスタが、キャッシュ内でヒットし、その結果、他のキャッシュ・ミス・ペナルティを伴わない、ということを保証する。

30

#### 【 0 1 3 3 】

さらに別の実施形態では、異なるオフセット割り当てが可能である場合に、`s y n c _ o _ c s r` 命令がバージョン・スタンプをページに内に書き込む。バージョン・スタンプは、異なるホスト間でパーティションを移行するときにオフセットを調整するため、またはオフセットを（例えば、`s y n c _ i _ c s r` がパーティションのオフセットのバージョン番号を読み取るときに）ハードウェア内で直接調整するか、もしくはソフトウェア内で調整するため、あるいはその両方のために、使用されてよい。

40

#### 【 0 1 3 4 】

本発明の別の態様に従って、複数の構成状態レジスタを格納するか、または読み込む一括動作を実行するための能力が提供される。構成状態レジスタの個別の読み込みまたは格納は、各読み取りまたは書き込みが順序通りに実行され、次の命令が開始される前に完了するため、高価になる。さらに、プロセッサ内構成状態レジスタの名前変更の欠如がロールバックを許可しないため、正しい例外 / エラー・シーケンスが保証される。しかし、本発明の1つまたは複数の態様に従って、メモリ・ユニット（ページなど）からの構成状態レジスタの一括読み込みおよび一括格納が提供される。

#### 【 0 1 3 5 】

例えば、構成状態レジスタ格納命令または動作（例えば、`S T _ C S R`）が、複数のプ

50

ロセッサ内構成状態レジスタをメモリに格納する（すなわち、現在のコンテキスト（例えば、アプリケーション、スレッドなど）に関連付けられた構成状態レジスタの内容を、特定の構成状態レジスタに対して定義された、選択されたメモリ位置に格納する）ために使用され、構成状態レジスタ読み込み命令または動作（例えば、L D \_ C S R）が、メモリに格納された構成状態レジスタをプロセッサに再び読み込む（すなわち、現在のコンテキストに関連付けられた構成状態レジスタの内容をメモリからプロセッサに再び読み込む）ために使用される。

#### 【 0 1 3 6 】

メモリに格納されてよいプロセッサ内（メモリによって補助されていない、とも呼ばれる）構成状態レジスタには、メモリ内（例えば、補助メモリ・ユニット（例えば、ページ）内）の位置が割り当てられる。1つの例では、メモリ位置またはメモリ・ユニットあるいはその両方は、明確に定義された定義済みの位置 / ユニットであり、したがって命令は、位置 / ユニットを指定するためのオペランドを含む必要がない。別の実施形態では、特定の位置 / ユニットは、命令のオペランドとして指定されてよい。さらに別の実施形態では、各命令が、格納される / 読み込まれる特定のレジスタを示すためのオペランドを含んでよい。その他の変形も可能である。

10

#### 【 0 1 3 7 】

さらに、ページは、メモリ・ユニットの1つの例にすぎない。その他のユニットが可能である。また、ページは通常4KBであるが、他の実施形態では他のサイズであってよい。多くの可能性が存在する。

20

#### 【 0 1 3 8 】

前述したS T \_ C S R 命令およびL D \_ C S R 命令に加えて、本発明の態様に従って使用されてよい別の命令は、m t s p r T C B R、n e x t \_ u - > c s r \_ p a g e である。この命令は、特定のコンテキスト（例えば、プロセッサ、スレッドなど）に関するメモリ内構成状態レジスタをレジスタ（T C B Rなど）に格納するために使用されるメモリ領域のベース・アドレスを読み込むために使用される。その後、このアドレスは、本明細書において説明されているように、ベース・アドレスを採用する処理において使用される。この命令では、n e x t \_ u - > c s r \_ p a g e は、命令を発行するコンテキストに関するデータを格納するユーザ・データ構造を参照する。このデータは、メモリ内構成状態レジスタを格納するメモリ・ユニット（例えば、ページ）のベース・アドレスを含む。m t s p r が指定されているが、他の構成状態レジスタへの移動（m t c s r）命令が使用されてよい。また、T C B R はベース・レジスタの1つの例にすぎない。他のベース・レジスタが指定されてよい。多くの変形が可能である。

30

#### 【 0 1 3 9 】

上記の命令に加えて、キャッシュをメモリまたはプロセッサ内レジスタと同期させるための2つの同期命令が提供されてよい。例えば、s y n c \_ o \_ c s r は、キャッシュおよび1つまたは複数のメモリ内構成状態レジスタを同期させるために使用され、s y n c \_ i \_ c s r は、キャッシュおよび1つまたは複数のプロセッサ内構成状態レジスタを同期させるために使用される。

40

#### 【 0 1 4 0 】

本明細書において説明されているように、1つの態様では、複数の構成状態レジスタが読み込まれるか、または格納される。介在する例外は存在せず、すなわち、例外が回避され、動作が、動作のすべての構成状態レジスタに対して完了するか、またはどの構成状態レジスタに対しても完了しない。さらに、ページ・フォールトが存在しない（例えば、ページが固定され、ページが読み込まれた後でも、同じページへの参照が保証される）。必要に応じて、ハードウェアが、プロセスを再開可能にすることができる（例えば、マイクロコードまたは状態マシン内の読み込みまたは格納シーケンス）。

#### 【 0 1 4 1 】

図23～図25を参照して説明されているように、複数の構成状態レジスタを格納する / 読み込む命令を使用することによって、順序通りの位置を保証し、命令を順序通りに完

50

了するなどの、特定の高価な動作があまり頻繁に使用されなくなる。図23～図25の処理は、プロセッサによって実行される。

#### 【0142】

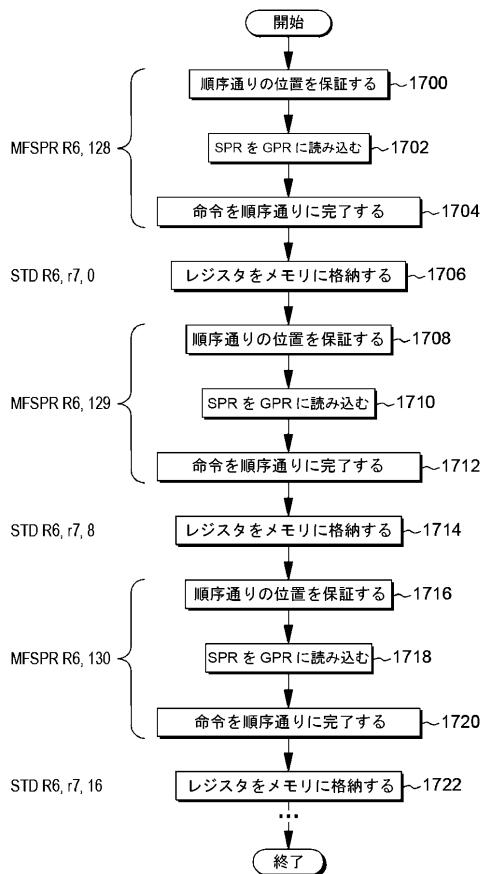

図23を参照すると、複数の構成状態レジスタをメモリに格納するために個別の命令（すなわち、一括動作ではない）を使用する1つの例が、図23を参照して説明される。1つの例では、構成状態レジスタをメモリに移動するために、構成状態レジスタからの移動命令および格納命令が使用される。例えば、1つの例では、構成状態レジスタがSPRであり、構成状態レジスタからの移動命令がmfsprである。他の構成状態レジスタおよび対応する命令が使用されてよい。

#### 【0143】

この例では、SPRからの移動(mfspr)命令などのmfspr命令の実行に基づいて、順序通りの位置が保証される(ステップ1700)。その後、命令によって指定された構成状態レジスタ(例えば、SPR)の内容が、構成状態レジスタから、例えば汎用レジスタ(GPR:general purpose register)にコピーされる(ステップ1702)。命令が順序通りに完了する(ステップ1704)。その後、格納命令(STD)を介して、汎用レジスタの内容がメモリに格納される(ステップ1706)。この同じプロセスが、多数の構成状態レジスタであってよいメモリに格納される構成状態レジスタごとに、繰り返される(例えば、ステップ1708～1722)。したがって、メモリに格納される構成状態レジスタごとに、順序通りの位置を保証し、順序通りに命令を完了する動作が必要になる。

10

20

#### 【0144】

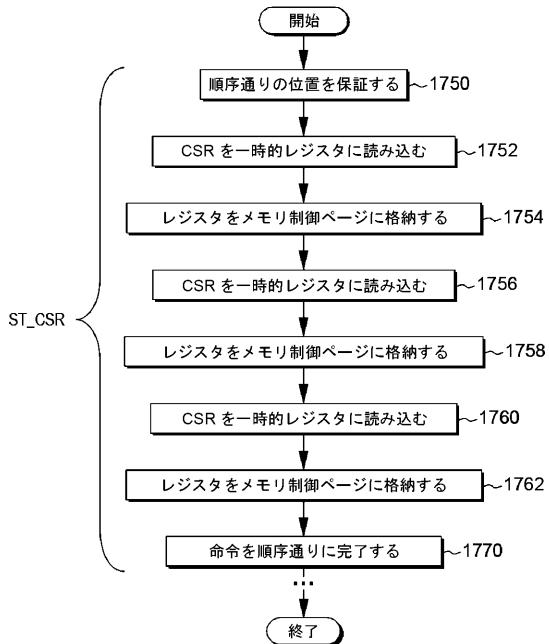

しかし、本発明の態様に従って、図24を参照して説明されているように、順序通りの位置を保証する単一の動作および順序通りに命令を完了する単一の動作を使用して、複数の構成状態レジスタをメモリに格納する構成状態レジスタ格納(ST\_CSR)命令が提供される。

#### 【0145】

図24を参照すると、構成状態レジスタ格納命令(ST\_CSR)の実行に基づいて、順序通りの位置に達する(ステップ1750)。次に、選択された構成状態レジスタの内容が一時的レジスタに読み込まれる(ステップ1752)。さらに次に、一時的レジスタの内容がメモリ(例えば、メモリ制御ページ(memory control page))に格納される(ステップ1754)。1つまたは複数の追加の構成状態レジスタに対して、読み込み/格納動作が、1回または複数回、繰り返される(1756～1762)。選択された構成状態レジスタ(多数のそのようなレジスタであってよい)をメモリにコピーした後に、命令が順序通りに完了する(ステップ1770)。

30

40

#### 【0146】

1つの例では、ST\_CSR命令が、コピーされるレジスタを指定するためのオペランドを含まず、代わりに、現在のコンテキスト(例えば、プロセス、スレッドなど)のプロセッサ内構成状態レジスタのすべてがコピーされる。別の例では、メモリにコピーされる1つまたは複数の構成状態レジスタを指定するためのオペランドが含まれ、使用されてよい。その他の変形も可能である。

#### 【0147】

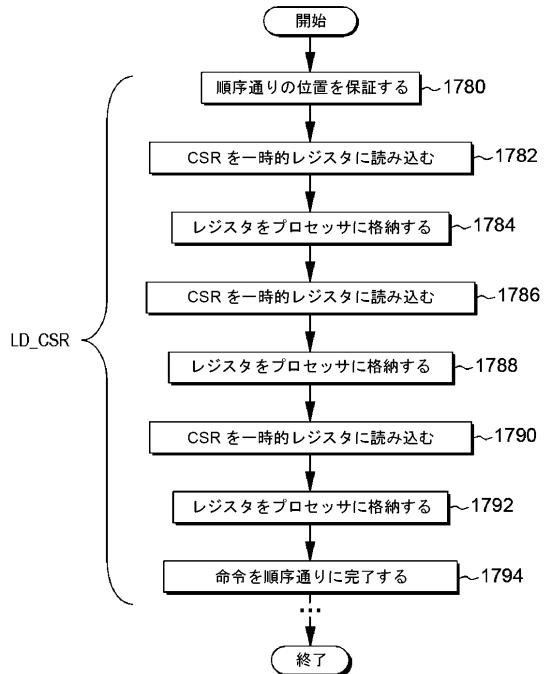

さらに別の例では、一括読み込み動作(例えば、LD\_CSR)を使用して、複数の構成状態レジスタがメモリからプロセッサ内にコピーされてよい。

#### 【0148】

図25を参照すると、構成状態レジスタ読み込み(LD\_CSR)命令の実行に基づいて、順序通りの位置が保証される(ステップ1780)。次に、選択された構成状態レジスタの内容がメモリから取得され、一時的レジスタに読み込まれる(ステップ1782)。その後、一時的レジスタの内容が、対応するプロセッサ内構成状態レジスタに格納される(ステップ1784)。1つまたは複数の(場合によっては、多数の)追加の構成状態レジスタに対して、読み込み/格納動作が、1回または複数回、繰り返される(1786)

50

~ 1 7 9 2 )。その後、命令が順序通りに完了する(ステップ1 7 9 4)。

#### 【0 1 4 9】

1つの例では、LD\_C S R命令が、コピーされるレジスタを指定するためのオペランドを含まず、代わりに、現在のコンテキスト(例えば、プロセス、スレッドなど)の構成状態レジスタのすべてがコピーされる。別の例では、メモリからコピーされる1つまたは複数の構成状態レジスタを指定するためのオペランドが含まれ、使用されてよい。

#### 【0 1 5 0】

1つの態様では、一括動作を実行するための命令が、構成状態レジスタのグループに対して同じ動作(例えば、格納、読み込みなど)を実行してよく、このグループは共通の特徴によって定義される。この共通の特徴は、例えば、レジスタの数値範囲、同じアクセス許可またはコンテキスト(例えば、ユーザ、オペレーティング・システム、ハイパーバイザ)を有していること、同じ機能的目的(例えば、例外処理、時間管理など)を有していること、または同じ実装の特性(例えば、構成状態レジスタのセットがメモリに格納されている)を有していること、などであってよい。

10

#### 【0 1 5 1】

一括格納または一括読み込みあるいはその両方の動作の使用は、コンピュータ内の処理を改善する。例えば、一括格納動作を使用して複数の構成状態レジスタをメモリに効率的にコピーすることによって、コンテキスト切り替え処理がより高速かつ効率的に実行されてよい。その他の恩恵が実現されてもよい。

20

#### 【0 1 5 2】

さらに別の態様では、処理を容易にするために、構成状態レジスタが格納されるメモリ内の位置を示すアーキテクチャの配置制御が提供されてよい。例えば、ハードウェアが、構成状態レジスタが格納されるメモリ内の位置を識別するための制御のセットを定義する。1つの例として、アプリケーションの状態を格納するためのベース・アドレスを指定する少なくとも1つの構成状態レジスタが、提供される。1つの例として、ベース・アドレスがゲスト物理アドレスであり、すなわち、ゲスト・オペレーティング・システムが、それ自身のアドレス空間内のアドレスを指定する。例えば、アドレスが指定される場合、ゲストがホスト物理アドレスを指定できるようにすると、仮想化およびセキュリティを損なうことがあるため、ゲスト・レベルのアドレス(例えば、ゲスト実アドレス、ゲスト物理アドレス、またはゲスト仮想アドレス)が指定される。

30

#### 【0 1 5 3】

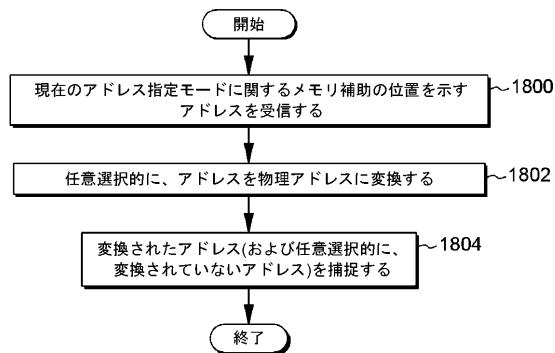

アーキテクチャの構成制御の指定に関する詳細が、図26を参照してさらに説明される。1つの例では、プロセッサがこの論理を実行する。最初に、現在の実行環境(例えば、アプリケーションの状態、スレッドの状態、オペレーティング・システムの状態、ハイパーバイザの状態、特定のゲスト・オペレーティング・システムまたはホスト・オペレーティング・システムのレベルなど)に関するメモリ補助の位置を示すアドレス(すなわち、ベース・アドレス)が受信される(ステップ1 8 0 0)。例えば、仮想マシン/論理パーティションに関して、ハイパーバイザはハイパーバイザのアドレス(例えば、ホスト仮想アドレスまたはホスト絶対アドレス、ホスト物理アドレス、ホスト実アドレス)を使用し、オペレーティング・システムはゲスト実アドレスまたはゲスト仮想アドレスを使用する。プロセッサは、構成状態レジスタを格納するためのメモリ・ページの位置を示すアドレス(すなわち、ベース・アドレス)を取得する。

40

#### 【0 1 5 4】

任意選択的に、ベース・アドレスが物理アドレスに変換される(ステップ1 8 0 2)。(変換がすでに実行されていることがあり、またはアドレスを変換する必要がない)。1つの実施形態では、この変換がページ・フォールトを引き起こすことがある。さらに別の実施形態では、ページ・フォールトを防ぐために、本手法の1つまたは複数の態様を実行する前に、例えばページを固定することによって、連携するハードウェアおよびソフトウェアが使用される。

#### 【0 1 5 5】

50

さらに、1つの例では、変換されたアドレスが捕捉される（ステップ1804）。すなわち、1つの例では、変換されたアドレスがキャッシュされる。別の実施形態では、変換されていないアドレスおよび変換されたアドレスの両方が格納される。

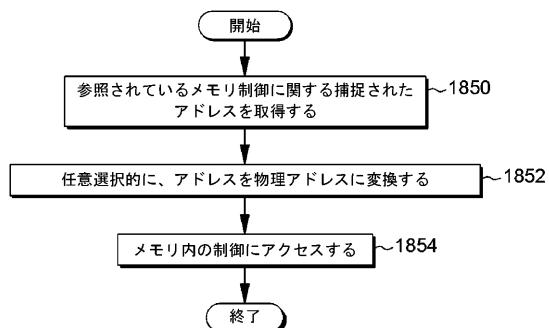

#### 【0156】

図27を参照する別の実施形態では、参照されているメモリ制御（例えば、構成状態レジスタ）に関する捕捉されたアドレスが取得される（ステップ1850）。さらに、このアドレスが物理アドレスに変換され（ステップ1852）、メモリ内の制御（例えば、構成状態レジスタ）がアクセスされる（ステップ1854）。この変換はページ・フォールトを引き起こすことがあるが、連携するハードウェアおよびソフトウェアを使用して、例えば本手法の1つまたは複数の態様を実行する前にページを固定することによって、ページ・フォールトを防ぐことができる。10

#### 【0157】

1つの実施形態では、循環する依存関係を防ぐために、ベース・アドレスが、例えばメモリではなく、構成状態レジスタに格納される。その他の例が可能である。

#### 【0158】

さらに、1つの実施形態では、ベース・アドレスが物理アドレス／実アドレスに変換され、別の実施形態では、ベース・アドレスが次のレベルのスーパーバイザのアドレスに変換される（すなわち、オペレーティング・システムがページ・アドレスを設定するときに、ベース・アドレスがスーパーバイザのアドレスに変換される）。その他の例が可能である。20

#### 【0159】

1つの例として、変換されていない（物理／実）ベース・アドレスおよび変換された（物理／実）ベース・アドレスの両方が格納される。これによって、すべての構成状態レジスタのアクセスでアドレス変換（例えば、動的アドレス変換（D A T : dynamic address translation））を実行する必要がなくなり、ページ・フォールトを処理する必要がなくなる。

#### 【0160】

1つの実施形態では、変換された（実／物理）ベース・アドレスがプロセッサのレジスタ内で維持され、変換されていないベース・アドレスがメモリ内構成状態レジスタ内で維持される。そのような実施形態では、構成状態レジスタのベース・アドレスの読み出しのソフトウェア要求に応答して、変換されていないアドレスが再度提供される。変換されたアドレスは、メモリ内の位置からそのようなアドレスにアクセスするために使用されてよい。その他の可能性が存在する。30

#### 【0161】

本明細書において説明されているように、1つまたは複数のメモリ内構成状態レジスタが格納されるメモリ内の位置を指定するベース・アドレスを含んでいる、構成状態レジスタなどの制御が提供される。これらのメモリ内構成状態レジスタは、プロセッサ内レジスタになるようにアーキテクチャによって定義されたレジスタであるが、本発明の1つまたは複数の態様に従って、メモリ内構成状態レジスタに変換されている。少なくとも、メモリに格納される構成値がレジスタではなく、メモリ内に存在するようにアーキテクチャによって定義されているため、これらのメモリ内構成状態レジスタは、メモリに格納される構成値とは異なっている。メモリに格納される構成値は、アーキテクチャによって定義されたプロセッサのレジスタではない。40

#### 【0162】

さらに別の態様では、プログラム環境と、例えばオペレーティング・システム環境もしくはその他のスーパーバイザ環境との間、または異なるアプリケーションもしくはスレッド間、あるいはその両方などでのコンテキスト切り替え時に、効率が達成される。コンテキスト切り替えが実行されるときに、以前のコンテキストのデータが保存される。1つの例では、コンテキスト・データを保存するために、構成状態レジスタの内容がプロセッサ内レジスタから読み出されて、メモリに保存される。次に、実行を再開するために構成状

態レジスタを読み込むことを含めて、次のコンテキストのデータが読み込まれる。これは高価なプロセスである。

#### 【 0 1 6 3 】

格納キューに基づく投機および不規則な順序での実行がこのプロセスを加速する、メモリ内構成状態レジスタの実行を伴う本発明の態様に従っても、コンテキストの保存および復元に関連する大きなコストが、やはり存在する。

#### 【 0 1 6 4 】

したがって、本発明の態様に従って、構成状態レジスタのページ操作によってコンテキスト切り替えが実行される。1つの例では、構成状態レジスタのメモリ内格納の位置が構成可能である。コンテキストを切り替えるときに、古い構成状態レジスタのデータを構成状態レジスタのメモリ・ユニット（またはページ）からコピーし、新しいデータを構成状態レジスタのページにコピーする代わりに、異なる構成状態レジスタのメモリ・ユニット（またはページ）が選択され、それによって、プロセッサから見える構成状態レジスタの値を変更する。

10

#### 【 0 1 6 5 】

本発明の態様に従って、構成状態レジスタのアンロードおよび再読み込みが必要となるのを避けるために、1つまたは複数の構成状態レジスタのメモリ内の位置（本明細書ではCSR補助メモリと呼ばれる）を示す、例えばベース構成状態レジスタ（本明細書ではベース・レジスタと呼ばれる）に含まれているベース・ポインタまたはベース・アドレス（本明細書ではベースと呼ばれる）を変更することによって、コンテキスト切り替えが実行される。

20

#### 【 0 1 6 6 】

この態様から恩恵を受けることができるコンテキスト切り替えは、オペレーティング・システムが異なるアプリケーション間で切り替えを実行する、オペレーティング・システムのコンテキスト切り替え、ハイパーバイザまたは仮想マシン・モニタが異なるパーティションまたは仮想マシンを切り替える、ハイパーバイザのコンテキスト切り替え、および異なるハードウェア・スレッド間のハードウェア・スレッドのコンテキスト切り替えを含めて、複数の種類が存在する可能性がある。各コンテキスト切り替えは、異なるレジスタに影響を与える。例えば、オペレーティング・システムによって使用されるコンテキスト切り替えの一部としてアプリケーションを切り替えるときに、そのアプリケーションに対応するいくつかの構成状態レジスタが別の位置に変更されるが、他の構成状態レジスタは変更されない（例えば、オペレーティング・システムの構成状態レジスタは変更されない）。さらに、ハイパーバイザのコンテキスト切り替えでは、切り替えられるさらに多くのレジスタが存在することがある。ハードウェア・スレッドのコンテキスト切り替えの場合も同様である。さらに、以下では、ハードウェア・スレッドのコンテキスト切り替えに関する詳細が説明される。

30

#### 【 0 1 6 7 】

1つの実施形態では、ハードウェア・スレッドのコンテキスト切り替えの場合、プロセッサが、スレッド・スケジューラを使用して、プロセッサに読み込まれる複数のスレッドから選択する。しかし、本発明の態様に従って、ハードウェアが、ハードウェアによってスケジューリングされ得る複数のスレッドから選択してよく、この複数のスレッドの数は、プロセッサに読み込まれるハードウェア・スレッドのコンテキストの数を超える。すなわち、本発明の態様に従って、本明細書において説明されているように、コンテキスト切り替えの能力は、ハードウェアが、プロセッサに読み込まれるスレッドよりも多くのスレッドを使用できるようにする。スレッドが選択され、ハードウェアが、そのスレッドのメモリ内構成情報を選択することによって、スレッドをスケジューリングする。1つの実施形態では、実行可能なレジスタの一部が、チップ上のレジスタ・ファイルまたは高速な第2のレベルのストレージに格納される。別の実施形態では、汎用レジスタも、メモリ内の構成ページに格納され、スレッドがスケジューリングされるときに、そこから読み込まれる。これは、必要性が生じたときに（例えば、最初にアクセスされたときに、各レジスタ

40

50

に対して)、または一括して(例えば、スケジューリングされた時間にすべてのレジスタに対して)、実行される。

#### 【0168】

1つの実施形態では、ソフトウェア・エージェント(例えば、オペレーティング・システムまたはハイパーバイザ)に、別の構成状態レジスタのベースへのポインタを変更することを決定させるのではなく、ハードウェアが、ハードウェアの基準に応答して、ベース・ポインタ自体を調整する。ハードウェアにおいて複数のスレッドのうちの1つが選択され、複数のスレッドに基づいて、構成状態レジスタを含んでいるシステム・メモリ・ページへのポインタのうちの1つが選択される。

#### 【0169】

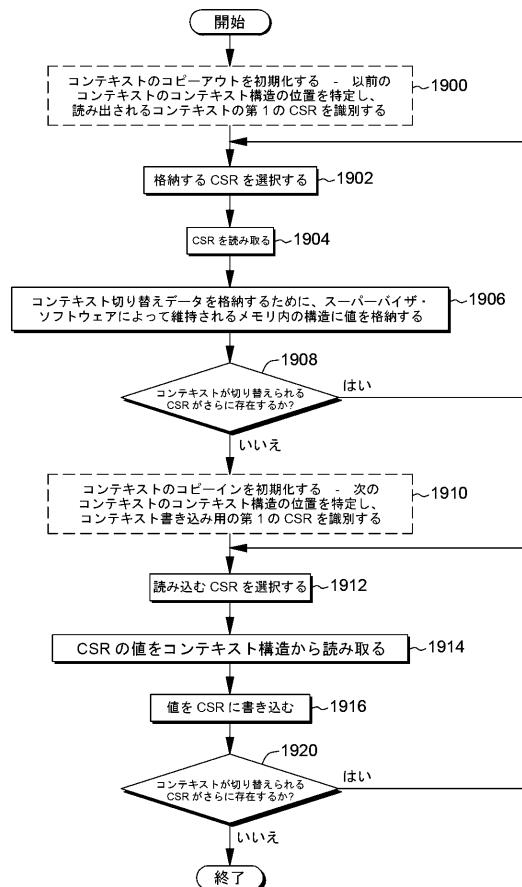

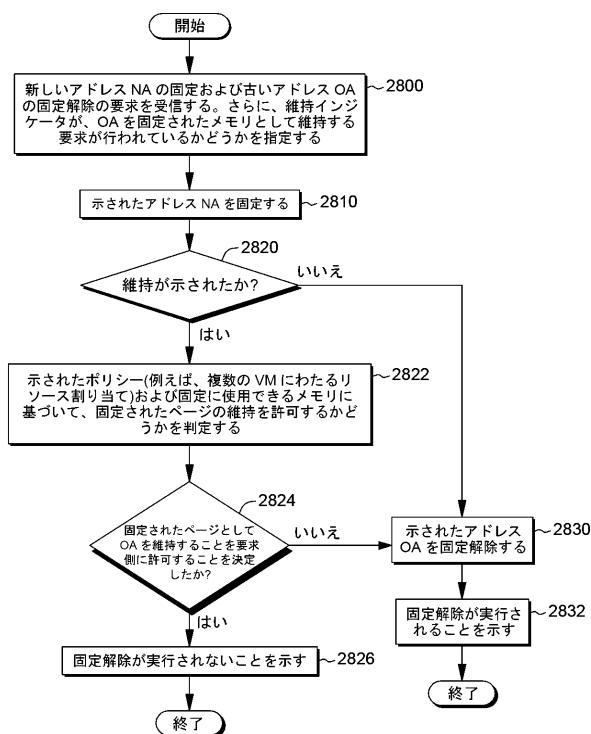

コンテキスト切り替えを実行することに関連する詳細が、図28および図29を参照してさらに説明される。図28は、データがコピーされるコンテキスト切り替えを実行するための1つのプロセスを示しており、図29は、本発明の態様に従ってポインタが変更されるコンテキスト切り替えを実行するための別のプロセスを示している。

#### 【0170】

最初に図28を参照すると、コンテキスト切り替えが実行される場合、コンテキストのコピーアウトが、古いコンテキスト・データをコピーアウトするよう初期化される(ステップ1900)。この初期化は、以前のコンテキストのコンテキスト構造(例えば、スーパーバイザ構造)の位置を特定し、読み出されるコンテキストの第1の構成状態レジスタを識別することを含む。

10

#### 【0171】

例えば、コンテキストは、仮想マシン、論理パーティション、プロセス、スレッドなどのうちの1つであることができる。コピーアウト・プロセスが続行する。

#### 【0172】

格納される構成状態レジスタが選択される(ステップ1902)。この反復では、この構成状態レジスタは、上で識別された構成状態レジスタである。選択された構成状態レジスタが読み取られ(ステップ1904)、コンテキスト切り替えデータを格納するために、構成状態レジスタの内容が、例えばスーパーバイザ・ソフトウェア(またはハードウェア)によって維持されるメモリ内の構造に格納される(ステップ1906)。次に、コンテキストが切り替えられる構成状態レジスタがさらに存在するかどうかに関する判定が行われる(照会1908)。そのような構成状態レジスタが存在する場合は、処理がステップ1902を続行する。

20

#### 【0173】

以前のコンテキストのデータをコピーアウトした後に、新しいコンテキストについて、コピーイン・プロセスが実行される。したがって、コンテキストのコピーインが初期化され、次のコンテキストのコンテキスト構造の位置が特定され、コンテキスト書き込み用の第1の構成状態レジスタが識別される(ステップ1910)。メモリに読み込まれる構成状態レジスタが選択され(ステップ1912)、選択された構成状態レジスタの内容がコンテキスト構造(例えば、スーパーバイザ構造)から読み取られる(ステップ1914)。読み取られたコンテキスト・データが、メモリ内の構成状態レジスタに書き込まれる(ステップ1916)。コンテキストが切り替えられる構成状態レジスタがさらに存在するかどうかに関する判定が行われる(照会1920)。そのような構成状態レジスタが存在する場合は、処理がステップ1912を続行する。そのような構成状態レジスタが存在しない場合は、処理が完了する。

30

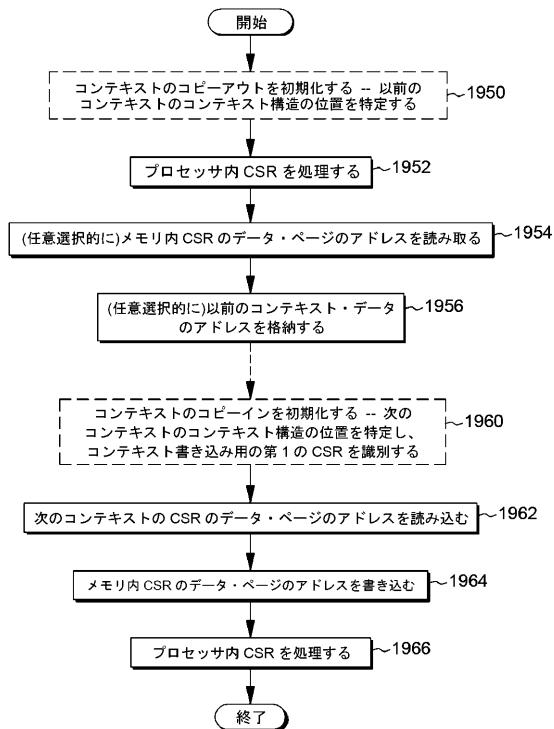

#### 【0174】

図29を参照すると、本発明の態様に従って、コンテキスト切り替えプロセスの別の例が説明されている。この例では、データをコピーする代わりに、データへのポインタが操作される。最初に、コンテキストのコピーアウトが初期化され、以前のコンテキストのコンテキスト構造(例えば、スーパーバイザ構造またはハードウェア構造)の位置が特定される(ステップ1950)。この場合も、コンテキストは、仮想マシン、論理パーティシ

40

50

ヨン、プロセス、スレッドなどのうちの 1 つであることができる。次に、レジスタの内容がメモリに格納されるように、プロセッサ内構成状態レジスタが処理される（ステップ 1952）。1 つの実施形態では、この処理は、図 28 を参照して説明されているように、例えばコピー・ループを使用して実行される。別の実施形態では、この処理は、例えば一括コピー動作（例えば、S T \_ C S R）を使用して実行される。

#### 【0175】

メモリ内構成状態レジスタのデータ・ユニットのアドレス（すなわち、例えば、このコンテキストの構成状態レジスタを格納するために使用されるメモリ・ページのアドレス（ベース・アドレス））が読み取られ（ステップ 1954）、コンテキスト構造に格納されてよい（ステップ 1956）。1 つの例では、このアドレスが変化せず、そのため、このアドレスを繰り返し読み取ってコンテキスト構造に格納する必要がない。代わりに、このアドレスは、最初に、またはそのページが新しい位置に移動されたときに、格納される。この値は、コンテキスト切り替えデータを格納するために、例えばスーパーバイザ・ソフトウェアまたはハードウェアによって維持されるメモリ内の構造に格納される。

10

#### 【0176】

コピーアウト・プロセスの実行後に、新しいコンテキスト・データを指示するため、コピーイン・プロセスが利用される。したがって、コンテキストのコピーイン・プロセスが初期化され、次のコンテキストのコンテキスト構造（例えば、スーパーバイザ構造またはハードウェア構造）の位置が特定され、コンテキスト書き込み用の第 1 の構成状態レジスタが識別される（ステップ 1960）。次のコンテキストの構成状態レジスタのデータ・ユニットのアドレスが読み込まれる（ステップ 1962）。すなわち、例えば、新しいコンテキストの構成状態レジスタを格納するためのメモリ・ページのアドレス（ベース・アドレス）が取得される。さらに、メモリ内構成状態レジスタのデータ・ページのアドレス（ベース・アドレス）が書き込まれる（ステップ 1964）。さらに、プロセッサ内構成状態レジスタが処理される（ステップ 1966）。1 つの例として、例えばコピー・ループまたは一括読み込み（例えば、L D \_ C S R）を使用して、このコンテキストのプロセッサ内構成状態レジスタがメモリから読み込まれる。

20

#### 【0177】

前述したように、コンテキスト切り替えにおいてポインタ操作が使用されてよい。これは、仮想マシンの移行にも当てはまる。

30

#### 【0178】

1 つの実施形態では、仮想マシン（または論理パーティション）の移行をまたはライブ・マシンの移行あるいはその両方を加速するために、メモリ内レジスタが使用されてよい。1 つの例では、従来手法に従ってページが移行されるが、メモリ内構成状態レジスタが移動されない。1 つの例として、プロセッサ内構成状態レジスタを捕捉するために S T \_ C S R 命令または動作が使用されるが、構成状態レジスタが移動されない。メモリ内の構成のメモリ・ページは移動される。

#### 【0179】

さらに別の実施形態では、ライブ・マシンの移行の場合、マシンが休止されているときに、メモリ内構成状態レジスタの状態が移動される。複数のコンテキスト（例えば、複数のスレッド / プロセスなど）が存在する場合、この移動が複数のページを含んでよい。

40

#### 【0180】

1 つの実施形態では、ホストの移行形式およびターゲットの移行形式に互換性がない場合（例えば、構成状態レジスタが、アーキテクチャの異なる実装によってメモリ内構成状態レジスタのページ内の異なるオフセットにマッピングされる場合）、移行エージェントによって調整が実行される。1 つのそのような実施形態では、構成状態レジスタ形式のアーキテクチャまたはマイクロアーキテクチャのバージョン番号が提供され、受信システムがレイアウトを調整する責任を負う。別の実施形態では、受信システムおよび送信システムが転送形式をネゴシエートする。別の実施形態では、転送形式が、例えば構成状態レジスタの値の線形リストまたは<キー、値>の対として定義され、このキーは構成状態レジ

50

スタ番号であり、この値は構成状態レジスタの値である。

#### 【0181】

さらに他の実施形態では、プロセッサが、外部で構成された構成状態レジスタのレイアウト・マップ（例えば、レイアウト識別子を構成状態レジスタに読み込むことによって、ソフトウェアが指定する）に基づいて再マッピング論理を適応させて、複数のバージョンのレイアウトをサポートしてよい。

#### 【0182】

少なくとも一部のプロセッサの実施形態では、設計によって、一部の値を、メモリ内レジスタとして識別されたレジスタのカスタムのプロセッサ内の位置にキャッシュしてよい。したがって、コンテキスト切り替えを実行するときに、キャッシュされたコピー（すなわち、個別の古いキャッシュされた値）が同期される。1つの例では、古いキャッシュされた値を無効化することをプロセッサに示すコンテキスト同期命令（`c s y n c`）が提供される。この命令は、例えば、コンテキスト切り替えが実行されるたびに実行される。1つの例では、コンテキストのすべての構成状態レジスタに対応するキャッシュされた値が無効化される。他の例では、特定のレジスタのキャッシュされた値が無効化される。

10

#### 【0183】

本明細書において説明されているように、コンテキスト切り替え時に、構成状態レジスタをコピーする代わりに、新しいページが示されてよい。このようにして、構成状態レジスタのコンテキスト・イメージがすでに保存されているため、少なくともメモリ内で維持されている構成状態レジスタに関して、コンテキスト切り替えを減らす。

20

#### 【0184】

さらに、1つの実施形態では、ページ置き換えを伴うコンテキスト切り替えが有効化される。新しいコンテキストのメモリ・ページを読み込む前に、（少なくとも、メモリ内に存続しているレジスタに関して）メモリ・イメージが同期される。

#### 【0185】

1つの実施形態に従って、構成状態レジスタ同期命令が提供される。具体的には、この命令は、すべてのキャッシュされた値をフラッシュし、切り替えが実行された後にキャッシュを抑制してよく、反対に、値をキャッシュに再び保存できるということを示してよい。例示的な命令は次を含む。

30

#### 【0186】

送信CSRの同期      `s y n c _ o _ C S R`

#### 【0187】

新しい補助ページの読み込み      `m t s p r    T C B R, n e x t _ u - > s p r _ p a g e`

#### 【0188】

受信SPRの同期      `s y n c _ i _ C S R`

#### 【0189】

別の実施形態では、ベース・レジスタ（例えば、`T C B R`）への構成状態レジスタへの移動命令（例えば、`m t s p r`命令）が、キャッシュされた送信値および受信値の同期を自動的に実行する。

40

#### 【0190】

さらに別の態様では、1つまたは複数のメモリ内構成状態レジスタを格納するために使用されるメモリ内の位置を示す、ベース構成状態レジスタに格納されてよい、ゲスト・ベース・アドレス（guest base address）を読み込むことに基づいて、ページ・フォールトの可能性を防ぐために、ゲスト・ベース・アドレスから対応するホスト・ベース・アドレスへのアドレス変換が実行される。この変換は、例えば直ちに（すなわち、ベース・アドレスを受信することに基づいて、ベース・アドレスを使用する前に、例えばストレージの参照中に）実行される。例えば、仮想アドレスがベース・レジスタに読み込まれるときには（例えば、ゲスト・ベース・アドレスを、ベース・アドレスとして使用される構成状態ベース・レジスタ（例えば、`T C B R`）に読み込むことなどの、ベースへの読み込み）、シ

50

システムが物理メモリ・アドレスへのアドレス変換を自動的に実行し、変換された物理アドレスが仮想アドレスと共に捕捉される。1つのアーキテクチャの実施形態に従って、ベース・レジスタへの読み込みが、変換の実行を引き起こすか、または引き起こす可能性のある命令として識別される。

#### 【0191】

アドレスを変換できない場合、変換フォールトが選択される。例えばページ・テーブル・エントリ（下で説明される）で指定された許可に従って、ページが読み取りおよび書き込みのためにアクセス可能になるか、またはページ・フォールトが引き起こされる。

#### 【0192】

実行されるベース・アドレスの変換を引き起こすか、または引き起こす可能性のある動作の実行に基づいてアドレス変換を自動的に実行することに関する詳細が、図30を参照してさらに説明される。この処理はプロセッサによって実行され、1つの例では、この処理は、構成状態レジスタ・メモリ・ベース・レジスタに対する構成状態レジスタへの移動命令（例えば、`m t s p r` 命令）の実行に基づいて実行される。この処理は、その他の命令の実行に基づいて実行されてもよい。

10

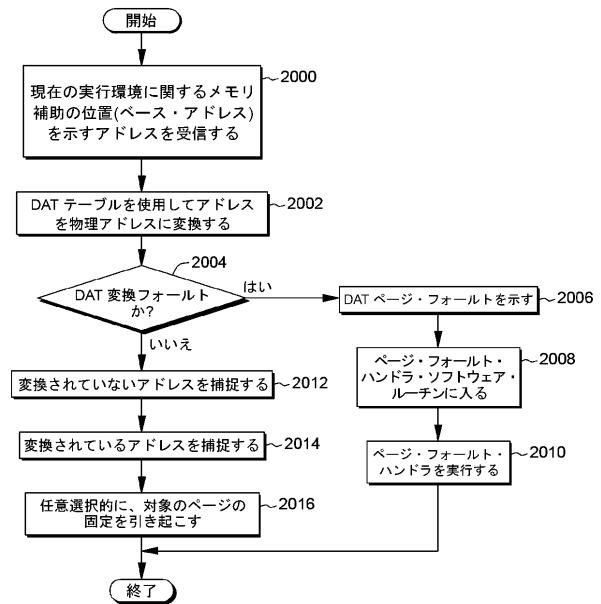

#### 【0193】

この命令の実行に基づいて、現在の実行環境に関するメモリ補助の位置を示すアドレス（例えば、ベース・アドレス）が受信される（ステップ2000）。`m t s p r` の1つの定義に従って、場合によっては動的アドレス変換（DAT）のページ・フォールトを招くように、`m t s p r` が定義される。したがって、本発明の態様に従って、変換が必要とされるということを決定する前であっても、`m t s p r` の一部としてアドレス変換が自動的に実行される。

20

#### 【0194】

受信されたベース・アドレスが、例えばDATテーブルを使用して、物理ベース・アドレスに変換され（ステップ2002）、その例が下でさらに説明される。DAT変換フォールトが発生したかどうかに関する判定が行われる（照会2004）。DAT変換フォールトが発生した場合、DATページ・フォールトが示される（ステップ2006）。ページ・フォールト・ハンドラ・ソフトウェア・ルーチンに入り（ステップ2008）、ページ・フォールト・ハンドラが実行される（ステップ2010）。1つの例では、このフォールトが許容されるフォールト（例えば、ページ・アウト）である場合、ページ・フォールト・ハンドラに従って、命令が再開される。そうでない場合、コンテキストまたは実行環境（例えば、オペレーティング・システム、ハイパーバイザ、仮想マシン、スレッド、プロセスなど）がエラー指示を受信し、場合によってはコンテキストの終了を引き起こす。

30

#### 【0195】

照会2004に戻り、DAT変換フォールトが存在しない場合、変換されていないベース・アドレスが捕捉される（例えば、レジスタに格納される）（ステップ2012）。さらに、変換されたベース・アドレスが捕捉される（例えば、キャッシュされる）（ステップ2014）。任意選択的に、対象のページが固定される（ステップ2016）。

40

#### 【0196】

動的アドレス変換の一例に関する詳細が、図31～図32を参照してさらに説明される。この処理は、プロセッサによって実行される。

#### 【0197】

動的アドレス変換は、仮想アドレスを対応する実（または絶対）アドレスに変換するプロセスである。動的アドレス変換は、CPUによって生成された命令アドレスおよびデータ・アドレスに対して指定されてよい。仮想アドレスは、一次仮想アドレス、二次仮想アドレス、AR（Access Register：アクセス・レジスタ）によって指定された仮想アドレス、またはホーム仮想アドレスであってよい。アドレスは、一次アドレス空間制御要素（ASCE：address space control element）、二次アドレス空間制御要素、ARによって指定されたアドレス空間制御要素、またはホーム・アドレス空間制御要素をそれぞれ用

50

いて変換される。適切なアドレス空間制御要素の選択後の変換プロセスは、4種類の仮想アドレスのすべてで同じである。アドレス空間制御要素は、セグメント・テーブル指定または領域テーブル指定であってよい。セグメント・テーブル指定または領域テーブル指定は、実ストレージまたは絶対ストレージ内でオペレーティング・システムによって確立されたテーブルを用いて実行される変換を引き起こす。

#### 【0198】

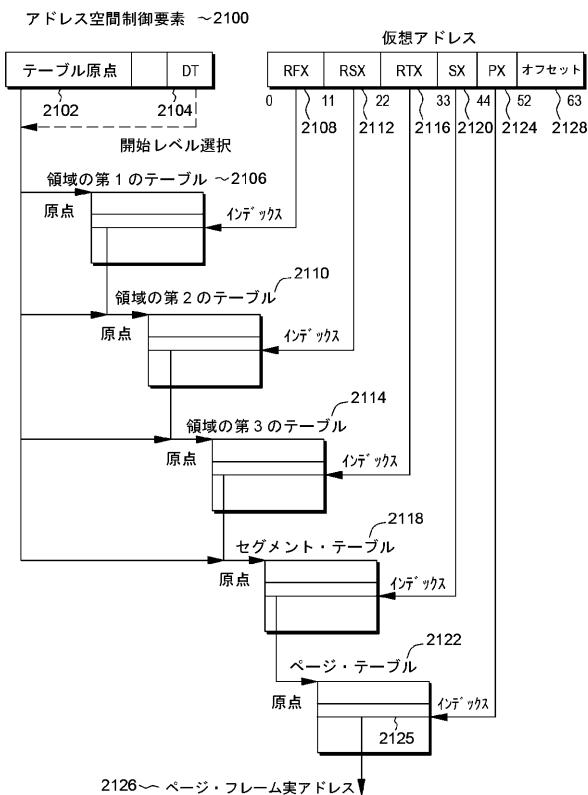

変換のプロセスにおいて、セグメント・テーブル指定または領域テーブル指定を使用するときに、情報の3種類の単位（領域、セグメント、およびページ）が認識される。それに応じて、仮想アドレスが4つのフィールドに分割される。1つの例では、64ビット・アドレスの場合、ビット0～32が領域インデックス（R X : region index）と呼ばれ、ビット33～43がセグメント・インデックス（S X : segment index）と呼ばれ、ビット44～51がページ・インデックス（P X : page index）と呼ばれ、ビット52～63がバイト・インデックス（B X : byte index）と呼ばれる。仮想アドレスのR Xの部分は、それ自体が3つのフィールドに分割される。1つの実施形態では、ビット0～10が領域の第1のインデックス（R F X : region first index）と呼ばれ、ビット11～21が領域の第2のインデックス（R S X : region second index）と呼ばれ、ビット22～32が領域の第3のインデックス（R T X : region third index）と呼ばれる。

#### 【0199】

仮想アドレスを実アドレスに変換する1つの例が、図31を参照して説明される。このプロセスは、本明細書ではDATウォーク（またはページ・ウォーク）と呼ばれ、DATウォークでは、アドレス変換テーブル内を進んで、あるアドレス（例えば、仮想アドレス）を別のアドレス（例えば、実アドレス）に変換する。この例では、アドレス空間制御要素（ASCE）2100がテーブル原点2102および指定タイプ（DT : designation type）制御2104を含んでおり、指定タイプ制御2104は、変換の開始レベルの指示（すなわち、階層内のどのレベルでアドレス変換が開始するかの指示）である。テーブル原点2102およびDT2104を使用して、特定のテーブルの原点が特定される。次に、このテーブルに基づいて、仮想アドレスのビットが、特定のテーブルのインデックスを参照して次のレベルのテーブルの原点を取得するために使用される。例えば、領域の第1のテーブル（RFT : region first table）2106が選択された場合、仮想アドレスのビット0～10（RFX）2108が、領域の第1のテーブルのインデックスを参照して領域の第2のテーブル2110の原点を取得するために使用される。次に、仮想アドレスのビット11～21（RSX）2112が、領域の第2のテーブル（RST : region second table）2110のインデックスを参照して領域の第3のテーブル2114の原点を取得するために使用される。同様に、仮想アドレスのビット22～32（RTX）2116が、領域の第3のテーブル（RTT : region third table）2114のインデックスを参照してセグメント・テーブル2118の原点を取得するために使用される。次に、仮想アドレスのビット33～43（SX）2120が、セグメント・テーブル2118のインデックスを参照してページ・テーブル2122の原点を取得するために使用され、仮想アドレスのビット44～51（PX）2124が、ページ・テーブル2122のインデックスを参照して、ページ・フレーム実アドレス（PFR A : page frame real address）2126を含んでいるページ・テーブル・エントリ（PTE : page table entry）2125を取得するために使用される。次に、このページ・フレーム実アドレスがオフセット2128（ビット52～63）と結合されて（例えば、連結されて）、実アドレスを取得する。1つの実施形態では、次に接頭辞の付加が適用されて、対応する絶対アドレスを取得してよい。

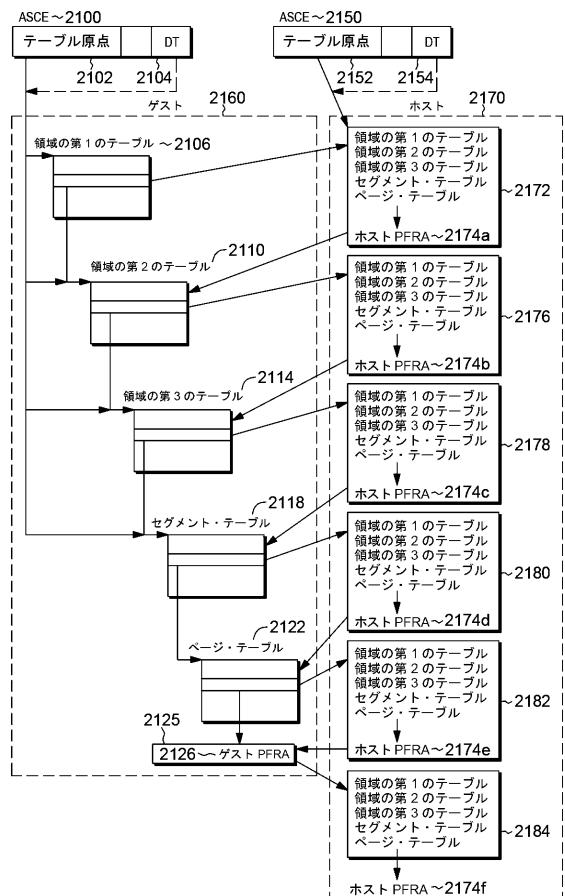

#### 【0200】

アドレス変換の別の例が、図32を参照して説明される。この例では、DATウォークが実行されて、初期ゲスト仮想アドレスを最終的なホスト実アドレスに変換する。この例では、アドレス空間制御要素（ASCE）2100はゲスト・アドレス空間制御要素であり、ASCE2100のDT2104は、ゲスト・アドレス変換構造2160によって決

10

20

30

40

50

定されたゲスト変換が、テーブル原点 2102 によって指示された領域の第 1 のテーブル 2106 で開始することを示す。したがって、初期ゲスト仮想アドレス（例えば、RFX2108）の適切なビットが、領域の第 1 のテーブル 2106 のインデックスを参照して領域の第 1 のテーブルのエントリのポインタを取得するために使用される。領域の第 1 のテーブルのエントリ（RFTE : region first table entry）のアドレスは、ゲスト実アドレスまたはゲスト絶対アドレスである。このゲスト実アドレスまたはゲスト絶対アドレスは、主記憶装置の原点および制限が適用されて、適切な場合に、ホスト仮想アドレスに対応する。次に、ホスト・アドレス変換構造 2170 を使用して、この中間のホスト仮想アドレスが変換される。具体的には、アドレス空間制御要素（ASCE）2150 は、ホスト・アドレス変換構造 2172 内の変換の開始レベルを示すために使用されるホスト・アドレス空間制御要素である。DT2154 によって示された開始レベル（例えば、領域の第 1 のテーブル）に基づいて、図 31 を参照して説明されたように、ホスト仮想アドレスの特定のビットが、テーブル原点 2152 で示されたテーブルのインデックスを参照するために使用され、このテーブルが、ホスト・アドレス変換 2172 を使用した変換に使用される。ゲスト RFTE に対応するホスト仮想アドレスの変換は、ホスト・ページ・フレーム実アドレス（PTRA）2174a が取得されるまで継続する。

#### 【0201】

中間のホスト・ページ・フレーム実アドレスにあるデータは、ゲスト・アドレス変換構造（例えば、この特定の例では、ゲストの領域の第 2 のテーブル 2110）の次のレベルへのポインタであり、前述したように変換が継続する。具体的には、ホスト・アドレス変換構造 2176、2178、2180、および 2182 が、ゲストの領域の第 2 のテーブル 2110、領域の第 3 のテーブル 2114、セグメント・テーブル 2118、およびページ・テーブル 2122 に関連付けられた中間のホスト仮想アドレスを変換するために使用され、その結果、ホスト PTRA 2174b、2174c、2174d、および 2174e をそれぞれ得る。ホスト・ページ・フレーム実アドレス 2174e は、ゲスト・ページ・テーブル・エントリ 2125 のアドレスを含む。ゲスト・ページ・テーブル・エントリ 2125 は、ゲスト・ページ・フレーム実アドレス 2126 を含み、ゲスト・ページ・フレーム実アドレス 2126 が初期ゲスト仮想アドレスからのオフセットと連結されて、対応するゲスト絶対アドレスを取得する。場合によっては、次に、主記憶装置の原点および制限が適用されて、対応するホスト仮想アドレスを計算し、その後、前述したように、アドレス変換構造 2184 を使用してこのホスト仮想アドレスが変換され、ホスト・ページ・フレーム実アドレス 2174f を取得する。次に、ホスト・ページ・フレーム実アドレスがホスト仮想アドレスのオフセット（例えば、ビット 52 ~ 63）と結合されて（例えば、連結されて）、最終的なホスト実アドレスを取得する。これによって、ホスト実アドレスへのゲスト仮想アドレスの変換が完了する。

#### 【0202】

上記の例では変換が領域の第 1 のテーブルで開始しているが、これは 1 つの例にすぎない。変換は、ゲストまたはホストのいずれかの任意のレベルで開始してよい。

#### 【0203】

1 つの実施形態では、アドレス変換を改善するために、仮想アドレスから実アドレスまたは絶対アドレスへの変換マッピングが、トランスレーション・ルックアサイド・バッファ（TLB : translation look-aside buffer）のエントリに格納される。TLB は、仮想アドレスの変換速度を改善するためにメモリ管理ハードウェアによって使用されるキャッシュである。次に仮想アドレスの変換が要求されたときに、TLB がチェックされ、その仮想アドレスが TLB 内にある場合、TLB のヒットが存在し、実アドレスまたは絶対アドレスが TLB から取り出される。その仮想アドレスが TLB 内にない場合、前述したようにページ・ウォークが実行される。

#### 【0204】

示されているように、ゲスト変換が TLB に含まれてよい。これらのエントリは、1 つまたは複数のホスト変換を暗黙的に含む複合ゲストノホスト・エントリであってよい。例

10

20

30

40

50

えば、ゲスト仮想 T L B エントリは、初期ゲスト仮想アドレスから最終的なホスト実アドレスまたはホスト絶対アドレスまでの変換全体をバッファしてよい。この場合、図 3 2 で前述したように、ゲスト T L B エントリは、すべての中間のホスト変換 2 1 7 2、2 1 7 6、2 1 7 8、2 1 8 0、および 2 1 8 2、ならびに最終的なホスト変換 2 1 8 4 を暗黙的に含む。別の例では、階層的 T L B が、初期ゲスト仮想アドレスからゲスト・ページ・テーブル 2 1 2 2 の関連付けられた原点までの変換をバッファする T L B の第 1 のレベル内のエントリ、およびゲスト・ページ・テーブル・エントリのアドレスから最終的なホスト実アドレスまたはホスト絶対アドレスまでの変換をバッファする T L B の第 2 のレベルからの別のエントリを含んでよい。この例では、図 3 2 に示されているように、T L B の第 1 のレベル内のゲスト・エントリが、ゲスト領域およびセグメント・テーブルを補助するホスト変換に対応する中間のホスト変換 2 1 7 2、2 1 7 6、2 1 7 8、および 2 1 8 0 を暗黙的に含み、第 2 のレベル内のゲスト・エントリが、ゲスト・ページ・テーブルを補助する中間のホスト変換 2 1 8 2 および最終的なホスト変換 2 1 8 4 を暗黙的に含む。トランスレーション・ルックアサイド・バッファの多くの実装が可能である。

10

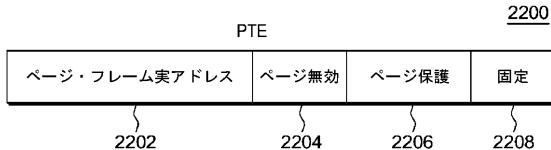

## 【0 2 0 5】

上記の例では、ページ・フレーム実アドレスが、ページ・テーブルのページ・テーブル・エントリに含まれる。ページ・テーブルは 1 つまたは複数のエントリを含み、ページ・テーブル・エントリの詳細が、図 3 3 を参照してさらに説明される。

## 【0 2 0 6】

1 つの例では、ページ・テーブル・エントリ ( P T E ) 2 2 0 0 が、メモリの特定のページに関連付けられ、例えば以下を含む。

20

## 【0 2 0 7】

( a ) ページ・フレーム実アドレス ( P F R A ) 2 2 0 2 : このフィールドは、実(例えば、ホスト実)ストレージ・アドレスの左端のビットを提供する。これらのビットが右側の仮想アドレスのバイト・インデックス・フィールドと連結された場合に、実アドレスが取得される。

## 【0 2 0 8】

( b ) ページ無効インジケータ ( I : Indicator ) 2 2 0 4 : このフィールドは、ページ・テーブル・エントリに関連付けられたページが使用可能であるかどうかを制御する。このインジケータが 0 である場合、ページ・テーブル・エントリを使用することによって、アドレス変換が進む。インジケータが 1 である場合、ページ・テーブル・エントリを変換に使用することはできない。

30

## 【0 2 0 9】

( c ) ページ保護インジケータ 2 2 0 6 : このフィールドは、ページへの格納アクセスが許可されるかどうかを制御する。

## 【0 2 1 0】

( d ) 固定インジケータ 2 2 0 8 : このフィールドは、本発明の態様に従って、このページが固定されるかどうかを示すために使用される。1 つの例では、1 が、このページが固定されることを示し、0 が、このページが固定されないことを示す。

40

## 【0 2 1 1】

ページ・テーブル・エントリは、本明細書に記載されたフィールドより多いフィールド、少ないフィールド、または異なるフィールド、あるいはその組合せを含んでよい。例えば、Power Architecture では、P T E が、メモリの対応するブロックが参照されたかどうかを示す参照インジケータ、またはメモリの対応するブロックが格納されていることを示す変更インジケータ、あるいはその両方を含んでよい。その他の変形が可能である。

## 【0 2 1 2】

本発明のさらに別の態様では、管理の柔軟性の向上を可能にするために、例えば、ホストおよびゲストの属性、コンテキスト、または実行環境( 例えば、スレッドの状態、アプリケーションの状態、オペレーティング・システムの状態、ハイパーバイザの状態、特定

50

のゲスト・オペレーティング・システムまたはホスト・オペレーティング・システムのレベルなど)、あるいはその組合せに基づいて、構成状態レジスタが分離されて割り当たられる。例えば、構成状態レジスタは、ハイパーバイザ、オペレーティング・システム、アプリケーション、スレッド番号、またはその他の実行環境などによって分離されてよい。

#### 【0213】

特定の例として、ハイパーバイザ特権構成状態レジスタが、ハイパーバイザによって割り当たされたメモリのユニット(例えば、ページ)に格納され、オペレーティング・システム特権構成状態レジスタが、オペレーティング・システムのメモリのユニット(例えば、ページ)に格納される、などとなる。さらに、複数のスレッドがサポートされ、スレッドごとに構成状態レジスタが複製される場合、メモリの別々のユニット(例えば、ページ)がスレッドごとにサポートされてよい。そのような分離の例が、図34に示されている。

#### 【0214】

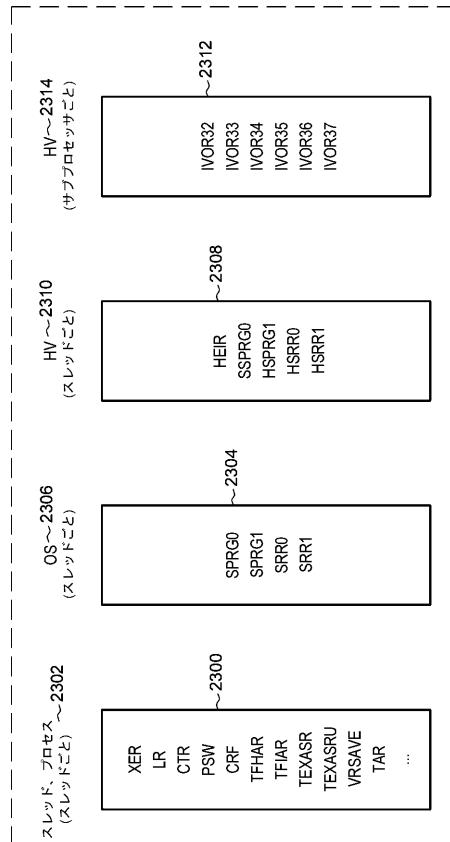

図34に示されているように、構成状態レジスタの1つのセット2300がスレッドまたはプロセス2302によって使用され、構成状態レジスタの別のセット2304がオペレーティング・システム2306によって使用され、構成状態レジスタのさらに別のセット2308がハイパーバイザ2310によって使用され、構成状態レジスタのさらに別のセット2312がハイパーバイザ2314によって使用される。その他の例も可能である。

#### 【0215】

1つの例では、特定の実行環境の構成レジスタは、その実行環境に対して静的に定義され、その実行環境によって読み取り可能または書き込み可能なレジスタを含む。さらに別の例では、レジスタが使用に基づいて動的に割り当たられる。その他の例も可能である。

#### 【0216】

1つの実施形態では、別々のメモリ領域が(例えば、複数の割り当て可能な変換ユニットとして)、別々に制御可能な各実行環境(例えば、スレッド、プロセス、オペレーティング・システム、ハイパーバイザ)に割り当たられ、したがって、その実行環境に関連付けられた構成状態レジスタのセットが、そのメモリ領域に割り当たられる。1つの例では、一部の構成状態レジスタが複数の実行環境からアクセス可能であってよい(例えば、オペレーティング・システムから読み取りアクセス可能であり、ハイパーバイザから読み取り/書き込み(R/W: read/write)アクセス可能である)ため、論理的所有権に基づいて構成状態レジスタが対応するメモリ領域に割り当たられる。

#### 【0217】

異なる実行環境が異なる特権レベルを有していることがあるが、1つの様態では、特権レベルのレベルが高いほど、より低いレベルのアクセスを制御することができる。本明細書に記載されたLD\_CSR命令およびST\_CSR命令ならびに同期動作を使用して、特定の特権レベルが指定されてよい。

#### 【0218】

1つの例では、前述したように構成状態レジスタ番号が再マッピングされ、すなわち、各グループ化に関してレジスタを同じ位置に配置するように、構成状態レジスタ番号のインデックスが圧縮される。

#### 【0219】

実行環境ごとにレジスタの特定のセットを提供することによって、コンテキスト切り替えを含む特定の種類の処理が容易になる。前述したように、実行環境に基づいてレジスタの特定のセットを割り当て、別々のメモリ・ユニットをそれらのセットに割り当てるこによって、レジスタおよび、それらのレジスタを使用するプロセス(コンテキスト切り替えを含む)の管理を容易にする。

#### 【0220】

本明細書において説明されているように、構成状態レジスタの状態をアンロードして再び読み込むのではなく、構成状態ベース・レジスタ内のベース・アドレス・ポインタを変

10

20

30

40

50

更することによって、コンテキスト切り替えが実行されてよい。これを実現するために、ユーザ・モードの状態が、ユーザのコンテキストを切り替えるように、スーパーバイザの状態から独立して切り替え可能になり、オペレーティング・システムの状態が、仮想マシンを切り替えるように、ハイパーバイザの状態から独立して切り替え可能になり、ハードウェアごとのスレッドまたはサブプロセッサの状態が、それらが他のスレッド／サブプロセッサから独立して切り替えられる場合、独立して切り替え可能になる。別々のメモリ領域および別々に割り当て可能な構成状態レジスタが、これを容易にする。

#### 【0221】

本発明の1つの態様に従って、別々の構成状態ベース・レジスタが、メモリ内構成状態レジスタの各グループ化の位置（ベース）を指定する。さらに、少なくとも1つの実施形態では、ベース・レジスタの各々に対するアクセス制御が、適切なアクセス許可を有する。例えば、オペレーティング・システムによって切り替えられるコンテキストの場合、オペレーティング・システム特権が、ベース・レジスタを変更するための最低限の前提条件であり、ハイパーバイザによって切り替えられるコンテキストの場合、ハイパーバイザ特権が、そのようなベース・レジスタを変更するための最低限の前提条件である、などとなる。

#### 【0222】

さらに別の態様では、1つまたは複数の構成状態レジスタの格納（すなわち、CSR補助メモリ）を提供するホスト・レベルのソフトウェア（ハイパーバイザまたは仮想マシン・モニタなど）によるメモリ・ユニット（例えば、ページ）の移動を防ぐための能力が、提供される。1つの例では、この能力は、メモリ・ユニットを固定すること、およびCSR補助メモリの自動的固定の指示を提供することを含む。

#### 【0223】

1つまたは複数の構成状態レジスタの格納を提供するメモリのベースを示す構成状態レジスタ（すなわち、TCBRなどのベース・レジスタ）が書き込まれる場合、アーキテクチャの仕様に従って、指示が現在のゲストのホストに提供される。少なくとも1つの実施形態では、この指示は例外に対応する。1つの実施形態では、例外タイプが、構成状態ベース・レジスタに対する書き込みイベントを示す。構成状態ベース・レジスタの変更の指示を受信することに応答して、少なくとも1つのホスト・スーパーバイザ・ソフトウェア（例えば、ハイパーバイザまたは仮想マシン・モニタ）が、ページ固定情報を更新するための動作を実行する。本発明の1つの態様では、固定情報を更新することが、固定されたCSR補助メモリ・ページのアドレスを記録すること、またはページに対応する固定インジケータを設定することを含む。別の態様では、固定情報を更新することが、特定の構成状態ベース・レジスタの以前に記録されたアドレスを、固定されたCSR補助メモリに対応する1つまたは複数の記録されたアドレスのプールから削除すること、または固定インジケータをリセットすることによって、以前に固定されたCSR補助メモリ・ページを固定解除することをさらに含む。

#### 【0224】

本発明の1つの態様に従って、これらの更新によって、1つまたは複数のホスト・レベルがCSR補助メモリをページ・アウトまたは移動しないことを保証し、それによって、キャッシュされたアドレス変換を無効化し、そうしなければ、構成状態レジスタに対する更新を引き起こし、ページ変換フォールトをもたらす。本発明の別の態様では、CSR補助メモリの位置の通知を提供し、いずれかのキャッシュされた変換を更新する機会を1つまたは複数のホストに与えることによって、固定情報が、CSR補助メモリの位置を移動するために使用されてもよい。

#### 【0225】

さらに、複数のレベルのゲスト方式をサポートするために、構成状態レジスタを補助するメモリ（CSR補助メモリ）を指し示すベース・レジスタを初期化する命令が、ホストの複数のレベルで例外を他動詞的に引き起こして、適切な固定を保証するように、さらに指定されてよい。1つの実施形態では、ホストの1つのレベルのみが通知され、そのホス

10

20

30

40

50

トが、適切なときに、H C A L L (ハイパーバイザ呼び出し) によって固定を引き起こす。

#### 【0226】

構成状態レジスタのメモリ補助ページをメモリ内で固定することによって、構成状態レジスタがアクセスされるときに、ページ・フォールトが回避される。このページ・フォールトは、ソフトウェアによって予期されないことがあり、例えば、ソフトウェアが、どの命令がトラップを引き起こしたかをチェックし、トラップを引き起こした命令が、データ・ページ・フォールトを引き起こしたメモリにアクセスするように定義されていない命令だったことを検出したなどの場合に、一部のソフトウェアにおいて p a n i c ( ) を引き起こすことがある。p a n i c ( ) は、予期されないイベントが発生したときにオペレーティング・システムにおいて実行される呼び出しであり、通常はシステム・クラッシュをもたらす。

10

#### 【0227】

固定は、例えば、循環する例外を回避するため（例えば、例外に関連する構成状態レジスタに使用されるページが使用可能でない場合、そのページに関するページ・フォールト例外が引き起こされる必要がある、など）、および（例えば、構成状態レジスタの処理を伴う例外およびその他の外部イベントに対する）高速な応答を保証するためにも、使用される。

20

#### 【0228】

1つの実施形態では、固定はソフトウェアにおいて実行される。例えば、下で説明されているように、固定は、準仮想化された環境内のソフトウェアのコンテキスト切り替えと運動して、ハイパーバイザ呼び出し (H C A L L) を使用して実行されてよい。

20

#### 【0229】

1つの実施形態では、コンテキスト（例えば、スレッドのコンテキスト、またはプロセスのコンテキスト、または論理パーティションのコンテキスト、または仮想マシンのコンテキスト、またはオペレーティング・システムのコンテキストなど）が、スーパーバイザ・ソフトウェアによって初期化されるときに、スーパーバイザが、初期化されているコンテキストに対応する1つまたは複数の構成状態レジスタの格納を提供するために、メモリを割り当てる。

30

#### 【0230】

1つの例では、この割り当ては、適切なアライメントおよびサイズのメモリを提供する割り当てルーチンを呼び出すことによって実行されてよい。少なくとも1つの実施形態に従って、返されたアドレスが、コンテキストに対応する情報を格納するメモリ領域に格納される。1つの実施形態では、このメモリ領域は「u領域」と呼ばれ、変数「u」によって示される。少なくとも1つの実施形態では、変数 u は、コンテキストに関して記録されるさまざまな属性に対応する複数のメンバーを含む、レコード、構造体、クラス、または他の複合データ・タイプである。少なくとも1つの実施形態では、この構造体は、少なくとも1つのC S R 補助メモリ・ページのアドレスに対応するメンバー（フィールド）を含む。少なくとも1つの例では、このメンバーに、「c s r \_ p a g e」という名前が付けられる。

40

#### 【0231】

```

my_csr_page_pointer = 補助ページの割り当て

```

#### 【0232】

```

u.csr_page = my_csr_page_pointer

```

#### 【0233】

準仮想化された環境内で、例えばハイパーバイザに対するH C A L L を使用して、C S R 補助メモリの固定を実行するときに、コンテキスト切り替えのコンテキスト・シーケンス（例えば、図28および図29のうちの1つに従うシーケンス）が、固定H C A L L および固定解除H C A L L を含めて拡張される。本発明のこの態様でのコンテキスト切り替えの1つの実施形態に従って、以下のステップが実行される。

50

**【 0 2 3 4 】**

( 1 ) 既知の手法に従って、汎用レジスタ、浮動小数点レジスタ、ベクトル・レジスタなどを含むが、これらに限定されない、以前のコンテキストの非 C S R の状態を保存する。

**【 0 2 3 5 】**

( 2 ) ( 例えは、図 2 8 および図 2 9 のうちの 1 つの手法に基づいて ) プロセッサ内構成状態レジスタを保存する。

**【 0 2 3 6 】**

( 3 ) 受信 C S R 補助メモリ・ページ ( すなわち、次のコンテキストに切り替える ( 有効化する ) ことの一部として、構成状態レジスタのメモリ・ページとして有効化されているページ ) を固定する : H C A L L ( P I N , n e x t \_ u - > c s r \_ p a g e ) 。 n e x t \_ u は、次のコンテキストとして切り替えられて ( 有効化されて ) いるコンテキストの u 領域を指し示すポインタである。 10

**【 0 2 3 7 】**

( 4 ) 任意選択的に、少なくとも 1 つの実施形態では、送信構成状態レジスタを同期する : s y n c \_ o \_ c s r 。

**【 0 2 3 8 】**

( 5 ) 有効化されているコンテキストに対応する C S R 補助メモリのベース・アドレスを含むベース・レジスタを読み込む ( 1 つの例では、この C S R は T C B R に対応する ) : m t s p r T C B R , n e x t \_ u - > c s r \_ p a g e 。 20

**【 0 2 3 9 】**

( 6 ) 任意選択的に、少なくとも 1 つの実施形態では、受信構成状態レジスタを同期する : s y n c \_ i \_ c s r 。

**【 0 2 4 0 】**

( 7 ) 送信 C S R 補助メモリ・ページ ( すなわち、以前のコンテキストを切り替える ( 無効化する ) ことの一部として、 C S R 補助メモリ・ページとして無効化されているページ ) を固定解除する : H C A L L ( U N P I N , p r e v \_ u - > c s r \_ p a g e ) 。 p r e v \_ u は、以前のコンテキストとして切り替えられて ( 無効化されて ) いるコンテキストの u 領域を指し示すポインタである。 30

**【 0 2 4 1 】**

( 8 ) 既知の手法に従って、汎用レジスタ、浮動小数点レジスタ、ベクトル・レジスタなどを含むが、これらに限定されない、次のコンテキストの他の非 C S R の状態を読み込む。

**【 0 2 4 2 】**

( 9 ) 制御を新たに有効化されたコンテキストに移す。例えは、( P o w e r I S A と連動する実装では ) r f i d 命令を使用して、オペレーティング・システムからアプリケーションのスレッドまたはプロセスのコンテキストに移す。

**【 0 2 4 3 】**

当業者は、本明細書における上記のステップの順序が変更されてよいということを、理解するであろう。例えは、少なくとも 1 つの実施形態では、固定動作の前に、固定解除動作が実行されてよい。その他の変形が可能である。 40

**【 0 2 4 4 】**

別の実施形態では、 T C B R などのベース・レジスタを読み込むことに応答して、固定が実行される。通知イベント ( 例えは、割り込み ) が、スーパーバイザに引き起こされてよい。複数のスーパーバイザ・レベルが存在する場合、1 つの実施形態では、通知イベントが各スーパーバイザ・レベルに引き起こされる。通知イベントを受信することに応答して、固定情報が更新される。

**【 0 2 4 5 】**

別の実施形態では、値をベース・レジスタに書き込むことによって、固定されたページを示すページ・テーブル・エントリ指示フラグが対応する P T E 内で設定される。ページ 50

・テーブル・エントリの複数のレベルが存在する場合、ページ・テーブル・エントリ指示フラグがレベルごとに設定されてよい。

#### 【0246】

少なくとも別の実施形態では、固定プロセスまたは固定解除プロセスを開始する固定命令および固定解除命令のうちの少なくとも1つが提供される。

#### 【0247】

さらに別の実施形態では、どのページが「固定されている」かを決定するために、システム内で有効なベース・レジスタを調べることによって、ホスト・ソフトウェアによって固定が決定されてよく、すなわち、ベース・レジスタ（例えば、TCBR）の複数の内容が、固定されたページの記録を表す。少なくとも1つの実施形態では、ページを移動またはページ・アウトする前に、スーパーバイザ・レベルのソフトウェアが、ページ・アドレスがベース・レジスタのうちの少なくとも1つに含まれるアドレスに対応するかどうかを判定することによって、ページが固定されたページに対応するかどうかを判定する。

10

#### 【0248】

さらに別の実施形態では、ホストが、例えば1つの実施形態例では例外として、固定の通知イベントを受信してよい。通知を受信することに基づいて、ホスト・システムが、固定されるアドレスを受信し、将来メモリを管理するときに参照するために、そのアドレスを格納する。1つの実施形態では、通知は、固定解除されている以前のアドレスに関する情報（例えば、ベース構成状態レジスタに格納されている以前の値、または例えば構成状態レジスタを使用してその他の方法で提供される別の値）も含む。

20

#### 【0249】

固定通知をホストに提供する1つの例に関する詳細が、図35を参照してさらに説明される。この論理は、プロセッサによって実行される。図35を参照すると、メモリ内構成状態レジスタを含んでいるメモリ・ページ（またはその他のメモリのユニット）に関して、新しい構成値（例えば、ゲスト・アドレス）が受信される（ステップ2400）。1つの例では、この新しい構成値がベース・レジスタ（例えば、TCBRなど）に格納される。しかし、他の実施形態では、この値が別の方法で提供されてよい。

20

#### 【0250】

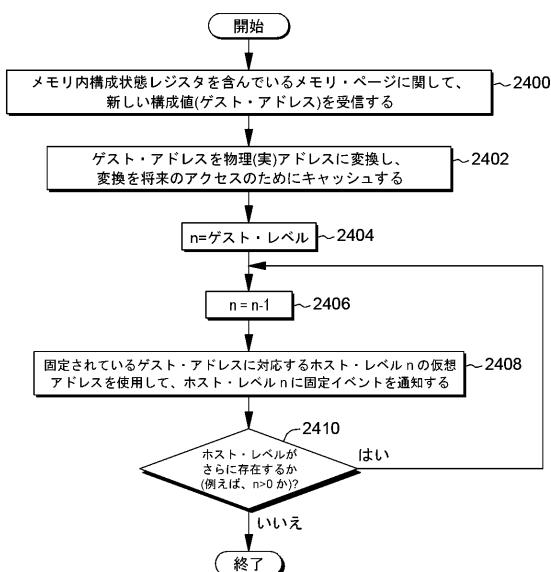

メモリ・ページのゲスト・アドレス（例えば、ゲスト仮想アドレスまたはゲスト実アドレス）が変換される（ステップ2402）。1つの例では、ゲスト・アドレスが物理的実アドレスに変換され、この変換が将来のアクセスのためにキャッシュされる。変数nが、ゲスト・レベルと同じに設定される（ステップ2404）。次にnが、選択された値（例えば、1）によってデクリメントされる（ステップ2406）。固定されているゲスト・アドレスに対応するホスト・レベルnの仮想アドレスを使用して、ホスト・レベルnに固定イベントが通知される（ステップ2408）。さらに、ホスト・レベルがさらに存在するか（例えば、nが0より大きいか）どうかに関する判定が行われる（照会2410）。ホスト・レベルがさらに存在する場合は、処理がステップ2406を続行する。ホスト・レベルがそれ以上存在しない場合は、処理が完了する。

30

#### 【0251】

1つの実施形態では、アドレスに対応するページ・テーブル・エントリ内の、ビットなどのインジケータによって、固定が示される。このビットは、ページが固定されており、ゲストによって使用中であるということを示す。この固定インジケータの1つの例が、図33に示されている。

40

#### 【0252】

固定に関連する詳細が、図36に示されている例示的な変換動作および固定動作を参照して、さらに説明される。1つの例では、プロセッサがこの処理を実行する。最初に、メモリ内構成状態レジスタを含んでいるメモリ・ページに関して、新しい構成値（例えば、ゲスト・アドレス）が受信される（ステップ2500）。ゲスト・アドレスが物理アドレスに変換され、この変換が将来のアクセスのためにキャッシュされる（ステップ2502）。変数nが、ゲスト・レベルと同じに設定され、ADDRESSがゲスト仮想アドレス

50

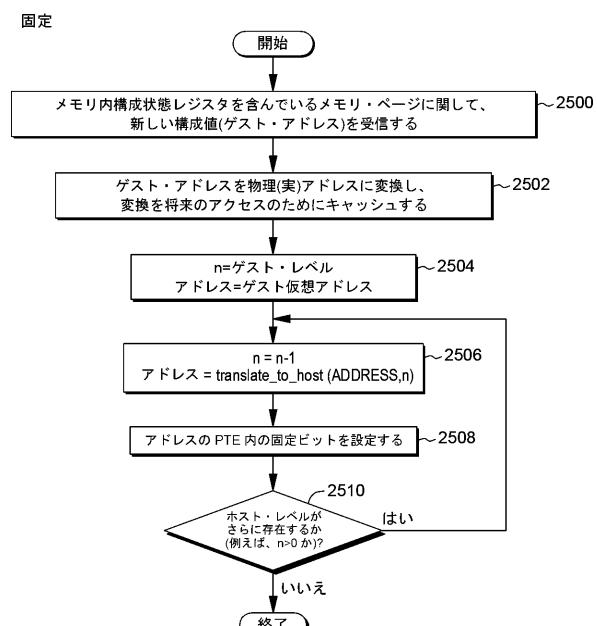

と同じに設定される(ステップ2504)。その後、nが定義された値(1など)だけデクリメントされ、ADDRESSESがtranslate\_to\_host(ADDRESSES, n)と同じに設定される(ステップ2506)。すなわち、ADDRESSESが、ホスト・レベル用の変換されたホスト・アドレスに設定される。アドレスのページ・テーブル・エントリ内で、固定インジケータ(例えば、ビット)が設定される(例えば、1に設定される)(ステップ2508)。さらに、ホスト・レベルがさらに存在するか(すなわち、nが0より大きいか)どうかに関する判定が行われる(照会2510)。ホスト・レベルがさらに存在する場合は、処理がステップ2506を続行する。ホスト・レベルがそれ以上存在しない場合は、処理が終了する。この時点で、ADDRESSESは、固定されたページの物理アドレスに対応し、アドレス変換との相乗効果に使用され得る。

10

#### 【0253】

変換およびキャッシングに基づいて、1つの例ではすべてのホスト・レベルで、インジケータ(例えば、ビット)が設定される。1つの実施形態では、ページ・テーブル・ウォーキングおよび固定指示が結合される。これによって、変換が、固定指示に使用されるのと同じページ・テーブル・エントリにアクセスするために、性能が向上する。

#### 【0254】

1つの実施形態では、別の値(例えば、構成状態レジスタに格納されている以前の値(アドレス)、または例えば構成レジスタを使用してその他の方法で提供される別の値)に対して、固定解除が実行される。

20

#### 【0255】

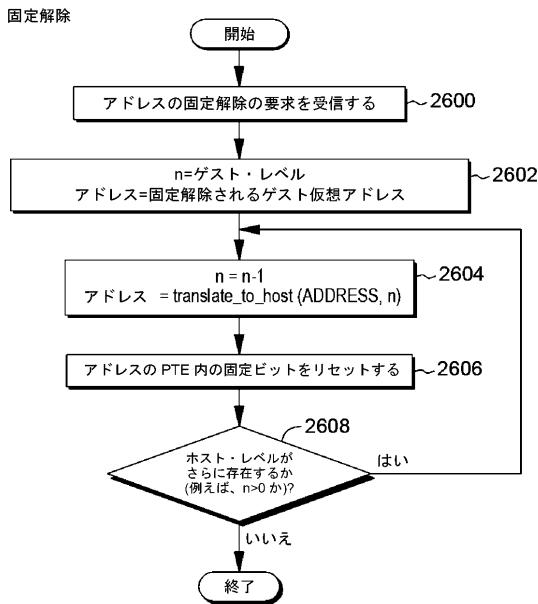

変換動作および固定解除動作に関連する処理の一例が、図37を参照して説明される。1つの例では、プロセッサがこの処理を実行する。最初に、アドレスの固定解除の要求が受信される(ステップ2600)。この要求は、固定解除されるゲスト仮想アドレスを含む。さらに、nが、ゲスト・レベルと同じに設定され、ADDRESSESが、固定解除されるゲスト仮想アドレスと同じに設定される(ステップ2602)。次に、nが定義された値(1など)だけデクリメントされ、ADDRESSESがtranslate\_to\_host(ADDRESSES, n)と同じに設定される(ステップ2604)。すなわち、ADDRESSESが、ホスト・レベル用の変換されたホスト・アドレスに設定される。アドレスのページ・テーブル・エントリ内の固定インジケータ(例えば、ビット)が、リセットされる(例えば、0に設定される)(ステップ2606)。その後、ホスト・レベルがさらに存在するか(例えば、nが0より大きいか)どうかに関する判定が行われる(ステップ2608)。ホスト・レベルがさらに存在する場合は、処理がステップ2604を続行する。ホスト・レベルがそれ以上存在しない場合は、処理が終了する。この時点で、ADDRESSESは、固定解除されたページの物理アドレスに対応する。

30

#### 【0256】

本明細書において説明されているように、メモリのユニットが固定されるということの決定に基づいて、通知が、例えば自動的に提供される。この通知は、インジケータを設定すること、割り込みを引き起こすこと、例外を提供することなどによるものであってよい。多くの変形が可能である。

40

#### 【0257】

さらに別の態様では、準仮想化された固定呼び出しを介して、効率的な固定管理が提供される。ページが導入されるたびに、それらのページの固定および固定解除を行う必要がないということが、望ましい。一方、ホストのページ・キャッシングを不必要に断片化しないように、固定されるページの数を制限し、ページ割り当ての自由度を制限することも、望ましい。したがって、ホストによって固定解除されるページをゲストが指定する固定HCALLL(ハイパーバイザ呼び出し)が、導入される。ハイパーバイザは、固定解除されるページが固定解除されたかどうかを示すことができ、それによって、ハイパーバイザが使用可能なリソースを有している場合に、すべてのページに対して固定要求を呼び出す必要がないように、ゲストに柔軟性を与える。

#### 【0258】

50

この呼び出しは、1つの実施形態では、CSRメモリ補助ページへのベース・ポインタまたはベース・アドレス（ベース）を更新することを含む。さらに、1つの実施形態では、ゲストは、ページを固定された状態で維持するかどうかを指定する。

#### 【0259】

別の実施形態では、ハイパーバイザは、ハイパーバイザがリソース不足の状況に陥ったときに、オペレーティング・システムへのコールバックによって、以前にオペレーティング・システムに残されている固定されたページを返すことを要求してよい。1つの実施形態では、オペレーティング・システムは、コールバックへの応答として、固定解除する1つまたは複数のページを指定する。

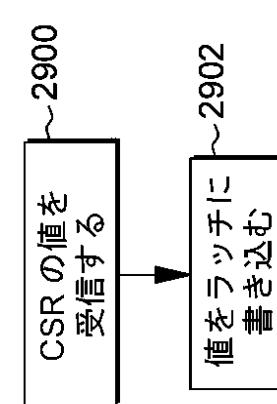

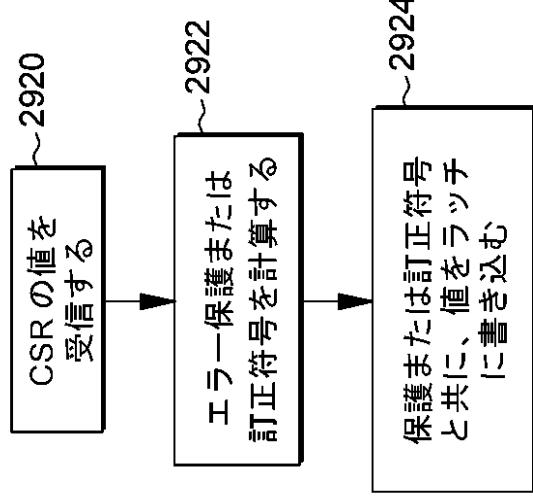

#### 【0260】