(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-4796

(P2008-4796A)

(43) 公開日 平成20年1月10日(2008.1.10)

| (51) Int.CI.          | F 1        |   | テーマコード (参考) |

|-----------------------|------------|---|-------------|

| H01L 21/822 (2006.01) | H01L 27/04 | A | 5 F 038     |

| H01L 27/04 (2006.01)  | H01L 21/82 | D | 5 F 064     |

| H01L 21/82 (2006.01)  |            |   |             |

審査請求 未請求 請求項の数 6 O L (全 10 頁)

|           |                              |            |                                                                                            |

|-----------|------------------------------|------------|--------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2006-173478 (P2006-173478) | (71) 出願人   | 000005821<br>松下電器産業株式会社<br>大阪府門真市大字門真1006番地                                                |

| (22) 出願日  | 平成18年6月23日 (2006. 6. 23)     | (74) 代理人   | 100086737<br>弁理士 岡田 和秀                                                                     |

|           |                              | (72) 発明者   | 小島 友和<br>大阪府門真市大字門真1006番地 パナソニック半導体システムテクノ株式会社内                                            |

|           |                              | (72) 発明者   | 小川 宗彦<br>大阪府門真市大字門真1006番地 パナソニック半導体システムテクノ株式会社内                                            |

|           |                              | F ターム (参考) | 5F038 CA02 CA03 CA06 CA18 DF01<br>EZ20<br>5F064 BB22 CC09 DD05 DD15 DD18<br>DD19 DD24 DD26 |

(54) 【発明の名称】半導体装置および回路素子レイアウト方法

## (57) 【要約】

【課題】トランジスタ対を含むセルを複数備え複数の出力端子を有する半導体装置において、複数出力の均一な特性を得るために相対精度の向上を図ると、装置サイズの増大による半導体装置のコストアップを招く。さらに、素子数が多くなるほど、面積が増大し、大局ばらつきに起因する相対精度のばらつきが拡大する。

【解決手段】トランジスタ対を含むセルを複数備えた半導体装置は、複数のセルが等間隔に並べられてセル群を構成し、隣接セルトランジスタ間距離  $d_2$  が各セルのトランジスタ対におけるトランジスタ間距離  $d_1$  に等しくされている。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

トランジスタ対を含むセルを複数備えた半導体装置であって、前記複数のセルが等間隔に並べられてセル群を構成し、隣接セルトランジスタ間距離が各セルのトランジスタ対におけるトランジスタ間距離に等しくされている半導体装置。

**【請求項 2】**

さらに、前記セル群の両端におけるセルの外側に、各セルのトランジスタから前記トランジスタ間距離を隔てた位置にダミートランジスタが配置されている請求項1に記載の半導体装置。

**【請求項 3】**

さらに、前記セル群の両端におけるセルの外側に、各セルのトランジスタから前記トランジスタ間距離を隔てた位置に前記セルと同一仕様のダミーセルが配置されている請求項1に記載の半導体装置。

**【請求項 4】**

前記トランジスタ対におけるトランジスタのチャンネル長またはチャンネル幅が前記トランジスタ間距離に等しくされている請求項1から請求項3までのいずれかに記載の半導体装置。

**【請求項 5】**

前記セル群の全長を $x$ 、前記セル群を構成するセルの個数を $n$ 、前記セルを構成するトランジスタ対の個数を $m$ 、トランジスタ間距離および隣接セルトランジスタ間距離を $d_1$ 、トランジスタの前記全長 $x$ 方向のサイズを $L$ として、

$$x = 2 \cdot n \cdot m (L + d_1)$$

の関係を満たしている請求項1から請求項4までのいずれかに記載の半導体装置。

**【請求項 6】**

トランジスタ対を含むセルを複数備えた半導体装置における回路素子レイアウト方法であって、

前記セル群の全長を $x$ 、前記セル群を構成するセルの個数を $n$ 、前記セルを構成するトランジスタ対の個数を $m$ 、トランジスタ間距離および隣接セルトランジスタ間距離を $d_1$ 、トランジスタの前記全長 $x$ 方向のサイズを $L$ として、

$$x = 2 \cdot n \cdot m (L + d_1)$$

の関係を満たす条件でセル構成を自動的に行う回路素子レイアウト方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、トランジスタ対を含むセルを複数備え複数の出力端子を有する半導体装置および回路素子レイアウト方法に関する。特には、液晶表示ドライバを好適適用対象とする。

**【背景技術】****【0002】**

従来より、隣接セルどうし間で相対精度が要求される同一仕様の複数のセルを有する半導体装置において、素子のマッチングをとることにより複数端子の出力特性を向上させる技術が知られている（例えば、特許文献1、特許文献2参照）。

**【0003】**

例えば液晶ドライバを構成する半導体装置は、各セルが演算増幅器で構成されている。その複数の演算増幅器どうし間でオフセット電圧やスルーレートを等しくすることにより、画像データの輝度むらや色むらなどを低減し、高い画質を得るようにしている。

**【0004】**

図5に従来の半導体装置A5の構成例を示す。図5において、Qはトランジスタ、S、G、Dはそれぞれトランジスタのソース、ゲート、ドレイン、Q<sub>D</sub>はダミー素子である。エッジングずれやマスクずれに対して、向きを揃えてトランジスタを配置することにより

10

20

30

40

50

、相対精度を確保するようにしている。

#### 【0005】

セル  $C_1 \sim C_n$  は演算増幅器であり、差動増幅回路やカレントミラー回路を備えている。それらを構成するトランジスタは 2 つが対になって（トランジスタ対）、等間隔に並列されている。両トランジスタの相対精度により、その特性が決定される。トランジスタの配置を対称化することに加えて、配線、コンタクトを等しくすることにより（メタルの等長性や等材料性）、トランジスタ対の特性を対称的に等しくなるようにしている。各セルの差動増幅回路やカレントミラー回路は、両端にダミー素子  $Q_D$  を追加することにより、素子の中心を原点とする対称性をもたせている。セル  $C_1 \sim C_n$  の隣接どうし間で特性が互いに等しくなるようにしている。

10

#### 【0006】

一般に、半導体装置の製造上のはらつきは、局所はらつきと大局はらつきからなることが知られている。局所はらつきは、プロセス変動の白色雑音にあたる不規則な成分である。大局はらつきは、製造時の温度勾配などに起因する成分で、ウエハ全体にわたってながらかな変化を示す。

#### 【0007】

トランジスタの局所はらつきに対する対策として、「しきい値電圧のはらつきは、トランジスタサイズの積  $L \cdot W$  の平方の逆数に比例する。」（）という現象に着目し、トランジスタにおけるチャンネル長  $L$  やチャンネル幅  $W$  を決定する。

20

#### 【0008】

大局はらつきに対する対策として、コモンセントロイド型や網目状配置のワッフル型などの点対称のトランジスタ対をレイアウトする方式がある。これによれば、トランジスタ対の相対精度を高め、大局はらつきの影響を極小化できることが知られている（例えば、非特許文献 1 参照）。

#### 【0009】

このような方法を用いて、差動増幅回路やカレントミラー回路の相対精度を向上させ、セル単体の特性を確保している。そして、セルを複数個並べた半導体装置では複数端子の出力特性の均一化を図っている。

【特許文献 1】特開 2006-101108 号公報（第 4 - 5 頁、第 1 - 3 図）

【特許文献 2】特許第 3179424 号（第 3 - 4 頁、第 1 - 8 図）

30

【非特許文献 1】J.Bastors, M.Steyert, B.Graindourze, W.Sansen "Matching of MOS Transistors with Different Layout Styles" IEEE International Conference on Microelectronics Test Structures, Vol.9, pp.17-18, March.1996

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

上記の半導体装置 A5 においては、セル単体の特性向上に注力しているため、各出力端子の電圧を 5V にする場合、プロセスはらつきの影響を受けると、セル  $C_1$  から 5V、セル  $C_2$  から 5.02V、セル  $C_3$  から 4.98V というように、隣接間ではらついてしまう。また、このはらつきは不規則に起こる。これは、レイアウト配置でポリシリコンの密度や距離が異なり、大局はらつきの要因が複雑かつ大きいためである。

40

#### 【0011】

セルの特性に合わせてトランジスタのはらつきなどの各パラメータを調査し、各セルを設計し、セルを配列する。この場合、セルサイズは回路設計の終了段階でないと正確に求めにくい。加えて、面積縮小のためにトランジスタ間距離を調整すると、相対精度の劣化を招く可能性がある。セル  $C_1$  とセル  $C_2$ 、セル  $C_2$  とセル  $C_3$  といった隣接するセルどうし間の相対精度については、プロセスはらつきの影響を避けることがむずかしい。

#### 【0012】

トランジスタ・ダミー素子間距離  $d_1$  や隣接セルのダミー素子間距離  $d_3$  をトランジスタ間距離  $d_1$  に等しくすることが考えられる。しかし、ダミー素子間距離  $d_3$  やダミー

50

素子サイズ  $d_4$  によってはローディング効果の影響が異なり、やはりばらつきが解消されない。ダミー素子間距離  $d_3$  を大きくすれば、大局ばらつきの影響も増大し、その結果、セルの特性がばらつくことになる。

#### 【0013】

ダミー素子間距離  $d_3 = 0$  として隣接セルの 2 つのダミー素子を共通化することも考えられる。しかし、それでもダミー素子の領域分だけはやはり大局ばらつきの影響を受ける。

#### 【0014】

ダミー素子のサイズをトランジスタのサイズと同一にすれば、精度向上が期待できる。しかし、ダミー素子の占有面積が増大し、本来のトランジスタの必要面積の約 2 倍の面積を要することになってしまい。これでは、セル  $C_1$  とセル  $C_n$  との離間距離が 2 倍となり、相対精度ばらつきが拡大してしまう。これは、セル数が多いほど大きな影響となる。また、サイズ増大による半導体装置のコストアップも招来する。

#### 【0015】

本発明は、このような事情に鑑みて創作したものであり、複数のセルで構成される半導体装置において、面積増大化や回路複雑化を招くことなく、複数端子の出力特性の均一化を実現できる半導体装置および回路素子レイアウト方法を提供することを目的としている。

#### 【課題を解決するための手段】

#### 【0016】

本発明による半導体装置は、トランジスタ対を含むセルを複数備えた半導体装置であって、前記複数のセルが等間隔に並べられてセル群を構成し、隣接セルトランジスタ間距離が各セルのトランジスタ対におけるトランジスタ間距離に等しくされていることを特徴するものである。

#### 【0017】

この構成においては、複数のセルを等間隔に並べた上で、隣接セルトランジスタ間距離をトランジスタ間距離に等しくしてあるので、大局ばらつきが一定化され、個々のセルにダミー素子を挿入しなくても複数端子の出力特性の均一化が図られる。

#### 【0018】

上記構成において、さらに、前記セル群の両端におけるセルの外側に、各セルのトランジスタから前記トランジスタ間距離を隔てた位置にダミートランジスタが配置されているという態様がある。

#### 【0019】

また上記の構成において、さらに、前記セル群の両端におけるセルの外側に、各セルのトランジスタから前記トランジスタ間距離を隔てた位置に前記セルと同一仕様のダミーセルが配置されているという態様がある。

#### 【0020】

ダミートランジスタまたはダミーセルを配置してあるので、相対精度のさらなる向上が可能であるとともに、ダミートランジスタまたはダミーセルを配置するのはセル群の両端のみであり、個々のセルにはダミー素子を設けていないので、面積増加は抑制される。

#### 【0021】

さらに上記の構成において、前記トランジスタ対におけるトランジスタのチャンネル長またはチャンネル幅が前記トランジスタ間距離に等しくされているという態様がある。

#### 【0022】

トランジスタのしきい値電圧のばらつきはトランジスタサイズ  $W$ ,  $L$  の積の平方の逆数に比例した値に近似するが、許容されるしきい値電圧のばらつきの範囲でチャンネル長またはチャンネル幅を定め、これに等しくなるようにトランジスタ間距離が設定されている。したがって、特性の向上とセルサイズの最適化とが簡易に達成される。

#### 【0023】

さらに上記の構成において、前記セル群の全長を  $\times$ 、前記セル群を構成するセルの個数

10

20

30

40

50

を  $n$ 、前記セルを構成するトランジスタ対の個数を  $m$ 、トランジスタ間距離および隣接セルトランジスタ間距離を  $d_1$ 、トランジスタの前記全長 × 方向のサイズを  $L$  として、

$$x = 2 \cdot n \cdot m (L + d_1) \dots \dots \dots \quad (1)$$

の関係を満たしているという様態がある。

#### 【0024】

本発明による回路素子レイアウト方法は、トランジスタ対を含むセルを複数備えた半導体装置における回路素子レイアウト方法であって、

前記セル群の全長を  $x$ 、前記セル群を構成するセルの個数を  $n$ 、前記セルを構成するトランジスタ対の個数を  $m$ 、トランジスタ間距離および隣接セルトランジスタ間距離を  $d_1$ 、トランジスタの前記全長 × 方向のサイズを  $L$  として、

$$x = 2 \cdot n \cdot m (L + d_1) \dots \dots \dots \quad (2)$$

の関係を満たす条件でセル構成を自動的に行うものである。

#### 【0025】

上記の条件で構成したセル群は、プロセスばらつきに対して変動が小さく、しかもセル群のサイズも小さい。また、各セルにはダミー素子が必要ないので、相対精度を向上させながら、面積増加が抑制される。

#### 【発明の効果】

#### 【0026】

本発明によれば、複数のセルを等間隔に並べた上で、隣接セルトランジスタ間距離をトランジスタ間距離に等しくしてあるので、大局ばらつきを一定化でき、個々のセルへのダミー素子の挿入なしで面積増大化や回路複雑化を招くことなく、複数端子の出力特性を均一化することができる。

#### 【0027】

特に、液晶ドライバに適用すれば、出力特性の均一性が画質の改善に大きく寄与することになり、特性向上とコストダウンの両立が可能となる。この液晶ドライバを搭載する液晶表示装置は、小面積（狭額）でローコストなものとなる。

#### 【発明を実施するための最良の形態】

#### 【0028】

以下、本発明にかかる半導体装置および回路素子レイアウト方法の実施の形態について図面に基づいて詳細に説明する。

#### 【0029】

##### （実施の形態 1）

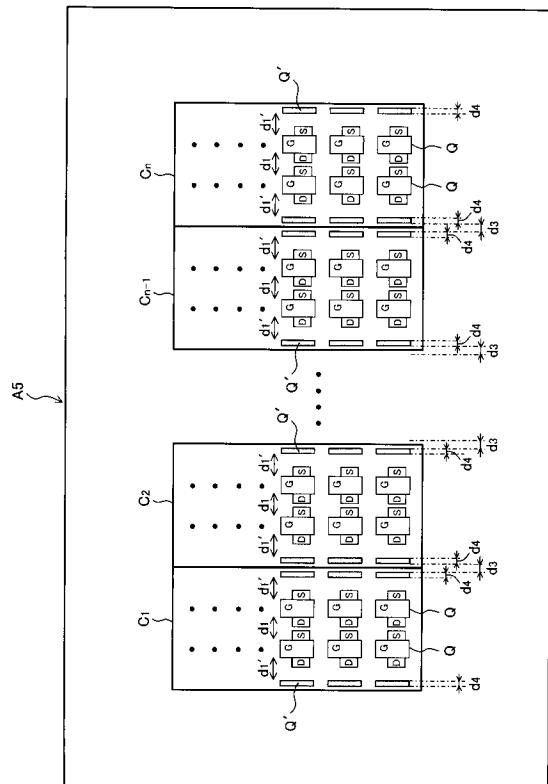

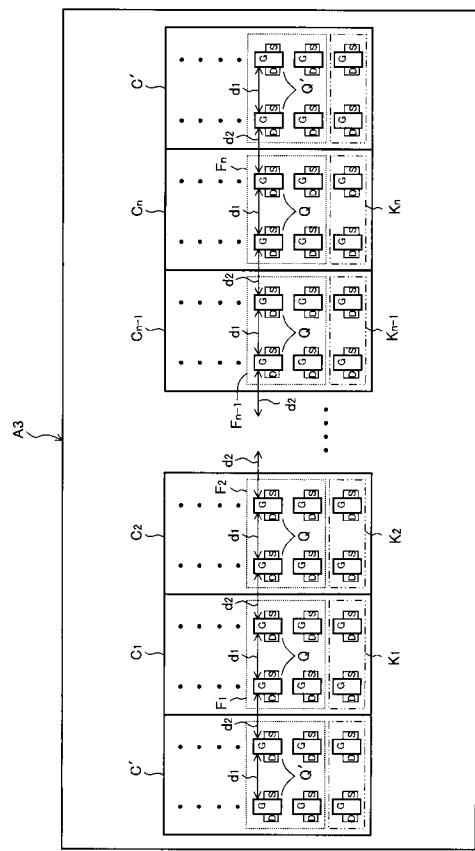

図 1 は本発明の実施の形態 1 における半導体装置 A 1 の概略構成を示す平面図である。

#### 【0030】

図 1において、 $C_1 \sim C_n$  ( $n$  は 2 以上の自然数) は互いに同一仕様のセル、 $F_1 \sim F_n$  はセルを構成する差動增幅回路、 $K_1 \sim K_n$  はセルを構成するカレントミラー回路である。差動增幅回路もカレントミラー回路も 1 対のトランジスタからなるトランジスタ対に構成されている。 $d_1$  はトランジスタ間距離（厳密にはゲート端からゲート端までの距離）である。

#### 【0031】

複数のセル  $C_1 \sim C_n$  が等間隔に並べられてセル群を構成しており、隣接セルトランジスタ間距離  $d_2$  が各セルのトランジスタ対におけるトランジスタ間距離  $d_1$  に等しくされている ( $d_1 = d_2$ )。

#### 【0032】

差動增幅回路、カレントミラー回路以外で同様に相対精度を必要とするトランジスタ対で構成する回路は、同様に配置するものとする。さらに、差動增幅回路およびカレントミラー回路のセルごとに、コモンセントロイド型やワッフル型配置をとっても構わない。

#### 【0033】

また、差動增幅回路、カレントミラー回路以外で相対精度を必要としないトランジスタについては、セルの幅は変えずに、高さ方向でトランジスタ数に応じて伸縮を行えばよい

10

20

30

40

50

。この場合は、トランジスタの等距離性やトランジスタの向き、配置には特に制限はなく、面積を縮小化するように配置すればよい。

#### 【0034】

セル  $C_1 \sim C_n$  のそれぞれに対して入力された信号はそれぞれ差動增幅回路  $F_1 \sim F_n$  およびカレントミラー回路  $K_1 \sim K_n$  で信号処理され、 $n$  個の信号として出力される。このとき、例えば液晶ドライバでは、入力信号のレベルが等しいときは、出力信号のレベルも等しいことが期待される。出力電圧だけでなく、信号の立ち上がり時間、立ち下がり時間、波形の歪み、スルーレート、位相余裕なども等しいことが望ましい。

#### 【0035】

本実施の形態によれば、隣接セルトランジスタ間距離  $d_2$  をトランジスタ間距離  $d_1$  に等しくしている ( $d_1 = d_2$ ) ので、面積増大化や回路複雑化を招くことなく、複数端子の出力特性の均一化を実現することができる。

#### 【0036】

半導体製造装置により複数のMOSトランジスタを同一寸法で製造した場合に、

$$A_{0i} = A_0 + d_0 / dx \cdot x_i + d_0 / dy \cdot y_i \dots \dots \dots \quad (3)$$

$$A_i = A_0 + d_0 / dx \cdot x_i + d_0 / dy \cdot y_i \dots \dots \dots \quad (4)$$

となることが知られている。ここで、チップ上で原点を設定し、その原点でのMOSトランジスタの特性を  $A_0$  (しきい値電圧)、 $A$  (ベータ) とする。また、トランジスタの大局部ばらつきを ( $d_0 / dx, d_0 / dy, d_0 / dx, d_0 / dy$ ) として 1 次元の勾配をもつと仮定する。注目するトランジスタの中心座標を  $x_i, y_i$  とし、その平均特性 ( $A_{0i}, A_i$ ) を上記のモデル式 (3), (4) で与える。A は平均 (Average) を意味する。

#### 【0037】

このような条件下において、隣接セルトランジスタ間距離  $d_2$  をトランジスタ間距離  $d_1$  に等しくすることで大局ばらつきを一定化する。その結果、ダミー素子を挿入している従来例に比べて、大局ばらつきを大幅に抑制することが可能となっている。

#### 【0038】

セル単体での特性向上に注力する図 5 の従来技術の場合、プロセスばらつきの影響を受けると、セル  $C_1$  から 5 V、セル  $C_2$  から 5.02 V、セル  $C_3$  から 4.98 V というよう 30 うに隣接間で不規則にはらついてしまう。

#### 【0039】

これに対して、図 1 に示す本実施の形態の構成では、セル群全体のポリシリコンの分布および密度が等しく、かつ等間隔に配置しているので、大局ばらつきが 1 次近似となる (変化するとしてもリニアに変化する)。すなわち、各出力端子の電圧を 5 V にする場合、セル  $C_1$  から 4.98 V、セル  $C_2$  から 5.0 V、セル  $C_3$  から 5.02 V という具合で、大局ばらつきが一定化し、隣接間のばらつきを大幅に低減することが可能となる。面積増大化や回路複雑化を招くことなく、複数端子の出力特性の均一化を実現することができる。

#### 【0040】

本実施の形態の技術を液晶ドライバへ適用する場合、画質の改善を図ることができる。

#### 【0041】

##### (実施の形態 2)

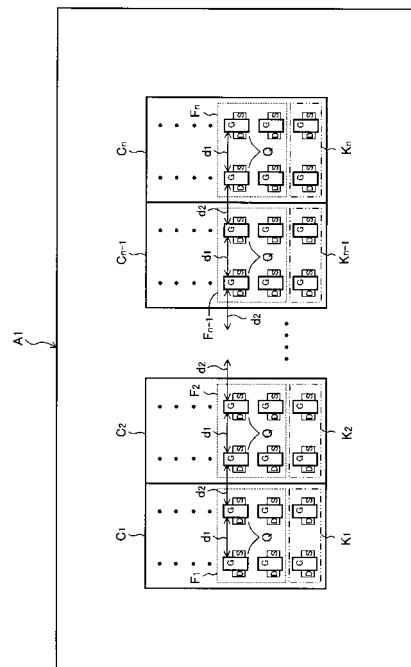

図 2 は本発明の実施の形態 2 における半導体装置 A 2 の概略構成を示す平面図である。図 2 において、実施の形態 1 の図 1 におけるのと同じ符号は同一構成要素を指している。本実施の形態においては、図 1 の構成に加えて、セル群の両端におけるセル  $C_1, C_n$  の外側にそれぞれダミートランジスタ Q を配置している。ダミートランジスタ Q は各セル  $C_1, C_n$  のトランジスタ Q からトランジスタ間距離  $d_1$  を隔てた位置に配置されている。すなわち、ここでも、隣接セルトランジスタ間距離  $d_2$  がトランジスタ間距離  $d_1$  に等しくされている ( $d_1 = d_2$ )。その他の構成については、実施の形態 1 と同様であるので、説明を省略する。

10

20

30

40

50

## 【0042】

本実施の形態によれば、トランジスタの分布密度がセル群の全長にわたって均一になるので、セルの相対精度をさらに向上できる。ダミートランジスタQ<sub>1</sub>を配置するのはセル群の両端のみであり、個々のセルC<sub>1</sub>～C<sub>n</sub>にはダミートランジスタを設けていないので、面積増加は抑制されている。

## 【0043】

## (実施の形態3)

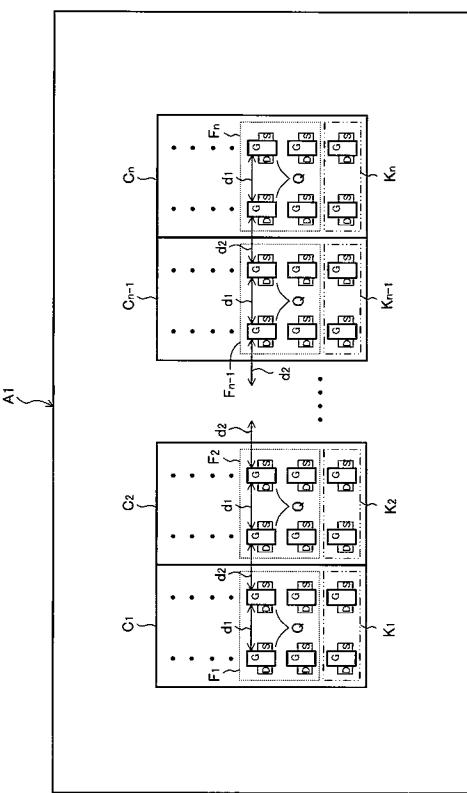

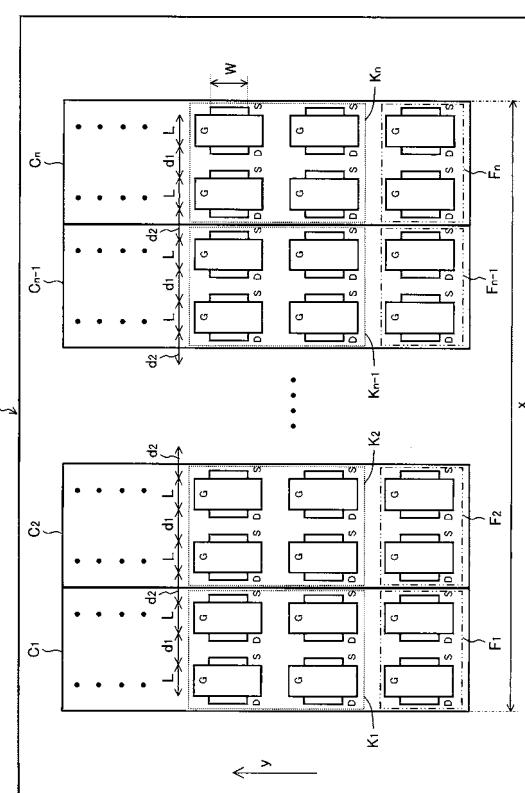

図3は本発明の実施の形態3における半導体装置A<sub>3</sub>の概略構成を示す平面図である。図3において、実施の形態1の図1におけるのと同じ符号は同一構成要素を指している。本実施の形態においては、図1の構成に加えて、セル群の両端におけるセルC<sub>1</sub>、C<sub>n</sub>の外側にそれぞれダミーセルC<sub>0</sub>を配置している。ダミーセルC<sub>0</sub>はサイズ・素子間隔が各セルと同一仕様となっている。ダミーセルC<sub>0</sub>における内側のトランジスタは、各セルC<sub>1</sub>、C<sub>n</sub>のトランジスタQ<sub>1</sub>からトランジスタ間距離d<sub>1</sub>を隔てた位置に配置されている。すなわち、ここでも、隣接セルトランジスタ間距離d<sub>2</sub>がトランジスタ間距離d<sub>1</sub>に等しくされている(d<sub>1</sub>=d<sub>2</sub>)。その他の構成については、実施の形態1と同様であるので、説明を省略する。

## 【0044】

本実施の形態によれば、トランジスタおよびセルの分布密度がセル群の全長にわたって均一になるので、セルの相対精度をさらに向上できる。ダミーセルC<sub>0</sub>を配置するのはセル群の両端のみであり、個々のセルC<sub>1</sub>～C<sub>n</sub>にはダミートランジスタを設けていないので、面積増加は抑制されている。

## 【0045】

## (実施の形態4)

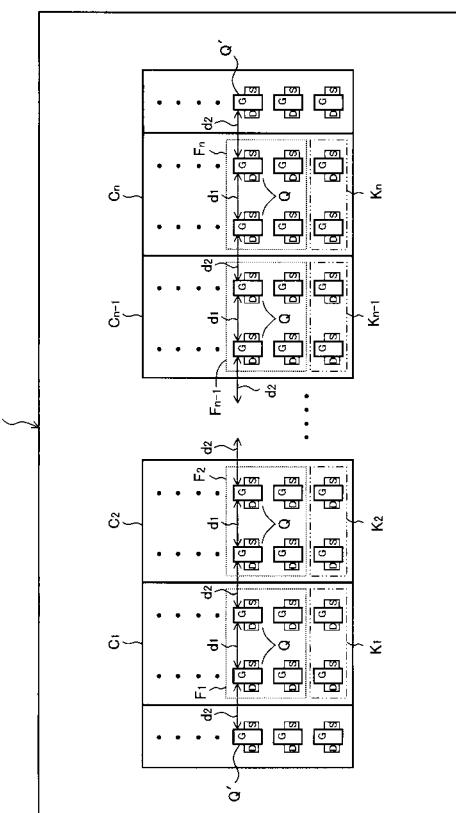

図4は本発明の実施の形態4における半導体装置A<sub>4</sub>の概略構成を示す平面図である。図4において、実施の形態1の図1におけるのと同じ符号は同一構成要素を指している。本実施の形態においては、トランジスタサイズであるチャンネル長Lをトランジスタ間距離d<sub>1</sub>に等しく構成している。

## 【0046】

セル群の全長をx、セル群を構成するセルの個数をn、セルを構成するトランジスタ対の個数をm(図示例ではトランジスタ対は1対であるので、m=1)、トランジスタ間距離および隣接セルトランジスタ間距離をd<sub>1</sub>(=d<sub>2</sub>)、トランジスタの全長×方向のサイズをLとする。

$$x = 2 \cdot n \cdot m (L + d_1) \dots \dots \dots \quad (5)$$

の関係を満たしている。

## 【0047】

以下、半導体装置A<sub>4</sub>の回路素子レイアウト方法について説明する。

## 【0048】

1) しきい値電圧のばらつきのデータから、前述の関係(5)に従って、許容されるトランジスタサイズL、Wを選ぶ(L:チャンネル長、W:チャンネル幅)。

## 【0049】

2) トランジスタ対を同じトランジスタサイズL、Wで構成し、さらに、トランジスタ間距離d<sub>1</sub>をチャンネル長Lと等しくする。

## 【0050】

ここで、トランジスタ間距離d<sub>1</sub>がチャンネル長Lと等しいとは、トランジスタの最小加工精度Lの範囲を含む。

## 【0051】

$$|d_1| \leq L \pm L \dots \dots \dots \quad (6)$$

3) 隣接セルトランジスタ間距離d<sub>2</sub>もチャンネル長Lと等しくする(=トランジスタ間距離d<sub>1</sub>)。

## 【0052】

10

20

30

40

50

図示例は、 $m = 1$  のときに相当し、

$$x = 2 \cdot n (L + d_1)$$

となる。

#### 【0053】

以上の1)~3)の手順に従えば、トランジスタのばらつきのデータからセル群のサイズ $x$ をセルの回路設計完了前に決定することができる。こうようにして構成したセル群は、プロセスばらつきに対して変動が小さく、しかもセル群のサイズも小さい。

#### 【0054】

特性に合わせた各パラメータの調査を伴うことから回路設計の終了段階でないとセルサイズが正確に求めにくい従来技術に比べて、本実施の形態においては、しきい値電圧のばらつきのデータから関係( )に従ってセルに許容されるトランジスタサイズ $L, W$ を選ぶだけであるので、特性向上と面積最小化のための処理の効率が高いものとなる。しかも、各セルにはダミー素子が必要ないので、相対精度を向上させながら、面積増加が抑制される。

#### 【0055】

液晶ドライバにおいて上記の手順を実行してセルの均一性に関する規格を決定すると、回路設計工程、レイアウト設計工程を行わなくとも、セルサイズ、液晶ドライバのサイズを決定できる。回路設計工程、レイアウト設計工程に依存しないため、セルサイズを迅速かつ正確に決定できる。併せて、セル群の均一性と液晶ドライバの面積を小さくできることから、特性向上、コストダウンだけでなく、開発期間を短縮化することができる。また、トランジスタサイズ $L$ または $W$ を決定するだけで、それ以降の工程は、人手を介さずに実施することができる。

#### 【0056】

本実施の形態によれば、面積増大化や回路複雑化を招くことなく、複数端子の出力特性の均一化を実現できる。

#### 【0057】

なお、上記では $x$ 方向に関して説明したが、 $y$ 方向にも適用できることはいうまでもない。さらに、 $x$ 方向、 $y$ 方向の両方向に適用することで、相対精度をさらに向上させることができる。

#### 【0058】

なお、上記ではいずれの実施の形態の場合もMOSトランジスタについて説明したが、バイポーラトランジスタ、抵抗、コンデンサ、コイルを用いて同様の回路を構成できることはいうまでもない。

#### 【0059】

さらに本発明は、上記実施の形態に限定されることなく、発明の主旨の範囲内で自由に変形、変更可能である。

#### 【産業上の利用可能性】

#### 【0060】

本発明の半導体装置によれば、半導体装置の面積増大化および回路複雑化を招くことなく複数端子の出力特性の均一化を実現でき、特に、液晶表示ドライバや有機EL表示ドライバなどの半導体装置に有用である。

#### 【図面の簡単な説明】

#### 【0061】

【図1】本発明の実施の形態1における半導体装置の概略構成を示す平面図

【図2】本発明の実施の形態2における半導体装置(ダミートランジスタ付き)の概略構成を示す平面図

【図3】本発明の実施の形態3における半導体装置(ダミーセル付き)の概略構成を示す平面図

【図4】本発明の実施の形態4における半導体装置の概略構成を示す平面図

#### 【図5】従来技術における半導体装置の概略構成を示す平面図

10

20

30

40

50

## 【符号の説明】

## 【0062】

A1 ~ A5 半導体装置

C1 ~ Cn セル

F1 ~ Fn 差動増幅回路(トランジスタ対)

K1 ~ Kn カレントミラー回路(トランジスタ対)

C ダミーセル

Q ダミートランジスタ

L チャンネル長

W チャンネル幅

d1 トランジスタ間距離

d2 隣接セルトランジスタ間距離

x セル群の長さ

10

【図1】

【図2】

【図3】

【図4】

【図5】