(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-142780

(P2006-142780A)

(43) 公開日 平成18年6月8日(2006.6.8)

(51) Int.C1.

B 41 J 2/05

(2006.01)

F 1

B 41 J 3/04

103 B

テーマコード(参考)

2C057

審査請求 未請求 請求項の数 13 O L (全 15 頁)

(21) 出願番号

特願2004-339443 (P2004-339443)

(22) 出願日

平成16年11月24日 (2004.11.24)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(72) 発明者 櫻井 將貴

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内F ターム(参考) 2C057 AF61 AG46 AG82 AG91 AL13

AN01 AP82 AR20

(54) 【発明の名称】 ヘッド基板、記録ヘッド、ヘッドカートリッジ、及びその記録ヘッド或いはヘッドカートリッジを用いた記録装置

## (57) 【要約】

【課題】 記録素子の抵抗のばらつきと配線抵抗および駆動素子のオン抵抗などからなる寄生抵抗のばらつきとを分離して測定可能なヘッド基板、記録ヘッド、ヘッドカートリッジ、及びその記録ヘッド或いはヘッドカートリッジを用いた記録装置を提供することである。

【解決手段】 複数の記録素子と複数の記録素子を駆動する複数の駆動素子とを備えたヘッド基板に、複数の記録素子にテスト信号を入力する第1の端子と、複数の記録素子の少なくとも一部の記録素子に関し、それらの記録素子を選択駆動する選択信号を入力する第2の端子と、その選択信号により選択された記録素子の両端の電位を出力する第3及び第4の端子とを備えるようにする。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

複数の記録素子と前記複数の記録素子を駆動する複数の駆動素子とを備えたヘッド基板であって、

前記複数の記録素子にテスト信号を入力する第1の端子と、

前記複数の記録素子の少なくとも一部の記録素子に関し、該記録素子を選択駆動する選択信号を入力する第2の端子と、

前記選択信号により選択された記録素子の少なくとも一端の電位を出力する第3の端子とを有することを特徴とするヘッド基板。

**【請求項 2】**

前記選択信号により選択された記録素子に関し、もう一方の端の電位を出力する第4の端子をさらに有することを特徴とする請求項1に記載のヘッド基板。

**【請求項 3】**

前記複数の駆動素子は第1のMOSトランジスタであることを特徴とする請求項1又は2に記載のヘッド基板。

**【請求項 4】**

前記選択信号により記録素子を選択するための第2のMOSトランジスタと、

前記テスト信号により記録素子に通電するための第3のMOSトランジスタとをさらに有することを特徴とする請求項3に記載のヘッド基板。

**【請求項 5】**

前記選択信号は前記第1及び第2のMOSトランジスタのゲートに共通入力され、

前記テスト信号は前記第3のMOSトランジスタのゲートに入力されることを特徴とする請求項4に記載のヘッド基板。

**【請求項 6】**

前記少なくとも一端の電位とは、前記記録素子が前記第1のMOSトランジスタに接続される側の電位であることを特徴とする請求項3乃至5のいずれかに記載のヘッド基板。

**【請求項 7】**

前記もう一方の端の電位とは、前記記録素子が前記第1のMOSトランジスタに接続される側とは反対側の前記複数の記録素子に共通の電源が接続される側の電位であることを特徴とする請求項5に記載のヘッド基板。

**【請求項 8】**

前記複数の記録素子に共通の電源を接続する側と前記第4の端子との間に直列に接続される第4及び第5のMOSトランジスタをさらに有し、

前記第4のMOSトランジスタのゲートには前記選択信号が、前記第5のMOSトランジスタには前記テスト信号が入力されることを特徴とする請求項7に記載のヘッド基板。

**【請求項 9】**

請求項1乃至8のいずれかに記載のヘッド基板を用いた記録ヘッド。

**【請求項 10】**

前記記録ヘッドは、インクを吐出して記録を行うインクジェット記録ヘッドであることを特徴とする請求項9に記載の記録ヘッド。

**【請求項 11】**

前記インクジェット記録ヘッドは、熱エネルギーを利用してインクを吐出するために、インクに与える熱エネルギーを発生するための電気熱変換体を備えていることを特徴とする請求項9に記載の記録ヘッド。

**【請求項 12】**

請求項10又は11に記載のインクジェット記録ヘッドと該インクジェット記録ヘッドにインクを供給するためのインクを貯留するインクタンクとを有することを特徴とするヘッドカートリッジ。

**【請求項 13】**

請求項9乃至11のいずれかに記載の記録ヘッド或いは請求項12に記載のヘッドカート

10

20

30

40

50

リッジを用いて記録を行う記録装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はヘッド基板、記録ヘッド、ヘッドカートリッジ、及びその記録ヘッド或いはヘッドカートリッジを用いた記録装置に関し、特に、例えば、インクを吐出するために必要な熱エネルギーを発生する電気熱変換素子とそれを駆動するための駆動回路を同一の基板上に形成したヘッド基板、そのヘッド基板を用いた記録ヘッド、その記録ヘッドを用いたヘッドカートリッジ、及びその記録ヘッド或いはヘッドカートリッジを用いた記録装置に関する。

10

【背景技術】

【0002】

従来よりワードプロセッサ、パーソナルコンピュータ、ファクシミリ等に用いられるおける情報出力装置として、所望される文字や画像等を記録用紙やフィルム等のシート状の記録媒体に行うプリンタが知られている。

【0003】

プリンタの記録方式としては様々な方式が知られているが中でも、記録媒体に対して非接触で記録が可能であり、カラー記録が容易であり、静肅性に富む等の利点があることからインクジェット方式が特に注目されている。

【0004】

特に、ヒータに数μ秒程度通電することで発生する熱エネルギーにより誘発されるインクの発泡現象をインク液滴の吐出に利用するサーマルインクジェット方式は、高密度に多数のノズルを記録ヘッドに形成することが可能である。

20

【0005】

このようなサーマルインクジェット方式の記録ヘッド（以下、記録ヘッド）では、シリコン単結晶基板などに半導体集積回路プロセスによりインクを加熱するヒータとその保護膜、およびヒータに電流を流すためのドライバ回路とその制御を行う論理回路などを一体で形成した記録素子（以下、ヒータボード）を用いている。

【0006】

図9は従来より一般的に知られているヒータボード内部のヒータとその駆動回路の回路構成を示す図である。

30

【0007】

図9において、101はインクの加熱を行うためのヒータ、102はヒータへの電流印加のスイッチとなるドライバトランジスタ、103～104はヒータ101及びドライバトランジスタ102を記録ヘッド外部との電気的接続を行うためのパッドへと引き出すための配線に寄生する配線抵抗、105～106はそれぞれ外部から電源を印加するためのパッド端子VH（正電位）およびGNDH（基準電位）である。

40

【0008】

図9から明らかなように、ヒータ101とドライバトランジスタ102は1対1の関係になっており、任意のドライバトランジスタを選択駆動することで、対応するヒータへの電流の通電制御が可能となる。ここで、ドライバトランジスタの選択駆動は、ヒータボード内部回路（不図示）から出力される素子選択出力がドライバトランジスタのゲート端子107に加えられることにより行われる。

【0009】

さて、パッドからヒータ、ドライバトランジスタへの電気的接続は、図9にも示されているように、複数の隣接したヒータとドライバトランジスタを一つのまとまりとして、それぞれのまとまりに対して独立した配線で行われている。これは各々のヒータ、ドライバトランジスタとパッド間の距離による抵抗値のズレを、一定の範囲内となるようにするためにあり、かつ各々のまとまりの中で同時に通電するヒータを一つに限定することで、配線抵抗での電圧降下を、各々のまとまりの間で一定なものとするためである。

50

## 【0010】

このようにヒータボード上に多数形成したヒータは、理想的には全てのヒータで均一なばらつきのないパワーを発生できることが望まれるが、実際にはばらつきが存在する。

## 【0011】

このばらつきとしては、ヒータとヒータボード上の電気接点となるパッドとを接続する配線抵抗、およびヒータへの通電制御を行うドライバトランジスタのオン抵抗、及びヒータの抵抗値ばらつきなどにより生じるものである。

## 【0012】

ヒータで発生するパワー（電力）のばらつきは、ヒータの抵抗値ではないばらつき、即ち、配線抵抗やドライバトランジスタのオン抵抗のばらつきに対しては直接的に影響を受ける。即ち、ヒータ以外の抵抗が高くなると、その高くなつた抵抗で電圧および電流が消費されることとなり、ヒータで発生するパワーが減少するのである。

## 【0013】

一方、ヒータ抵抗のばらつきは、パワーのばらつきに対しては圧縮されて影響する。

## 【0014】

即ち、ヒータ抵抗のばらつきにより、個々のヒータ抵抗が設計中心値よりも高いものとなつた場合、そのヒータに印加される電圧は大きくなる一方、流れる電流は小さくなる。しかしながら、発生電力は電圧と電流の積として表現されるので、結果としては電圧と電流の増減が相殺され、ヒータ以外の抵抗がばらついた場合に比較して小さい影響となる。

## 【0015】

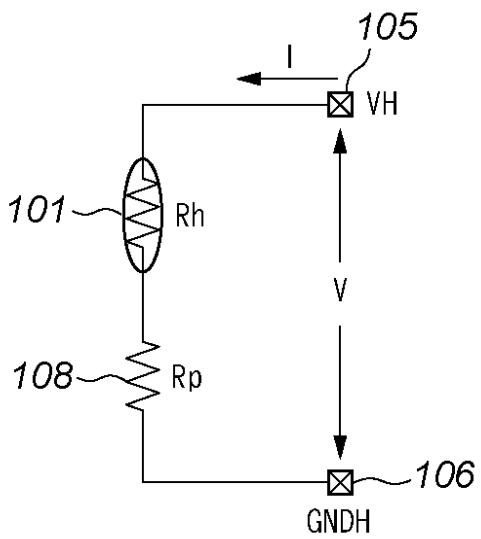

図10は1つのヒータに電流を流す回路構成を模式的に示す図である。

## 【0016】

図10において、 $R_h$ はヒータ101の抵抗、 $R_p$ がヒータ以外の配線抵抗およびトランジスタのオン抵抗などの寄生抵抗108の合計である。これらの抵抗は直列に接続されているものである。

## 【0017】

ここで、設計中心値として、ヒータ抵抗を $R_h = 100$ 、配線およびオン抵抗のなどからなる寄生抵抗を $R_p = 50$ 、端子間の電源電圧（V）を $V = 15V$ と仮定する。

## 【0018】

この条件で、ヒータで発生するパワーは、系としての合計抵抗が $100 + 50 = 150$ 、端子間の電圧が $15V$ であることから電流（I）は、

$$I = V / R = 15V / 150 = 0.1A \text{ であるため、}$$

$$V \times I = R \times I^2 = 100 \times (0.1A)^2 = 1W \text{ となる。}$$

## 【0019】

ここで、寄生抵抗が中心値の50から60にばらついたと仮定すると、ヒータで発生するパワーは、

系としての合計抵抗が $100 + 60 = 160$ 、端子間の電圧が $15V$ であることから、

$$I = V / R = 15V / 160 = 0.0938A \text{ であるため、}$$

発生するパワーは、

$$P = V \times I = R \times I^2 = 100 \times (0.0938A)^2 = 0.880W \text{ となる。}$$

## 【0020】

一方、寄生抵抗は中心値50のままで、ヒータの抵抗値が中心値の100から110にばらついたと仮定すると、系としての合計抵抗は先ほどと同様の $100 + 60 = 160$ 、端子間の電圧が $15V$ であることから、

$$I = V / R = 15V / 160 = 0.0938A \text{ である。}$$

## 【0021】

しかしながら、ヒータで発生するパワーは、

$P = V \times I = R \times I^2 = 110 \times (0.0938A)^2 = 0.968W$ となる。従つて、ヒータ抵抗の高い値へのばらつきは寄生抵抗のばらつきよりもパワーのばらつきに対す

る影響は小さいものとなる。同様に、ヒータ抵抗の低い値へのばらつきも、寄生抵抗のばらつきよりパワーのばらつきに対する影響は小さい。

#### 【0022】

以上説明したように、ヒータボードに形成された記録要素であるヒータ抵抗、及び配線や駆動トランジスタのオン抵抗などの寄生抵抗は、その抵抗値にばらつきがある。

#### 【0023】

そして、これら抵抗値のばらつきは、許容範囲であるかどうかを電気的に測定することによって判断される。従来、このような測定はヒータ抵抗および寄生抵抗の合計抵抗を測定することにより行われている。

#### 【0024】

上記の説明から明らかなように、抵抗値ばらつきの要因がヒータ抵抗であるのか、寄生抵抗であるのかによってヒータで発生するパワーのばらつきは異なったものとなる。

#### 【特許文献1】特開2003-11373号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0025】

さて、記録ヘッドの安定的な動作確認という観点から見ると、本来必要な情報はヒータで発生するパワーのばらつきであるが、従来ではそのばらつき測定をヒータ抵抗と寄生抵抗との合計抵抗を測定していたため、ばらつき要因がヒータ抵抗であるのか、寄生抵抗であるのかの分離が困難であった。上記の検討からも明らかなように、このばらつき要因がヒータ抵抗による場合には、寄生抵抗による場合よりも許容範囲を広くすることが可能である。

#### 【0026】

しかしながら上記従来例では、これらの要因の分離が困難であったので、常に最悪の事態を想定する必要があり、測定により得られたばらつきが全て寄生抵抗からの寄与によるものであった場合においても問題がないようにその規格を規定する必要があった。そのため、本来ヒータで発生するパワーが製品としての規格を満たすものであったとしても、系全体としての合計の抵抗値がその規格を満足しない場合においては、そのヒータボードを不良として判定することとなり、これが歩留まりを低下させる要因となっていた。

#### 【0027】

本発明は上記問題点に鑑みてなされたもので、記録素子の抵抗のばらつきと、配線抵抗および駆動素子のオン抵抗などからなる寄生抵抗のばらつきとを分離して測定可能なヘッド基板、記録ヘッド、ヘッドカートリッジ、及びその記録ヘッド或いはヘッドカートリッジを用いた記録装置を提供することを目的としている。

#### 【課題を解決するための手段】

#### 【0028】

上記目的を達成するために本発明のヘッド基板は、以下のよう構成からなる。

#### 【0029】

即ち、複数の記録素子と前記複数の記録素子を駆動する複数の駆動素子とを備えたヘッド基板であって、前記複数の記録素子にテスト信号を入力する第1の端子と、前記複数の記録素子の少なくとも一部の記録素子に関し、該記録素子を選択駆動する選択信号を入力する第2の端子と、前記選択信号により選択された記録素子の少なくとも一端の電位を出力する第3の端子とを有することを特徴とする。

#### 【0030】

さらに、前記選択信号により選択された記録素子に関し、もう一方の端の電位を出力する第4の端子を備えると良い。

#### 【0031】

ここで、前記複数の駆動素子は第1のMOSトランジスタであり、前記選択信号により記録素子を選択するための第2のMOSトランジスタと、前記テスト信号により記録素子に通電するための第3のMOSトランジスタとをさらに備えることが望ましい。

10

20

30

40

50

## 【0032】

この場合、前記選択信号は第1及び第2のMOSトランジスタのゲートに共通入力され、前記テスト信号は第3のMOSトランジスタのゲートに入力されるように構成することが望ましい。

## 【0033】

また、前記少なくとも一端の電位とは、前記記録素子が第1のMOSトランジスタに接続される側の電位であり、前記もう一方の端の電位とは、前記記録素子が第1のMOSトランジスタに接続される側とは反対側の前記複数の記録素子に共通の電源が接続される側の電位である。

## 【0034】

さらに、前記複数の記録素子に共通の電源を接続する側と前記第4の端子との間に直列に接続される第4及び第5のMOSトランジスタを備え、第4のMOSトランジスタのゲートには前記選択信号が、第5のMOSトランジスタには前記テスト信号が入力されるように構成すると良い。

## 【0035】

また他の発明に従えば、上記構成のヘッド基板を用いた記録ヘッドを備える。

## 【0036】

前記記録ヘッドは、インクを吐出して記録を行うインクジェット記録ヘッドでも良く、そのインクジェット記録ヘッドは、熱エネルギーを利用してインクを吐出するために、インクに与える熱エネルギーを発生するための電気熱変換体を備えていることがより好ましい。

## 【0037】

さらに他の発明に従えば、上記構成のインクジェット記録ヘッドとそのインクジェット記録ヘッドにインクを供給するためのインクを貯留するインクタンクとを有することを特徴とするヘッドカートリッジを備える。

## 【0038】

またさらに他の発明に従えば、上記の構成の記録ヘッド或いはヘッドカートリッジを用いて記録を行う記録装置を備える。

## 【発明の効果】

## 【0039】

従って本発明によれば、記録素子の少なくとも一端の電圧が端子を通してヘッド基板の外部に出力することができるので、記録素子の例えは抵抗成分とそれ以外の寄生抵抗成分を分離して測定することが可能になるという効果がある。

## 【0040】

これにより、従来の抵抗値測定により実施していたばらつきの許容範囲を記録素子に直接起因するパワーばらつきによる許容範囲とすることが可能となるので、そのばらつきの許容範囲を従来よりも広いものとすることが可能となる。そのため従来の測定方法では不良品となっていたヘッド基板を良品と判定することが可能となり、その製造歩留まりの向上を達成することができる。

## 【発明を実施するための最良の形態】

## 【0041】

以下添付図面を参照して本発明の好適な実施例について、さらに具体的かつ詳細に説明する。

## 【0042】

なお、この明細書において、「記録」(「プリント」という場合もある)とは、文字、図形等有意の情報を形成する場合のみならず、有意無意を問わず、また人間が視覚で知覚し得るように顕在化したものであるか否かを問わず、広く記録媒体上に画像、模様、パターン等を形成する、または媒体の加工を行う場合も表すものとする。

## 【0043】

また、「記録媒体」とは、一般的な記録装置で用いられる紙のみならず、広く、布、ブ

10

20

30

40

50

ラスチック・フィルム、金属板、ガラス、セラミックス、木材、皮革等、インクを受容可能なものも表すものとする。

#### 【0044】

さらに、「インク」(「液体」と言う場合もある)とは、上記「記録(プリント)」の定義と同様広く解釈されるべきもので、記録媒体上に付与されることによって、画像、模様、パターン等の形成または記録媒体の加工、或いはインクの処理(例えば記録媒体に付与されるインク中の色剤の凝固または不溶化)に供され得る液体を表すものとする。

#### 【0045】

またさらに、「ノズル」とは、特にことわらない限り吐出口ないしこれに連通する液路およびインク吐出に利用されるエネルギーを発生する素子を総括して言うものとする。

#### 【0046】

なお、説明で用いる「素子基体上」という表現は、単に素子基体の上を指し示すだけでなく、素子基体の表面、表面近傍の素子基体内部側をも示すものである。また、本発明でいう「作りこみ(ビルトイン(built-in))」とは、別体の各素子を単に基体上に配置することを指し示している言葉ではなく、各素子を半導体回路の製造工程などによって素子基体上に一体的に形成、製造することを示すものである。

#### 【0047】

<インクジェット記録装置の説明(図1)>

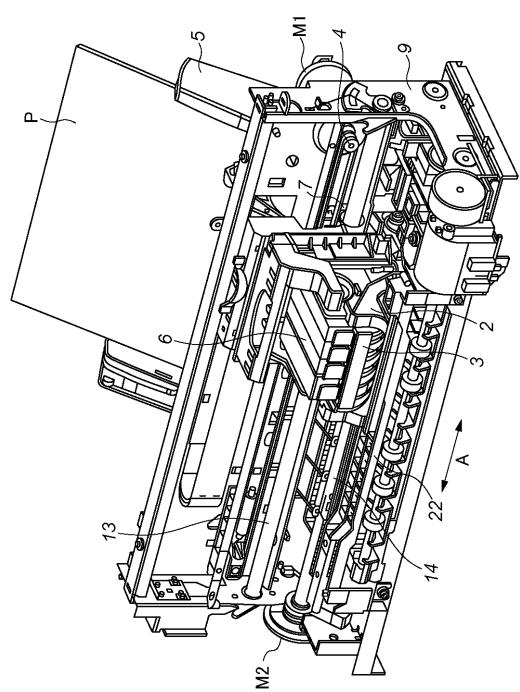

図1は本発明の代表的な実施例であるインクジェット記録装置1の構成の概要を示す外観斜視図である。

#### 【0048】

図1に示すように、インクジェット記録装置(以下、記録装置という)は、インクジェット方式に従ってインクを吐出して記録を行なう記録ヘッド3を搭載したキャリッジ2にキャリッジモータM1によって発生する駆動力を伝達機構4より伝え、キャリッジ2を矢印A方向に往復移動させるとともに、例えば、記録紙などの記録媒体Pを給紙機構5を介して給紙し、記録位置まで搬送し、その記録位置において記録ヘッド3から記録媒体Pにインクを吐出することで記録を行なう。

#### 【0049】

また、記録ヘッド3の状態を良好に維持するためにキャリッジ2を回復装置10の位置まで移動させ、間欠的に記録ヘッド3の吐出回復処理を行う。

#### 【0050】

記録装置1のキャリッジ2には記録ヘッド3を搭載するのみならず、記録ヘッド3に供給するインクを貯留するインクカートリッジ6を装着する。インクカートリッジ6はキャリッジ2に対して着脱自在になっている。

#### 【0051】

図1に示した記録装置1はカラー記録が可能であり、そのためにキャリッジ2にはマゼンタ(M)、シアン(C)、イエロー(Y)、ブラック(K)のインクを夫々、収容した4つのインクカートリッジを搭載している。これら4つのインクカートリッジは夫々独立に着脱可能である。

#### 【0052】

さて、キャリッジ2と記録ヘッド3とは、両部材の接合面が適正に接触されて所要の電気的接続を達成維持できるようになっている。記録ヘッド3は、記録信号に応じてエネルギーを印加することにより、複数の吐出口からインクを選択的に吐出して記録する。特に、この実施形態の記録ヘッド3は、熱エネルギーを利用してインクを吐出するインクジェット方式を採用しており、記録信号に応じて対応する電気熱変換体にパルス電圧を印加することによって対応する吐出口からインクを吐出する。

#### 【0053】

さらに、図1において、14は記録媒体Pを搬送するために搬送モータM2によって駆動される搬送ローラである。

#### 【0054】

10

20

30

40

50

なお、上述した例では、記録ヘッドとインクを貯留するインクカートリッジとは分離可能な構成であるが、以下に説明するように、これら記録ヘッドとインクカートリッジとが一体となったヘッドカートリッジをキャリッジ2に搭載しても良い。

【0055】

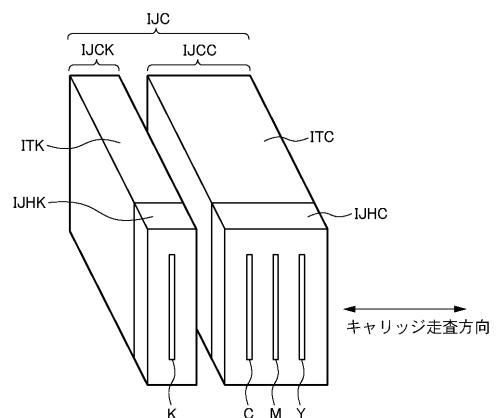

図2はヘッドカートリッジの構成の一例を示す外観斜視図である。

【0056】

図2に示されているように、インクジェットカートリッジIJCはブラックインクを吐出するカートリッジIJKとシアン(C)、マゼンタ(M)、イエロ(Y)の3色のカラーインクを吐出するカートリッジIJCから構成されており、これら2つのカートリッジは互いに對して分離可能であり、夫々独立にキャリッジ2と脱着可能である。

10

【0057】

カートリッジIJKはブラックインクを貯留するインクタンクITKとブラックインクを吐出して記録する記録ヘッドIJKとから成り立っているが、これらは一体型の構成となっている。同様に、カートリッジIJCはシアン(C)、マゼンタ(M)、イエロ(Y)の3色のカラーインクを貯留するインクタンクITCとこれらカラーインクを吐出して記録する記録ヘッドIJCとから成り立っているが、これらは一体型の構成となっている。なお、この実施例ではインクタンク内にインクが充填されているカートリッジとなっている。

【0058】

さらに、図2から明らかなように、ブラックインクを吐出するノズル列、シアンインクを吐出するノズル列、マゼンタインクを吐出するノズル列、イエロインクを吐出するノズル列はキャリッジ移動方向に並んで配置され、ノズルの配列方向はキャリッジ移動方向とは交差する方向となっている。

20

【0059】

<インクジェット記録装置の制御構成(図3)>

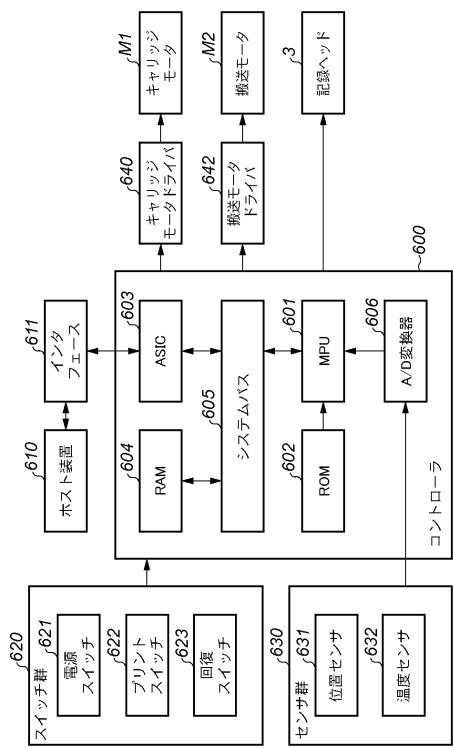

図3は図1に示した記録装置の制御構成を示すブロック図である。

【0060】

図3に示すように、コントローラ600は、MPU601、後述する制御シーケンスに対応したプログラム、所要のテーブル、その他の固定データを格納したROM602、キャリッジモータM1の制御、搬送モータM2の制御、及び、記録ヘッド3の制御のための制御信号を生成する特殊用途集積回路(ASSIC)603、画像データの展開領域やプログラム実行のための作業用領域等を設けたRAM604、MPU601、ASIC603、RAM604を相互に接続してデータの授受を行うシステムバス605、以下に説明するセンサ群からのアナログ信号を入力してA/D変換し、デジタル信号をMPU601に供給するA/D変換器606などで構成される。

30

【0061】

また、図2において、610は画像データの供給源となるコンピュータ(或いは、画像読み取り用のリーダやデジタルカメラなど)でありホスト装置と総称される。ホスト装置610と記録装置1との間ではインターフェース(I/F)611を介して画像データ、コマンド、ステータス信号等を送受信する。

40

【0062】

さらに、620はスイッチ群であり、電源スイッチ621、プリント開始を指令するためのプリントスイッチ622、及び記録ヘッド3のインク吐出性能を良好な状態に維持するための処理(回復処理)の起動を指示するための回復スイッチ623など、操作者による指令入力を受けるためのスイッチから構成される。630はホームポジションhを検出するためのフォトカプラなどの位置センサ631、環境温度を検出するために記録装置の適宜の箇所に設けられた温度センサ632等から構成される装置状態を検出するためのセンサ群である。

【0063】

さらに、640はキャリッジ2を矢印A方向に往復走査させるためのキャリッジモータ

50

M 1 を駆動させるキャリッジモータドライバ、642 は記録媒体 P を搬送するための搬送モータ M 2 を駆動させる搬送モータドライバである。

【0064】

ASIC 603 は、記録ヘッド 3 による記録走査の際に、RAM 602 の記憶領域に直接アクセスしながら記録ヘッドに対して記録素子（ヒータ）の駆動データ（DATA）を転送する。

【0065】

次に、上記構成の記録装置の記録ヘッドに用いられるヘッド基板についてのいくつかの実施例について説明する。特に、ヘッド基板上（ヒータボード上）に作りこまれる駆動回路の構成を中心に説明する。

10

【0066】

なお、基板の上には各記録素子に対応してインク吐出口やこのインク吐出口に連通した流路を形成する部材（不図示）が設けられており、これにより記録ヘッドを構成する。

【0067】

そして、この記録素子上に供給されるインクを記録素子の駆動によって加熱することで膜沸騰による気泡を発生させインクを吐出口から吐出する構成となっている。

【実施例1】

【0068】

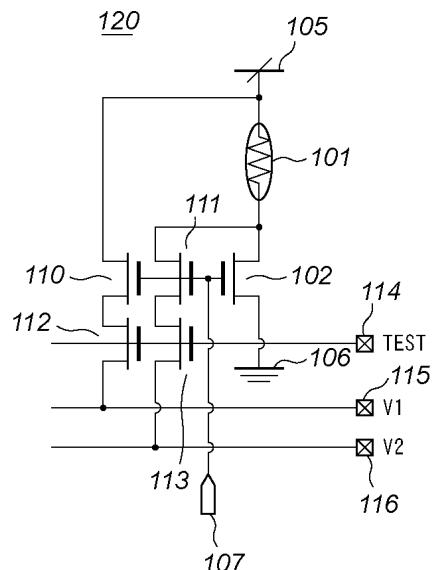

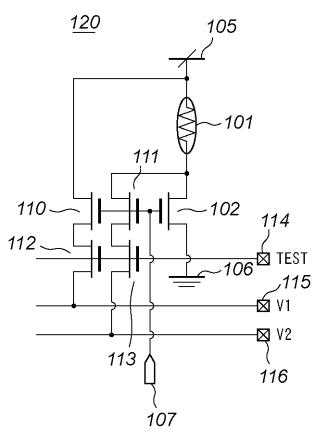

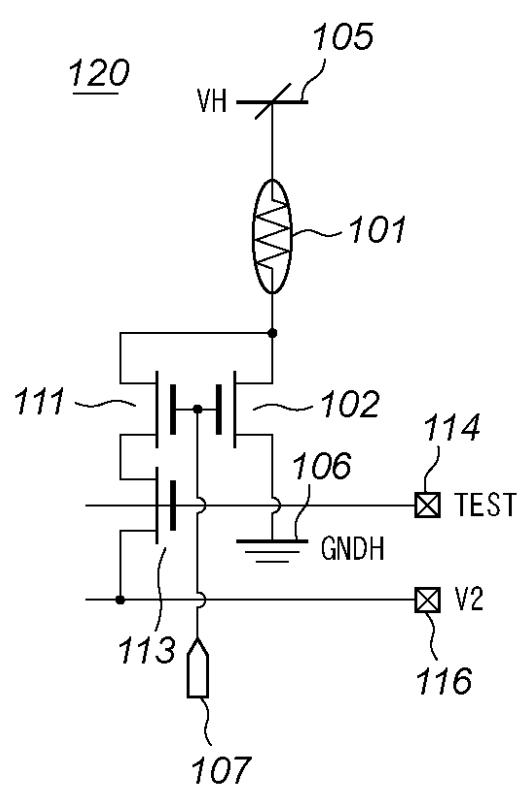

図4は本発明の実施例1に従うヒータ周辺回路の1ビット分の回路120の構成を示す図である。なお、図4において、既に従来例において言及したのと同じ構成要素には同じ参照番号を付し、その説明は省略する。

20

【0069】

図4に示されているように、ヒータ101の両端のノードはMOSトランジスタからなるビットセレクトスイッチ110及び111、MOSトランジスタからなるテストセレクトスイッチ112及び113を介し、モニタ出力端子115及び116へと接続されている。

20

【0070】

なお、この実施例では、ビットセレクトスイッチ110が（+）側でビットセレクトスイッチ111が（-）側になり、テストセレクトスイッチ112が（+）側でテストセレクトスイッチ113が（-）側になっている。また、モニタ出力端子115が（+）側でモニタ出力端子116が（-）側になっている。

30

【0071】

また、図4から分かるように、ビットセレクトスイッチ110と111のゲート端子107は内部回路からの素子選択出力が接続されており、テストセレクトスイッチ112と113のゲートは外部から印加されるテストセレクト端子114を介して論理信号（TEST）が入力される。なお、テストセレクトスイッチ112、113のゲートに印加される信号は、テストセレクト端子114からの信号が直接印加されてもよいし、何らかの論理演算を行った信号が入力されるものでもよい。

【0072】

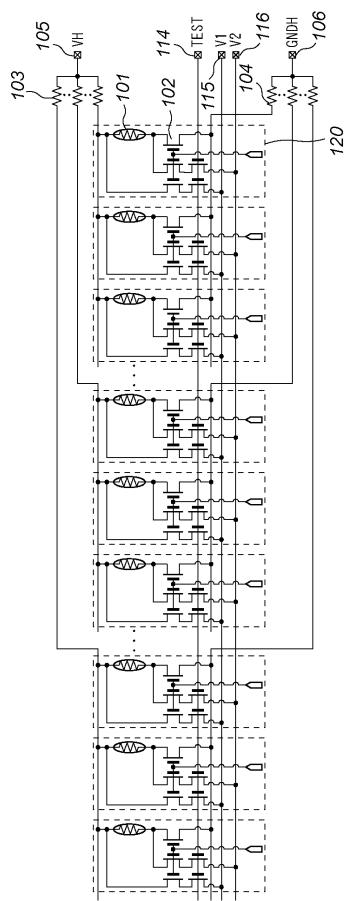

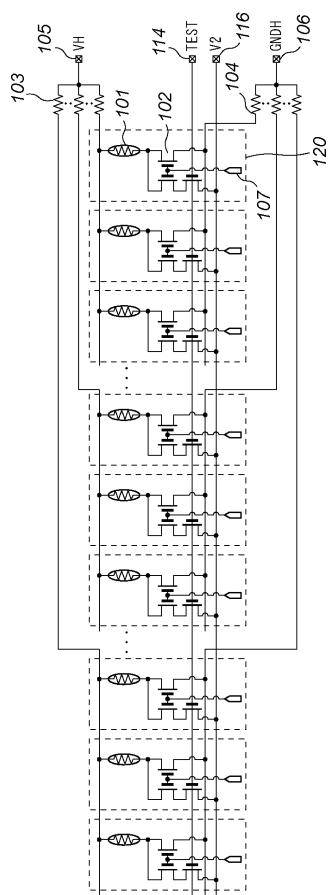

図5は図4に示した1ビット分の回路120が複数並んだヒータ周辺回路の構成を示す図である。なお、図5においても、既に従来例において言及したのと同じ構成要素には同じ参照番号を付し、その説明は省略する。

40

【0073】

図5では、図4で説明した1ビット分の回路120を破線内に示しており、この1ビット回路が複数配置されていることが示されている。

【0074】

図5から分かるように、複数の1ビット回路120各々に含まれるヒータの両端ノードは、図4を参照してビットセレクトスイッチ110～111、テストセレクトスイッチ112～113を介し、モニタ出力端子115および116へと接続されている。

50

【0075】

ピットセレクトスイッチ 110～111 のゲートは、各 1 ピット回路の内部回路からの素子選択出力が接続されている。

【0076】

また、テストセレクト端子 114 は各 1 ピット回路 120 のテストセレクトスイッチ 112～113 のゲートへと共通に入力されている。

【0077】

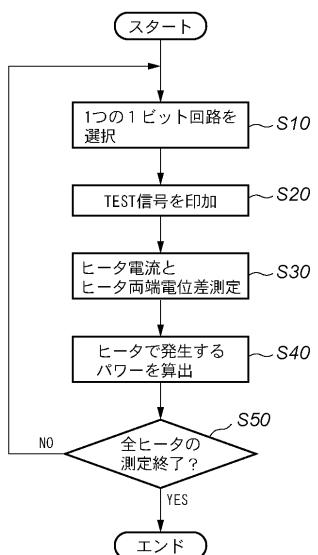

次に、以上のような構成の回路の動作についてフローチャートを参照して説明する。

【0078】

図 6 は実施例 1 に従う抵抗測定手順を示すフローチャートである。

【0079】

まず、ステップ S10 ではヒータにて発生するパワーを測定しようとする任意の 1 つの 1 ピット回路 120 を内部回路からのゲート端子 107 を介した素子選択出力により選択する。

【0080】

さらに、ステップ S20 では、テストセレクト端子 114 にテストセレクトスイッチ 112～113 についてもオンとなる論理信号 (TEST) を印加する。

【0081】

ここで、テストセレクトスイッチは全てのビットでオン状態となっているが、選択した任意の 1 つのビットセレクトスイッチのみがオン状態となっているため、モニタ出力端子 115 と 116 には選択したビットのヒータの両端の電位 (V1, V2) が出力されることとなる。

【0082】

ステップ S30 ではヒータに電流を導通し、その電流値 (I) とヒータ両端の差電圧値 (V1 - V2) を測定する。

【0083】

そして、ステップ S40 では、ステップ S30 で得られた値からヒータで発生するパワーを求める。

【0084】

ステップ S50 では、全ての記録素子 (ヒータ) についての測定が終了したかどうかを調べ、測定未終了であれば、処理はステップ S10 に戻り、素子選択出力を次の 1 ピット回路 120 のゲート端子 107 に入力して測定対象を選択し、前述の処理を繰り返す。これに対し、測定終了と判断されれば処理を終了する。

【0085】

このように測定を、順次各ビットに対して行うことで、従来の配線抵抗やトランジスタのオン抵抗を含めた抵抗ばらつきのみではなく、ヒータで発生するパワーのばらつきを求めることができる。その結果、そのばらつき許容範囲を従来よりも大きくすることにより歩留まり向上を達成できる。

【実施例 2】

【0086】

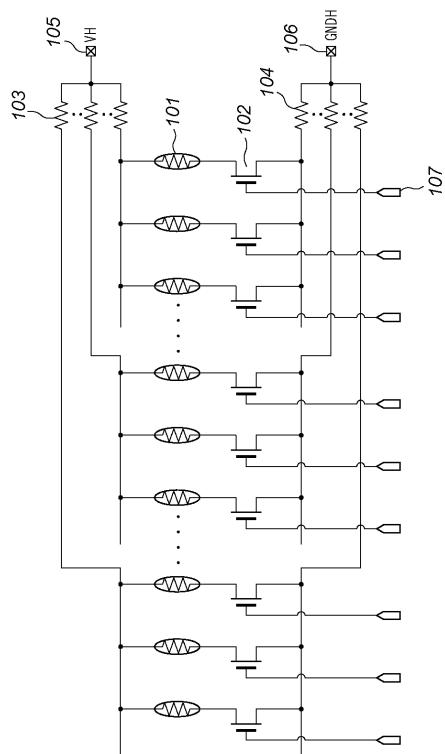

図 7 は本発明の実施例 2 に従うヒータ周辺回路の 1 ピット分の回路 120 の構成を示す図である。なお、図 7 において、既に従来例や実施例 1 において言及したのと同じ構成要素には同じ参照番号を付し、その説明は省略する。

【0087】

この実施例の特徴は、実施例 1 の構成がヒータの両端の電位がモニタ端子へ引き出し可能となっていたのに対し、一方の端子のみを引き出す構成とし簡略化を図った点である。

【0088】

即ち、図 7 に示す構成によれば、ヒータ 101 のドライバトランスタ 102 側のノードはピットセレクトスイッチ 111、テストセレクトスイッチ 113 を介し、モニタ出力端子 116 へと接続されている。ここで、ピットセレクトスイッチ 111 のゲートはゲート端子 107 を介して内部回路からの素子選択出力が接続されており、テストセレクトスイ

10

20

30

40

50

ツチ 113 のゲートは外部から印加されるテストセレクト端子 114 からの論理信号 (TEST) が接続されている。なお、テストセレクトスイッチ 113 のゲートに印加される信号は、テストセレクト端子 114 からの信号が直接印加されてもよいし、何らかの論理演算を行った信号が入力されるものでもよい。この点は実施例 1 と同様である。

#### 【0089】

図 8 は図 7 に示した 1 ビット分の回路 120 が複数並んだヒータ周辺回路の構成を示す図である。なお、図 8 においても、既に従来例や実施例 1 において言及したのと同じ構成要素には同じ参照番号を付し、その説明は省略する。

#### 【0090】

図 8 では、図 7 で説明した 1 ビット分の回路 120 を破線内に示しており、この 1 ビット回路が複数配置されていることが示されている。 10

#### 【0091】

図 8 に示す構成によれば、複数の 1 ビット回路 120 各々に含まれるヒータ 101 のドライバトランジスタ 102 側のノードはビットセレクトスイッチ 111、テストセレクトスイッチ 113 を介し、モニタ出力端子 116 へと接続されている。ビットセレクトスイッチ 111 のゲートにはゲート端子 107 を介して、実施例 1 と同様に素子選択出力が入力されている。テストセレクト端子 114 は各 1 ビット回路 120 のテストセレクトスイッチ 113 のゲートへと共通に入力されている。

#### 【0092】

次に、以上のような構成の回路の動作について説明する。

#### 【0093】

実施例 2 でも実施例 1 と同様にテストセレクトスイッチをオンとし、任意の 1 つのビットセレクトスイッチをオンすることで、ヒータのドライバトランジスタ側のノード電位がモニタ出力端子 116 へと出力される。後の手順は実施例 1 と同様である。 20

#### 【0094】

この実施例は、電源端子 (VH) 105 側に存在する寄生抵抗 103 が、ドライバトランジスタのオン抵抗および電源端子 (GNDH) 106 側に存在する寄生抵抗 104 の合計抵抗及びヒータ 101 の抵抗値に対して十分小さいもので、ヒータ 101 で発生するパワーを測定する上で問題ない場合に適用できる。その場合、ヒータボードのレイアウト面積を抑制することが可能となるという利点がある。 30

#### 【0095】

ここで、ドライバトランジスタ側の電位を引き出す構成としては次のようなことがある。即ち、ドライバトランジスタ 102 のオン抵抗を十分小さくするためにはそのサイズを大きくする必要があり、これにはヒータボード設計上限界があるため、ドライバトランジスタ 102 のオン抵抗は一定の値を有するものとなり、その抵抗値のばらつきがヒータで発生するパワーのばらつき測定に対する影響を無視することは困難な場合が多い。一方、電源端子 (VH) 側の配線抵抗に寄生する抵抗は、その配線の膜厚を増加するなどの手段により抑制することが可能である。

#### 【0096】

その場合、この実施例のようにヒータ 101 とドライバトランジスタ 102 の間のノードの電位が測定できる構成であれば、トランジスタのオン抵抗成分および電源端子 (GNDH) 側の配線抵抗成分を除去した抵抗成分を測定可能となるため、そのばらつき許容範囲は従来に比較して大きくすることが可能となり、歩留まりの向上が図られる。 40

#### 【0097】

また、電源端子 (VH) 配線側の寄生抵抗 603 がヒータ 101 の抵抗およびトランジスタ 102 のオン抵抗などに対して十分小さいものであれば、電源端子 (VH) 105 とモニタ端子 116 の差電圧 (VH - V2)、及びヒータ 101 に流れる電流 (I) から測定されるパワーをほぼヒータで発生するパワーと見なすことが可能となる。このような場合、実施例 2 の構成は、実施例 1 のそれに比べ素子数を減らすことが可能になるので、ヒータボードのレイアウト面積を抑制しつつ、歩留まりの向上が達成できる。 50

## 【0098】

なお、実施例1～2では、図示した全てのビットのヒータ両端の電位が引き出し可能とした構成を示しているが、本発明はこの引き出しを全てのビットに対して行わなければならないものではなく、例えば、複数ビット間隔で間歇的に引き出しを行ってたとしても、その測定から得られるヒータで発生するパワーのばらつきから許容範囲を評価することができるので、その効果は依然として有効である。

## 【0099】

なぜなら、通常、半導体集積回路技術により高密度に配置されたヒータやドライバトランジスタでは隣接した素子間でその特性に急峻な変化があるものではない場合が多く、たとえ、数ビット毎の特性を抜取って測定としたとしても、ヒータボード内でのヒータで発生するパワーのばらつきを一定の確度を持ちつつ把握することが可能であるからである。また、測定のためのスイッチ素子を各ヒータに配置するには、一定のレイアウト面積が必要となるため、この面積を抑制する目的で複数ビット間隔にスイッチ素子を配置し、必要とされる測定確度を維持しつつ、レイアウト面積の増加を抑制することができるという利点もあるからである。

## 【0100】

さらに、以上の実施例において、記録ヘッドから吐出される液滴はインクであるとして説明し、さらにインクタンクに収容される液体はインクであるとして説明したが、その収容物はインクに限定されるものではない。例えば、記録画像の定着性や耐水性を高めたり、その画像品質を高めたりするために記録媒体に対して吐出される処理液のようなものがインクタンクに収容されていても良い。

## 【0101】

以上の実施例は、特にインクジェット記録方式の中でも、インク吐出を行わせるために利用されるエネルギーとして熱エネルギーを発生する手段（例えば電気熱変換体やレーザ光等）を備え、前記熱エネルギーによりインクの状態変化を生起させる方式を用いることにより記録の高密度化、高精細化が達成できる。

## 【0102】

また以上の実施例はシリアルスキャンタイプのインクジェット記録装置を例として説明したが、本発明はこれに限らず、記録可能な記録媒体の最大幅の長さを持つフルライン記録ヘッドを用いたインクジェット記録装置にも、本発明は有効に適用できる。そのような記録ヘッドとしては、複数の記録ヘッドの組合せによってその長さを満たす構成や、一体的に形成された1個の記録ヘッドとしての構成のいずれでもよい。

## 【0103】

加えて、以上の実施例のようなシリアルスキャンタイプのものでも、装置本体に固定された記録ヘッド、あるいは装置本体に装着されることで装置本体との電気的な接続や装置本体からのインクの供給が可能になる交換自在のカートリッジタイプの記録ヘッドを用いた場合にも本発明は有効である。

## 【0104】

さらに加えて、本発明のインクジェット記録装置の形態としては、コンピュータ等の情報処理機器の画像出力装置として用いられるものの他、リーダ等と組合せた複写装置、さらには送受信機能を有するファクシミリ装置の形態を採るもの等であってもよい。

## 【図面の簡単な説明】

## 【0105】

【図1】本発明の代表的な実施例であるインクジェット記録装置の断面図である。

【図2】ヘッドカートリッジの構成の一例を示す外観斜視図である。

【図3】図1に示した記録装置の制御構成を示すブロック図である。

【図4】本発明の実施例1に従うヒータ周辺回路1ビット分の回路構成を示す図である。

【図5】本発明の実施例1に従うヒータ周辺回路の構成を示す図である。

【図6】抵抗測定の手順を示すフローチャートである。

【図7】本発明の実施例2に従うヒータ周辺回路1ビット分の回路構成を示す図である。

10

20

30

40

50

【図8】本発明の実施例2に従うヒータ周辺回路の構成を示す図である。

【図9】従来より一般的に知られているヒータボード内部のヒータとその駆動回路の回路構成を示す図である。

【図10】1つのヒータに電流を流す回路構成を模式的に示す図である。

【符号の説明】

【0106】

101 ヒータ

102 ドライバトランジスタ

103、104 配線抵抗

105、106 電源端子

10

107 内部回路からの素子選択出力

108 寄生抵抗

110、111 ピットセレクトスイッチ

112、113 テストセレクトスイッチ

114 テストセレクト端子

115、116 モニタ出力端子

120 1ピットヒータ周辺回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】