(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6570055号

(P6570055)

(45) 発行日 令和1年9月4日(2019.9.4)

(24) 登録日 令和1年8月16日(2019.8.16)

|                         |                    |

|-------------------------|--------------------|

| (51) Int.Cl.            | F 1                |

| GO 1 R 31/28 (2006.01)  | GO 1 R 31/28 V     |

| GO 1 R 31/02 (2006.01)  | GO 1 R 31/02       |

| HO 1 L 21/66 (2006.01)  | HO 1 L 21/66 F     |

| HO 1 L 23/12 (2006.01)  | HO 1 L 23/12 501 P |

| HO 1 L 21/822 (2006.01) | HO 1 L 27/04 E     |

請求項の数 11 (全 18 頁) 最終頁に続く

|                                                                                                               |                              |                                          |

|---------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------|

| (21) 出願番号                                                                                                     | 特願2015-94219(P2015-94219)    | (73) 特許権者 301021533                      |

| (22) 出願日                                                                                                      | 平成27年5月1日(2015.5.1)          | 国立研究開発法人産業技術総合研究所                        |

| (65) 公開番号                                                                                                     | 特開2016-211917(P2016-211917A) | 東京都千代田区霞が関1-3-1                          |

| (43) 公開日                                                                                                      | 平成28年12月15日(2016.12.15)      | (74) 代理人 100079108                       |

| 審査請求日                                                                                                         | 平成30年4月24日(2018.4.24)        | 弁理士 稲葉 良幸                                |

| (出願人による申告) 平成26年度、独立行政法人新エネルギー・産業技術総合開発機構委託研究「次世代スマートデバイス開発プロジェクト／車載用障害物センシングデバイスの開発」、産業技術力強化法第19条の適用を受ける特許出願 |                              | (74) 代理人 100109346                       |

|                                                                                                               |                              | 弁理士 大貫 敏史                                |

|                                                                                                               |                              | (74) 代理人 100144325                       |

|                                                                                                               |                              | 弁理士 小瀧 高弘                                |

|                                                                                                               |                              | (72) 発明者 荒賀 佑樹                           |

|                                                                                                               |                              | 茨城県つくば市東1-1-1 国立研究開発法人産業技術総合研究所 つくばセンター内 |

最終頁に続く

(54) 【発明の名称】半導体チップ、半導体装置及び半導体検査システム

## (57) 【特許請求の範囲】

## 【請求項1】

基板と、

前記基板を貫通し、前記基板との間に絶縁膜が設けられた1以上のT S V (T h r o u g h S i l i c o n V i a) と、

前記T S Vとの間に絶縁膜が設けられ、前記基板の前記1以上のT S V周辺に配置されるとともに前記基板に設けられた拡散層と電気的に接続されることにより、前記基板の電位を安定させるためのガードリングとして機能するメタル配線と、

前記基板に実装されると共に前記メタル配線に電気的に接続され、前記1以上のT S Vからの雑音信号を前記メタル配線を介して検出するための検出回路とを備える半導体チップ。

## 【請求項2】

前記1以上のT S Vに対して、個別に信号を入力するための入力回路を更に備える請求項1記載の半導体チップ。

## 【請求項3】

前記入力回路は、前記基板に実装される回路をテストするためのバウンダリスキャン回路である、

請求項2記載の半導体チップ。

## 【請求項4】

前記検出回路は、前記T S Vからの雑音信号を電流として外部へ出力可能である、

請求項 1 乃至請求項 3 のいずれか 1 項記載の半導体チップ。

【請求項 5】

請求項 1 乃至請求項 4 のいずれか 1 項記載の半導体チップと、

前記検出回路から出力された信号に基づき、前記 TSV に関する異常を検出するための制御装置と

を備える、半導体検査システム。

【請求項 6】

基板と、

前記基板を貫通し、前記基板との間に絶縁膜が設けられた 1 以上の TSV (Through Silicon Via) と、

10

前記 TSV との間に絶縁膜が設けられ、前記基板の前記 1 以上の TSV 周辺に配置されるとともに前記基板に設けられた拡散層と電気的に接続されることにより、前記基板の電位を安定させるためのガードリングとして機能するメタル配線と、

前記基板に実装されると共に前記ガードリングに電気的に接続され、前記 1 以上の TSV からの雑音信号を前記メタル配線を介して検出するための検出回路と

を備える半導体チップを複数積層して構成される半導体装置。

【請求項 7】

第 1 の層に係る前記半導体チップの前記 TSV の少なくとも一部は、第 2 の層に係る前記半導体チップに電気的に接続され、

前記第 1 の層に係る前記半導体チップに含まれる前記 TSV からの雑音信号を、前記第 2 の層に係る前記半導体チップの前記検出回路で検出可能である、

請求項 6 記載の半導体装置。

20

【請求項 8】

前記半導体チップは、

前記 1 以上の TSV に対して、個別に信号を入力するための入力回路

を更に備える、請求項 6 又は請求項 7 記載の半導体装置。

【請求項 9】

前記入力回路は、前記基板に実装される回路をテストするためのバウンダリスキャン回路である、

請求項 8 記載の半導体装置。

30

【請求項 10】

前記検出回路は、前記 TSV からの雑音信号を電流として外部へ出力可能である、

請求項 6 乃至請求項 9 のいずれか 1 項記載の半導体装置。

【請求項 11】

請求項 6 乃至請求項 10 のいずれか 1 項記載の半導体装置と、

前記検出回路から出力された信号に基づき、前記半導体チップ間の接続に関する異常を検出するための制御装置と

を備える、半導体検査システム。

【発明の詳細な説明】

【技術分野】

40

【0001】

本発明に係るいくつかの態様は、半導体チップ、半導体装置及び半導体検査システムに関する。

【背景技術】

【0002】

半導体装置の分野においては、回路基板に貫通電極を設けた上で、この回路基板を積層する TSV (Through Silicon Via) 技術が知られている（例えば、非特許文献 1, 2）。TSV では、μm 単位の間隔で、各回路基板を接続するための接続用貫通電極 (TSV) を配置することが可能である。TSV を用いた接続は、従来のワイヤボンディングと比較して接続距離を短くすることができるため、接続部分に係る寄生容

50

量、寄生抵抗、及び寄生インダクタンスが小さくなる。これにより、TSVによる接続は回路遅延の軽減や消費電力の低減等を図ることが可能である。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】Jonghyun Cho, Kihyun Yoon, Jun So Pak, Joohee Kim, Junho Lee, Hyungdong Lee, Kunwoo Park and Joungho Kim, "Guard Ring Effect for Through Silicon Via (TSV) Noise Coupling Reduction", CPMT Symposium Japan, 2010 IEEE, 24-26 Aug. 2010

【非特許文献2】Erik Jan Marinissen, "Testing TSV-Based Three-Dimensional Stacked ICs", Design, Automation & Test in Europe Conference & Exhibition (DATE), 2010, 8-12 March 2010

10

【発明の概要】

【発明が解決しようとする課題】

【0004】

TSVの断裂や構造不良があると信号の伝達が行われなくなるため、TSVに関する検査を行う必要がある。TSVにおける検査は、信号を入力及び出力できるように、半導体チップから露出したTSVに対して探針を刺す、又は当てる等の手法により、TSVに物理的にアクセスする必要がある。しかしながら、TSVに探針を刺す等の手法による物理的なTSVへのアクセスは、TSVの破損を招く。また、高い密度で実装された多数のTSVの1つ1つにアクセスするのは極めて困難である。

20

【0005】

つまり、半導体チップにおけるTSVへの物理的なアクセスは困難であるため、TSVに関するテストは、半導体チップを積層した上で、被積層である半導体チップに実装されたテスト回路等を用いて検査する必要があった。しかしながら、積層後における検査では、積層された半導体チップの内1つでも不良があれば、積層されている他の半導体チップを含む半導体装置全体が不良となるため、製造歩留まりが著しく低下するという課題がある。

【0006】

本発明のいくつかの態様は前述の課題に鑑みてなされたものであり、TSVに関する不良を好適に検査することのできる半導体チップ、半導体装置及び半導体検査システムを提供することを目的の1つとする。

30

【課題を解決するための手段】

【0007】

本発明に係る半導体チップは、基板と、前記基板を貫通する1以上のTSV (Through Silicon Via)と、前記基板の前記1以上のTSV周辺に配置され、前記基板の電位を安定させるためのガードリングとして機能するメタル配線と、前記基板に実装されると共に前記メタル配線に電気的に接続され、前記1以上のTSVからの雑音信号を前記メタル配線を介して検出するための検出回路とを備える。

40

【0008】

本発明に係る半導体装置は、基板と、前記基板を貫通する1以上のTSV (Through Silicon Via)と、前記基板の前記1以上のTSV周辺に配置され、前記基板の電位を安定させるためのガードリングとして機能するメタル配線と、前記基板に実装されると共に前記ガードリングに電気的に接続され、前記1以上のTSVからの雑音信号を前記メタル配線を介して検出するための検出回路とを備える半導体チップを複数積層して構成される。

【0009】

なお、本発明において、「部」や「手段」、「装置」、「システム」とは、単に物理的手段を意味するものではなく、その「部」や「手段」、「装置」、「システム」が有する

50

機能をソフトウェアによって実現する場合も含む。また、1つの「部」や「手段」、「装置」、「システム」が有する機能が2つ以上の物理的手段や装置により実現されても、2つ以上の「部」や「手段」、「装置」、「システム」の機能が1つの物理的手段や装置により実現されても良い。

【図面の簡単な説明】

【0010】

【図1】半導体チップの断面図の具体例を示す図である。

【図2】図1に示した半導体チップを積層した半導体装置の断面図の具体例を示す図である。

【図3】本発明の実施形態に係る半導体チップの断面図の具体例を示す図である。 10

【図4】図3に示した半導体チップの回路構成の概要を示す図である。

【図5】図4に示した半導体チップを積層した半導体装置の回路構成の概要を示す図である。

【図6】検出回路の具体例を示す図である。

【図7】図6に示した検出回路の一部の具体例を示す図である。

【図8】図7に示した回路の更に具体的な構成例を示す図である。

【図9】検出回路の具体例を示す図である。

【図10】図3に示した半導体チップ、及び図5に示した半導体装置を検査可能な検査システムの構成例を示す図である。

【図11】本発明の実施形態に係る半導体チップの断面図の具体例を示す図である。 20

【図12】信号波形の具体例を示す図である。

【図13】本発明の実施形態に係る半導体装置の断面図の具体例を示す図である。

【図14】図10に示した検査システムでの信号に係る処理を説明するための図である。

【発明を実施するための形態】

【0011】

以下に本発明の実施形態を説明する。以下の説明及び参照する図面の記載において、同一又は類似の構成には、それぞれ同一又は類似の符号が付されている。

【0012】

### 1. 概要

半導体装置の技術分野では、回路が実装された半導体チップにTSV (Through Silicon Via) と呼ばれる貫通電極を設け、当該TSVにより各層の半導体チップ間で信号を伝達する技術が知られている。 30

【0013】

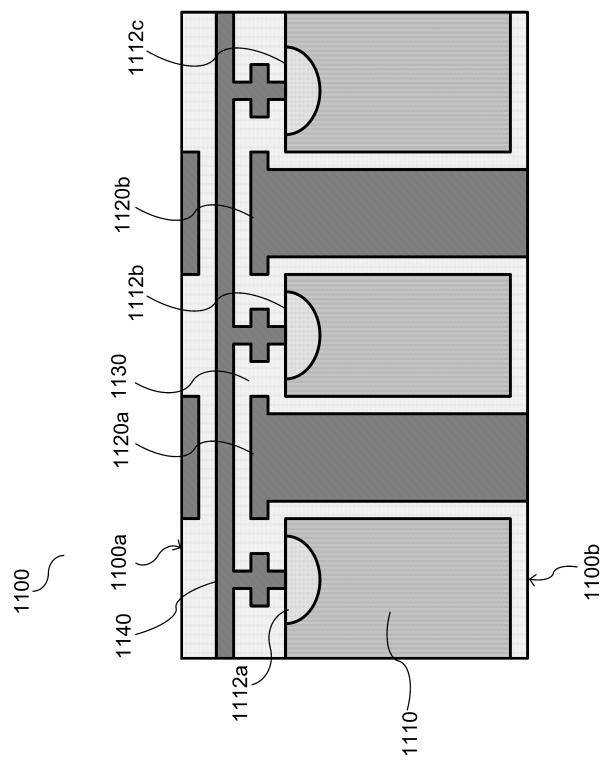

以下、図1を参照しながらTSVを含む半導体チップの構成について説明する。図1は、半導体チップ1100の断面図である。半導体チップ1100は、シリコン基板1110と、TSV1120a及び1120b(以下、総称してTSV1120とも呼ぶ。)と、絶縁膜1130と、とメタル配線1140とを含む。

【0014】

シリコン基板1110は、電気回路が実装される板状の部品である。半導体チップ1100の上面1100a側のシリコン基板1110上には、P+拡散領域1112a、1112b及び1112c(以下、総称してP+拡散領域1112とも呼ぶ。)が形成される。P+拡散領域1112は、シリコン基板1110上に形成されるP型の拡散層であり、メタル配線1140に接続される。これにより、シリコン基板1110に発生した電位をメタル配線1140に伝達することができる。 40

【0015】

メタル配線1140は、TSV1120よりも半導体チップ1100の上面1100a側に、TSV1120を周状に取り囲むように形成され、ガードリングを構成する。メタル配線1140は、シリコン基板1110の各所に形成されるP+拡散領域1112をそれぞれ電気的に接続し、また、メタル配線1140はTSV1120と極めて近い電位に保たれる。これによりメタル配線1140は、TSV1120からの電気的雑音電流を外 50

部へ逃す経路となる。また、メタル配線 1140 は、TSV1120 周辺のシリコン基板 1110 の電位を安定させることができる。

【0016】

半導体チップ 1100 において、TSV1120 は  $\mu\text{m}$  単位の間隔で配置することが可能である。これにより従来のワイヤボンディング等の手法と比較すると、TSV1120 を用いる手法は接続距離を短くすることが可能であるため、接続部分に係る寄生容量、寄生抵抗、寄生インダクタンスを低減することができる。これに伴い、ワイヤボンディング等の手法に比べ、TSV1120 を用いる手法は回路遅延の軽減や低消費電力化を見込むことができる。

【0017】

ここで、図 1 に示した半導体チップ 1100 において、TSV1120 に関する不良があるか否かを検出する場合には、半導体チップ 1100 の下面 1100b 側から TSV1120 にアクセスする必要がある。この方法としては、例えば TSV1120 に探針を刺す、又は当てる等の手法のほか、半導体チップ 1100 を、検査用のテスト回路が実装された他の半導体チップに積層した上で、当該テスト回路を用いて半導体チップ 1100 の TSV1120 を検査する手法が考えられる。

【0018】

図 2 に、図 1 に示した半導体チップ 1100 における TSV1120 を検査可能な半導体装置 1000 の断面図を示す。半導体装置 1000 においては、テスト回路 1220 が実装された半導体チップ 1200 に半導体チップ 1100 が積層されている。なお、図 2 の例では半導体装置 1000 には半導体チップ 1100 及び 1200 の 2 層しか積層されていないが、3 層以上積層してもよい。

【0019】

半導体チップ 1100 には、メタルパッド 1150a 及び 1150b (以下、総称してメタルパッド 1150 とも呼ぶ。) がそれぞれ TSV1120a 及び 1120b の下面 1100b 側に、半導体チップ 1100 から露出するように形成されている。メタルパッド 1150a 及び 1150b は、それぞれマイクロバンプ 1230a 及び 1230b (以下、総称してマイクロバンプ 1230 とも呼ぶ。) を介して半導体チップ 1200 に接続されている。

【0020】

半導体チップ 1200 にはテスト回路 1220 が含まれている。テスト回路 1220 は、マイクロバンプ 1230 及びメタルパッド 1150 を介して TSV1120 に電気的に接続されている。これにより、テスト回路 1220 は TSV1120 に電気的な信号を入力すると共に、TSV1120 から出力された電気的な信号を検出することができる。

【0021】

このような手法では、積層された半導体チップ 1100 及び 1200 を含む多数の半導体チップのうち 1 つでも不良があれば、全ての半導体チップを含む半導体装置 1000 全体として不良となる。すなわち、製造歩留まりが著しく劣化するという課題がある。

【0022】

2. 概略構成

そこで、以下に説明する実施形態では、積層する前に個々の半導体チップの TSV に関する不良の有無を検出した上で、半導体チップの積層後に、半導体チップ間の接続不良の有無を検出する。

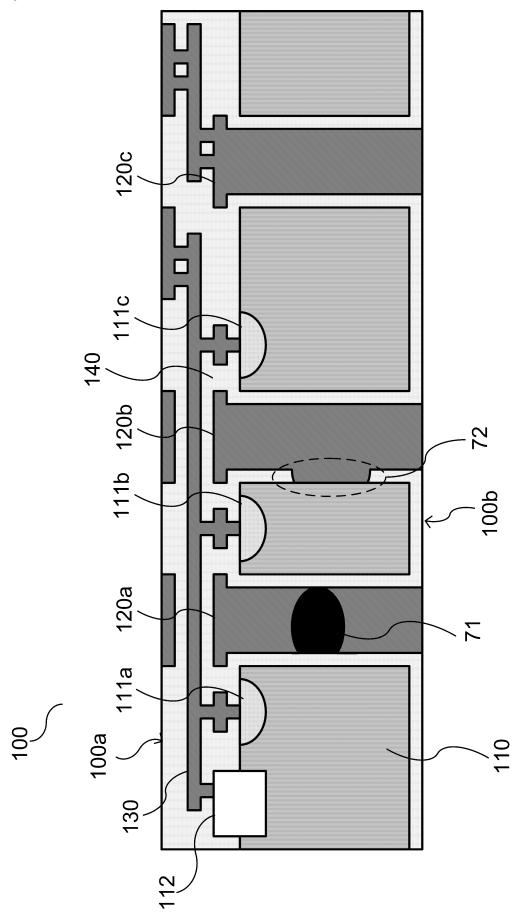

【0023】

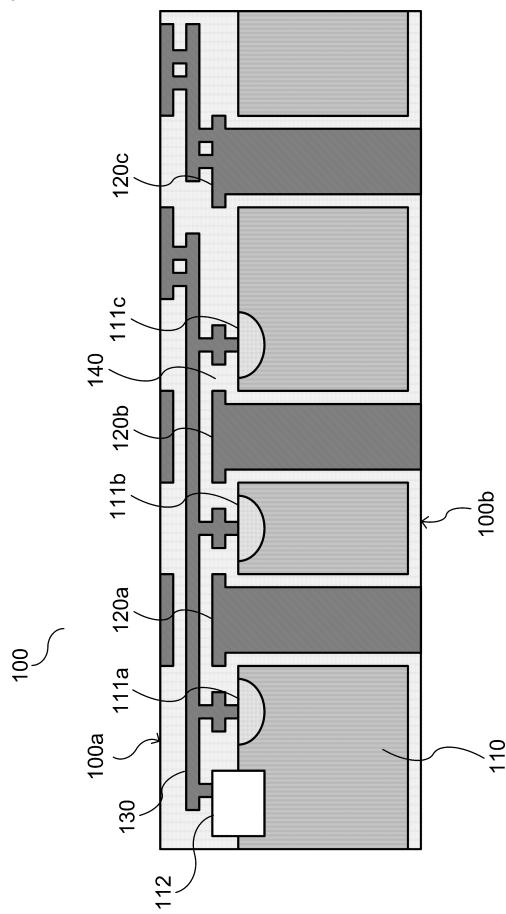

図 3 に、本実施形態に係る半導体チップ 100 の構成を示す。図 3 は、半導体チップ 100 の断面図である。半導体チップ 100 は、シリコン基板 110 と、TSV120a、120b 及び 120c (以下、総称して TSV120 とも呼ぶ。) と、メタル配線 130 と、絶縁膜 140 とを含む。

【0024】

シリコン基板 110 は、電気回路が実装される板状の部品である。また、シリコン基板

10

20

30

40

50

110には、P+拡散領域111a、111b及び111c（以下、総称してP+拡散領域111とも呼ぶ。）及び検出回路112が設けられる。P+拡散領域111は、半導体チップ100の上面100a側のシリコン基板110上に形成されるP型の拡散層である。P+拡散領域111は、後述のメタル配線130にそれぞれ接続される。検出回路112は、当該メタル配線130に電気的に接続されることにより、メタル配線130を介して、シリコン基板110の電位を検出する。検出回路112の具体例等については後述する。

#### 【0025】

TSV120は、シリコン基板110を貫通する電極であり、必要に応じてシリコン基板110上に実装される各種部品と電気的に接続される。図3の例では、TSV120は半導体チップ100の下面100b側に露出しており、他の半導体チップと接続可能になっている。

絶縁膜140は、シリコン基板110とTSV120との間、TSV120とメタル配線130との間等を絶縁する。

#### 【0026】

メタル配線130は、TSV120よりも半導体チップ100の上面100a側に、TSV120を周状に取り囲むように形成され、ガードリングを構成する。メタル配線130は、シリコン基板110の各所に形成されるP+拡散領域111を電気的に接続し、また、TSV120と極めて近い電位に保たれる。これによりメタル配線130は、TSV120からの電気的雑音電流を外部へ逃す経路となる。また、メタル配線130は、TSV周辺のシリコン基板110の電位を安定させることができる。

#### 【0027】

メタル配線130は、検出回路112にも接続される。これにより検出回路112は、P+拡散領域111を介して、シリコン基板110に生じる電位を検出することができる。よって、TSV120に電圧信号を入力した上で、当該信号に応じてシリコン基板110に生じる雑音信号を検出回路112で検出し、当該検出された信号を評価することにより、TSV120に異常が発生しているか否かを検出できる。

#### 【0028】

なおここで、TSV120への信号の入力には、バウンダリスキャン回路を用いることができる。バウンダリスキャンは、シリコン基板110上に配置された各種部品を個別にテストするための手法であるため、個別のTSV120に対して信号を入力するように制御することも可能である。

#### 【0029】

##### 3. 回路構成

###### 3.1. 概略回路構成

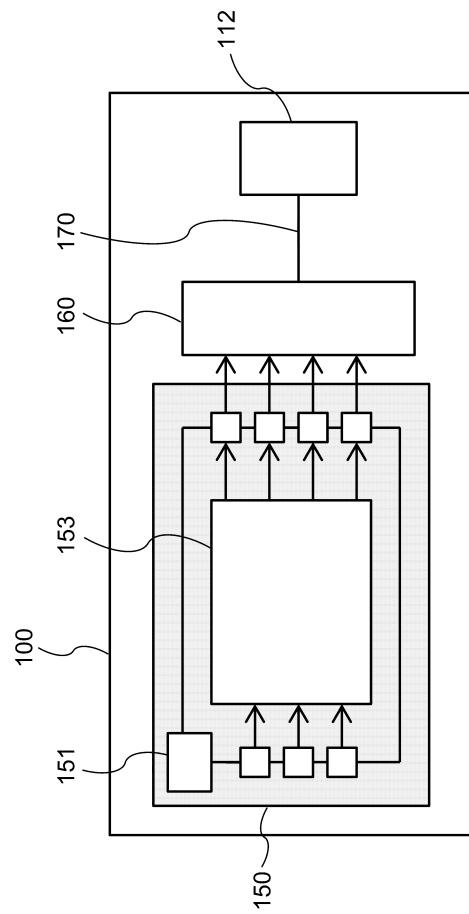

図4に、バウンダリスキャン回路を用いてTSV120へ信号を入力する場合の回路構成の概略を示す。図4に示すように、半導体チップ100に実装される回路には、回路テスト構造150、TSVアレイ160、及び検出回路112を含む。

#### 【0030】

回路テスト構造150は、半導体チップ100に含まれる製品回路153に対するテスト信号を入力するためのバウンダリスキャン制御回路151、及び製品回路153を含む。

#### 【0031】

バウンダリスキャン制御回路151は、バウンダリスキャンにより製品回路153に含まれるLSI等の各種部品や回路接続等の異常を検出するための制御回路である。また本実施形態においては、バウンダリスキャン制御回路151は、製品回路153を介してTSV120に対して個別に信号を入力することもできる。

#### 【0032】

製品回路153は、半導体チップ100に実装される任意の回路であり、バウンダリスキャン制御回路151による被検査対象である。製品回路153は、通常動作時には他の

半導体チップに実装された回路などと共に、特定の機能を提供する。

【0033】

TSVアレイ160は、図3に示した複数のTSV120を含む。回路テスト構造150からの信号は、TSVアレイ160に含まれるTSV120に個別に入力することが可能である。

【0034】

接続170は、TSVアレイ160からの信号を検出回路112へ伝達するための電気的な信号伝達経路である。より具体的には、例えば、TSV120から絶縁膜140を介してシリコン基板110へ電気的雑音が伝達され、当該雑音がメタル配線130を介して検出回路112へ伝達される経路が接続170である。

10

【0035】

つまり、本実施形態では、バウンダリスキャン制御回路151からTSV120に対し信号を入力している。これにより、TSVアレイ160に含まれる個別のTSV120に、他の検査用の半導体チップ等から信号を入力する必要がない。つまり、半導体チップ100の積層前にTSV120の検査を行うことが可能である。

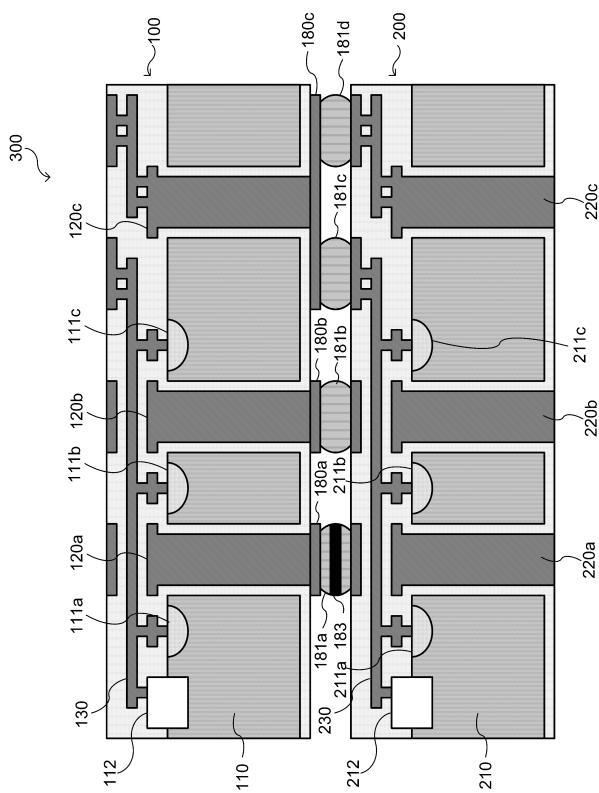

【0036】

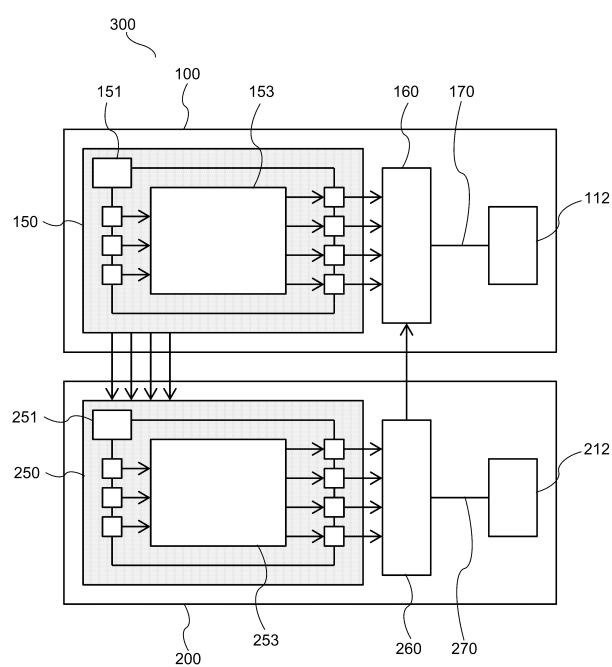

なお、半導体チップ100を積層した場合であっても、バウンダリスキャン制御回路151で半導体チップ100を含む各半導体チップに対して信号を入力することも可能である。図5に、半導体チップ100を積層させた半導体装置300の概略回路構成を示す。

20

【0037】

半導体装置300は、半導体チップ100及び200が積層して構成されている。半導体チップ100の概略構成は図4に示したものと同様であるが、回路テスト構造150は、TSVアレイ160のみならず、半導体チップ200の回路テスト構造250に対しても出力している。

【0038】

半導体チップ200は、半導体チップ100と同様の構成を有する。すなわち、半導体チップ200に実装される回路には、回路テスト構造250、TSVアレイ260、及び検出回路212を含む。回路テスト構造250、TSVアレイ260、及び検出回路212の機能及び構成の概要は、それぞれ半導体チップ100の回路テスト構造150、TSVアレイ160、及び検出回路112と同様であるため、ここでは説明を省略する。しかしながら、半導体チップ200のTSVアレイ260は、半導体チップ100のTSVアレイ160に電気的に接続される。これにより、例えば、バウンダリスキャン制御回路151から出力された信号は、TSVアレイ160やTSVアレイ260を構成する各々のTSVに対して出力され、更に当該信号に基づく検出信号を検出回路112で検出することが可能となる。

30

【0039】

### 3.2. 検出回路112の構成

以下、検出回路112の回路構成例を説明する。図6乃至図9は、検出回路112の回路構成例を示す図である。以下、順に説明する。

【0040】

40

#### 3.2.1. 第1の回路構成例

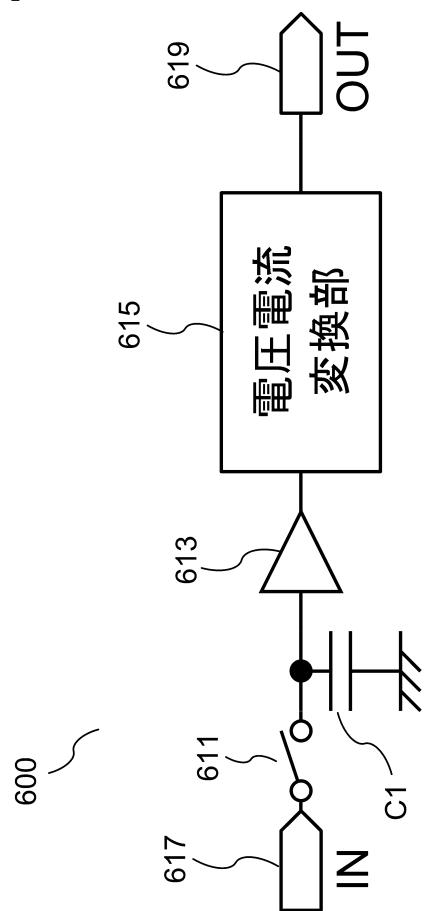

まず、図6乃至図8を参照しながら検出回路112の第1の構成例である検出回路600について説明する。検出回路600は、スイッチ611、キャパシタC1、アンプ613、及び電圧電流変換部615を含む。

【0041】

スイッチ611の一端は入力端子617に接続されており、他端はアンプ613の入力側及びキャパシタC1に接続されている。つまりスイッチ611は、入力端子617と、アンプ613の入力側及びキャパシタC1とを電気的に接続するか否かを切り替える。

【0042】

アンプ613は、入力側が、キャパシタC1を介して接地されると共にスイッチ611

50

を介して入力端子 617 に接続され、出力側が電圧電流変換部 615 の入力側に接続される。これによりアンプ 613 は、入力端子 617 から入力された電圧信号を増幅し、電圧電流変換部 615 へと出力する。

【0043】

電圧電流変換部 615 は、アンプ 613 の出力側、及び出力端子 619 と接続されている。電圧電流変換部 615 は、アンプ 613 から入力された電圧信号を電流信号に変換し、当該電流信号を出力端子 619 へと出力する。

【0044】

このように構成することにより、検出回路 600 は、入力端子 617 に入力された電圧信号を、寄生インピーダンスによる影響を避けることのできる DC 電流信号として、半導体チップ 100 外へ出力することができる。

10

【0045】

出力端子 619 から半導体チップ 100 外へ出力された電流信号は、AD コンバータに出力され、検出される。AD コンバータは複数のタイミングで電流信号を取得することにより、シリコン基板 110 に漏出した TSV 120 からの電気雑音を検出することができる。半導体チップ 100 外での雑音検出に係る構成やその動作例などについては、図 10 や図 14 等を参照しながら後述する。

【0046】

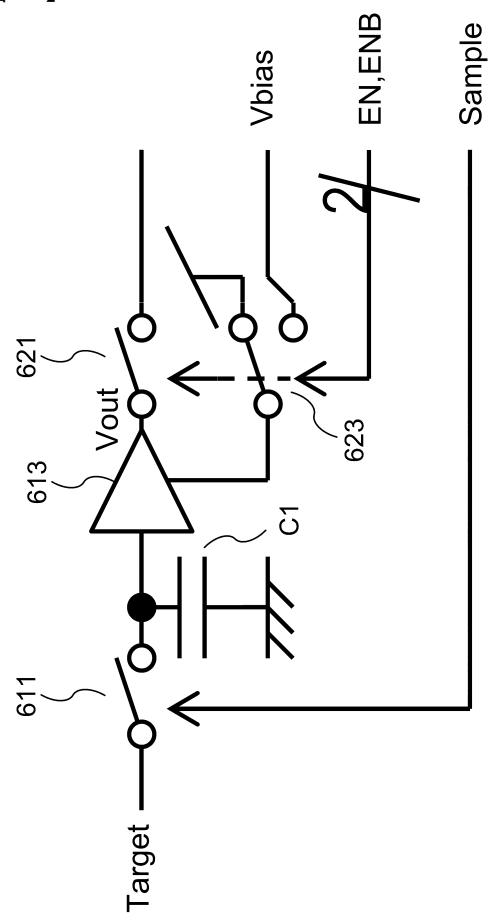

図 7 及び図 8 に、図 6 に示した検出回路 600 のうち、電圧電流変換部 615 に入力するまでの部分の具体的な回路構成例を示す。図 7 及び図 8 の例では、アンプ 613 の出力側にスイッチ 621 が接続されている。スイッチ 621 の出力側は、電圧電流変換部 615 の入力側に接続される。スイッチ 621 の ON / OFF は、外部から入力される信号 EN / ENB により切り替えられる。ここで、信号 EN、ENB は、イネーブル信号及びその反転信号であり、レジスタ回路から入力することができる。信号 EN / ENB により ON / OFF が切り替えられるスイッチ 621 により、アンプ 613 の出力電圧 Vout を電圧電流変換部 615 へ出力するか否かが切り替え可能である。

20

【0047】

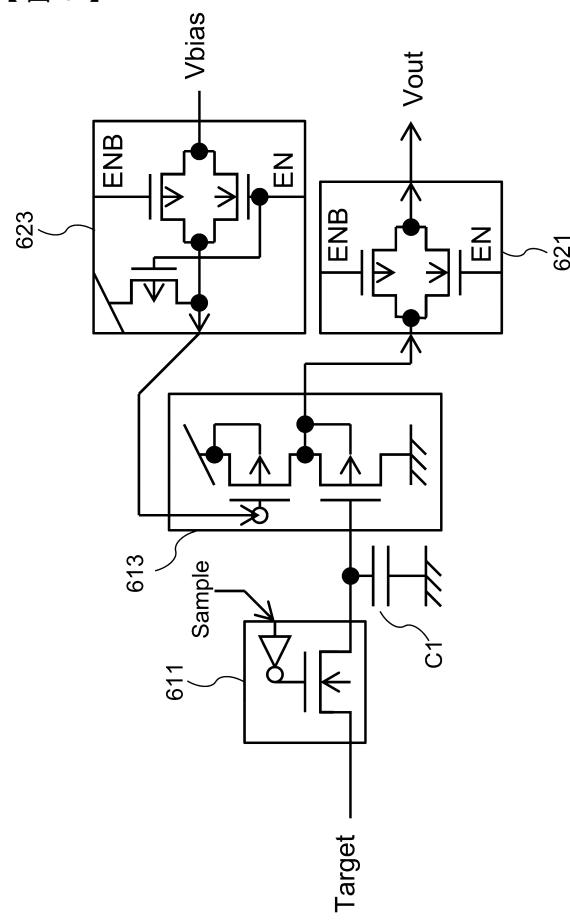

また、アンプ 613 を動作させるための電圧が、電圧源とバイアス電圧 Vbias との間で切り替え可能に入力される。アンプ 613 は、図 8 に記載の通り、例えば p チャネル半導体によるソースフォロワ回路として実現することが可能である。

30

【0048】

スイッチ 611 は、Sample 信号により切り替え可能となっている。Sample 信号は、入力端子 617 から入力された Target 信号の検出タイミングを指定するための信号である。Sample 信号によりスイッチ 611 の ON / OFF を切り替えることにより、任意のタイミングで Target 信号の電圧を検出回路 600 で検出することが可能となる。

【0049】

3.2.2. 第 2 の回路構成例

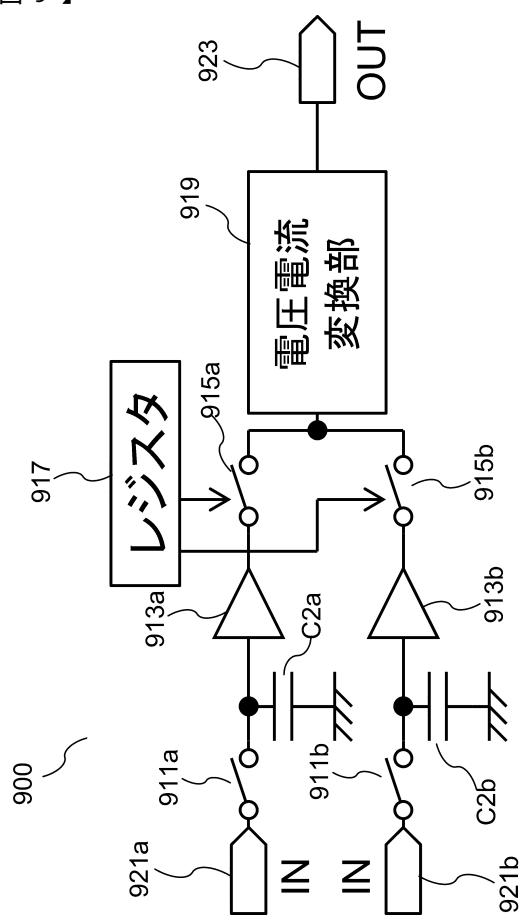

図 6 及び図 7 に示した検出回路 112 は入力端子 617 を 1 つしか有していないが、レジスタ回路と組み合わせることにより、半導体チップ 100 の複数箇所からの入力に対する検査を可能とすることも考えられる。図 9 を参照しながら、検出回路 112 の第 2 の構成例である検出回路 900 について説明する。検出回路 900 は、スイッチ 911a 及び 911b、キャパシタ C2a 及び C2b、アンプ 913a 及び 913b、レジスタ 917、及び電圧電流変換部 919 を含む。

40

【0050】

スイッチ 911a の一端は入力端子 921a に接続されており、他端はアンプ 913a の入力側及びキャパシタ C2a の一端に接続されている。つまりスイッチ 911a は、入力端子 921a と、アンプ 913a とを電気的に接続するか否かを切り替える。スイッチ 911b も同様に、一端は入力端子 921b に接続されており、他端はアンプ 913b の入力側及びキャパシタ C2b の一端に接続されている。つまりスイッチ 911b は、入力

50

端子 9 2 1 b と、アンプ 9 1 3 b とを電気的に接続するか否かを切り替える。

【0051】

アンプ 9 1 3 a は、入力側が、キャパシタ C 2 a を介して接地されるとともにスイッチ 9 1 1 a を介して入力端子 9 2 1 a に接続され、出力側がスイッチ 9 1 5 a に接続される。アンプ 9 1 3 b も同様に、入力側が、キャパシタ C 2 b を介して接地されると共にスイッチ 9 1 1 b を介して入力端子 9 2 1 b に接続され、出力側がスイッチ 9 1 5 b に接続される。

【0052】

スイッチ 9 1 5 a は、レジスタ 9 1 7 により、アンプ 9 1 3 a 及び電圧電流変換部 9 1 9 を導通させるか否かを切り替える。同様にスイッチ 9 1 5 b は、レジスタ 9 1 7 により、アンプ 9 1 3 b 及び電圧電流変換部 9 1 9 を導通させるか否かを切り替える。

10

【0053】

なお、スイッチ 9 1 1 a、キャパシタ C 2 a、アンプ 9 1 3 a、並びにスイッチ 9 1 5 a を組み合わせた回路の詳細な構成は、図 7 及び図 8 に示したものと同一の構成とすることができます。同様に、スイッチ 9 1 1 b、キャパシタ C 2 b、アンプ 9 1 3 b、並びにスイッチ 9 1 5 b を組み合わせた回路の詳細な構成も、図 7 及び図 8 に示したものと同一の構成とすることができます。

【0054】

レジスタ 9 1 7 は、スイッチ 9 1 5 a 及び 9 1 5 b の ON / OFF を切り替え制御するための EN、ENB 信号を出力する。例えば検査対象の TSV に係る信号を検出するためのメタル配線 1 3 0 に入力端子 9 2 1 a が接続されている場合には、レジスタ 9 1 7 はスイッチ 9 1 5 a を ON とし、スイッチ 9 1 5 b を OFF とする。同様に、入力端子 9 2 1 b に接続されているメタル配線に係る検査を行う場合には、スイッチ 9 1 5 a を OFF にすると共にスイッチ 9 1 5 b を ON とする。これにより、半導体チップ 1 0 0 の複数箇所を 1 つの検出回路 9 0 0 でテストすることが可能となる。

20

【0055】

電圧電流変換部 9 1 9 の入力側は、スイッチ 9 1 5 a を介してアンプ 9 1 3 a の出力側と、スイッチ 9 1 5 b を介してアンプ 9 1 3 b の出力側とそれぞれ接続されており、電圧電流変換部 9 1 9 の出力側は、出力端子 9 2 3 に接続されている。つまり、電圧電流変換部 9 1 9 は、アンプ 9 1 3 a 又は 9 1 3 b から入力された電圧信号を電流信号に変換し、当該電流信号を出力端子 9 2 3 へ出力する。このように構成することにより、検出回路 9 0 0 は、入力端子 9 2 1 a または 9 2 1 b に入力された電圧信号を、寄生インピーダンスによる影響を避ける事のできる DC 電流信号として、半導体チップ 1 0 0 外へと出力することができる。

30

【0056】

#### 4. 異常検出のための全体の機能構成例

図 6 乃至図 9 に具体例を示した検出回路 1 1 2 から半導体チップ 1 0 0 外へ出力された電流信号は、AD コンバータ (ADC) に出力され、検出される。AD コンバータは複数のタイミングで電流信号を取得することにより、シリコン基板 1 1 0 に漏出した TSV 1 2 0 からの雑音を検出することができる。以下、シリコン基板 1 1 0 に漏出した雑音信号を検出するためのシステム構成を、図 1 0 を参照しながら説明する。図 1 0 は、半導体チップ 1 0 0 における TSV 1 2 0 の雑音を検出する検査システム 1 全体の機能構成例を示す図である。

40

【0057】

#### 4. 異常検出のための全体の機能構成例

なお、図 1 0 の例では、検査システム 1 の検査対象は半導体チップ 1 0 0 となっているが、半導体チップ 1 0 0 を積層した半導体装置 3 0 0 を検査対象としてもよい。

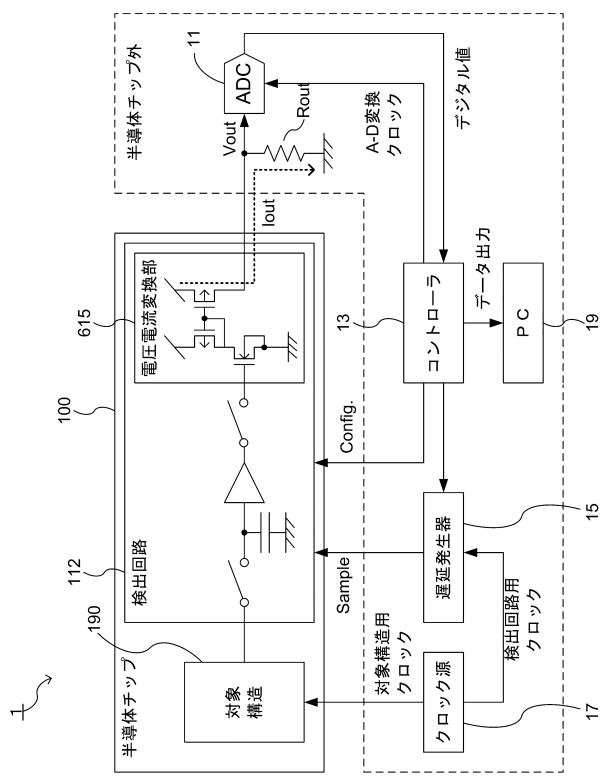

【0058】

検査システム 1 は、検査対象の半導体チップ 1 0 0 と、抵抗素子 Rout と、ADC 1 1 と、コントローラ 1 3 と、遅延発生器 1 5 と、クロック源 1 7 、PC (Personal

50

1 Computer) 19とを含む。ここで、半導体チップ100は、検査対象となるTSV120等を含む対象構造190と、検出回路112とから大きく構成される。対象構造190には、図4に示した回路テスト構造150、及び、検査対象のTSV120により構成されるTSVアレイ160を含むことができる。またここでは検出回路112は、図6乃至図8に示した第1の回路構成例により構成されるものとする。

#### 【0059】

検出回路112に含まれる電圧電流変換部615の出力端子は、抵抗素子Routを介して接地されると共に、ADC11の入力端へ入力される。電圧電流変換部615から出力され、抵抗素子Routに流れる電流がIoutとすると、ADC11には電圧Vout = Rout × Iout (オームの法則) が入力される。

10

#### 【0060】

ADC11は、入力された電圧Voutを、デジタル値へ変換してコントローラ13へ出力する。なお、ADC11が動作するためのA-D(アナログ-デジタル)クロックは、コントローラ13からADC11へ入力される。

#### 【0061】

コントローラ13は、ADC11から入力を受けた検出信号のデジタル値を、検出タイミングの情報と共にPC(Personal Computer)19へ出力する。またコントローラ13は、検出回路112に対して設定用の信号(Config.)を出力する。更にコントローラ13は、検出回路112で信号検出のタイミングを決めるサンプリングクロックであるSample信号を生成するために遅延を発生させるべく、遅延発生器15に対して遅延を設定する。

20

#### 【0062】

遅延発生器15は、クロック源17から入力を受けた検出回路用クロックに対してコントローラ13からの要求に従い遅延を発生させることにより、検出回路112での信号検出のタイミングを定めるためのサンプリングクロックであるSample信号を生成し、検出回路112へ出力する。

#### 【0063】

クロック源17は、例えば水晶振動子等によりクロックを発生させ、半導体チップ100の対象構造190に対して対象構造用クロックを出力すると共に、遅延発生器15に対して検出回路用クロックを出力する。クロック源17が半導体チップ100に入力する対象構造用クロックは、例えばバウンダリスキャン制御回路151等に入力される。

30

#### 【0064】

このような検査システム1を用いれば、半導体チップ100のシリコン基板110に漏出した信号の適宜のタイミングにおけるデジタル値を検出することができる。PC19においてこれらのデジタル値を組み合わせることにより、元となる信号の波形を再生することができる。この信号波形の再生にかかる具体例は、図14を参照しながら後述する。

#### 【0065】

##### 5. TSV120の異常検知の具体例

以下、図11乃至図14を参照しながら、上記検査システム1を用いた、半導体チップ100及び半導体装置300に対する異常検知の具体例を説明する。

40

#### 【0066】

ここでは、半導体チップ100の構造は、特に言及しない限り、図11に示す形となっているものとする。図11に示した半導体チップ100の基本的な構造は、図3に示したものと同様である。しかしながら図11の例におけるTSV120aには、不良としての断裂71が生じている。これにより、例えばTSV120aに対して下面100b側から信号を入力している場合には、断裂71よりも上面100a側のTSV120aの部分には、当該信号は伝達されない。同様に、TSV120aに対して上面100a側から信号を入力している場合には、断裂71よりも下面100b側のTSV120aの部分には、当該信号は伝達されない。

50

## 【0067】

また、図11に示した半導体チップ100では、本来、TSV120bとシリコン基板110との間にるべき絶縁膜140に、不良としての孔部72が形成されている。これによりTSV120bとシリコン基板110とが、当該孔部72において物理的に接触している。なおここでは、絶縁膜140に孔部72が形成されているものとしているがこれに限られるものではなく、例えば絶縁膜140の膜厚がTSV120bとシリコン基板110との間で薄くなっていても同様となる。

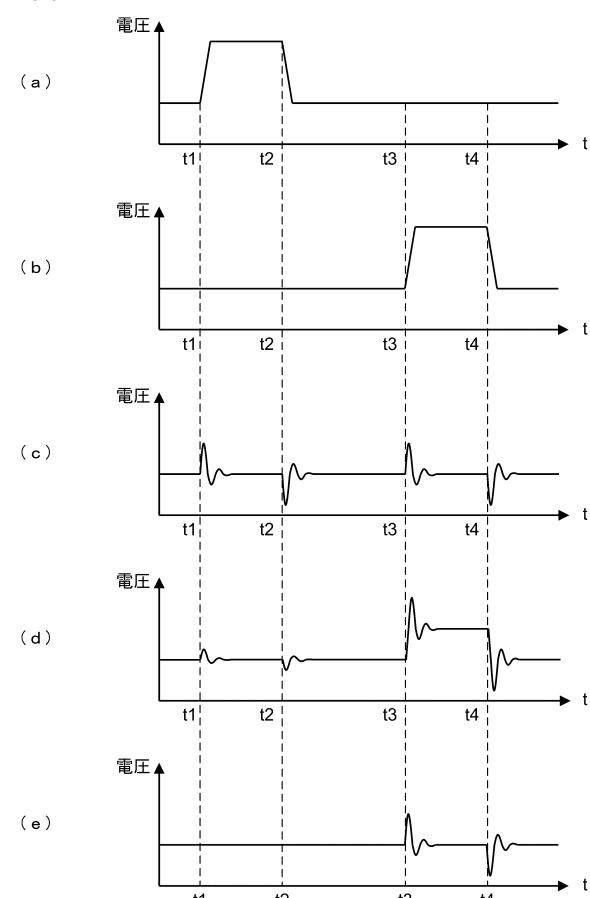

## 【0068】

このような半導体チップ100のTSV120a及び120bに対し、それぞれ図12の(a)及び(b)に示す電圧信号を入力するものとする。すなわち、TSV120aには、時刻t1で立ち上がりを開始し、時刻t2に立ち下がりを開始する方形波を入力し、TSV120bには、時刻t3から立ち上がりを開始し、時刻t4に立ち下がりを開始する方形波を入力する。

## 【0069】

図12の(a)及び(b)の信号を、図3に示した正常なTSV120a及び120bに入力した場合に、シリコン基板110に発生し、検出回路112に入力される信号の波形を図12(c)に示す。シリコン基板110には、TSV120a及び120bに入力した信号が変化を開始する時刻t1、t2、t3及びt4以降の一定時間、ノイズ(雑音)が発生している。

## 【0070】

次に、図12の(a)及び(b)の信号を、図11に示した不良のTSV120a及び120bに入力した場合に、シリコン基板110に発生し、検出回路112に入力される信号波形の例を図12(d)に示す。

## 【0071】

先述の通り、図11に示した半導体チップ100においては、TSV120aには断裂71が発生している。これにより、例えば下面100b側からTSV120aに信号を入力している場合には、断裂71よりも上面100a側には信号が伝達されない。このため、TSV120aの電圧変化に伴い、TSV120aからシリコン基板110に与えられる影響は小さくなる。よって、図12(d)の信号では、時刻t1及びt2においてシリコン基板110に発生するノイズの大きさが小さくなっている。

## 【0072】

また、図11に示した半導体チップ100においては、TSV120bとシリコン基板110との間において、絶縁膜140に孔部72が形成されている。つまり、TSV120bとシリコン基板110との間が十分に絶縁されていない。これにより、図12(d)の信号では、時刻t3と時刻t4との間ににおいてTSV120bの電圧が上昇すると、それに伴いシリコン基板110の電圧も上昇している。

## 【0073】

このように、シリコン基板110に発生し、検出回路112に入力される電圧波形により、TSV120に不良が発生しているか否か、及びどのような不良が発生しているかを、半導体チップ100を他の半導体チップと積層する前に、特定することが可能である。

## 【0074】

さらに、このようにして不良がないと判断された半導体チップ100及び200を積層させた上で、同様の検査を行うことにより、半導体チップ100及び200を接続する接続部分の異常も検出することができる。

## 【0075】

ここでは、半導体チップ100及び200を積層した半導体装置300は、特に言及しない限り図13に示す構造となっているものとする。半導体チップ100及び200の構造は、図3に示した正常な半導体チップ100と同様である。これに加えて、半導体チップ100のTSV120aの下面100b側にはメタルパッド180aが形成されており、当該メタルパッド180aがマイクロパンプ181により半導体チップ200に接続さ

10

20

30

40

50

れる。しかしながら、図13の例では、マイクロバンプ181aには不良である断裂183が含まれており、TSV120aと半導体チップ200とは電気的に接続されていない。

#### 【0076】

また、TSV120bには、半導体チップ100の下面100b側にメタルパッド180bが形成されており、当該メタルパッド180bがマイクロバンプ181bにより半導体チップ200に電気的に接続される。同様に、TSV120cの下面100b側にはメタルパッド180cが形成されており、当該メタルパッド180cがマイクロバンプ181c及び181dにより半導体チップ200に電気的に接続される。

#### 【0077】

このような半導体装置300において、半導体チップ100のTSV120a及び120bに対し、それぞれ半導体チップ200側から図12の(a)及び(b)に示した電圧信号を入力するものとする。半導体チップ100と200とが正常に接続されれば、検出回路112には図12(c)に示した信号が入力される。

#### 【0078】

しかしながら、図13に示した半導体装置300のように、TSV120aと半導体チップ200とを電気的に接続するためのマイクロバンプ181aに不良があり、両者が電気的に接続されていない場合には、TSV120aには電圧信号が入力されない。この結果、時刻t1及びt2においては、シリコン基板110にはノイズが発生せず、検出回路112に入力される信号は図12(e)に示すようなものとなる。つまり、検出回路112に入力される信号波形により、接続不良の有無を特定することができる。

#### 【0079】

##### 6. 検出される信号波形の具体例

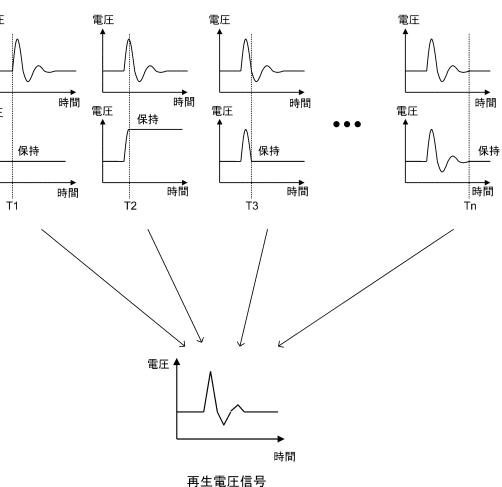

続いて、検出回路112に入力される信号波形を、検査システム1において再生する方法を、図14を参照しながら説明する。図14の1行目には、シリコン基板110に発生し、メタル配線130を介して検出回路112に入力される電圧の電圧波形を示す。

#### 【0080】

このような入力電圧に対し、検出回路112はコントローラ13による制御を受けたSaamp1e信号の入力を受けることにより、時刻T1、T2、T3及びTnで信号を検出する。より具体的には、例えば図6に示した検出回路600において、スイッチ611を、時刻T1まで時間、時刻T2までの時間、時刻T3までの時間、時刻Tnまでの時間、それぞれON状態とする。これにより、検出回路600から出力される出力電圧Voutの波形は、時刻T1、T2、T3及びTnまで、図14の2行目の波形となる。ADC11は、時刻T1、T2、T3及びTnにおいて検出された電圧値を保持し、これをデジタル値に変換した上でコントローラ13へと渡す。

#### 【0081】

コントローラ13は、このようにして集められた各時刻の電圧値に関するデータをPC19へデータ出力する。PC19はこれを合わせることにより、図14の下部に示すグラフのような信号波形を再生することができる。この結果、シリコン基板110から検出回路112に入力される信号の波形をPC19で再生することができるため、この波形を観察及び分析することにより、半導体チップ100に含まれるTSV120や、半導体チップ100及び200の間の接続に係る異常を検出することができる。

#### 【0082】

##### 7. 付記

なお、前述の実施形態の構成は、組み合わせたり或いは一部の構成部分を入れ替えたりしてもよい。また、本発明の構成は前述の実施形態のみに限定されるものではなく、発明の要旨を逸脱しない範囲内において種々変更を加えてもよい。

#### 【符号の説明】

#### 【0083】

|         |                                               |    |

|---------|-----------------------------------------------|----|

| 1 1     | : A D コンバータ                                   |    |

| 1 3     | : コントローラ                                      |    |

| 1 5     | : 遅延発生器                                       |    |

| 1 7     | : クロック源                                       |    |

| 1 9     | : P C                                         |    |

| 7 1     | : 断裂                                          |    |

| 7 2     | : 孔部                                          |    |

| 1 0 0   | : 半導体チップ                                      |    |

| 1 0 0 a | : 上面                                          | 10 |

| 1 0 0 b | : 下面                                          |    |

| 1 1 0   | : シリコン基板                                      |    |

| 1 1 1   | : 拡散領域                                        |    |

| 1 1 2   | : 検出回路                                        |    |

| 1 2 0   | : T S V ( T h r o u g h S i l i c o n V i a ) |    |

| 1 3 0   | : メタル配線                                       |    |

| 1 4 0   | : 絶縁膜                                         |    |

| 1 5 0   | : 回路テスト構造                                     |    |

| 1 5 1   | : バウンダリスキャン制御回路                               |    |

| 1 5 3   | : 製品回路                                        |    |

| 1 6 0   | : T S V アレイ                                   | 20 |

| 1 7 0   | : 接続                                          |    |

| 1 8 0   | : メタルパッド                                      |    |

| 1 8 1   | : マイクロバンプ                                     |    |

| 1 8 3   | : 断裂                                          |    |

| 1 9 0   | : 対象構造                                        |    |

| 2 0 0   | : 半導体チップ                                      |    |

| 2 1 0   | : シリコン基板                                      |    |

| 2 1 1   | : 拡散領域                                        |    |

| 2 1 2   | : 検出回路                                        |    |

| 2 2 0   | : T S V                                       | 30 |

| 2 3 0   | : メタル配線                                       |    |

| 2 5 0   | : 回路テスト構造                                     |    |

| 2 5 1   | : バウンダリスキャン制御回路                               |    |

| 2 5 3   | : 製品回路                                        |    |

| 2 6 0   | : T S V アレイ                                   |    |

| 2 7 0   | : 接続                                          |    |

| 3 0 0   | : 半導体装置                                       |    |

| 6 0 0   | : 検出回路                                        |    |

| 6 1 1   | : スイッチ                                        |    |

| 6 1 3   | : アンプ                                         | 40 |

| 6 1 5   | : 電圧電流変換部                                     |    |

| 6 1 7   | : 入力端子                                        |    |

| 6 1 9   | : 出力端子                                        |    |

| 6 2 1   | : スイッチ                                        |    |

| 9 0 0   | : 検出回路                                        |    |

| 9 1 1   | : スイッチ                                        |    |

| 9 1 3   | : アンプ                                         |    |

| 9 1 5   | : スイッチ                                        |    |

| 9 1 7   | : レジスタ                                        |    |

| 9 1 9   | : 電圧電流変換部                                     | 50 |

|           |          |

|-----------|----------|

| 9 2 1     | ：入力端子    |

| 9 2 3     | ：出力端子    |

| 1 0 0 0   | ：半導体装置   |

| 1 1 0 0   | ：半導体チップ  |

| 1 1 0 0 a | ：上面      |

| 1 1 0 0 b | ：下面      |

| 1 1 1 0   | ：シリコン基板  |

| 1 1 1 2   | ：拡散領域    |

| 1 1 2 0   | ：T S V   |

| 1 1 3 0   | ：絶縁膜     |

| 1 1 4 0   | ：メタル配線   |

| 1 1 5 0   | ：メタルパッド  |

| 1 2 0 0   | ：半導体チップ  |

| 1 2 1 0   | ：シリコン基板  |

| 1 2 2 0   | ：テスト回路   |

| 1 2 3 0   | ：マイクロバンプ |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/04 (2006.01) H 01 L 27/04 T

(72)発明者 菊地 克弥

茨城県つくば市東1-1-1 国立研究開発法人産業技術総合研究所 つくばセンター内

(72)発明者 青柳 昌宏

茨城県つくば市東1-1-1 国立研究開発法人産業技術総合研究所 つくばセンター内

審査官 名取 乾治

(56)参考文献 特開2014-120531 (JP, A)

特開平04-119000 (JP, A)

特開2009-294232 (JP, A)

特開2012-083262 (JP, A)

特開2015-078955 (JP, A)

国際公開第2009/147717 (WO, A1)

特開2010-219425 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 01 R 31/28

G 01 R 31/02

H 01 L 21/66

H 01 L 23/12

H 01 L 27/04