(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7108471号

(P7108471)

(45)発行日 令和4年7月28日(2022.7.28)

(24)登録日 令和4年7月20日(2022.7.20)

(51)国際特許分類

|         |                 |         |        |       |

|---------|-----------------|---------|--------|-------|

| H 0 4 N | 5/335(2011.01)  | H 0 4 N | 5/335  | 5 0 0 |

| H 0 4 N | 5/3745(2011.01) | H 0 4 N | 5/3745 |       |

請求項の数 13 (全24頁)

|                   |                             |          |                                            |

|-------------------|-----------------------------|----------|--------------------------------------------|

| (21)出願番号          | 特願2018-109660(P2018-109660) | (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22)出願日           | 平成30年6月7日(2018.6.7)         | (74)代理人  | 110003281<br>特許業務法人大塚国際特許事務所               |

| (65)公開番号          | 特開2019-17065(P2019-17065A)  | (72)発明者  | 小林 寛和<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| (43)公開日           | 平成31年1月31日(2019.1.31)       | (72)発明者  | 竹田 伸弘<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| 審査請求日             | 令和3年6月4日(2021.6.4)          | 審査官      | 大室 秀明                                      |

| (31)優先権主張番号       | 特願2017-132737(P2017-132737) |          |                                            |

| (32)優先日           | 平成29年7月6日(2017.7.6)         |          |                                            |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                     |          |                                            |

最終頁に続く

(54)【発明の名称】 固体撮像素子、撮像装置及び撮像方法

## (57)【特許請求の範囲】

## 【請求項1】

光子の受光頻度に応じた頻度でパルスを発するセンサ部がそれぞれ備えられた複数の画素と、

前記センサ部から発せられる前記パルスの数をカウントする第1のカウンタと、

外部から周期信号の供給を受けるインターフェースと、

単位時間あたりに検出される前記パルスの数の変化が閾値より大きい場合に、前記第1のカウンタのカウント値に応じた信号を出力する出力部と、を備え、

前記第1のカウンタは、前記周期信号に基づいてリセットされ、

前記出力部は、前記単位時間あたりに検出される前記パルスの数の変化が前記閾値以下の場合には、前記第1のカウンタのカウント値に応じた信号を出力しないことを特徴とする固体撮像素子。

## 【請求項2】

光子の受光頻度に応じた頻度でパルスを発するセンサ部がそれぞれ備えられた複数の画素と、

前記センサ部から発せられる前記パルスの数をカウントする第1のカウンタと、

前記第1のカウンタのカウント値を記憶する第1のラッチ部と、

前記第1のカウンタのカウント値を記憶する第2のラッチ部と、

外部から周期信号の供給を受けるインターフェースと、

単位時間あたりに検出される前記パルスの数の変化が閾値より大きい場合に、前記第1

のカウンタのカウント値に応じた信号を出力する出力部と、を備え、

前記第1のカウンタは、前記周期信号に基づいてリセットされ、

前記第1のラッチ部と前記第2のラッチ部とは、前記第1のカウンタのカウント値を前記

単位時間の周期に基づいて交互に記憶し、

前記出力部は、前記第1のラッチ部に記憶されたカウント値と前記第2のラッチ部に記憶

されたカウント値との差分が前記閾値より大きい場合に、前記第1のカウンタのカウント

値に応じた信号を出力することを特徴とする固体撮像素子。

**【請求項3】**

光子の受光頻度に応じた頻度でパルスを発するセンサ部がそれぞれ備えられた複数の画素

と、

前記センサ部から発せられる前記パルスの数をカウントする第1のカウンタと、

前記センサ部から発せられる前記パルスの数をカウントする第2のカウンタと、

前記第2のカウンタのカウント値を記憶する第1のラッチ部と、

前記第2のカウンタのカウント値を記憶する第2のラッチ部と、

外部から周期信号の供給を受けるインターフェースと、

単位時間あたりに検出される前記パルスの数の変化が閾値より大きい場合に、前記第1

のカウンタのカウント値に応じた信号を出力する出力部と、を備え、

前記第1のカウンタは、前記周期信号に基づいてリセットされ、

前記第2のカウンタは、前記周期信号よりも周期が短い周期信号に基づいてリセットされ、

前記第1のラッチ部と前記第2のラッチ部とは、前記第2のカウンタのカウント値を前記

単位時間の周期に基づいて交互に記憶し、

前記出力部は、前記第1のラッチ部に記憶されたカウント値と前記第2のラッチ部に記憶

されたカウント値との差分が前記閾値より大きい場合に、前記第1のカウンタのカウント

値に応じた信号を出力することを特徴とする固体撮像素子。

**【請求項4】**

前記第2のカウンタのピット幅は、前記第1のカウンタのピット幅よりも小さいことを特

徴とする請求項3に記載の固体撮像素子。

**【請求項5】**

前記出力部は、前記第1のラッチ部に記憶されたカウント値と前記第2のラッチ部に記憶

されたカウント値との差分が前記閾値より大きくなつた際の時間に関する情報を、前記第

1のカウンタのカウント値に応じた信号とともに出力することを特徴とする請求項3又は

4に記載の固体撮像素子。

**【請求項6】**

光子の受光頻度に応じた頻度でパルスを発するセンサ部がそれぞれ備えられた複数の画素

と、

前記センサ部から発せられる前記パルスの数をカウントする第1のカウンタと、

前記センサ部から発せられる前記パルスの数をカウントする第2のカウンタと、

前記第2のカウンタのカウント値を記憶する第1のラッチ部と、

前記第2のカウンタのカウント値を記憶する第2のラッチ部と、

外部から周期信号の供給を受けるインターフェースと、

単位時間あたりに検出される前記パルスの数の変化が閾値より大きい場合に、前記第1

のカウンタのカウント値に応じた信号を出力する出力部と、を備え、

前記第1のカウンタは、前記周期信号に基づいてリセットされ、

前記第2のカウンタは、前記周期信号に基づいてリセットされ、

前記第1のラッチ部と前記第2のラッチ部とは、前記第2のカウンタのカウント値を前記

単位時間の周期に基づいて交互に記憶し、

前記第1のカウンタは、前記周期信号の周期に基づいてリセットする第1のリセット動作

と、前記第1のラッチ部に記憶されたカウント値と前記第2のラッチ部に記憶されたカウ

ント値との差分が前記閾値より大きくなつたときにリセットする第2のリセット動作によ

りリセットされ、

前記出力部は、前記第1のカウンタが、前記第1のリセット動作によりリセットされた後、最初に前記第2のリセット動作によりリセットされてから、次に前記第1のリセット動作または前記第2のリセット動作によりリセットされるまでの前記第1のカウンタのカウント値に応じた信号を出力することを特徴とする固体撮像素子。

【請求項7】

前記第2のカウンタのビット幅は、前記第1のカウンタのビット幅よりも小さいことを特徴とする請求項6に記載の固体撮像素子。

【請求項8】

前記出力部は、前記第1のカウンタが、前記第1のリセット動作によりリセットされた後、最初に前記第2のリセット動作によりリセットされてから、次に前記第1のリセット動作または前記第2のリセット動作によりリセットされるまでの時間に関する情報を、前記第1のカウンタのカウント値に応じた信号とともにに出力することを特徴とする請求項6又は7に記載の固体撮像素子。

10

【請求項9】

前記出力部は、前記第1のカウンタが備えられた前記画素の座標を示す信号を、前記第1のカウンタのカウント値に応じた信号とともにに出力することを特徴とする請求項1から8のいずれか1項に記載の固体撮像素子。

【請求項10】

前記複数の画素の各々に前記第1のカウンタが備えられていることを特徴とする請求項1から9のいずれか1項に記載の固体撮像素子。

20

【請求項11】

前記センサ部は、アバランシェフォトダイオードを備えることを特徴とする請求項1から10のいずれか1項に記載の固体撮像素子。

【請求項12】

請求項1乃至11のいずれか1項に記載の固体撮像素子と、前記固体撮像素子から出力される信号を用いて所定の画像処理を行う画像処理部とを備えることを特徴とする撮像装置。

【請求項13】

前記画像処理部は、前記固体撮像素子から出力される信号を用いて、既に取得した画像の一部を更新することを特徴とする請求項12に記載の撮像装置。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、固体撮像素子、撮像装置及び撮像方法に関する。

【背景技術】

【0002】

近時では、撮像エリア内で物体に動きが発生した場合に、通常時の撮像よりも鮮明な画像で物体を撮像し得る撮像装置が提案されている（特許文献1）。また、新しい方式のイメージセンサとして、特許文献2に示すようなイメージセンサが提案されている。特許文献2に開示されたイメージセンサには、以下のような信号処理回路が各画素に備えられている。特許文献2では、光電変換素子で生成された電荷を蓄積する蓄積容量と、蓄積容量の電圧を基準電圧と比較し、両者が一致したときにパルスを出力する比較器と、比較器の出力により蓄積容量の電圧をリセット電圧に戻すリセット手段とが各画素に備えられている。

40

【先行技術文献】

【特許文献】

【0003】

【文献】特開2005-175719号公報

特開2015-173432号公報

【発明の概要】

【発明が解決しようとする課題】

50

## 【0004】

しかしながら、従来の技術では、必ずしも良好な撮影を行い得ない場合があった。

## 【0005】

本発明の目的は、良好な撮影を行い得る固体撮像素子、撮像装置及び撮像方法を提供することにある。

## 【課題を解決するための手段】

## 【0006】

実施形態の一観点によれば、光子の受光頻度に応じた頻度でパルスを発するセンサ部がそれぞれ備えられた複数の画素と、前記センサ部から発せられる前記パルスの数をカウントする第1のカウンタと、外部から周期信号の供給を受けるインターフェースと、単位時間あたりに検出される前記パルスの数の変化が閾値より大きい場合に、前記第1のカウンタのカウント値に応じた信号を出力する出力部と、を備え、前記第1のカウンタは、前記周期信号に基づいてリセットされ、前記出力部は、前記単位時間あたりに検出される前記パルスの数の変化が前記閾値以下の場合には、前記第1のカウンタのカウント値に応じた信号を出力しないことを特徴とする固体撮像素子が提供される。

10

## 【発明の効果】

## 【0007】

本発明によれば、良好な撮影を行い得る固体撮像素子、撮像装置及び撮像方法を提供することができる。

20

## 【図面の簡単な説明】

## 【0008】

【図1】第1実施形態による固体撮像素子を示す図である。

【図2】第1実施形態による固体撮像素子を示す図である。

【図3】第1実施形態による固体撮像素子の動作の例を示すタイミングチャートである。

【図4】第1実施形態による撮像装置を示すブロック図である。

【図5】第1実施形態による撮像装置の動作を示すフローチャートである。

【図6】第2実施形態による固体撮像素子を示す図である。

【図7】第2実施形態による固体撮像素子の動作の例を示すタイミングチャートである。

【図8】第3実施形態による固体撮像素子を示す図である。

30

【図9】第3実施形態による固体撮像素子の動作の例を示すタイミングチャートである。

## 【発明を実施するための形態】

## 【0009】

本発明の実施の形態について図面を用いて以下に説明する。なお、本発明は以下の実施形態に限定されるものではなく、適宜変更可能である。また、以下に示す実施形態を適宜組み合わせるようにしてもよい。

## 【0010】

## [第1実施形態]

第1実施形態による固体撮像素子、撮像装置及び撮像方法について図1乃至図5を用いて説明する。図1は、本実施形態による固体撮像素子を示す図である。

40

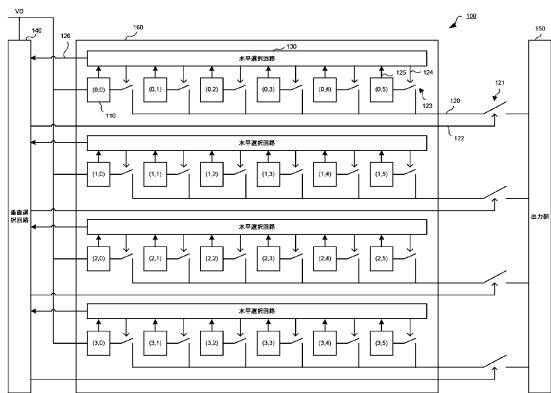

## 【0011】

図1に示すように、本実施形態による固体撮像素子100は、撮像部（撮像領域、画素アレイ領域）160と、水平選択回路（水平走査回路）130と、垂直選択回路（垂直走査回路）140と、出力部150とを備えている。

## 【0012】

撮像部160には、複数の画素110が行列状、即ち、マトリクス状に配されている。ここでは、説明の簡略化のため、24個の画素110が図示されているが、実際には多数の画素110が撮像部160に備えられている。各々の画素110に付された（p, q）（p, qはそれぞれ整数）は、当該画素110の座標を示している。pは行番号を示しており、qは列番号を示している。各々の画素110には、システム制御部404（図4参照）から同期信号VDが供給される（図2（b）参照）。撮像部160は、撮影光学系40

50

1 (図4参照)によって形成される光学像を受光する。各々の画素110に入射する光子が、各々の画素110においてカウントされるようになっている。画素110においてカウントされた光子の数に応じた出力信号が、水平出力線120を介して出力部150に出力されるようになっている。同一の行に位置する画素110によって取得された信号は、同一の水平出力線120を介して出力部150に伝送される。ここでは、4本の水平出力線が図示されているが、実際には、多数の出力信号線が備えられている。各々の水平出力線120には、スイッチ121が備えられている。画素110から出力される出力信号は、水平出力線120とスイッチ121とを介して出力部150に伝送される。

#### 【0013】

撮像部160の各々の行に対して、水平選択回路130が備えられている。なお、ここでは、水平選択回路130が撮像部160内に備えられている場合を例に説明するが、撮像部160の外側に水平選択回路130が備えられているてもよい。当該画素110が読み出し対象であるか否かを示す情報が、当該画素110から水平選択回路130に信号線125を介して供給されるようになっている。例えば、前フレームにおける当該画素110の画素値と現フレームにおける当該画素110の画素値との差分が閾値TH以下である場合には、以下になる。即ち、当該画素110は読み出し対象ではないということを示す情報が、当該画素110から水平選択回路130に信号線125を介して供給される。一方、前フレームにおける当該画素110の画素値と現フレームにおける当該画素110の画素値との差分が閾値THより大きい場合には、以下になる。即ち、当該画素110は読み出し対象であるということを示す情報が、当該画素110から水平選択回路130に信号線125を介して供給される。水平選択回路130は、各々の画素110から供給されるこのような情報をそれぞれ記憶する。水平選択回路130は、各々の画素110から供給されるこのような情報に基づいて、以下のような処理を行う。即ち、水平選択回路130は、当該水平選択回路130が備えられている行に位置する画素110のうちの読み出し対象となる画素110の数を示す情報を、信号線126を介して垂直選択回路140に供給する。水平選択回路130は、読み出し処理の際、当該水平選択回路130が備えられた行に位置する複数の画素110のうちの読み出し対象となる画素110を水平方向に順次選択する。画素110から出力される信号は、スイッチ123を介して水平出力線120に伝送されるようになっている。スイッチ123は、水平選択回路130から読み出し制御線124を介して供給される信号によって制御される。水平選択回路130は、読み出し対象の画素110から信号を読み出す際、当該画素110の出力信号線に備えられたスイッチ123をON状態にする。水平選択回路130は、読み出し対象の画素110に対して、列番号qが小さい順に読み出し処理を行う。水平選択回路130は、読み出し対象ではない画素110に対しては、読み出し処理を行わない。

#### 【0014】

垂直選択回路140には、水平方向に延在する複数の読み出し制御線122が備えられている。ここでは、4本の読み出し制御線122が図示されているが、実際には、多数の読み出し制御線122が備えられている。垂直選択回路140には、システム制御部404(図4参照)から同期信号(垂直同期信号)VDが供給されるようになっている。上述したように、各々の行に備えられた水平選択回路130からは、読み出し対象となる画素110の数を示す情報が、信号線126を介して垂直選択回路140に供給されるようになっている。垂直選択回路140は、各々の行において読み出し対象となる画素110の数を記憶する。垂直選択回路140は、読み出し処理の際、読み出し対象となる画素110が存在している行、即ち、読み出しの対象となる行を垂直方向に順次選択する。読み出し対象となる画素110が存在しない行に対しては、読み出し処理は行われない。垂直選択回路140は、読み出し制御線122を介してスイッチ121をON状態にすることによって、読み出しの対象となる行を選択する。垂直選択回路140は、当該行に存在している読み出し対象となる画素110の数に応じた時間だけ、当該行を選択する。読み出し対象となる画素110が当該行に多く存在している場合には、当該行が選択される時間が長くなり、読み出し対象となる画素110が当該行に多く存在していない場合には、当該行

10

20

30

40

50

が選択される時間は短くなる。

【0015】

垂直選択回路140によって行の選択を垂直方向に適宜行いつつ、水平選択回路130によって画素110の選択を水平方向に適宜行うことにより、読み出し対象の画素110から信号が読み出される。読み出し対象の画素110からそれぞれ読み出された信号は、水平出力線120をそれぞれ介して出力部150に供給される。出力部150は、撮像部160から順次供給される信号を用いて出力信号OUTPUTを生成する。出力部150は、例えば、低電圧差動伝送(LVDS: Low Voltage Differential 10 Signal)技術等を用いて、固体撮像素子100の外部に出力信号OUTPUTを出力する。この際、出力部150は、読み出し対象となった画素110の座標(p, q)を示す情報を、当該画素110から読み出された信号とともに出力する。固体撮像素子100は、同期信号VDに基づいて、第n番目のフレームに対する読み出し処理と、第n+1番目のフレームの露光処理とを並行して行う。

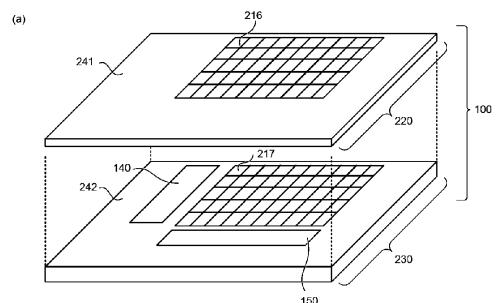

【0016】

図2は、本実施形態による固体撮像素子を示す図である。図2(a)は、本実施形態による固体撮像素子を示す斜視図である。図2(a)に示すように、固体撮像素子100は、2つの基板(半導体チップ)220, 230を積層することによって構成されている。図2(b)は、本実施形態による固体撮像素子100に備えられている画素110を示している。図2(b)においては、固体撮像素子100に備えられた複数の画素110のうちの1つの画素110が抜き出して示されている。

【0017】

図2(a)に示すように、固体撮像素子100は、撮影光学系401によって形成される光学像を受光する基板(上部基板)220と、主としてデジタル系の回路を備える基板(下部基板)230とから構成されている。図2(b)に示すように、画素110は、センサ部(受光部、画素部)216と計数部217とによって構成されている。画素110のうちのセンサ部216は、基板220に形成されている。画素110のうちの計数部217は、基板230に形成されている。複数のセンサ部216が、基板220に行列状に配列されている。複数の計数部217が、基板230に行列状に配列されている。複数のセンサ部216の各々と、これらのセンサ部216に対応する複数の計数部217の各々とが、互いに電気的に接続されている。こうして、複数の画素110がマトリクス状に配されている。センサ部216には、フォトダイオード201と、クエンチ素子202と、インバータ203とが備えられている。センサ部216にインバータ203が備えられているため、波形整形されたパルス信号PULSEがセンサ部216から計数部217に伝送される。従って、センサ部216から計数部217への伝送は比較的ロバストである。計数部217には、カウンタ204と、ラッチ回路(ラッチ部)Lat1、Lat2と、インバータ207と、減算器208と、比較器209, 210と、OR回路211と、乗算器212, 213と、スイッチ214, 215とが備えられている。垂直選択回路140と、出力部150とは、基板220の周辺回路部241又は基板230の周辺回路部242とのうちのいずれかに備えられている。ここでは、垂直選択回路140と、出力部150とが、基板230の周辺回路部242に配置されている場合を例に説明する。なお、図2(a)においては、水平選択回路130の図示が省略されている。水平選択回路130は、例えば基板230に備えられている。

【0018】

このように、本実施形態では、センサ部216が基板220に形成されており、計数部217が基板230に形成されている。回路規模が大きい計数部217が、センサ部216が備えられている基板220とは別個の基板230に備えられているため、センサ部216の面積を十分に確保することができる。このため、センサ部216の開口面積を十分に確保することができる。

【0019】

フォトダイオード201としては、単一光子を検出し得るアバランシェフォトダイオード

10

20

30

40

50

、即ち、S P A D ( S i n g l e P h o t o n A v a l a n c h e D i o d e 、 単一光子アバランシェダイオード) が用いられている。フォトダイオード 201 のアノードは接地電圧に接続されており、フォトダイオード 201 のカソードはクエンチ素子 202 の一端に接続されている。クエンチ素子 202 の他端にはバイアス電圧 V<sub>a</sub> が印加される。フォトダイオード 201 には、クエンチ素子 202 を介してフォトダイオード 201 の降伏電圧より大きいバイアス電圧 V<sub>a</sub> が印加され得る。このため、フォトダイオード 201 はガイガーモードと称される動作モードで動作し得る。即ち、フォトダイオード 201 に光子 ( フォトン ) が入射するとアバランシェ増倍現象を引き起こす。これにより、アバランシェ電流が生じ、クエンチ素子 202 において電圧降下が生ずる。クエンチ素子 202 は、フォトダイオード 201 のアバランシェ増倍現象を停止させるための抵抗素子である。ここでは、M O S トランジスタの抵抗成分を利用してクエンチ素子 202 が構成されている。アバランシェ増倍現象によってアバランシェ電流が生じると、クエンチ素子 202 において電圧降下が生じ、フォトダイオード 201 に印加されるバイアス電圧が降下する。バイアス電圧がフォトダイオード 201 の降伏電圧以下になるとアバランシェ増倍現象が停止する。その結果、アバランシェ電流が流れなくなり、フォトダイオード 201 には、再びバイアス電圧 V<sub>a</sub> が印加される。フォトダイオード 201 のカソードと、クエンチ素子 202 の一端とは、インバータ 203 の入力端子に接続されている。インバータ 203 の出力端子は、カウンタ 204 の入力端子に接続されている。フォトダイオード 201 に光子が入射すると、上記のような現象が生ずるため、インバータ 203 の入力端子において電圧変化が生じる。インバータ 203 は、かかる電圧変化に応じてパルス信号 P U L S E を生成し、生成したパルス信号 P U L S E をカウンタ 204 に出力する。こうして、波形整形されたパルス信号 P U L S E がインバータ 203 から出力される。このように、フォトダイオード 201 とクエンチ素子 202 とインバータ 203 とを含むセンサ部 216 においては、フォトダイオード 201 に光子が入射すると、光子の受光頻度に応じた頻度でインバータ 203 からパルス信号 P U L S E が出力される。より具体的には、フォトダイオード 201 に 1 つの光子が入射すると、インバータ 203 から 1 つのパルス信号 P U L S E が出力される。バイアス電圧 V<sub>a</sub> は、例えば +20 V 程度とすることができますが、これに限定されるものではない。例えば、フォトダイオード 201 のアノードを負の電位に接続するようにしてもよい。

#### 【 0 0 2 0 】

カウンタ 204 のクロック端子には、インバータ 203 から出力されるパルス信号 P U L S E が入力されるようになっている。カウンタ 204 は、パルス信号 P U L S E のパルス数をカウントする。カウンタ 204 のビット ( b i t ) 幅は、例えば 16 とすることができますが、これに限定されるものではない。カウンタ 204 のリセット端子には、同期信号 V<sub>D</sub> が供給されるようになっている。カウンタ 204 は、同期信号 V<sub>D</sub> の極性が変化した際に、カウント値 C N T を初期値、即ち、0 にリセットする。即ち、カウンタ 204 は、同期信号 V<sub>D</sub> が L o w レベルから H i g h レベルに変化した際に、カウント値 C N T を初期値にリセットする。また、カウンタ 204 は、同期信号 V<sub>D</sub> が H i g h レベルから L o w レベルに変化した際に、カウント値 C N T を初期値にリセットする。カウンタ 204 の出力端子は、ラッチ回路 L a t 1 , L a t 2 の D 端子に接続されている。従って、カウンタ 204 から出力されるカウント値 C N T は、ラッチ回路 L a t 1 , L a t 2 の D 端子にそれぞれ入力されるようになっている。

#### 【 0 0 2 1 】

ラッチ回路 L a t 1 の G 端子には、同期信号 V<sub>D</sub> が供給されるようになっている。ラッチ回路 L a t 2 の G 端子には、同期信号 V<sub>D</sub> がインバータ 207 を介して供給されるようになっている。ラッチ回路 L a t 1 は、同期信号 V<sub>D</sub> が L o w レベルから H i g h レベルに変化した際に、カウンタ 204 から出力されているカウント値 C N T を記録する。一方、ラッチ回路 L a t 2 は、同期信号 V<sub>D</sub> が H i g h レベルから L o w レベルに変化した際に、カウンタ 204 から出力されているカウント値 C N T を記録する。ラッチ回路 L a t 1 の Q 端子は、スイッチ 214 , 123 を介して水平出力線 120 に接続されている。また

10

20

30

40

50

、ラッチ回路 Lat 2 の Q 端子は、スイッチ 215, 123 を介して水平出力線 120 に接続されている。また、ラッチ回路 Lat 1 の Q 端子は、減算器 208 の一方の入力端子に接続されており、ラッチ回路 Lat 2 の Q 端子は、減算器 208 の他方の入力端子に接続されている。ラッチ回路 Lat 1 の Q 端子から出力されるカウント値 Lat 1 - Q と、ラッチ回路 Lat 2 の Q 端子から出力されるカウント値 Lat 2 - Q との差分が、減算器 208 によって求められる。減算器 208 によって求められたこれらの差分（差分値）は、比較器 209、210 に入力されるようになっている。比較器 209 は、減算器 208 によって求められた差分値が閾値 TH より大きいか否かを判定し、かかる差分値が閾値 TH よりも大きい場合には High レベルの信号を出力する。比較器 209 は、減算器 208 によって求められた差分値が閾値 - TH より小さいか否かを判定し、かかる差分値が閾値 - TH よりも小さい場合には High レベルの信号を出力する。比較器 209, 210 の出力端子は、OR 回路 211 の入力端子にそれぞれ接続されている。OR 回路 211 は、比較器 209, 210 から出力される信号のうちの少なくともいずれかが High レベルになると、High レベルの信号を出力する。OR 回路 211 から出力される信号は、乗算器 212、213 に入力されるようになっている。乗算器 212 には、同期信号 VD と OR 回路 211 の出力信号とが入力されるようになっている。同期信号 VD が High レベルであり、且つ、OR 回路 211 の出力信号が High レベルである際に、乗算器 212 の出力が High レベルとなる。スイッチ 214 は、乗算器 212 から出力される信号によって制御されるようになっている。同期信号 VD が High レベルであり、且つ、OR 回路 211 の出力信号が High レベルである際に、スイッチ 214 は ON 状態となる。即ち、同期信号 VD が High レベルであり、且つ、ラッチ回路 Lat 1, Lat 2 のカウント値 Lat 1 - Q, Lat 2 - Q の差分が閾値 TH より大きい場合、ラッチ回路 Lat 1 のカウント値 Lat 1 - Q がスイッチ 214 を介して画素 110 から出力される。乗算器 213 には、同期信号 VD をインバータ 207 で反転することによって得られる信号と OR 回路 211 の出力信号とが入力されるようになっている。同期信号 VD が Low レベルであり、且つ、OR 回路 211 の出力信号が High レベルである際に、乗算器 213 の出力が High レベルとなる。スイッチ 215 は、乗算器 213 から出力される信号によって制御されるようになっている。同期信号 VD が Low レベルであり、且つ、OR 回路 211 の出力信号が High レベルである際に、スイッチ 215 は ON 状態となる。即ち、同期信号 VD が Low レベルであり、且つ、ラッチ回路 Lat 1, Lat 2 のカウント値 Lat 1 - Q, Lat 2 - Q の差分が閾値 TH より大きい場合、ラッチ回路 Lat 2 のカウント値 Lat 2 - Q がスイッチ 215 を介して画素 110 から出力される。OR 回路 211 から出力される信号は、信号線 125 を介して水平選択回路 130 に入力される。ラッチ回路 Lat 1, Lat 2 のカウント値 Lat 1 - Q, Lat 2 - Q の差分が閾値 TH より大きい場合、即ち、当該画素 110 が読み出し対象の画素である場合には、OR 回路 211 から出力される High レベルの信号が水平選択回路 130 に供給される。一方、ラッチ回路 Lat 1, Lat 2 のカウント値 Lat 1 - Q, Lat 2 - Q の差分が閾値 TH 以下である場合、即ち、当該画素 110 が読み出し対象の画素でない場合、OR 回路 211 から出力される Low レベルの信号が水平選択回路 130 に供給される。こうして、当該画素 110 が読み出し対象の画素である場合には、水平選択回路 130 に例えれば “1” が記憶され、当該画素 110 が読み出し対象の画素でない場合には、水平選択回路 130 に例えれば “0” が記憶される。

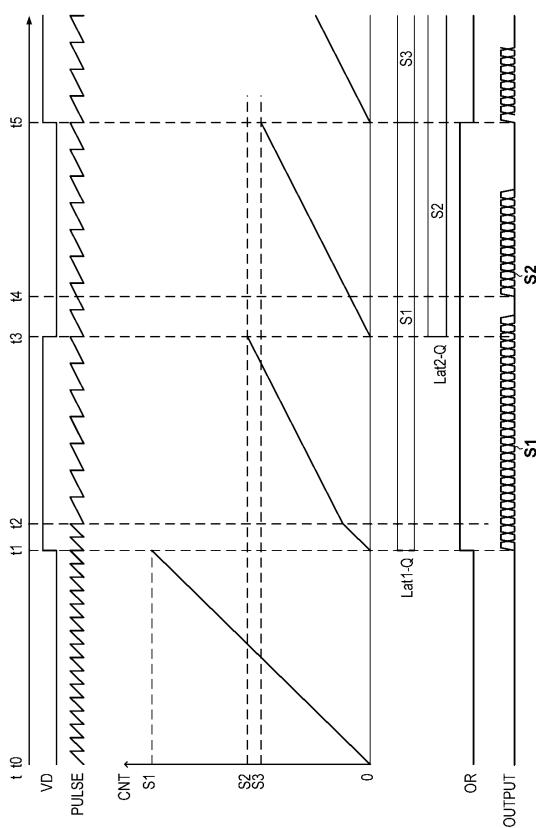

#### 【0022】

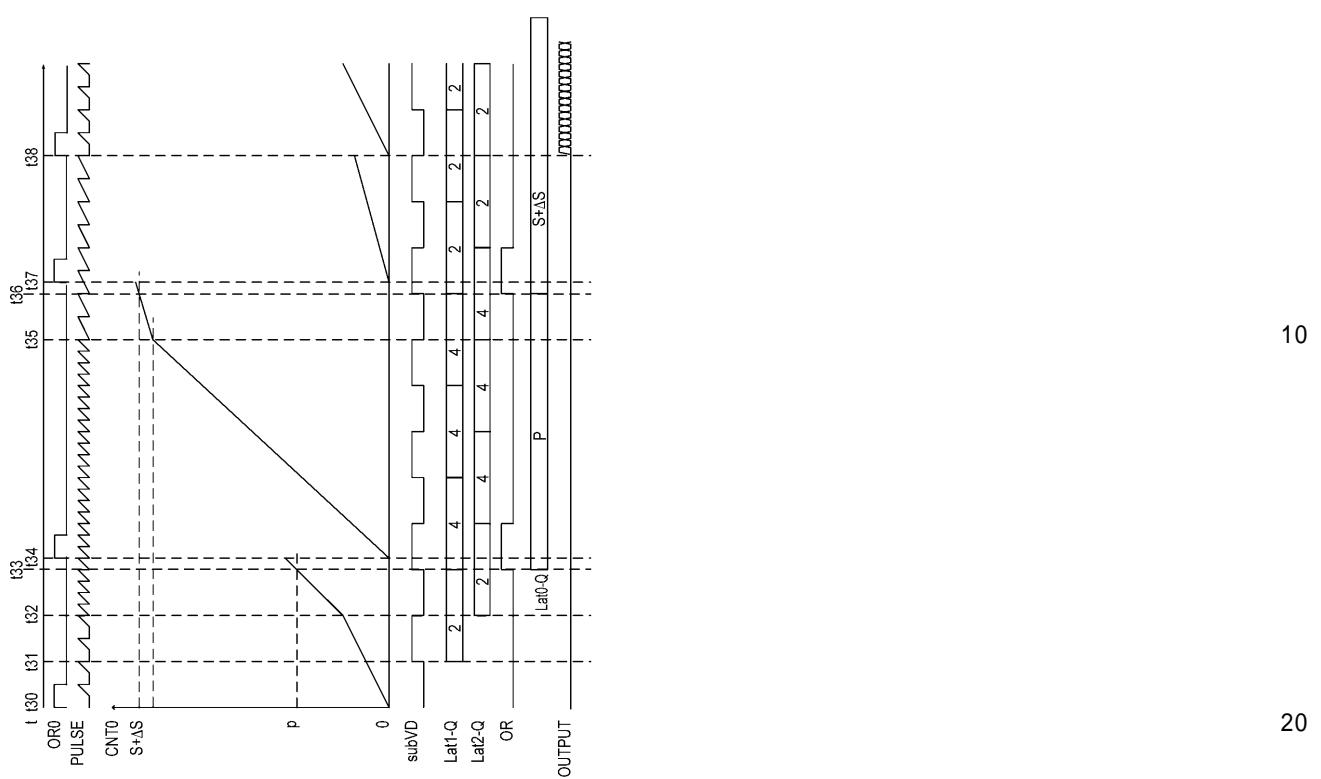

図 3 は、本実施形態による固体撮像素子の動作の例を示すタイミングチャートである。ここでは、複数の画素 110 のうちの 1 つの画素 110 の動作に着目して説明する。図 3 には、動画像を構成する複数のフレームのうちの 3 つのフレームに対応するタイミングチャートが示されている。タイミング t0 からタイミング t1 までの期間は、第 1 番目のフレームの撮影期間に対応している。タイミング t1 からタイミング t3 までの期間は、第 2 番目のフレームの撮影期間に対応している。タイミング t3 からタイミング t5 までの期間は、第 3 番目のフレームの撮影期間に対応している。タイミング t5 は、第 4 番目のフ

10

20

30

40

50

レームの撮影期間の開始のタイミングに対応している。

【0023】

図3に示すように、第1番目のフレームの撮影期間であるタイミング  $t_0$  からタイミング  $t_1$  までの期間において、同期信号  $V_D$  は  $Low$  レベルとなる。第2番目のフレームの撮影期間であるタイミング  $t_1$  からタイミング  $t_3$  までの期間において、同期信号  $V_D$  は  $High$  レベルとなる。第3番目のフレームの撮影期間であるタイミング  $t_3$  からタイミング  $t_5$  までの期間において、同期信号  $V_D$  は  $Low$  レベルとなる。第4番目のフレームの撮影期間の開始のタイミング  $t_5$  において、同期信号  $V_D$  は  $High$  レベルとなる。なお、図3に示すパルス信号  $PULSE$  は概念的に記載したものであり、パルス信号  $PULSE$  の立ち上がり波形は実際には急峻である。

10

【0024】

タイミング  $t_0$  において、カウンタ  $204$  は、パルス信号  $PULSE$  のカウントを開始する。

【0025】

タイミング  $t_1$  において、同期信号  $V_D$  が  $Low$  レベルから  $High$  レベルに変化する。ラッチ回路  $L_{at1}$  の  $G$  端子には同期信号  $V_D$  が入力されるようになっているため、タイミング  $t_1$  において、ラッチ回路  $L_{at1}$  の  $G$  端子の電位は  $Low$  レベルから  $High$  レベルに変化する。ラッチ回路  $L_{at1}$  の  $G$  端子の電位が  $Low$  レベルから  $High$  レベルに変化すると、ラッチ回路  $L_{at1}$  は、当該ラッチ回路  $L_{at1}$  の  $D$  端子に入力されているカウント値  $CNT$  を記憶する。図3に示す例では、タイミング  $t_1$  におけるカウンタ  $204$  のカウント値  $CNT$  は  $S1$  である。従って、ラッチ回路  $L_{at1}$  は、カウント値  $S1$  を画素値として記憶する。タイミング  $t_1$  は、第1番目のフレーム、即ち、最初のフレームの撮影期間の終了のタイミングであるため、ラッチ回路  $L_{at2}$  に記憶されているカウント値は  $0$  となっている。このため、ラッチ回路  $L_{at1}$  ,  $L_{at2}$  のカウント値  $L_{at1} - Q$  ,  $L_{at2} - Q$  の差分は閾値  $TH$  より大きく、OR回路  $211$  から  $High$  レベルの信号が出力される。OR回路  $211$  から出力される  $High$  レベルの信号は、水平選択回路  $130$  に供給される。OR回路  $211$  から供給される信号が  $High$  レベルであるため、水平選択回路  $130$  は、当該画素  $110$  を読み出し対象の画素として記憶する。水平選択回路  $130$  は、読み出し対象の画素  $110$  によって取得された信号が読み出されるように、適切なタイミングでスイッチ  $123$  を制御する。OR回路  $211$  から出力される  $High$  レベルの信号は、乗算器  $212$  にも供給される。同期信号  $V_D$  が  $High$  レベルであり、OR回路  $211$  から供給される信号も  $High$  レベルであるため、乗算器  $212$  の出力は  $High$  レベルとなる。乗算器  $212$  の出力が  $High$  レベルとなるため、スイッチ  $214$  が  $ON$  状態となり、ラッチ回路  $L_{at1}$  から出力されるカウント値  $S1$  を水平出力線  $120$  を介して出力部  $150$  に送信することが可能となる。OR回路  $211$  から出力される  $High$  レベルの信号は、乗算器  $213$  にも供給される。同期信号  $V_D$  を反転させることにより得られる信号が  $Low$  レベルであり、OR回路  $211$  からの信号が  $High$  レベルであるため、乗算器  $213$  の出力は  $Low$  レベルとなる。乗算器  $213$  の出力が  $Low$  レベルとなるため、スイッチ  $215$  が  $OFF$  状態となり、ラッチ回路  $L_{at2}$  のカウント値  $0$  は水平出力線  $120$  を介して出力部  $150$  に伝送されない。出力部  $150$  は、撮像部  $160$  から順次供給される信号を用いて出力信号  $OUTPUT$  を生成し、生成した出力信号  $OUTPUT$  を固体撮像素子  $100$  の外部に出力する。図3において、出力信号  $OUTPUT$  のうちに示された符号  $S1$  は、上記の説明において着目した1つの画素  $110$  から出力された信号を示している。こうして、タイミング  $t_1$  において、第1番目のフレームの撮影が完了する。そして、第1番目のフレームの画像信号の出力がタイミング  $t_1$  において開始される。

20

30

40

【0026】

図3に示す例においては、タイミング  $t_2$  において、画素  $110$  に入射する光の強度が低下している。このため、タイミング  $t_2$  より前とタイミング  $t_2$  より後とでは、単位時間あたりのカウント値  $CNT$  の増加量が異なっている。このため、タイミング  $t_3$  における

50

カウント値は、タイミング  $t_1$  におけるカウント値  $S_1$  よりも小さい  $S_2$  となる。タイミング  $t_3$  において、同期信号  $VD$  が  $HIGH$  レベルから  $LOW$  レベルに変化する。ラッチ回路  $Lat_2$  の  $G$  端子には、同期信号  $VD$  をインバータ  $207$  によって反転させることにより得られる信号が入力されるようになっているため、タイミング  $t_3$  において、ラッチ回路  $Lat_2$  の  $G$  端子の電位は  $LOW$  レベルから  $HIGH$  レベルに変化する。ラッチ回路  $Lat_2$  の  $G$  端子の電位が  $LOW$  レベルから  $HIGH$  レベルに変化すると、ラッチ回路  $Lat_2$  は、当該ラッチ回路  $Lat_2$  の  $D$  端子に入力されているカウンタ  $204$  のカウント値  $CNT$  を記憶する。このように、ラッチ回路  $Lat_1$  とラッチ回路  $Lat_2$  とは、カウンタ  $204$  のカウント値を、同期信号  $VD$  に対応する単位時間毎に交互に記憶する。タイミング  $t_3$  におけるカウンタ  $204$  のカウント値  $CNT$  は  $S_2$  である。従って、ラッチ回路  $Lat_2$  は、カウント値  $S_2$  を画素値として記憶する。タイミング  $t_3$  は、第 2 番目のフレームの撮影期間の終了のタイミングであるため、ラッチ回路  $Lat_1$  には第 1 番目のフレームの撮影期間において得られたカウント値  $S_1$  が記憶されている。ここでは、カウント値  $S_1$  とカウント値  $S_2$  との差分が閾値  $TH$  より大きい場合を例に説明する。ラッチ回路  $Lat_1, Lat_2$  のカウント値  $S_1, S_2$  の差分が閾値  $TH$  より大きいため、OR 回路  $211$  から  $HIGH$  レベルの信号が output される。OR 回路  $211$  から供給される信号が  $HIGH$  レベルであるため、水平選択回路  $130$  は、当該画素  $110$  を読み出し対象の画素として記憶する。水平選択回路  $130$  は、読み出し対象の画素  $110$  によって取得された信号が読み出されるように、適切なタイミングでスイッチ  $213$  を制御する。OR 回路  $211$  から出力される  $HIGH$  レベルの信号は、乗算器  $213$  にも供給される。同期信号  $VD$  をインバータ  $207$  で反転させることにより得られる信号が  $HIGH$  レベルであり、OR 回路  $211$  からの信号も  $HIGH$  レベルであるため、乗算器  $213$  の出力は  $HIGH$  レベルとなる。乗算器  $213$  の出力が  $HIGH$  レベルとなるため、スイッチ  $215$  が  $ON$  状態となり、ラッチ回路  $Lat_2$  から出力されるカウント値  $S_2$  を水平出力線  $120$  を介して出力部  $150$  に送信することが可能となる。OR 回路  $211$  から出力される  $HIGH$  レベルの信号は、乗算器  $212$  にも供給される。同期信号  $VD$  が  $LOW$  レベルであり、OR 回路  $211$  からの信号が  $HIGH$  レベルであるため、乗算器  $212$  の出力は  $LOW$  レベルとなる。乗算器  $212$  の出力が  $LOW$  レベルとなるため、スイッチ  $214$  が  $OFF$  状態となり、ラッチ回路  $Lat_1$  に記憶されているカウント値  $S_1$  は水平出力線  $120$  を介して出力部  $150$  に伝送されない。出力部  $150$  は、撮像部  $160$  から順次供給される信号を用いて出力信号  $OUTPUT$  を生成し、生成した出力信号  $OUTPUT$  を固体撮像素子  $100$  の外部に出力する。図 3 において、出力信号  $OUTPUT$  のうちに示された符号  $S_2$  は、上記の説明において着目した 1 つの画素  $110$  から出力された信号を示している。こうして、タイミング  $t_3$  において、第 2 番目のフレームの撮影が完了する。そして、第 2 番目のフレームの画像信号の出力がタイミング  $t_3$  以降において開始される。ここでは、第 1 番目のフレームの画像信号の出力がタイミング  $t_3$  において完了していない場合を例に説明する。このような場合、タイミング  $t_3$  よりも後のタイミング  $t_4$  において、第 2 番目のフレームの画像信号の出力が開始される。なお、第 1 番目のフレームの画像信号の出力がタイミング  $t_3$  において完了していないのは、第 1 番目のフレームについては、全ての画素  $110$  によって取得された信号を読み出すことを要するためである。第 2 番目のフレームの画像信号を読み出す際には、読み出し対象とならない画素  $110$  が生じ得る。読み出し対象とならない画素  $110$  が生じると、読み出しに要する時間は削減される。

#### 【0027】

なお、ここでは、第 1 番目のフレームの画像信号を読み出す際に、撮像部  $160$  に備えられた全ての画素  $110$  によって取得された信号を読み出す場合を例に説明したが、これに限定されるものではない。例えば、空間的に間引きを行うことにより、読み出しの対象となる画素  $110$  を減らし、第 1 番目のフレームの画像信号の読み出し時間を短縮するようにしてよい。このようにすれば、タイミング  $t_3$  よりも前の段階で、第 1 番目のフレームの画像信号の読み出しを完了することが可能となる。

#### 【0028】

10

20

30

40

50

タイミング  $t_5$  におけるカウント値は、タイミング  $t_3$  におけるカウント値  $S_2$  との差が比較的小さい  $S_3$  となる。タイミング  $t_5$  において、同期信号  $VD$  が  $Low$  レベルから  $High$  レベルに変化する。ラッチ回路  $Lat_1$  の  $G$  端子には、同期信号  $VD$  が入力されるようになっているため、タイミング  $t_5$  において、ラッチ回路  $Lat_1$  の  $G$  端子の電位は  $Low$  レベルから  $High$  レベルに変化する。ラッチ回路  $Lat_1$  の  $G$  端子の電位が  $Low$  レベルから  $High$  レベルに変化すると、ラッチ回路  $Lat_1$  は、当該ラッチ回路  $Lat_1$  の  $D$  端子に入力されているカウント値  $CNT$  を記憶する。図 3 に示す例では、タイミング  $t_5$  におけるカウント  $204$  のカウント値  $CNT$  は  $S_3$  である。従って、ラッチ回路  $Lat_1$  は、カウント値  $S_3$  を画素値として記憶する。タイミング  $t_5$  は、第 3 番目のフレームの撮影期間の終了のタイミングであるため、ラッチ回路  $Lat_2$  には第 2 番目のフレームの撮影期間において得られたカウント値  $S_2$  が記憶されている。ここでは、カウント値  $S_2$  とカウント値  $S_3$  との差分が閾値  $TH$  以下である場合を例に説明する。ラッチ回路  $Lat_1, Lat_2$  のカウント値  $S_2, S_3$  の差分が閾値  $TH$  以下であるため、OR 回路  $211$  から出力される信号は  $Low$  レベルとなる。OR 回路  $211$  から供給される信号が  $Low$  レベルであるため、水平選択回路  $130$  は、当該画素  $110$  を読み出し対象ではない画素として記憶する。水平選択回路  $130$  は、当該画素  $110$  によって取得された信号が読み出されないように、スイッチ  $123$  を制御する。OR 回路  $211$  から出力される  $Low$  レベルの信号は、乗算器  $212$  にも供給される。同期信号  $VD$  が  $High$  レベルであり、OR 回路  $211$  からの信号が  $Low$  レベルであるため、乗算器  $212$  の出力は  $Low$  レベルとなる。乗算器  $212$  の出力が  $Low$  レベルとなるため、スイッチ  $214$  が OFF 状態となり、ラッチ回路  $Lat_1$  のカウント値  $S_3$  は水平出力線  $120$  を介して出力部  $150$  に送信されない。OR 回路  $211$  から出力される  $Low$  レベルの信号は、乗算器  $213$  にも供給される。同期信号  $VD$  をインバータ  $207$  で反転することにより得られる信号が  $Low$  レベルであり、OR 回路  $211$  からの信号が  $Low$  レベルであるため、乗算器  $213$  の出力は  $Low$  レベルとなる。乗算器  $213$  の出力が  $Low$  レベルとなるため、スイッチ  $215$  が OFF 状態となり、ラッチ回路  $Lat_2$  に記憶されているカウント値  $S_2$  は水平出力線  $120$  を介して出力部  $150$  に伝送されない。出力部  $150$  は、撮像部  $160$  から順次供給される信号を用いて生成される出力信号  $OUTPUT$  を、固体撮像素子  $100$  の外部に出力する。こうして、タイミング  $t_5$  において、第 3 番目のフレームの撮影が完了する。そして、第 3 番目のフレームの画像信号の読み出しが、タイミング  $t_5$  において開始される。第 3 番目のフレームの画像信号を読み出す際にも、読み出し対象とならない画素  $110$  が生じ得るため、読み出しに要する時間は短縮される。

#### 【0029】

このように、本実施形態によれば、前フレームにおける画素値と、現フレームにおける画素値との差分が閾値以下である場合には、当該画素  $110$  を読み出し対象としない。このため、本実施形態によれば、画像信号の読み出しに要する時間を短縮することができる。

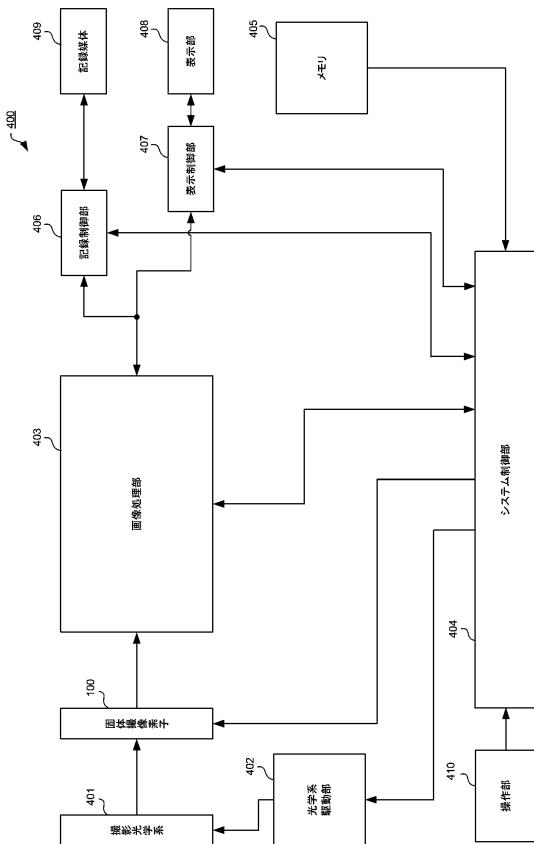

#### 【0030】

図 4 は、本実施形態による撮像装置を示すブロック図である。撮影光学系  $401$  には、フォーカスレンズ、ズームレンズ、及び、絞り等が備えられている。撮影光学系  $401$  は、被写体の光学像を形成し、形成した光学像を固体撮像素子  $100$  の撮像面に入射する。固体撮像素子  $100$  は、撮影光学系  $401$  によって形成される光学像を上記のようにして撮像する。固体撮像素子  $100$  は、撮像によって得られた出力信号  $OUTPUT$  を画像処理部  $403$  に出力する。

#### 【0031】

画像処理部  $403$  は、固体撮像素子  $100$  から出力される画像信号  $OUTPUT$  に基づいて、所定の画像処理を行う。具体的には、画像処理部  $403$  は、以下のようにして各フレームの画像を生成する。第 1 番目のフレームについては、上述したように、撮像部  $160$  に備えられた全ての画素  $110$  から画素値が読み出される。このため、画像処理部  $403$  は、読み出された全ての画素  $110$  の画素値に基づいて、第 1 番目のフレームを生成する。第 2 番目以降のフレームの読み出し処理においては、上述したように、読み出し対象と

10

20

30

40

50

ならない画素 110 が生じ得る。このため、画像処理部 403 は、読み出しが行われた画素 110 の画素値を用いて、前フレームを更新する。読み出しが行われた画素 110 に対応する部分については、画素値の更新が行われる。一方、読み出しが行われなかつた画素 110 に対応する部分については、画素値の更新は行われない。固体撮像素子 100 から出力される画像信号 OUT PUT には、読み出しが行われた画素 110 の座標 (p, q) を示す情報が含まれているため、画像処理部 403 は、読み出しが行われた画素 110 に対応する部分のみを選択的に更新する。画像処理部 403 は、画像を生成する過程において、信号の並べ替え、欠陥画素の補正、ノイズリダクション、色変換、ホワイトバランス補正、ガンマ補正、解像度変換、データ圧縮、3 面同時化、シャープネス調整等を更に行うこともできる。

10

#### 【0032】

メモリ 405 は、画像処理部 403 が演算処理等を行う際に用いられる。メモリ 405 としては、例えばDRAM (Dynamic Random Access Memory)、フラッシュメモリ等を用い得る。メモリ 405 は、連続撮影の際には、バッファメモリとしても用い得る。システム制御部 (処理部) 404 は、本実施形態による撮像装置 400 の全体の制御を司る。システム制御部 404 には、CPU (Central Processing Unit) 等が備えられている。また、システム制御部 404 は、画像処理部 403 によって処理された画像信号を、記録制御部 406 や表示制御部 407 に出力する。操作部 410 は、ボタン、スイッチ、電子ダイヤル等の操作部材によって構成される。ユーザ等が操作部 410 を操作すると、操作内容に応じた信号が操作部 410 からシステム制御部 404 に供給される。表示制御部 407 は、システム制御部 404 から供給される画像を表示部 408 に表示する。表示制御部 407 は、例えば、解像度、フレームレート、輝度域、色域等の表示フォーマットの調整を行い得る。表示制御部 407 は、8K UHDTV、4K UHDTV、HDTV 等の規格に基づく表示を行うことが可能である。表示部 408 は、撮像装置 400 の本体に備えられてもよいし、撮像装置 400 の本体とは別個であってもよい。表示部 408 が撮像装置 400 の本体と別個に設けられる場合には、表示制御部 407 と表示部 408 とが例えば接続ケーブルによって接続される。記録制御部 406 には、記録媒体 409 が装着される。記録媒体 409 としては、例えば、メモリカード等が用いられる。記録制御部 406 は、複数のフレームを含む動画

20

#### 【0033】

30

像データをMPEG方式等の公知の符号化方法によって圧縮する。そして、記録制御部 406 は、圧縮した動画像データを、exFAT ファイルシステム等のコンピュータと互換性のあるフォーマットに従って、記録媒体 409 に書き込む。光学系駆動部 402 は、撮影光学系 401 に備えられたフォーカスレンズ、ズームレンズ、絞り等の制御を行う。なお、外部装置と通信するための有線又は無線による通信インターフェースを、撮像装置 400 が更に備えるようにしてもよい。この場合、撮像装置 400 は、当該通信インターフェースを介して、生成した画像等を外部装置等に送信したり、外部装置から制御信号等を受信したりすることが可能となる。また、被写体に光を投射する光源装置を、撮像装置 400 が更に備えるようにしてもよい。この場合、当該光源装置は、例えば、同期信号 VD 等に同期してパルス状に光を発することができる。また、当該光源装置は、常時発光を行うことも可能である。当該光源装置によって被写体に光を照射し得るため、被写体をより確実に認識することが可能となる。

40

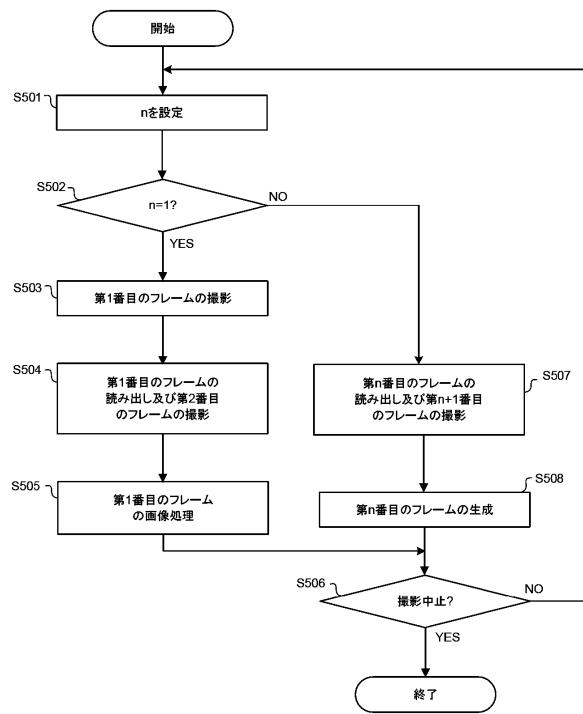

図 5 は、本実施形態による撮像装置の動作を示すフローチャートである。

#### 【0034】

ステップ S501 にて、システム制御部 404 は、n の値を設定する。n の初期値は 1 とする。

#### 【0035】

ステップ S502 において、システム制御部 404 は、n の値が 1 であるか否かを判定する。n の値が 1 である場合には (ステップ S502 において YES)、ステップ S503 に移行する。

50

## 【0036】

ステップS503において、システム制御部404は、第1番目のフレームの撮影処理を固体撮像素子100に実行させる。この後、ステップS504に移行する。

## 【0037】

ステップS504において、システム制御部404は、第1番目のフレームの読み出し処理を固体撮像素子100に実行させるとともに、第2番目のフレームの撮影処理を固体撮像素子100に実行させる。この後、ステップS505に移行する。

## 【0038】

ステップS505において、システム制御部404は、第1番目のフレームの画像処理を画像処理部403に実行させるとともに、表示部408を用いた画像の表示を表示制御部407に実行させる。この後、ステップS506に移行する。

10

## 【0039】

ステップS506において、システム制御部404は、撮影を中止するか否かを判定する。撮影を中止しない場合には（ステップS506においてNO）、ステップS501に戻る。ステップS501に戻った場合、システム制御部404は、nの値をインクリメントする。この後、ステップS502に移行する。nの値が1でない場合（ステップS502においてNO）、ステップS507に移行する。

## 【0040】

ステップS507において、システム制御部404は、第n番目のフレームの読み出し処理を固体撮像素子100に実行させるとともに、第n+1番目のフレームの撮影処理を固体撮像素子100に実行させる。

20

## 【0041】

ステップS508において、システム制御部404は、第n番目のフレームの生成処理を画像処理部403に実行させるとともに、表示部408を用いた画像の表示を表示制御部407に実行させる。第2番目以降のフレームの読み出し処理においては、上述したように、読み出し対象とならない画素110が生じ得る。このため、画像処理部403は、第n番目のフレームの読み出し処理において読み出された画素110の画素値を用いて、第n-1番目のフレームを更新することにより、第n番目のフレームを生成する。第n番目のフレームの読み出し処理において読み出された画素110に対応する部分については、画素値の更新が行われる。一方、第n番目のフレームの読み出し処理において読み出されなかった画素110に対応する部分については、画素値の更新は行われない。この後、ステップS506に移行する。

30

## 【0042】

撮影を中止する場合には（ステップS506においてYES）、図5に示す処理が終了する。

## 【0043】

このように、本実施形態によれば、単位時間あたりに検出されるパルスの数の変化が閾値THより大きい場合に、当該画素110に備えられたカウンタ204のカウント値に応じた信号が読み出される。単位時間あたりに検出されるパルスの数の変化が閾値TH以下である場合には、当該画素110に備えられたカウンタ204のカウント値に応じた信号は読み出されないため、読み出しに要する時間を短縮することができる。読み出しに要する時間を短縮することができるため、本実施形態によれば、高画素化を実現することができる、高解像度の画像を得ることが可能となる。例えば、本実施形態によれば、動きのある被写体の高解像度の動画像を得ることも可能となる。

40

## 【0044】

## [第2実施形態]

第2実施形態による固体撮像素子、撮像装置及び撮像方法を図6及び図7を用いて説明する。図1乃至図5に示す第1実施形態による固体撮像素子等と同一の構成要素には、同一の符号を付して説明を省略又は簡潔にする。

## 【0045】

50

本実施形態による固体撮像素子は、単位時間あたりに検出されるパルスの数の変化が閾値 THより大きくなつた段階で、当該画素 110に備えられたカウンタ 601のカウント値を読み出すものである。

#### 【0046】

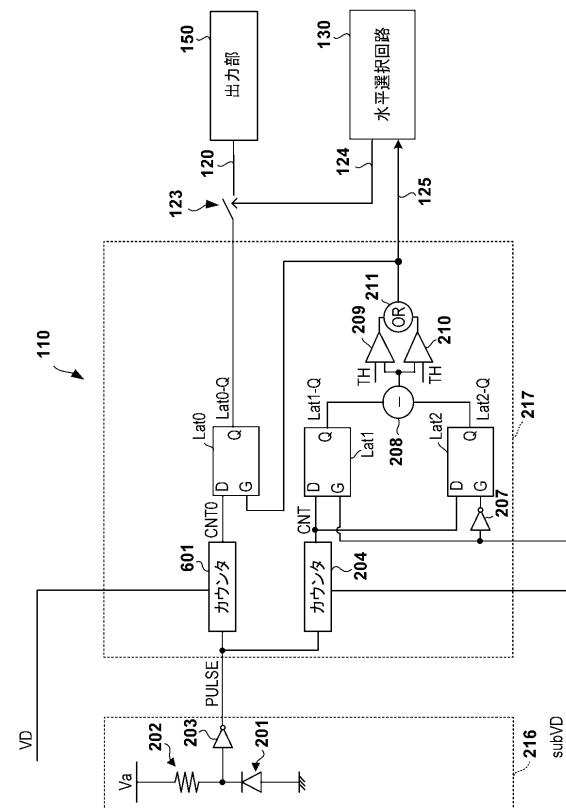

図 6 は、本実施形態による固体撮像素子を示す図である。図 6 は、本実施形態による固体撮像素子に備えられている画素 110を示している。図 6 においては、本実施形態による固体撮像素子に備えられた複数の画素 110のうちの 1つの画素 110が抜き出して示されている。

#### 【0047】

センサ部 216 には、第 1 実施形態の場合と同様に、フォトダイオード 201 と、クエンチ素子 202 と、インバータ 203 とが備えられている。計数部 217 には、カウンタ 204 と、ラッチ回路 Lat 1、Lat 2 と、インバータ 207 と、減算器 208 と、比較器 209, 210 と、OR 回路 211 と、カウンタ 601 と、ラッチ回路 Lat 0 とが備えられている。

#### 【0048】

カウンタ 204 のクロック端子及びカウンタ 601 のクロック端子には、インバータ 203 から出力されるパルス信号 PULSE が入力されるようになっている。カウンタ 204、601 は、パルス信号 PULSE のパルス数をそれぞれカウントする。カウンタ 204 のリセット端子には、同期信号 subVD が供給されるようになっている。同期信号 subVD は、図 7 に示すように、例えばデューティ比が 50% の信号である。同期信号 subVD は、同期信号 VD を分周することによって生成され得る。すなわち、同期信号 VD は、同期信号 subVD を複数倍した周期である。カウンタ 601 のリセット端子には、同期信号 VD が供給されるようになっている。本実施形態では、図 7 に示すように、パルス状の同期信号 VD が用いられる。同期信号 subVD の周期は、同期信号 VD の周期よりも短い。ここでは、説明の簡略化のため、同期信号 subVD の周期を、同期信号 VD の周期の 4 分の 1 とする場合を例に説明するが、これに限定されるものではない。カウンタ 204 は、同期信号 subVD の極性が変化した際に、カウント値 CNT を初期値、即ち、0 にリセットする。即ち、カウンタ 204 は、同期信号 subVD が Low レベルから High レベルに変化した際に、カウント値 CNT を初期値にリセットする。また、カウンタ 204 は、同期信号 subVD が High レベルから Low レベルに変化した際に、カウント値 CNT を初期値にリセットする。カウンタ 601 は、同期信号 VD のパルスの立ち上がりのタイミングで、カウント値 CNT0 を初期値、即ち、0 にリセットする。即ち、カウンタ 601 は、同期信号 VD が Low レベルから High レベルに変化した際に、カウント値 CNT0 を初期値にリセットする。カウンタ 204 のビット幅は、カウンタ 601 のビット幅よりも小さく設定されている。本実施形態において、カウンタ 204 のビット幅を、カウンタ 601 のビット幅よりも小さく設定し得るのは、同期信号 subVD の周期が、同期信号 VD の周期よりも小さいためである。同期信号 subVD の周期が、同期信号 VD の周期の例えれば 4 分の 1 である場合、カウンタ 204 のビット幅を、カウンタ 601 のビット幅より例えれば 3 減らすことができる。カウンタ 601 のビット幅が例えれば 16 である場合、カウンタ 204 のビット幅を 13 とすることができます。カウンタ 204 のビット幅を小さく設定することは、計数部 217 の小型化に寄与し、ひいては、高画素化等に寄与し得る。なお、ここでは、同期信号 subVD の周期を同期信号 VD の周期の 4 分の 1 程度とする場合を例に説明するが、これに限定されるものではない。また、ここでは、カウンタ 601 のビット幅を 16 とし、カウンタ 204 のビット幅を 13 とする場合を例に説明するが、これに限定されるものではない。カウンタ 204 の出力端子は、ラッチ回路 Lat 1, Lat 2 の D 端子に接続されている。従って、カウンタ 204 から出力されるカウント値 CNT は、ラッチ回路 Lat 1, Lat 2 の D 端子にそれぞれ入力されるようになっている。カウンタ 601 の出力端子は、ラッチ回路 Lat 0 の D 端子に接続されている。従って、カウンタ 601 から出力されるカウント値 CNT0 は、ラッチ回路 Lat 0 の D 端子に入力されるようになっている。

10

20

30

40

50

## 【0049】

ラッチ回路Lat1のG端子には、同期信号subVDが供給されるようになっている。ラッチ回路Lat2のG端子には、同期信号subVDがインバータ207を介して供給されるようになっている。ラッチ回路Lat1は、同期信号subVDがLowレベルからHighレベルに変化した際に、カウンタ204から出力されているカウント値CNTを記録する。一方、ラッチ回路Lat2は、同期信号subVDがHighレベルからLowレベルに変化した際に、カウンタ204から出力されているカウント値CNTを記録する。ラッチ回路Lat1のQ端子は、減算器208の一方の入力端子に接続されており、ラッチ回路Lat2のQ端子は、減算器208の他方の入力端子に接続されている。ラッチ回路Lat1のQ端子から出力されるカウント値Lat1-Qと、ラッチ回路Lat2のQ端子から出力されるカウント値Lat2-Qとの差分が、減算器208によって求められる。減算器208によって求められたこれらの差分(差分値)は、比較器209、210に入力されるようになっている。比較器209は、減算器208によって求められた差分値が閾値THより大きいか否かを判定し、かかる差分値が閾値THよりも大きい場合にはHighレベルの信号を出力する。比較器210は、減算器208によって求められた差分値が閾値-THより小さいか否かを判定し、かかる差分値が閾値-THよりも小さい場合にはHighレベルの信号を出力する。比較器209、210の出力端子は、OR回路211の入力端子にそれぞれ接続されている。OR回路211は、比較器209、210から出力される信号のうちの少なくともいずれかがHighレベルになると、Highレベルの信号を出力する。OR回路211から出力される信号は、ラッチ回路Lat0のG端子に入力されるようになっている。ラッチ回路Lat0は、OR回路211から出力される信号がLowレベルからHighレベルに変化した際に、カウンタ601から出力されているカウント値CNT0を記録する。ラッチ回路Lat0のQ端子は、スイッチ123を介して水平出力線120に接続されている。OR回路211から出力される信号は、信号線125を介して水平選択回路130にも入力されるようになっている。ラッチ回路Lat1、Lat2のカウント値Lat1-Q、Lat2-Qの差分が閾値THより大きい場合、即ち、当該画素110が読み出し対象の画素である場合には、OR回路211から出力されるHighレベルの信号が水平選択回路130に供給される。一方、ラッチ回路Lat1、Lat2のカウント値Lat1-Q、Lat2-Qの差分が閾値TH以下である場合、即ち、当該画素110が読み出し対象の画素でない場合には、OR回路211から出力されるLowレベルの信号が水平選択回路130に供給される。従って、当該画素110が読み出し対象の画素である場合には、水平選択回路130に例えば“1”が記憶され、当該画素110が読み出し対象の画素でない場合には、水平選択回路130に例えば“0”が記憶される。水平選択回路130は、読み出し対象の画素110によって取得された信号が読み出されるように、適切なタイミングでスイッチ123を制御する。

## 【0050】

例えば、撮影中に手振れが生じた場合には、OR回路211から出力される信号がLowレベルからHighレベルに変化し、当該タイミングにおけるカウンタ601のカウント値CNT0がラッチ回路Lat0に記憶される。従って、本実施形態によれば、手ぶれの影響が低減された画像を取得することが可能となる。

## 【0051】

また、被写体が動き始めた場合にも、OR回路211から出力される信号がLowレベルからHighレベルに変化し、当該タイミングにおけるカウンタ601のカウント値CNT0がラッチ回路Lat0に記憶される。従って、本実施形態によれば、被写体が動き出した瞬間の画像を取得することも可能となる。

## 【0052】

なお、本実施形態では、OR回路211から出力される信号がLowレベルからHighレベルに変化した時点におけるカウンタ601のカウント値が取得される。このため、本実施形態では、Auto Exposure(AE)等によって決定される正規の露光時間よりも短い露光時間の画像値が取得されることとなる。このため、取得された画素値に

10

20

30

40

50

対してゲイン補正等を行うことが好ましい。例えば、露光時間を示す情報を画像処理部403に供給するようすれば、画像処理部403等によってゲイン補正を行うことが可能である。例えば、出力部150は、読み出し対象となった画素110の座標(p, q)を示す情報とともに、当該画素110の露光時間を示す情報を出力信号OUTPUTに含ませる。なお、露光時間を示す情報は、例えば、subVD信号の極性が変化した回数に基づいて生成することが可能である。

#### 【0053】

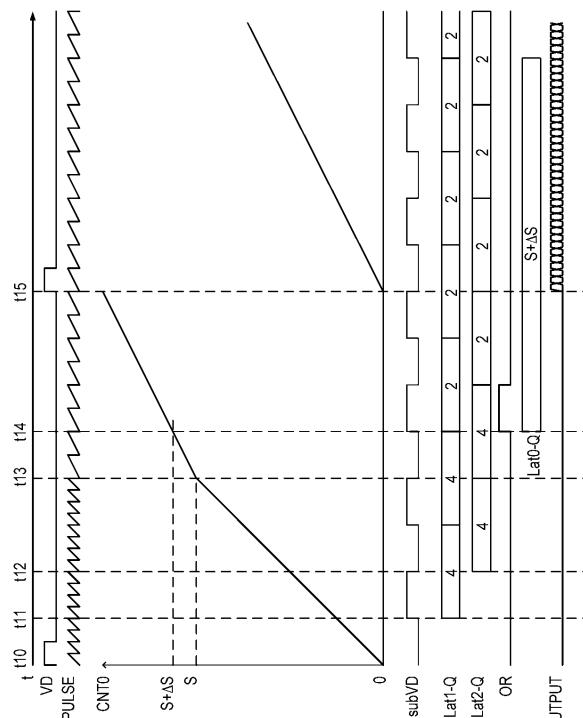

図7は、本実施形態による固体撮像素子の動作の例を示すタイミングチャートである。ここでは、複数の画素110のうちの1つの画素110の動作に着目して説明する。タイミングt10からタイミングt15までの期間、即ち、パルス状の同期信号VDが供給される間隔は、撮影期間に対応している。タイミングt15以降の期間は、読み出し期間に対応している。

10

#### 【0054】

図7に示すように、タイミングt10において、パルス状の同期信号VDが供給される。タイミングt10において、カウンタ601は、パルス信号PULSEのカウントを開始する。

#### 【0055】

タイミングt11において、同期信号subVDがLowレベルからHighレベルに変化する。ラッチ回路Lat1のG端子には同期信号subVDが入力されるようになっているため、タイミングt11において、ラッチ回路Lat1のG端子の電位はLowレベルからHighレベルに変化する。ラッチ回路Lat1のG端子の電位がLowレベルからHighレベルに変化すると、ラッチ回路Lat1は、当該ラッチ回路Lat1のD端子に入力されているカウント値CNTを記憶する。ここでは、説明を簡略化するため、カウント値CNTが4である場合を例に説明するが、これに限定されるものではない。タイミングt11におけるカウンタ204のカウント値CNTは4である。従って、ラッチ回路Lat1は、カウント値である4を記憶する。タイミングt11においては、ラッチ回路Lat2に記憶されているカウント値CNTは4であるものとする(図示せず)。このため、ラッチ回路Lat1, Lat2のカウント値Lat1-Q, Lat2-Qの差分は閾値TH以下であり、OR回路211から出力される信号はLowレベルのままである。

20

#### 【0056】

タイミングt12において、同期信号subVDがHighレベルからLowレベルに変化する。これにより、ラッチ回路Lat2のG端子の電位はLowレベルからHighレベルに変化する。ラッチ回路Lat2のG端子の電位がLowレベルからHighレベルに変化すると、ラッチ回路Lat2は、当該ラッチ回路Lat2のD端子に入力されているカウント値CNTを記憶する。タイミングt12におけるカウンタ204のカウント値CNTは4である。従って、ラッチ回路Lat2は、カウント値である4を記憶する。タイミングt12においては、ラッチ回路Lat1に記憶されているカウント値CNTは4となっている。このため、ラッチ回路Lat1, Lat2のカウント値Lat1-Q, Lat2-Qの差分は閾値TH以下であり、OR回路211から出力される信号はLowレベルである。

30

#### 【0057】

図7に示す例においては、タイミングt13において、画素110に入射する光の強度が低下している。このため、タイミングt13より前とタイミングt13より後とでは、単位時間あたりのカウント値CNT、CNT0の増加量が異なっている。このため、タイミングt14におけるカウント値CNTは、タイミングt13におけるカウント値CNTよりも小さくなる。タイミングt14において、同期信号subVDがLowレベルからHighレベルに変化し、ラッチ回路Lat1のG端子の電位がLowレベルからHighレベルに変化する。ラッチ回路Lat1のG端子の電位がLowレベルからHighレベルに変化すると、ラッチ回路Lat1は、当該ラッチ回路Lat1のD端子に入力されているカウント値CNTを記憶する。ここでは、説明を簡略化するため、タイミングt14

40

50

におけるカウンタ 204 のカウント値 CNT が 2 である場合を例に説明するが、これに限定されるものではない。タイミング t143 におけるカウンタ 204 のカウント値 CNT は 2 である。従って、ラッチ回路 Lat1 は、カウント値である 2 を記憶する。タイミング t13 においては、ラッチ回路 Lat2 に記憶されているカウント値 CNT は 4 となっている。ここでは、説明を簡略化するため、閾値 TH が 1 である場合を例に説明するが、これに限定されるものではない。ラッチ回路 Lat1, Lat2 のカウント値 Lat1 - Q, Lat2 - Q の差分が閾値 TH より大きいため、OR 回路 211 から出力される信号は Low レベルから High レベルに変化する。OR 回路 211 から供給される信号が High レベルであるため、水平選択回路 130 は、当該画素 110 を読み出し対象の画素として記憶する。水平選択回路 130 は、読み出し対象の画素 110 によって取得された信号が読み出されるように、適切なタイミングでスイッチ 123 を制御する。OR 回路 211 から出力される High レベルの信号は、ラッチ回路 Lat0 の G 端子にも供給される。ラッチ回路 Lat0 の G 端子の電位が Low レベルから High レベルに変化すると、ラッチ回路 Lat0 は、当該ラッチ回路 Lat0 の D 端子に入力されているカウント値 CNT0 を記憶する。タイミング t14 におけるカウンタ 601 のカウント値 CNT0 は、S+ S である。S は、タイミング t13 からタイミング t14 までの間におけるカウンタ 601 のカウント値 CNT0 の増加分である。同期信号 VD の周期に対して同期信号 subVD の周期を十分に小さくしておけば、S に対して十分に無視し得る程度にまで S を小さくし得る。ラッチ回路 Lat0 の Q 端子は、スイッチ 123 を介して水平出力線 120 に接続されている。ラッチ回路 Lat0 のカウント値 Lat0 - Q は、スイッチ 123 及び水平出力線 120 を介して画素 110 から出力されることとなる。

#### 【0058】

タイミング t15 以降において、出力部 150 は出力信号 OUTPUT を出力する。画像処理部 403 は、固体撮像素子 100 から出力される出力信号 OUTPUT を用いて、タイミング t15 より前の段階で既に取得しておいた画像の一部を更新する。上述したように、出力部 150 は、当該画素 110 の露光時間を示す情報を出力信号 OUTPUT に含ませる。画像処理部 403 は、当該画素 110 の露光時間を示す情報に基づいて、当該画素 110 によって取得された信号に対してゲイン補正を行う。

#### 【0059】

このように、本実施形態によれば、単位時間あたりに検出されるパルスの数の変化が閾値 TH より大きくなった段階で、当該画素 110 に備えられたカウンタ 601 のカウント値を取得する。このため、本実施形態によれば、例えば光強度の変化をトリガとして画素値を取得することができる。このため、本実施形態によれば、手ぶれの影響が低減された画像や、被写体が動き出した瞬間の画像等を取得することも可能となる。

#### 【0060】

##### [第3実施形態]

次に、本発明の第3実施形態について説明する。なお、第3実施形態は、画素の構成が、第2の実施形態と比較して、図6を参照して説明した画素 100 と異なる構成を有し、画素 100 に代えて用いられる。それ以外の構成は第2実施形態と同様であるため、以下、画素の構成及びその駆動について説明する。

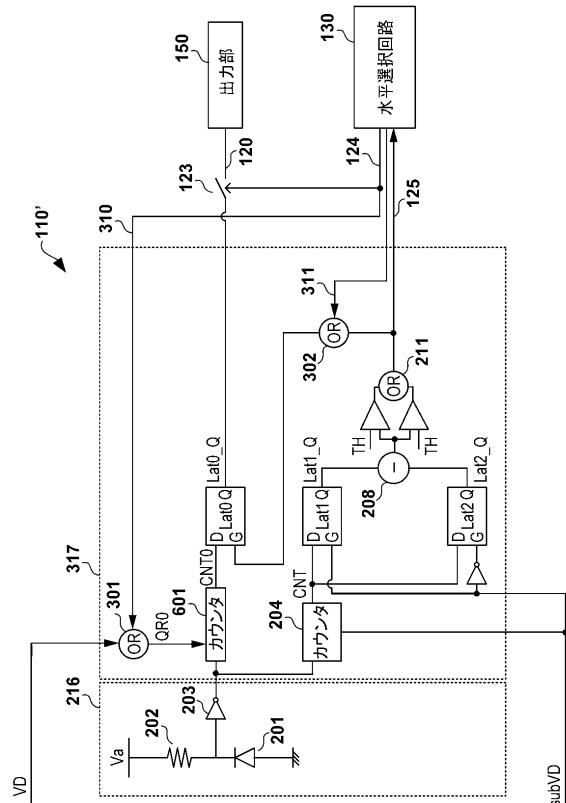

#### 【0061】

図8は、第3実施形態における画素 100' の概略構成を示す図である。なお、図8において、図6と同様の構成には同じ参照番号を付し、適宜説明を省略する。図8に示すように、本第3実施形態における画素 100' は、図6に示す構成にOR回路301及び302と、信号線 310 及び 311 が追加されたものである。OR回路 211 は、上述した実施形態で説明したように、ラッチ回路 Lat1, Lat2 のカウント値 Lat1 - Q, Lat2 - Q の差分が閾値 TH より大きくなると、信号線 125 を介して、水平選択回路 130 に High レベルの信号を出力する。

#### 【0062】

水平選択回路 130 は、信号線 310 に、信号線 125 を介して入力した OR 回路 211

10

20

30

40

50

からの信号を出力し、OR回路301は、同期信号VDと信号線310の信号とのいずれかがHighレベルである場合に、Highレベルの信号を出力する。これにより、カウンタ601は、同期信号VDがHighになるタイミング(第1のリセット動作)、または、カウント値Lat1-Q, Lat2-Qの差分が閾値THより大きくなつたタイミングから所定時間遅延した信号がHighレベルになるタイミング(第2のリセット動作)で、カウンタ601をリセットする。

#### 【0063】

また、水平選択回路130は、同期信号VDの1周期の間に、OR回路211から、Highレベルの信号が1回出力された場合に、同期信号VDによりカウンタ601がリセットされる直前のタイミングで、Highレベルの信号を信号線311に出力する。2回以上出力された場合には、出力しない。OR回路302は、OR回路211の出力と、信号線311への出力のいずれかがHighレベルである場合に、Highレベルの信号をラッチ回路Lat0のG端子に出力し、ラッチ回路Lat0は、そのときのカウント値CNT0をラッチする。これにより、後述するように、同期信号VDの1周期の間に起こつた最初の変化に応じた信号を出力することができる。

10

#### 【0064】

図9は、第3実施形態による固体撮像素子の動作の例を示すタイミングチャートである。ここでは、複数の画素110'のうちの1つの画素110'の動作に着目して説明する。なお、第3実施形態では、同期信号subVDは、デューティ比が50%、周期が同期信号VDの周期の6分の1の信号とする場合を例に説明するが、これに限定されるものではない。

20

#### 【0065】

タイミングt30からタイミングt38までの期間、即ち、パルス状の同期信号VDが供給される間隔は、撮影期間に対応している。タイミングt38以降の期間は、読み出し期間に対応している。図9に示すように、タイミングt30において、パルス状の同期信号VDが供給され、カウンタ601は、パルス信号PULSEのカウントを開始する。

#### 【0066】

タイミングt31において、同期信号subVDがLowレベルからHighレベルに変化する。ラッチ回路Lat1のG端子には同期信号subVDが入力されるようになっているため、ラッチ回路Lat1のG端子の電位はLowレベルからHighレベルに変化する。ラッチ回路Lat1のG端子の電位がLowレベルからHighレベルに変化すると、ラッチ回路Lat1は、当該ラッチ回路Lat1のD端子に入力されているカウント値CNTを記憶する。タイミングt31におけるカウンタ204のカウント値CNTが2の場合、ラッチ回路Lat1は、2を記憶する。また、タイミングt31において、ラッチ回路Lat2に記憶されているカウント値CNTが2である場合、ラッチ回路Lat1, Lat2のカウント値Lat1-Q, Lat2-Qの差分は閾値TH以下であるため、OR回路211から出力される信号はLowレベルのままである。

30

#### 【0067】

タイミングt32において、同期信号subVDがHighレベルからLowレベルに変化すると、ラッチ回路Lat2のG端子の電位がLowレベルからHighレベルに変化し、D端子に入力されているカウント値CNTを記憶する。タイミングt32におけるカウンタ204のカウント値CNTを2とすると、ラッチ回路Lat2は、2を記憶する。また、タイミングt32においては、ラッチ回路Lat1に記憶されているカウント値CNTは2であるため、カウント値Lat1-Q, Lat2-Qの差分は閾値TH以下であり、OR回路211から出力される信号はLowレベルである。

40

#### 【0068】

図9に示す例においては、タイミングt32において、画素110'に入射する光の強度が上昇している。このため、タイミングt32より前とタイミングt32より後とでは、単位時間あたりのカウント値CNT、CNT0の増加量が異なつてあり、タイミングt33におけるカウント値CNTは、タイミングt32におけるカウント値CNTよりも大きくなつた。

50

なる。また、同期信号 subVD が Low レベルから High レベルに変化し、ラッチ回路 Lat1 の G 端子の電位が Low レベルから High レベルに変化すると、ラッチ回路 Lat1 は、ラッチ回路 Lat1 の D 端子に入力されているカウント値 CNT を記憶する。タイミング t33 におけるカウンタ 204 のカウント値 CNT が、例えば、4 である場合、ラッチ回路 Lat1 は、4 を記憶する。また、タイミング t33 において、ラッチ回路 Lat2 に記憶されているカウント値 CNT は 2 である。閾値 TH が、例えば 1 である場合、カウント値 Lat1-Q, Lat2-Q の差分が閾値 TH より大きいため、OR 回路 211 から出力される信号は Low レベルから High レベルに変化する。OR 回路 211 から供給される信号が High レベルであるため、水平選択回路 130 は、当該画素 110' を読み出し対象の画素として記憶する。また、OR 回路 211 から出力された High レベルの信号は、OR 回路 302 を介してラッチ回路 Lat0 にも送られ、ラッチ回路 Lat0 は、この時点でラッチ回路 Lat0 の D 端子に入力されているカウント値 CNT を記憶する。ここでは、カウント P が記憶されるものとする。

10

#### 【0069】

一方、OR 回路 211 から出力された High レベルの信号は、水平選択回路 130 から OR 回路 301 へ送られる。これにより、OR 回路 301 の出力は、t33 から少し遅れて High レベルとなり、タイミング t34 でカウンタ 601 は 0 にリセットされる。

#### 【0070】

その後、輝度に変化無く、タイミング t35 で輝度が変化した場合、タイミング t35において、画素 110' に入射する光の強度が低下している。このため、タイミング t35 より前とタイミング t35 より後とでは、単位時間あたりのカウント値 CNT、CNT0 の増加量が異なっており、タイミング t36 におけるカウント値 CNT は、タイミング t35 におけるカウント値 CNT よりも大きくなる。また、同期信号 subVD が Low レベルから High レベルに変化し、ラッチ回路 Lat1 の G 端子の電位が Low レベルから High レベルに変化すると、ラッチ回路 Lat1 は、ラッチ回路 Lat1 の D 端子に入力されているカウント値 CNT を記憶する。タイミング t36 におけるカウンタ 204 のカウント値 CNT が、例えば、2 である場合、ラッチ回路 Lat1 は、2 を記憶する。また、タイミング t36 において、ラッチ回路 Lat2 に記憶されているカウント値 CNT は 2 である。閾値 TH が、例えば 1 である場合、カウント値 Lat1-Q, Lat2-Q の差分が閾値 TH より大きいため、OR 回路 211 から出力される信号は Low レベルから High レベルに変化する。OR 回路 211 から供給される信号が High レベルであるため、水平選択回路 130 は、当該画素 110' を読み出し対象の画素として記憶する。また、OR 回路 211 から出力された High レベルの信号は、OR 回路 302 を介してラッチ回路 Lat0 にも送られ、ラッチ回路 Lat0 は、この時点でラッチ回路 Lat0 の D 端子に入力されているカウント値 CNT を記憶する。ここでは、カウント S+ S が記憶されるものとする。

20

30

#### 【0071】

一方、OR 回路 211 から出力された High レベルの信号は、水平選択回路 130 から OR 回路 301 へ送られる。これにより、OR 回路 301 の出力は、t36 から少し遅れて High レベルとなり、タイミング t37 でカウンタ 601 は 0 にリセットされる。そして、タイミング t38 において、同期信号 VD が High レベルになると、カウンタ 601 は 0 にリセットされる。

40

#### 【0072】

図 9 に示す例では、OR 回路 211 から 2 回、High レベルの信号が出力され、カウント S+ S がラッチ回路 Lat0 に記憶されているため、水平選択回路 130 は、同期信号 VD 直前の信号は出力しない。ここで、OR 回路 211 から 1 回しか High レベルの信号が出力されなかった場合には、同期信号 VD 直前に水平選択回路 130 が High レベルの信号を信号線 311 に出力する。これにより、カウンタ 601 がリセットされる前に、カウント値 CNT0 をラッチ Lat0 に記憶することができる。

#### 【0073】

なお、同期信号 V D の 1 周期の間にカウンタ 6 0 1 がリセットされた場合、第 2 の実施形態で説明したように、露光時間を示す情報を出力信号 O U T P U T に含ませ、画像処理部 4 0 3 がゲイン補正を行う。

【 0 0 7 4 】

上記の通り第 3 実施形態によれば、単位時間あたりに検出されるパルスの数の変化が閾値 T H より大きくなった段階で、当該画素 1 1 0 ' に備えられたカウンタ 6 0 1 のカウント値をリセットし、カウントをし直す。これにより、例えば光強度の変化をトリガとして画素値を取得することができる。このため、本実施形態によれば、手ぶれの影響が低減された画像や、被写体が動き出した瞬間の画像等を取得することも可能となる。

【 0 0 7 5 】

10

[ 変形実施形態 ]

以上、好ましい実施形態について説明したが、本発明はこれらの実施形態に限定されず、その要旨の範囲内で種々の変形及び変更が可能である。

【 0 0 7 6 】

例えば、上記実施形態では、固体撮像素子 1 0 0 と別個に画像処理部 4 0 3 が備えられている場合を例に説明したが、画像処理部 4 0 3 が固体撮像素子 1 0 0 備えられていてもよい。

【 0 0 7 7 】

また、上記実施形態では、複数の画素 1 1 0 または 1 0 0 ' の各々にカウンタ 2 0 4 , 6 0 1 やラッチ回路 L a t 0 , L a t 1 , L a t 2 等が備えられている場合を例に説明したが、これに限定されるものではない。例えば、互いに隣接する複数の画素 1 1 0 または 1 0 0 ' によって、これらが共用されるようにしてもよい。

20

【 0 0 7 8 】

本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける 1 つ以上のプロセッサがプログラムを読み出し実行する処理でも実現可能である。また、1 以上の機能を実現する回路（例えば、A S I C ）によっても実現可能である。

【 符号の説明 】

【 0 0 7 9 】

1 1 0 , 1 1 0 ' ... 画素、 1 2 0 ... 水平出力線、 1 3 0 ... 水平選択回路、 1 4 0 ... 垂直選択回路、 1 5 0 ... 出力部、 1 6 0 ... 撮像部、 2 0 1 ... フォトダイオード、 2 0 2 ... クエンチ素子、 2 0 3 ... インバータ、 2 0 4 ... カウンタ、 2 1 1 , 3 0 1 , 3 0 2 ... O R 回路、 6 0 1 ... カウンタ、 L a t 0 , L a t 1 , L a t 2 ... ラッチ回路、 T H ... 閾値、 V a ... 電源電圧

30

40

50

【四面】

【 四 1 】

【 図 2 】

【 义 3 】

【図4】

10

20

30

40

50

【図 5】

【図 6】

10

20

30

40

【図 7】

【図 8】

50

【図9】

10

20

30

40

50

---

フロントページの続き

(56)参考文献 特開2015-156966(JP,A)

特表2010-510732(JP,A)

特開平07-067043(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H04N 5/335

H04N 5/3745