(19) 日本国特許庁 (JP)

(12) 公 泰 特 許 公 報(A)

(11) 特許出願公表番号

特表2004-530243

(P2004-530243A)

(43) 公表日 平成16年9月30日(2004.9.30)

(51) Int.Cl.<sup>7</sup>

F |

### テーマコード（参考）

G 11 C 29/00

G 1 1 C 29/00

671 Q

2 G 1 3 2

GO 1 R 31/28

G 1 1 C 11/34

341D

5 B O 1 5

G 1 1 C 11/401

G 1 1 C 11/34

371A

5 L 106

GO 1 R 31/28

B

5MO24

審查請求 未請求 予備審查請求 有 (全 42 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2002-578510 (P2002-578510) |

| (86) (22) 出願日 | 平成14年3月8日 (2002. 3. 8)       |

| (85) 翻訳文提出日   | 平成15年9月30日 (2003. 9. 30)     |

| (86) 國際出願番号   | PCT/US2002/007340            |

| (87) 國際公開番号   | W02002/080183                |

| (87) 國際公開日    | 平成14年10月10日 (2002. 10. 10)   |

| (31) 優先権主張番号  | 09/823, 642                  |

| (32) 優先日      | 平成13年3月30日 (2001. 3. 30)     |

| (33) 優先権主張国   | 米国 (US)                      |

(71) 出願人 591003943

インテル・コーポレーション

アメリカ合衆国 95052 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレバード・2200

(74) 代理人 100064621

弁理士 山川 政樹

(72) 発明者 トリップ、マイケル

アメリカ合衆国・97116・オレゴン州

・フォレスト グローブ・スカイ レーン

・532

(72) 発明者 マク、タク

アメリカ合衆国・94587・カリフォルニア州・ユニオン シティ・デル ベイル

プレイス・30574

(54) 【発明の名称】メモリセルの構造試験

(57) 【要約】

第1及び第2のメモリセルを第1及び第2のビット線にそれぞれ結合し、前記第1及び第2のビット線を介して前記第1及び第2のメモリセルからデータを読み込み、前記第1及び第2のビット線の電圧レベルを比較することを含むメモリセルを試験するための装置及び方法。

**【特許請求の範囲】****【請求項 1】**

第1のビット線に結合された第1のメモリセルと、

第2のビット線に結合された第2のメモリセルと、

前記第1及び第2のメモリセルに結合され、該第1及び第2のメモリセルへのアクセスを

可能にするアドレスデコーダと、

前記第1及び第2のビット線に結合され、前記第1のビット線上の前記第1のメモリセル

から及び前記第2のビット線上の前記第2のメモリセルからデータが出力されたときに、

前記第1のビット線の電圧レベルを前記第2のビット線の電圧レベルと比較するコンパレ

ータ回路と、

を備える装置。

10

**【請求項 2】**

前記アドレスデコーダがメモリアドレスの部分をデコードすることを特徴とする請求項 1

に記載の装置。

**【請求項 3】**

前記第1及び第2のメモリセルがダイナミックRAMのメモリセルであることを特徴とす

る請求項 1 に記載の装置。

**【請求項 4】**

前記第1及び第2のメモリセルがスタティックRAMのメモリセルであることを特徴とす

る請求項 1 に記載の装置。

20

**【請求項 5】**

前記コンパレータ回路が前記第1のビット線に結合された第1の入力と、前記第2のビット

線に結合された第2の入力とを備えたシングルコンパレータからなることを特徴とする

請求項 1 に記載の装置。

**【請求項 6】**

前記コンパレータの出力は、前記第1のビット線の電圧レベルが前記第2のビット線の電

圧レベルと実質的に異なることを示す表示を記憶するようにラッチに結合されていること

を特徴とする請求項 5 に記載の装置。

**【請求項 7】**

前記ラッチのトリガされる時間が調整可能であることを特徴とする請求項 6 に記載の装置

。

30

**【請求項 8】**

前記第1のビット線の電圧レベルが前記第2のビット線の電圧レベルと実質的に異なる

ことを示す表示が生じる時は何時でも、該表示をラッチするようにトリガされるスティック

-ラッチであることを特徴とする請求項 6 に記載の装置。

**【請求項 9】**

前記コンパレータ回路が、

前記第1のビット線に結合された第1の入力と前記第2のビット線に結合された第2の入

力とを有する減算回路と、

前記減算回路の出力に結合された第1のコンパレータと、

前記減算回路の出力に結合された第2のコンパレータと

を含むことを特徴とする請求項 1 に記載の装置。

40

**【請求項 10】**

前記第1のコンパレータの出力が、前記第1のビット線と前記第2のビット線の間の電圧

レベルの差が第1の基準電圧を超えることを示す表示を記憶するように第1のラッチに結合

され、

前記第2のコンパレータの出力が、前記第1のビット線と前記第2のビット線の間の電圧

レベルの差が第2の基準電圧を下回ることを示す表示を記憶するように第2のラッチに結合

される

ことを特徴とする請求項 9 に記載の装置。

50

**【請求項 1 1】**

前記第1及び第2の基準電圧が調整可能であることを特徴とする請求項10に記載の装置。

。

**【請求項 1 2】**

前記第1及び第2のラッチのトリガされる時間が調整可能であることを特徴とする請求項10に記載の装置。

**【請求項 1 3】**

前記第1及び第2のラッチが、スティックーラッチであり、その結果、前記第1のラッチは、前記第1及び第2のビット線間の電圧レベルの差が前記第1の基準電圧を超えたことを示すあらゆる表示もラッチし、前記第2のラッチは、前記第1及び第2のビット線間の電圧レベルの差が前記第2の基準電圧を下回ったことを示すあらゆる表示をもラッチすることを特徴とする請求項10に記載の装置。

10

**【請求項 1 4】**

第1及び第2のメモリセルに同じ値を書き込み、

第1のメモリセルを第1のビット線に結合し、

第2のメモリセルを第2のビット線に結合し、

前記第1及び第2のビット線をコンパレータ回路の入力に結合し、

前記第1のビット線を介して前記第1のメモリセルから、及び前記第2のビット線を介して前記第2のメモリセルから同じ値を読み出し、

前記第1及び第2のビット線の電圧レベルを比較する

ことを含む方法。

20

**【請求項 1 5】**

前記第1のビット線の電圧レベルが前記第2のビット線の電圧レベルと実質的に異なることを示す、前記コンパレータ回路からの表示をラッチすることを更に含む請求項14に記載の方法。

**【請求項 1 6】**

前記第1のビット線と前記第2のビット線間の電圧レベルの差が実質的である程度を設定することを更に含む請求項14に記載の方法。

**【請求項 1 7】**

メモリアレイ内のコンパレータ回路であって、

前記メモリアレイ内の第1のメモリセルに結合された第1のビット線に結合された第1の入力と、

前記メモリアレイ内の第2のメモリセルに結合された第2のビット線に結合された第2の入力と、

スティックーラッチに結合された出力と、

を備えるコンパレータ回路。

30

**【請求項 1 8】**

前記コンパレータ回路が、前記第2のビット線を切り離して、前記メモリアレイ内の前記第1のメモリセルに結合された第3のビット線を接続するマルチブレク

サに結合されていることを特徴とする請求項17に記載のコンパレータ回路。

40

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、従来の機能試験で可能であった以上にメモリアレイ試験を迅速化する構造的試験手法の利用に関する。

**【背景技術】****【0 0 0 2】**

多くの電子デバイスに通常使用されるメモリアレイが、益々密集してパッケージ化されるにつれ、試験は急激に複雑になり、そのため個々のセル及び他のメモリアレイ部品を完全に試験するのに時間を要するようになった。その結果、製造時の試験工程は完了するまで

50

長くかかるようになり、発見された不良をデバッグするための作業時間も長くなる。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0003】

当該技術分野における一般的な方法では、メモリアレイ内のメモリセルに対して、種々の値の組み合わせを書き込み及びメモリから読み出す機能試験を採用している。しかしながら、メモリアレイ内のメモリセルの行及び列のサイズが両方とも増大し続けており、メモリセルを適切に試験するために要求される書き込み及び読み出し動作の数が急激に増大し、これにより、このような試験を実施するために必要な時間量においても急激な増加を引き起こしている。これは、部品の製造スループットと試験適用範囲の完全性との間のトレードオフの増加に関連する問題を促進することになり、不良のメモリアレイが消費者に渡る危険性が増大する。

10

#### 【0004】

また、このような機能的試験は不良の原因を追跡するために必要な情報の多くを提供しない。セルが最後に書き込まれたもの以外の値を返したことを検出したとき、その検査の結果は、アドレスデコーダの不良か、データラッチの不良か、データラインの不良か、メモリセルの不良か、あるいはドライバの不良であるかについての表示を提供しない。従って、後続の製造を改善することができるよう、及びメモリアレイのサイズが増大し続けるに伴って、これらの追加の試験を行うために必要とされる時間も増大する、メモリアレイ内の不良を分離するための別の試験が必要である。

20

#### 【課題を解決するための手段】

#### 【0005】

本発明は、一般に利用可能なDRAM及びSRAM ICの場合のように、ダイナミックにかつランダムにアクセス可能な、行及び列で編成されたメモリセルのアレイが存在するメモリアレイに関する。しかしながら、当業者には理解されるように、本発明は、限定ではないが、消去可能なROM IC、プログラマブル・ロジックデバイス、及びマイクロプロセッサ内のアレイに編成される構成要素を含む、他の回路のアレイにも適用可能である。

20

#### 【発明を実施するための最良の形態】

#### 【0006】

本発明の目的、特徴、及び利点は、以下の詳細な説明によって当業者には理解されるであろう。

30

説明の目的のための以下の詳細な説明において、本発明を完全に理解するために多くの詳細が記載される。しかしながら、本発明を実施するためにこれらの具体的な詳細が必要でないことは当業者には明らかであろう。

#### 【0007】

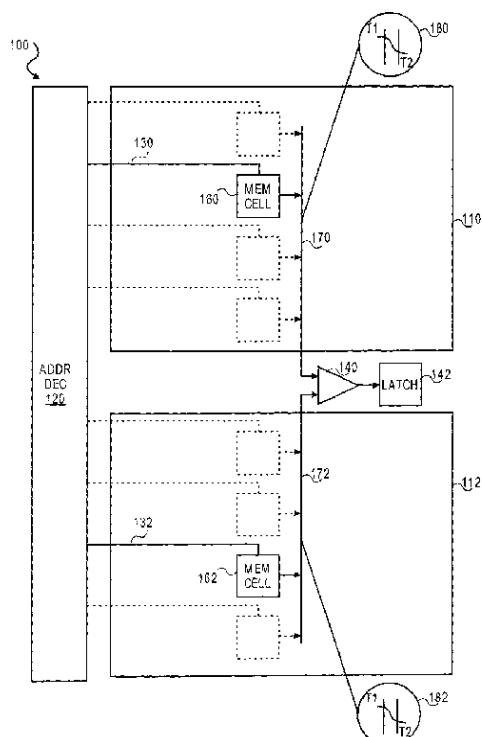

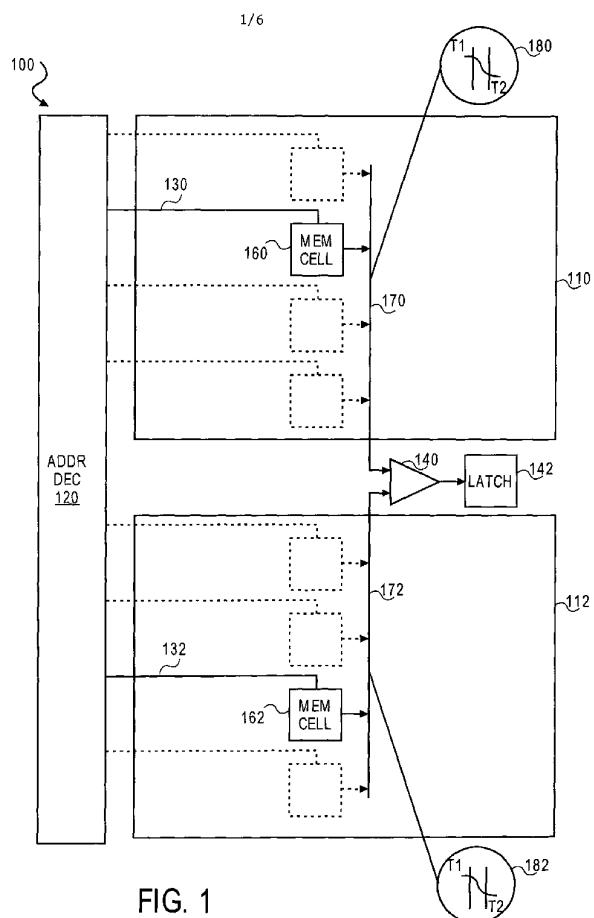

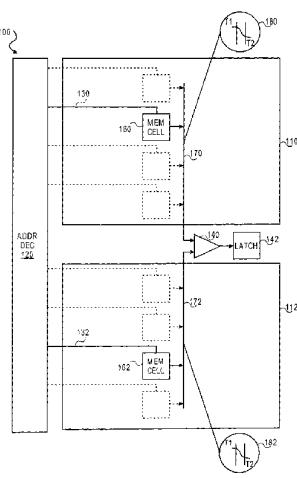

図1は本発明の一実施形態のブロック図である。メモリアレイ100は、上半部分110、下半部分112、複数のワード線（ワード線130と132を含む）を介して上半部分110と下半部分112の両方に接続されたアドレスデコーダ120、コンパレータ回路140、及びラッチ142を含むように示されている。上半部分110及び下半部分112内には、ビット線170及び172にそれぞれ接続されたメモリセル160及び162がそれぞれある。ビット線170及び172は、次いでコンパレータ回路140の入力に接続され、該コンパレータ回路は次にラッチ142に接続される。本発明の説明を明確にするために、上半部分110にはメモリセル160とビット線170だけが示され、下半部分112にはメモリセル162とビット線172だけが示されている。しかしながら、当業者には良く知られているように、典型的なメモリアレイには多くのビット線があり、それぞれのビット線にはこれに接続された多くのメモリセルがある。

40

#### 【0008】

メモリアレイ100の通常の動作の間、アドレスデコーダ120はメモリアドレスの部分をデコードし、アドレスデコーダ120を上半部分110と下半部分112とに接続する

50

ワード線の適切なものをオンにして、上半部分 110 と下半部分 112 内の適切なメモリセルにアクセスできるようにする。実行されているメモリの動作に応じて、上半部分 110 と下半部分 112 内のメモリセルに対し、メモリセルが接続されているビット線を介してデータが書き込まれ及び読み込まれる。例えば、両方のメモリセル 160 及び 162 に関連するメモリアドレスに対する書き込み動作の間、アドレスデコーダ 120 はメモリアドレスの部分をデコードし、ワード線 130 と 132 とをオンにして、ビット線 170 及び 172 を介してメモリセル 160 と 162 にアクセスできるようにする。

【0009】

本発明の一実施形態において、メモリセル 160 と 162 は、最初に各メモリセル 160 及び 162 にそれぞれビット線 170 及び 172 を介して同一のデータを書き込むことによって試験される。次に、ビット線 170 及び 172 は、それぞれ  $V_{cc}$  又は  $V_{ss}$  で表される高電圧状態又は低電圧状態にプリチャージされる。次いで、アドレスデコーダ 120 は、メモリセル 160 及び 162 に関連するメモリアドレスの部分をデコードする。次に、メモリセル 160 及び 162 は、該メモリセルのデータをビット線 170 及び 172 にそれぞれ出力する。コンパレータ回路 140 は、ビット線 170 及び 172 の電圧を連続して比較して、ビット線 170 と 172 の電圧が実質的に同じであるかどうかを示す信号を連続して発生させるシングル・コンパレータである。一実施形態において、ラッチ 142 は、試験中に 1つ又はそれ以上の所定時間でトリガされて、ビット線 170 及び 172 上でそれぞれ高から低へのサンプル変化を示す波形例 180 及び 182 の進行中の時間例  $t_1$  及び  $t_2$  のような時間におけるコンパレータ回路 140 の出力状態を捕えることができる。別の実施形態において、ラッチ 142 は、ビット線 170 及び 172 上の電圧が実質的に異なることを示すコンパレータ回路 140 からの信号のどのような発生をもラッチして記憶する「ステイツキーラッチ」として実現することができる。

【0010】

メモリアレイの通常の使用においてメモリセルを読み込むときに、ビット線を高電圧状態にプリチャージすることは一般的な方法である。従って、本発明の一実施形態において、メモリセルの試験は、メモリセルを読むときにビット線が高い状態にだけチャージされた状態で行われることになろう。しかしながら、通常用いられるメモリセルの設計によれば、プリチャージを高い状態にだけに制限すると、過度の漏れ又は他の条件に関して、メモリセルの回路の半分しか試験されない結果となる。従って本発明の別の実施形態では、ビット線が高い状態と低い状態の両方にプリチャージされた試験も含まれる。

【0011】

メモリセル 160 及び 162 を試験するためにコンパレータ回路 140 を使用することは、全く同一に設計されたビット線に接続された全く同一に設計されたメモリセルは、高い状態又は低い状態のいずれでも実質的に同じ割合で、これらのメモリセルに関連するビット線の電圧を駆動できなければならないという仮定に基づく。要するに、両方のビット線 170 及び 172 上で見られる波形（波形例 180 及び 182 のような）は実質的に同じに見えるべきである。また、コンパレータ回路のこのような使用は、メモリアレイ 100 のプロセス変動又は他の欠陥により、上半部分 110 と下半部分 112 の両方に対して同じ不良が生じることはほとんど無いという仮定に基づいており、そのため両方のメモリセル 160 と 162 が、ビット線 170 及び 172 上に見られる結果として生じたずれを有する波形が、実質的に同じに見えるようになる程同じ様態で欠陥があることになることは殆ど無い。換言すれば、粉塵や製造プロセスのエラーのような不純物は、上半部分 110 と下半部分 112 の両方に対して同様の影響を持たないことが想定され、その結果、本発明によって実行される試験では、上半部分 110 と下半部分 112 間の任意のメモリセルペア間に差が無いことを示すことになる。

【0012】

メモリアレイ 100 は、バッファ及び他の関連回路が中央に配置され、ビット線をより短くしてビット線に対してより望ましい電気特性を与えるように、当業者には周知の一般的な方法により上半部分 110 と下半部分 112 に分割されている。本発明は、この一般的

10

20

30

40

50

な方法の利点を生かして同じ中央配置を使用し、隣接するビット線の電気特性を比較するコンパレータ140のような中央配置のコンパレータ回路を設ける。しかしながら、当業者には明らかなように、このメモリアレイ100の上半部分110と下半部分112への分割は、本発明の実施には必ずしも必要ではない。本発明は、多くの他のレイアウト又はメモリアレイを含む構成要素の配置を用いて実施することができる。

【0013】

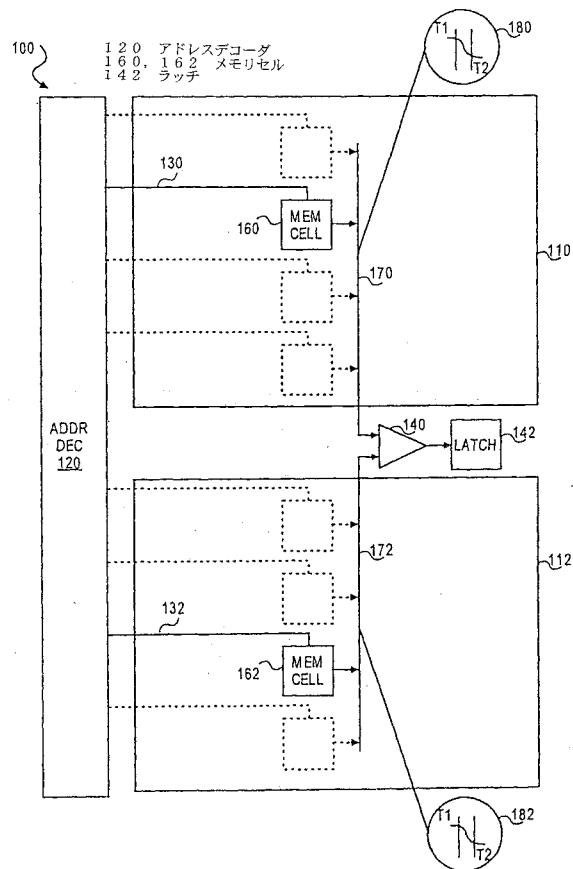

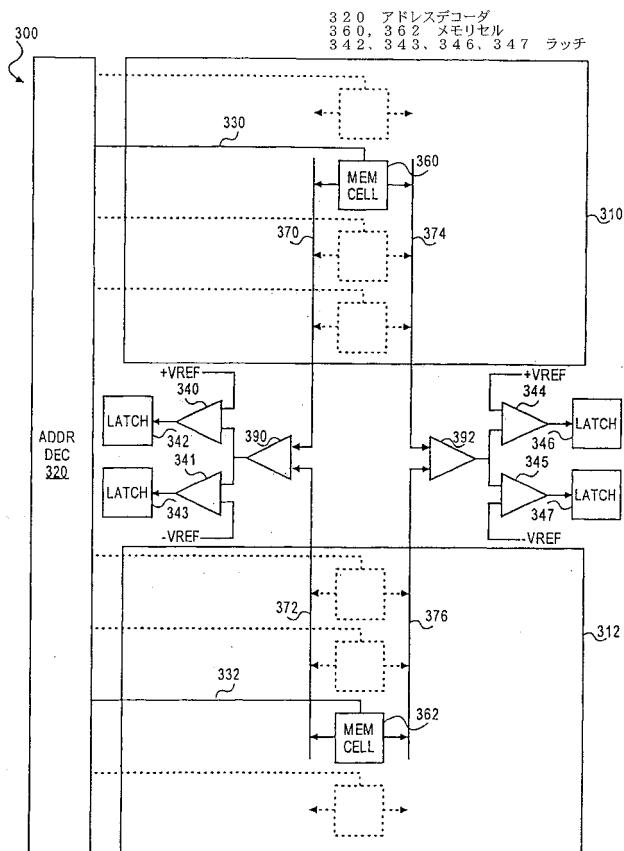

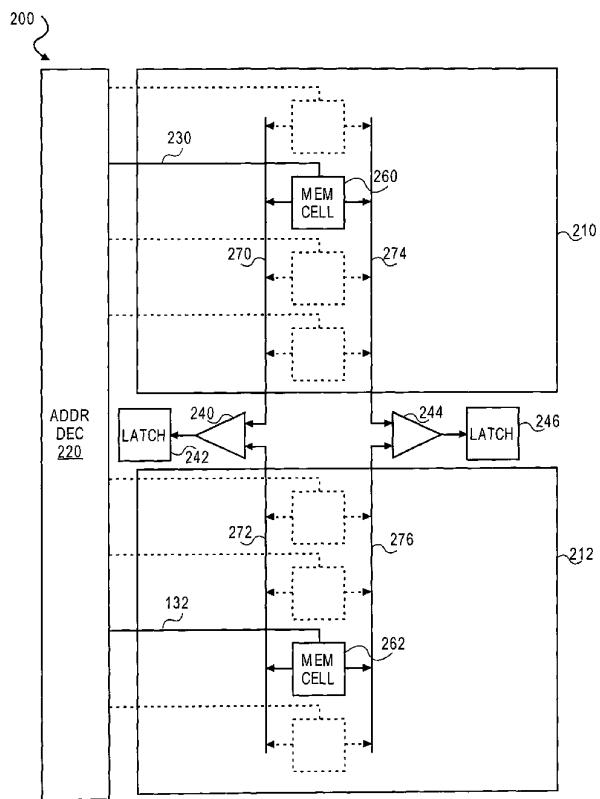

図2は本発明の別の実施形態のブロック図である。メモリアレイ200は、実質的に図1のメモリアレイ100と同等であり、図2の参照符号2××のアイテムは、図1の参照符号1××のアイテムに相当するようになっている。メモリアレイ100に対応して、メモリアレイ200は、ワード線230によって上半部分210内でメモリセル260に結合され、ワード線232によって下半部分212内でメモリセル262に結合されたアドレスデコーダ220を備えている。

【0014】

しかしながら、1つのビット線だけに各々が接続されたメモリセル160及び162と違って、メモリセル260及び262は各々1組のビット線（ビット線270と274、及びビット線272と276にそれぞれ）に接続されている。一実施形態において、各ビット線の組は各メモリセルと共に使用され、1ビットのデータとその補数を各メモリセルに書き込み、かつ読み出す。この実施形態では、1ビットのデータとその補数を読み込むために、各組のビット線をセンスアンプ上の異なる入力の組に経路付けることは一般的な方法である。しかしながら、別の実施形態では、各メモリセルに対してデータを書き込み及びセルから読み出すことが2つ（又はそれ以上）の完全に独立した経路を提供するために、2本（又は1本）のビット線が使用される。この実施形態におけるビット線のこの使用は、マルチポートメモリ構成要素が多くはこの方法で実装される結果が多い。

【0015】

メモリセル260及び262の各々に接続されたビット線の組を有する目的に関係なく、図1のメモリアレイ100のビット線170及び172に相当する方法で、ビット線270及び272はコンパレータ回路240の入力に接続され、ビット線274及び276はコンパレータ回路244の入力に接続される。また図1に対応して、コンパレータ回路240と244はラッチ242と246に接続される。

【0016】

データ及びその補数を運ぶビット線の組を使用してメモリセルに書き込み及びセルから読み出す本発明の実施形態において、メモリセル260及び262は、最初に、ビット線270と272及びビット線272と276をそれぞれ介して、各メモリセル260及び262に同じデータを書き込むことによって試験される。次に、ビット線270～276が、高い電圧状態か又は低い電圧状態のいずれかにプリチャージされる。次いで、アドレスデコーダ220は、メモリセル260及び262に関連するメモリアドレスの部分をデコードする。次に、メモリセル260及び262は、そのデータをビット線270と274、及びビット線272と276にそれぞれ出力する。コンパレータ回路240は、ビット線270と272の電圧を連続して比較して、ビット線270と272の電圧が実質的に同じであるかどうかを示す信号を連続して発生させるシングル・コンパレータである。コンパレータ回路244は、ビット線274及び276の電圧に関して同様のことを行う。一実施形態において、ラッチ242及び246は、試験中に1つ又はそれ以上の所定時間でトリガされて、これらの時間にコンパレータ回路240及び244の出力状態を捕えることができる。別の実施形態において、ラッチ242及び246はそれぞれ、これらに関連するビット線上の電圧が実質的に異なったことを示す、これらが接続されたコンパレータ回路からの信号のどのような発生をもラッチして記憶する「スティック・ラッチ」として実装することができる。

【0017】

更に、データ及びその補数を運ぶビット線の組を使用してメモリセルへ書き込み及びセルから読み出し、メモリセルからの読み出しにセンスアンプを使用する実施形態においては

、そのセンスアンプを、メモリセルを試験するためのコンパレータ回路として使用されるコンパレータとして機能せしように構成することができる。これは、別々のビット線を必要に応じて選択的に接続し又は切り離すマルチプレクサを使用することによって達成することができ、これによりセンスアンプがこれら2つの機能のいずれか一方を実行することが可能となる。或いは、別の実施形態では、センスアンプとコンパレータは別個の構成要素のままであってもよい。

【0018】

メモリセルの各々に取り付けられたビット線のいずれかを使用して、メモリセルに個別に書き込み及びセルから読み出すことができる本発明の別の実施形態においては、マルチポートメモリの場合のように、メモリセルは上述とほぼ同じ方法で試験される。しかしながら、メモリ260及び262の書き込み機能に欠陥がないことを保証するために、各メモリ260及び262の試験は2回実行され、最初にビット線270及び272を使用してメモリセル260及び262にそれぞれ同じデータを書き込み、次に同様にビット線274及び276を使用して行われる。

【0019】

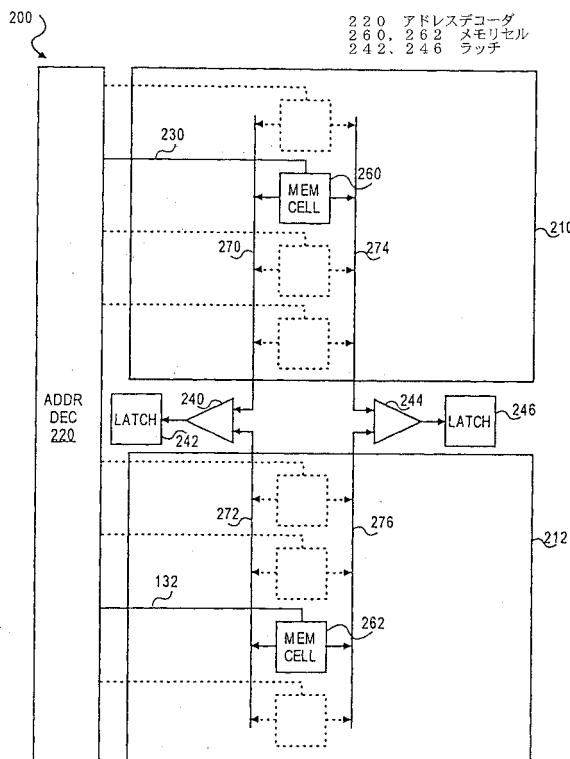

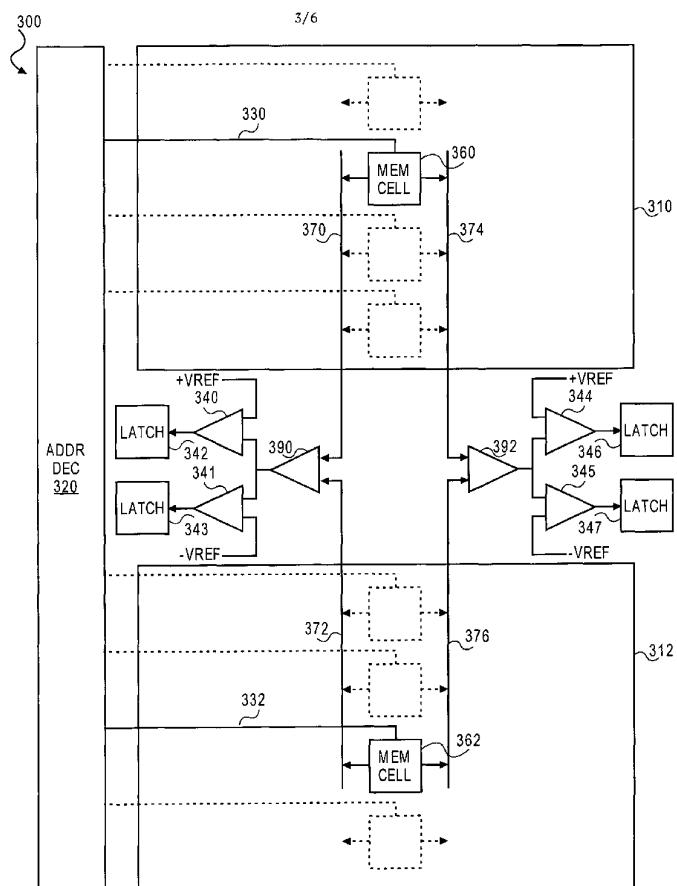

図3は本発明の更に別の実施形態のブロック図である。メモリアレイ300は図2のメモリアレイ200と実質的に同じであり、コンパレータ回路とこれに関連するラッチを除いて、図3の参照符号3××のアイテムは図2の番号2××のアイテムに相当するようになっている。メモリアレイ200に対応して、メモリアレイ300は、ワード線330によって上半部分310内でメモリセル360に結合され、ワード線332によって下半部分312内でメモリセル362に結合されたアドレスデコーダ320を備えている。同様にメモリアレイ200に対応して、メモリセル360はビット線370及び372に結合され、メモリセル362はビット線372及び376に結合される。

【0020】

図2に示された実施形態と違って、図3のコンパレータ回路は、それぞれ減算回路と1組のコンパレータから構成される。ビット線370及び372は減算回路390の入力に接続される。減算回路390は、ビット線372の一方の電圧レベルからビット線370の他方の電圧レベルを減算し、正又は負のいずれかの電圧出力とする減算の結果として生じる差を表す電圧を出力する。次に、この減算回路390の出力は、コンパレータ340及び341の各々2つの入力の一方に接続される。これに対して、ビット線374及び376は減算回路392の入力に接続され、減算回路392の出力はコンパレータ344及び345の各々2つの入力の一方に接続される。コンパレータ340及び344の各々の他方の入力は、高電圧レベル基準+vrrefに接続され、コンパレータ341及び345の各々の他方の入力は、低電圧レベル基準-vrrefに接続される。コンパレータ340、341、344、及び345はそれぞれ、ラッチ342、343、346、及び347の入力に接続される。

【0021】

メモリアレイ300のメモリセルが、1組のビット線を用いて書き込み及び読み出すようになっているか、又は各セルに接続された2つのビット線の各々が、個別に書き込み及び読み出すようになっているかに關係なく、メモリアレイ300のメモリセル360及び362の試験は、図2のメモリセル260及び262に関して上に記載された方法とほぼ同様に実行される。しかしながら、図3に示されるように各々が減算回路と1組のコンパレータからなる該コンパレータ回路の構成は、比較されている1組のビット線の電圧が互いに異なる程度を制御するより大きな能力をもたらす。より正確には、+vrrefと-vrrefとを調整することによって、コンパレータ340及び344をバイアスし、コンパレータ340又は344のいずれかが機能不良を示す信号を出力する前に、ビット線370及び372の電圧レベルを調整可能な程度まで異なるようにする。ビット線370と372間の電圧レベルの差が大きくなり+vrrefを超える場合には、コンパレータ340はラッチ342に対して+vrrefを超えたことを示す信号を出力し、ビット線370と372間の電圧レベルの差が小さくなり-vrrefを下回る場合には、コンパレータ344

10

20

30

40

50

はラッチ 346 に対して -vref を下回ったことを示す信号を出力する。

【0022】

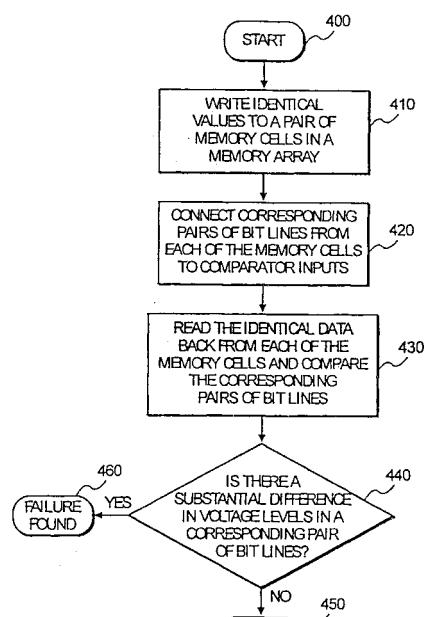

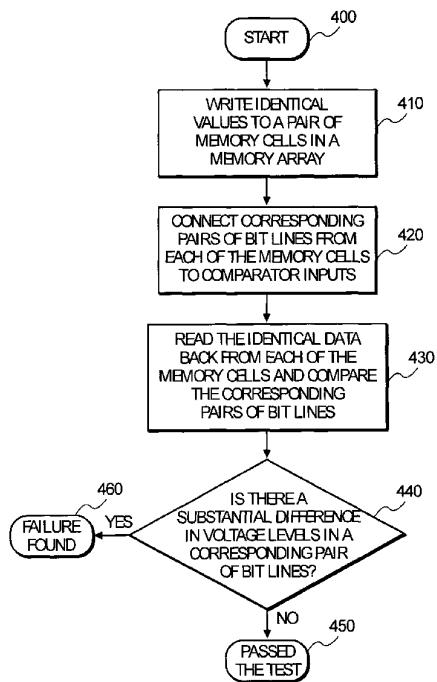

図4は本発明の一実施形態のフローチャートである。400からスタートし、410において、メモリアレイの1組のメモリセルに同じ値を書き込む。420において、この2つのメモリセルの各々から、対応するビット線の組をコンパレータ回路の入力に接続する。一実施形態において、ここでは各メモリセルが1つのビット線だけに接続されており、これは420において2つのビット線の各々をシングルコンパレータ回路の入力に接続することを意味する。或いは、各メモリセルを2つのビット線に接続する別の実施形態では、420において、1つのメモリセルからの各ビット線を、別のメモリセルからの対応するビット線と共にコンパレータ回路に接続する。

10

【0023】

430において、メモリセルの組の各々からこの同じ値を読み出し、コンパレータ回路に接続されたビット線の各対応する組を比較する。対応するビット線の組の間で電圧レベルが実質的に異なる場合には、次に460において故障が検出される。しかしながら、対応するビット線の組の間で電圧レベルに実質的な差がない場合には、メモリセルの組と、及びこれらが接続されたビット線とのこの試験は450において合格となる。

【0024】

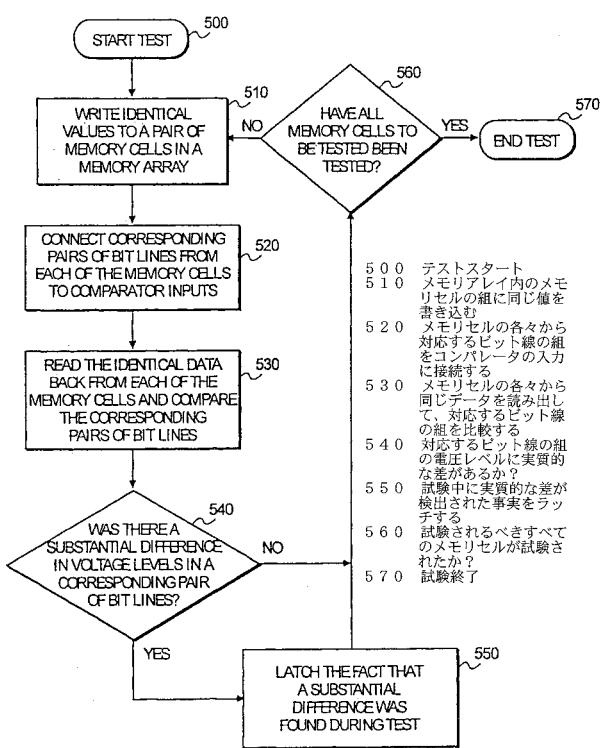

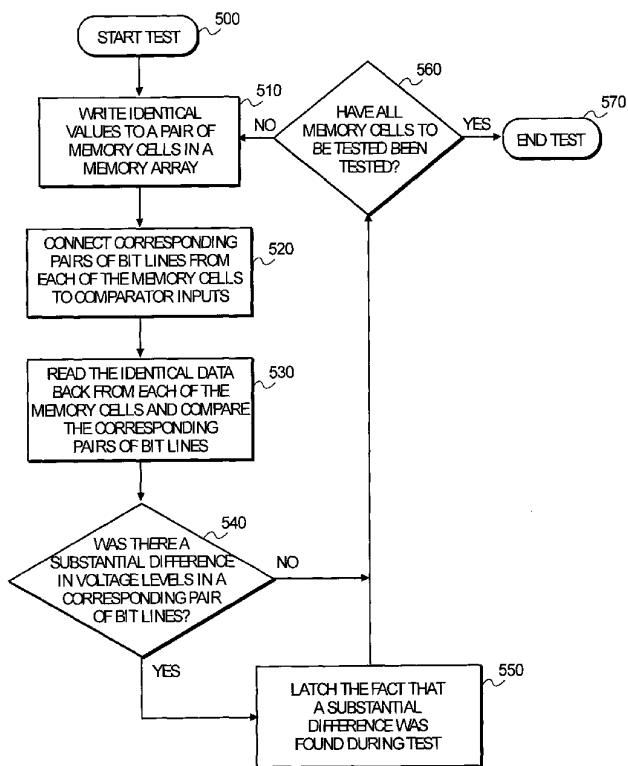

図5は本発明の別の実施形態のフローチャートである。メモリアレイにおけるメモリセルの試験は500からスタートする。510において、メモリアレイの1組のメモリセルに同じ値を書き込み、520において、メモリセルの組の各メモリセルに結合された対応するビット線の組をコンパレータ回路の入力に接続する。次に530において、メモリセルの組から該同じ値を読み出し、対応するビット線の組の電圧レベルを比較する。540において、対応するビット線の組の電圧レベルに実質的な差が検出された場合、550において、実質的な差を検出したことをラッチする。しかしながら、このような実質的な差が540で検出されたかどうかに関係なく、560において、試験されるべきメモリセルがもう存在しない場合には、試験は終了する。さもなければ、510において、メモリセルのもう別の組に対して試験を繰り返す。

20

【0025】

一実施例として、図1と図5の両方を様々に参照すると、510において、ビット線170及び172をそれぞれ使用して同じ値をメモリセル160及び162に書き込む。520において、ビット線170及び172をコンパレータ回路140の入力に接続する。530において、ビット線170及び172をそれぞれ使用して、メモリセル160及び162の両方に書き込まれた同じデータをメモリセル160及び162から読み出し、コンパレータ回路140を使用してビット線170及び172の電圧レベルを比較する。コンパレータ回路140が、ビット線170及び172間の実質的な電圧差を検出すると、ラッチ142によってこの事実の表示をラッチする。560において更にメモリセルが試験され場合には、次に510において、別の同じ値の組を別のメモリセルの組に書き込む。或いは、同じデータを読み出す一方の試験では高電圧状態にプリチャージし、同じデータを読み出す他方の試験では低電圧状態にプリチャージするビット線170及び172を用いて、メモリセル160及び162に対して試験を繰り返すことができる。

30

【0026】

別の実施例として、図2と図5の両方を様々に参照すると、メモリセル260及び262をビット線の組を用いて書き込み及び読み出す場合、特にビット線270及び272をデータの書き込み及び読み出しに使用する場合には、ビット線274及び276をデータの補数の書き込み及び読み出しに使用する。510において、同じデータをメモリセル260及び262にそれぞれ書き込むためにビット線270及び272を使用して、同じ値をメモリセル260及び262に書き込み、一方ではビット線274及び276を使用して、メモリセル260及び262にそれぞれ同じ補数データを書き込む。520において、ビット線270及び272をコンパレータ回路240の入力に接続し、ビット線274及び276はコンパレータ回路244の入力に接続する。530において、メモリセル260

40

50

0から読み出すためにビット線270及び274を使用し、メモリセル262から読み出すためにビット線272及び276を使用して、メモリセル260及び262の両方に書き込まれた同じデータと補数とを読み出す。コンパレータ回路240がデータを読み出している間に、ビット線270と272との間に実質的な電圧差を検出すると、ラッチ242によってこの事実の表示をラッチする。これに対して、コンパレータ回路244がデータの補数を読み出している間に、ビット線274と276との間に実質的な電圧差を検出すると、ラッチ244によってこの事実の表示をラッチする。560において、更にメモリセルを試験する場合には、次に510において、別の同じ値の組を別のメモリセルの組に書き込む。或いは、一方の試験においては高い状態にプリチャージし、他方の試験においては低い状態にプリチャージするビット線270、272、274、及び276を用いて、メモリセル260及び262に対して試験を繰り返すことができる。

10

## 【0027】

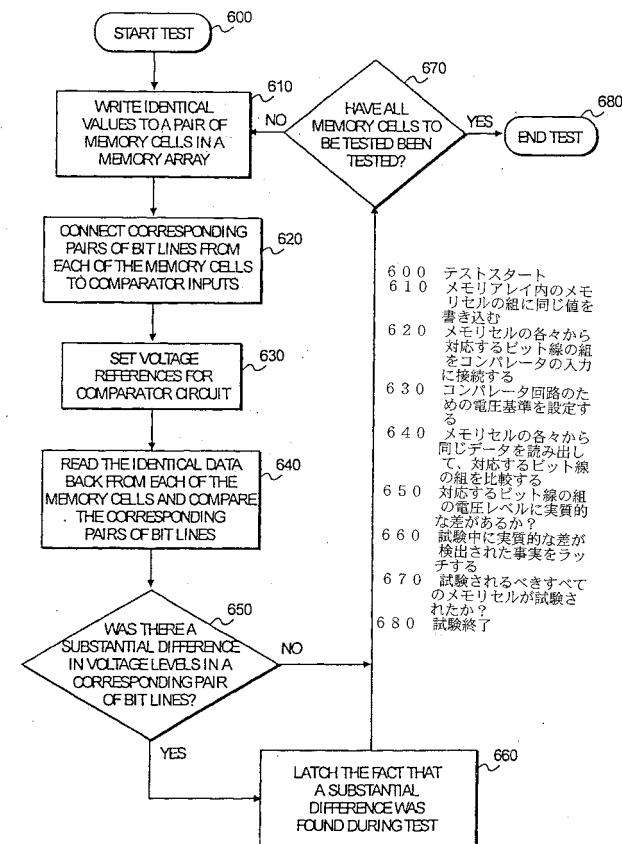

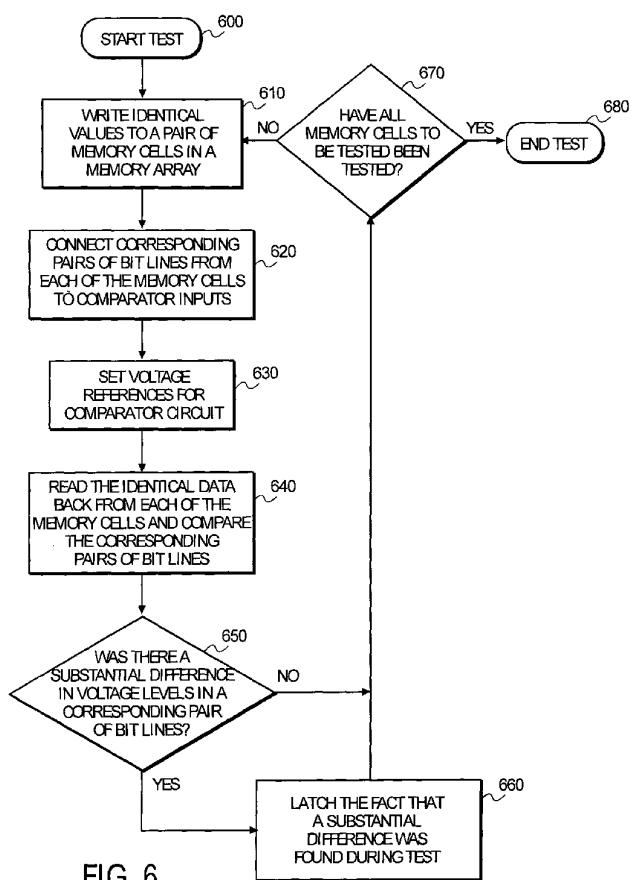

図6は、本発明の更に別の実施形態のフローチャートである。ビット線の組を使用してメモリアレイのデータ及びその補数の両方のビットを書き込み及び読み出すメモリセルの試験は600からスタートする。610において、メモリアレイの1組のメモリセルに同じ値を書き込み、620において、メモリセルの組の各メモリセルに結合された、データ及び補数データの対応するビット線の組をコンパレータ回路の入力に接続する。次に630において、コンパレータ回路によって使用される電圧基準を設定する。640において、メモリセルの組から同じ値を読み出し、データ及びその補数の対応するビット線の組の電圧レベルを比較する。650において、対応するビット線の組の電圧レベルに実質的な差が検出された場合、660において、実質的な差を検出したことをラッチする。しかしながら、このような実質的な差が650において検出されたかどうかに関係なく、670において、試験されるべきメモリセルがもう存在しない場合には、試験は終了する。さもなければ、610において、メモリセルの別の組に対して試験を繰り返す。或いは、同じデータの読み出すの間に高いプリチャージと低いプリチャージの両方でビット線を試験することが望ましい場合には、試験を繰り返すことができる。

20

## 【0028】

実施例として、図3と図6の両方を様々に参照すると、セル360及び362をビット線の組を用いて書き込み及び読み出す場合、特にビット線370及び372をデータの書き込み及び読み出しに使用する場合には、ビット線374及び376をデータの補数の書き込み及び読み出しに使用する。610において、同じデータをメモリセル360及び362にそれぞれ書き込むために、ビット線370及び372を使用して、メモリセル360及び362に同じ値を書き込み、一方ではビット線374及び376を使用して、メモリセル360及び362にそれぞれ同じ補数データを書き込む。620において、ビット線370及び372を減算回路390の入力に接続し、該減算回路はコンパレータ340及び341と共にコンパレータ回路を構成する。これに対して、ビット線374及び376を減算回路392の入力に接続し、該減算回路はコンパレータ344及び345と共にコンパレータ回路を構成する。630において、コンパレータ340及び341の入力に結合された電圧基準+ vrefと、コンパレータ344及び345の入力に結合された電圧基準- vrefを両方とも設定する。640において、以前にメモリセル360及び362に書き込まれた同じデータ及びそのデータの補数を、メモリセル360から読み出すためにビット線370及び374を用いて読み出し、メモリセル362から読み出すためにビット線372及び376を用いて読み出す。650において、対応するビット線370及び372、又はビット線374及び376の組の電圧レベルに実質的な差が検出された場合、660において、ラッチ342、343、346、又は347の適切な1つによって、この発生がラッチされる。

30

40

## 【0029】

より具体的には、減算回路390は、ビット線370の電圧をビット線372の電圧から減算し、結果として生じる差を表す電圧をコンパレータ340及び341の両方の入力に出力する。ビット線370及び372間の電圧レベルに差がある場合、減算器回路390

50

の出力は、ビット線 370 又は 372 のいずれの電圧レベルが高いかによって、負又は正のいずれかである非ゼロ電圧レベルとなる。コンパレータ 340 は減算回路 390 からのこの出力を比較し、出力の電圧レベルが +vref より高い場合、ラッチ 342 によってこのことの表示がラッチされる。同様に、コンパレータ 341 は減算回路 390 からの出力を比較し、出力の電圧レベルが -vref より低い場合、ラッチ 343 によってこのことの表示がラッチされる。これに対して、減算回路 392 は、ビット線 374 及び 376 の電圧レベル間の差を表す出力をコンパレータ 344 及び 345 の入力に与え、次に、該コンパレータは、それぞれ +vref 及び -vref に対してこの出力を比較し、この出力レベルが +vref よりも高いか、又は -vref よりも低いかのを示す表示をそれぞれラッチ 346 及び 347 によってラッチする。

10

#### 【0030】

670において、更にメモリセルを試験する場合には、次に 610において、別の同じ値の組を別のメモリセルの組に書き込む。或いは、一方の試験においては高い状態にプリチャージし、他方の試験においては低い状態にプリチャージするビット線 370、372、374、及び 376 を用いて、メモリセル 360 及び 362 に対して試験を繰り返すことができる。

#### 【0031】

本発明を好適な実施形態に関連して説明してきた。前述の説明に照らして、種々の代替、変更、変形、及び使用が当業者には理解されるであろうことは明白である。本発明が電子デバイスの他の機能に支援されて実施することができることは当業者によって理解されるであろう。

20

#### 【0032】

本発明の実施例の実施形態は、ひとつにはビット線によってアクセス可能なメモリアレイの内容で説明されている。しかしながら、本発明は広範な電子デバイス、マイクロエレクトロニクスデバイス、及びマイクロメカニカルデバイスに適用可能である。

#### 【図面の簡単な説明】

#### 【0033】

【図 1】本発明の一実施形態のプロック図である。

【図 2】本発明の別の実施形態のプロック図である。

【図 3】本発明の更に別の実施形態のプロック図である。

30

【図 4】本発明の一実施形態のフローチャートである。

【図 5】本発明の別の実施形態のフローチャートである。

【図 6】本発明の更に別の実施形態のフローチャートである。

【図1】

【図2】

【図3】

【図4】

- 400 スタート

410 メモリアレイ内のメモリセルの組に同じ値を書き込む

420 メモリセルの各々から対応するビット線の組をコンパレータの入力に接続する

430 メモリセルの各々から同じデータを読み出して、対応するビット線の組を比較する

440 対応するビット線の組の電圧レベルに実質的な差があるか?

450 試験をパス

460 故障検出

【図5】

【図6】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

10 October 2002 (10.10.2002)

PCT

(10) International Publication Number

WO 02/080183 A2

(51) International Patent Classification: G11C 29/00 (81) Designated States (national): AE, AG, AI, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CI, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SL, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW

(21) International Application Number: PCT/US02/07340

(22) International Filing Date: 8 March 2002 (08.03.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

09/823,642 30 March 2001 (30.03.2001) US

(71) Applicant: INTEL CORPORATION (US/US); 2200 Mission College Boulevard, Santa Clara, CA 95052 (US)

(72) Inventors: TRIPP, Michael; 532 Sky Lane, Forest Grove, OR 97116 (US); MAK, Tak; 30574 Del Valle Place, Union City, CA 94587 (US); SPICA, Michael; 1166 S.E. 54th Avenue, Hillsboro, OR 97123 (US).

(74) Agents: MALLIE, Michael, J.; Blakely, Sokoloff, Taylor &amp; Zafman, 7th floor, 12400 Wilshire Boulevard, Los Angeles, CA 90025 et al. (US).

(81) Designated States (regional): ARPO patent (GH, GM, KL, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NL, SN, TD, TG).

(84) Published:

— without international search report and to be republished upon receipt of that report

entirely in electronic form (except for this front page) and

available upon request from the International Bureau

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

A2

(54) Title: MEMORY CELL STRUCTURAL TEST

(57) Abstract: An apparatus and method for testing memory cells comprising coupling a first and a second memory cell to a first and a second bit lines, respectively, reading data from the first and second memory cells through the first and second bit lines, and comparing the voltage levels of the first and second bit lines.

WO 02/080183

WO 02/080183

PCT/US02/07340

## MEMORY CELL STRUCTURAL TEST

FIELD OF THE INVENTION

The present invention is related to the use of structural testing techniques

5 to speed the testing of a memory array beyond what is possible with conventional

functional tests.

ART BACKGROUND

As memory arrays commonly used in many electronic devices become

10 increasingly larger and more densely packed, the test complexity increases

exponentially, and so does the time required to thoroughly test the individual

cells and other memory array components. As a result, manufacturing test

processes take increasing longer to complete, as do efforts to debug the faults that

are found.

15 Common practice within the art is to make use of functional tests wherein

various combinations of values are written to and read back from memory cells

within a memory array. However, as both the rows and columns of memory cells

within memory arrays continue to increase in size, the number of write and read

operations required to adequately test the memory cells increases exponentially,

20 and causes a corresponding exponential increase in the amount of time required

to carry out such tests. This has prompted questions about engaging in making

increasing tradeoffs between manufacturing throughput of parts and

thoroughness of test coverage, increasing the likelihood that faulty memory

arrays will be passed on to customers.

25 Such functional tests also do not provide much in the way of information

needed to trace the source of the failure. In essence, when it is found that a cell

has returned a value other than what was last written to it, this result doesn't not

provide an indication as to whether it was an address decoder fault, a data latch

WO 02/080183

PCT/US02/07340

fault, a data line fault, a memory cell fault or a driver fault. Therefore, further tests are needed to isolate the fault within the memory array so that subsequent manufacturing yields may be improved, and as memory arrays continue to increase in size, the length of time required to perform these additional tests also increases.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The objects, features, and advantages of the present invention will be apparent to one skilled in the art in view of the following detailed description in 10 which:

Figure 1 is a block diagram of one embodiment of the present invention.

Figure 2 is a block diagram of another embodiment of the present invention.

Figure 3 is a block diagram of still another embodiment of the present 15 invention.

Figure 4 is a flow chart of one embodiment of the present invention.

Figure 5 is a flow chart of another embodiment of the present invention.

Figure 6 is a flow chart of still another embodiment of the present 20 invention.

#### DETAILED DESCRIPTION

In the following description, for purposes of explanation, numerous details are set forth in order to provide a thorough understanding of the present invention. However, it will be apparent to one skilled in the art that these specific details are not required in order to practice the present invention.

25 The present invention concerns memory arrays in which there exists an array of memory cells organized in rows and columns, wherein the memory cells are dynamically and randomly accessible, as in the case of commonly available DRAM and SRAM ICs. However, as those skilled in the art will appreciate, the

WO 02/080183

PCT/US02/07340

present invention is also applicable to arrays of other circuits, including but not limited to, erasable ROM ICs, programmable logic devices and components organized into arrays within microprocessors.

Figure 1 is a block diagram of one embodiment of the present invention.

5 Memory array 100 is depicted as comprised of top half 110, bottom half 112, address decoder 120 connected to both top half 110 and bottom half 112 via a plurality of word lines (including word lines 130 and 132), comparator circuit 140, and latch 142. Within top half 110 and bottom half 112 are memory cells 160 and 162, respectively, connected to bit lines 170 and 172, respectively. Bit lines 170

10 and 172 are in turn connected to the inputs of comparator circuit 140, which is in turn connected to latch 142. For purposes of clarity in discussing of the present invention, only memory cell 160 and bit line 170 are shown in top half 100, and only memory cell 162 and bit line 172 are shown in bottom half 112. However, as known by those skilled in the art, a typical memory array will have many bit

15 lines, each of which will have many memory cells connected to it.

During normal operation of memory array 100, address decoder 120 decodes part of a memory address and turns on appropriate ones of the word lines connecting address decoder 120 with top half 110 and bottom half 112 to enable access to appropriate memory cells within top half 110 and bottom half

20 112. Depending on the memory operation being performed, data is either written to or read from memory cells in top half 110 and bottom half 112 via the bit lines to which they are connected. For example, during a write operation to a memory address associated with both memory cells 160 and 162, address decoder 120 decodes part of the memory address and turns on word lines 130 and 132 to

25 enable access to memory cells 160 and 162 through bit lines 170 and 172, respectively.

In one embodiment of the present invention, memory cells 160 and 162 are tested by first writing identical data to each of memory cells 160 and 162 through

WO 02/080183

PCT/US02/07340

bit lines 170 and 172, respectively. Bit lines 170 and 172 are then precharged to either a high voltage state or a low voltage state, commonly referred to as Vcc or Vss, respectively. Address decoder 120 then decodes part of a memory address associated with memory cells 160 and 162. Memory cells 160 and 162 then output 5 their data onto bit lines 170 and 172, respectively. Comparator circuit 140 is a single comparator that continuously compares the voltages on bit lines 170 and 172, and continuously generates a signal indicating whether or not the voltages on bit lines 170 and 172 are substantially similar. In one embodiment, latch 142 may be triggered at one or more predetermined times during the test to capture the 10 state of the output of comparator circuit 140 at such times, such as example times t1 and t2 during the progress of example waveforms 180 and 182 showing sample high-to-low transitions on bit lines 170 and 172, respectively. In another embodiment, latch 142 could be implemented as a "sticky latch" that latches and stores any occurrence of a signal from comparator circuit 140 indicating that the 15 voltages on bit lines 170 and 172 became substantially different.

It is common practice when reading memory cells during normal use of a memory array to precharge the bit lines to a high voltage state. Therefore, in one embodiment of the present invention, the testing of the memory cells would be carried out with the bit lines being charged only to a high state when reading the 20 memory cells. However, due to commonly used memory cell designs, limiting precharging to only a high state would result in as much as half of the circuitry of a memory cell not being tested for excessive leakage or other conditions. Therefore, another embodiment of the present invention would entail testing with the bit lines precharged to both high and low states.

25 The use of comparator circuit 140 to test memory cells 160 and 162 is based on the assumption that identically designed memory cells connected to identically designed bit lines should be able to drive the voltages of their associated bit lines either high or low at a substantially similar rate. In short, the waveforms seen on

WO 02/080183

PCT/US02/07340

both bit lines 170 and 172 (such as example waveforms 180 and 182) should look substantially similar. This use of a comparator circuit is also based on the assumption of it being highly unlikely that a process variation or other defect in memory array 100 will result in identical faults to both top half 110 and bottom half 112, and so it is highly unlikely that both memory cells 160 and 162 will be defective in ways similar enough that the resulting errant waveforms seen on bit lines 170 and 172 will look substantially the same. In other words, it is presumed that an impurity, such as a dust particle or a fabrication process error, will not have identical effects on both top half 110 and bottom half 112 such that tests carried out in accordance with the present invention will reveal no differences between any pair of memory cells between top half 110 and bottom half 112.

Memory array 100 is shown as split into top half 110 and bottom half 112 in accordance with a common practice known to those skilled in the art so that buffers and other associated circuitry may be centrally located, and allowing the bit lines to be kept short to give the bit lines more desirable electrical characteristics. The present invention takes advantage of this common practice to make use of the same central location provided to centrally locate comparator circuits, such as comparator 140, to compare the electrical characteristics of adjacent bit lines. However, as will also be clear to those skilled in the art, this split of memory array 100 into top half 110 and bottom half 112 is not necessary to the practice of the present invention. The present invention may be practiced with numerous other layouts or placements of the components comprising a memory array.

Figure 2 is a block diagram of another embodiment of the present invention. Memory array 200 is substantially similar to memory array 100 of Figure 1, and items numbered with 2xx numbers in Figure 2 are meant to correspond to items numbered with 1xx numbers in Figure 1. In a manner corresponding to memory array 100, memory array 200 is comprised of address

WO 02/080183

PCT/US02/07340

decoder 220, coupled to memory cell 260 within top half 210 by word line 230, and coupled to memory cell 262 within bottom half 212 by word line 232.

However, unlike memory cells 160 and 162, which were each connected to only one bit line, memory cells 260 and 262 are each connected to a pair of bit lines (bit lines 270 and 274, and bit lines 272 and 276, respectively). In one embodiment, pairs of bit lines are used with each memory cell to write and read both a bit of data and its compliment to and from each memory cell. In this embodiment, it would be common practice to route each pair of bit lines to a pair of differential inputs on sense amplifiers for reading a bit of data and its compliment. However, in an alternate embodiment, two (or more) bit lines are used to provide two (or more) entirely independent routes by which data may be written to or read from each memory cell. This use of the bit lines in this alternate embodiment would often reflects the way in which a multiple port memory component is often implemented.

15        Regardless of the purpose for having a pair of bit lines connected to each of memory cells 260 and 262, in a manner that corresponds to bit lines 170 and 172 of memory array 100 of Figure 1, bit lines 270 and 272 are connected to the inputs of comparator circuit 240, and bit lines 274 and 276 are connected to the inputs of comparator circuit 244. Also corresponding to Figure 1, the outputs of

20        comparator circuits 240 and 244 are connected to latches 242 and 246.

In an embodiment of the present invention where memory cells are written to and read from using pairs of bit lines that carry data and its compliment, memory cells 260 and 262 are tested by first writing identical data to each of memory cells 260 and 262 through bit lines 270 and 274, and bit lines 272 and 276, respectively. Bit lines 270 through 276 are then precharged to either a high voltage state or a low voltage state. Address decoder 220 then decodes part of a memory address associated with memory cells 260 and 262. Memory cells 260 and 262 then output their data onto bit lines 270 and 274, and bit lines 272 and

WO 02/080183

PCT/US02/07340

276, respectively. Comparator circuit 240 is a single comparator that continuously compares the voltages on bit lines 270 and 272, and continuously generates a signal indicating whether or not the voltages on bit lines 270 and 272 are substantially similar. Comparator circuit 244 does the same with the voltages on 5 bit lines 274 and 276. In one embodiment, latches 242 and 246 may be triggered at one or more predetermined times during the test to capture the state of the output of comparator circuits 240 and 244 at those times. In another embodiment, latches 242 and 246 could each be implemented as a "sticky latch" that latches and stores any occurrence of a signal from the comparator circuits to which they are 10 connected indicating that voltages on their associated bit lines became substantially different.

Furthermore, in an embodiment where memory cells are written to and read from using pairs of bit lines to carry data and its compliment and sense amplifiers are used in reading from memory cells, the sense amplifiers could also 15 be configured to serve as the comparators used as the comparator circuits to test the memory cells. This could be accomplished through the use of multiplexers to selectively connect and disconnect different ones of the bit lines as needed to allow the sense amplifiers to perform one or the other of these two functions. Otherwise, in an alternate embodiment, the sense amplifiers and the comparators 20 could remain separate components.

In an alternate embodiment of the present invention where memory cells may be independently written to or read from using either of the bit lines attached to each of the memory cells, as in the case of a multiple port memory, the memory cells are tested in much the same manner just described. However, to ensure that 25 the function of writing memory cells 260 and 262 is free of defects, the testing of each of memory cells 260 and 262 would be carried out twice, first using bit lines 270 and 272 to write identical data to memory cells 260 and 262, respectively, and then again using bit lines 274 and 276.

WO 02/080183

PCT/US02/07340

Figure 3 is a block diagram of yet another embodiment of the present invention. Memory array 300 is substantially similar to memory array 200 of Figure 2, and items numbered with 3xx numbers in Figure 3 are meant to correspond to items numbered with 2xx numbers in Figure 2, with exception of 5 the comparator circuits and their associated latches. In a manner corresponding to memory array 200, memory array 300 is comprised of address decoder 320, coupled to memory cell 360 within top half 310 by word line 330, and coupled to memory cell 362 within bottom half 312 by word line 332. Also in a manner corresponding to memory array 200, memory cell 360 is coupled to bit lines 370 10 and 374, and memory cell 362 is coupled to bit lines 372 and 376.

Unlike the embodiment depicted in Figure 2, the comparator circuits of Figure 3 are each comprised of a subtracting circuit and a pair of comparators. Bit lines 370 and 372 are connected to the inputs of subtracting circuit 390. Subtracting circuit 390 subtracts the voltage level of one of bit lines 370 from the 15 voltage level of the other of bit lines 372, and outputs a voltage that represents the difference resulting from the subtraction, which could be either a positive or negative voltage output. This output of subtracting circuit 390 is, in turn, connected to one of the two inputs on each of comparators 340 and 341. Correspondingly, bit lines 374 and 376 are connected to the inputs of subtracting 20 circuit 392, and the output of subtracting circuit 392 is connected to one of the two inputs on each of comparators 344 and 345. The other input on each of comparators 340 and 344 are connected to a high voltage level reference, +vref, and correspondingly, the other input on each of comparators 341 and 345 are connected to a low voltage reference, -vref. The outputs of comparators 340, 341, 25 344 and 345 are connected to the inputs of latches 342, 343, 346 and 347, respectively.

Regardless of whether the memory cells of memory array 300 are written to and read from with a pair of bit lines, or each of the two bit lines connected to

WO 02/080183

PCT/US02/07340

each cell are meant to be used to perform independent read and write operations, the testing of memory cells 360 and 362 of memory array 300 is carried out in much the same way as was described above for memory cells 260 and 262 in Figure 2. However, the configuration of comparator circuits that are each 5 comprised of a subtracting circuit and a pair of comparators as shown in Figure 3 affords greater ability to control the degree to which the voltages on pairs of bit lines that are being compared may differ from each other. More precisely, by adjusting +vref and -vref, comparators 340 and 344 can be biased to allow the voltage levels on bit lines 370 and 372 to differ to a degree that is adjustable before 10 either comparator 340 or 344 outputs a signal indicating a malfunction. If the difference in voltage levels between bit lines 370 and 372 is such that it rises above +vref, then comparator 340 will output a signal indicating so to latch 342, and if the difference in voltage levels between bit lines 370 and 372 is such that it drops below -vref, then comparator 344 will output a signal indicating so to latch 346.

15 **Figure 4** is a flow chart of one embodiment of the present invention. Starting at 400, identical values are written to a pair of memory cells in a memory array at 410. At 420, corresponding pairs of bit lines from each of the two memory cells are connected to the inputs of a comparator circuit. In one embodiment, where each memory cell is connected to only one bit line, this would 20 mean that each of the two bit lines would be connected to the inputs of a single comparator circuit at 420. Alternatively, in another embodiment where each memory cell is connected to two bit lines, then each bit line from one memory cell is connected to a comparator circuit along with a corresponding bit line from the other memory cell at 420.

25 At 430, the identical values are read back from each of the pair of memory cells, and each corresponding pair of bit lines connected to a comparator circuit are compared. If the voltage levels differ substantially between a corresponding pair of bit lines, then a failure is found at 460. However, if there are no

WO 02/080183

PCT/US02/07340

substantially differing voltage levels between corresponding pairs of bit lines, then this test of the pair of memory cells and the bit lines to which they are connected passes at 450.

Figure 5 is a flow chart of another embodiment of the present invention.

- 5 The testing of memory cells in a memory array starts at 500. At 510, identical values are written to a pair of memory cells in a memory array, and at 520, corresponding pairs of bit lines coupled to each memory cell in the pair of memory cells are connected to the inputs of a comparator circuit. Then, at 530, the identical values are read back from the pair of memory cells, and the voltage levels of the corresponding pairs of bit lines are compared. If, at 540, a substantial difference is found in the voltage levels in a corresponding pair of bit lines, then the fact that a substantial difference was found is latched at 550. However, regardless of whether such a substantial difference was found at 540, the test ends if there are no more memory cells to be tested at 560. Otherwise, the test is 10 repeated for another pair of memory cells at 510.

- 15

By way of one example, referring variously to both Figures 1 and 5, at 510, identical values are written to memory cells 160 and 162, using bit lines 170 and 172, respectively. At 520, bit lines 170 and 172 are connected to the inputs of comparator circuit 140. At 530, the identical data written to both memory cells 20 160 and 162 is read back from memory cells 160 and 162, using bit lines 170 and 172, respectively, and the voltage levels on bit lines 170 and 172 are compared using comparator circuit 140. If comparator circuit 140 detects a substantial difference in voltage between bit lines 170 and 172, then an indication of this fact is latched by latch 142. If, at 560, more memory cells are to be tested, then at 510, 25 another pair of identical values are written to another pair of memory cells.

Alternatively, the test may be repeated for memory cells 160 and 162, with bit lines 170 and 172 being pre-charged to a high state for one test of reading back the

WO 02/080183

PCT/US02/07340

identical data, and then being pre-charged to a low state for another reading back of the identical data.

By way of another example, referring variously to both Figures 2 and 5, where memory cells 260 and 262 are written to and read from with pairs of bit lines, and specifically, where bit lines 270 and 272 are used to write and read data, while bit lines 274 and 276 are used to write and read the compliments of the data. At 510, identical values are written to memory cells 260 and 262, using bit lines 270 and 272 to write identical data to memory cells 260 and 262, respectively, while bit lines 274 and 276 are used to write identical compliment data to memory cells 260 and 262, respectively. At 520, bit lines 270 and 272 are connected to the inputs of comparator circuit 240, and bit lines 274 and 276 are connected to the inputs of comparator circuit 244. At 530, the identical data and compliments written to both memory cells 260 and 262 is read back using bit lines 270 and 274 to read back from memory cell 260, and bit lines 272 and 276 to read back from memory cell 262. If comparator circuit 240 detects a substantial difference in voltage between bit lines 270 and 272 while reading back the data, then an indication of this fact is latched by latch 242. Correspondingly, if comparator circuit 244 detects a substantial difference in voltage between bit lines 274 and 276 while reading back compliment data, then an indication of this fact is latched by latch 244. If, at 560, more memory cells are to be tested, then at 510, another pair of identical values are written to another pair of memory cells. Alternatively, the test may be repeated for memory cells 260 and 262, with bit lines 270, 272, 274 and 276 being pre-charged to a high state for one test, and then being pre-charged to a low state for the other test.

25       **Figure 6** is a flow chart of still another embodiment of the present invention. The testing of memory cells using pairs of bit lines to read and write both bits of data and their compliments in a memory array starts at 600. At 610, identical values are written to a pair of memory cells in a memory array, and at

WO 02/080183

PCT/US02/07340

620, corresponding ones of bit lines for data and complimentary data that are coupled to each memory cell in the pair of memory cells are connected to the inputs of comparator circuits. Then, at 630, voltage references used by the comparator circuits are set. At 640, the identical values are read back from the 5 pair of memory cells, and the voltage levels of the corresponding pairs of bit lines for data and their compliments are compared. If, at 650, a substantial difference is found in the voltage levels in a corresponding pair of bit lines, then the fact that a substantial difference was found is latched at 660. However, regardless of whether such a substantial difference was found at 650, the test ends if there are 10 no more memory cells to be tested at 670. Otherwise, the test is repeated for another pair of memory cells at 610. Alternatively, the test may also be repeated if it is desired to test the bit lines with both a high and a low pre-charging during the reading back of the identical data.

By way of example, referring variously to both Figures 3 and 6, where 15 memory cells 360 and 362 are written to and read from with pairs of bit lines, and specifically, where bit lines 370 and 372 are used to write and read data, while bit lines 374 and 376 are used to write and read the compliments of the data. At 610, identical values are written to memory cells 360 and 362, using bit lines 370 and 372 to write identical data to memory cells 360 and 362, respectively, while bit 20 lines 374 and 376 are used to write identical compliment data to memory cells 360 and 362, respectively. At 620, bit lines 370 and 372 are connected to the inputs of subtracting circuit 390, which together with comparators 340 and 341, comprise a comparator circuit. Correspondingly, bit lines 374 and 376 are connected to the inputs of subtracting circuit 392, which together with comparators 344 and 345, 25 also comprise a comparator circuit. At 630, voltage reference +vref, which is coupled to inputs of comparators 340 and 341, and voltage reference -vref, which is coupled to inputs of comparators 344 and 345, are both set. At 640, the identical data and compliments of that data earlier written to both memory cells 360 and

WO 02/080183

PCT/US02/07340

362 is read back, using bit lines 370 and 374 to read back from memory cell 360, and bit lines 372 and 376 to read back from memory cell 262. At 650, if a substantial difference was found in the voltage levels of corresponding pairs of bit lines 370 and 372 or bit lines 374 and 376, then at 660, the occurrence of this is

- 5 latched by the appropriate one of latches 342, 343, 346 or 347.

More specifically, subtractor circuit 390 subtracts the voltage on bit line 370 from bit line 372, and outputs a voltage representing the resulting difference to the inputs of both comparators 340 and 341. If there is a difference in the voltage levels between bit lines 370 and 372, then the output of subtractor circuit 390 will

10 be a non-zero voltage level that will be either negative or positive depending on which of bit lines 370 or 372 have the higher voltage level. Comparator 340 compares this output from subtracting circuit 390, if the voltage level of the output is higher than +vref, then an indication that this is so is latched by latch 342. Similarly, comparator 341 compares the output from subtracting circuit 390,

15 and if the voltage level of the output is lower than -vref, then an indication that this is so is latched by latch 343. Correspondingly, subtracting circuit 392 provides an output representing the difference between the voltage levels of bit lines 374 and 376 to the inputs of comparators 344 and 345, which in turn, compare this output to +vref and -vref, respectively, and any indication that the

20 voltage level of this output has risen above +vref or dropped below -vref is latched by latches 346 and 347, respectively.

If, at 670, more memory cells are to be tested, then at 610, another pair of identical values are written to another pair of memory cells. Alternatively, the test may be repeated for memory cells 360 and 362, with bit lines 370, 372, 374 and

25 376 being pre-charged to a high state for one test, and then being pre-charged to a low state for the other test.

The invention has been described in conjunction with the preferred embodiment. It is evident that numerous alternatives, modifications, variations

WO 02/080183

PCT/US02/07340

and uses will be apparent to those skilled in the art in light of the foregoing description. It will be understood by those skilled in the art, that the present invention may be practiced in support of other functions in an electronic device.

The example embodiments of the present invention are described in the context of an array of memory cells accessible, in part, by bit lines. However, the present invention is applicable to a variety of electronic, microelectronic and micromechanical devices.

WO 02/080183

PCT/US02/07340

CLAIMS

What is claimed is:

1. An apparatus, comprising:

- a first memory cell coupled to a first bit line;

- 5 a second memory cell coupled to a second bit line;

- an address decoder coupled to the first and second memory cells to enable access to the first and second memory cells; and

- a comparator circuit coupled to the first and second bit lines to compare the voltage level on the first bit line with the voltage level on the second bit at a time

- 10 when data is output from the first memory cell on the first bit line and from the second memory cell on the second bit line.

2. The apparatus of claim 1, wherein the address decoder decodes part of a memory address.

3. The apparatus of claim 1, wherein the first and second memory cells

15 are dynamic RAM memory cells.

4. The apparatus of claim 1, wherein the first and second memory cells

are static RAM memory cells.

5. The apparatus of claim 1, wherein the comparator circuit is

comprised of a single comparator with a first input coupled to the first bit line and

20 a second input coupled to the second bit line.

6. The apparatus of claim 5, wherein the output of the comparator is

coupled to a latch to store an indication that the voltage level on the first bit line

differs substantially from the voltage level on the second bit line.

7. The apparatus of claim 6, wherein the time at which the latch is triggered is adjustable.

8. The apparatus of claim 6, wherein the latch is a sticky latch that is triggered to latch an indication that the voltage level on the first bit line differs substantially from the voltage level on the second bit line at any time that such an indication takes place.

9. The apparatus of claim 1, wherein the comparator circuit is comprised of:

a subtracting circuit with a first input coupled to the first bit line and a second input coupled to the second bit line;

10 a first comparator coupled to the output of the subtracting circuit; and

a second comparator coupled to the output of the subtracting circuit.

10. The apparatus of claim 9, wherein:

the output of the first comparator is coupled to a first latch to store an indication that difference in voltage levels between the first bit line and the second bit line has risen above a first reference voltage; and

the output of the second comparator is coupled to a second latch to store an indication that the difference in voltage levels between the first bit line and the second bit line has dropped below a second reference voltage.

20

20 11. The apparatus of claim 10, wherein the first and second reference voltages are adjustable.

12. The apparatus of claim 10, wherein the time at which the first and second latches are triggered is adjustable.

WO 02/080183

PCT/US02/07340

13. The apparatus of claim 10, wherein the first and second latches are sticky latches such that the first latch will latch any indication that the differences in voltage level between the first and second bit lines has risen above the first voltage reference and the second latch will latch any indication that the differences in voltage level between the first and second bit lines has dropped below the second reference voltage.

14. A method, comprising:

writing identical values to the first and second memory cells;

coupling a first memory cell to a first bit line;

10 coupling a second memory cell to a second bit line;

coupling the first and second bit lines to inputs of a comparator circuit;

reading the identical values from the first memory cell through the first bit line and from the second memory cell through the second bit line;

comparing the voltage levels on the first and second bit lines.

15. 15. The method of claim 14, further comprising latching an indication from the comparator circuit that the voltage level of the first bit line differs substantially from the voltage level of the second bit line.

16. The method of claim 14, further comprising setting the degree to which the difference in voltage levels between the first bit line and the second bit line is substantial.

17. A comparator circuit in a memory array comprising:

a first input coupled to a first bit line that is coupled to a first memory cell in the memory array;

WO 02/080183

PCT/US02/07340

a second input coupled to a second bit line that is coupled to a second memory cell in the memory array; and an output coupled to a sticky latch.

18. The comparator circuit of claim 17, wherein the comparator circuit is coupled to a multiplexer to disconnect the second bit line, and to connect a third bit line that is coupled to the first memory cell in the memory array.

WO 02/080183

PCT/US02/07340

2/6

FIG. 2

WO 02/080183

PCT/US02/07340

FIG. 3

4/6

FIG. 4

FIG. 5

6/6

## 【国際公開パンフレット（コレクトバージョン）】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

10 October 2002 (10.10.2002)

PCT

(10) International Publication Number

WO 02/080183 A3

(51) International Patent Classification: G11C 29/00

(74) Agents: MALLIE, Michael, J.; Blakely, Sokoloff, Taylor &amp; Zafman, 7th floor, 12400 Wilshire Boulevard, Los Angeles, CA 90025 et al. (US).

(21) International Application Number: PCT/US02/07340

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DV, EC, EH, ES, H, GB, GD, GH, GH, GM, HR, HU, ID, IL, IN, IS, JP, KR, KG, KP, KR, KZ, L, C, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(22) International Filing Date: 8 March 2002 (08.03.2002)

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SI, SZ, TZ, UG, ZM, ZW); Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM); European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BJ, BJ, CI, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 09/823,642 30 March 2001 (30.03.2001) US

(54) Title: MEMORY CELL STRUCTURAL TEST

(71) Applicant: INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

(72) Inventors: TRIPP, Michael; 532 Sky Lane, Forest Grove, OR 97116 (US), MAK, Tak; 30574 Del Valle Place, Union City, CA 94587 (US), SPICA, Michael; 1166 SE 54th Avenue, Hillsboro, OR 97123 (US).

[Continued on next page]

WO 02/080183 A3

(57) Abstract: An apparatus and method for testing memory cells comprising coupling a first and a second memory cell to a first and a second bit lines, respectively, reading data from the first and second memory cells through the first and second bit lines, and comparing the voltage levels of the first and second bit lines.

---

**WO 02/080183 A3****Published:**

— with international search report*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.***(88) Date of publication of the international search report:**

17 April 2003

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                   | International Application No<br>PCT/US 02/07340                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 G11C29/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 G11C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, PAJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |                                                                                |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Citation of document, with indication, where appropriate, of the relevant passages                                                | Relevant to claim No.                                                          |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DE 199 08 513 A (SAMSUNG ELECTRONICS CO LTD) 2 December 1999 (1999-12-02)<br>abstract<br>column 4, line 35 - line 47; figures 1,2 | 1,14,15,<br>17                                                                 |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | US 6 064 601 A (KIM BYUNG-CHUL ET AL)<br>16 May 2000 (2000-05-16)<br>column 1, line 50 -column 2, line 31;<br>figures 2,3         | 2,3                                                                            |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | US 5 894 445 A (KOBAYASHI TATSUJI)<br>13 April 1999 (1999-04-13)<br>column 2, line 14 - line 37; figure 1                         | 1-18                                                                           |

| <input type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| <p>* Special categories of cited documents:</p> <p>*A* document defining the general state of the art which is not considered to be of particular relevance</p> <p>*E* earlier document, but published on or after the international filing date</p> <p>*I* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another document (other special reasons, as specified)</p> <p>*C* document relating to an oral disclosure, use, exhibition or other means</p> <p>*P* document published prior to the international filing date but later than the priority date claimed</p> <p>*T* later document published after the international filing date or priority date and not in conflict with the application but which nevertheless may be of interest in understanding the invention</p> <p>*X* document of particular relevance; the claimed invention can be considered to involve an inventive step when the document is taken alone</p> <p>*Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is taken in combination with one or more other documents, such combination being obvious to a person skilled in the art</p> <p>*G* document member of the same patent family</p> |                                                                                                                                   |                                                                                |

| Date of the actual completion of the international search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Date of mailing of the international search report                                                                                |                                                                                |