#### ROYAUME DE BELGIQUE

# BREVET D'INVENTION

MINISTERE DES AFFAIRES ECONOMIQUES

NUMERO DE PUBLICATION: 1001065A3

NUMERO DE DEPOT: 8701347

Classif. Internat.: G06F

Date de délivrance : 27 Juin

1989

#### Le Ministre des Affaires Economiques,

Vu la Convention de Paris du 20 Mars 1883 pour la Protection de la propriété industrielle;

Vu la loi du 28 Mars 1984 sur les brevets d'invention, notamment l'article 22;

Vu l'arrêté royal du 2 Décembre 1986 relatif à la demande, à la délivrance et au maintien en vigueur des brevets d'invention, notamment l'article 28;

Vu le procès verbal dressé le 26 Novembre 1987 à 15h30 à 1'Office de la Propriété Industrielle

# ARRETE:

ARTICLE 1.- Il est délivré à : INTERNATIONAL BUSINESS MACHINES CORPORATION Armonk, NEW YORK 10504(ETATS-UNIS D'AMERIQUE)

représenté(e)(s) par : VOSSWINKEL Philippe, BUREAU GEVERS S.A., Rue de Livourne 7 - 1050 BRUXELLES.

un brevet d'invention d'une durée de 20 ans, sous réserve du paiement des taxes annuelles, pour : CONVERSION DU MODE DE SIGNAUX DE COMMANDE POUR ORDINATEURS.

INVENTEUR(S): Heath Chester Asbury, NE 30th Place 681, Boca Raton, Florida 33431 (US); Jackson Kevin Michael, SW 22nd Circle 2920, Apt. D1, Delray Beach, Florida 33445 (US); Judice Darryl Edmond, SW 28th Avenue 1087, Boynton Beach, Florida 33435 (US); Pestonji, Hoshang Ratan, NW 107 Terrace 500, Coral Springs, Florida 33071 (US)

Priorité(s) 24.03.87 US USA 029511

ARTICLE 2.- Ce brevet est délivré sans examen préalable de la brevetabilité de l'invention, sans garantie du mérite de l'invention ou de l'exactitude de la description de celle-ci et aux risques et périls du(des) demandeur(s).

Bruxelles, le 27 Juin 1989 PAR DELEGATION SPECIALE:

Directour.

# CONVERSION DU MODE DE SIGNAUX DE COMMANDE POUR ORDINATEURS

# Art antérieur

La présente invention concerne les systèmes de calcul comportant des unités de commande d'interruption et plus particulièrement des systèmes plus efficaces qui sont conditionnés pour convertir et répondre à des commande de logiciel concernant des signaux signaux de commande étant interruptions, ces normalement incompatibles avec le système.

5

On connaît des systèmes de ce type dans l'art antérieur comme par exemple les ordinateurs personnels IBM XT et 10 AT, qui comportent une ou plusieurs unités de commande d'interruption programmables interconnectées dans le système et qui traitent les interruptions dans ledit système et ainsi réduisent le temps consacré par l'unité centrale de traitement (CPU) au logiciel et au 15 traitement. On peut citer à titre d'exemple d'unité de commande d'interruption de ce type, l'unité de commande d'interruption programmable (PIC) 8259A Intel qui peut interruptions de priorité jusqu'à huit manipuler vectorisées pour l'unité CPU. (\*Intel est une marque de 20 Intel Corporation). Les caractéristiques de l'unité 8259A sont décrites par exemple dans le manuel Intel intitulé "Microsystem Components Handbook", 1984, pages 2-120 à 2-137. L'unité PIC 8259A peut être programmée par des signaux de commande de logiciel pour répondre à 25 des modes d'interruption déclenchée par un front ou un niveau. Il est souhaitable avec certains systèmes de calcul de fonctionner principalement avec du logiciel qui n'utilise que des signaux de commande de logiciel relatifs aux interruptions dans un seul mode mais de 30 répondre à des signaux de commande de logiciel relatifs

aux interruptions issus d'autres configurations de système ou programmes basés sur un mode différent.

#### Résumé de l'invention

5

10

15

Selon les enseignements de la présente invention, un système de calcul personnel comportant une unité de commande d'interruption associée, est de préférence conçu pour fonctionner avec des programmes et répondre à des signaux de commande de logiciel relatifs aux interruptions dans un mode tel que le mode sensible aux niveaux, mais comprend des circuits qui permettent au système de convertir et de répondre à des signaux de commande de logiciel relatifs à des interruptions dans un autre mode comme le mode sensible aux ou déclenché par les fronts, le système traitant ainsi les signaux en mode sensible aux fronts d'une manière compatible comme s'il s'agissait de signaux en mode sensible aux niveaux.

20

25

30

35

La pratique de la présente invention offre un avantage significatif étant donné que le logiciel, y compris les programmes d'applications, qui serait autrement incompatible, est rendu compatible et qu'un grand nombre de ces programmes peuvent être utilisés dans le système.

Dans la réalisation préférée décrite ici, le système de calcul personnel utilise du logiciel qui ne délivre normalement que des signaux de commande d'interruption sensibles aux niveaux en permanence. Il est souhaitable de pouvoir utiliser du logiciel qui serait autrement incompatible, délivrant des signaux de commande d'interruption sensibles aux fronts. Une logique de circuits est ajoutée au système sensible aux niveaux et intercepte tous les signaux de commande d'interruption

sensibles aux fronts et les traite de la même manière que des signaux de commande sensibles aux niveaux.

Les principes de réponse et de conversion peuvent être appliqués à la situation inverse, c'est à dire signaux de commande sensibles aux fronts contre signaux de commande sensibles aux niveaux ainsi qu'au traitement de types de signaux de commande autres que des signaux de commande d'interruption.

10

15

25

30

Pour une meilleure compréhension de la présente invention ainsi que d'autres caractéristiques et avantages de celle ci, on se reportera à la description qui va suivre faite à l'aide des dessins ci joints et aux revendications annexées à ce document et qui délimitent le cadre de la présente invention.

# Brève description des dessins

20 En se reportant aux dessins, on voit que:

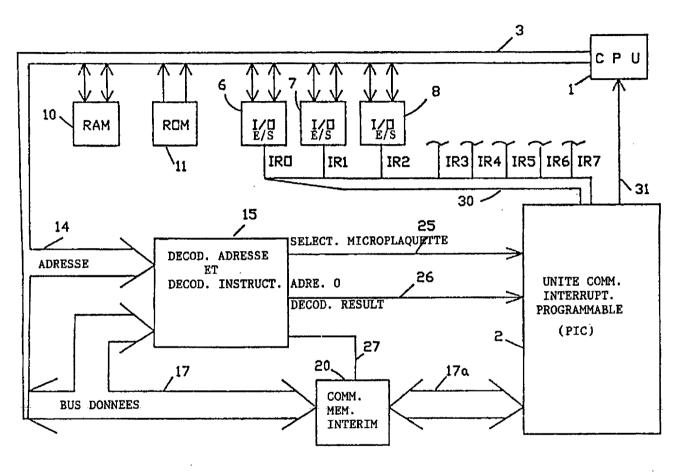

La figure 1 représente un système de calcul comprenant une unité CPU, une unité de commande d'interruption programmable et une logique de commande de mémoire intermédiaire et décodage pour traiter des signaux de commande d'interruption selon la présente invention.

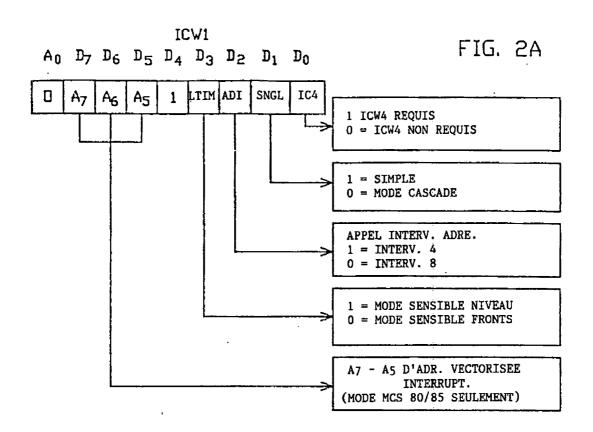

Les figures 2A et 2B illustrent respectivement le format d'un mot đe commande d'initialisation de commande (ICW1) et d'un mot représentatif d'opération (OCW1) utilisés dans le système de la figure 1.

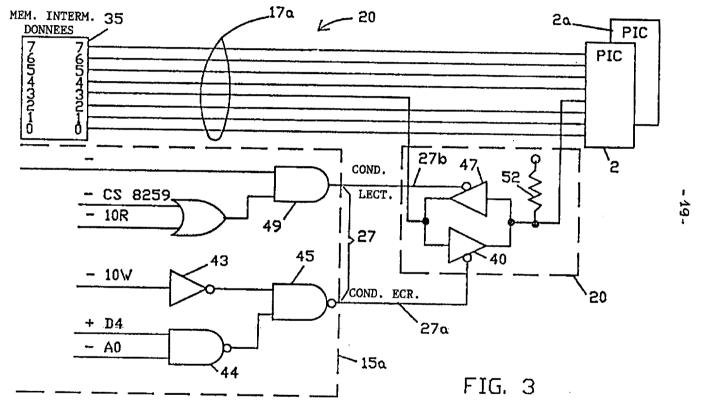

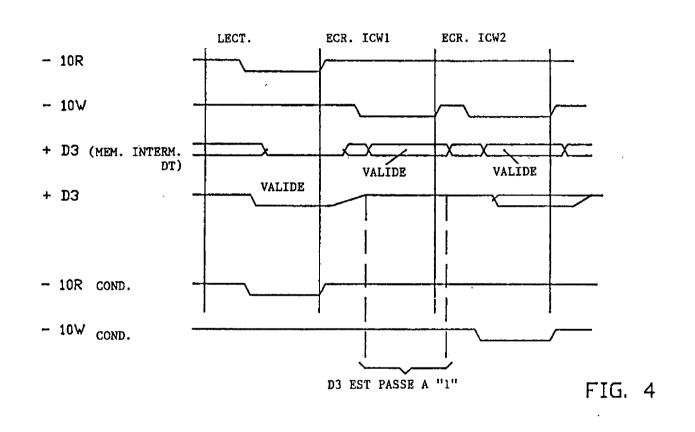

La figure 3 montre des détails de la logique de 35 commande de mémoire intermédiaire de la figure 1 comprenant une ligne de conditionnement d'écriture et une ligne de conditionnement de lecture. La figure 4 est un schéma chronologique montrant les formes d'ondes des signaux générés pendant l'initialisation de l'unité de commande d'interruption programmable, et montrant plus particulièrement l'utilisation du mot de commande ICW1.

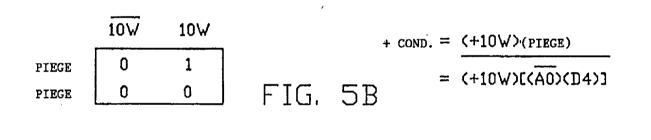

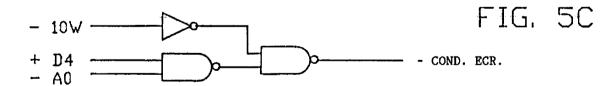

Les figures 5A, 5B et 5C illustrent la logique et les conditions particulières au fonctionnement de la ligne de conditionnement de lecture de la figure 3.

10

5

Les figures 6A, 6B et 6C montrent la logique et les conditions de fonctionnement du circuit de conditionnement de lecture de la figure 3.

#### Description détaillée

15

Le système de calcul de la figure 1 comprend une unité centrale de traitement (CPU) 1 interconnectée avec une unité de commande d'interruption programmable (PIC) 2 et au moyen du bus 3 (comprenant le bus d'adresse 14 et le bus de données 17) avec d'autres éléments comprenant les dispositifs d'entrée/sortie (E/S) 6-8, une mémoire à accès aléatoire (RAM) 10 et une mémoire permanente (ROM) 11.

25

30

35

20

Des signaux d'adresse sont dirigés par le bus 14 au bloc de décodage d'adresses et de décodage d'instructions 15 et des signaux de données dirigés par le bus de données 17 au bloc 15 et à la logique de commande de mémoire intermédiaire 20. Divers signaux de données, de statuts et de commande sont délivrés comme le signal de sélection microplaquette sur la ligne 25, le signal d'adresse "0" sur la ligne 26 et le signal de résultat décodage sur la ligne 27, ce qui représente un signal -conditionnement écriture (ligne 27a, Figure 3) ou un signal -conditionnement lecture (ligne 27b, Figure 3). L'unité de commande de mémoire intermédiaire délivre des données au moyen du bus 17a à l'unité de commande d'interruption 2.

L'unité de commande d'interruption programmable 5 jusqu'à huit interruptions de vectorisées pour l'unité CPU 1 au moyen des huit lignes IR2, etc. à IR7 par le bus 30. dispositifs E/S 6-8 seulement sont représentés connectés dans le système de la figure 1 aux lignes 10 IRO, IR1 et IR2.

L'unité de commande d'interruption 2 fonctionne comme une unité de gestion générale. Elle accepte des requêtes des dispositifs E/S, détermine laquelle des requêtes à l'entrée a l'importance la plus élevée (priorité), détermine si une requête à l'entrée a une valeur de priorité plus élevée que le niveau couramment servi et délivre une interruption par la ligne (INT) 31 à l'unité CPU en se fondant sur cette détermination.

20

25

30

35

15

Chaque dispositif E/S a généralement un programme spécial ou "routine" qui est associé à ses exigences fonctionnelles ou opérationnelles spécifiques et est appelé "routine de service". L'unité de commande d'interruption 2, après avoir délivré une interruption à l'unité CPU 1, délivre des informations à l'unité CPU 1 qui peuvent "indiquer" le compteur programme à la routine de service associée au dispositif demandeur. Ce "pointeur" est une adresse d'une table de vectorisation et elle est considérée comme une donnée vectorisée.

Une sélection de modes de priorité est disponible pour le programmeur si bien que la manière suivant laquelle les requêtes sont traitées par l'unité de commande d'interruption 2 peut être configurée pour répondre aux exigences du système. Les modes de priorité peuvent être dynamiquement changés ou reconfigurés n'importe

quand pendant le programme principal. Ainsi, la structure d'interruption peut être définie comme requis.

La séquence d'interruption est entièrement décrite dans le manuel "Microsystem Components Handbook" indiqué précédemment.

# Programmation de l'unité 8259A

10

15

L'unité de commande d'interruption 2 accepte deux types de mots de commande générés par l'unité CPU 1.

(1) Mots de commande d'initialisation (ICW): Le format de ICW1 est représenté à la figure 2A. Avant de pouvoir commencer une opération normale, l'unité de commande d'interruption 2 doit être amenée à un point de début par une séquence de 2 à 4 multiplets synchronisés par des impulsions WR.

20

- (2) Mots de commande d'opération (OCW): Le format de OCW1 est représenté à la figure 2B. Ce sont les mots de commande qui commande le fonctionnement de l'unité 8259A dans divers modes d'interruption. Ces modes sont décrits dans le manuel indiqué précédemment et sont:

- 25

- a) Le mode entièrement imbriqué

- b) Le mode à priorité tournante

- 30

- c) Le mode à masque spécial

- d) Le mode sélectif

Les mots OCW peuvent être écrits dans l'unité 8259A n'importe quand après l'initialisation.

35

Chaque fois qu'un signal de commande est délivré avec A0=0 et D4=1, ceci est interprété comme le mot de

commande d'initialisation 1 (ICW1). ICW1 commence la séquence d'initialisation pendant laquelle ce qui suit se déroule automatiquement.

- a) Le circuit de détection de front est restauré, ce qui signifie qu'à la suite de l'initialisation, une entrée de requête d'interruption (IR) doit assurer une transition niveau bas à niveau haut pour générer une interruption.

- b) Le registre de masques d'interruptions est effacé.

15

35

- c) La priorité 7 est attribuée à l'entrée IR7.

- d) L'adresse de mode asservi est établie à 7.

- e) Le mode à masque spécial est effacé et le signal de lecture statut est conditionné à IRR.

- f) Si IC=0, toutes les fonctions sélectionnées sur ICW4 sont alors conditionnées à zéro.

- Les modes déclenchés par les fronts et les niveaux sont programmés en utilisant le bit 3 dans ICW1. Voir la figure 2A.

- Si LTIM="0", une requête d'interruption sera reconnue par une transition niveau bas à niveau haut sur une entrée IR. L'entrée IR peut rester au niveau haut sans générer une autre interruption.

- Si LTIM="1", une requête d'interruption sera reconnue par un niveau "haut" sur une entrée IR et il n'y a pas besoin de détection de front. La requête d'interruption doit être retirée avant la délivrance du signal de commande EOI ou avant le conditionnement de l'interruption CPU pour éviter l'apparition d'une seconde interruption.

Le système de calcul de la figure 1 est configuré pour fonctionner normalement avec du logiciel comme des

programmes d'applications qui délivrent des signaux de commande relatifs à des interruptions (ICW1) au moment de l'initialisation qui établit principalement un mode niveaux pour l'unité de commande sensible aux d'interruptions 2. Il est souhaitable de maintenir l'unité de commande d'interruptions 2 dans un tel mode sensible aux niveaux pour améliorer les performances et réduire les problèmes de bruit qui résultent en une fausse détection d'une interruption. Cependant, lorsque ceci est assuré, le logiciel qui délivre des signaux de commande sensibles aux fronts comme le signal ICW1 en fronts. au moment mode sensible aux de l'initialisation, devient incompatible. Si l'unité de commande d'interruptions 2 est programmée en mode sensible aux fronts par du logiciel écrit pour d'autres systèmes de calcul, le système ne terminera pas la séquence d'interruption. De la logique est ajoutée pour éviter l'initialisation de l'unité de commande en mode sensible aux fronts. Cette caractéristique assure la compatibilité du programme avec d'autres systèmes. Un système ne présentant pas cette caractéristique est susceptible d'être moins compatible logiciel de calculateur personnel applications de pré-existant.

25

30

20

5

10

15

A la figure 1, chaque fois qu'un signal de commande déclenché par un front, est décodé par le bloc 15, le bloc logique de commande de mémoire intermédiaire 20 piège les signaux de commande et l'unité de commande est conditionnée pour répondre de la même manière que si un signal de commande sensible à un niveau était reçu.

Le mode sensible aux fronts est actif pendant le 35 premier mot de commande d'initialisation (ICWI). L'apparition de cette condition est détectée et le bit de données LTIM pour le mode établi sur le bus 17a, est passé dans un mode sensible aux niveaux. La logique requise pour cette fonction au bloc 20 comprend des mémoires intermédiaires à trois états pour transférer les données bidirectionnelles avec un peu de logique de support pour effectuer le décodage. Des détails sont représentés à la figure 3.

5

10

15

20

25

A la figure 3, on voit une mémoire intermédiaire de données 35 qui délivre des données par le bus 17a à l'unité de commande d'interruption (PIC) 2. Une autre unité PIC 2a peut être prévue, si on le désire, avec la sélection appropriée de l'une des deux pendant le fonctionnement. La logique de commande de mémoire intermédiaire 20 comprend les blocs 40 et 47 et une résistance 52. Comme indiqué, le résultat du décodage 27 représente soit un signal -conditionnement écriture sur la ligne 27a, soit un signal -conditionnement lecture sur la ligne 27b issue d'un port dans 15a du bloc de décodage d'adresse et d'instruction 15. Un signal -conditionnement écriture au bloc 40 commande des opérations d'écriture impliquant des unités de commande d'interruption 2 ou 2a. Une autre logique d'écriture comprend les blocs 43-45. Un -conditionnement lecture au bloc 47 commande opérations de lecture impliquant les unités de commande d'interruption 2 et 2a. Une autre logique de lecture comprend les blocs 48 et 49.

A la figure 3, lorsqu'un mot de commande est écrit à 1'une des unités de commande d'interruption 2 ou 2a, le signal -conditionnement écriture sur la ligne 27a est actif sauf pendant une écriture pour le mot de commande ICW1. En n'activant pas le signal -conditionnement écriture pendant une écriture pour ICW1, le bit de donnée 3 du signal de commande est maintenu au niveau haut par la résistance 52. Lorsque le bit de donnée 3=1 pendant une écriture à ICW1, l'unité de commande

d'interruption sélectionnée est conditionnée à ou reste en mode sensible aux niveaux. Les statuts et états des diverses lignes de commande et de données pour les opérations de lecture et d'écriture, mais plus particulièrement pour ICWI écriture, sont représentés à la figure 4.

Le développement de la logique pour la commande des opérations d'écriture est illustré aux figures 5A-5C et est fondé sur les paramètres suivants:

### Conditionnement écriture

#### Fonction

Ne permet pas aux données issues du bus XDATA d'être dirigées vers l'unité 8259 lorsque le premier mot de commande d'initialisation (ICW1) est en cours d'écriture.

Le développement logique pour la commande des opérations de lecture est illustré aux figures 6A-6C et est fondé sur les paramètres suivants:

25

30

20

5

10

15

# Conditionnement lecture

#### Fonction

Permet aux données issues de l'unité 8259 d'être dirigées vers le bus XDATA pendant un cycle de lecture à la microplaquette ou pendant un cycle INTA à la microplaquette.

Donc, que les unités de commande soient prévues pour 35 être programmées en mode sensible aux niveaux ou en mode sensible aux fronts, le circuit modifie toujours le signal de commande au mode sensible aux niveaux. En outre, il est évident que les principes inventifs énoncés ici peuvent être appliqués à la conversion du mode de commande sensible aux niveaux au mode de commande sensible aux fronts et à la conversion de types de signaux de commande autres que des signaux de commande d'interruption et dans d'autres circonstances où il est souhaitable d'établir une compatibilité entre plusieurs systèmes, programmes ou logiciels autrement incompatibles.

10

15

20

De plus ou en alternance, le signal de conditionnement d'écriture peut être utilisé pour signaler à l'unité de traitement qu'un signal de commande déclenché par un front a été détecté. Cette information peut être utilisée par le processeur pour indiquer d'autres défauts (code dépendant du temps, décodages incomplets, essais de transfert de données avec un équipement non connecté) qui peuvent être associés à des signaux de commande déclenchés par un front. L'unité đe traitement peut alors décider discontinuer l'opération, de modifier l'opération ou de poursuivre avec les défauts.

Bien qu'une réalisation préférée de la présente invention ait été décrite et illustrée ici, il est évident qu'il n'est pas question de limiter ladite invention à la réalisation précise décrite ici et que tous nos droits sont réservés en ce qui concerne tous les changements et modifications qui pourraient y être apportés dans le cadre de celle ci tel que défini par les revendications ci jointes.

#### Revendications

1. Système de calcul normalement conçu pour fonctionner avec des signaux de commande de logiciel dans un premier mode de commande, caractérisé en ce qu'il comprend:

5

un dispositif programmable capable de fonctionner sous la commande d'un signal de commande soit dans ledit premier mode, soit dans un second mode, et

des moyens de détection pouvant fonctionner avant la transmission d'un signal de commande audit dispositif programmable, pour détecter des signaux de commande de logiciel dans l'un ou l'autre mode et si un signal de commande dans ledit second mode est détecté avant la transmission dudit signal de commande dans ledit second mode audit dispositif programmable, pour convertir ledit signal de commande dans ledit second mode en signal de

commande dans ledit premier mode.

20

- 2. Système selon la revendication 1 dans lequel lesdits signaux de commande de logiciel sont délivrés par ledit calculateur pendant une période d'initialisation permettant de conditionner ledit dispositif programmable.

- 3. Système selon la revendication 1 ou 2 dans lequel moyens de détection comprennent circuits présentant une logique de commande 30 d'écriture et de lecture pour commander données vers et transfert des depuis dispositif programmable pendant le déroulement des opérations effectuées par le système, lesdits circuits pouvant fonctionner sous la commande de 35 signaux de commande issus du calculateur pour

décoder tout signal de commande de logiciel dans le second mode et le transformer en un signal de commande dans ledit premier mode.

- 5 4. Système selon la revendication 1, 2 ou 3 dans lequel lesdits moyens de détection dirigent un signal vers ledit calculateur pour indiquer une conversion de mode, ce qui fait que ledit calculateur détermine en outre si le logiciel qui a généré ledit signal de commande de logiciel est compatible avec le système de calcul.

- 5. Système selon l'une quelconque des revendications précédentes dans lequel lesdits signaux de 15 commande comprennent un nombre prédéterminé de bits de données et de commande et dans lequel la distinction entre un signal de commande dans le premier mode et un signal de commande dans le second mode est assurée par l'inspection logique 20 d'un emplacement de bit particulier dans lesdits mots de commande et dans lequel lesdits circuits convertissent ledit emplacement de bit particulier en un bit de commande dans le premier mode avant transmission audit dispositif programmable.

6. Système de calcul normalement conçu pour fonctionner avec des signaux de commande de logiciel dans un mode sensible aux niveaux, caractérisé en ce qu'il comprend:

25

30

une unité de commande d'interruption programmable capable de fonctionner soit en mode sensible aux fronts, soit en modé sensible aux niveaux, et

des moyens de détection pouvant fonctionner avant la transmission du signal de commande à ladite unité de commande d'interruption pour détecter des signaux de commande de logiciel dans l'un ou l'autre mode et si un signal de commande en mode sensible aux fronts est détecté, pour convertir ledit signal de commande en mode sensible aux fronts en signal de commande en mode sensible aux niveaux.

7. Système selon la revendication 6 dans lequel lesdits signaux de commande de logiciel sont délivrés par ledit calculateur pendant une période d'initialisation pour conditionner ladite unité de commande d'interruption programmable.

- Système selon la revendication 6 ou 7 dans lequel 8. - 15 lesdits moyens de détection comprennent de commande de mémoire intermédiaire logique présentant des éléments de commande d'écriture et de lecture pour commander le transfert des données vers et depuis ladite unité de 20 d'interruption programmable pendant le déroulement opérations du système, ladite logique commande đe mémoire intermédiaire pouvant fonctionner sous la commande de signaux calculateur pour décoder tout signal de commande 25 de logiciel dans le second mode et pour passer ledit signal de commande dans ledit premier mode.

- 9. Système selon la revendication 8, 9 ou 10 dans lequel lesdits signaux de commande comprennent un nombre prédéterminé de bits de données et dans lequel la distinction entre un signal de commande dans un premier mode et un signal de commande dans un second mode est assurée par l'inspection logique d'un emplacement de bit particulier dans lesdits mots de commande et dans lequel ladite logique de commande de mémoire intermédiaire convertit ledit emplacement de bit particulier en

un bit de statut de premier mode avant transmission à ladite unité de commande d'interruption programmable.

- Système selon l'une quelconque des revendications 10. 5 6 à 9 dans lequel lesdits moyens de détection dirigent signal vers ledit un calculateur, indiquant une conversion de mode dudit signal de commande en mode sensible aux fronts en un signal de commande en mode sensible aux niveaux, ce qui 10 fait que ledit calculateur détermine en outre si le logiciel qui a généré ledit signal de commande en mode sensible aux fronts est compatible avec ledit système de calcul.

- 11. Système de calcul normalement conçu pour fonctionner avec des signaux de commande logiciel dans un mode sélectionné et préféré choisi entre le mode sensible aux niveaux et le mode sensible aux fronts, caractérisé en ce qu'il 20 comprend:

15

25

30

35

une unité de commande d'interruption programmable capable de fonctionner soit dans un mode sensible aux fronts, soit dans un mode sensible aux niveaux, et

des moyens de détection pouvant fonctionner avant transmission d'un signal de commande logiciel à ladite unité de commande d'interruption pour détecter des signaux de commande de logiciel dans l'un ou l'autre mode et si un signal de commande de logiciel qui n'est pas dans le mode sélectionné et préféré, est détecté, convertir ledit signal de commande de mode en un dit signal de commande dans le mode sélectionné et préféré.

12. Système selon la revendication 11 dans lequel lesdits moyens de détection comprennent logique de commande de mémoire intermédiaire présentant des éléments de commande d'écriture et de lecture pour commander le transfert des données depuis ladite unité d'interruption programmable pendant le déroulement des opérations assurées par le système, logique de commande de mémoire intermédiaire pouvant fonctionner sous la commande de signaux du calculateur pour décoder tout signal de commande de logiciel non sélectionné et préféré et passer ledit signal de commande à traiter dans un statut de signal de commande sélectionné et préféré.

15

10

5

13. Système selon la revendication 11 ou 12 dans lequel lesdits moyens de détection dirigent un signal vers ledit calculateur, indiquant une conversion de mode d'un signal de commande de logiciel qui n'est pas dans le mode sélectionné et préféré en un signal de commande dans le mode sélectionné et préféré, ce qui fait que ledit calculateur détermine en outre si le logiciel qui a généré le signal de commande de logiciel qui n'est pas dans le mode sélectionné et préféré, est compatible avec ledit système de calcul.

FIG. 1

FIG. 2B

CCV1

A<sub>0</sub> D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub>

1 M<sub>7</sub> M<sub>6</sub> M<sub>5</sub> M<sub>4</sub> M<sub>3</sub> M<sub>2</sub> M<sub>1</sub> M<sub>0</sub>

MASQ. INTERRUPT.

1 = COND. MASQ.

0 = REST. MASQ.

| (+)<br>10W       | (+)<br>PIEGE     | (+)<br>PIEGE     | _                                          | FIG. | 54 |

|------------------|------------------|------------------|--------------------------------------------|------|----|

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>0<br>1<br>0 | REPOS<br>REPOS<br>ECR. VALIDE<br>ECR. ICW1 |      |    |

| $\infty$ |

|----------|

|          |

|          |

| $\circ$  |

|          |

| $\sim$   |

| 4        |

| 7        |

| 7        |

|   | (-)<br>SELECT.                  | (-)<br>10R                 | (-)                        | (+)<br>1OR<br>COND.             | FIG.                                           | 6A |

|---|---------------------------------|----------------------------|----------------------------|---------------------------------|------------------------------------------------|----|

| • | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1 | 1<br>1<br>1<br>0<br>1<br>0<br>1 | NON VALIDE<br>LECT.<br>NON LECT.<br>NON VALIDE |    |

| CS |   |   |   | cs |

|----|---|---|---|----|

|    | 1 | 1 | 1 | 1  |

|    | 1 | 0 | 0 | 0  |

| •  |   |   |   |    |

+ COND. =

$$(-INTA)$$

=  $(-CS)(-IOR)$

- COND. =  $(-INTA)$  +  $(-CS)(-IOR)$  |  $-ICS$  |

# RAPPORT DE RECHERCHE

établi en vertu de l'article 21 § 1 et 2 de la loi belge sur les brevets d'invention du 28 mars 1984

BE 8701347 B0 886

| DC        | CUMENTS CONSIDERES COMME PERTINE                                                                                                                                       | INTS                       |                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------|

| Catégorie | Citation du document avec indication, en cas de besoin,<br>des parties pertinentes                                                                                     | Revendication<br>concernée | CLASSEMENT DE LA<br>DEMANDE (Int. Cl.4)                                    |

| X         | US-A-3 938 101 (IBM) * Colonne 1, lignes 47-63; colonne 2, lignes 28-37; figure 1 *                                                                                    | 1,3                        | G 06 F 9/46<br>G 06 F 13/24                                                |

| X         | EP-A-O 169 565 (NEC)  * Page 3, lignes 25-36; page 4, lignes 1-31; page 9, lignes 13-29; figure 2 *                                                                    | 1,3                        |                                                                            |

| A         |                                                                                                                                                                        | 4,13                       |                                                                            |

| A         | NEW ELECTRONICS, vol. 29, no. 6,<br>novembre 1986, page 24; W. MILLAR:<br>"Interfacing the ADCO808"<br>* En entier *                                                   | 6                          |                                                                            |

| A         | IBM TECHNICAL DISCLOSURE BULLETIN, vol. 29, no. 6, novembre 1986, pages 2380-2381, New York, US; "Interrupt sharing for personal computer" * Page 2381, lignes 15-16 * | 6                          |                                                                            |

|           |                                                                                                                                                                        |                            | DOMAINES TECHNIQUES<br>RECHERCHES (Int. CL4)                               |

|           |                                                                                                                                                                        |                            | G 06 F 9/46<br>G 06 F 13/24<br>G 06 F 13/26<br>G 06 F 9/44<br>G 06 F 13/38 |

|           |                                                                                                                                                                        |                            | To an and a second                                                         |

|           | Date d'achèvement de la recherche 21-12-1988                                                                                                                           | DHEE                       | RE R.F.B.M.                                                                |

EPO FORM (503 00.82 (PO448)

CATEGORIE DES DOCUMENTS CITES

- X: particulièrement portinent à lui seul

Y: particulièrement portinent en combinaison avec un

autre document de la même catégorie

A: arrièro-plan technologique

O: divulgation non-écrite

P: document intercalaire

- T: théorie ou principe à la base de l'invention

E: document de brevet antérieur, mais publié à la date de dépôt ou après cette date

D: cité dans la demande

L: cité pour d'autres raisons

- & : membre de la même famille, document correspondant

#### ANNEXE AU RAPPORT DE RECHERCHE RELATIF A LA DEMANDE DE BREVET BELGE NO.

BE 8701347

886

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités:dans le rapport de recherche visé ci-dessus.

Les dits members sont contenus au fichier informatique de l'Office européen des brevets à la date du 05/01/89

Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

| Document brevet cité<br>au rapport de recherche | Date de<br>publication | Membre(s) de la<br>famille de brevet(s) | Date de<br>publication |

|-------------------------------------------------|------------------------|-----------------------------------------|------------------------|

| US-A- 3938101                                   | 10-02-76               | DE-A,C 2460011                          | 10-07-75               |

| 03 A 3330101                                    | 10 02 .0               | FR-A,B 2279159                          | 13-02-76               |

|                                                 |                        | GB-A- 1452847                           |                        |

|                                                 |                        | CA-A- 1024658                           | 17-01-78               |

|                                                 |                        | JP-A- 50098751                          | 06-08-75               |

| EP-A- 0169565                                   | 29-01-86               | JP-A~ 61033546                          | 17-02-86               |

|                                                 |                        |                                         |                        |

|                                                 |                        |                                         |                        |

|                                                 |                        |                                         |                        |

|                                                 |                        |                                         |                        |

|                                                 |                        |                                         |                        |

|                                                 |                        |                                         |                        |

|                                                 |                        |                                         |                        |

|                                                 |                        |                                         |                        |

|                                                 |                        |                                         |                        |

|                                                 |                        |                                         |                        |

|                                                 |                        |                                         |                        |

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82