# [45] May 1, 1973

| [34] | TIVE | LUA   | NCE | $\mathbf{D}\mathbf{R}$ | 3 I P |      | CKI   | عدان | XI |

|------|------|-------|-----|------------------------|-------|------|-------|------|----|

| 100  |      |       |     |                        |       |      | 200   |      |    |

| (75) | Invo | ntor. | Can |                        | D     | Doob | afall |      | T- |

[75] Inventor: George D. Rockefeller, Jr., Morris

Plains, N.J.

[73] Assignee: Westinghouse Electric Corporation,

Pittsburgh, Pa.

[22] Filed: May 25, 1972

[21] Appl. No.: 256,668

[52] U.S. Cl. ............317/27 R, 235/151.31, 317/36 D

[56] References Cited

### **UNITED STATES PATENTS**

| 3,569,785 | 3/1971 | Durbeck  | 235/151.31 X |

|-----------|--------|----------|--------------|

| 3,654,516 | 4/1972 | Traversi | 317/27 R     |

Primary Examiner—James D. Trammell Attorney—A. T. Stratton et al.

## [57] ABSTRACT

An apparatus for determining the peak value of the sinusoidal component of an electrical quantity which may include a non-sinusoidal component by means of comparing the first and second differential magnitudes of the electrical quantity at any time interval of the period of the sinusoidal component whereby the value of any low rate of change component is attenuated, as for example the D.C. offset which is normally present during fault conditions. The apparatus also includes means to determine the phase angles between two sinusoidal components and when such two sinusoidal components represent current and voltage to determine the magnitude of the impedance of the network energized by said sinusoidal quantities.

### 37 Claims, 24 Drawing Figures

## SHEET 01 OF 19

SHEET 02 OF 19

SHEET 03 OF 19

SHEET 05 OF 19

SHEET OB OF 19

|                         |     |             | 1   |    |    |    |     |    |          |    |    |    |     |      |     |    |            |    |    |    |                                       |

|-------------------------|-----|-------------|-----|----|----|----|-----|----|----------|----|----|----|-----|------|-----|----|------------|----|----|----|---------------------------------------|

| ပ                       | A41 | A6I         | A5I |    |    |    | A6I |    |          |    |    |    | A4V | A6V. | A5V |    | A6V        |    |    |    |                                       |

| CONDUCTING<br>AND GATES | A2I |             |     |    |    |    |     |    |          |    |    |    |     |      |     |    |            | -  |    |    |                                       |

| υ <b>∢</b>              | A2V |             |     |    |    |    |     |    |          |    |    |    |     |      |     |    |            |    |    |    | · · · · · · · · · · · · · · · · · · · |

| TI ME                   | 40  | 41          | 42  | 43 | 4  | 45 | \$  | 47 | <b>⇔</b> | 49 | 50 | 51 | 52  | 53   | 54  | 55 | 56         | 57 | 28 | 59 |                                       |

| G                       | A61 | A5I         | A4I |    |    |    | A5I |    |          |    |    |    | A6V | A5V  | A4V |    | A5V        |    |    |    | 7                                     |

| CONDUCTING<br>AND GATES | AII |             |     | -  |    |    |     |    |          |    |    |    |     |      |     |    |            |    |    |    |                                       |

| ζ                       | Alv |             |     |    |    |    |     |    |          |    |    |    |     |      |     |    |            |    |    |    | 1                                     |

| TI ME                   | 20  | 21          | 22  | 23 | 24 | 52 | 26  | 27 | 28       | 59 | 30 | 31 | 32  | 33   | 34  | 35 | <b>3</b> % | 37 | 88 | 39 | T                                     |

| NG<br>S                 | A5I | A4I         | A6I |    |    |    | A4I |    |          |    |    |    | A5V | A4V  | A6V |    | A4V        |    |    |    |                                       |

| CONDUCTIN<br>AND GATES  | A3I |             |     |    |    |    |     |    |          |    |    |    |     |      |     |    |            |    |    |    |                                       |

| K C                     | A3V |             |     |    |    |    |     |    |          |    |    |    |     |      |     | ** | -          |    |    |    |                                       |

| TI ME<br>I NT.          | 0   | ,— <b>,</b> | 2   | 3  | 4  | 5  | 9   | 7  | ∞        | 6  | 10 | 11 | 12  | 13   | 14  | 15 | 16         | 17 | 18 | 19 | ł                                     |

F1G. 5A

|                      |      |     |     |      |     |     | A53  |     |     |                                                  |     |     |     |      |     |       | A 102 |       |       |     |

|----------------------|------|-----|-----|------|-----|-----|------|-----|-----|--------------------------------------------------|-----|-----|-----|------|-----|-------|-------|-------|-------|-----|

|                      |      |     |     |      |     |     | A52  |     |     |                                                  |     |     |     |      | A99 |       | A75   |       |       |     |

|                      |      |     |     |      |     |     | A51  |     |     |                                                  |     |     |     |      | A98 |       | A54   |       |       |     |

|                      |      | A91 |     |      |     |     | A49  |     |     |                                                  |     |     |     |      | A96 |       | A52   |       |       |     |

| S                    |      | A87 |     |      |     |     | A47  |     |     |                                                  |     |     |     |      | A46 |       | A51   |       |       |     |

| D GATE               |      | A86 |     |      |     |     | A33  |     |     |                                                  |     |     |     | A97  | A44 |       | A50   | A105  |       |     |

| ING AN               |      | A82 | A88 |      |     |     | A31  | A65 | •   |                                                  | A95 |     |     | A38  | A42 | A 101 | A48   | A104  |       |     |

| CONDUCTING AND GATES |      | A27 | A35 |      |     |     | A29  | A56 |     |                                                  | A87 |     |     | A37A | A41 | A100  | A34   | A 103 | A 107 |     |

| 00                   |      | A26 | A16 | A38  |     |     | A 19 | A55 | A85 | A91                                              | A86 |     | A89 | A37  | A16 | A46   | A32   | A66   | A106  |     |

|                      | A36  | A25 | A12 | A37A | A45 | A45 | A16  | A27 | A75 | A64                                              | A81 |     | A84 | A 18 | A12 | A44   | A20   | A59   | A27   |     |

|                      | A30  | A15 | All | A37  | A43 | A43 | A14  | A26 | A58 | A63                                              | A27 | A94 | A83 | A15  | A11 | A40   | A16   | A48   | A26   |     |

|                      | A23  | A13 | 49  | A21  | A42 | A40 |      | A25 |     | A36                                              |     |     | A35 | A13  |     | A39   | A12   |       | 1     | A92 |

|                      | A 10 | A7  | A8  | A17  | A41 | A39 | All  | A22 | A47 | A30A                                             | A25 | A90 | A10 | A7   | A8  | A21   | A11   | A14   | A22   | A85 |

| \LS                  | 9    | 41  | 42  | 43   | 44  | 45  | 46   | 47  | 84  | 49                                               | 50  | 51  | 52  | 53   | 54  | 55    | 56    | 57    | 58    | 59  |

| II ME<br>I NTERVALS  | 20   | 21  | 22  | 23   | 24  | 25  | 26   | 27  | 82  | 82                                               | 8   | 31  | 32  | 33   | 怒   | 35    | 8     | 37    | 88    | 33  |

| TIME                 | 0    |     | 2   | 3    | 4   | 5   | 9    | 1   | ∞   | <del>                                     </del> | 2   | 11  | 12  | 13   | 14  | 15    | 91    | 17    | 18    | 19  |

FIG. 5B

SHEET 08 OF 19

SHEET 09 OF 19

SHEET 10 OF 19

SHEET 11 OF 19

SHEET 12 OF 19

|                                                                    |                                           | ОСТ                                       | ANT OF A                                  | NGLE θ <sup>1</sup>                       |                                      |                                           |                                           |                                      |

|--------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------------|

|                                                                    | 1                                         | 2                                         | 3                                         | 4                                         | 5                                    | 6                                         | 7                                         | 8                                    |

| F3  BB  >  AA <br>F4  DD  >  CC                                    | 0                                         | 1<br>1                                    | 1<br>1                                    | 0<br>0                                    | 0<br>0                               | 1<br>1                                    | 1<br>1                                    | 0                                    |

| F5 AA<br>F6 CC                                                     | 0<br>0                                    | 0<br>0                                    | 1<br>1                                    | 1<br>1                                    | 1<br>1                               | 1<br>1                                    | 0<br>0                                    | 0<br>0                               |

| F7 BB<br>F8 DD                                                     | 1<br>1                                    | 1<br>1                                    | 1<br>1                                    | 1<br>1                                    | 0<br>0                               | 0                                         | 0<br>0                                    | 0<br>0                               |

| OR (-θ)                                                            | 0                                         | l                                         | 0                                         | 1                                         | 0                                    | 1                                         | 0                                         | 1                                    |

| A67<br>A68<br>A69<br>A70<br>A71<br>A72<br>A73<br>A74<br>A76<br>A77 | 1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1 | 0<br>0<br>0<br>0<br>0<br>0<br>1<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>1<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>1<br>0<br>0<br>0 |

| A79<br>A80                                                         | 0<br>0                                    | 0<br>0                                    | 0<br>0                                    | 0                                         | 0<br>0                               | 1<br>0                                    | 1<br>0                                    | 0<br>1                               |

FIG. 7

## SHEET 13 GF 19

SHEET 14 GF 19.

SHEET 15 OF 19

SHEET 16 OF 19

SHLET 17 OF 19

FIG.I3C

## SHEET 18 OF 19

FIG.14

SHEET 19 OF 19

#### IMPEDANCE DISTANCE RELAY

## BRIEF SUMMARY OF THE INVENTION

The voltage and magnitude at which electric power is transmitted is constantly being increased. This increased power makes it desirable to interrupt any fault current in as short a time period as possible to maintain system stability and to minimize fault current damage and at the same time to maintain system security by preventing interruptions due to transient conditions which do not require such an interruption.

In accordance with this invention the peak magnitude of the sinusoidal quantity or quantities is determined by utilizing the first and second derivatives of the quantity. These derivatives are obtained by measuring the quantity of the sinusoidal component either continually or at frequent intervals. In the case of an analogue device, the sine and cosine quantities may be eliminated by squaring the cosine quantity of the first derivative and squaring the sine quantity of the second derivative of the sinusoidal quantity. The two quantities are thereafter added together and equated to unity in accordance with the trigonometric functions that the sum of the sine quantity squared and of the cosine quantity squared equals unity.

In the case of a digital sampling of the sinusoidal quantity, the first and second differences of the quantity which approximate the first and second differentials of the quantity are utilized. If desired, these difference quantities could be treated as set out above by squaring and equating to unity. I prefer, however, to utilize these difference quantities by dividing the second difference quantity by the first difference quantity and of thereafter using the values which have been established for trigonometric functions and which are readily available in table form. For example, by determining the angle from the tangent table portion and thereafter using the cosine quantity for that angle the peak magnitude of the quantity may be mathematically determined.

If the magnitudes of two sinusoidal quantities are substantially simultaneously sampled the angle between the two quantities is equal to the difference between the two angles as determined from the tables. If the sinusoidal quantities are current and voltage the magnitude of the impedance of that portion of the line through which the fault current flows may be determined by ratioing the peak magnitudes of the quantities.

## BRIEF DESCRIPTION OF THE DRAWINGS

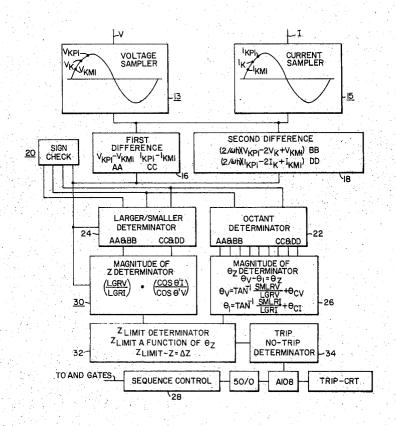

FIG. 1 is a block diagram of an impedance relay associated with a transmission line embodying the invention;

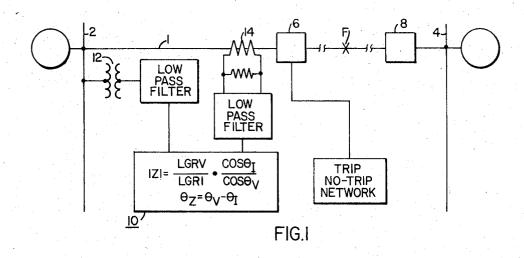

FIG. 2 is a more detailed block diagram showing the relay of FIG. 1 in somewhat greater detail;

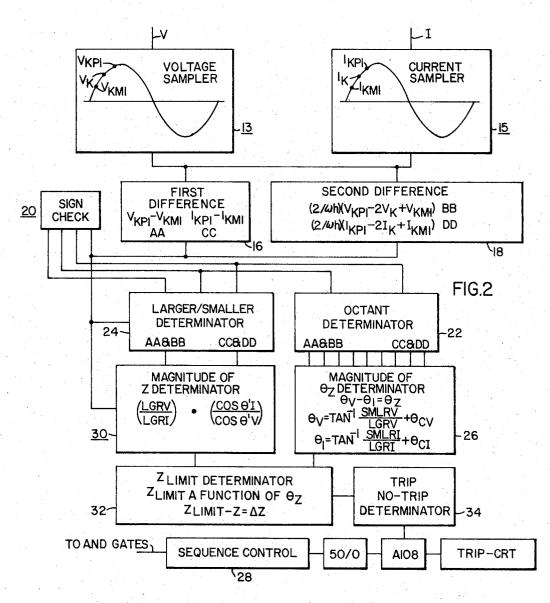

FIG. 3 is a diagram helpful in understanding the octant determination of the angles;

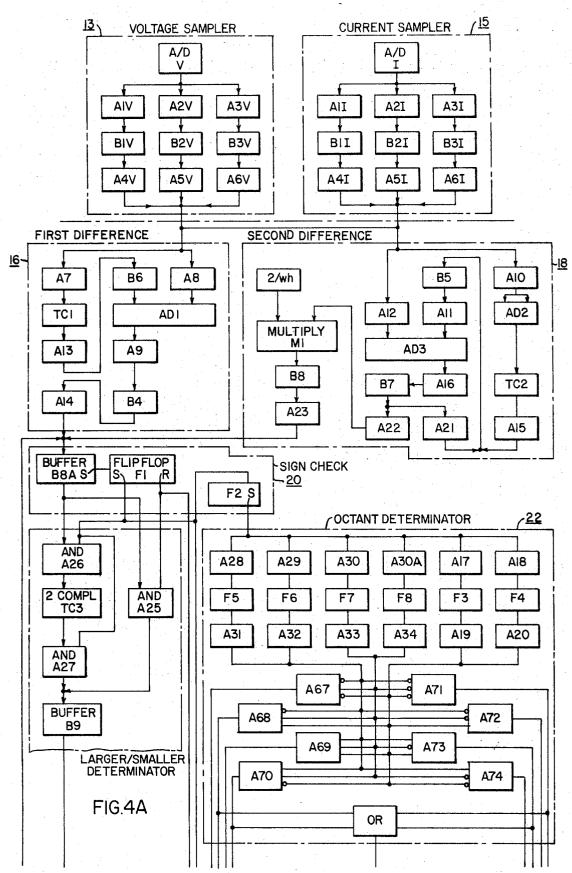

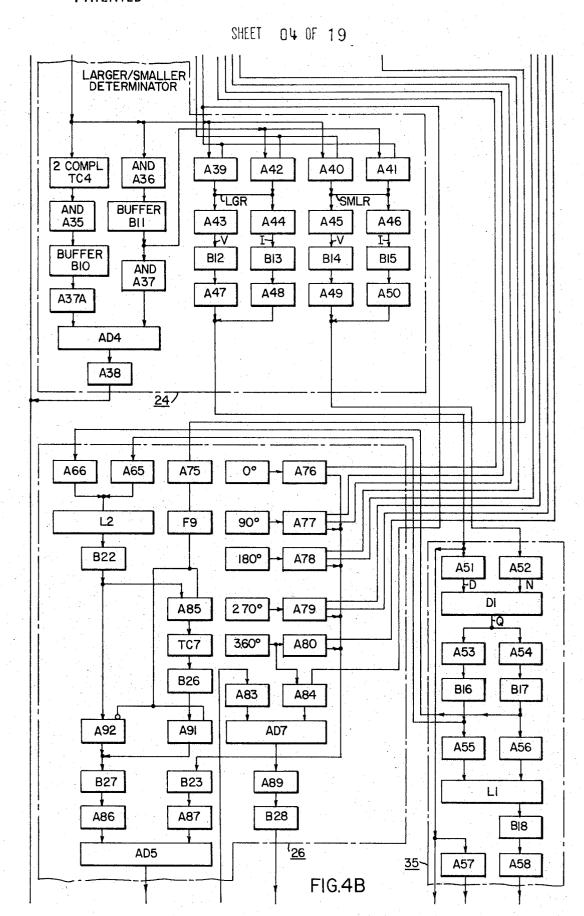

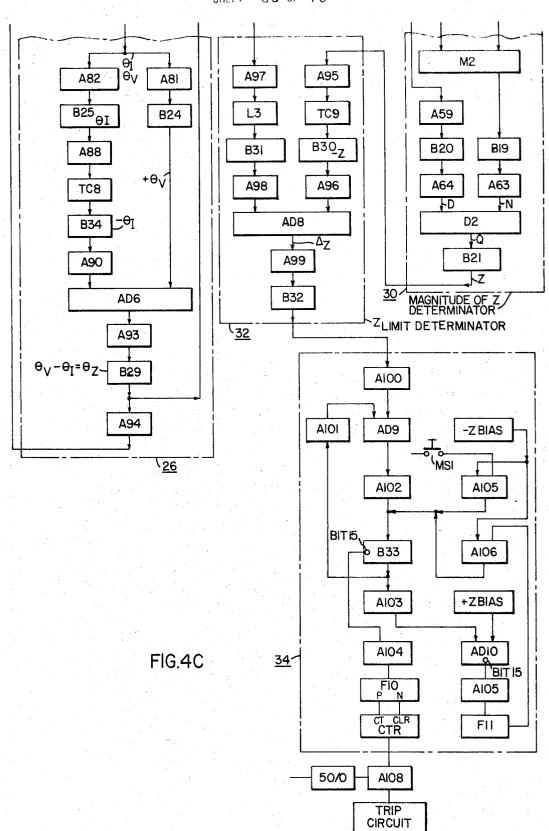

FIGS. 4A, 4B and 4C are block diagrams showing the relay of FIGS. 1 and 2 in still greater detail;

FIGS. 5A and 5B are tables setting forth the operating of the AND networks of FIG. 4;

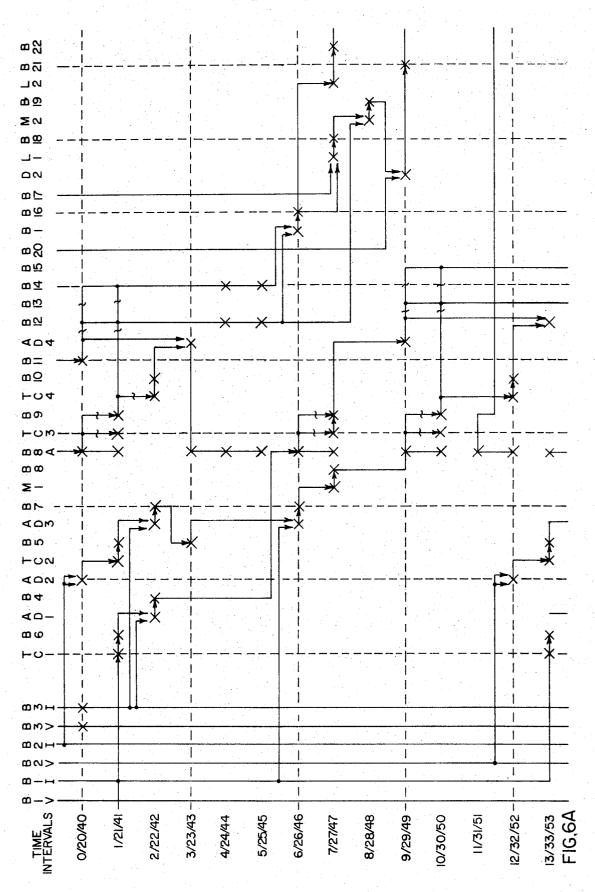

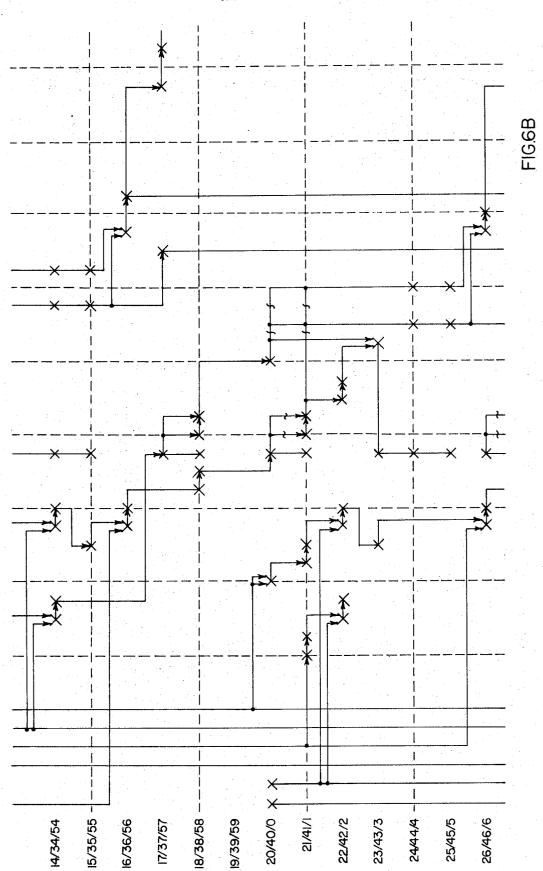

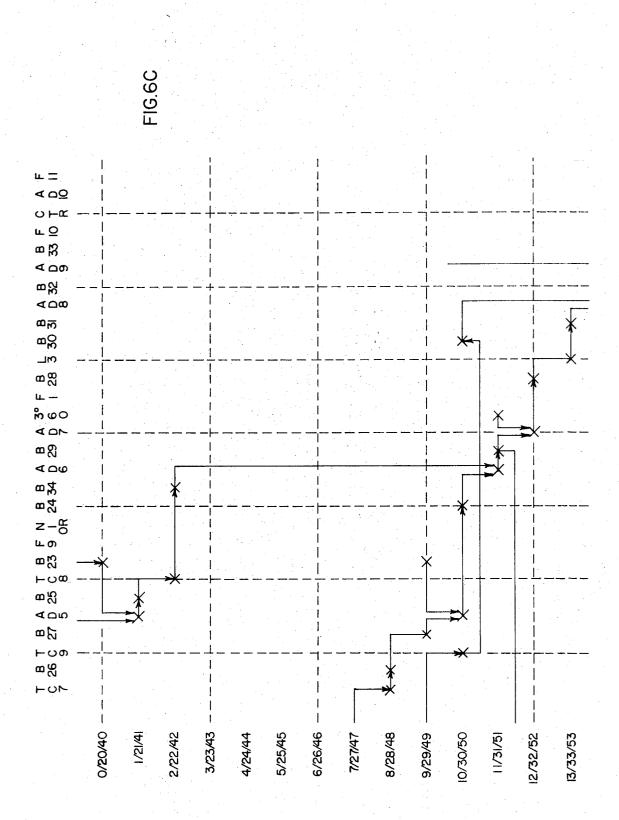

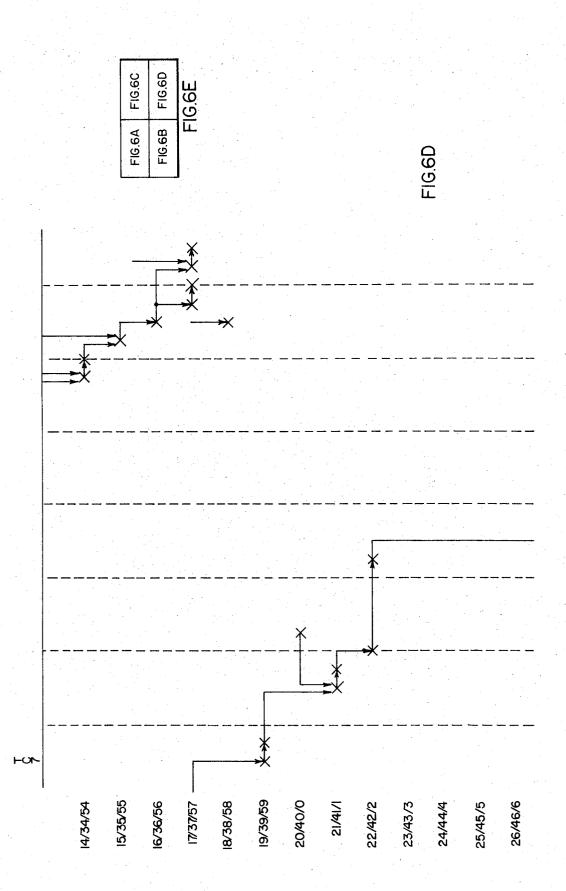

FIGS. 6A, 6B, 6C, 6D and 6E are abbreviated flow charts showing the flow of information through the block diagram of FIG. 4;

FIG. 7 is a chart illustrating the logical outputs of the octant determining units;

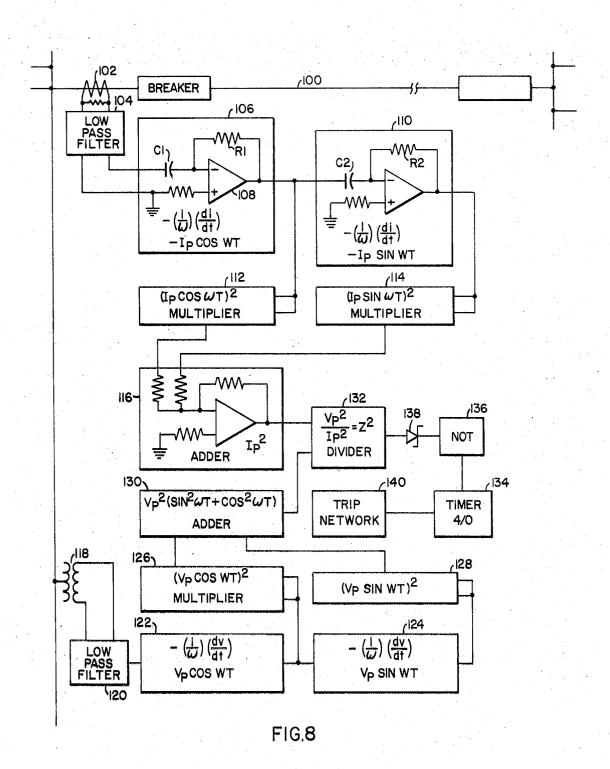

FIG. 8 is a schematic diagram of a modified form of relay embodying the invention;

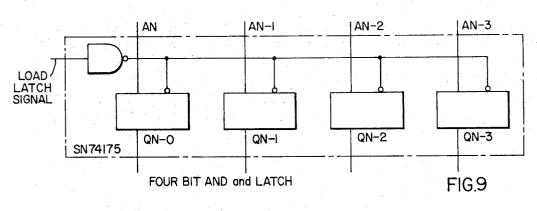

FIG. 9 is a schematic illustration of an implementation of a Four Bit AND and Buffer;

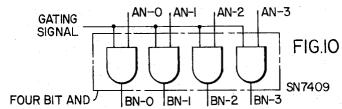

FIG. 10 is a schematic illustration of an implementation of a Four Bit AND;

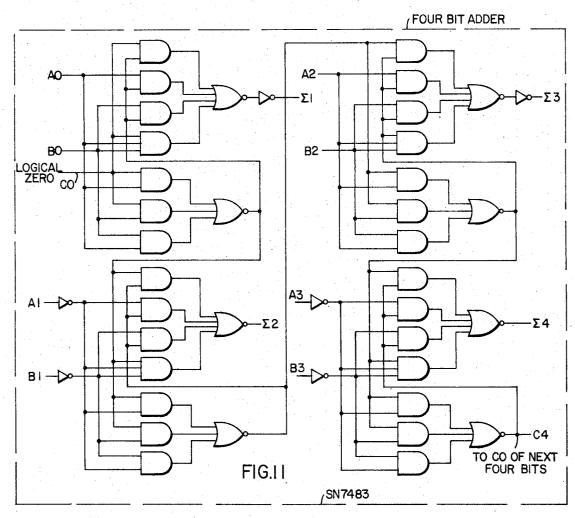

FIG. 11 is a schematic illustration of an implementation of a Four Bit adder;

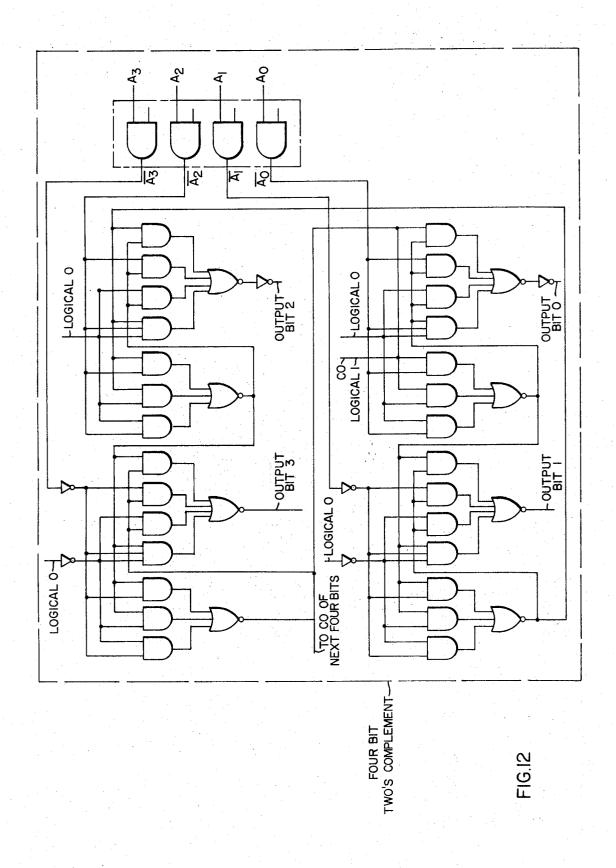

FIG. 12 is a schematic illustration of an implementation of a Four Bit Two's Complement Logic;

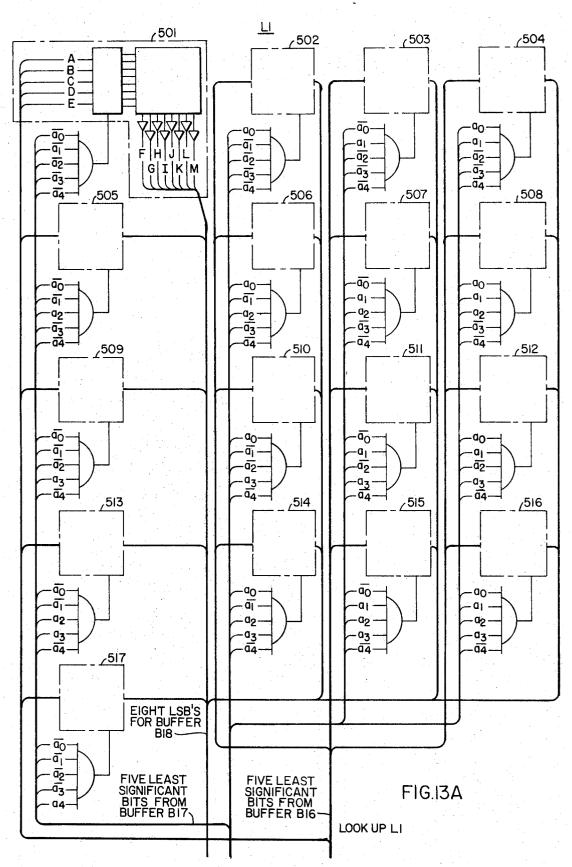

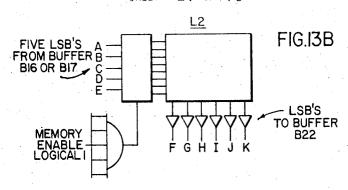

FIGS. 13A, 13B and 13C are schematic illustrations of an implementation of the three Look-Up tables;

FIG. 14 is a schematic illustration of an implementation of a multiplier; and

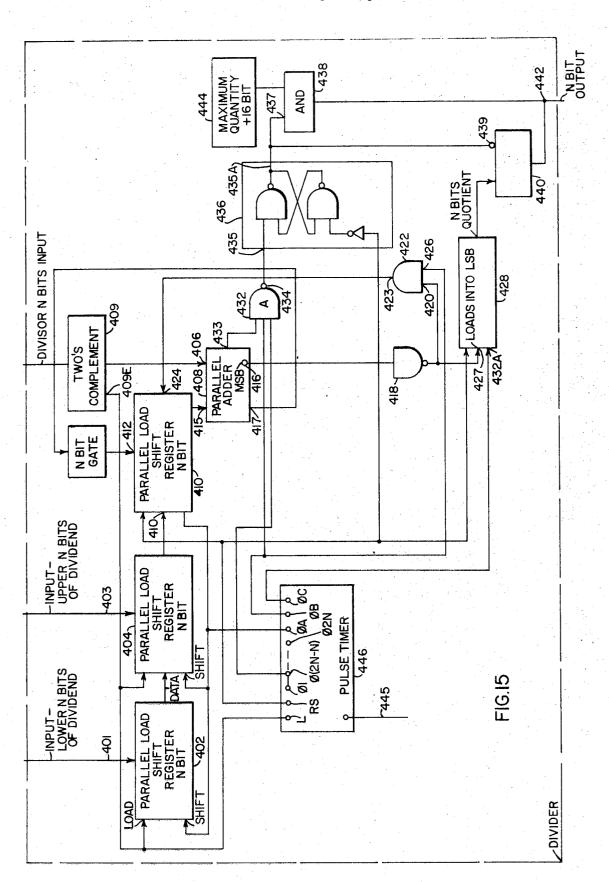

FIG. 15 is a schematic illustration of an implementation of a divider.

#### **DETAILED DESCRIPTION**

Referring to the drawings by characters of reference, the numeral 1 indicates generally a power transmission line connected to first and second busses 2 and 4 through power circuit breakers 6 and 8 respectively. Only the protective relay 10 associated with the breaker 6 is illustrated. The relay 10 is of the class of relays known as distance relays and more specifically the class in which the relay provides a control signal which is a measure of the impedance Z of the line from the bus 2 to the fault F. If the magnitude of the im-30 pedance Z at its angle  $\theta_z$  is above a predetermined value the breaker will not be tripped even if the line is faulted. If the magnitude of Z at its angle  $\theta_z$  is less than a predetermined value, the fault is considered as being within the reach of the relay 10 and the breaker 6 will be tripped to disconnect the line 1 from the energized bus 2.

The relay 10 is energized with voltage and current signals from the potential and current transformers 12 and 14 and as will be discussed in greater detail below 40 to determine the magnitude of Z from the magnitude of the first and second derivatives (first and second differences) of the sinusoidal current and voltage components and the angles thereof at the instant the sinusoidal components were measured. As illustrated in 45 FIG. 1, the magnitude of Z is determined by multiplying the ratio of the larger voltage derivative to the larger current derivative by the ratio of the cosine of the angle of the current with respect to the cosine of the angle of the voltage. When the magnitude of Z at 50 the angle  $74_z$  is below a critical value for a critical number of consecutive measurements the relay 10 trips the breaker 6.

The voltage samples, V<sub>KMI</sub>, V<sub>K</sub>; and V<sub>KP1</sub> are derived from the transformer 12 by the voltage sampling network 13. These samples are taken at equal intervals h which do not necessarily have any relationship to the frequency of the sinusoidal voltage component. The current samples I<sub>KMI</sub>; I<sub>K</sub>; and I<sub>KP1</sub> are similarly taken by the current sampling network 15 by the transformer 14. Preferably the corresponding current and voltage samples are simultaneously taken but since the value of h is small and the samples are sequentially taken, the error will be small. For example, h may be of the magnitude 1/2ω of the sinusoidal component at the nominal line frequency.

The component magnitudes are taken in the order KM1 K; and KP1 and converted into the first and

second difference quantities by the networks 16 and 18. As will be explained in greater detail below, these quantities are simplified into voltage quantities AA and BB and into current quantities CC and DD. The sign of each of these quantities AA through DD is sequentially checked in the sign check network 20 and sign signals are delivered to the octant determining network 22 for later use in determining the true angle  $\theta_V$  and  $\theta_I$  of the voltage and current sinusoidal wave components.

The quantities AA through DD are sequentially delivered to the larger-smaller determining networks 24 where the positive absolute value of AA is added to the negative absolute value of BB. If the sign of the sum is positive, |AA| > |BB|, |AA| = LGRV and |BB| |

The angles  $\theta_V$  and  $\theta_I$  are determined by the angle 25 magnitude determining network 26 which includes an arctan look-up table for determining the first octant angle  $\theta'_I$  and thereafter  $\theta'_V$  under control of the AND gate sequencing network 28. The network 28 maintains the AND gates enabled throughout the time periods as set forth in FIGS. 5A and 5B. The octant determining network 22 determines the addition or subtraction of  $\theta'_I$  and  $\theta'_V$  from 90°; 180°; 270°; and 360° so that  $\theta'_I$  and  $\theta'_V$  are transformed into the absolute angles  $\theta_I$  and  $\theta_V$  as may be seen by reference to FIG. 3. Angle  $\theta_Z$  is determined by subtracting  $\theta_I$  and  $\theta_V$ . If the resulting angle is negative thereafter 360° is added thereto to make  $\theta_Z$  a positive quantity.

The magnitude of Z is determined in the "magnitude of Z" network 30 which is supplied with the quantities LGRV and LGRI from the network 24 and with the arctan values of  $\theta'_I$  and  $\theta'_V$  from the angle determining network 26. The arctan values are supplied to a two-part look-up table which is programmed to provide an output value equal to (128)  $(\cos \theta'_I)/(\cos \theta'_V)$ . The output of this look-up table L1 is then progressively multiplied by LGRV and divided by LGRI to provide a quantity equal to 128Z.

The angle of 128Z is supplied to the  $Z_{LIMIT}$  look-up 50 table L3 in the  $Z_{LIMIT}$  determination network 32 which provides an output equal to  $128Z_{LIMIT}$ . The value of 128Z is negated and added to the value of 128Z  $_{LIMIT}$ . If the sum  $\Delta Z$  is negative, Z is greater than  $Z_{LIMIT}$  and no fault exists within the reach of the relay 10. If the sum  $\Delta Z$  is positive, the value of Z is less than the value of  $Z_{LIMIT}$  and a fault exists within the reach of the relay.

The output  $\Delta Z$  is supplied to the Trip-No-Trip determining network 34. This network integrates successive positive values of  $\Delta Z$  and when the result of its integration produces a positive output signal for two successive  $\Delta Z$  inputs will supply a trip signal to the breaker 6.

The sequence control or network 28 when initially energized energizes a timer 50/0 which after a 50 ms delay enables an AND network A108 which as will be discussed below in connection with FIG. 4 prevents the energization of the trip circuit TRIP-CRT by any false

operation prior to the loading of the buffers or latches in the voltage or current samplers 13 and 15. As will be discussed more fully below, three samples of each over the desired time interval is necessary to provide a  $\Delta Z$  of the proper magnitude. After the apparatus has made the original three sequential samples, determination of  $\Delta Z$  is made for each new sample of current and voltage as will be seen from the flow chart of FIG. 6.

The following is a mathematical explanation of the operation of relay 10. Since the peak value of the voltage and of the current is determined in the same manner, the explanation will be directed toward the voltage determination. At any instant in the voltage wave the value of the voltage v may be expressed as follows:

$$v = V_X + V_P \sin \theta V$$

Where  $V_p$  is the peak value and  $\theta_V$  is the angle (0° to 360°) at the particular instant and  $V_X$  is the value of any voltage present the value of which changes at a low rate or remains constant as, for example, a D.C. component. It will be appreciated that  $\theta_V$  is a time factor and may be expressed as  $\omega t$  where  $\omega$  equals  $2\pi f$  where f = frequency in Hertz and t is time in seconds.

$$dv/dt = \omega V_P \cos \omega t \cong (V_{KP1} - V_{KM1}/2h)$$

$$\frac{d^2v}{dt^2} = -\omega^2 V_{\rm P} \sin \omega t \cong \frac{(V_{\rm KP1} - V_{\rm K})/h - (V_{\rm K} - V_{\rm KM1})/h}{h}$$

$$-\omega^2 V_P \sin \omega t \cong (V_{KP1} - 2V_K + V_{KM1}/h^2)$$

$$\sin \omega t \cong -(V_{KP1} - 2V_K + V_{KM1}) (1/h\omega^2 V_P)$$

$$\cos \omega t \cong (V_{KP1} - I_{KM1}) (1/2\hbar\omega V_P)$$

$$\tan \omega t = \sin \omega t/\cos \omega t = -(V_{KP1} - 2V_K + V_{KM1})/(V_{KM} - V_{KM1}) \times 2/\omega h = \tan \theta_V$$

and

$$\tan \theta_V = -BB/AA$$

where

$$AA = (V_{KP1} - V_{KM1})$$

and

$BB = (V_{KM1} - 2V_K + V_{KM1}) (2/\omega h)$

The function of the voltage angle  $\theta_V$  in the first quadrant will be defined as angle  $\theta'_V$ . The value of tan  $\theta'_V$  in the first quadrant will vary from 0 to  $\infty$ . However, within the first octant (0° to 45°) the value of tan  $\theta'_V$  will vary from 0 to 1.000 which values are easily manipulated. In the second octant (45° to 90° the values of tan  $(90^\circ - \theta'_V)$  will vary from 1.000 to 0. As will be evident from FIG. 3,  $\theta_V$  in the first octant  $\theta'_V = \tan^{-1}(-BB/+AA)$ ; in the second octant  $\theta_V = 90^\circ - \theta'_V = 90^\circ - \tan^{-1}(+AA/-BB)$ ; in the third octant  $\theta_V = 90^\circ + \theta'_V = 90^\circ + \tan^{-1}(-AA/-BB)$ ; and so on until in the eighth octant  $\theta_V = 360^\circ - \theta'_V = 360^\circ - \theta'_V = 360^\circ - \tan^{-1}(+BB/+AA)$ .

Summarizing the foregoing, it is observed that in each octant  $\theta'_{V}$  is equal to  $\tan^{-1}(SMLRV/LGRV)$  and the magnitude of angle  $\theta'_{V}$  is always between 0° and 45°. In the first and second octants, the sign of BB is negative and the sign of AA is positive. In the third and fourth octants, the signs of AA and of BB are both negative; in the fifth and sixth octants, the sign of AA is

negative and the sign of BB is positive; and in the seventh and eighth octants, the signs of AA and BB are both positive. The first, fourth, fifth and eighth octants are distinguishable from the second, third, sixth and seventh octants by the fact that in the odd numbered 5 octants the larger LGRV is AA and the smaller SMLRV is BB. In the even numbered octants the LGRV is BB and the SMLRV is AA. The quadrants are therefore determined by the signs of AA and BB and the different octants within the quadrants are determined by the 10 relative absolute magnitudes of AA and BB. Having determined the octant, the absolute magnitude of  $\theta_{\nu}$  is obtained by adding or subtracting  $\theta'_{\nu}$  to 0°, 90°, 180°, 270°, and 360° as indicated in FIG. 3.

The value of Z is the quotient of voltage and current. 15 As may be seen in FIG. 3,

$$V_P = LGRV/\cos\theta'_V$$

and

$$I_p = LGRI/\cos\theta'_V$$

therefore

$$Z = \frac{V_{P}}{I_{P}} = \frac{\frac{LGRV}{\cos \theta' v}}{\frac{LGRI}{\cos \theta' v}} = \frac{LGRV}{LGRI} \frac{\cos \theta' v}{\cos \theta' v}$$

The values of  $V_P$  and  $I_P$  could of course be calculated and the calculated magnitudes divided. However, to minimize calculating times the relay 10 determinations of Z is done by means of a two-part look-up table in which the input quantity initially supplied thereto is the value of the arctan of  $\theta'_I$  or of  $\theta'_V$ . The first part of the part of the look-up table L1 from which the arctan value is obtained. The second part of the look-up table provides an output quantity which is 128 times the value of the quotient of the cosines of the angle  $\theta'$ , and of the  $\theta'_{\nu}$ . The constant 128 is equal to  $2^7$  and insures 40 that a number greater than 1 will define the ratio with sufficient accuracy. The "looked-up" quantity equal to the quantity (128)  $\cos\theta'_{\nu}/\cos\theta'_{\nu}$  is thereafter multiplied by LGRV and thereafter divided by LGRI.

It is believed that the further description of the relay 45 10 may best be presented by a description of the operation thereof with particular reference to the more detailed block diagrams of FIG. 4, to the time chart of FIG. 5 and to the flow chart of FIG. 6. The charts of FIGS. 5 and 6 are somewhat simplified to eliminate some duplication since the same AND networks beginning with AND network A7 will be rendered conducting at each x, (x + 20) and (x + 40) interval as illustrated in FIG. 5B. In accordance with my invention I utilize each measurement of each component as the value KP1, K and KM1 at x, (x+20), and (x+40) time interval repeating each 60 intervals (FIG. 5A).

As is more clearly illustrated in FIG. 6 the relay 10 uses 34 time intervals to completely process one set of current and voltage data to its determination of  $\Delta Z$ . During this time interval, however, a second set of data is being processed so that a  $\Delta Z$  determination is made each 20 intervals as indicated by FIGS. 5 and 6. The total time for the 20 intervals is equal to time h which may, for example, be  $1.3263 \times 10^{-3}$  seconds. This interval with a 60 Hz wave will make this quantity  $2/\omega h =$ 4.000.

A complete determination of  $\Delta Z$  will be described starting at an initial time interval just prior to time 0 in which the quantities  $V_{KM1}$  and  $V_k$  are in buffers B1V and B2V, respectively, and the quantities  $I_{KM1}$  and  $I_K$ are in the buffer B1I and B2I, respectively. At time 0 the AND networks A3V and A3I as well as the A/D, and A/D<sub>V</sub> converters are rendered conducting. Conduction of the AND network A3V and of the A to D converter  $A/D_V$  supplies the value  $V_{KP1}$  to the buffer 3V. Conduction of the AND network A3I renders the A to D converter A/D, effective to supply the value  $I_{KP1}$ to the buffer B3I. During this same time interval O the AND network A5I and A10 are rendered conducting and the quantity  $I_K$  is supplied from the buffer B2I to both of the two input terminals of adder AD2.

During the time interval 1, the AND network A15 is rendered conducting and the quantity 21<sub>K</sub> supplied by the adder AD2 is inverted by the twos complement TC2 into  $-2I_K$  and  $-2I_K$  is supplied to the buffer B5. During this same time interval 1 the AND networks A4I and A7 are rendered conducting, whereby the quantity I<sub>KM1</sub> is supplied from the buffer B1I through the twos complement TC1 and AND network A13 to the buffer B6 as  $-I_{KM1}$ .

At the time interval 2, the AND networks A6I and A8 are rendered conducting to supply the quantity  $I_{KP1}$ to the adder AD1 to which the buffer B6 is supplying the quantity  $-I_{KM1}$ . These two quantities are added together and are transmitted through the AND network A9 to the buffer B4 as  $(I_{KP1} - I_{KM1})$  and is designated as the quantity CC. During this same time interval 2, the AND networks A6I and A12 are rendered conducting and the quantity  $I_{KP1}$  is supplied from buffer B31 to one look-up table L1 determines the portion of the second 35 input of the adder AD3. At the same time, the quantity -21<sub>K</sub> is supplied through the now-conducting AND network All to the other input of the adder AD3. The output quantity  $(I_{KP1}-2I_K)$  is supplied to the buffer B7 through the AND network A16.

During the time interval 3 the AND network A21 is rendered conducting whereby the quantity  $(I_{KP1}-2I_K)$  is transferred from the buffer B7 to the buffer B5.

During the time interval 6, the AND network A4I and A12 are rendered conducting whereby the quantity I<sub>KM1</sub> is transmitted from the buffer B1I to one input terminal of the adder AD3, and the AND network All also conducts to transmit the quantity  $(I_{KP1}-2I_K)$  from the buffer B5 to the other terminal of the adder AD3. The adder AD3 adds these quantities and they pass through the AND network A16 into the buffer B7 as the quantity  $(I_{KP1}-2I_K+I_{KM1})$ . Also during this time interval 6, the conducting AND network A14 conducts the quantity CC from the buffer B4 into the sign checking buffer B8A. If this quantity CC is positive, the flip-flop F1 will be actuated by the logical 0 of the sign bit of the buffer 8A to supply a logical 0 output quantity of the flip-flop F2 and a logical 1 to the AND network A25. The flipflop F1, being supplied with a logical 0, supplies a logical 0 to the AND network A26. Therefore during the interval 7 when conducting signals are supplied to all of the AND networks A25, A26, and A27 only the AND network A25 will conduct and the quantity of +CC will be transferred from the buffer B8A into the buffer B9 as + |CC|. If, however, the quantity CC is negative the sign bit 15 of sign buffer B8A supplies a logical 0 to the AND network A25 and a logical 1 to the flip-flop F1 which provides a logical 1 at its output terminal S and

to the AND networks A26 and A27 so that during the time interval 7 the quantity -CC would be supplied through the conducting AND networks A26 and A27 and through the twos complement TC3 and supplied as + |CC| to the buffer B9.

The logical 0's or 1's from the flip-flop F2 are supplied to each of the AND networks A17, A18, A28, A29, A30, and A30A, however, only one of these AND networks will be rendered conducting at any one time by this sequencing control (FIGS. 5A and 5B) so that only one of the flip-flops F3-F8 will be supplied with the logical 0 or 1. Therefore to simplify the explanation only the AND network and flip-flop combination effective at that time will be discussed in detail. During the time interval 6, the AND network A29 will be conducting and the logical 0 or 1, as the case may be, will be supplied to and actuate the flip-flop F6. A logical 0 will cause the flip-flop F6 to provide a logical 0 at its output form of single bit buffers as compared with the multibit buffers (see FIG. 9).

During the interval 7, the AND network A22 conducts and the quantity  $(I_{KP1}-2I_K+I_{KM1})$  stored in the buffer B7 is supplied to the multiply network M1 where 25 |CC| in the buffer B11 becomes LGRI and logical 1's it is multiplied by the quantity  $2/\omega h$  and the quantity  $(I_{KP1}-2BK+I_{KM1})$  (2/ $\omega h$ ) which is designated DD is supplied to the buffer B8.

At the time interval 9, the quantity DD stored in the buffer B8 is transmitted through the now conducting AND network A23 to the buffer B8A. If the quantity DD is positive the sign output quantity is a logical 0 and flip-flip F1 is actuated to provide a logical 1 to the AND network 25 so that during the next time interval 10, the AND network A25 will conduct and the quantity DD will be transferred directly to the buffer B9 as + |DD|. If the quantity DD in the buffer B8A is negative, the sign output quantity of buffer B8A is a logical 1 and the flip-flop F1 provides a logical 1 to the AND networks A26 and A27 interval 10 the quantity DD will be transferred through the AND networks A26 and A27 and the twos complement TC3 into the buffer B9 as a positive quantity +|DD|. As discussed above with respect to the quantity CC a logical 0 or 1 is supplied to the flip-flop F2 from the sign buffer B8A. During the time interval 9, the AND network A30A will conduct to transmit the logical 0 or 1 to the flip-flop F8 which thereupon maintains at its output a logical 0 or 1 corresponding to the logical output of flip-flop F2.

During the time interval 9, the quantity + |CC| which was stored in the buffer B9 transfers to the buffer B11 through the conducting AND network A36. The quantity + |DD| is transferred to the buffer B9 during the interval 10.

During the time interval 12, the quantity +|DD| is transferred from the buffer 9 through the twos complement TC4 and through the now-conducting AND network A35 into the buffer B10 as -|DD|. During this same interval 12, the AND networks A5V and A10 conduct and transmit the quantity  $V_K$  from the buffer B2V into the two inputs of the adder network AD2 from hence it is supplied to the twos complement TC2 during the time intervals 12 and 13 and the resulting quantity  $-2V_K$  is transmitted through AND network A15 to the buffer B5. Also during the interval 13, the quantity V<sub>KM1</sub> is transmitted through the AND net-

works A4V and A7 and through the twos complement TC1 and AND network A13 where it is stored in the buffer B6 as the quantity minus -V<sub>KM1</sub>. Likewise, during the interval 13 the quantity +|CC| from the buffer B11 and the quantity -|DD| from the buffer B10 are transmitted through the conducting AND networks A37A and A37 to the adder AD4. The quantity CC-DD from the adder AD4 flows through the conducting AND network A38 to the buffer B8A. If the quantity |CC| is greater than the quantity |DD|, the sign buffer B8A will have a logical 0 at its S output and the flip-flops F1 and F2 will be actuated to provide logical 0's at their outputs. If, however, the quantity |DD|is greater than the quantity |CC|, the sign buffer B8A will have a logical 1 at its outputs, which is energized by bit 15, and the flip-flops F1 and F2 will be actuated to supply logical 1 at their S outputs. At the same time the AND network A18 is energized and if the S output of and conversely. The flip-flops F1-F10 may take the 20 flip-flop F2 is a logical 1 the flip-flop F4 will provide a logical 1 at its output indicating that the quantity |DD|is LGRI and is greater than the quantity |CC| which becomes SMLRI.

If the quantity CC-DD is positive then the quantity are supplied to the AND networks A40 and A42. During the time interval 14, when the AND network A44 and A46 are conductive, the LGRI quantity is transferred to the buffer B13 through the AND networks A42 and A44. If, however, the quantity CC-DD is negative, then the quantity CC is SMLRI and logical 1's are supplied to the AND networks A39 and A41 so that at time 14 the quantity SMLRI is transferred to the buffer 15 through the AND networks A41 and A46. If the quantity in buffer 11 is LGRI, the quantity in buffer B9 is SMLRI and conversely. During the interval 15 the AND networks 44 and A46 will remain conductive and the quantity |DD| in the buffer B9 will be transferred to the buffer B13 if it is LGRI or to buffer B15 it is is SMLRI because of the logical 0's and 1's supplied to the AND networks A39 and A40.

During the interval 14, the AND networks A6V and A8 will be conducting to transmit the quantities  $V_{KP1}$  to one terminal of the adder AD1. The buffer B6 energizes the other terminal of the adder AD1 with the quantity  $-V_{KM1}$  whereby the quantity  $(V_{KP1}-V_{KM1})$  will be placed in the buffer B4 through the conducting AND network A9 and is the quantity  $\overline{AA}$ . Further, dur-50 ing the time interval 14, the quantity  $V_{KP1}$  will be transmitted from the buffer B3V through the AND networks A6V and A12 to one terminal of the adder AD3. The other terminal of adder AD3 is supplied with  $-2V_K$  by the buffer B5 through the AND network A11. The output quantity of the adder AD3 is supplied through the AND network A16 to the buffer B7 as the quantity  $(V_{KP1} - 2_{K}^{V}).$

During the interval 15, the quantity  $(V_{VP1}-2V_K)$  is transferred from the buffer B7 through the conducting AND network A21 to the buffer B5.

The AND networks A4V and A12 conduct during time interval 16 to transmit the quantity  $V_{KM1}$  from the buffer B1V to one terminal of the adder AD3. At the same time, the AND network A11 conducts to supply the quantity  $V_{KP1}-2V_K$  from the buffer B5 to the other input terminal of the adder AD3. The output quantity  $(V_{KP1}-2^{V}_{K}+{}^{V}_{KM1})$  will be transmitted through the conducting AND network A16 to the buffer B7. Also during the interval 16, the quantity, LGRI in the buffer B13 is transmitted through the conducting AND networks A48 and A51 to the denominator or divisor terminal of the divide network D1 and the quantity 5 SMLRI will be transmitted from the buffer B15 through the conducting AND networks A50 and A52 to the numerator or dividend input terminal of the divider D1. The output quantity SMLRI/LGRI will be supplied to the buffer B17 through the conducting AND network A54. This quantity SMLRI/LGRI is the tangent of  $\theta'_{I}$ . During the interval 17, the tangent  $\theta'$ , quantity is transmitted through the conducting AND network A66 to the look-up table L2 which determines the degree magnitude of the angle  $\theta'_I$  in degrees and supplies it to the buffer B22.

During the same interval 17, the quantity AA is transmitted from the buffer B4 through the AND network A14 to the buffer B8A for a sign check determination 20 as discussed with respect to the quantity CC during the time interval 6 for actuation of the flip-flop F5. Further, during the interval 17, the quantity LGRI stored in the buffer B13 is transmitted to the buffer B20 through the conducting AND network A48 and A59.

During the time interval 18, the quantity  $(V_{KP1}-2V)$  $_{K}+V_{KM1}$ ) is transmitted to the multiply network M1 through the conducting AND network A22 where it is multiplied by the quantity  $2/\omega h$  and deposited in the buffer B8 as the quantity  $(V_{KP1}-2V_K+V_{KM1})$   $(2/\omega h)$  30 which quantity is the quantity designated BB. If the quantity AA in the buffer B8A is a positive quantity, it will be transferred from the buffer B8A through the AND network A25 to the buffer B9 as +|AA|. If this quantity AA is negative, it is transferred through the 35 AND networks A26 and A27 and through the twos complement TC3 to the buffer B9 as the positive quantity + |AA|.

During the time interval 16, the AND networks A20, A32, and A34 conduct to supply the logical 0's and 1's at the outputs of the flip-flops F4, F6, and F8 to the inputs of the AND networks A67-A74. Certain of the input terminals of the AND networks A67, A68, and input terminals. The output connections of the AND networks A68, A70, A71, and A73 are connected to the input terminals of an OR network OR. It will be apparent from FIG. 7 that the OR network OR will supply a logical 1 through the AND network A75 to cause the 50 flip-flop F9 to provide a logical 1 at its output solely when the octant of angle  $\theta'$  is in the even quadrants. Therefore, when during the time interval 19, the AND networks A85 and A92 are actuated by the sequence control 28, the degree magnitude of the angle  $\theta'_I$  is 55 transmitted to the buffer B27 either directly through the AND network A92 or through the AND networks A85 and A92 and the two's complement TC7 to provide a minus or plus magnitude of  $\theta'$ , depending upon the octant of  $\theta'_I$ . If the OR network has a logical 1 output, the AND network A75 will be energized to cause the flip-flop F9 to place a logical 1 signal on the AND network A85 and because of the negated input a logical 0 signal on the AND network A92. This occurs if the angle  $\theta_i$  is in the second, fourth, sixth or eighth octant whereby the angle  $\theta'_I$  is converted to  $-\theta'_I$  by the twos complement network TC7. If, however, the angle  $\theta_I$  is

in the first, third, fifth or seventh octant, then the OR network has logical 0 output and will transmit a signal to flip the flip-flop F9 to cause it to have a logical 0 output signal which prevents the AND network A85 from conducting and causes the AND network A92 to conduct under control of the sequencing network 28 so that the angle  $\theta'_i$  is deposited as  $+\theta'_i$  in the buffer B27.

During the time interval 20, the quantity BB is transmitted from the buffer B8 through the AND network A23 to the buffer B8A for a sign check. If the quantity BB is negative, the buffer B8A will cause the flip-flop F1 to have a logical 1 output at its S terminal so that during the next interval 21, the quantity BB will be transmitted through the AND network A26, the twos complement TC3 and the AND network A27 into the buffer B9 as a + |BB|. If, however, the quantity BB is positive, the R output of the flip-flop F1 supplies a logical 1 signal to the AND network A25 which will become conductive during the time interval 21 by the sequence network 28 quantity +BB will be deposited directly in the buffer B9 as + |BB|. The outputs of the AND networks A67-A74 are connected to and supply logical 0 and 1 quantities to the AND networks A76-A80 so that the proper one of the AND networks A76-A80 will conduct to supply an angle magnitude signal to the buffer B23. All of the AND networks A76-A80 are supplied with signals at the same time from its sequence network 28; however, only the one thereof which is supplied with a logical 1 signal from the AND networks A67-A74 will conduct.

During the interval 21, the  $\pm \theta'_{I}$  quantity stored in buffer B27 will be transmitted to the adder AD5 through the AND network A86. At this same time, the AND network A87 will be conducting to supply the angle quantity in the buffer B23 to the adder AD5. Therefore, depending upon the octant in which the angle of  $\theta_I$  lies, adder AD5 will add to the quantity  $\pm \theta'_I$ (in B27) the proper angle quantity which is in buffer B23 to devise the absolute value of the angle of  $\theta_1$ which is transmitted through A82 into the buffer B25. During the interval 22, the quantity  $\theta_r$  is transmitted from the buffer B25 through the twos complement TC8 A70-A74 are negated as indicated by the 0's at their 45 and the conducting AND network 88 into the buffer B34 as  $-\theta_I$  and the quantity + |BB| in buffer B9 is transmitted through the twos complement TC4 and the conducting AND network A35 into buffer B10 as the quantity -|BB|.

During the interval 23, the quantity -|BB| from the buffer B10 and the quantity + |AA| from the buffer B11 are supplied to the adder AD4 through the AND networks A37 and A37A and the total AA-BB is supplied through the AND network A38 to the buffer B8A which checks the sign to determine which is the larger, the quantity |AA| or the quantity |BB|. If the quantity |AA| is larger, a plus quantity will be in buffer B8A and the flip-flops F1 and F2 will have logical 0 output signals at their S output terminals. If, however, the quantity |BB| is larger than the quantity |AA|, the quantity in the buffer B8A will be negative and the flipflops F1 and F2 will have logical 1 output signals at their S output terminals. As discussed above, the sequence network 28 will render the AND network A17 conductive to supply this logical 1 signal to flipflop F3. If |AA| is greater than |BB| and consequently the LGRV then AND networks A42 and A43 are conductive (time interval 24) and this signal is transmitted into the buffer B12. If, however, |BB| is larger than |AA|, then |AA|, is SMLRV and the AND networks A41 and A45 will be conducting and SMLRV will be deposited in the buffer B14.

During the interval 25, the quantity |BB| in buffer B9 will be transmitted to one of the buffers B12 and B14. If the quantity |BB| is SMLRV then the AND networks A40 and A45 will be rendered conducting and it will go into the buffer B14. If, however, the quantity |BB| is greater than the quantity |AA| then it is LGRV and the networks A39 and A43 will be rendered conducting and the quantity LGRV will be deposited in the buffer 12.

During the interval 26, the quantity LGRV from the buffer B12 is transmitted to the denominator or divisor terminal D of the divide network D1 through the conducting AND circuits A47 and A51 and the quantity SMLRV is transmitted from the buffer B14 to the nu- 20 merator or dividend terminal N of the divide network D1 through the now-conducting AND networks A49 and A52. The output quantity SMLRV/LGRV of the divide network D1 then flows into the buffer B16 through the conducting AND network A53.

During the interval 27, the quantity SMLRV/LGRV, which is the tangent of  $\theta'_{\nu}$ , is transmitted to the twopart look-up table L1 through the conducting AND network A55. The magnitude of the tangent of  $\theta'_{\nu}$ selects a circuit through which the tangent of  $\theta'_I$  quantity SMLRI/LGRI from the buffer B17 will flow into the second part of the look-up table L1 through the AND network A56. The output of the second part of the twopart look-up table L1 supplies an output quantity (128)  $(\cos\theta'_I\theta'_V)$  to the buffer B18.

During this same interval 27, the quantity SMLRV/LGRV in B16 which is equal to the tangent of the angle  $\theta'_{\nu}$  is supplied through the AND network A65 to the look-up table L2. The output of table L2 is a quantity equal to the magnitude of the angle  $\theta'_{\nu}$  and is stored in buffer B22.

The octant of the angle  $\theta_v$  is determined by the AND networks A67-A74 under control of the flip-flops F3, F5, and F7 which flip-flops control the AND networks 45 lower limit of the magnitude of Z (Z<sub>LIMIT</sub>) and is stored A67-A74 in the manner described in connection with the octant determination of  $\theta_I$  above. If angle  $\theta_V$  is in the first, third, fifth, or seventh octant, the output signal of OR will be a logical 0 and the output of flip-flop F9 will be a logical 0, so that the magnitude of the angle 50 and A96 are rendered conducting to supply the +Z<sub>LIMIT</sub>  $\theta'_{\nu}$  will be deposited in the buffer B27 as  $+\theta'_{\nu}$ . If the angle is in the second, fourth, sixth, or eighth octant, a logical 1 signal will be supplied by the OR network and a logical 1 signal will be supplied by the flip-flop F9 to the AND networks A85 and A92 whereby the quantity 55  $-\theta'_{\nu}$  is stored in the buffer B27.

During the time interval 28 the quantity (128) (Cos  $\theta'_1$ )/(Cos  $\theta'_v$ ) from the buffer B18 and the quantity LGRV from the buffer B12 are supplied to the input of the multiplier M2 through the conducting AND networks A58, A47 and A57 as absolute numbers. The product output of the multiplier M2 is supplied as a 32 bit number to the 32 bit latch or buffer B19.

During the time interval 29, the 16 bit quantity LGRI stored in the buffer B20 is transmitted to the denominator input D of the dividing network D2, through the conducting AND network A64 and the 32 bit quantity

(128)  $(\cos\theta'_I)$  (LGRV)/COS $\theta'_V$  stored in the buffer B19 is transmitted to the numerator terminal N of the dividing network D2 through the 32 bit AND network A63. The resulting output of network D2 is a 16 bit quantity [(128)  $(\cos\theta'_I)$  (LGRV)/ $\cos\theta'_V$ LGRI], equal to the quantity Z and is deposited in the buffer B21. As will be discussed more fully in connection with FIG. 15, the divider D2 includes an overflow indicator whereby the quantity supplied to buffer B21 will be a maximum positive 15 bit quantity should the quotient be a quantity which cannot be expressed in 15 bits.

During the time interval 30, the quantity in buffer B27 which is either  $-\theta'_{\nu}$  of  $+\theta'_{\nu}$ , depending upon the octant of  $\theta_v$  is supplied to one terminal of the adder ADS through the AND network A86 and the angle quantity stored in the buffer B23 is supplied to the other terminal of the adder AD5 through the AND network A87. The output of AD5 is the magnitude of the angle  $\theta_V$  and flows to buffer B24 through the AND network A81. Also, during the time interval 30, the quantity Z in the buffer B21 flows through the conducting AND network A95 and the twos complement network TC9 and to the buffer B30 as the quantity -Z.

During the interval 31, the quantity  $\theta_V$  from the buffer B24 and the quantity  $-\theta_I$  from the buffer B34 is supplied to the adder AD6. The sum quantity  $(\theta_V - \theta_I)$ passes through the conducting AND network A93 into the buffer B29 and is equal to angle  $\theta_z$  the impedance angle. The magnitude of angle  $\theta_z$  is supplied to the sign checking buffer B8A through the AND network A94. If the magnitude of this quantity is negative the flip-flop F1 and F2 will be actuated to render the AND circuit 84 conducting whereby the quantity 360 is supplied to one terminal of the adder AD7. During the time interval 32, the AND network A83 conducts and transmits the magnitude of the angle  $\theta_{V}$  to the other terminal of the AD7. The output quantity of the adder AD7 is the value of  $+\theta_z$  which is transmitted to the buffer B28 through the AND network A89.

During the time interval 33, the AND network A97 is rendered conducting to supply the magnitude  $+\theta_z$  to the look-up table L3. The output of the table L3 is the in the buffer B31.  $Z_{LIMIT}$  is the minimum limit of Z which does not represent a fault within the reach of the relay 10.

During the time interval 34, the AND networks A98 quantity from the buffer B31 and the -Z quantity from buffer 30 to the adder AD8. The sum thereof (+Z<sub>LIMIT</sub>-Z) is supplied through the AND network A99 to the buffer B32 as  $\Delta Z$ .

If the magnitude of  $\Delta Z$  is a negative quantity no fault exists within the reach of the relay 10. Conversely, if the magnitude of  $\Delta Z$  is positive, a fault should exist within the reach of the relay 10. In order to insure the maximum security of the line and not deenergize the line falsely, the first  $\Delta Z$  which indicates a fault within the reach of the relay 10 will not trip the breaker. To trip, there must be at least two consecutive  $\Delta Z$  trip signals. Since these ΔZ quantities are supplied each ½ω seconds or every  $1.3263 \times 10^3$  seconds, the use of two successive fault signals will not cause excessive damage to the line even with a close in fault and a stiff bus supply.

In accordance with my invention, I provide a Trip-No-Trip determining network 34 which requires an increasing number of  $\Delta Z$  trip signals as the location of the fault approaches the reach limit of the relay 10. The operation of the network 34 will first be described assuming a no-fault line condition in which the  $\Delta Z$ 's are negative or at the most only an occasional positive  $\Delta Z$ which may be caused by transients or otherwise. The first  $\Delta Z$ , which is provided as described, will be transmitted by the AND network A100 to the one input terminal of the adder AD9 during the time interval 35 and will be assumed to be of a magnitude equal to -30. At the same time interval, the quantity in the buffer B33 (assumed to be -200) will be transmitted through the AND network A101 to the other input terminal of the adder AD9.

Thereafter, during the time interval 36, the output quantity of the adder AD9 (-230) will be transmitted to the buffer B33 through the AND network A102. 20 During the time interval 37, the -230 quantity is supplied to one terminal of the adder AD10. When a negative sign is supplied to the flip-flop F10 through the AND network A104 it provides a "clear" signal to the counter CTR which, if it had been energized to a count, 25 will be returned to 0. The -230 quantity supplied to the adder AD10 will be added to the Z bias signal which has the magnitude +200. The resultant sum output of the adder AD10 will be negative (-30), and when AND network A105 conducts the negative sign, 30 will be supplied to the flip-flop F11. With a positive input sign, the flip-flop F11 supplies a logical 0 signal to the AND network A106. Conversely with a negative input supplier to the flip-flop F11 a logical 1 signal is transmitted to the enable input of the AND network A106. This logical 1 signal causes the AND network A106 (internal 38) to supply a quantity -200 from the -Z bias to reset buffer B33 to a -200 quantity. This resetting of buffer B33 occurs each time the quantity supplied thereto from the adder AD9 is greater than -200.

It will be appreciated from the foregoing that whenever a series of  $+\Delta Z$  signals is supplied, the quantity stored in buffer B33 will become less and less negative 45 at a rate depending upon the magnitude of these + signals. Since the flip-flop F11 resets the buffer B33 only when its quantity decreases below -200, the + quantities will eventually put a + quantity in the buffer B33. When this occurs, the next time in which AND 50 network A104 conducts it will place a + input sign on the input of flip-flop F10. This causes the flip-flop F10 to transmit a count signal to the counter CTR. If thereafter a second + signal is transmitted by the adder AD9 the subsequent conduction of the AND networks 55 A102 and A104 will supply a + sign to and actuate the flip-flop F10 to supply a second signal to the count input CT of the counter CTR. The counter CTR at a second count signal will actuate the trip circuit of the

It will be appreciated that a close-in fault will cause  $\Delta Z$  to be a positive quantity approaching  $Z_{LIMIT}$  and if such quantity is +201 or greater the counter CTR will actuate the trip circuit at the second  $\Delta Z$  output. If, however, the fault is closer to the reach or decision making point, the value of  $+\Delta Z$  will be less and a greater number of  $\Delta Z$  signals will be required to over-

come the -200 quantity which is initially stored in the buffer B33. This permits a longer decision making period which is permissible because the fault current will be less at the more remote fault location. An initial -200 quantity can be stored in buffer B33 by closing the manually operable switch MS1 to render AND network A107 conducting. This will prevent any false tripping due to an uncontrolled + quantity in buffer B33.

It will be appreciated that if desired the elements of FIG. 4 may be combined and reduced in number. As for example, a single adder, a single multiply network, a single divide network, and a single analog to digital sampler with a plurality of buffer or storage networks which hold the various quantities and provide these quantities to the networks which manipulate them could be used. Such an apparatus could be a general purpose digital computer such as the Prodac-2000 computer sold by Westinghouse Electric Corporation which may be programmed to manipulate the quantities  $V_{KP1}$ ;  $V_{K}$ ;  $V_{KM1}$ ;  $I_{KP1}$ ;  $I_{K}$ , and  $I_{KM1}$  into the quantities Z,  $\theta_Z$ , and  $\Delta Z$  and finally into the decision made output quantity for the trip circuit.

In the form of the invention illustrated in FIG. 8, analog quantities derived by differentiating the analog current and voltage quantities are utilized. The current in line 100 is sampled by the current transformer 102 and the quantity is filtered in the low pass filter 104 and is supplied as the quantity  $(I_X + I_P \sin \omega t)$  to the differentiating and multiplying network 106. The filter effectively removes any high frequency in the output of the transformer 102, however, any low of change transient passes through as the quantity  $I_X$ . The network 106 includes an operational amplifier 108 having a feedback resistor  $R_I$  and an input capacitor  $C_I$  and provides an output quantity  $-R_IC_1$  (di/dt). The values of  $R_1$  and  $C_1$  are chosen to equal  $1/\omega$  whereby the output quantity of network 106 equals the quantity  $-I_P$   $Cos \omega t$ .

This quantity is supplied to a second differentiating and multiplying network 110 wherein the values of  $R_2$  and  $C_2$  are chosen to equal  $1/\omega$  whereby the output quantity of network 110 will equal  $I_P \sin \omega t$ . The quantity  $-I_P \cos \omega t$  is supplied to both input terminals of a first multiplier network 112 so that it is effectively squared and becomes  $(I_P)^2(\cos^2\omega t)$ . Similarly the quantity  $(-I_P \sin \omega t)$  is squared by the second multiplier network 114 and becomes  $(I_P)^2(\sin^2 \omega t)$ . Any suitable analog multiplying network may be used such as the multiplier sold by Intronics Incorporated and designated model M420.

The quantities  $I_P^2$  ( $\cos^2 \omega t$  and  $I_P^2 \sin^2 \omega t$ ) are supplied to the two input terminals of an operational amplifier summing network 116 which provides the quantity  $I_P^2$  ( $\cos^2 \omega t + \sin^2 \omega t$ ). Since  $\cos^2 \omega t + \sin^2 \omega t$  equals unity the output quantity of network becomes  $I_P^2$ .

Similarly as described, the bus or line voltage is sampled by the potential transformer 118 passes AND through the low pass filter 120 so that the quantity  $(V_X+V_P\sin\omega t)$  is supplied to the differentiating and multiplying network 122. This network, like the network 106, is adjusted to provide a multiplication factor of  $1/\omega$  and its output quantity becomes  $(-V_P\cos\omega t)$  and is supplied to the differentiating and multiplying network 124. The network 124 like the network 110 is

adjusted to provide the multiplication factor of  $1/\omega$ whereby its output becomes  $(+V_P \sin \omega t)$ . The quantities  $(-V_P \cos \omega t)$  and  $(+V_P \sin \omega t)$  are squared by the multipliers 126 and 128 and the squared quantities are added together by the adder 130 to provide the quantity  $V_P$ .

The quantities  $I_P^2$  and  $V_P^2$  are supplied to the denominator and numerator terminals, respectively, of the dividing network 132 to provide an output quantity Z<sup>2</sup>. The dividing network 132 may take any of various forms, as for example, the analog divider sold by Intronics Incorporated as model D401. The output quantity Z<sup>2</sup> actuates a timer 134 through a NOT network 136 and a zener diode 138. The network 136 and timer 134 may be similar to the NOT network 68 and timer 62 of Altfather U.S. Pat. No. 3,443,159, dated May 6, 1969 with a time interval of 4/0 milliseconds. The zener diode interrupts the logical 1 signal and supplies a logical 0 signal to the NOT network 136 when the value of 20 Z is less than the critical reach value or  $Z_{LIMIT}$ representing the maximum reach of the relay. Therefore, when the value of Z becomes less than  $Z_{LIMIT}$  the zener diode 136 supplies an 0 logical signal to network 136 which initiates the 4 millisecond timing of the 25 take the form as illustrated in FIGS. 13A, 13B, and timer 134. If the value of Z remains less for the complete 4 ms timing of timer 134, the timer actuates the trip network 140. If the value of Z does not remain less than Z<sub>LIMIT</sub>, then the NOT network 136 resets the timer without intended delay as indicated by the 30 designation 4/0.

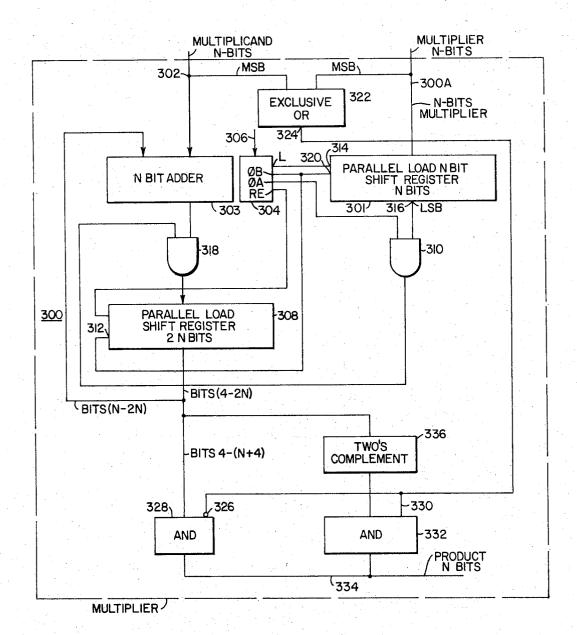

FIG. 4 is a block diagram showing AND networks having the prefix A, buffer or storage networks having the prefix B, adder networks having the prefix AD, multiplying networks having the prefix M, dividing networks having the prefix D, twos complement networks having the prefix TC and look-up tables having the prefix L. For purposes of simplicity, single lines interconnect these blocks as if single bit numbers are used. In reality multiple bit numbers are used in the handling of quantities. The number of bits is not important beyond the necessity of having a sufficient number to determine the quantities with a reasonable degree of accuracy. For example, 16 bit quantities may be used 45 except where discussed as being otherwise.

By having the number of bits equal to an even multiple of 4, standard chips may be utilized to make up the blocks. In some instances the AND network controlling the input to a buffer may be combined with the buffer 50 into a single chip. As for example, the AND network A1V and buffer B1V may take the form of four "Four Bit AND and Latch" chips, as for example, the Texas Instrument chips SN 74175 (see FIG. 9). Similarly the AND networks which follow a latch or buffer such as 55 network A4V following a latch or buffer B1V may comprise four chips such as Texas Instrument chips SN 7409 (see FIG. 10). Chips SN 7409 may also be used for AND networks A7, A8, A22, among others. The buffer networks supplied from two or more AND networks may take the form of the combined AND and latch of FIG. 9. However, in this instance the load latch signal is applied to the combination after the AND gate is opened to permit the new quantity to be supplied 65 thereto and latched in the combination AND and latch.

The adders AD may take the form of four chips such as the Texas Instrument chips SN 7483 (FIG. 11)

wherein the 16A inputs are connected to receive the 16 output bits of one of the amounts to be added and the 16B inputs are connected to receive the 16 output bits of the other of the amounts to be added. A logical 0 is supplied to the C0 input of the chip having the least significant number supplied thereto. The C4 output of the first chip is supplied to the C0 input of the second chip,

The twos complement TC may, for example, take the form of four Texas Instrument chips SN 7483 as used in the adder (FIG. 11) and four chips Texas Instrument SN 7403 (FIG. 12). The A rather than the A signals are supplied by the chip SN 7403 to the A inputs of the chips SN 7483. The chips have their input B1, B2, B3, and B4 supplied with logical 0 signals. A logical 1 signal is supplied the C0 terminal of the chip having the least significant four bits supplied thereto. The second chip which is supplied with the second least significant four bits has its least significant bit input C0 connected to the C4 terminal of the first chip. The remaining third and fourth chips SN 7483 are similarly connected together and to the second chip.

The look-up networks or tables L1, L2, and L3 may 13C, respectively. The look-up table L1 (FIG. 13A) comprises a plural number of decode and memory cells such as the Texas Instrument SN 54/7488 chips. Assuming an eight bit output, 17 SN 54/7488 chips 501-517 will be used to provide an eight bit output which will provide a satisfactory accuracy for lookup table L1 without necessitating the use of an undue number of chips. The look-up table L1 is of the two part type which provides 289 addresses. The five binary select input terminals A, B, C, D, and E, respectively, of the chips 510-517 are connected in parallel with each other and selectively to the five least significant bits of the 16 bit output of the buffer B16 through AND 40

The least significant five of the 16 bit output of buffer B17, namely bits  $A_0$ - $A_4$  and their complements  $A_0-A_4$  are connected to the five input circuits 1, 2, 3, 4, and 5 of the memory enable circuits of the chips 501-517. The complement or bar signals  $\overline{A}_3$  and  $A_4$  of the two most significant of the five utilized bits of buffer B17 are connected to the input lead 4 of the chips 510-508 and 517 and to the lead five of the chips 501-516. The status or real signals of the least significant bit of the two most significant bits used A<sub>3</sub> is connected to the enable circuits 4 of the 509-516 chips. The status or real signal of the most significant of the two most significant bits used A<sub>4</sub> is connected to the memory enable circuit 5 of the 517 chip. The memory enable circuit 1 the chips 501, 503, 505, 507, 509, 511, 513, 515, and 517 are connected to the complement signal A<sub>0</sub>, while the memory enable circuit 1 of the chips 502, 504, 506, 508, 510, 512, 514, and 516 are connected to the status signal Ao of the least significant of the five used bits of the buffer B17. The memory enable circuit 1 of the chips 501, 502, 505, 506, 509, 510, 513, 514, and 517 are connected to the complement or bar signal A<sub>1</sub>, while the chips 503, 504, 507, 508, 511, 512, 515 and 516 are connected to the status signals A, of the second least significant of the five used bits of buffer B17. The memory enable circuits of the chips 501-504, 509-512 & 517 are connected to the complement or bar signal  $\overline{A}_2$  while the chips 505-508 and 513-516 are connected to the status signals A2 of the third least significant bit of the five used bits of the buffer B17. Each of the respective eight outputs F-M of the chips 501-517 are individually connected together 5 to provide an eight bit output to the buffer B18 which is equal to (128)  $\cos\theta'_I/\cos\theta'_V$ .

The look-up table L2, (FIG. 13B) is a 17 place table and consequently needs no more than a 5 bit address with a six bit output and as such may utilize a single chip (SN 54/7488) rather than the plural chips used for the table L1. The five bit address which comprises the five least significant output bits of the one of the buffers B16 or B17 which happens to be connected thereto by the AND networks A65 or A66. A logical 0 is applied to the memory enable. The output bits will be supplied by the outputs 1-6.

The look-up table L3 (FIG. 13C) is a 361 place table. An address of 8 bits is supplied thereto from buffer B28 and an eight bit output is provided thereby to buffer B31. This table L3 comprises six chips 520-521 (SN 54/7488). The like numbered output connections F-M of each chip are respectively connected together nections A-E are connected respectively to the least significant five bits of the eight bit address with connection A connected to the least and connection E connected to the most significant of the five least significant bits. The status and complement signals of the 30 three most significant bits of the eight bit address are connected to three memory enable circuits 1, 2, and 3 of the memory enable in the manner set forth with respect to enable circuits 1-3 of FIG. 13A.

The analog to digital converter  $A/D_I$  and  $A/D_V$  are <sup>35</sup> alike and, for example, may be the multiplier digitizer sold by Xerox Data System as type MD 41 and described in their publication No. 901254c, dated July 15, 1968. This device will digitize a ±10 volt input signal to a 15 bit quantity, of which the upper 14 bits are used. The most significant or sign bit 14 is strapped to the top three bits of the current and voltage magnitude storage buffers through the AND's A<sub>1</sub>-A<sub>3</sub> in an extended manner so that the most significant bit 15 of 45 the 16 bit signal will be the sign bit. The input signal for the A/D<sub>1</sub> is derived from a current transformer through a low pass filter while the input signal for the  $A/D_V$  is derived from a potential transformer through a second low pass filter. The converters are each pulsed to 50 digitize the voltage and current signals at time intervals 0, 20, and 40, and multiples thereof by the sequence control 28.

The flip-flops or flags F3-F9 are single bit devices and may take any of various forms. They should be 55 devices which will be actuated to provide a logical 1 or 0 output signal in response to the application thereto of a logical 1 or 0 signal at the time a triggering pulse is applied to the respective input controlling AND network associated therewith and to maintain the logical 60 signal until reset by the application of a subsequent triggering pulse. If desired, one of the bit circuits and the latch signal of the chip of FIG. 9 could be utilized. In such event the latch signal input would be energized during the interval that the respective input AND network is enabled to energize the respective flag network. In the case of the flags F3-F9 the input ANDs could be

eliminated and the flags controlled by a trigger signal from the sequence control subsequent to the time that the flag input signal is present (during the interval that the respective input AND is rendered conducting).

Buffer 8A is similar to the buffer or latch illustrated in FIG. 9. Its sign checking function is obtained by connecting the input terminal of flip-flop F1 to the most significant bit 15 of the buffer B8A, which is utilized as the sign bit. When the bit 15 is a logical 1 the flip-flop F1 is set to place a logical 1 at its set output terminal S indicating a negative sign of the quantity in buffer B8A and conversely the flip-flop F1 will be reset to place a logical 1 at its R output when the bit 15 is a logical 0 indicating a positive number in buffer B8A.

It will be apparent from FIG. 4 that a positive quantity in buffer B8A will result in a first enabling logical 1 signal from flip-flop F1 into AND A25 and a disabling logical 0 signal into AND A26. Therefore the positive quantity is transferred to buffer B9 through AND A25 upon the application of the trigger signal from the sequencing control 28. Conversely, a negative quantity in buffer B8A causes a first enabling logical 1 signal to be applied to ANDs A26 and A27, whereby the negaas are the binary select connections A-E. These con- 25 tive quantity is transferred into the buffer B9 as a positive quantity. It will be appreciated that a logical 1 signal can be applied to the flip-flops F3-F8 only if a negative quantity is in the buffer B8A at the time the proper AND network is rendered conducting by the sequencing control 28.

> The flip-flop F9 is similarly controlled by the OR network OR which supplied a logical 1 signal when a logical 1 signal is supplied to any of its input connections from the AND networks A68, A70, A71, and A73. The logical 1, so supplied, causes flip-flop F9 to supply a logical 1 signal to be supplied to the AND network A85, A81, and A92. Since the AND network A92 has a NOT input the logical 1 output of F9 disables the AND A92 and provides a first enabling signal to the ANDs A85 and A91. Conversely, a logical 0 from flip-flop F9 disables A85 and A91 and provides a first enabling signal to AND A92.

The AND network A104 and flip-flop F10 combination may take the form described above in connection with the F3-F8 networks except that a second or complement signal is utilized and which may be derived by the use of a NOT output terminal. The input of A104 is supplied from the sign bit or 15th bit of the signal in buffer B33. The AND network A105 and flip-flop F11 combination is likewise similar and its logical 1 output supplies a first enabling signal to the AND network A106. The output bit 15 of adder AD10 which is energized by the sign bit is negated so that when the bit 15 indicates a negative sum quantity it supplies a logical 1 to the A105-F11 combination to cause a logical 1 enabling quantity to be supplied to the AND network A106 so that the network A106 will transmit a -200 quantity to the buffer under control of the sequencing control 28 as described above.

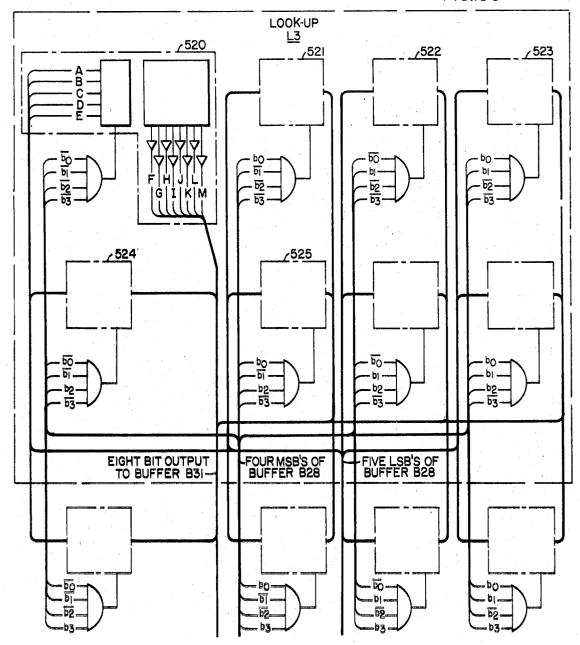

FIG. 14 shows schematically one form of multiplying network 300 which may be used for the multipliers M1 and M2. One of the quantities, which is designated as the multiplier in FIG. 14, is supplied as a 16 bit quantity by the conductor means 300A to the shift register 301. The shift register may, for example, be a Texas Instrument SN 74195 device. The other quantity, which is designated the multiplicand, is supplied as a 16 bit quantity by the conductor means 302 to the adder 303 which, for example, may be a Texas Instrument SN 7483 device. At the proper time interval (see FIG. 5B) the sequence control 28 opens the proper ANDs and 5 the quantities to be multiplied are supplied to the multiplying network. At this same time, the sequence control 28 supplies an initiating pulse to the pulse timer 304 through the lead 306. When initiated, the timer 304 supplies a reset pulse RE to the reset input of shift register 308 and a pulse L to the loading input terminal 314 of register 301. After the short time interval required to load the quantities, the timer 304 provides an N number square wave spaced main pulses as there are bits in the quantities which in this instance is 16. These N main pulses sequence the N operations required to multiply the input quantities after which the timer 304 will reset itself for its next operation.

Each N main pulse comprises two sequentially oc- 20 curring pulses  $\phi_A$  and  $\phi_B$ . Assuming the timer 304 has been initiated and the initial loading pulse has been supplied to the N bit multiplier register 301 and the multiplier loaded therein and the resulting pulse RE has been applied to and has reset the 2N bit register 308, 25 the next  $\phi_A$  pulse will enable the AND 310. If the LSB bit in register 301 at output terminal 316 is a 1, the AND 310 will conduct and enable the AND 318 to load the N bit sum from adder 303 into the N most significant bits of the register 308. Since initially the bits in 30 register 308 are all 0's, this N bit sum will be the N bit multiplicand which in the case of M1 is derived from buffer B7 and which in the case of M2 is derived from buffer B18. If the LSB at terminal 316 is a logical 0 the sum from the adder 303 will not be loaded into the register 308.

After the  $\phi_A$  logical 1 pulse is terminated, a logical 1  $\phi_B$  pulse will occur which is applied to the shift input terminal 312 of register 308 and the shift input terminal 320 of the register 301. This shifts the least significant bit LSB of the N most significant bits in the register 308 into the most significant of the N least significant bits. The shift in register 301 connects the next least significant bit of the multiplier to the LSB terminal 316 and the operation described is repeated N times, whereby the product will appear in the register 308.

In the case of multiplier M2 the desired product loaded into buffer B19 should be equal to 16 times the actual product of the multiplicand and multiplier supplied thereto. For this purpose the 16 bits loaded into the buffer are bits 5-21 (4-20 if the least significant bit is numbered 0). The product of M2 will always be positive because absolute or positive values are supplied as both the multiplicand and multiplier.

In the case of M1 the product will be plus or minus, depending upon the sign of the quantity in buffer B7. The most significant bit is utilized on the sign bit and if a logical 0, the quantity is positive and if a logical 1, the quantity is negative. The sign bits of the multiplicand and multiplier are supplied to the two input terminals of an exclusive OR 322. The output terminal 324 of OR 322 is supplied to the NOT input 326 of AND 328 and to the real input 330 of AND 332. If the sign of each the multiplicand and multiplier is the same, a logical 0 signal is supplied by the OR 322 and the AND 328 is effective to transmit the N bit product in the register 308

as a positive number through the output conductors 334 to buffer B8A. If the signs of multiplicand and multiplier are different, the OR provides a logical 1 and the negative product in the register is transmitted through a twos complement 336 (see FIG. 13), the AND 332, and conductors 334 to the buffer B8A.

FIG. 15 shows schematically one form of dividing network 400 which may be used for the dividers D1 and D2. The numerator or dividend input will provide 2N or 32 bits. The least significant bits of the dividend are supplied to the 16 bit parallel input 401 of the shift register 402 which may for example be of the Texas Instrument type (SN 74195). The 16 most significant bits of the dividend are supplied to the 16 bit parallel input 403 of the shift register 404. The divisor is a 16 bit quantity and is supplied to one parallel input 406 of the parallel adder 408 through a twos complement 409. The twos complement may take the form illustrated in FIG. 12, wherein the adder may take the form illustrated in FIG. 11.

The most significant bits MSB from the registers 402 and 404 are serially supplied to the least significant bit LSB serial input 410 of the shift register 411. The 16 bit quantity in the register 411 is supplied to the other parallel input 415 of the adder 408. The 16 bit output sum from the 16 bit output 417 of the adder 408 is connected to the parallel input 412 of the register 411, and the output sum may be loaded in the register 411 when a logical 1 signal is supplied to the loading control input 424.