(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5111867号

(P5111867)

(45) 発行日 平成25年1月9日(2013.1.9)

(24) 登録日 平成24年10月19日(2012.10.19)

(51) Int.Cl.

F 1

|             |               |                  |      |        |         |

|-------------|---------------|------------------|------|--------|---------|

| <b>G09F</b> | <b>9/30</b>   | <b>(2006.01)</b> | G09F | 9/30   | 3 3 8   |

| <b>H01L</b> | <b>29/786</b> | <b>(2006.01)</b> | H01L | 29/78  | 6 1 6 V |

| <b>H01L</b> | <b>21/336</b> | <b>(2006.01)</b> | H01L | 29/78  | 6 1 8 B |

| <b>G02F</b> | <b>1/1368</b> | <b>(2006.01)</b> | H01L | 29/78  | 6 1 2 Z |

|             |               |                  | GO2F | 1/1368 |         |

請求項の数 8 (全 39 頁)

(21) 出願番号

特願2007-6570 (P2007-6570)

(22) 出願日

平成19年1月16日 (2007.1.16)

(65) 公開番号

特開2008-175842 (P2008-175842A)

(43) 公開日

平成20年7月31日 (2008.7.31)

審査請求日

平成21年6月23日 (2009.6.23)

(73) 特許権者 502356528

株式会社ジャパンディスプレイイースト

千葉県茂原市早野3300番地

(74) 代理人 100075959

弁理士 小林 保

(73) 特許権者 506087819

パナソニック液晶ディスプレイ株式会社

兵庫県姫路市飾磨区妻鹿日田町1-6

(74) 代理人 100075959

弁理士 小林 保

(74) 代理人 110000154

特許業務法人はるか国際特許事務所

(72) 発明者 河村 哲史

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上の画素領域に、

ソース信号線と、薄膜トランジスタのソース領域部と、チャネル領域部（ゲート電極の直下の部分）と、ドレイン領域部と、画素電極とを、第1透明酸化物層で形成される同一の層に一体的に形成し、

前記チャネル領域部はキャリア濃度が低くシート抵抗が高い膜（半導体層）として形成してなり、

前記第1透明酸化物層の上に、絶縁膜を形成し、

前記絶縁膜の上に、ゲート信号線および該ゲート信号線に接続される薄膜トランジスタのゲート電極を第2透明酸化物層で形成される同一の層に一体的に形成し、

前記第2透明酸化物層にレーザ光を照射して前記ゲート信号線および薄膜トランジスタのゲート電極を結晶改質してキャリア濃度が高くシート抵抗が低い膜（導体層）として形成してなる

ことを特徴とする表示装置。

## 【請求項 2】

前記第1透明酸化物層は、ZnOによって構成したものであることを特徴とする請求項1に記載の表示装置。

## 【請求項 3】

前記基板の液晶側の画素領域には、

10

20

前記絶縁膜上に第1絶縁膜を介して該画素電極に重畠して配置されるとともに、並設された複数の電極からなる櫛歯状電極として構成され該画素電極との間で電界を生じさせる対向電極を有し、

前記対向電極の各電極の中途部において該対向電極と一体となって前記ゲート信号線とほぼ平行に走行するコモン信号線を形成し、

前記コモン信号線を通して映像信号に対して基準となる基準電圧を前記櫛歯状電極に印加するようにしたことを特徴とする請求項1に記載の表示装置。

#### 【請求項4】

前記絶縁膜は画素領域の全域に形成されていることを特徴とする請求項1に記載の表示装置。 10

#### 【請求項5】

前記導体層は、画素領域の全域に形成された第2透明酸化物層を選択的に導電体化させて形成されていることを特徴とする請求項1に記載の表示装置。

#### 【請求項6】

前記第1透明酸化物層に、前記ゲート電極の直下のチャネル領域部とソース領域部およびドレイン領域部のそれぞれの間に、前記ソース領域部およびドレイン領域部よりもキャリア濃度の低いLDD領域部（電界緩和領域）が形成されていることを特徴する請求項1に記載の表示装置。

#### 【請求項7】

前記第1透明酸化物層のソース信号線を構成する部分の上層あるいは下層に金属層が形成されていることを特徴とする請求項1に記載の表示装置。 20

#### 【請求項8】

基板上の画素領域に、

ソース信号線と、薄膜トランジスタのソース領域部と、チャネル領域部（ゲート電極の直下の部分）と、ドレイン領域部と、画素電極とを同一の層で一体的に形成する第1透明酸化物層および金属層がそのいずれかを上層として形成し、

前記チャネル領域部はキャリア濃度が低くシート抵抗が高い膜（半導体層）として形成してなり、

前記第1透明酸化物層の上に、絶縁膜を形成し、

前記絶縁膜の上に、ゲート信号線および該ゲート信号線に接続される薄膜トランジスタのゲート電極を第2透明酸化物層で形成される同一の層に一体的に形成し、 30

前記第2透明酸化物層にレーザ光を照射して前記ゲート信号線および薄膜トランジスタのゲート電極を結晶改質してキャリア濃度が高くシート抵抗が低い膜（導体層）として形成してなり、

前記金属層はソース信号線を構成し、

前記第1透明酸化物層は少なくとも前記ゲート電極の直下のチャネル領域部を除いた他の領域が導電体化され、該導電体化された部分で前記ソース信号線と接続された薄膜トランジスタのソース領域部、画素電極、該画素電極に接続される前記薄膜トランジスタのドレイン領域部を構成している

ことを特徴とする表示装置。 40

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は表示装置に係り、各画素に薄膜トランジスタを備える表示装置に関する。

##### 【背景技術】

##### 【0002】

たとえばアクティブ・マトリックス型の液晶表示装置は、液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、x方向に延在されy方向に並設されるゲート信号線とy方向に延在されx方向に並設されるソース信号線とで囲まれた領域を画素領域とし、この画素領域には、少なくとも、該ゲート信号線からの信号（走査信号）によって才 50

ンされる前記薄膜トランジスタと、このオンされた該薄膜トランジスタを介して前記ソース信号線からの映像信号が供給される画素電極とを備えて構成されている。

**【0003】**

そして、前記薄膜トランジスタ、ゲート信号線、ソース信号線、および画素電極等は、フォトリソグラフィ技術による選択エッチングによって所望のパターンに形成された導電層、半導体層、絶縁膜等を所望の順序で基板上に積層させることによって形成されている。

**【0004】**

このような構成からなる表示装置は、フォトリソグラフィ技術による選択エッチングの工程数を低減させることが要望され、たとえば、基板上に形成された半導体材料膜を、その所定の領域に導電性を付与することによって、薄膜トランジスタのチャネル領域部、ソース領域部およびドレイン領域部に加工するとともに、該ドレイン領域部に接続される画素電極を形成する技術が知られている（特許文献1参照）。

【特許文献1】特開2003-50405号公報

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0005】**

しかし、上記特許文献1に記載された表示装置は、ソース信号線が前記半導体材料膜とは別個に形成したものであり、それらの形成においてそれぞれの選択エッチング工程を必要とすることを免れないものとなっていた。

**【0006】**

また、前記ソース信号線は、その形成の際のマスク合わせの限界から、前記半導体材料膜の領域の一部として形成される画素電極と狭い間隔で配置せざるを得ないものとなっていた。このため、画素の開口率の向上に限界を有するものとなっていた。

**【0007】**

本発明の目的は、製造工数を低減し得る構成の表示装置を提供することにある。

**【0008】**

また、本発明の他の目的は、画素の開口率の向上を図った表示装置を提供することにある。

**【課題を解決するための手段】**

**【0009】**

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

**【0010】**

(1) 本発明による表示装置は、たとえば、基板SUB上の画素領域に、

ソース信号線と、薄膜トランジスタのソース領域部と、チャネル領域部（ゲート電極の直下の部分）と、ドレイン領域部と、画素電極とを、第1透明酸化物層で形成される同一の層に一体的に形成し、

前記チャネル領域部はキャリア濃度が低くシート抵抗が高い膜（半導体層）として形成してなり、

前記第1透明酸化物層の上に、絶縁膜を形成し、

前記絶縁膜の上に、ゲート信号線および該ゲート信号線に接続される薄膜トランジスタのゲート電極を第2透明酸化物層で形成される同一の層に一体的に形成し、

前記第2透明酸化物層にレーザ光を照射して前記ゲート信号線および薄膜トランジスタのゲート電極を結晶改質してキャリア濃度が高くシート抵抗が低い膜（導体層）として形成してなることを特徴とする。

**【0011】**

(2) 本発明による表示装置は、たとえば、(1)の構成を前提とし、前記第1透明酸化物層を、ZnOによって構成したものであることを特徴とする。

**【0012】**

(3) 本発明による表示装置は、たとえば、(1)の構成を前提とし、前記基板SUB

10

20

30

40

50

の液晶側の画素領域には、

前記絶縁膜上に第1絶縁膜を介して該画素電極に重畠して配置されるとともに、並設された複数の電極からなる櫛歯状電極として構成され該画素電極との間で電界を生じさせる対向電極を有し、

前記対向電極の各電極の中途部において該対向電極と一体となって前記ゲート信号線とほぼ平行に走行するコモン信号線を形成し、

前記コモン信号線を通して映像信号に対して基準となる基準電圧を前記櫛歯状電極に印加するようにしたことを特徴とする。

#### 【0013】

(4) 本発明による表示装置は、たとえば、(1)の構成を前提とし、前記絶縁膜は画素領域の全域に形成されていることを特徴とする。 10

#### 【0016】

(5) 本発明による表示装置は、たとえば、(1)の構成を前提とし、前記導体層は、画素領域の全域に形成された第2透明酸化物層を選択的に導電体化させて形成されていることを特徴とする。

#### 【0017】

(6) 本発明による表示装置は、たとえば、(1)の構成を前提とし、前記第1透明酸化物層に、前記ゲート電極の直下のチャネル領域部とソース領域部およびドレイン領域部のそれぞれの間に、前記ソース領域部およびドレイン領域部よりもキャリア濃度の低いLD 20 D領域部(電界緩和領域)が形成されていることを特徴する。

#### 【0018】

(7) 本発明による表示装置は、たとえば、(1)の構成を前提とし、前記第1透明酸化物層のソース信号線を構成する部分の上層あるいは下層に金属層が形成されていることを特徴とする。

#### 【0019】

(8) 本発明による表示装置は、たとえば、基板上の画素領域に、ソース信号線と、薄膜トランジスタのソース領域部と、チャネル領域部(ゲート電極の直下の部分)と、ドレイン領域部と、画素電極とを同一の層で一体的に形成する第1透明酸化物層および金属層がそのいずれかを上層として形成し、

前記チャネル領域部はキャリア濃度が低くシート抵抗が高い膜(半導体層)として形成してなり、 30

前記第1透明酸化物層の上に、絶縁膜を形成し、

前記絶縁膜の上に、ゲート信号線および該ゲート信号線に接続される薄膜トランジスタのゲート電極を第2透明酸化物層で形成される同一の層に一体的に形成し、

前記第2透明酸化物層にレーザ光を照射して前記ゲート信号線および薄膜トランジスタのゲート電極を結晶改質してキャリア濃度が高くシート抵抗が低い膜(導体層)として形成してなり、

前記金属層はソース信号線を構成し、

前記第1透明酸化物層は少なくとも前記ゲート電極の直下のチャネル領域部を除いた他の領域が導電体化され、該導電体化された部分で前記ソース信号線と接続された薄膜トランジスタのソース領域部、画素電極、該画素電極に接続される前記薄膜トランジスタのドレイン領域部を構成していることを特徴とする。 40

#### 【0029】

なお、本発明は以上の構成に限定されず、本発明の技術思想を逸脱しない範囲で種々の変更が可能である。

#### 【発明の効果】

#### 【0030】

このように構成した表示装置は製造工数の低減し得る構成とすることができる。また、画素の開口率の向上を図ることができる。

#### 【発明を実施するための最良の形態】

10

20

30

40

50

**【 0 0 3 1 】**

以下、本発明による表示装置およびその製造方法の実施例について図面を用いて説明をする。

**【 0 0 3 2 】****実施例 1**

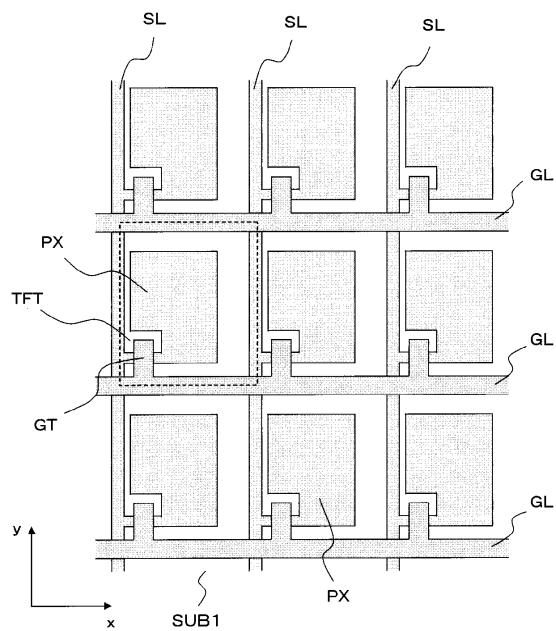

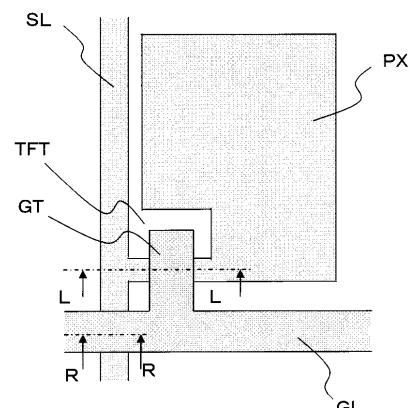

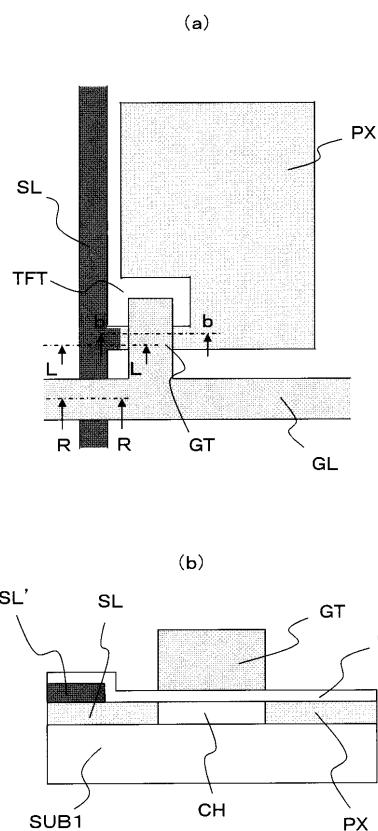

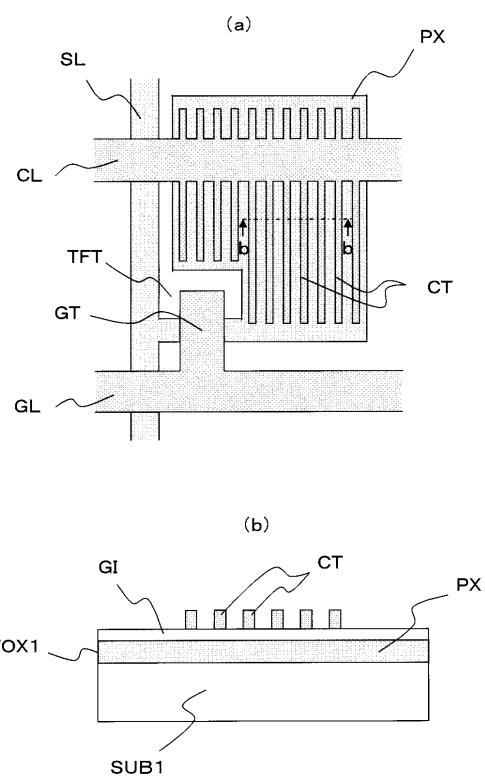

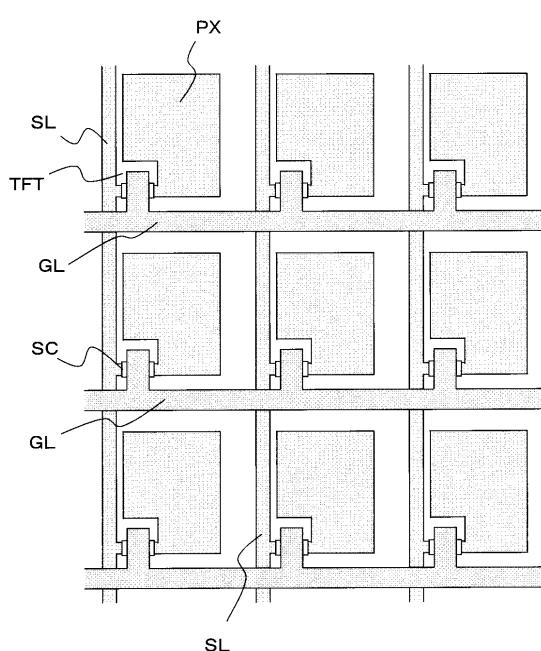

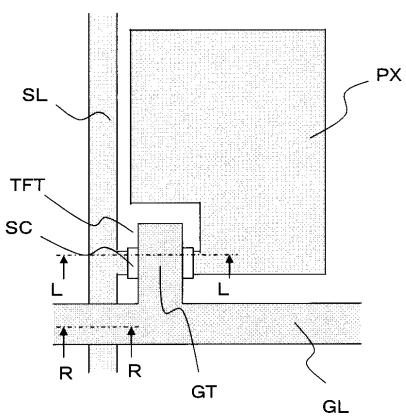

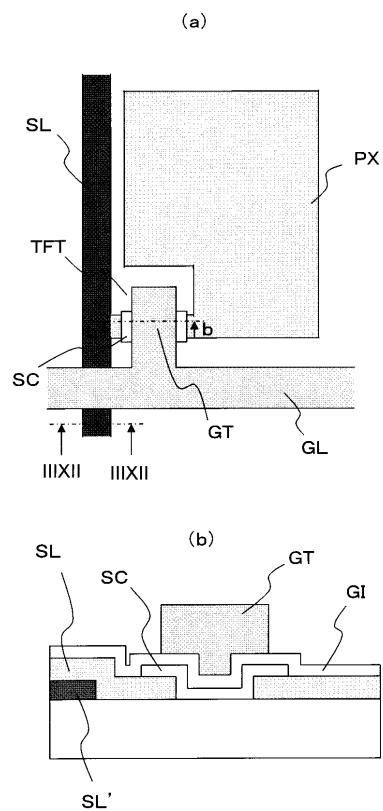

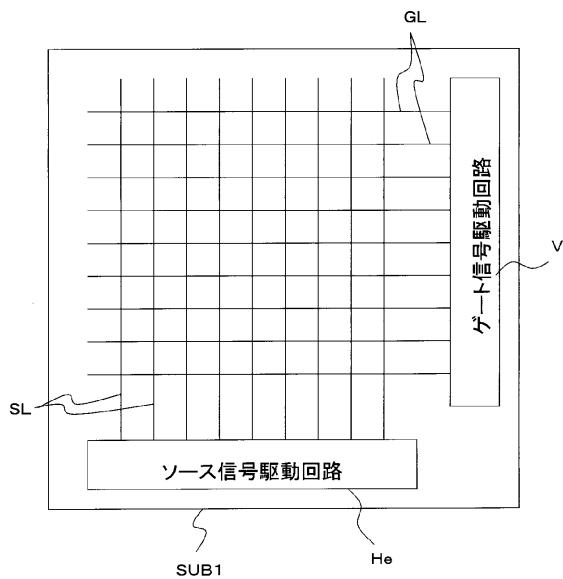

図1は、液晶表示装置の液晶を介して対向配置される各基板のうち一方の基板SUB1の液晶側の面の液晶表示領域に形成される回路の一実施例を示す構成図である。

**【 0 0 3 3 】**

図1において、y方向に延在されx方向に並設されるソース信号線SLと、このソース信号線SLと絶縁されてx方向に延在されy方向に並設されるゲート信号線GLを有し、これら各信号線によって囲まれる矩形状の領域が画素の領域（図中点線枠で示す）に相当するようになっている。これにより、各画素はマトリックス状に配置され、この画素群によって前記液晶表示領域を構成するようになっている。

**【 0 0 3 4 】**

各画素の領域にはその大部分にわたってたとえば透明電極からなる画素電極PXが形成され、この画素電極PXは薄膜トランジスタTFTを介してたとえば図中左側に隣接するソース信号線SLと接続されるようになっている。該薄膜トランジスタTFTは、そのオン、オフの駆動によって、ソース信号線SLからの信号を画素電極PXへの供給、非供給を制御するようになっている。

**【 0 0 3 5 】**

前記薄膜トランジスタTFTは、前記ゲート信号線GLの延在部で形成されるゲート電極GTが半導体層の上方に配置され、いわゆるトップゲート型と称されるMIS（Metal Insulator Semiconductor）構造となっている。

**【 0 0 3 6 】**

これにより、各ゲート信号線GLのそれぞれに信号（走査信号）が順次供給されることにより、画素列の各画素の薄膜トランジスタTFTがオンされ、そのオンのタイミングに応じて各ソース信号線SLにそれぞれ映像信号を供給することにより、この映像信号の電圧は前記画素列の各画素における画素電極PXに印加されるようになる。

**【 0 0 3 7 】**

なお、この実施例に示す液晶表示装置は、前記基板SUB1と液晶を介して配置される図示しない他の基板を有し、この基板の液晶側の面には各画素に共通な対向電極が形成され、この対向電極はたとえば透明電極から構成され、前記ソース信号線SLに供給される信号（映像信号）に対して基準となる電圧からなる信号が供給されるようになっている。前記液晶には前記画素電極PXと対向電極の電位差によって発生する電界が印加され、該液晶の分子が拳動するようになっている。

**【 0 0 3 8 】**

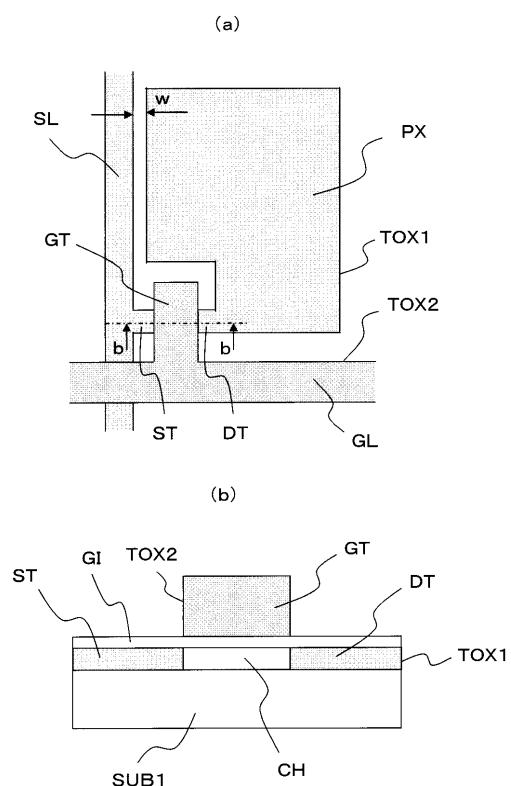

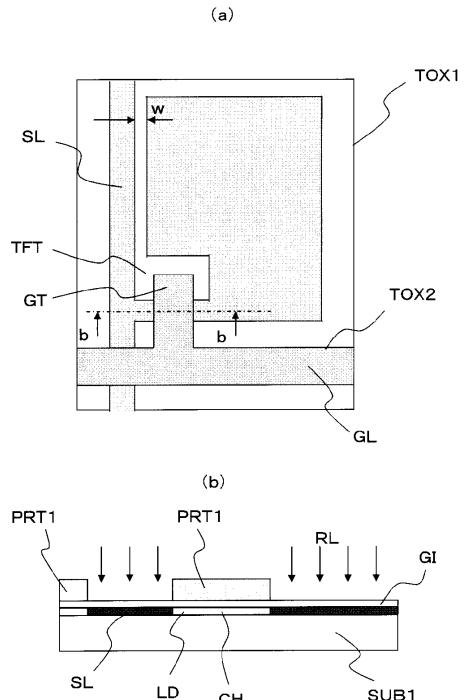

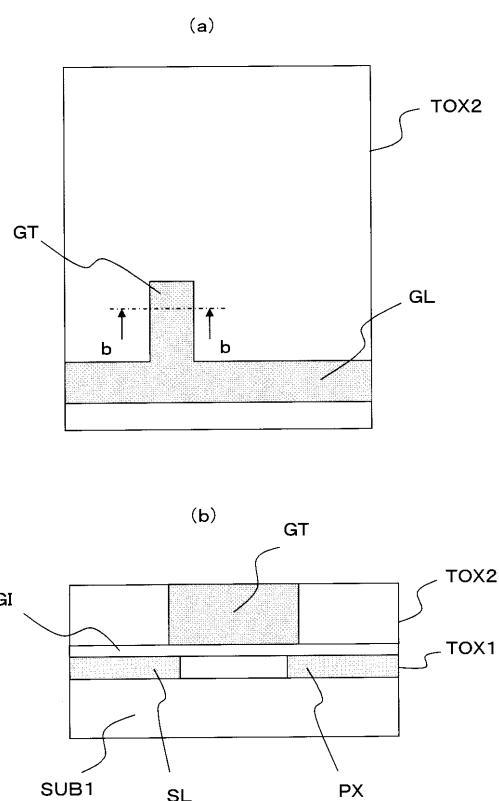

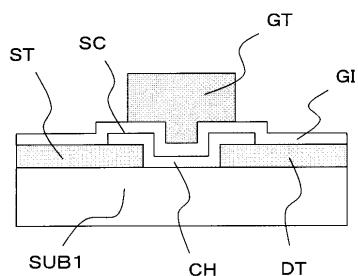

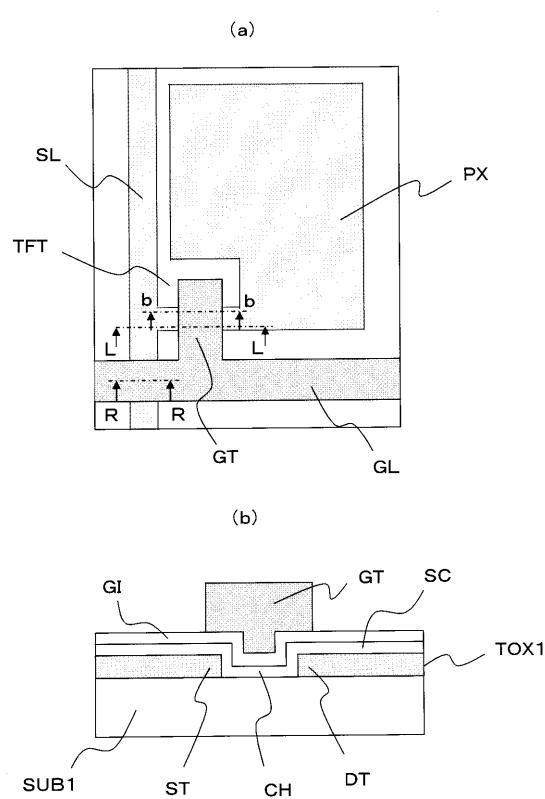

図2(a)は、図1に示した各画素のうち一の画素を抜き出して描いた図である。また、図2(b)は図2(a)のb-b線における断面図である。

**【 0 0 3 9 】**

図2において、ソース信号線SL、薄膜トランジスタTFTのソース領域部ST、チャネル領域部CH（ゲート電極GTの直下の部分）、ドレイン領域部DT、および画素電極PXは、最初、一体的に形成された同一層の第1透明酸化物層TOX1によって形成されるようになっている。

**【 0 0 4 0 】**

すなわち、該第1透明酸化物層TOX1において、前記チャネル領域部CHはキャリア濃度が低くシート抵抗が高い膜（半導体層）として形成され、ソース信号線SL、薄膜トランジスタTFTのソース領域部ST、ドレイン領域部DT、および画素電極PXの形成領域はキャリア濃度が高くシート抵抗が低い膜（導電体層）として形成されている。この場合、たとえば、シート抵抗がソース信号線SL、画素電極PX < ソース領域部ST、ドレイン領域部DT < チャネル領域部CHという順で高くなるように形成してもよく、ソ-

10

20

30

40

50

ス信号線 S L < 画素電極 P X 、ソース領域部 S T 、ドレイン領域部 D T < チャネル領域分 C H という順で高くなるように形成してもよい。後者の場合、画素電極 P X はキャリア濃度を比較的低くしてその透明度を損なうことなく形成できるという効果を奏する。

#### 【 0 0 4 1 】

このように構成されたソース信号線 S L と画素電極 P X は第 1 透明酸化物層 T O X 1 によって一体的にかつ同一層で形成されているため、それらの間隔（図中 w で示す）を最小限に小さくすることができる。ソース信号線 S L と画素電極 P X を別個の工程で形成した場合と比較するとマスク合わせの限界によってそれらの間隔が大きくなってしまう不都合を解消できるからである。これにより、画素の開口率の向上を図った構成とができる。10

#### 【 0 0 4 2 】

ゲート信号線 G L および薄膜トランジスタ T F T のゲート電極 G T は、たとえば I T O ( Indium Tin Oxide ) あるいはキャリア濃度が高くシート抵抗が低い Z n O 等の第 2 透明酸化物層 T O X 2 によって一体的にかつ同一層で形成されている。この場合、該ゲート信号線 G L およびゲート電極 G T は上述のような透明酸化物層に限られることはなく、たとえば金属層によって形成するようにしてもよい。ゲート信号線 G L の電気抵抗をさらに低減させたい場合にはそれに相当する材料の金属層を用いるのが適当だからである。

#### 【 0 0 4 3 】

また、前記第 1 透明酸化物膜 T O X 1 は、基板 S U B 1 の表面に形成され、その上面は絶縁膜 G I によって被われ、前記ゲート電極 G T は前記第 1 透明導電膜 T O X 1 のチャネル領域部 C H の上方に前記絶縁膜 G I を介して配置されている。前記絶縁膜 G I は薄膜トランジスタ T F T のゲート絶縁膜として機能する。20

#### 【 0 0 4 4 】

上述のように、前記第 1 透明酸化物層 T O X 1 はキャリア濃度の高い領域とキャリア濃度の低い領域が領域的に区分けして形成され、前者を導電体層とし後者を半導体層として形成されたものとなっている。そこで、前記液晶表示装置の製造方法を説明する前に、透明酸化物層 T O X においてキャリア濃度の高い領域を低い領域と区分けして選択的に形成する場合のいくつかの実施例について説明する。

#### 【 0 0 4 5 】

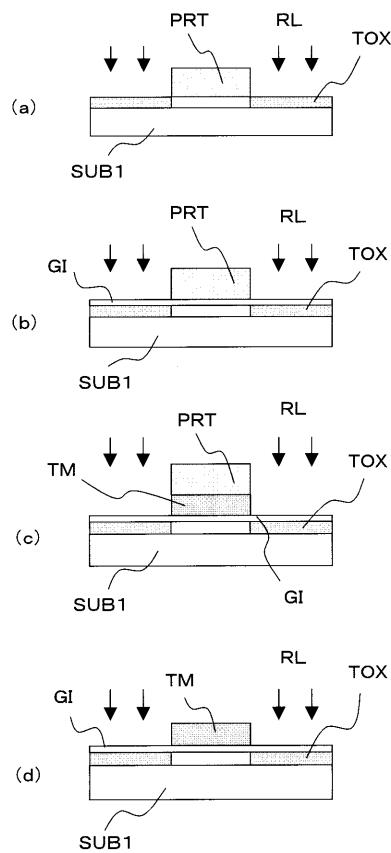

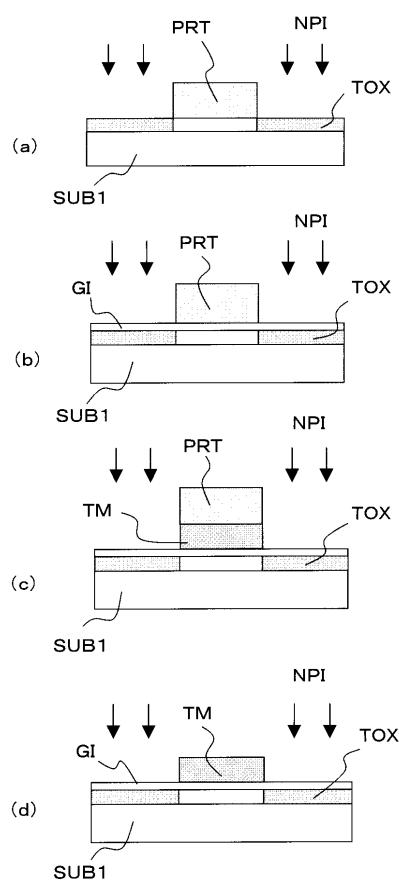

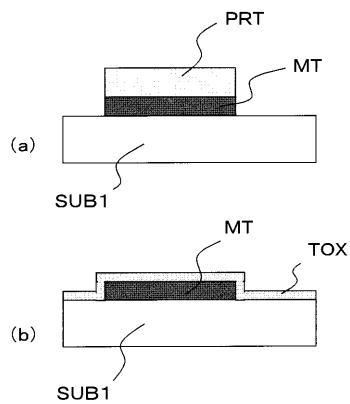

図 3 は、基板 S U B 1 の上面に形成した透明酸化物層 T O X にキャリア濃度の高い領域を選択的に形成する場合の一実施例を示した図である。30

#### 【 0 0 4 6 】

図 3 ( a ) において、基板 S U B 1 の上面に透明酸化物層 T O X を形成し、その透明酸化物層 T O X の表面の領域のうちキャリア濃度を高くする領域以外の領域にマスクとしてたとえばフォトレジスト膜 P R T を形成する。

#### 【 0 0 4 7 】

そして、前記透明酸化物層 T O X にレーザ光 R L を照射する。このレーザ光 R L としてはたとえば K r F エキシマレーザを用いるのが好適であるが、他の光源であってもよい。これにより、該フォトレジスト膜 P R T から露出された透明酸化物層 T O X の領域は該光によって結晶改質がなされキャリア濃度を向上させた領域として形成することができる。40

#### 【 0 0 4 8 】

図 3 ( b ) は、透明酸化物層 T O X にキャリア濃度の高い領域を光照射によって選択的に形成する場合の他の実施例を示し、透明酸化物層 T O X の表面に予め絶縁膜 G I を形成しておき、この絶縁膜 G I を通してレーザ光 R L を前記透明酸化物層 T O X に照射することが図 3 ( a ) の場合と異なっている。

#### 【 0 0 4 9 】

図 3 ( c ) は、透明酸化物層 T O X にキャリア濃度の高い領域を光照射によって選択的に形成する場合の他の実施例を示し、透明酸化物 T O X が絶縁膜 G I で被われ、この絶縁膜 G I の一部の領域において形成されたたとえば電極 T M および該電極 T M に積層されたフォトレジスト膜 P R T をマスクとして、レーザ光 R L を前記透明酸化物層 T O X に照射50

することが図3( b )の場合と異なっている。

**【0050】**

図3( d )は、透明酸化物層TOXにキャリア濃度の高い領域を光照射によって選択的に形成する場合の他の実施例を示し、図3( c )に示す電極TMを形成するためのフォトレジスト膜PRTを除去した後に前記電極TMをマスクとして、レーザ光PLを前記透明酸化物層TOXに照射することが図3( c )の場合と異なっている。

**【0051】**

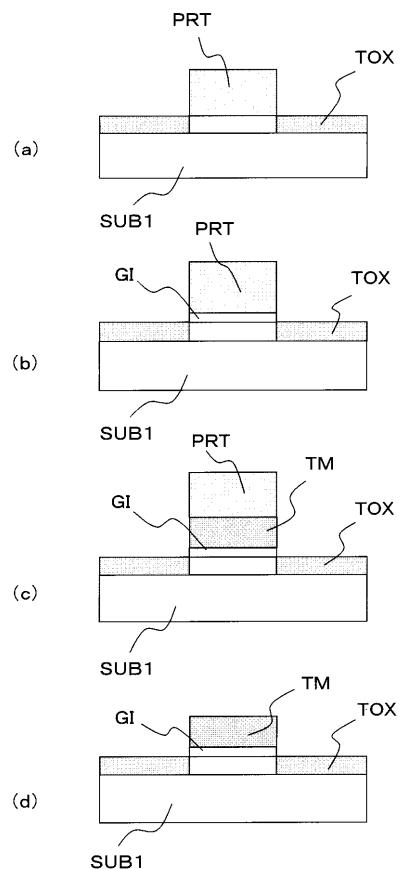

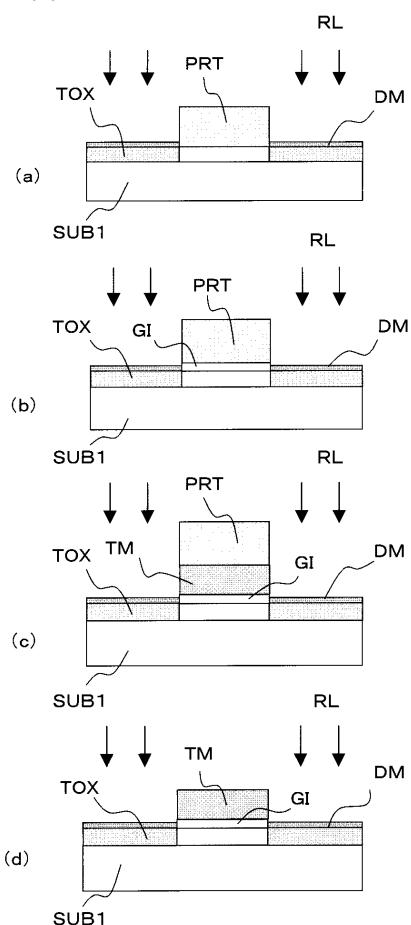

図4は、基板SUB1の上面に形成した透明酸化物層TOXにキャリア濃度の高い領域を選択的に形成する場合の他の実施例を示した図である。

**【0052】**

図4( a )において、基板SUB1の上面に透明酸化物層TOXを形成し、その透明酸化物層TOXの表面の領域のうちキャリア濃度を高くする領域以外の領域にマスクとしてたとえばフォトレジスト膜PRTを形成する。

**【0053】**

そして、前記透明酸化物層TOXに前記フォトレジスト膜PRTを残したまま還元雰囲気下において熱アニールを施す。

**【0054】**

これにより、該フォトレジスト膜PRTから露出された透明酸化物層TOXの領域は該熱アニールによって結晶改質がなされキャリア濃度を向上させた領域として形成することができる。

**【0055】**

図4( b )は、透明酸化物層TOXにキャリア濃度の高い領域を熱アニールによって選択的に形成する場合の他の実施例を示し、透明酸化物層TOXの表面に選択的に形成された絶縁膜GIとこの絶縁膜GIの上面に形成され該絶縁膜GIを選択的に形成する際に用いられたフォトレジスト膜PRTを残したまま熱アニールを施すことが図4( a )の場合と異なっている。

**【0056】**

図4( c )は、透明酸化物層TOXにキャリア濃度の高い領域を熱アニールによって選択的に形成する場合の他の実施例を示し、透明酸化物層TOXの表面に選択的に形成された絶縁膜GIおよび電極TMの積層体とこの積層体の上面に形成され該電極TMおよび絶縁膜GIを形成する際に用いられたフォトレジスト膜PRTを残したまま熱アニールを施すことが図4( b )の場合と異なっている。

**【0057】**

図4( d )は、透明酸化物層TOXにキャリア濃度の高い領域を熱アニールによって選択的に形成する場合の他の実施例を示し、透明酸化物層TOXの表面に選択的に形成された絶縁膜GIおよび電極TMの積層体を形成する際に用いられたフォトレジスト膜PRTを除去した状態で熱アニールを施すことが図4( c )の場合と異なっている。

**【0058】**

図5は、基板SUB1の上面に形成した透明酸化物層TOXにキャリア濃度の高い領域を選択的に形成する場合の他の実施例を示した図である。

**【0059】**

図5( a )において、基板SUB1の上面に透明酸化物層TOXを形成し、その透明酸化物層TOXの表面の領域のうちキャリア濃度を高くする領域以外の領域にマスクとしてたとえばフォトレジスト膜PRTを形成する。

**【0060】**

そして、前記透明酸化物層TOXに不純物イオンNPIを注入する。この不純物イオンNPIとしては必要に応じてn型あるいはp型が使用される。

**【0061】**

これにより、該フォトレジスト膜PRTから露出された透明酸化物層TOXの領域は該不純物イオンNPIの注入によってキャリア濃度を向上させた領域として形成することが

10

20

30

40

50

できる。

**【0062】**

図5(b)は、基板SUB1の上面に形成した透明酸化物層TOXにキャリア濃度の高い領域を不純物イオンNPIの注入によって形成する場合の他の実施例を示した図である。透明酸化物層TOXの表面に予め絶縁膜GIを形成しておき、この絶縁膜GIを通して不純物イオンNPIの注入を前記透明酸化物層TOXに行っていることが図5(a)の場合と異なっている。

**【0063】**

図5(c)は、透明酸化物層TOXにキャリア濃度の高い領域を不純物イオンNPIの注入によって形成する場合の他の実施例を示し、透明酸化物層TOXが絶縁膜GIで被われ、この絶縁膜GIの一部の領域において形成されたたとえば電極TMおよび該電極TMに積層されたフォトレジスト膜PRTをマスクとして、不純物イオンNPIの注入を前記透明酸化物層TOXに行っていることが図5(b)の場合と異なっている。

**【0064】**

図5(d)は、透明酸化物層TOXにキャリア濃度の高い領域を不純物イオンNPIの注入によって形成する場合の他の実施例を示し、図5(c)に示す電極TMを形成するためのフォトレジスタ膜PRTを除去した後に前記電極TMをマスクとして、不純物イオンNPIの注入を前記透明酸化物層TOXに行っていることが図5(c)の場合と異なっている。

**【0065】**

図6は、基板SUB1の上面に形成した透明酸化物層TOXにキャリア濃度の高い領域を選択的に形成する場合の他の実施例を示した図である。

**【0066】**

図6(a)において、基板SUB1の上面に透明酸化物層TOXを形成し、その透明酸化物層TOXの表面の領域のうちキャリア濃度を高くする領域以外の領域にマスクとしたとえばフォトレジスト膜PRTを形成する。

**【0067】**

そして、前記マスクから露出された透明酸化物層TOXの表面にn型あるいはp型の不純物からなるドーパント原料DMを堆積する。

**【0068】**

さらに、前記透明酸化物層TOXにレーザ光RLの照射(あるいは熱アニール)を行う。このレーザ光RLとしてはたとえばKrFエキシマレーザを用いるのが好適であるが、他の光源であってもよい。

**【0069】**

これにより、該フォトレジスト膜PRTから露出された透明酸化物層TOXの領域は該ドーパント原料DMの拡散がなされキャリア濃度を向上させた領域として形成することができる。

**【0070】**

図6(b)は、透明酸化物層TOXにキャリア濃度の高い領域をドーパント原料DMの拡散によって形成する場合の他の実施例を示し、透明酸化物層TOXの表面に選択的に形成された絶縁膜GIとこの絶縁膜GIの上面に形成され該絶縁膜GIを選択的に形成する際に用いられたフォトレジスト膜PRTを残したままレーザ光RLの照射(あるいは熱アニール)を行うことが図6(a)の場合と異なっている。

**【0071】**

図6(c)は、透明酸化物層TOXにキャリア濃度の高い領域をドーパント原料DMの拡散によって形成する場合の他の実施例を示し、透明酸化物層TOXの表面に選択的に形成された絶縁膜GIおよび電極TMの積層体とこの積層体の上面に形成され該電極TMおよび絶縁膜GIを形成する際に用いられたフォトレジスト膜PRTを残したままレーザ光RLの照射(あるいは熱アニール)を行うことが図6(b)の場合と異なっている。

**【0072】**

10

20

30

40

50

図6(d)は、透明酸化物層TOXにキャリア濃度の高い領域をドーパント原料DMの拡散によって形成する場合の他の実施例を示し、透明酸化物層TOXの表面に選択的に形成された絶縁膜GIおよび電極TMの積層体を形成する際に用いられたフォトレジスト膜PRTを除去した状態でレーザ光RLの照射(あるいは熱アニール)を行うことが図6(c)の場合と異なっている。

#### 【0073】

次に、前記液晶表示装置の製造方法を説明するが、その工程の際において、透明酸化物層にキャリア濃度の高い領域を低い領域と区分けして選択的に形成する場合、上述した図3～図6に示した何れかの手法を採用してもよい。以下の説明では、たとえばレーザ光の照射による手法を例に挙げて説明をする。

10

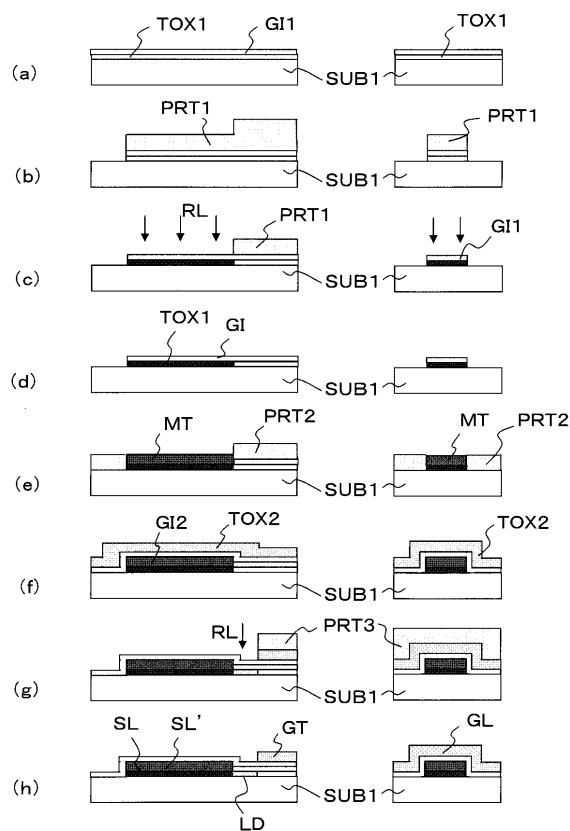

#### 【0074】

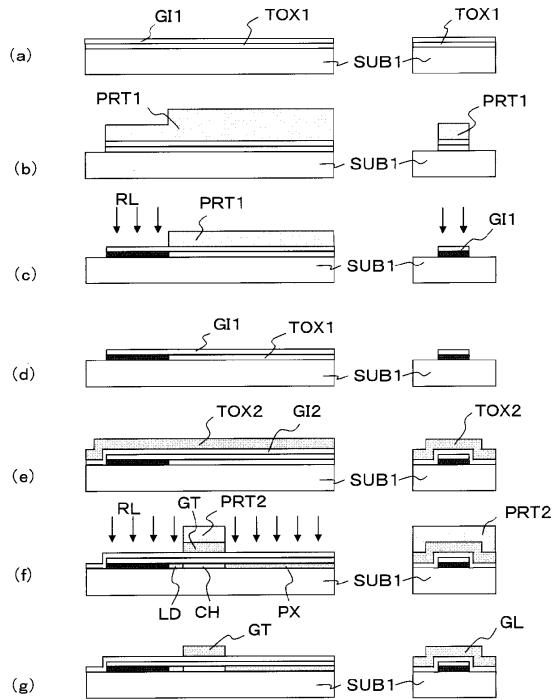

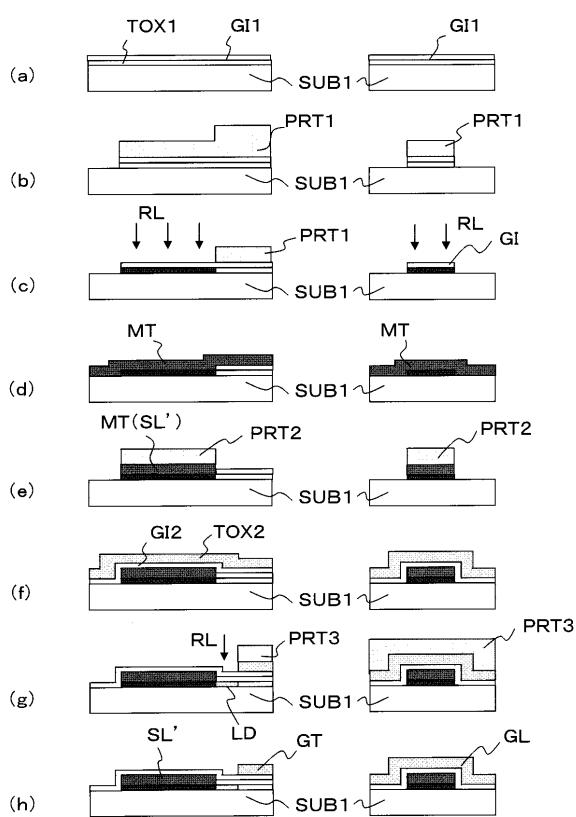

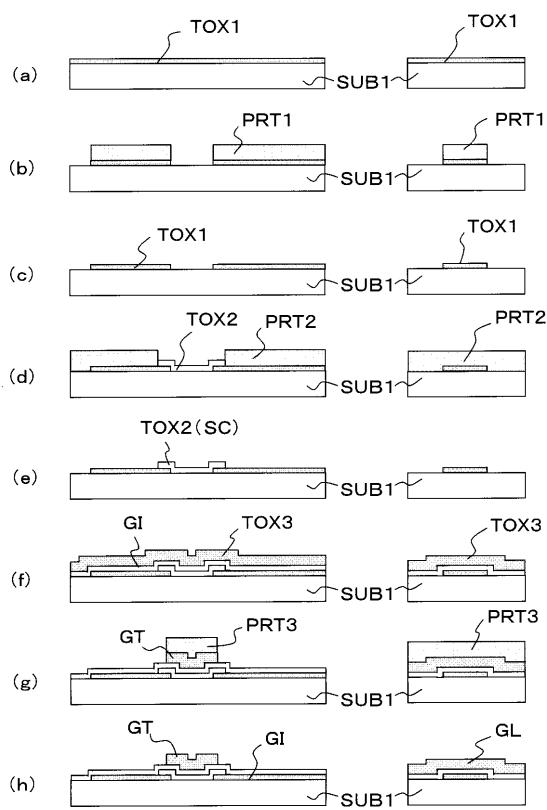

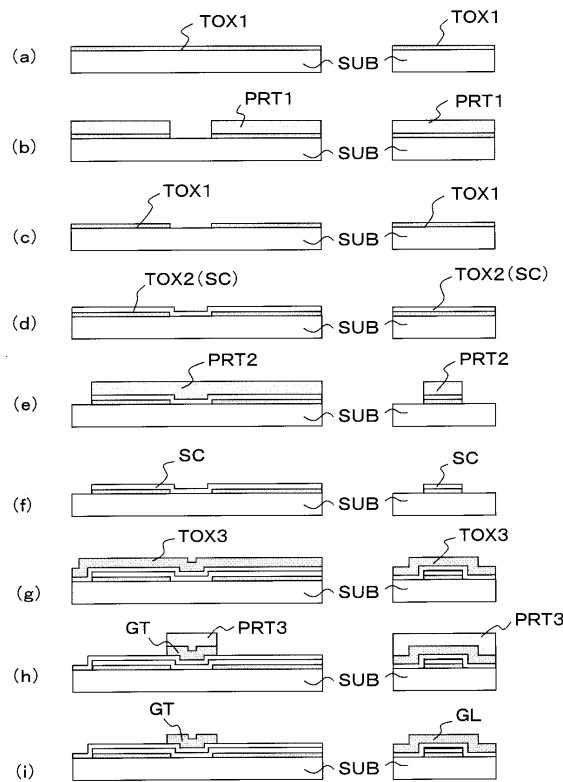

図8は、液晶表示装置の製造方法の一実施例を示す工程図である。ここで、図8に示す工程は液晶表示領域の一画素における工程図を示し、図8の左側に示す工程図は図7のL-L線の個所に相当し、図8の右側に示す工程図は図7のR-R線の個所に相当している。なお、図7に示す画素は図2に示した画素と同じである。

#### 【0075】

また、以下の工程では、薄膜トランジスタTFTのチャネル領域部CHのソース領域部STおよびドレイン領域部DTへの各側にLDD領域部を形成する場合も併せて示している。ここで、LDD領域部はゲート電極GTとの間ににおいて電界緩和を行うように機能する。

20

#### 【0076】

以下、工程順に説明する。

#### 【0077】

工程1.

図8(a)に示すように、たとえばガラスからなる基板SUB1を用意し、この基板SUB1の表面(液晶側の面)にたとえばZnO等からなる高抵抗の第1透明酸化物層TOX1およびたとえばSiO<sub>2</sub>等からなる第1絶縁膜GI1を順次成膜する。ここで、前記第1絶縁膜GI1は薄膜トランジスタTFTの形成領域においてそのゲート絶縁膜として機能するようになっている。

#### 【0078】

30

工程2.

図8(b)に示すように、前記第1絶縁膜GI1の上面の全域に第1フォトレジスト膜PRT1を形成し、この第1フォトレジスト膜PRT1を所定のパターンに形成する。

#### 【0079】

ここで、パターン化された第1フォトレジスト膜PRT1は、図7に示す画素のうち、ソース信号線SL、このソース信号線SLと接続される薄膜トランジスタTFT、この薄膜トランジスタTFTと接続される画素電極PXを形成すべく領域に形成され、かつ、前記薄膜トランジスタTFTのチャネル領域部およびその両脇のいわゆるLDD領域(電界緩和領域)の形成領域において高くそれ以外の部分が低いというように二段の高低を有するようにして形成されている。

40

#### 【0080】

このような高低差のある第1フォトレジスト膜PRT1は、たとえば遮光、いわゆる半透光、透光の3段階からなる透光量の異なるフォトマスクを用いて前記第1フォトレジスト膜PRT1を感光することによって形成される。このような第1フォトレジスト膜PRT1はいわゆるハーフトーンマスクあるいはグレートーンマスクを用いた露光によって形成することができる。

#### 【0081】

そして、このように形成された第1フォトレジスト膜PRT1をマスクとし、このマスクから露出された第1絶縁膜GI1およびこの第1絶縁膜GI1の下層の第1透明酸化物層TOX1を順次エッティングし、基板SUB1の表面を露出させる。

50

## 【0082】

このようにして第1透明酸化物層TOXと第1絶縁膜GI1の積層体は、ソース信号線SL、このソース信号線SLと接続される薄膜トランジスタTFT、この薄膜トランジスタTFTと接続される画素電極PXの形成領域に残存される。

## 【0083】

工程3.

図8(c)に示すように、前記第1フォトレジスト膜PRT1の表面を底面方向に適当量の除去を行うことによって、該第1フォトレジスト膜PRT1を、ソース信号線SL、このソース信号線SLと接続される薄膜トランジスタTFT(そのチャネル領域部およびLDD領域部の部分を除く)、この薄膜トランジスタTFTと接続される画素電極PXの各形成領域において完全に除去し、前記薄膜トランジスタTFTのチャネル領域部およびLDD領域部の形成領域にのみ残存させるようにする。10

## 【0084】

そして、第1絶縁膜GI1を通して第1透明酸化物層TOX1にたとえばレーザ光RLを照射することによって該第1透明酸化物層TOX1に結晶改質を行う。該第1透明酸化物層TOX1にキャリア濃度を向上させ低抵抗化を図るためである。この場合、前記第1フォトレジスト膜PRT1が形成されている部分においてレーザ光RLの照射が阻止され該第1フォトレジスト膜RLの直下の第1透明酸化物層TOX1は高抵抗が維持される。

## 【0085】

のことから、ソース信号線SL、このソース信号線SLと接続される薄膜トランジスタTFT(そのチャネル領域部およびLDD領域部の部分を除く)、この薄膜トランジスタTFTと接続される画素電極PXの各形成領域においてキャリア濃度を高めて導電体化し、前記薄膜トランジスタTFTのチャネル領域の部分においてキャリア濃度が低い半導体のまま残ることになる。20

## 【0086】

工程4.

図8(d)に示すように、前記第1フォトレジスト膜PRT1を全て除去する。

## 【0087】

工程5.

図8(e)に示すように、たとえばSiO<sub>2</sub>からなる第2絶縁膜GI2、たとえばITO(Indium Tin Oxide)からなる第2透明酸化物層TOX2を順次成膜する。ここで、前記第2絶縁膜GI2は、ソース信号線SLに対する後述のゲート信号線GLの層間絶縁膜として機能するようになる。30

## 【0088】

工程6.

図8(f)に示すように、前記第2透明酸化物層TOX2の上面に第2フォトレジスト膜PRT2を形成し、この第2フォトレジスト膜PRT2を所定のパターンに形成する。すなわち、ゲート信号線GL、このゲート信号線GLと接続される前記薄膜トランジスタTFTのゲート電極GTの各形成領域に前記第2フォトレジスト膜を残存させる。ここで、ゲート電極GTの形成領域は、薄膜トランジスタTFTのチャネル領域部の直上の部分であり、該チャネル領域の両脇のLDD領域は除かれる。40

## 【0089】

そして、この第2フォトレジスト膜PRT2から露出された第2透明酸化物層TOX2をエッチングし、残存された第2透明酸化物層TOX2によって前記ゲート信号線SLおよびゲート電極Tを構成する。

## 【0090】

さらに、前記第2フォトレジスト膜PRT2をそのまま残存させ、第2絶縁膜GI2、第1絶縁膜GI1を通して第1透明酸化物層TOX1にレーザ光RLを照射する。

## 【0091】

このレーザ光RLの照射によって、薄膜トランジスタTFTのチャネル領域部CHの両50

脇のLDD領域LDにおいてキャリア濃度が高められるようになる。この場合、前記工程3においてキャリア濃度が高められた第1透明酸化物層TOX1の部分においてもさらにキャリア濃度が高められることから、相対的に見て前記LDD領域LDは比較的導電性の小さな領域として形成されることになる。

#### 【0092】

工程7.

図8(g)に示すように、前記第2フォトレジスト膜PRT2を全て除去する。その後は、基板SUB1の表面に図示せぬ配向膜を形成することによって完了する。

#### 【0093】

上述のように、基板SUB1の液晶側の面の液晶表示領域は、前記第1フォトレジスト膜PRT1および第2フォトレジスト膜PRT2を用いたいわゆる2フォト工程で製造することができる。10

#### 【0094】

また、第1フォトレジスト膜PRT1は、第1透明酸化物層TOX1および第1絶縁膜G1の順次積層体の選択エッチングの際のマスク、および前記第1透明酸化物層TOX1におけるキャリア濃度の高い領域の選択的形成の際のマスクとしてそれぞれ機能するが、フォトリソグラフィ技術の適用は一回で済むことになり、工程の大幅低減を図ることができる。

#### 【0095】

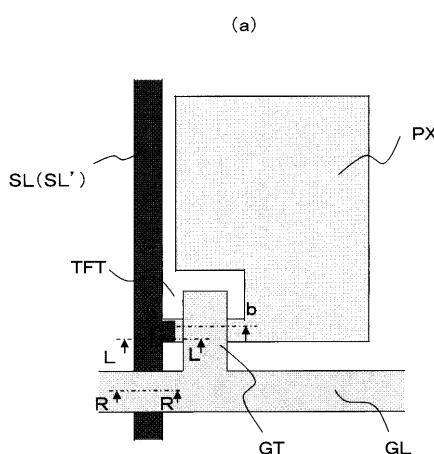

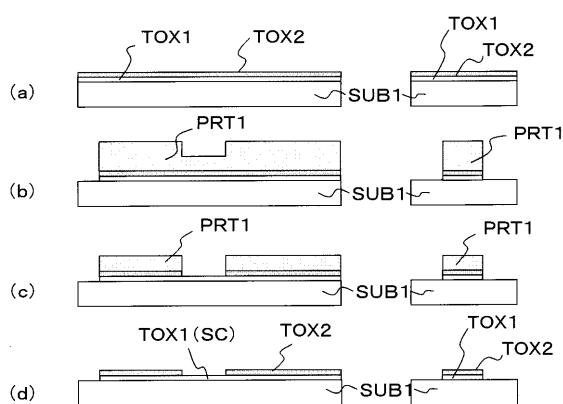

図9は、前記液晶表示装置の製造方法の他の実施例を示す工程図である。図9は、図8と対応した図となっており、したがって、図9の左側に示す工程図は図7のL-L線の個所に相当し、図9の右側に示す工程図は図7のR-Rの個所に相当している。20

#### 【0096】

以下、工程順に説明する。

#### 【0097】

工程1.

図9(a)に示すように、基板SUB1を用意し、この基板SUB1の表面(液晶側の面)にたとえばZnO等からなる高抵抗の第1透明酸化物層TOX1およびたとえばSiO<sub>2</sub>等からなる第1絶縁膜G1を順次成膜する。

#### 【0098】

工程2.

図9(b)に示すように、前記第1絶縁膜G1の上面の全域に第1フォトレジスト膜PRT1を形成し、この第1フォトレジスト膜PRT1を所定のパターンに形成する。

#### 【0099】

ここで、パターン化された第1フォトレジスト膜PRT1は、図7に示す画素のうち、ソース信号線SL、このソース信号線SLと接続される薄膜トランジスタTFT、この薄膜トランジスタTFTと接続される画素電極PXの各形成領域に形成され、かつ、ソース信号線SLの部分が低くそれ以外の部分が高いというように二段の高低を有するようにして形成されている。

#### 【0100】

そして、前記第1フォトレジスト膜PRT1をマスクとし、このマスクから露出された第1絶縁膜G1およびこの第1絶縁膜G1の下層の第1透明酸化物層TOX1を順次エッチングし、基板SUB1の表面を露出させる。

#### 【0101】

このようにして第1透明酸化物層TOX1と第1絶縁膜G1の積層体は、ソース信号線SL、このソース信号線SLと接続される薄膜トランジスタTFT、この薄膜トランジスタTFTと接続される画素電極PXの形成領域に残存される。

#### 【0102】

工程3.

図9(c)に示すように、前記第1フォトレジスト膜PRT1の表面を底面方向に適當

10

20

30

40

50

量の除去を行うことによって、該第1フォトレジスト膜PRT1を、ソース信号線SLの形成領域において完全に除去し、前記薄膜トランジスタTFTのチャネル領域部、このチャネル領域部に隣接しソース信号線SL側のLDD領域部、および画素電極PXの各形成領域にのみ残存させるようにする。

**【0103】**

そして、第1絶縁膜GI1を通して第1透明酸化物層TOX1にレーザ光RLを照射することによって該第1透明酸化物層TOX1に結晶改質を行う。この場合、前記第1フォトレジスト膜PRT1が形成されている部分においてレーザ光RLの照射が阻止され該第1フォトレジスト膜PRT1の直下の第1透明酸化物層TOX1は高抵抗が維持される。

**【0104】**

工程4.

図9(d)に示すように、前記第1フォトレジスト膜PRT1を全て除去する。

**【0105】**

工程5.

図9(e)に示すように、たとえばSiO<sub>2</sub>からなる第2絶縁膜GI2、たとえばITO(Indium Tin Oxide)からなる第2透明酸化物層TOX2を順次成膜する。

**【0106】**

工程6.

図9(f)に示すように、前記第2透明酸化物層TOX2の上面に第2フォトレジスト膜PRT2を形成し、この第2フォトレジスト膜PRT2を所定のパターンに形成する。すなわち、ゲート信号線GL、このゲート信号線GLと接続される前記薄膜トランジスタTFTのゲート電極GTの各形成領域に前記第2フォトレジスト膜PRT2を残存させる。ここで、ゲート電極GTの形成領域は、薄膜トランジスタTFTのチャネル領域部の直上の部分であり、該チャネル領域部に隣接するソース信号線SL側のLDD領域LDは除かれる。

**【0107】**

そして、この第2フォトレジスト膜PRT2から露出された第2透明酸化物層TOX2をエッチングし、残存された第2透明酸化物層TOX2によって前記ゲート信号線GLおよびゲート電極GTを構成する。

**【0108】**

さらに、前記第2フォトレジスト膜PRT2をそのまま残存させ、第2絶縁膜GI2、第1絶縁膜GI1を通して第1透明酸化物層TOX1にレーザ光RLを照射する。

**【0109】**

このレーザ光RLの照射によって、薄膜トランジスタTFTのチャネル領域部に隣接するソース信号線SL側のLDD領域LDにおいてキャリア濃度が高められるようになる。この場合、前記工程3においてキャリア濃度が高められた第1透明酸化物層TOX1の部分においてもさらにキャリア濃度が高められることから、相対的に見て前記LDD領域LDは比較的導電性の小さな領域として形成されることになる。

**【0110】**

さらに、薄膜トランジスタTFTのチャネル領域部に隣接する画素電極PXの部分において、ソース信号線SL側のLDD領域LDの形成領域と同様に相対的に見て比較的導電性の小さな領域として形成されることになる。画素電極PXは、図示しない他の電極(対向電極)との間で電界を生じせしめる電極として機能することから導電性が比較的に小さくてもよいことに基づくものである。そして、ZnO等の第1透明酸化物層TOX1は、キャリア濃度を高め過ぎると金属化してしまいもはや透明でなくなるが、前記画素電極PXにおいては透明を維持できる程度のキャリア濃度にできる効果を奏する。

**【0111】**

なお、図8、図9に示した製造方法において、第1透明酸化物層TOX1にキャリア濃度の高い領域を形成する場合に、レーザ光RLの照射を一実施例として挙げたものであるが、図3～図6に示す方法、あるいは他の方法を用いてもよいことは上述したとおりであ

10

20

30

40

50

る。

#### 【0112】

また、図3～図6において示した方法のうちには、透明酸化物層TOXの表面に絶縁膜GIを形成していない状態でレーザ光RLの照射等をする方法も示している。したがって、図8、図9に示した製造方法において、最初、絶縁膜GIを形成していない状態で透明酸化物層TOXにキャリア濃度の高い領域を形成し、その後に、絶縁膜GIを形成するような工程として適用するようにしてもよい。

#### 【0113】

さらに、図8、図9に示した工程の後に、アレイ端におけるソース信号線に電気的コンタクトをとるために、コンタクトに必要なアレイ端領域以外の領域にフォトレジスト膜を直描あるいはマスク蒸着し、該当するアレイ端部分の絶縁膜をエッチング除去することによってフォト工程を増やすことなく製造を実現することができる。

10

#### 【0114】

##### 実施例2

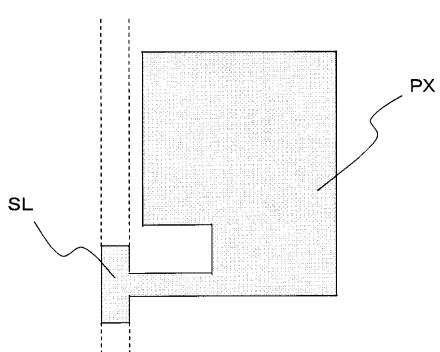

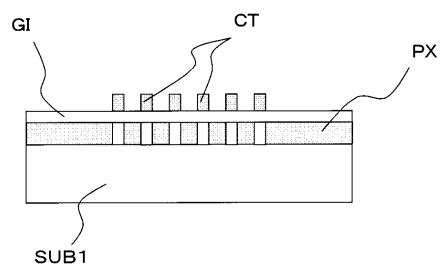

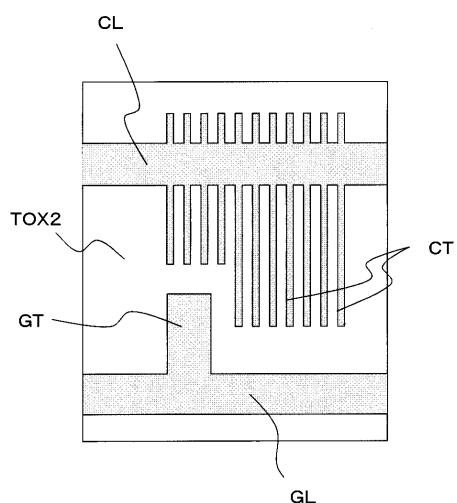

図10は、本発明による表示装置の画素の構成の他の実施例を示す平面図で、図2(a)に対応した図となっている。

#### 【0115】

図10において、基板SUB1の表面の全域にわたって形成された第1透明酸化物層TOX1の面の区分された各領域に、ソース信号線SL、このソース信号線SLに接続される薄膜トランジスタTFT、この薄膜トランジスタTFTに接続される画素電極PXが形成されている。

20

#### 【0116】

図2(a)の場合と比較して異なる構成は、基板SUB1の表面に、ソース信号線SL、薄膜トランジスタTFT、画素電極PXの形成領域以外の領域においてもキャリア濃度の低い第1透明酸化物層(実効的に絶縁体として機能する)TOX1が形成されていることがある。すなわち、基板SUB1の表面の全域に形成された第1透明酸化物層TOX1は選択的にエッチングされていない構成となっている。

#### 【0117】

このようにした場合であっても、ソース信号線SLと画素電極PXは第1透明酸化物層TOX1によって一体的にかつ同一層で形成されるため、それらの間隔(図中wで示す)を最小限に小さくでき、画素の開口率の向上を図った構成とすることができます。

30

#### 【0118】

このように構成した第1透明酸化物層TOX1は、実施例1において図8、あるいは図9に示した製造方法において、第1フォトレジスト膜PRT1の形成の際に、通常どおりにフォトレジスト膜を形成すればよく、たとえばハーフ露光された段差のあるフォトレジスト膜を形成しなくてもよい効果を奏する。

#### 【0119】

すなわち、たとえば図8(c)に示した工程に対応し、図10(a)のb-b線の個所における工程を示す図10(b)に示すように、第1フォトレジスト膜PRT1によって、薄膜トランジスタTFTのチャネル領域部CHおよびその両脇のLDD領域部LDを被うフォトレジスト膜、ソース信号線SL、薄膜トランジスタTFT、画素電極PXの形成領域以外の領域を被うフォトレジスト膜を形成し、その後は、図8に示した工程を経ればよいことになる。また、図9に示した製造方法を採用する場合においても同様である。

40

#### 【0120】

このような構成からなる表示装置は、液晶に面する表面における段差構造を少なくできるという効果を奏する。

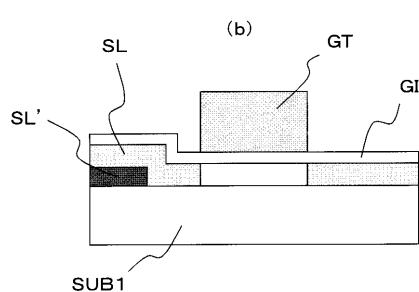

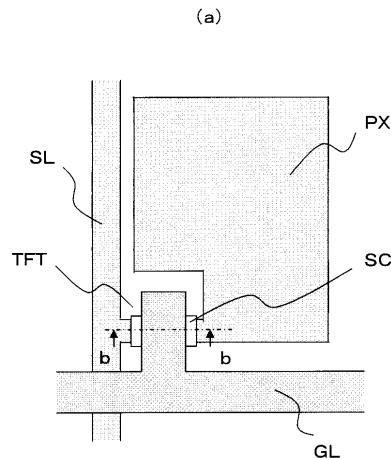

#### 【0121】

##### 実施例3

図11(a)は、本発明による表示装置の画素の構成の他の実施例を示す平面図で、図7、10(a)と対応した図である。また、図11(b)は図11(a)のb-b線にお

50

ける断面図である。

**【0122】**

図7、10(a)の場合と比較して異なる構成は、主となるソース信号線SL'が電気的抵抗の低いたとえば金属層で他の部材とは独立に形成されていることがある。

**【0123】**

ここで、前記ソース信号線SL'を主と称したのは、該ソース信号線SL'にたとえば全域に及んで積層された第1透明酸化物層TOX1からなるソース信号線SLが形成されているからである。

**【0124】**

すなわち、前記ソース信号線SL'が形成された基板SUB1の表面に図7、10に示した構成が積層され、図7、10に示したソース信号線SLが前記ソース信号線SL'に重畠して形成されるようになっている。10

**【0125】**

図7、10の場合の構成と比較し、第1透明酸化物層TOX1から構成されるソース信号線SLは、その下層に金属層から構成される前記ソース信号線SL'、と接続して形成されることから、電気的抵抗を大幅に低減させることができる効果を奏する。

**【0126】**

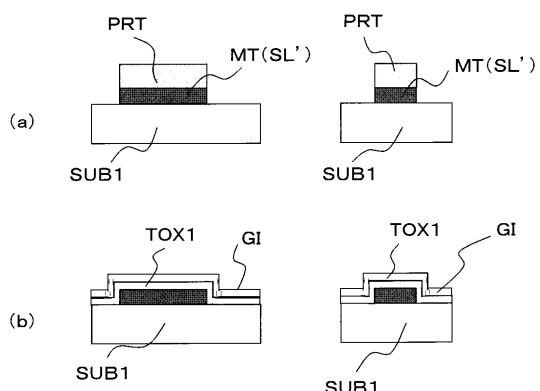

この場合、図11では、第1透明酸化物層TOX1からなるソース信号線SLと金属層からなるソース信号線SLは、それらの中心軸を一致づけてそれらの幅をほぼ同一としたものであるが、金属層からなるソース信号線SLの幅を第1透明酸化物層TOX1からなるソース信号線SLの幅よりも小さく構成するようにしてもよい。ソース信号線を全体として充分に電気的抵抗を低減させることができるからである。20

**【0127】**

図12は、前記ソース信号線SL'を基板SUB1の表面に形成する場合における製造方法の工程を示した工程図である。

**【0128】**

図中の左側に描いた工程図は図11(a)のL-L線における断面図で示し、右側に描いた工程図は図11(a)のR-R線における断面図で示している。

**【0129】**

図12(a)に示すように、基板SUB1の表面の全域に金属層MTを形成し、この金属層MTの表面においてパターン化されたフォトトレジスト膜PRTをマスクとして該金属層MTを選択エッチングすることにより、前記ソース信号線SL'を形成する。30

**【0130】**

次に、前記フォトトレジスト膜PRTを除去した後に、図12(b)に示すように、たとえばZnOからなる第1透明酸化物層TOX1、および、たとえばSiO2からなる絶縁膜GIを順次積層させる。

**【0131】**

この工程は、たとえば図8(a)に示す工程に相当し、その後、図8(b)~図8(g)を経ることにより、図11に示した構成を完成させることができる。

**【0132】**

上述した実施例では、ソース信号線SL'の全域にわたって第1透明酸化物層TOX1からなるソース信号線SLを積層させた構成としたものである。しかし、これに限定されることはなく、ソース信号線SL'の一部分にのみ前記ソース信号線SLを積層させる構成としてもよい。たとえば、薄膜トランジスタTFTの近傍におけるソース信号線SL'のみに前記ソース信号線SLを積層させる構成としてもよい。ソース信号線SL'は金属層で形成されていることから、それ自体で電気的抵抗を充分に低減させることができるからである。

**【0133】**

この場合、前記第1透明酸化物層TOX1および絶縁膜GIの順次積層体は、たとえば図13に示すパターンのようにして形成され、そのソース信号線SLとして形成される部40

分は薄膜トランジスタ TFT の形成領域の近傍のみに止まって構成されている。

**【0134】**

**実施例 4**

図 14 (a) は、本発明による表示装置の画素の構成の他の実施例を示す平面図で、図 11 (a) と対応した図である。また、図 14 (b) は図 14 (a) の b - b 線における断面図である。

**【0135】**

図 11 (a) の場合と比較し、同様に主たるソース信号線 SL' を有するが、該ソース信号線 SL' は前記ソース信号線 SL の上層に配置されていることが図 11 (a) の場合と異なっている。

10

**【0136】**

この場合においてもソース信号線 SL' は、たとえば金属層で形成され、また第 1 透明酸化物層 TOX1 からなるソース信号線 SL と積層されて形成されていることから、電気的抵抗を大幅に低減させることができる。

**【0137】**

また、図 14 では、第 1 透明酸化物層 TOX1 からなるソース信号線 SL と金属層からなるソース信号線 SL' は、それらの中心軸を一致づけてそれらの幅をほぼ同一としたものであるが、金属層からなるソース信号線 SL' の幅を第 1 透明酸化物層 TOX1 からなるソース信号線 SL の幅よりも小さく構成するようにしてもよい。ソース信号線を全体として充分に電気的抵抗を低減させることができるからである。

20

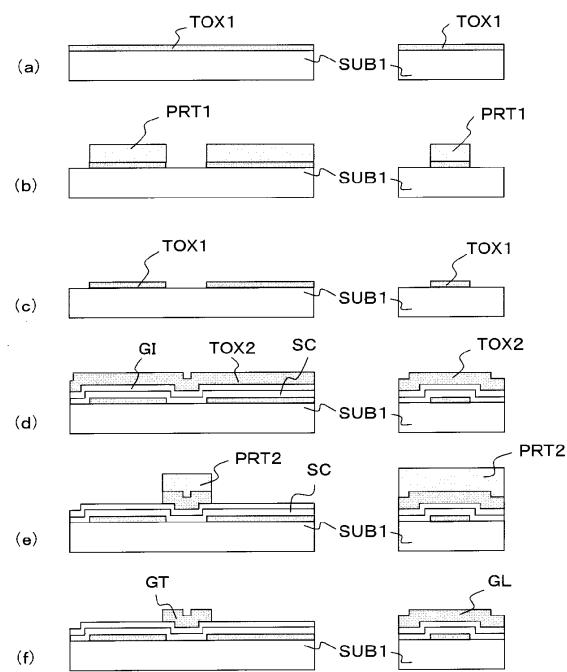

**【0138】**

図 15 は、前記表示装置の画素の製造方法の一実施例を示す工程図であり、図中左側の工程図は図 14 (a) の L - L 線における断面図で示し、図中右側の工程図は図 14 (a) の R - R 線における断面図で示している。

**【0139】**

以下、工程順に説明する。

**【0140】**

**工程 1 .**

図 15 (a) に示すように、基板 SUB1 を用意し、この基板 SUB1 の表面にたとえば ZnO 等からなる高抵抗の第 1 透明酸化物層 TOX1 およびたとえば SiO<sub>2</sub> 等からなる第 1 絶縁膜 GI1 を順次成膜する。

30

**【0141】**

**工程 2 .**

図 15 (b) に示すように、前記第 1 絶縁膜 GI1 の上面の全域に第 1 フォトレジスト膜 PRT1 を形成し、この第 1 フォトレジスト膜 PRT1 を所定のパターンに形成する。

**【0142】**

ここで、パターン化された第 1 フォトレジスト膜 PRT1 は、図 14 (a) に示す画素のうち、ソース信号線 SL' 、このソース信号線 SL' と接続される薄膜トランジスタ TFT 、この薄膜トランジスタ TFT と接続される画素電極 PX の各形成領域に形成され、かつ、前記薄膜トランジスタ TFT のチャネル領域部およびその両脇の LDD 領域部の形成領域において高くそれ以外の部分が低いというように二段の高低を有するようにして形成されている。

40

**【0143】**

そして、前記第 1 フォトレジスト膜 PRT1 をマスクとし、このマスクから露出された第 1 絶縁膜 GI1 およびこの第 1 絶縁膜 GI1 の下層の第 1 透明酸化物層 TOX1 を順次エッチングし、基板 SUB1 の表面を露出させる。

**【0144】**

このようにして第 1 透明酸化物層 TOX1 と第 1 絶縁膜 GI1 の積層体は、ソース信号線 SL' 、このソース信号線 SL' と接続される薄膜トランジスタ TFT 、この薄膜トランジスタ TFT と接続される画素電極 PX の形成領域に残存される。

50

## 【0145】

工程3.

図15(c)に示すように、前記第1フォトレジスト膜PRT1の表面を底面方向に適量の除去を行うことによって、該第1フォトレジスト膜PRT1を、薄膜トランジスタTFTのチャネル領域部およびその両脇のLDD領域部の形成領域にのみ残存させるようする。

## 【0146】

そして、第1絶縁膜GI1を通して第1透明酸化物層TOX1にレーザ光RLを照射することによって該第1透明酸化物層TOX1に結晶改質を行いキャリア濃度を向上させる。この場合、前記第1フォトレジスト膜TOX1が形成されている部分においてレーザ光RLの照射が阻止され該第1フォトレジスト膜PRT1の直下の第1透明酸化物層TOX1は高抵抗が維持される。

10

## 【0147】

工程4.

図15(d)に示すように、前記第1フォトレジスト膜PRT1を全て除去する。

## 【0148】

工程5.

図15(e)に示すように、基板SUB1の表面に第2フォトレジスト膜PRT2を形成し、該第2フォトレジスト膜PRT2をパターン化することによって、ソース信号線SLを形成する部分において除去され他の部分において残存される第2フォトレジスト膜PRT2を形成する。

20

## 【0149】

そして、該第2フォトレジスト膜PRT2から露出する前記第1絶縁膜GI1を選択エッチングし、前記第1透明酸化物層TOX1の結晶改質がなされた部分(ソース信号線SLの部分)を露呈させる。

## 【0150】

さらに、前記第2フォトレジスト膜PRT2をそのまま残存させ、その上方から金属を蒸着させ、該第2フォトレジスト膜PRT2を剥離させる。いわゆるリフトオフ法と称され、前記第1透明酸化物層TOX1の結晶改質がなされた部分(ソース信号線SLの部分)に金属層MTが形成されることになる。この金属層MTはソース信号線SLに積層して形成されるソース信号線SL'に相当するものとなる。

30

## 【0151】

工程6.

図15(f)に示すように、前記第2フォトレジスト膜PRT2を除去し、たとえばSiO<sub>2</sub>からなる第2絶縁膜GI2およびたとえばITO膜からなる第2透明酸化物層TOX2を順次形成する。

## 【0152】

工程7.

図15(g)に示すように、基板SUB1の表面に第3フォトレジスト膜PRT3を形成し、該第3フォトレジスト膜PRT3をパターン化することによって、ゲート信号線GLおよび薄膜トランジスタTFTのゲート電極GTを形成する部分において残存される第3フォトレジスト膜PRT3を形成する。

40

## 【0153】

そして、第3フォトレジスト膜PRT3をマスクとし、このマスクから露出する前記第2透明酸化物層TOX2を選択エッチングし、その下層の第2絶縁膜GI2を露呈させる。

## 【0154】

さらに、前記第3フォトレジスト膜PRT3をそのまま残存させ、前記第2絶縁膜GI2を通して第1透明酸化物層TOX1にレーザ光RLを照射する。これにより、ゲート電極GTの直下の薄膜トランジスタTFTのチャネル領域部と前記ソース信号線SL'との

50

間の領域において結晶改質がなされ LDD 領域部 LD が形成される。このため、この工程におけるレーザ光 RL による結晶改質は、前記工程 3 におけるレーザ光 RL による結晶改質よりも、その改質程度を小さくする必要がある。

**【 0 1 5 5 】**

工程 8 .

図 15 ( h ) に示すように、前記第 3 フォトレジスト膜 PRT3 を除去する。

**【 0 1 5 6 】**

図 16 は、前記表示装置の画素の製造方法の他の実施例を示す工程図であり、図中左側の工程図は図 14 ( a ) の L - L 線における断面図で示し、図中右側の工程図は図 14 ( a ) の R - R 線における断面図で示している。

10

**【 0 1 5 7 】**

以下、工程順に説明する。

**【 0 1 5 8 】**

工程 1 .

図 16 ( a ) に示すように、基板 SUB1 を用意し、この基板 SUB1 の表面にたとえば ZnO 等からなる高抵抗の第 1 透明酸化物層 TOX1 およびたとえば SiO<sub>2</sub> 等からなる第 1 絶縁膜 GI1 を順次成膜する。

**【 0 1 5 9 】**

工程 2 .

図 16 ( b ) に示すように、前記第 1 絶縁膜 GI1 の上面の全域に第 1 フォトレジスト膜 PRT1 を形成し、この第 1 フォトレジスト膜 PRT1 を所定のパターンに形成する。

20

**【 0 1 6 0 】**

ここで、パターン化された第 1 フォトレジスト膜 PRT1 は、図 14 ( a ) に示す画素のうち、ソース信号線 SL 、このソース信号線 SL と接続される薄膜トランジスタ TFT 、この薄膜トランジスタ TFT と接続される画素電極 PX の各形成領域に形成され、かつ、前記薄膜トランジスタ TFT のチャネル領域部およびその両脇の LDD 領域部の形成領域において高くそれ以外の部分が低いというように二段の高低を有するようにして形成されている。

**【 0 1 6 1 】**

そして、前記第 1 フォトレジスト膜 PRT1 をマスクとし、このマスクから露出された第 1 絶縁膜 GI1 およびこの第 1 絶縁膜 GI1 の下層の第 1 透明酸化物層 TOX1 を順次エッティングし、基板 SUB1 の表面を露出させる。

30

**【 0 1 6 2 】**

このようにして第 1 透明酸化物層 TOX1 と第 1 絶縁膜 GI1 の積層体は、ソース信号線 SL 、このソース信号線 SL と接続される薄膜トランジスタ TFT 、この薄膜トランジスタ TFT と接続される画素電極 PX の部分に残存される。

**【 0 1 6 3 】**

工程 3 .

図 16 ( c ) に示すように、前記第 1 フォトレジスト膜 PRT1 の表面を底面方向に適当量の除去を行うことによって、該第 1 フォトレジスト膜 PRT1 を、薄膜トランジスタ TFT のチャネル領域部およびその両脇の LDD 領域部の形成領域にのみ残存させるようする。

40

**【 0 1 6 4 】**

そして、第 1 絶縁膜 GI1 を通して第 1 透明酸化物層 TOX1 にレーザ光 RL を照射することによって該第 1 透明酸化物層 TOX1 に結晶改質を行いキャリア濃度を向上させる。この場合、前記第 1 フォトレジスト膜 PRT1 が形成されている部分においてレーザ光 RL の照射が阻止され該第 1 フォトレジスト膜 PRT1 の直下の第 1 透明酸化物層 TOX1 は高抵抗が維持される。

**【 0 1 6 5 】**

その後、さらに前記第 1 フォトレジスト膜 PRT1 をマスクとして、前記第 1 絶縁膜 GI1 をマスクとして、前記第 1 絶縁膜 GI1 を除去する。

50

I 1 を除去する。

**【 0 1 6 6 】**

工程 4 .

図 16 ( d ) に示すように、基板 S U B 1 の表面の全域に金属を蒸着し、金属層 M T を形成する。

**【 0 1 6 7 】**

工程 5 .

図 16 ( e ) に示すように、基板 S U B 1 の表面の全域に第 2 フォトレジスト膜 P R T 2 を形成し、この第 2 フォトレジスト膜 P R T 2 をパターン化して、ソース信号線 S L の形成領域に第 2 フォトレジスト膜 P R T 2 を残存させる。

10

**【 0 1 6 8 】**

そして、この第 2 フォトレジスト膜 P R T 2 をマスクとし、このマスクから露出された前記金属層 M T を選択エッチングする。

**【 0 1 6 9 】**

さらに、前記第 2 フォトレジスト膜 P R T 2 を除去し、残存された前記金属層 M T をソース信号線 S L ' として構成する。

**【 0 1 7 0 】**

工程 6 .

図 16 ( f ) に示すように、たとえば S i O<sub>2</sub> からなる第 2 絶縁膜 G I 2 およびたとえば I T O 膜からなる第 2 透明酸化物層 T O X 2 を順次形成する。

20

**【 0 1 7 1 】**

工程 7 .

図 16 ( g ) に示すように、基板 S U B 1 の表面に第 3 フォトレジスト膜 P R T 3 を形成し、該第 3 フォトレジスト膜 P R T 3 をパターン化することによって、ゲート信号線 G L および薄膜トランジスタ T F T のゲート電極 G T を形成する部分において残存される第 3 フォトレジスト膜 P R T 3 を形成する。

**【 0 1 7 2 】**

そして、第 3 フォトレジスト膜 P R T 3 をマスクとし、このマスクから露出する前記第 2 透明酸化物層 T O X 2 を選択エッチングし、その下層の第 2 絶縁膜 G I 2 を露呈させる。

30

**【 0 1 7 3 】**

さらに、前記第 3 フォトレジスト膜 P R T 3 をそのまま残存させ、前記第 2 絶縁膜 G I 2 を通して第 1 透明酸化物層 T O X 1 にレーザ光 R L を照射する。これにより、ゲート電極 G T の直下の薄膜トランジスタ T F T のチャネル領域部と前記ソース信号線 S L ' との間の領域において結晶改質がなされ L D D 領域部 L D が形成される。このため、この工程におけるレーザ光 L D による結晶改質は、前記工程 3 におけるレーザ光 L D による結晶改質よりも、その改質程度を小さくする必要がある。

**【 0 1 7 4 】**

工程 8 .

図 16 ( h ) に示すように、前記第 3 フォトレジスト膜 P R T 3 を除去する。

40

**【 0 1 7 5 】**

実施例 5

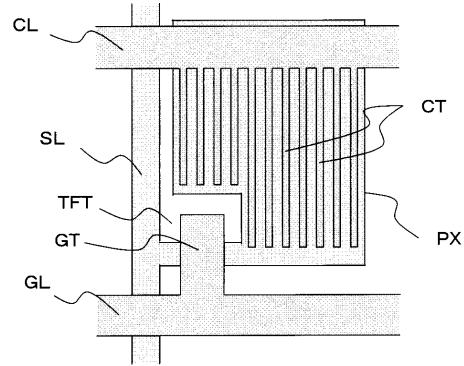

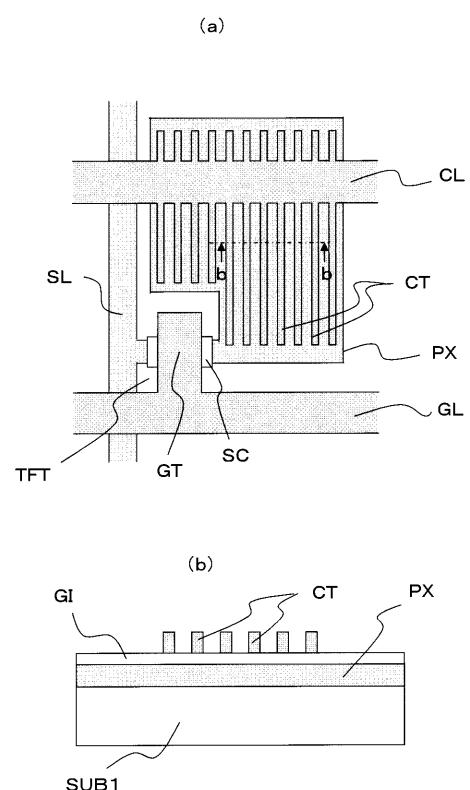

図 17 ( a ) は、本発明による表示装置の画素の構成の他の実施例を示す平面図である。また、図 17 ( b ) は、図 17 ( a ) の b - b 線における断面図である。

**【 0 1 7 6 】**

図 17 に示す画素は、基板 S U B 1 の液晶側の画素領域において画素電極 P X とこの画素電極 P X との間で電界を生じせしめる対向電極 C T を有するように構成されている。

**【 0 1 7 7 】**

画素電極 P X は薄膜トランジスタ T F T を介してソース信号線 S L から映像信号が供給される構成となっており、上述した実施例に示した構成とほぼ同じとなっている。

50

## 【0178】

前記対向電極 C T は、前記画素電極 P X に絶縁膜（たとえば第 1 絶縁膜）を介し該画素電極 P X と重畳して配置されるとともに、並設された多数の電極からなる櫛歯状電極として構成されている。

## 【0179】

なお、この対向電極 C T はその各電極の中途部において前記ゲート信号線 G L とほぼ平行に走行するコモン信号線 C L と一緒に形成され、該コモン信号線 C L を通して映像信号に対して基準となる基準電圧が前記櫛歯状電極に印加されるようになっている。

## 【0180】

また、前記コモン信号線 C L と一緒に形成的櫛歯状電極は前記ゲート信号線 G L と同層となつており、たとえば該ゲート信号線 G L の形成の際に同時に形成されるようになっている。 10

## 【0181】

このように構成された画素に図示しない配向膜を介して配置される液晶の分子は前記画素電極 P X と対向電極 C T の間に発生する電界によって挙動するようになっている。

## 【0182】

そして、この場合における画素の構成は、その画素電極 P X においてその全域にわたって結晶改質（あるいは不純物ドーピング）がなされて導体化されたものとなっている。

## 【0183】

その製造において、たとえば実施例 1 の図 8 に示したような方法を用い、ソース信号線 S L における結晶改質（あるいは不純物ドーピング）と同時に画素電極 P X の結晶改質（あるいは不純物ドーピング）をした場合は、画素電極はその全域にわたって結晶改質（あるいは不純物ドーピング）がなされる。 20

## 【0184】

しかし、このような構成に限定されることはなく、たとえば、図 17 ( b ) に対応する図 18 に示すように、画素電極 P X の前記対向電極 C T の直下における領域において結晶改質がなされていない場合であってもよい。画素の製造において、たとえば実施例 1 の図 9 に示したような方法を用いた場合、画素電極 P X へのレーザ光 R L の照射（あるいは不純物ドーピング）の際に既に形成されている対向電極 C T がマスクとなり、図 18 に示すような構成となる。

## 【0185】

なお、この場合にあって、画素電極 P X はコモン信号線 C L の下方においてもキャリア濃度が低くなってしまい、画素電極 P X 内に電位が到達し難いという不都合を解消したい場合が生じる。 30

## 【0186】

この場合、図 19 に示すように、対向電極 C T と一緒に形成するコモン信号線 C L を画素領域の周辺側に位置づけるように、すなわち、対向電極 C T の一端部において該コモン信号線 C L を結合させるパターンとして形成することによって、画素電極 P X の有効利用が図れるようになる。

## 【0187】

## 実施例 6

図 20 ( a ) は、本発明による表示装置の画素の構成の他の実施例を示す平面図であり、基板 S U B 1 の面に形成する 2 つの各透明酸化物層のうち上層に形成される第 2 透明酸化物層 T O X 2 が画素の領域の全域に形成され、その一部にゲート信号線 G L およびゲート電極 G T が形成されていることを示した図となっている。また、図 20 ( b ) は、図 20 ( a ) の b - b 線における断面図である。 40

## 【0188】

基板 S U B 1 の面に形成する 2 つの各透明酸化物層 T O X 1、T O X 2 のうち、下層に形成される第 1 透明酸化物層 T O X 1 は、画素の領域の全域に形成され、その一部にソース信号線 S L、このソース信号線 S L に接続される薄膜トランジスタ T F T、この薄膜トランジスタ T F T に接続される画素電極 P X が形成されている。 50

**【 0 1 8 9 】**

この第1透明酸化物層TOX1において、前記ソース信号線SL、薄膜トランジスタTFT、画素電極PX以外の領域にあっては結晶改質（あるいは不純物ドーピング）がなされていない領域（絶縁領域）となっている。このことから、この第1透明酸化物層TOX1は段差が形成されていない平坦な層として構成されている。

**【 0 1 9 0 】**

また、この第1透明酸化物層TOX1の上面には絶縁膜GIを介して第2透明酸化物層TOX2が画素の領域の全域に形成され、その一部にゲート信号線GLおよびこのゲート信号線GLに接続されたゲート電極GTが形成されている。すなわち、この第2透明酸化物層TOX2において、前記ゲート信号線GL、ゲート電極GT以外の領域にあっては結晶改質（あるいは不純物ドーピング）がなされておらず充分な透明性が確保された領域となっている。したがって、この第2透明酸化物層TOX2にあっても段差が形成されていない平坦な層として構成される。10

**【 0 1 9 1 】**

このように構成した表示装置は、画素の領域の全域に形成された第1透明酸化物層TOX1、絶縁膜GI、第2透明酸化物層TOX2の順次積層体によって、ソース信号線SL、ゲート信号線GL、薄膜トランジスタTFT、画素電極PXを形成できることから、表面における段差の発生を回避できる構成とすることができます。

**【 0 1 9 2 】**

また、図21は、本発明による表示装置の画素の構成の他の実施例を示す平面図であり20、図20(a)に対応した図となっている。

**【 0 1 9 3 】**

図21は、基板SUB1に対向電極CTおよびこの対向電極CTと接続されるコモン信号線CLを備えるものを示し、これら対向電極CTおよびコモン信号線CLは図20(a)に示した第2透明酸化物層TOX2の一部に形成されるようになっている。

**【 0 1 9 4 】**

基板SUB1の表面に形成された第2透明酸化物層TOX2に選択的に結晶改質（あるいは不純物ドーピング）を行って、ゲート信号線GL、ゲート電極GTとともに、前記対向電極CT、コモン信号線CLを形成するようになっている。

**【 0 1 9 5 】**

このように構成した表示装置においても、基板SUB1の表面における段差の発生を回避できる構成とすることができます。30

**【 0 1 9 6 】****実施例7**

図22は基板SUB1の表面にアレイ状に配置された各画素の一実施例を示した平面図で、図1と対応した図である。

**【 0 1 9 7 】**

図1の場合と比較して異なる構成は、薄膜トランジスタTFTにあり、その半導体層SCがたとえばゲート電極GTの両脇からはみ出して形成されている。この半導体層SCは、ソース信号線SLおよび画素電極PX等を構成する第1透明酸化物層TOX1と別個に形成されるものとして構成されている。40

**【 0 1 9 8 】**

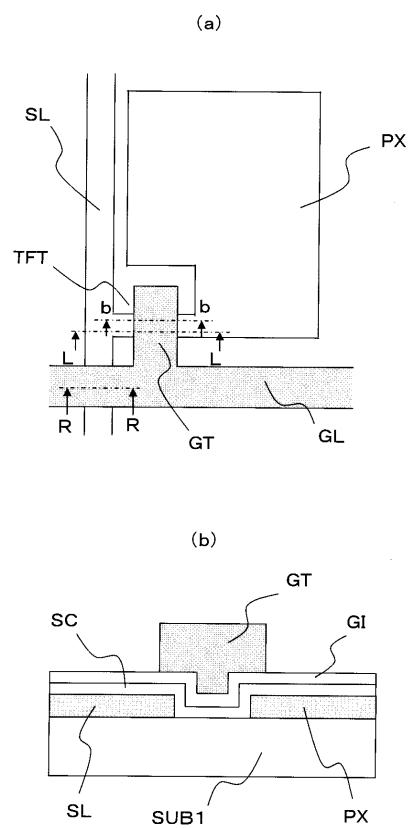

図23(a)は、前記各画素のうちの一画素を抜き出し拡大して示した図であり、そのb-b線における断面図を図23(b)に示している。

**【 0 1 9 9 】**

図23(b)において、基板SUB1の表面に薄膜トランジスタTFTのソース領域部STとドレイン領域部DTが物理的に離間されて配置されている。

**【 0 2 0 0 】**

前記ソース領域部STはソース信号線SLの延在部として前記ドレイン領域部DTは画素電極PXの延在部として形成され、これらはいずれもたとえば不純物がドープされたZ

nOやITO等の透明導電膜からなる第1透明酸化物層TOX1によって形成されている。

**【0201】**

すなわち、前記第1透明酸化物層TOX1は、ソース信号線SL、このソース信号線SLの延在部としての薄膜トランジスタTFTのソース領域部ST、画素電極PX、この画素電極PXの延在部としての薄膜トランジスタTFTのドレイン領域部の各形成領域に形成され、さらに、薄膜トランジスタTFTのチャネル領域部に切り欠き部が形成されたパターンとして構成されている。

**【0202】**

そして、前記ソース領域部STとドレイン領域部DTの間には、半導体層SCがその一端において前記ソース領域部STと重畳し他端において前記ドレイン領域部DTと重畳して配置されている。ソース領域部STとドレイン領域部DTとの間にある前記半導体層SCは薄膜トランジスタTFTのチャネル領域部CHとして機能するようになっている。10

**【0203】**

このように形成された基板SUB1の表面には前記ソース信号線SL、ソース領域部ST、半導体層SC、ドレイン領域部DT、画素電極PX等を被って絶縁膜GIが形成され、この絶縁膜GIの上面に前記半導体層SCのチャネル領域に重畳してゲート電極GTが形成されている。このゲート電極GTはゲート信号線GLの延在部として構成されている。20

**【0204】**

図25は、前記表示装置の製造方法の一実施例を示す工程図である。

**【0205】**

ここで、図25に示す工程は液晶表示領域の一画素における工程図を示し、図25の左側に示す工程図は図23に示す画素の図中L-Lの個所に相当し、図25の右側に示す工程図は図23に示す画素の図中R-Rの個所に相当している。なお、図24に示す画素は図23(a)に示した画素と同様となっている。

**【0206】**

以下、工程順に説明する。

**【0207】**

工程1.

図25(a)に示すように、基板SUB1を用意し、この基板SUB1の表面にたとえば不純物がドープされたZnOからなる第1透明酸化物層TOX1を形成する。30

**【0208】**

工程2.

図25(b)に示すように、基板SUB1の表面に第1フォトレジスト膜PRT1を形成し、これをパターン化することにより、ソース信号線SL、このソース信号線SLの延在部となる薄膜トランジスタTFTのソース領域部ST、画素電極PX、この画素電極PXの延在部となる薄膜トランジスタTFTのドレイン領域部DTの形成領域における第1フォトレジスト膜PRT1を残存させる。

**【0209】**

そして、残存された第1フォトレジスト膜PRT1をマスクとし、このマスクから露出された第1透明酸化物層TOX1を選択エッチングする。これにより、ソース信号線SL、薄膜トランジスタTFTのソース領域部ST、画素電極PX、薄膜トランジスタTFTのドレイン領域部DTが形成される。40

**【0210】**

工程3.

図25(c)に示すように、前記第1フォトレジスト膜PRT1を除去する。

**【0211】**

工程4.

図25(d)に示すように、基板SUB1の表面に第2フォトレジスト膜PRT2を形50

成し、これをパターン化することにより、前記ソース領域部 S T とドレイン領域部 D T の離間部、ソース領域部 S T の前記離間部側の先端部、ドレイン領域部 D T の前記離間部側の先端部を露出させるように穴開けがなされた第 2 フォトレジスト膜 P R T 2 を残存させる。

【 0 2 1 2 】

そして、基板 S U B 1 の表面に、真性あるいは低濃度の不純物がドープされたたとえば Z n O からなる第 2 透明酸化物層 T O X 2 を形成する。

【 0 2 1 3 】

工程 5 .

図 2 5 ( e ) に示すように、前記第 2 フォトレジスト膜 P R T 2 を除去することにより 10 、ソース領域部 S T とドレイン領域部 D T の離間部において、一端が前記ソース領域部 S T と重畠し他端が前記ドレイン領域部 D T と重畠して配置される第 2 透明酸化物層 T O X 2 を選択的に形成する。いわゆるリフトオフ法による形成である。この第 2 透明酸化物層 T O X 2 は薄膜トランジスタ T F T の半導体層 S C として構成される。

【 0 2 1 4 】

工程 6 .

図 2 5 ( f ) に示すように、基板 S U B 1 の表面に、たとえば S i O <sub>2</sub> 膜からなる絶縁膜 G I 、たとえば I T O 膜からなる第 3 透明酸化物層 T O X 3 を順次形成する。

【 0 2 1 5 】

前記絶縁膜 G I は、薄膜トランジスタ T F T のゲート絶縁膜および前記ソース信号線 S L に対する後述のゲート信号線 G L の層間絶縁膜として機能するようになっている。 20

【 0 2 1 6 】

なお、薄膜トランジスタ T F T のゲート絶縁膜は、工程 4 において薄膜トランジスタ T F T の半導体層に積層される絶縁膜を形成しておくことによって、形成するようにしてもよい。

【 0 2 1 7 】

工程 7 .

図 2 5 ( g ) に示すように、基板 S U B 1 の表面に第 3 フォトレジスト膜 P R T 3 を形成し、これをパターン化することにより、ゲート電極 G T およびこのゲート電極 G T に接続されるゲート信号線 G L の形成領域における第 3 フォトレジスト膜 P R T 3 を残存させる。 30

【 0 2 1 8 】

そして、残存された第 3 フォトレジスト膜 P R T 3 をマスクとし、このマスクから露出された第 3 透明酸化物層 T O X 3 を選択エッチングする。これにより、ゲート電極 G T およびゲート信号線 G L が形成される。

【 0 2 1 9 】

工程 8 .

図 2 5 ( h ) に示すように、第 3 フォトレジスト膜 P R T 3 を除去する。

【 0 2 2 0 】

図 2 6 ( a ) は、本発明による表示装置の画素の他の実施例を示した平面図で、図 2 3 ( a ) と対応した図である。また、図 2 6 ( a ) の b - b 線における断面図を図 2 2 ( b ) に示している。 40

【 0 2 2 1 】

図 2 3 の場合と比較して異なる構成は、薄膜トランジスタ T F T のチャネル領域部として機能する半導体層 S C にあり、この半導体層 S C は薄膜トランジスタ T F T のチャネル領域部のみならずソース信号線 S L 、薄膜トランジスタ T F T のソース領域部 S T およびドレイン領域部 D T 、画素電極 P X の上方に積層されて形成されていることにある。

【 0 2 2 2 】

図 2 7 は、前記表示装置の製造方法の一実施例を示す工程図である。

【 0 2 2 3 】

ここで、図27に示す工程は液晶表示領域の一画素における工程図を示し、図27の左側に示す工程図は図26(a)に示す画素の図中L-Lの個所に相当し、図27の右側に示す工程図は図26(a)に示す画素の図中R-Rの個所に相当している。

**【0224】**

以下、工程順に説明する。

**【0225】**

工程1.

図27(a)に示すように、基板SUB1を用意し、この基板SUB1の表面にたとえば不純物がドープされたZnOからなる第1透明酸化物層TOX1を形成する。

**【0226】**

10

工程2.

図27(b)に示すように、基板SUB1の表面に第1フォトレジスト膜PRT1を形成し、これをパターン化することにより、薄膜トランジスタTFTの半導体層SCが形成される領域において孔開けされた第1フォトレジスト膜PRT1を残存させる。

**【0227】**

そして、残存された第1フォトレジスト膜PRT1をマスクとし、このマスクから露出された第1透明酸化物層TOX1を選択エッチングする。

**【0228】**

工程3.

図27(c)に示すように、前記第1フォトレジスト膜PRT1を除去する。

20

**【0229】**

工程4.

図27(d)に示すように、基板SUB1の表面に、真性あるいは低濃度の不純物がドープされたたとえばZnOからなる第2透明酸化物層TOX2を形成する。

**【0230】**

この第2透明酸化物層TOX2は、前記第1透明酸化物層TOX1の選択エッチングされた部分において薄膜トランジスタTFTの半導体層SCとして機能するものである。

**【0231】**

工程5.

図27(e)に示すように、基板SUB1の表面に第2フォトレジスト膜PRT2を形成し、これをパターン化することにより、ソース信号線SL、薄膜トランジスタTFTのソース領域部ST、チャネル領域部CH、ドレイン領域部DT、および画素電極PXの形成領域における第2フォトレジスト膜PRT2を残存させる。

30

**【0232】**

そして、残存された第2フォトレジスト膜PRT2をマスクとし、このマスクから露出された第1透明酸化物層TOX1を選択エッチングする。

**【0233】**

工程6.

図27(f)に示すように、前記第2フォトレジスト膜PRT2を除去する。これにより、基板SUB1の表面には、ソース信号線SL、このソース信号線SLの延在部として構成される薄膜トランジスタTFTのソース領域部ST、画素電極PX、この画素電極PXの延在部として構成される薄膜トランジスタTFTのドレイン領域部DTを構成する第1透明酸化物層TOX1、および薄膜トランジスタTFTの半導体層SCの形成領域(前記第1透明酸化物層TOX1の開口が設けられた部分)、前記第1透明酸化物層TOX1の上方の領域に第2透明酸化物層TOX2が形成されることになる。

40

**【0234】**

工程7.

図27(g)に示すように、基板SUB1の表面にたとえばSiO<sub>2</sub>膜からなる絶縁膜GI、たとえばITO膜からなる第3透明酸化物層TOX3を順次形成する。

**【0235】**

50

前記絶縁膜 G I は、薄膜トランジスタ TFT のゲート絶縁膜および前記ソース信号線 S L に対する後述のゲート信号線 G L の層間絶縁膜として機能するようになっている。

**【 0 2 3 6 】**

工程 8 .

図 27 ( h ) に示すように、基板 SUB 1 の表面に第 3 フォトレジスト膜 P RT 3 を形成し、これをパターン化することにより、ゲート電極 G T およびこのゲート電極 G T に接続されるゲート信号線 G L の形成領域における第 3 フォトレジスト膜 P RT 3 を残存させる。

**【 0 2 3 7 】**

そして、残存された第 3 フォトレジスト膜 P RT 3 をマスクとし、このマスクから露出された第 3 透明酸化物層 T O X 3 を選択エッチングする。これにより、ゲート電極 G T およびゲート信号線 G L が形成される。10

**【 0 2 3 8 】**

工程 9 .

図 27 ( i ) に示すように、第 3 フォトレジスト膜 P RT 3 を除去する。

**【 0 2 3 9 】**

図 26 に示した画素の構成は、薄膜トランジスタ TFT のチャネル領域部を構成する半導体層 S C をソース信号線 S L 、薄膜トランジスタ TFT のソース領域部 S T およびドレイン領域部 D T 、画素電極 P X を構成する透明酸化物層の上層に配置させた構成としたものである。しかし、これらの層の位置関係を逆にし、薄膜トランジスタ TFT のチャネル領域部を構成する半導体層 S C をソース信号線 S L 、薄膜トランジスタ TFT のソース領域部 S T およびドレイン領域部 D T 、画素電極 P X を構成する透明酸化物層の下層に配置させる構成とするようにしてもよい。20

**【 0 2 4 0 】**

このように構成される画素の製造方法の一実施例を、途中までの工程として図 28 に示している。

**【 0 2 4 1 】**

以下、工程順に説明する。

**【 0 2 4 2 】**

工程 1 .

図 28 ( a ) に示すように、基板 SUB 1 を用意し、この基板 SUB 1 の表面に、たとえば ZnO からなる第 1 透明酸化物層 T O X 1 、さらにたとえば不純物がドープされた ZnO からなる第 2 透明酸化物層 T O X 2 を順次形成する。30

**【 0 2 4 3 】**

工程 2 .

図 28 ( b ) に示すように、基板 SUB 1 の表面に第 1 フォトレジスト膜 P RT 1 を形成し、この第 1 フォトレジスト膜 P RT 1 をパターン化することにより、ソース信号線 S L 、このソース信号線 S L の延在部として構成される薄膜トランジスタ TFT のソース領域部 S T 、薄膜トランジスタ TFT のチャネル領域部 C H 、画素電極 P X 、この画素電極 P X の延在部として構成される薄膜トランジスタ TFT のドレイン領域部 D T の形成領域に残存させ、かつ、薄膜トランジスタ TFT のチャネル領域部 C H の形成領域において他の部分よりも厚さの小さい第 1 フォトレジスト膜 P RT 1 を形成する。40

**【 0 2 4 4 】**

そして、この第 1 フォトレジスト膜 P RT 1 をマスクとして、このマスクから露出する第 2 透明酸化物層 T O X 2 、さらにその下層の第 1 透明酸化物層 T O X 1 を選択エッチングする。

**【 0 2 4 5 】**

工程 3 .

図 28 ( c ) に示すように、前記第 1 フォトレジスト膜 P RT 1 の表面を底面方向に適量の除去を行うことによって、薄膜トランジスタ TFT のチャネル領域部の形成領域に50

おける第2透明酸化物層TOX2の表面を露呈させ、その他の部分において該第1フォトレジスト膜PRT1を残存させる。

**【0246】**

そして、残存された第1フォトレジスト膜PRT1をマスクとして、薄膜トランジスタTFTのチャネル領域部の形成領域における第2透明酸化物層TOX2を選択エッチングし、その下層の第1透明酸化物層TOX1の表面を露呈させる。

**【0247】**

工程4.

図28(d)に示すように、前記第1フォトレジスト膜PRT1を除去する。そして、その後の工程は、図27(g)ないし(i)を経て完了する。

10

**【0248】**

図29(a)は、本発明による表示装置の画素の構成の他の実施例を示す平面図であり、図26(a)に対応する図となっている。

**【0249】**

図26の場合と比較して異なる構成は、薄膜トランジスタTFTの半導体層SCとして形成した第2透明酸化物層TOX2が、該薄膜トランジスタTFTのチャネル領域部CHの近傍部に止まらず、画素領域の全域に及んで形成されていることにある。

**【0250】**

また、図29において、第1透明酸化物層TOX1は、ソース信号線SL、このソース信号線SLの延在部として形成される薄膜トランジスタTFTのソース領域部ST、画素電極PX、画素電極PXの延在部として形成される薄膜トランジスタTFTのドレイン領域部DTの各形成領域において形成されたものである。

20

**【0251】**

図30は、前記表示装置の製造方法の一実施例を示す工程図である。

**【0252】**

ここで、図30は、前記画素における工程図を示し、図30の左側に示す工程図は図29(a)の画素の図中L-Lの個所に相当し、図30の右側に示す工程図は図29(a)の画素の図中R-Rの個所に相当している。

**【0253】**

以下、工程順に説明する。

30

**【0254】**

工程1.

図30(a)に示すように、基板SUB1を用意し、この基板SUB1の表面にたとえば不純物がドープされたZnOからなる第1透明酸化物層TOX1を形成する。

**【0255】**

工程2.

図30(b)に示すように、基板SUB1の表面に第1フォトレジスト膜PRT1を形成し、これをパターン化することにより、ソース信号線SL、ソース信号線SLの延在部として構成される薄膜トランジスタTFTのソース領域部ST、画素電極PX、画素電極PXの延在部として構成される薄膜トランジスタTFTのドレイン領域部DTの形成領域に第1フォトレジスト膜PRT1を残存させる。

40

**【0256】**

そして、残存された第1フォトレジスト膜PRT1をマスクとし、このマスクから露出する前記第1透明酸化物層TOX1を選択エッチングする。

**【0257】**

工程3.

図30(c)に示すように、第1フォトレジスト膜PRT1を除去する。

**【0258】**

工程4.

図30(d)に示すように、基板SUB1の表面に、真性あるいは低濃度の不純物がド

50

ープされたたとえばZnOからなる半導体層SC、たとえばSiO<sub>2</sub>膜からなる絶縁膜GIを順次形成する。

【0259】

前記半導体層SCは、薄膜トランジスタTFTの形成領域にあってはその半導体層として機能し、前記絶縁膜GIは、薄膜トランジスタTFTのゲート絶縁膜および前記ソース信号線SLに対する後述のゲート信号線GLの層間絶縁膜として機能するようになっている。

【0260】

その後、基板SUB1の表面に、たとえばITOからなる第2透明酸化物層TOX2を形成する。

10

【0261】

工程5.

図30(e)に示すように、基板SUB1の表面に第2フォトレジスト膜PRT2を形成し、これをパターン化することにより、ゲート電極GTおよびこのゲート電極GTに接続されるゲート信号線GLの形成領域における第2フォトレジスト膜PRT2を残存させる。

【0262】

そして、残存された第2フォトレジスト膜PRT2をマスクとし、このマスクから露出された第2透明酸化物層TOX2を選択エッチングする。これにより、ゲート電極GTおよびゲート信号線GLが形成される。

20

【0263】

工程6.

図30(f)に示すように、第2フォトレジスト膜PRT2を除去する。

【0264】

実施例8

図31(a)は、本発明による表示装置の画素の構成の他の実施例を示す平面図で、図23(a)と対応した図となっている。また、図31(b)は図31(a)のb-b線における断面図である。

【0265】

図23の場合と比較して異なる構成は、透明酸化物層で形成したソース信号線SLと重ねて新たなソース信号線SL'を設けたことにある。

30

【0266】

すなわち、ソース信号線SL'はたとえば金属層から構成され基板SUB1の表面に形成されている。

【0267】

そして、このようにソース信号線SL'が形成された基板SUB1の表面に図23に示した構成を形成し、該ソース信号線SL'に前記ソース信号線SLを重畳するようにしたものである。

【0268】

このように構成することにより、金属層を含む多層構造のソース信号線を得ることができ、該ソース信号線の電気的な抵抗を大幅に低減させることができる。

40

【0269】

図32は、このように構成された表示装置の製造方法の一実施例を途中の工程まで示した工程図で、図31(a)のIIIXII-IIIXII線における断面図を示している。

【0270】

まず、図32(a)に示すように、基板SUB1を用意し、この基板SUB1の表面の全域に金属層MTを形成し、この金属層MTの表面にフォトレジスト膜PRTを形成し、これをパターン化して、ソース信号線SL'を形成する領域にフォトレジスト膜PRTを残存させる。

【0271】

50

そして、このフォトレジスト膜 P R T をマスクとし、このマスクから露出する前記金属層 M T を選択エッチングする。

#### 【 0 2 7 2 】

次に、図 3 2 ( b ) に示すように、前記フォトレジスト膜 P R T を除去し、基板 S U B 1 の表面にたとえば不純物がドープされた Z n O からなる透明酸化物層 T O X を形成する。この透明酸化物層 T O X の形成は、図 2 5 ( a ) の工程に相当し、その後において、図 2 5 ( b ) ~ 図 2 5 ( h ) の工程を経ることにより、図 3 1 に示した画素を完成させることができる。

#### 【 0 2 7 3 】

図 3 1 に示した構成は、金属層からなるソース信号線 S L ' の長手方向のほぼ全域に及んで透明酸化物層のソース信号線 S L が積層された構成としたものである。しかし、透明酸化物層のソース信号線 S L は、ソース信号線 S L ' のほぼ全長にわたって形成する必要はなく、たとえば薄膜トランジスタ T F T の近傍部のみに形成するようにしてもよい。このような構成においても、ソース信号線の電気的抵抗を低減させることができるからである。

#### 【 0 2 7 4 】

また、図 3 1 に示した構成は、金属層からなるソース信号線 S L ' を透明酸化物層のソース信号線 S L の下層に形成したものである。しかし、金属層からなるソース信号線 S L ' を透明酸化物層のソース信号線 S L の上層に形成するようにしてもよい。

#### 【 0 2 7 5 】

図 3 3 は、該ソース信号線 S L ' をソース信号線 S L の上層に形成した場合の一実施例を示す構成図で、図 3 1 と対応させて描いている。

#### 【 0 2 7 6 】

##### 実施例 9

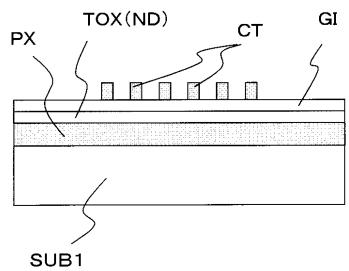

図 3 4 ( a ) は、本発明による表示装置の画素の構成の他の実施例を示す平面図であり、図 2 3 ( a ) と対応した図となっている。また、図 3 4 ( b ) は図 3 4 ( a ) の b - b 線における断面図である。

#### 【 0 2 7 7 】

図 2 3 ( a ) の場合と比較して異なる構成は、基板 S U B 1 の表面において、前記画素電極 P X との間に電界を生じせしめる対向電極 C T とこの対向電極 C T に映像信号に対して基準となる電圧を有する信号を供給するためのコモン信号線 C L を備えることにある。

#### 【 0 2 7 8 】

該対向電極 C T は、画素電極 P X に対して絶縁膜 G I を介して重畠され、互いに並設される多数の電極群で構成され、コモン信号線 C L と一体となって形成されている。

#### 【 0 2 7 9 】

また、対向電極 C T およびコモン信号線 C L は、たとえばゲート信号線 G L と同層に形成されている。

#### 【 0 2 8 0 】

さらに、対向電極 C T およびコモン信号線 C L は金属層で構成してもよく、また、たとえば、図 2 1 で示したように、画素の全域にわたった形成した透明酸化物層にゲート信号線 G L ( ゲート電極 G T ) とともに選択的に形成してもよい。

#### 【 0 2 8 1 】

また、図 3 4 ( b ) に対応した図である図 3 5 に示すように、前記絶縁膜 G I と画素電極 P X との間にたとえば不純物ドーピングがなされていない透明酸化物層 T O X ( N D ) が介在していてもよい。この透明酸化物層 T O X ( N D ) は、たとえば薄膜トランジスタ T F T の形成領域において半導体層 S C として機能するもので、選択的に除去するのを回避して画素の領域に及んで形成されるものである。

#### 【 0 2 8 2 】

##### 実施例 1 0

図 3 6 は、基板 S U B 1 に上述した構成の画素 ( 図示せず ) が形成されているとともに

10

20

30

40

50

、各ゲート信号線 G L への走査信号の供給は該基板 S U B 1 に搭載されるゲート信号駆動回路 V によってなされ、各ソース信号線 S L への映像信号の供給は該基板 S U B 1 に搭載されるソース信号駆動回路 H e によってなされることを示している。

#### 【 0 2 8 3 】

前記ゲート信号線 G L は、モリブデン、クロム、タンゲステン、アルミ、銅、チタン、ニッケル、タンタル、銀、亜鉛、あるいはその他の金属の単膜、それらの合金膜、それらの積層膜、それらと I T O や Z n O 等の透明酸化物層の積層膜によって構成してもよい。

#### 【 0 2 8 4 】

また、ソース信号線 S L を透明酸化物層と金属層の多層構造で構成する場合、前記金属層として、モリブデン、クロム、タンゲステン、アルミ、銅、チタン、ニッケル、タンタル、銀、亜鉛、あるいはその他の金属の単膜、それらの積層膜、それらの合金膜によって構成してもよい。

10

#### 【 0 2 8 5 】

なお、図 3 6 には図示されていないが、基板 S U B 1 に画素電極 P X との間で電界を発生せしめる対向電極 C T を形成する場合において、該対向電極 C T あるいはこの対向電極 C T に信号を供給するコモン信号線 C L は、モリブデン、クロム、タンゲステン、アルミ、銅、チタン、ニッケル、タンタル、銀、亜鉛、あるいはその他の金属の単膜、それらの積層膜、それらの合金膜、それらと I T O や Z n O 等の透明酸化物層の積層膜によって構成してもよい。

#### 【 0 2 8 6 】

なお、前記基板 S U B は、通常のガラス基板以外に、たとえば合成樹脂あるいはステンレス等からなるフレキシブル基板として構成してもよい。低温で成膜可能な材料を用いているため基板 S U B 1 の材料に合成樹脂を用いることができるからである。

20

#### 【 0 2 8 7 】

上述した表示装置およびその製造方法は、透過型、反射型、半透過型、I P S 型、あるいは I P S - P r o 型の各液晶表示装置はもちろんのこと、有機 E L 表示装置等の他の表示装置にも適用できる。各画素毎に薄膜トランジスタを備えアクティブマトリクス駆動がなされる表示装置において同様の課題を有するからである。

#### 【 0 2 8 8 】

上述した各実施例はそれぞれ単独に、あるいは組み合わせて用いても良い。それぞれの実施例での効果を単独あるいは相乗して奏することができるからである。

30

#### 【 図面の簡単な説明 】

#### 【 0 2 8 9 】

【 図 1 】液晶表示装置の液晶を介して対向配置される各基板のうち一方の基板の液晶側の面の液晶表示領域に形成される回路の一実施例を示す構成図である。

【 図 2 】図 1 に示した各画素のうち一の画素の構成の一実施例を示す図である。

【 図 3 】基板の上面に形成した透明酸化物層にキャリア濃度の高い領域を選択的に形成する場合の一実施例を示した図である。

【 図 4 】基板の上面に形成した透明酸化物層にキャリア濃度の高い領域を選択的に形成する場合の他の実施例を示した図である。

40

【 図 5 】基板の上面に形成した透明酸化物層にキャリア濃度の高い領域を選択的に形成する場合の他の実施例を示した図である。

【 図 6 】基板の上面に形成した透明酸化物層にキャリア濃度の高い領域を選択的に形成する場合の他の実施例を示した図である。

【 図 7 】図 8 に示す工程図の断面個所を示す画素の平面図である。

【 図 8 】図 7 に示す画素を有する液晶表示装置の製造方法の一実施例を示す工程図である。

【 図 9 】図 7 に示す画素を有する液晶表示装置の製造方法の他の実施例を示す工程図である。

【 図 1 0 】本発明による表示装置の画素の構成の他の実施例を示す平面図である。

50

【図11】本発明による表示装置の画素の構成の他の実施例を示す平面図である。

【図12】図11に示す金属層からなるソース信号線の一実施例を示す工程図である。

【図13】図11に示す画素の構成の改変例を示す説明図である。

【図14】本発明による表示装置の画素の構成の他の実施例を示す平面図である。

【図15】図14に示す画素を有する液晶表示装置の製造方法の一実施例を示す工程図である。

【図16】図14に示す画素を有する液晶表示装置の製造方法の他の実施例を示す工程図である。

【図17】本発明による表示装置の画素の他の実施例を示す構成図である。 10

【図18】本発明による表示装置の画素の他の実施例を示す構成図である。

【図19】本発明による表示装置の画素の他の実施例を示す構成図である。

【図20】本発明による表示装置の画素の他の実施例を示す構成図である。

【図21】本発明による表示装置の画素の他の実施例を示す構成図である。

【図22】液晶表示装置の液晶を介して対向配置される各基板のうち一方の基板の液晶側の面の液晶表示領域に形成される回路の他の実施例を示す構成図である。

【図23】図22に示した各画素のうち一の画素の構成の一実施例を示す図である。

【図24】図25に示す工程図の断面個所を示す画素の平面図である。

【図25】図24に示す画素を有する液晶表示装置の製造方法の一実施例を示す工程図である。 20

【図26】本発明による表示装置の画素の他の実施例を示す構成図である。

【図27】図26に示す画素を有する表示装置の製造方法の一実施例を示す工程図である。

【図28】図26に示す画素を有する表示装置の製造方法の他の実施例を示す工程図である。

【図29】本発明による表示装置の画素の他の実施例を示す構成図である。

【図30】図29に示す画素を有する表示装置の製造方法の一実施例を示す工程図である。

【図31】本発明による表示装置の画素の他の実施例を示す構成図である。

【図32】図31に示す画素を有する表示装置の製造方法を示す工程図である。 30

【図33】本発明による表示装置の画素の他の実施例を示す構成図である。

【図34】本発明による表示装置の画素の他の実施例を示す構成図である。

【図35】本発明による表示装置の画素の他の実施例を示す構成図である。

【図36】本発明による表示装置において基板に信号駆動回路が搭載されていることを示す説明図である。

#### 【符号の説明】

##### 【0290】

S U B 1 ..... 基板、 S L 、 S L ' ..... ソース信号線、 G L ..... ゲート信号線、 G T ..... ゲート電極、 T F T ..... 薄膜トランジスタ、 S T ..... ソース領域部、 D T ..... ドレイン領域部、 C H ..... チャネル領域部、 L D ..... L D D 領域部、 P X ..... 画素電極、 G I ..... 絶縁膜、 P R T ..... フォトレジスト膜、 R L ..... レーザ光、 T O X ..... 透明酸化物層、 T M ... 金属層、 N P I ..... 不純物イオン、 D M ..... ドーパント原料、 C T ..... 対向電極、 C L ..... コモン信号線、 S C ..... 半導体層、 V ..... ゲート信号駆動回路、 H e ..... ソース信号駆動回路。 40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

(b)

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

---

フロントページの続き

(72)発明者 佐藤 健史

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

(72)発明者 波多野 睦子

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

(72)発明者 豊田 善章

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

審査官 小野 博之

(56)参考文献 特開2003-050405(JP,A)

特開2004-319673(JP,A)

特開2002-319682(JP,A)

特開平05-114724(JP,A)

特開平09-318975(JP,A)

特開平09-269503(JP,A)

特開2008-040343(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 09 F 9 / 30

G 02 F 1 / 1368

H 01 L 21 / 336

H 01 L 29 / 786