#### (19) World Intellectual Property Organization International Bureau

#### (43) International Publication Date 14 November 2002 (14.11.2002)

#### **PCT**

#### (10) International Publication Number WO 02/090243 A2

(51) International Patent Classification7: B81B 3/00, B81C 1/00, G02B 26/02

[GB/GB]; 4F1 3 Viewforth Square, Edinburgh EH10 4LP (GB). PODLECKI, Jean [FR/GB]; 48/2 North Gyle Grove, Edinburgh EH12 8LF (GB).

(21) International Application Number: PCT/GB02/02009

(74) Agent: McDONOUGH, Jonathan; Urquhart-Dykes & Lord, Tower House, Merrion Way, Leeds LS2 8PA (GB).

(22) International Filing Date: 2 May 2002 (02.05.2002)

(81) Designated States (national): CN, JP, US.

(25) Filing Language: English

> (84) Designated States (regional): European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR).

(26) Publication Language: English

Published:

(30) Priority Data: 0110932.1 4 May 2001 (04.05.2001)

> without international search report and to be republished upon receipt of that report

(71) Applicant (for all designated States except US): ALCA-TEL OPTRONICS UK LIMITED [GB/GB]; Starlaw Park, Starlaw Road, Livingston, West Lothian EH54 8SF (GB).

> For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(72) Inventors; and

(75) Inventors/Applicants (for US only): BLAIRE, Paul

(54) Title: THICK SANDWICH WAFER FOR MEMS FABRICATION

(57) Abstract: An improved method of manufacturing MEMS devices having relatively large components, such as large diameter micro mirrors, which require to be tilted at an angle to the wafer substrate, or displaced generally vertically, is described. In the described embodiment an SOI wafer having a sacrificial oxide layer at least 20 µm thick is formed. This provides sufficient space between the wafer substrate and a component formed in the upper silicon layer to allow a relatively large component to be tilted or displaced by a desired amount relative to the wafer substrate, The SOI wafer may be formed by bonding two separate SOI wafers together, A MEM device formed according to the method is also claimed.

### Thick Sandwich Wafer for MEMS Fabrication

The present invention relates to the field of micro machined devices, also often referred to as micro-electro-mechanical systems (MEMS). More specifically, though not exclusively, the invention relates to an improved technique for fabricating MEMS devices which require large tilt, or displacement of components in a generally vertical direction, relative to the wafer in which they are fabricated.

10

15

20

25

5

MEMS, and MEMS devices which incorporate optical components (i.e. Micro-optical Electro-Mechanical or MOEMS devices), enable the manufacture of complex free-space mechanical and optical circuits on a single silicon chip. For the avoidance of doubt, the term MEMS as used hereinafter is intended to also include MOEMS. Various techniques are known for fabricating MEMS devices incorporating various mechanical and/or optical components, including movable and/or rotatable components.

The gap between the moving components of a MEMS device and the underlying substrate is an important parameter in MEMS design as it governs the vertical movement range of the movable MEMS component when that vertical movement is in any way towards the substrate, e.g. displacement into the substrate and particularly tilt. An example of the former might be a beam that is required to flex substantially into the body of the substrate. Another example is a membrane that deflects into the substrate. Tilt is an important aspect in MEMS devices where large (≥ 500 µm diameter) optical components such as lenses, mirrors, etc. are required to have moderate angular tilt ranges. Alternatively these may be small (< 500 µm diameter) optical components required to have large angular tilt

ranges. Either could be employed within, for example, a free space optical system such as an optical cross connect or optical scanner where large angular ranges are vital to ensure that an optical beam can be displaced or scanned over a large area where the dimensions of the scan area are greater then the separation between the scan area and the MEMS device.

The methods employed to fabricate 3-dimensional movable MEMS structures dictate the maximum gap between the moving components of a MEMS device and the underlying substrate. The three principal known methods will now be described.

### Surface micro-machining

5

10

15

20

25

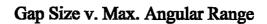

The MEMS structures are built using a succession of deposited and patterned "structural" layers and "sacrificial" layers. The structural layers are made of deposited polycrystalline material, usually polysilicon (polySi) thin metal layers. The sacrificial layers are typically boron phosphosilicate glass which is a form of doped silicon oxide (SiO<sub>2</sub>). In fabrication methods that employ the removal of sacrificial layers the air gap between the released moving components and substrate of a MEMS device is very small due to the typically thin sacrificial layer available. The graph of Fig.2 illustrates graphically the amount of tilt (in degrees) which is available for tiltable, generally planar, micro-components, such as micromirrors, for different air gap thicknesses between the tiltable component and the silicon substrate in which the micro-component is fabricated (the thickness of the air gap is determined by the thickness of the sacrificial oxide layer used). The different plot lines are for the four different component diameters indicated. It can be seen from the graph that the larger the diameter the larger the tilt required, and therefore the larger the air gap required. For a typical sacrificial layer thickness of 2 µm the tilt angle is

restricted to  $<\pm2^{\circ}$  for component diameters of  $>115\mu m$ . Induced stress in the deposited layers, leading to cracking and peeling of the layers, limit the thickness to typically  $1-2 \mu m$ .

5 There are two further issues with surface micro-machining beyond the intrinsically thin sacrificial layers. Where the actuation of the component is generally vertical relative to the wafer in which they are fabricated the thin sacrificial layer only permits small movements (tilts, displacements, etc) before some part of the components comes into contact with the substrate layer. In order to increase the vertical movement range of the components 10 additional structures must be included that raise the component, component supports and actuator to a higher level above the substrate in order to allow a larger freedom of movement. This is the case with the Lucent Technologies Inc dual axis tilting micro-mirror device described in Opto Laser Europe, 15 76, July 2000, page 26. Such additions add an unwanted complexity to the design and fabrication process, require assembly at component level and reduce the packing density of components of a wafer. This ultimately reduces device yield. Further the polySi layers are not flat after release due to induced stress arising from the deposition process. This leads to a poor 20 quality component when the flatness of the component is of paramount importance e.g. optical components.

### Bulk-micro machining + wafer bonding

25

In this technique, the MEMS structures are bulk-micro machined (i.e. substantially deeper etch depths than for surface micro-machining) using partial etches through both sides of the wafer, typically mono-crystalline silicon (Si), which is then fixed (anodic bonding or glued) onto another bulk-micro machined wafer which incorporates other actuation mechanisms, e.g. the electrodes. In bulk micro-machining a sacrificial layer is not

10

15

20

WO 02/090243 PCT/GB02/02009

employed to fabricate the MEMS device and consequentially large gaps between the moving components of a MEMS device and the underlying substrate are achieved.

An accurate realisation of the structural properties of the MEMS component is critical for precise and controlled actuation. The removal of the sacrificial etch layer from the process also serves to remove an etch stop layer thus the process must rely on in-situ etch depth measurement. The deposition techniques of surface micro-machining lead to considerably more accurate component realisation. Further the post fabrication assembly step of surface micro-machining is comparable in this case with an assembly step that requires two micro-machined wafers to be fixed together either by, e.g., anodic bonding or simply gluing. This is a wafer scale process requiring precise alignment as again the accurate realisation of the structural properties of the MEMS component is critical for precise and controlled actuation. This is further exacerbated given the prior fabrication steps diminish the surface quality of the wafers, which is vitally important in wafer bonding. Moreover, polishing techniques cannot be used as they would destroy the structures in the process. Furthermore the combination of wafer scale alignment and reduced surface quality can lead to a variation in the gap between the upper (moving) and lower (actuator means) parts of the MEMS component. Again realisation of a constant separation is critical for precise, controllable actuation.

# 25 Surface micro-machining of SOI wafers plus wafer bonding

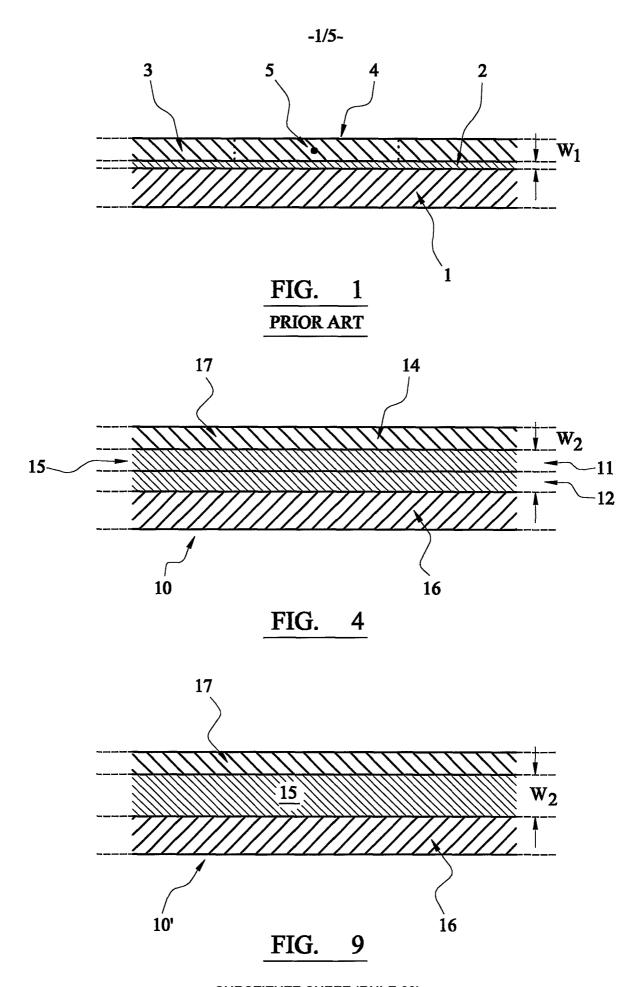

The fabrication principal is surface micro-machining but this technique uses a commercially available silicon-on-insulator (SOI) wafer as illustrated in Fig.1 The wafer is formed of a silicon substrate 1 with a thin sacrificial layer 2 of SiO<sub>2</sub> on top and a further layer 3 of Si on top of the SiO<sub>2</sub> layer. As with

the bulk micro-machining process the use of mono-crystalline Si leads to flatter and stronger components than those available using surface micro-machining and polysilicon layers. The current SOI manufacture process is limited by (wet) thermal growth process for SiO<sub>2</sub> which is governed through a square law relationship, such that the grown thickness is proportional to the square root of the growth time. While a 2µm layer may be grown in approximately 9 hours, a layer thickness of 10 to 30µm would require approx.8 to 62 days during which time it will be understood the deposition system must be run continuously.

10

15

20

25

5

Practical limitations set the maximum  $SiO_2$  layer thickness  $w_1$  to  $5\mu m$ . A MEMS structure 4 (for example a planar mirror) can be realized in the upper Si layer. However, the thin  $SiO_2$  layer 2 provides only a very small air gap (when the unwanted portions of the sacrificial layer are etched away) of thickness  $w_1$  between the released component and the silicon substrate when contacts are realised in the underlying substrate. Where the structure to be rotated is relatively large it will be appreciated that the air gap will not be thick enough to allow any significant tilt of the structure (about axis 5). SOI surface micro-machining can be combined with bulk machining in that an additional wafer contacting the actuator means can be bonded on either side of the SOI wafer. However, this approach carries with it the same disadvantages already discussed above.

It is an object of the present invention to avoid or minimize one or more of the foregoing disadvantages.

According to a first aspect of the invention we provide a method of fabricating a micro-electro-mechanical device comprising: providing a substrate; depositing a sacrificial layer of material which is at least 20µm

thick on top of the substrate; depositing a component layer of material on top of the sacrificial layer; and fabricating in the component layer at least one component which requires to be rotated and/or displaced relative to the substrate.

5

10

15

20

The sacrificial layer of material may advantageously be at least 30µm thick.

The at least one component may be a substantially planar component, for example a mirror, which requires to be rotated from a first plane generally parallel to the plane of the substrate to a second plane at an angle to the plane of the substrate.

Alternatively, or additionally, the at least one component may, for example, be a membrane or a cantilever which requires to be displaced in a direction generally perpendicular to the substrate, or with at least a component of motion perpendicular to the substrate. For the avoidance of doubt, this displacement may take the form of a movement of the whole component, or only a portion of the component. For example, the component may require to be flexed toward or away from the substrate (e.g. where the component is a membrane or cantilever beam).

The component layer is preferably made of a single crystalline material, preferably silicon. Alternatively, though less preferably, the component layer may be made of a polycrystalline material, for example polysilicon.

25 The sacrificial layer is preferably made of silicon dioxide (SiO<sub>2</sub>). The substrate is preferably made of silicon.

One advantage of the MEM device of the invention is that relatively large structures requiring relatively large vertical displacement can now be

10

15

20

achieved, since the thickness of the sacrificial layer allows the provision of a sufficiently large air gap between the component and the silicon substrate for the required rotation/tilt/displacement to be achieved. The inventive device also has a higher packing density than the above-described MEMS devices in which the rotatable component is raised above the plane of the upper component layer. Also, by using silicon as the component layer, good quality components, for example optical components such as mirrors, can be formed in the component layer (as compared with prior art devices in which the component layer is made of polysilicon). Actuator means may conveniently be provided through back vias (also sometimes known as "wafer feedthroughs") ensuring a uniform electrode-actuator gap separation.

According to a second aspect of the invention there is provided a method of fabricating a micro-electro-mechanical device comprising: forming a first wafer structure by depositing a sacrificial layer which is at least 10µm thick on top of a substrate; forming a second wafer structure substantially identical to the first wafer structure; bonding the first and second wafer structures together, with the sacrificial layers adjacent one another so as to form a composite wafer comprising a lower substrate, a combined sacrificial layer having a thickness of at least 20µm, and an upper component layer; and fabricating in the upper component layer at least one component which requires to be rotated and/or displaced relative to the lower substrate.

The sacrificial layer of each of the first and second wafers is preferably made of SiO<sub>2</sub> and the substrate of each of the first and second wafers is preferably made of silicon.

This latter method has the advantage of reducing the growing time to grow the thick sacrificial layer e.g. two  $SiO_2$  layers of thickness  $10\mu m$  can be grown together in the same time as one  $SiO_2$  layer of thickness  $20\mu m$ .

The method according to either the first or second above-described aspects of the invention may further include fabricating actuator means in the device, preferably in the substrate, and using the actuator means to displace the at least one component and/or rotating it from a first plane to a second plane.

10

15

20

25

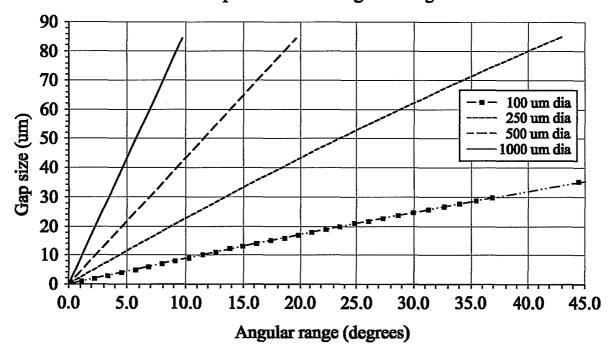

Preferably, each said SiO<sub>2</sub> layer is formed using a Flame Hydrolysis Deposition (FHD) process. FHD allows the growth of the required thickness of SiO<sub>2</sub> layer to be achieved in a much shorter period (generally between one to two orders of magnitude faster) than with traditional techniques for manufacturing SOI wafers, such as thermal growth (wet or dry oxidation techniques) or other deposition techniques such as Chemical Vapour Deposition (CVD). For example, wet oxidation of Si to form a layer of SiO<sub>2</sub> 10 to 30µm thick would take approx. 8 to 62 days, while FHD deposition and consolidation for a layer thickness of 10 to 30µm would only take approx. 13 to 14 hours (approx. 12 hours of which is the consolidation time, which is effectively independent of layer thickness). Fig.3 shows the time which would be required (in days) using thermal oxidation to achieve the SiO<sub>2</sub> thickness required for increasing tilt angle, for four different mirror diameters. Also as oxidation growth occurs on the whole wafer a polishing step is required to remove the SiO<sub>2</sub> on one side of the wafer, unlike FHD deposition. Nevertheless, such other growth methods may be used if desired.

10

20

25

According to another aspect of the invention there is provided a microelectro-mechanical device comprising a wafer formed of a substrate on top of which is a sacrificial layer which is at least 20µm thick, and an upper component layer on top of the sacrificial layer, and wherein fabricated in the upper component layer is at least one, preferably substantially planar, component which is rotatable and/or displaceable relative to the substrate.

The at least one component may be rotatable from a first plane generally parallel to the plane of the substrate to a second plane disposed at an angle to the plane of the silicon substrate. Alternatively, or additionally, the component may be displaceable in a direction substantially perpendicular to the substrate, or with at least a component of displacement perpendicular to the substrate.

15 The upper component layer is preferably silicon, the sacrificial layer is preferably SiO<sub>2</sub> and the substrate is preferably silicon.

The rotatable component may be permanently fixed in place after it has been tilted, prior to the MEMS device being used, or more commonly the component is tilted back and forward throughout operational use of the MEMs device e.g. in order to on/off switch a signal.

The at least one component fabricated in the upper component layer may be a mirror. Advantageously, the mirror has a relatively large diameter, preferably in the range of 500-1000µm. Preferably, the mirror can be tilted at an angle of at least 5 to 10 degrees to the silicon substrate. Figure 3 shows the time required (in days) using thermal oxidation to achieve the required depth of SiO<sub>2</sub> to allow this tilt range.

WO 02/090243

5

15

20

Preferably, the device further includes actuator means, most preferably electrostatic actuator means, fabricated in the wafer, most conveniently in the substrate, for actuating the at least one component to rotate it from the first to the second plane, or to displace the component generally vertically (e.g. by causing the component to flex). By integrating the actuator means in the wafer this avoids the need for a post process bonding of the MEMS device to another wafer incorporating the actuator means.

A preferred embodiment of the invention will now be described, by way of example only, and with reference to the accompanying drawings in which: 10 Fig.1 is a schematic cross-sectional view of a conventional SOI wafer; Fig.2 is a graph illustrating the amount of tilt available for increasing gap thickness between a micro-component and the substrate of an SOI wafer in which the component is formed, the different plot lines representing four different component diameters;

Fig.3 is a graph illustrating the time which would be required to grow, using thermal oxidation, an SiO<sub>2</sub> layer thick enough to allow a desired maximum tilt angle for four different diameters of a tiltable mirror component; Fig.4 is a schematic cross-sectional view of a new SOI wafer having a thick oxide layer;

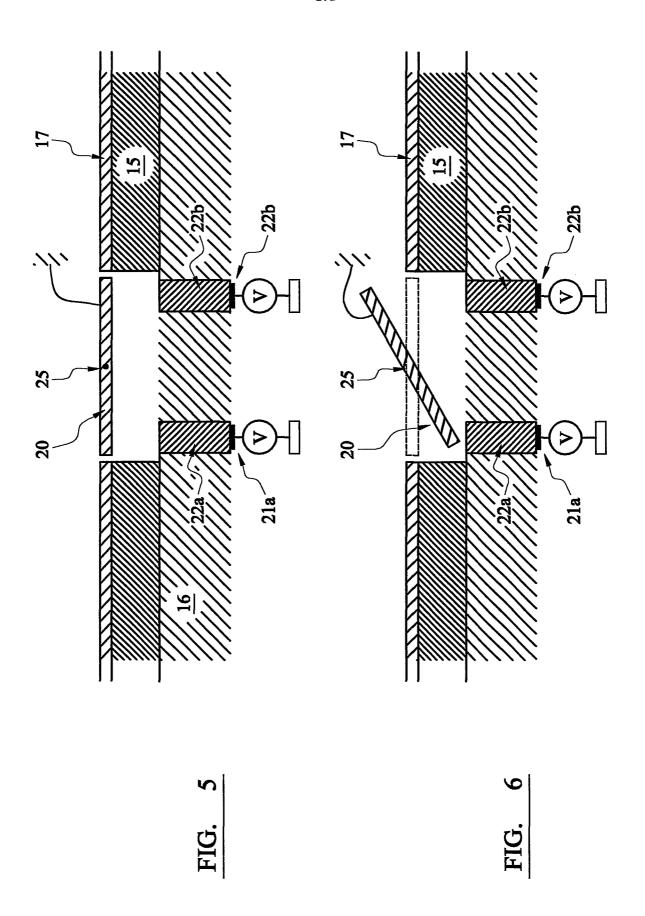

- Fig.5 is a schematic cross-sectional view of a MEMS device fabricated in the SOI wafer of Fig.3, according to one embodiment of the invention; Fig.6 shows the MEMS device of Fig.4 rotated from the generally horizontal plane in which it is shown in Fig.3, to its final angled orientation;

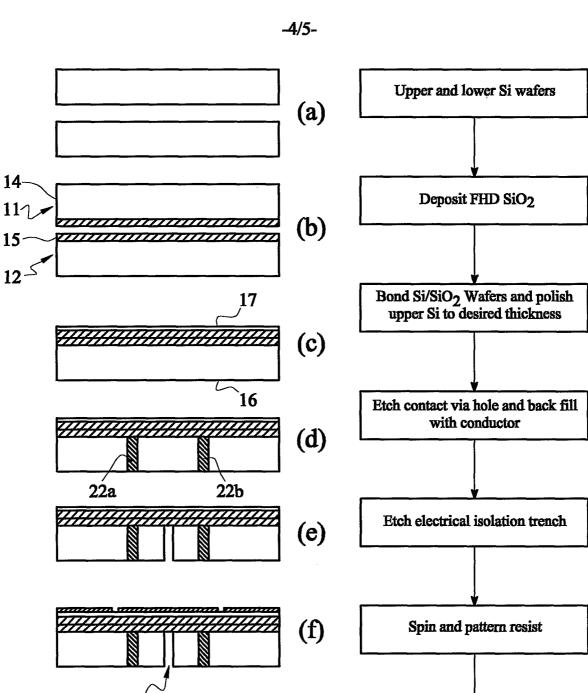

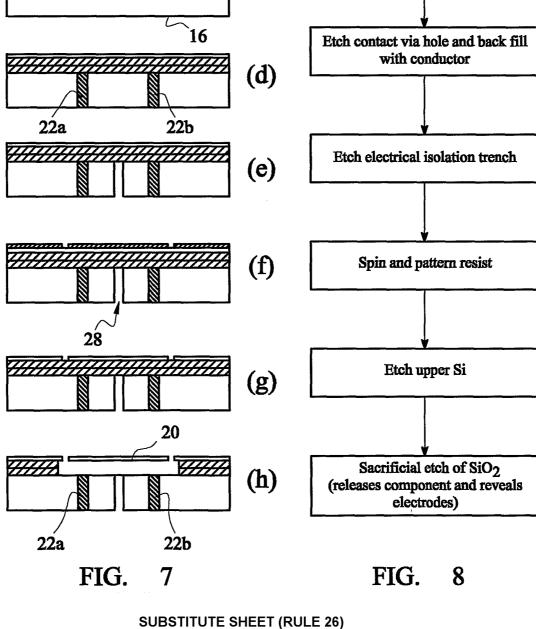

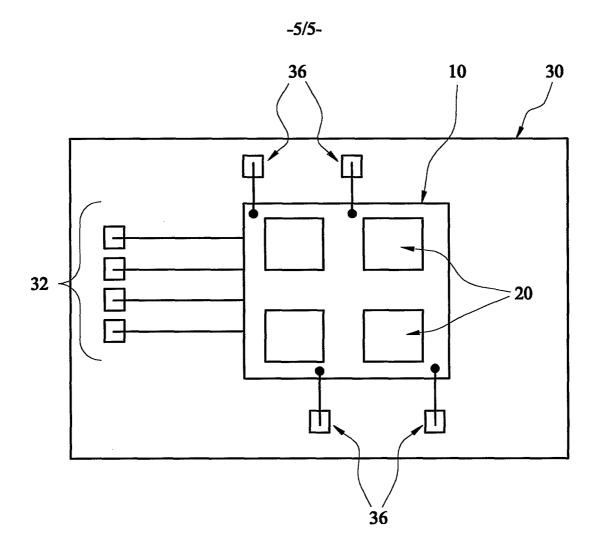

- Figs.7(a) to (h) are cross-sectional views illustrating the process steps 25 necessary to fabricate a MEMS device like that of Figs.4 to 6; Fig. 8 is a flow diagram of the process steps illustrated in Fig. 7; Fig. 9 is a schematic cross-sectional view of a new SOI wafer for fabricating a MEMS device in, according to an alternative embodiment of the invention;

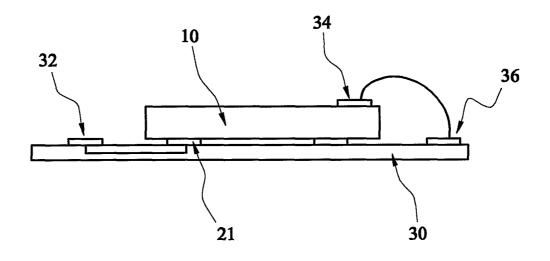

Fig.10 is a schematic plan view of a flip-chip assembled MEMS device containing an array of four micro-mirrors; and Fig.11 is a schematic side view of the device of Fig.7, showing only two of

5

10

15

the electrical connections.

Fig.4 illustrates an improved SOI wafer 10 in which a tiltable mirror component is to be micro machined. This wafer 10 is formed from two identical separate wafers 11,12 which are bonded together prior to the micro machining operation. Each separate wafer 11,12 consists of a silicon substrate 14 which is approximately microns to hundreds of microns thick, and an SiO<sub>2</sub> layer 15 deposited thereon which is at least 10μm thick. The SiO<sub>2</sub> layer is deposited by FHD, or alternatively by (wet) thermal oxidation (although the latter will take much longer). The benefit of FHD is that the FHD process can deposit an SiO<sub>2</sub> layer at a rate which is typically between one to two orders of magnitude faster than by using thermal oxidation. The upper surfaces of the SiO<sub>2</sub> layers of each separate wafer 11,12 are bonded together, for example by anodic bonding, thereby forming the SOI wafer of Fig.4, having an SiO<sub>2</sub> layer at least 20μm thick, a silicon substrate 16 and an upper silicon layer 17.

20

25

A tiltable mirror component 20 can then be machined in the upper silicon layer 17 using conventional MEMS micro machining technology, with sacrificial etching of the SiO<sub>2</sub> layer. Fig.5 shows the fabricated mirror component once the unwanted areas of sacrificial oxide layer have been etched away (to release the mirror). The mirror tilts about an axis 25 which lies in the upper silicon layer. The mirror 20 has a relatively large diameter of about 250-750μm, and can be rotated to its desired final position at an angle of, for example, about 14 to 5 degrees respectively assuming a 30μm

10

15

20

25

thick SiO<sub>2</sub> layer (see Fig.2), relative to the substrate 16, using electrostatic actuation means 22a,22b formed in the wafer substrate.

The electrostatic actuator comprises a pair of buried electrodes 22a,22b in the substrate 16. The electrodes are formed in the substrate (in conventional manner well-known to those skilled in the MEMS art) by etching into the back of the substrate and depositing a conductive layer that forms the electrodes under the movable component and leads out to also form the contact points for later bonding. Respective contact pads 21a,21b are provided on the exposed lower face of the electrodes 22a,22b, for electronic control of the actuator (by applying appropriate voltages thereto) so as to tilt the mirror 20 either down towards the left-hand one 22a of the electrodes (see Fig. 6), or down towards a right-hand one 22b of the electrodes. (The mirror 20 is earthed.) A 30µm air gap between the mirror (in its original plane) and the silicon substrate allows for a tilt of about  $\pm 7^{\circ}$  for a 500  $\mu$ m diameter mirror 20. The tilt angle available for this and other mirror diameters at this and other air gap thicknesses are readily apparent from Fig.2. A gap size of at least 20µm will allow a minimum tilt angle of 5 to 2 degrees for mirrors (or other components) of 500 to 1000µm diameter respectively.

In summary, the process steps necessary for creating the inventive device (containing the electrodes 22) of Fig.5 are listed in the flow diagram of Fig.9, and are schematically illustrated in Figs.7(a) to (h), and are as follows:

Figs.7(a)&(b): Deposit (preferably by FHD) the required SiO<sub>2</sub> layer 15 on each of the two Si wafers 11,12 (which will be the upper and lower wafers);

10

15

20

25

Fig.7(c): Bond the  $SiO_2$  layers of the two wafers together, and polish the upper Si layer 17 to a desired thickness, to obtain the desired  $SiO_2$  on  $SiO_2$  wafer;

Fig.7(d): Etch into the lower Si substrate using the SiO<sub>2</sub> as the etch stop, and back fill the etch hole(s) (or conformal coat the hole walls) with conductor, doped polysilicon for example, to form the electrodes 22a,22b; Fig.7(e) Etch an electrical isolation trench 28 between the electrodes (if desired);

(NB These two etch steps could alternatively be carried out prior to the bonding together of the two wafers)

Fig.7(f): Spin and pattern the upper Si layer 17 of the wafer with resist; Fig.7(g): Etch the upper Si layer, to form the moveable component 20 (as in Fig. 5), and remove the resist (as in conventional micro-machining); Fig.7(h): Carry out sacrificial etch of the SiO<sub>2</sub>, to release the movable component 20 and reveal the electrodes 22 under the movable component.

Flip-chip assembly techniques may be used, if desired, so that all electrical contact pads (including those for the mirror) are located on the same side of the assembled device. Thus, the wafer 10 would be flip-chip assembled to the upper side of a board 30 (see Figs.10 and 11), with the contact pads 21 connected to corresponding contacts 32 accessible on the upper side of the board 30, and any electrical connections 34 on the upper component layer of the wafer 20 (such connections may for example be required to earth the movable structures: multiple connections are likely as each component would be electrically isolated and therefore require an earth) being connected to respective electrical connections 36 also accessible on the upper side of the board 30. (NB Only two electrical connections are shown in Fig.11, for clarity)

WO 02/090243

5

10

15

20

25

14

PCT/GB02/02009

In the illustrated embodiment of Fig. 10, an array of substantially identical mirrors 20 is formed in the new "thick oxide layer" SOI wafer according to the invention. Only four mirrors are shown in Fig.10, but it will be appreciated that arrays of up to approximately 8x8 mirrors, and ultimately much larger arrays, will be generally desirable for switching applications. For example, some optical crossconnect switches may comprise a 500 x 500 matrix array of mirrors, or even a 1000 x 1000 matrix array. It will be appreciated that for such large crossconnects in order to minimize insertion loss due to diffraction losses, much larger mirror diameters are required than in smaller arrays. In fact, in order to keep diffraction losses to an acceptable level in such large crossconnects, the optical signal beam diameter will generally be in the range of 300-500 µm in which case a mirror diameter greater than 500µm is generally required. If smaller diameter, more collimated signal beams were used there would be much larger diffraction losses and thus larger insertion loss. Typically, for a 500 x 500 crossconnect, an oxide layer thickness of about 100 µm may be required, in order to enable large enough mirrors to be used, and for these mirrors to be able to be tilted by a sufficiently large angle to perform the desired switching operations. In general, the larger the size of the crossconnect matrix, the larger the mirror diameter required, and thus the greater the thickness of oxide layer required.

According to an alternative embodiment of the invention, the SOI wafer 10 may be formed as a single wafer, by depositing an SiO<sub>2</sub> layer of at least 20µm thickness onto a silicon substrate and then depositing the upper layer of silicon thereon. Such an SOI wafer is illustrated in Fig. 9. The disadvantage of this embodiment, as compared with the composite wafer of Fig. 4, is the increased time it will take to deposit a 20µm oxide layer on one

15

silicon substrate, as compared with a 10µm layer on each of two silicon substrates.

It will be appreciated that the above described embodiments offer significant advantages over prior art MEMS devices incorporating similarly sized mirror (or other) components, such as a higher packing density, mass production compatibility, good mechanical and optical properties, and no requirement for post process assembling of one wafer to another.

Further modifications and variations to the above-described embodiments are of course possible without departing from the scope of the invention. For example, if desired the actuator could be fabricated in a separate wafer to that of the mirror, although the benefits of an integrated actuator are then no longer available.

5

16

### **CLAIMS**

5

15

20

25

- 1. A method of fabricating a micro-electro-mechanical (MEM) device comprising: providing a substrate; depositing a sacrificial layer which is at least 20µm thick on top of the substrate; depositing a component layer on top of the sacrificial layer; and fabricating in the component layer at least one component which requires to be rotated and/or displaced relative to the substrate.

- 2. A method according to claim 1, wherein the sacrificial layer is at least 30µm thick.

- 3. A method according to claim 1 or claim 2, wherein said at least one component is substantially planar and requires to be rotated from a first plane generally parallel to the plane of the substrate to a second plane at an angle to the plane of the substrate.

- 4. A method according to any preceding claim, wherein said at least one component requires to be displaced in a direction substantially perpendicular to the substrate.

- 5. A method according to any preceding of claim, wherein the substrate is silicon, the sacrificial layer is formed by depositing a layer of SiO<sub>2</sub>, and the component layer is formed by depositing a layer of silicon on top of the SiO<sub>2</sub> layer, whereby an SOI wafer is formed.

- 6. A method of fabricating a micro-electro-mechanical (MEM) device comprising: forming a first wafer structure by depositing a sacrificial layer which is at least 10µm thick on top of a substrate; forming a

WO 02/090243

5

25

second wafer structure substantially identical to the first wafer structure; bonding the first and second wafer structures together, with the sacrificial layers adjacent one another so as to form a composite wafer comprising a lower substrate, a combined sacrificial layer having a thickness of at least 20µm, and an upper component layer; and fabricating in the upper component layer at least one component which requires to be rotated and/or displaced relative to the lower substrate.

- 7. A method according to claim 6, wherein said at least one component is substantially planar and requires to be rotated from a first plane generally parallel to the plane of the lower substrate to a second plane at an angle to the plane of the lower substrate.

- 8. A method according to claim 6 or claim 7, wherein said at least one component requires to be displaced in a direction substantially perpendicular to the plane of the lower substrate.

- 9. A method according to any of claims 6 to 8, wherein said sacrificial layer of each of the first and second wafers is made of SiO<sub>2</sub>, and the substrate of each of the first and second wafers is made of silicon.

- 10. The method according to any preceding claim, further including fabricating actuator means in the device and using the actuator means to rotate and/or displace said at least one component.

- 11. The method according to claim 5 or claim 9, wherein the or each said SiO<sub>2</sub> layer is formed using Flame Hydrolysis Deposition (FHD).

WO 02/090243

PCT/GB02/02009

12.A micro-electro-mechanical (MEM) device comprising a wafer formed of a substrate on top of which is a sacrificial layer which is at least 20µm thick, and a component layer on top of the sacrificial layer, and wherein fabricated in the component layer is at least one component which is rotatable and/or displaceable relative to the substrate.

18

- 13. A MEM device according to claim 12, wherein said at least one component is rotatable from a first plane generally parallel to the plane of the substrate to a second plane disposed at an angle to the plane of the substrate.

- 14.A MEM device according to claim 12 or claim 13, wherein said at least one component is displaceable in a direction substantially perpendicularly to the substrate.

- 15. A MEM device according to any of claims 12 to 14, wherein the substrate is made of silicon, the sacrificial layer is made of SiO<sub>2</sub> and the component layer is made of silicon.

20

25

5

10

15

- 16.A MEM device according to any of claims 12 to 15, wherein said at least one component fabricated in the component layer is a mirror.

- 17.A MEM device according to claim 16, wherein the mirror has a diameter in the range of 500-1000µm.

- 18.A MEM device according to claim 16 or claim 17, wherein the mirror is tilted at an angle of at least 5 degrees to the substrate.

19

- 19.A MEM device according to claim 17 or claim 18, wherein the sacrificial layer has a thickness  $\geq 100 \mu m$ .

- 20. A MEM device according to claim 19, wherein a matrix array of mirrors is fabricated in the component layer, the size of the matrix being at least 500 x 500.

- 21.A MEM device according to any of claims 12 to 20, further including actuator means fabricated in the wafer, for actuating said at least one component to rotate and/or displace it relative to the substrate.

- 22. A MEM device according to claim 21, wherein the actuator means comprises electrostatic actuator means.

10

5

SUBSTITUTE SHEET (RULE 26)

-2/5-

FIG. 2

## Oxidation Time v. Max. Angular Range

FIG. 3

**SUBSTITUTE SHEET (RULE 26)**

FIG. 10

FIG. 11

**SUBSTITUTE SHEET (RULE 26)**