(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-4030

(P2019-4030A)

(43) 公開日 平成31年1月10日(2019.1.10)

| (51) Int.Cl.                  | F 1        | テーマコード (参考) |

|-------------------------------|------------|-------------|

| <b>H01L 29/739</b> (2006.01)  | H01L 29/78 | 655B 5F048  |

| <b>H01L 29/78</b> (2006.01)   | H01L 29/78 | 657D        |

| <b>H01L 21/8234</b> (2006.01) | H01L 29/78 | 655D        |

| <b>H01L 27/06</b> (2006.01)   | H01L 29/78 | 653A        |

|                               | H01L 29/78 | 652Q        |

審査請求 未請求 請求項の数 5 O L (全 12 頁) 最終頁に続く

|           |                              |            |                                          |

|-----------|------------------------------|------------|------------------------------------------|

| (21) 出願番号 | 特願2017-117072 (P2017-117072) | (71) 出願人   | 000004260<br>株式会社デンソー<br>愛知県刈谷市昭和町1丁目1番地 |

| (22) 出願日  | 平成29年6月14日 (2017.6.14)       | (74) 代理人   | 110001128<br>特許業務法人ゆうあい特許事務所             |

|           |                              | (72) 発明者   | 村川 浩一<br>愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内       |

|           |                              | (72) 発明者   | 住友 正清<br>愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内       |

|           |                              | (72) 発明者   | 高橋 茂樹<br>愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内       |

|           |                              | F ターム (参考) | 5F048 AC10 BA01 BB19 BC03 BC12<br>BD07   |

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】リカバリ状態でのサージピーク電圧を小さくする。

【解決手段】IGBT領域1およびFWD領域2が共通の半導体基板10に形成されている半導体装置において、フィールドストップ層22をコレクタ層20およびカソード層21から離れて形成する。そして、FWD素子2aに順方向電流が流れている状態から当該電流を遮断してリカバリ状態となった際、FWD素子2a内の第1キャリアの一部がコレクタ層20へと流れることにより、サージピーク電圧を小さくする量の第2キャリアが第2電極23からコレクタ層20を介してドリフト層11に注入されるようにする。

【選択図】図3

## 【特許請求の範囲】

## 【請求項 1】

I G B T 素子 (1 a) を有する I G B T 領域 (1) と、 F W D 素子 (2 a) を有する F W D 領域 (2) とが共通の半導体基板 (10) に形成されている半導体装置において、

第 1 導電型のドリフト層 (11) と、

前記ドリフト層上に形成された第 2 導電型のベース層 (12) と、

前記ベース層の表層部であって、前記ベース層を挟んで前記ドリフト層から離れた位置に形成され、前記ドリフト層よりも高不純物濃度とされた第 1 導電型のエミッタ領域 (16) と、

前記ドリフト層を挟んで前記ベース層と反対側であって、前記 I G B T 領域に形成された第 2 導電型のコレクタ層 (20) と、

前記ドリフト層を挟んで前記ベース層と反対側であって、前記 F W D 領域に形成され、前記コレクタ層と隣接する第 1 導電型のカソード層 (21) と、

前記ベース層と、前記コレクタ層および前記カソード層との間に形成されたフィールドストップ層 (22) と、を有する前記半導体基板と、

前記エミッタ領域と前記ドリフト層との間に位置する前記ベース層の表面に配置されたゲート絶縁膜 (14) と、

前記ゲート絶縁膜上に配置されたゲート電極 (15) と、

前記ベース層および前記エミッタ領域と電気的に接続される第 1 電極 (18) と、

前記コレクタ層および前記カソード層と電気的に接続される第 2 電極 (23) と、を備え、

前記フィールドストップ層は、前記コレクタ層および前記カソード層から離れて形成されており、

前記 F W D 素子に順方向電流が流れている状態から当該電流を遮断してリカバリ状態となつた際、前記 F W D 素子内の第 1 キャリアの一部が前記コレクタ層へと流れることにより、サージピーク電圧を小さくする量の第 2 キャリアが前記第 2 電極から前記コレクタ層を介して前記ドリフト層に注入される半導体装置。

## 【請求項 2】

前記フィールドストップ層は、前記半導体基板の厚さ (L1) に対する前記フィールドストップ層と前記コレクタ層および前記カソード層との間隔 (L2) の比率が 21.5% 未満となる位置に形成されている請求項 1 に記載の半導体装置。

## 【請求項 3】

前記フィールドストップ層は、前記半導体基板の厚さ (L1) に対する前記フィールドストップ層と前記コレクタ層および前記カソード層との間隔 (L2) の比率が 2~21% となる位置に形成されている請求項 1 に記載の半導体装置。

## 【請求項 4】

前記カソード層には、前記コレクタ層と離れた位置に、前記第 2 電極と電気的に接続される第 2 導電型のキャリア注入層 (24) が形成されている請求項 1 に記載の半導体装置。

## 【請求項 5】

前記キャリア注入層は、複数形成されている請求項 4 に記載の半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、絶縁ゲート構造を有する絶縁ゲートバイポーラトランジスタ（以下では、 I G B T という）素子とフリーホイールダイオード（以下では、 F W D という）素子とが共通の半導体基板に形成された半導体装置に関するものである。

## 【背景技術】

## 【0002】

従来より、例えば、インバータ等に使用されるスイッチング素子として、 I G B T 素子

10

20

30

40

50

を有する IGBT 領域と、 FWD 素子を有する FWD 領域とが共通の半導体基板に形成された半導体装置が提案されている（例えば、特許文献 1 参照）。

#### 【0003】

具体的には、この半導体装置では、N<sup>-</sup>型のドリフト層を構成する半導体基板の表層部にベース層が形成され、ベース層を貫通するように複数のトレンチが形成されている。そして、各トレンチには、ゲート絶縁膜およびゲート電極が順に形成されている。また、ベース層の表層部には、トレンチに接するようにN<sup>+</sup>型のエミッタ領域が形成されている。半導体基板の他面側には、P<sup>+</sup>型のコレクタ層およびN<sup>+</sup>型のカソード層が形成されている。そして、コレクタ層およびカソード層上には、ドリフト層よりも高不純物濃度とされたN型のフィールドストップ層（以下では、FS層という）が形成されている。詳しくは、FS層は、コレクタ層およびカソード層と接するように形成されている。

10

#### 【0004】

半導体基板の一面側にはベース層およびエミッタ領域と電気的に接続される上部電極が形成されている。半導体基板の他面側にはコレクタ層およびカソード層と電気的に接続される下部電極が形成されている。

#### 【0005】

このような半導体装置では、半導体基板の他面側にコレクタ層が形成されている領域がIGBT素子を有するIGBT領域とされ、カソード層が形成されている領域がFWD素子を有するFWD領域とされている。なお、FWD領域では、上記構成とされることにより、N型のカソード層、FS層、およびドリフト層と、P型のベース層とによってPN接合を有するFWD素子が構成される。

20

#### 【0006】

上記半導体装置では、IGBT素子は、上部電極に下部電極より低い電圧が印加されると共にゲート電極に所定電圧が印加されると、ベース層のうちのトレンチと接する部分にN型の反転層（すなわち、チャネル）が形成される。そして、IGBT素子は、エミッタ領域から反転層を介して電子がドリフト層に供給されると共にコレクタ層から正孔がドリフト層に供給され、伝導度変調によりドリフト層の抵抗値が低下してオン状態となる。

30

#### 【0007】

また、FWD素子は、上部電極に下部電極より高い電圧が印加されると、ベース層から正孔がドリフト層に供給されると共にカソード層から電子がドリフト層に供給されてオン状態となる。その後、FWD素子は、下部電極に上部電極より高い電圧が印加されると、FWD素子内に蓄積された正孔が上部電極に引き寄せられると共に電子が下部電極に引き寄せられることでリカバリ電流が発生するリカバリ状態となり、リカバリ状態が経過した後にオフ状態となる。

40

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

#### 【特許文献 1】特許第5157201号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

しかしながら、このような半導体装置では、リカバリ状態において、ドリフト層とベース層との間に構成される空乏層が下部電極側（すなわち、半導体基板の他面側）に伸びることでリカバリ状態でのサージピーク電圧（以下では、単にサージピーク電圧ともいう）が大きくなり易い。そして、サージピーク電圧が大きくなることにより、半導体装置が破壊されてしまうことが懸念される。

40

#### 【0010】

本発明は上記点に鑑み、リカバリ状態でのサージピーク電圧を小さくできる半導体装置を提供することを目的とする。

50

#### 【課題を解決するための手段】

## 【0011】

上記目的を達成するための請求項1では、IGBT素子(1a)を有するIGBT領域(1)と、FWD素子(2a)を有するFWD領域(2)とが共通の半導体基板(10)に形成されている半導体装置において、第1導電型のドリフト層(11)と、ドリフト層上に形成された第2導電型のベース層(12)と、ベース層の表層部であって、ベース層を挟んでドリフト層から離れた位置に形成され、ドリフト層よりも高不純物濃度とされた第1導電型のエミッタ領域(16)と、ドリフト層を挟んでベース層と反対側であって、IGBT領域に形成された第2導電型のコレクタ層(20)と、ドリフト層を挟んでベース層と反対側であって、FWD領域に形成され、コレクタ層と隣接する第1導電型のカソード層(21)と、ベース層と、コレクタ層およびカソード層との間に形成されたFS層(22)と、を有する半導体基板と、エミッタ領域とドリフト層との間に位置するベース層の表面に配置されたゲート絶縁膜(14)と、ゲート絶縁膜上に配置されたゲート電極(15)と、ベース層およびエミッタ領域と電気的に接続される第1電極(18)と、コレクタ層およびカソード層と電気的に接続される第2電極(23)と、を備え、FS層は、コレクタ層およびカソード層から離れて形成されており、FWD素子に順方向電流が流れている状態から当該電流を遮断してリカバリ状態となった際、FWD素子内の第1キャリアの一部がコレクタ層へと流れることにより、サージピーク電圧を小さくする量の第2キャリアが第2電極からコレクタ層を介してドリフト層に注入されるようにしている。

10

## 【0012】

これによれば、リカバリ状態において、サージピーク電圧を小さくできる第2キャリアが注入されるようにしている。このため、半導体装置が破壊されることを抑制できる。

20

## 【0013】

なお、上記および特許請求の範囲における括弧内の符号は、特許請求の範囲に記載された用語と後述の実施形態に記載される当該用語を例示する具体物等との対応関係を示すものである。

30

## 【図面の簡単な説明】

## 【0014】

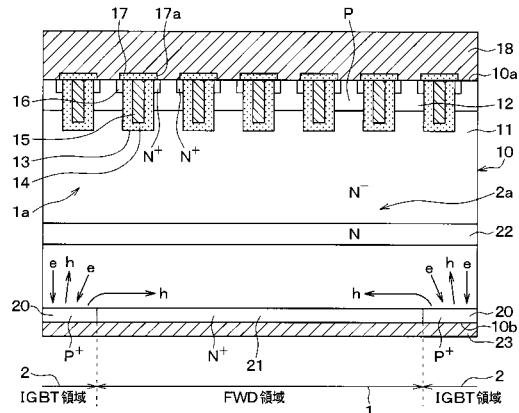

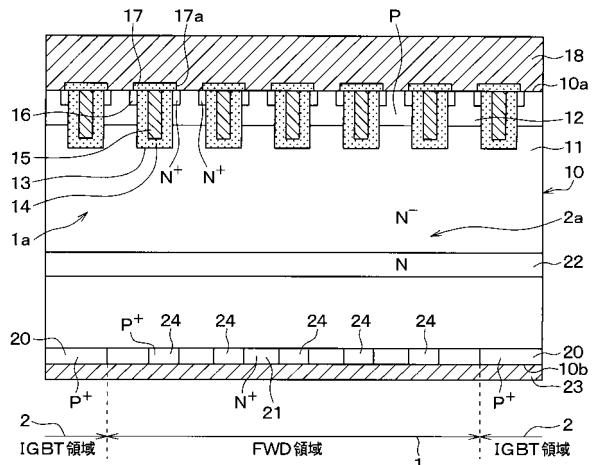

【図1】第1実施形態における半導体装置の平面模式図である。

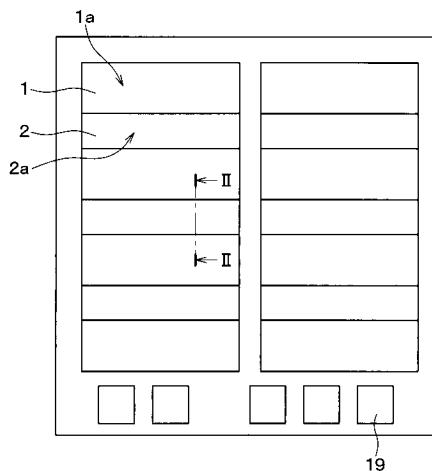

【図2】図1中のII-II線に沿った断面図である。

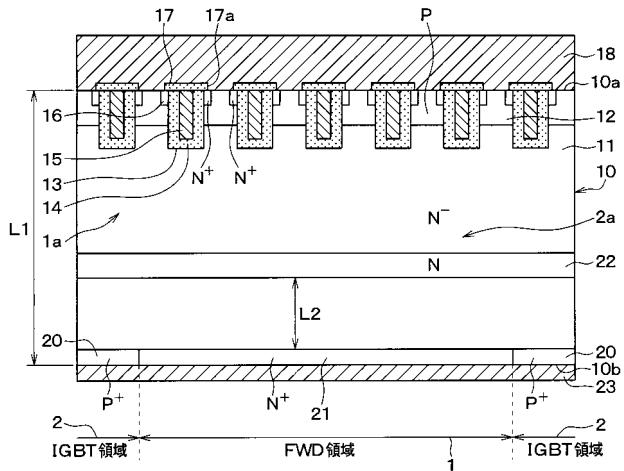

【図3】リカバリ状態におけるコレクタ層へと流れる電子と、コレクタ層から注入される正孔との状態を示す模式図である。

40

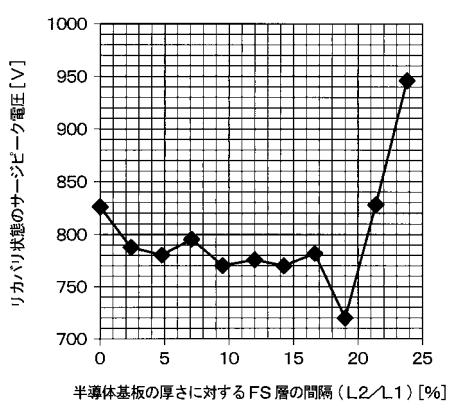

【図4】サージピーク電圧と、半導体基板の厚さに対するFS層の間隔との関係を示すシミュレーション結果である。

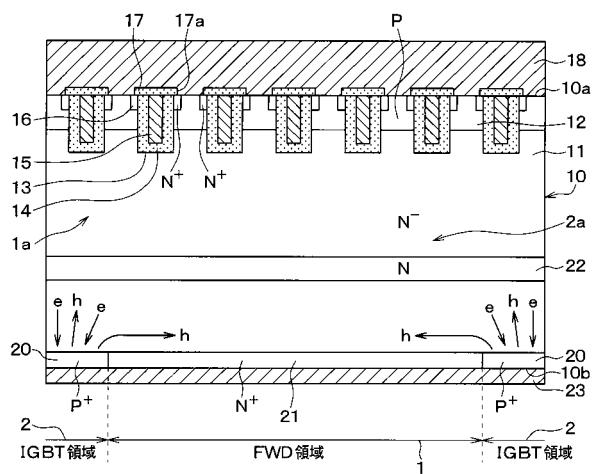

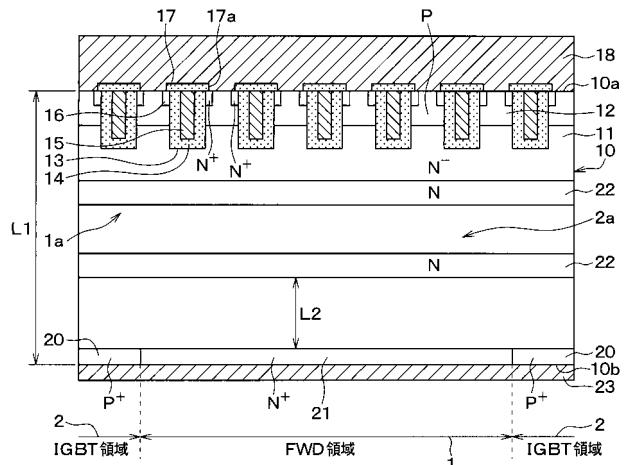

【図5】第2実施形態における半導体装置の断面図である。

【図6】他の実施形態における半導体装置の断面図である。

## 【発明を実施するための形態】

## 【0015】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。

## 【0016】

(第1実施形態)

40

第1実施形態について図面を参照しつつ説明する。なお、本実施形態の半導体装置は、例えば、インバータ、DC/DCコンバータ等の電源回路に使用されるパワースイッチング素子として利用されると好適である。

## 【0017】

図1に示されるように、半導体装置は、IGBT素子1aを有するIGBT領域1と、FWD素子2aを有するFWD領域2とが共通の半導体基板10に形成されたRC(すなわち、Reverse Conducting) - IGBTとされている。特に限定されるものではないが、本実施形態では、IGBT領域1およびFWD領域2は、一方向に沿って延設されていると共に、延設方向と交差する方向に交互に形成されている。なお、図1中では、IGBT

50

領域1およびFWD領域2は、紙面左右方向に沿って延設され、紙面上下方向に交互に形成されている。

【0018】

図2に示されるように、半導体基板10は、N<sup>+</sup>型のドリフト層11を有している。なお、半導体基板10は、例えば、シリコン基板で構成される。そして、ドリフト層11上(すなわち、半導体基板10の一面10a側)には、P型のベース層12が形成されている。

【0019】

また、半導体基板10には、ベース層12を貫通してドリフト層11に達するように複数のトレンチ13が形成されている。これにより、ベース層12は、トレンチ13によって複数個に分離されている。本実施形態では、複数のトレンチ13は、IGBT領域1およびFWD領域2にそれぞれ形成され、半導体基板10の一面10aの面方向のうちの一方に沿って等間隔に形成されたストライプ状とされている。なお、図2中では、各トレンチ13は、紙面垂直方向に沿って形成されている。

10

【0020】

各トレンチ13は、各トレンチ13の壁面を覆うように形成されたゲート絶縁膜14と、このゲート絶縁膜14の上に形成されたポリシリコン等により構成されるゲート電極15とにより埋め込まれている。これにより、トレンチゲート構造が構成されている。

【0021】

ベース層12の表層部(すなわち、半導体基板10の一面10a側)には、ドリフト層11よりも高不純物濃度とされたN<sup>+</sup>型のエミッタ領域16が形成されている。具体的には、エミッタ領域16は、ベース層12内において終端し、かつ、トレンチ13の側面に接するように形成されている。より詳しくは、エミッタ領域16は、トレンチ13間の領域において、トレンチ13の長手方向に沿ってトレンチ13の側面に接するように棒状に延設され、トレンチ13の先端よりも内側で終端する構造とされている。なお、本実施形態では、トレンチ13の壁面のうちのエミッタ領域16とドリフト層11との間に位置する部分が、エミッタ領域とドリフト層との間に位置するベース層の表面に相当する。

20

【0022】

半導体基板10の一面10a上には、BPSG(すなわち、Boron Phosphorus Silicon Glass)等で構成される層間絶縁膜17が形成されている。そして、層間絶縁膜17上には、層間絶縁膜17に形成されたコンタクトホール17aを介してエミッタ領域16およびベース層12と電気的に接続される上部電極18が形成されている。つまり、層間絶縁膜17上には、IGBT領域1においてエミッタ電極として機能し、FWD領域2においてアノード電極として機能する上部電極18が形成されている。

30

【0023】

なお、本実施形態では、上部電極18が第1電極に相当している。また、図1に示されるように、半導体基板10の一面10a上には、ゲート電極15や図示しない温度センサ等と接続される複数のパッド部19が形成されている。

【0024】

そして、図2に示されるように、IGBT領域1では、ドリフト層11のうちのベース層12側と反対側(すなわち、半導体基板10の他面10b側)にP<sup>+</sup>型のコレクタ層20が形成されている。また、FWD領域2では、ドリフト層11のうちのベース層12側と反対側(すなわち、半導体基板10の他面10b側)にN<sup>+</sup>型のカソード層21が形成されている。つまり、IGBT領域1とFWD領域2とは、半導体基板10の他面10b側に形成される層がコレクタ層20であるかカソード層21であるかによって区画されている。そして、本実施形態では、コレクタ層20上の部分がIGBT領域1とされ、カソード層21上の部分がFWD領域2とされている。なお、コレクタ層20およびカソード層21は、半導体基板10の他面10bから一面10aに向かって同じ深さまで形成されている。

40

【0025】

50

また、ドリフト層 11 には、ベース層 12 側と反対側（すなわち、半導体基板 10 の他面 10b 側）に、ドリフト層 11 よりも高不純物濃度とされた N 型の FS 層 22 が形成されている。具体的には、FS 層 22 は、コレクタ層 20 およびカソード層 21 と離れた位置に形成されている。言い換えると、FS 層 22 は、ドリフト層 11 内に形成されている。つまり、FS 層 22 は、コレクタ層 20 およびカソード層 21 との間にドリフト層 11 の一部が残存するように形成されている。なお、FS 層 22 は、具体的には後述するが、半導体基板 10 の厚さ L1 に対する FS 層 22 とコレクタ層 20 およびカソード層 21 の間隔 L2 の比率が所定値となるように形成されている。

#### 【0026】

コレクタ層 20 およびカソード層 21 を挟んでドリフト層 11 と反対側（すなわち、半導体基板 10 の他面 10b）には、コレクタ層 20 およびカソード層 21 と電気的に接続される下部電極 23 が形成されている。つまり、IGBT 領域 1 においてはコレクタ電極として機能し、FWD 領域 2 においてはカソード電極として機能する下部電極 23 が形成されている。本実施形態では、下部電極 23 が第 2 電極に相当している。

#### 【0027】

そして、上記のように構成されていることにより、FWD 領域 2 においては、ベース層 12 をアノードとし、ドリフト層 11、FS 層 22、カソード層 21 をカソードとして PN 接合された FWD 素子 2a が構成されている。

#### 【0028】

以上が本実施形態における半導体装置の構成である。なお、本実施形態では、N 型、N<sup>+</sup> 型、N<sup>-</sup> 型が第 1 導電型に相当しており、P 型、P<sup>+</sup> 型が第 2 導電型に相当している。また、本実施形態では、半導体基板 10 は、上記のように、コレクタ層 20、カソード層 21、ドリフト層 11、FS 層 22、ベース層 12、エミッタ領域 16 を含んで構成されている。次に、上記半導体装置の作動について説明する。

#### 【0029】

まず、半導体装置は、下部電極 23 に上部電極 18 より高い電圧が印加されると、ベース層 12 とドリフト層 11 との間に形成される PN 接合が逆導通状態となって空乏層が形成される。この際、ゲート電極 15 に、絶縁ゲート構造の閾値電圧 Vth 未満であるローレベル（例えば、0V）の電圧が印加されているときには、上部電極 18 と下部電極 23 との間に電流は流れない。

#### 【0030】

そして、IGBT 素子 1a をオン状態にするには、下部電極 23 に上部電極 18 より高い電圧が印加された状態で、ゲート電極 15 に、絶縁ゲート構造の閾値電圧 Vth 以上であるハイレベルの電圧が印加されるようにする。これにより、ベース層 12 のうちのトレンチ 13 と接している部分には、反転層が形成される。そして、IGBT 素子 1a は、エミッタ領域 16 から反転層を介して電子がドリフト層 11 に供給されることによってコレクタ層 20 から正孔がドリフト層 11 に供給され、伝導度変調によりドリフト層 11 の抵抗値が低下することでオン状態となる。

#### 【0031】

また、IGBT 素子 1a をオフ状態にし、FWD 素子 2a をオン状態にする（すなわち、FWD 素子 2a をダイオード動作させる）際には、上部電極 18 と下部電極 23 に印加する電圧をスイッチングし、上部電極 18 に下部電極 23 より高い電圧を印加する。そして、ゲート電極 15 に絶縁ゲート構造の閾値電圧 Vth 未満であるローレベル（例えば、0V）の電圧を印加する。これにより、ベース層 12 のうちのトレンチ 13 と接する部分に反転層が形成されなくなり、上部電極 18 からベース層 12 を介して正孔が供給されると共に、下部電極 23 からカソード層 21 を介して電子が供給されることで FWD 素子 2a がダイオード動作をする。

#### 【0032】

その後、FWD 素子 2a をオン状態からオフ状態にする際には、下部電極 23 に上部電極 18 より高い電圧を印加する逆電圧印加を行う。つまり、FWD 素子 2a に順方向電流

10

20

30

40

50

が流れている状態から当該電流を遮断する際、下部電極 23 に上部電極 18 より高い電圧を印加する逆電圧印加を行う。これにより、FWD 素子 2a がリカバリ状態となる。そして、ベース層 12 中の正孔が上部電極 18 側に引き寄せられると共にドリフト層 11 中の電子が下部電極 23 側に引き寄せられることでリカバリ電流が発生し、ベース層 12 とドリフト層 11 との間の空乏層が伸びる。

【0033】

ここで、リカバリ状態では、図 3 に示されるように、ドリフト層 11 中の電子の一部がコレクタ層 20 を介して下部電極 23 にも流れ込む。そして、コレクタ層 20 に電子が流れ込むことにより、下部電極 23 からコレクタ層 20 を介して正孔がドリフト層 11 に注入される。

10

【0034】

この際、本実施形態の半導体装置では、FS 層 22 がコレクタ層 20 およびカソード層 21 から離れて形成されている。このため、本実施形態の半導体装置では、FS 層 22 がコレクタ層 20 およびカソード層 21 と接している従来の半導体装置と比較して、コレクタ層 20 上およびその近傍に位置する領域の内部抵抗が大きくなる。このため、本実施形態の半導体装置では、従来の半導体装置と比較して、電子がコレクタ層 20 に流れ込む際の電圧降下が大きくなる。つまり、本実施形態の半導体装置では、従来の半導体装置と比較して、コレクタ層 20 上およびその近傍の領域の電位が低くなり易い。

【0035】

したがって、本実施形態の半導体装置では、リカバリ状態において、電子がコレクタ層 20 へと流れ込み易くなり、これに伴ってコレクタ層 20 を介してドリフト層 11 に注入される正孔の量が増加する。そして、コレクタ層 20 から注入される正孔は、半導体基板 10 の面方向に沿っても広がるため、カソード層 21 上の領域にも正孔が供給される。このため、本実施形態の半導体装置では、リカバリ状態において、FWD 領域 2 でキャリアが枯渇し難くなり、空乏層が半導体基板 10 の他面 10b 側に伸び難くなる。つまり、リカバリ状態において、FWD 領域 2 の空間電荷密度が上昇し、空乏層が半導体基板 10 の他面 10b 側に伸び難くなる。これにより、リカバリ状態において、完全空乏化を抑制でき、サージピーク電圧を小さくできる。

20

【0036】

なお、本実施形態では、電子が第 1 キャリアに相当し、正孔が第 2 キャリアに相当している。また、本実施形態の FS 層 22 は、後述するように、リカバリ状態において、サージピーク電圧が小さくなる適量の正孔が注入される位置に形成されている。

30

【0037】

そして、本発明者らは、さらに、サージピーク電圧の大きさと、半導体基板 10 の厚さ L1 に対する FS 層 22 とコレクタ層 20 およびカソード層 21 との間隔 L2 の比率について検討を行い、図 4 に示す結果を得た。

【0038】

なお、図 1 に示されるように、半導体基板 10 の厚さ L1 とは、半導体基板 10 の一面 10a と他面 10b との間の長さのことである。FS 層 22 とコレクタ層 20 およびカソード層 21 との間隔 L2 とは、FS 層 22 とコレクタ層 20 およびカソード層 21 との間の半導体基板 10 の厚さ方向に沿った長さのことである。図 4 中では、FS 層 22 とコレクタ層 20 およびカソード層 21 との間隔 L2 を、単に FS 層 22 の間隔と示してある。以下では、半導体基板 10 の厚さ L1 に対する FS 層 22 とコレクタ層 20 およびカソード層 21 との間隔 L2 の比率 [ % ] を単に L2 / L1 として説明する。

40

【0039】

図 4 に示されるように、L2 / L1 が 0 の場合を基準とすると、サージピーク電圧は、L2 / L1 を 0 から徐々に大きくすると小さくなる。なお、L2 / L1 が 0 の場合とは、FS 層 22 がコレクタ層 20 およびカソード層 21 と接している場合のことである。

【0040】

そして、サージピーク電圧は、L2 / L1 が 2 ~ 17 % となる際にほぼ等しくなる。ま

50

た、サージピーク電圧は、 $L_2 / L_1$  が 17 % よりさらに大きくなるようにすると急峻に小さくなり、 $L_2 / L_1$  が約 19 % となる場合に最も小さくなる。 $L_2 / L_1$  が 17 % から 19 % の間にサージピーク電圧が急峻に小さくなるのは、ドリフト層 11 に注入される正孔が増加することにより、サージピーク電圧に到達した時点から定電圧になる時点までの間のサステイン電圧が大きくなることに起因するものである。

#### 【0041】

しかしながら、サージピーク電圧は、 $L_2 / L_1$  が 19 % より大きくなるようにすると徐々に上昇し、 $L_2 / L_1$  が 21.5 % となる場合、 $L_1 / L_2$  が 0 である場合と同様の大きさとなる。そして、サージピーク電圧は、 $L_2 / L_1$  が 21.5 % より大きくなるようにすると、さらに上昇する。サージピーク電圧が  $L_2 / L_1$  を 21.5 % より大きくなした場合にさらに大きくなるのは、 $L_2 / L_1$  が大きくなり過ぎることによって正孔が過度に注入され、サステイン電圧がさらに大きくなることでサージピーク電圧が大きくなってしまうためである。つまり、FS 層 22 とコレクタ層 20 およびカソード層 21 との間隔  $L_2$  が広くなり過ぎると、サージピーク電圧が逆に大きくなってしまう。

#### 【0042】

したがって、本実施形態では、FS 層 22 は、サージピーク電圧が小さくなる適量の正孔が注入されるように、 $L_2 / L_1$  が 21.5 % 未満となる位置に形成されている。より詳しくは、FS 層 22 は、サージピーク電圧が安定して小さくなるように、 $L_2 / L_1$  が 2 ~ 19 % となるように形成されることが好ましい。

#### 【0043】

なお、図 4 は、半導体基板 10 の厚さを 80  $\mu\text{m}$ 、ドリフト層 11 の不純物濃度を  $1.0 \times 10^{14} \text{ cm}^{-3}$ 、FS 層 22 の不純物濃度を  $1.0 \times 10^{16} \text{ cm}^{-3}$ 、ベース層 12 の不純物濃度を  $2.5 \times 10^{17} \text{ cm}^{-3}$ 、カソード層 21 の不純物濃度を  $5.0 \times 10^{19} \text{ cm}^{-3}$  としたときのシミュレーション結果である。但し、不純物濃度等を変更したとしても、サージピーク電圧の大きさは変化するが、サージピーク電圧の波形と、 $L_2 / L_1$  との関係は変化しない。つまり、 $L_2 / L_1$  が 21.5 % 未満となるように FS 層 22 を形成することにより、不純物濃度等に関わらずサージピーク電圧を小さくできる。

#### 【0044】

以上説明したように、本実施形態では、FS 層 22 をコレクタ層 20 およびカソード層 21 と離れた位置に形成している。そして、リカバリ状態において、サージピーク電圧を小さくできるように、コレクタ層 20 から適量の正孔がドリフト層 11 に注入されるようにしている。つまり、 $L_1 / L_2$  が 21.5 % 未満となるようにしている。このため、サージピーク電圧を小さくでき、半導体装置が破壊されることを抑制できる。

#### 【0045】

##### (第 2 実施形態)

第 2 実施形態について説明する。第 2 実施形態は、第 1 実施形態に対して、カソード層 21 内にキャリア注入層を形成したものであり、その他に関しては第 1 実施形態と同様であるため、ここでは説明を省略する。

#### 【0046】

本実施形態では、図 5 に示されるように、カソード層 21 内に  $\text{P}^+$  型のキャリア注入層 24 が複数形成されている。本実施形態では、複数のキャリア注入層 24 は、カソード層 21 の延設方向に沿ってストライプ状となるように形成されている。

#### 【0047】

これによれば、リカバリ状態では、ドリフト層 11 内の正孔は、コレクタ層 20 と共にカソード層 21 内に位置するキャリア注入層 24 にも流れ込む。そして、ドリフト層 11 には、キャリア注入層 24 を介しても正孔が注入される。このため、リカバリ状態において、FWD 領域 2 でさらにキャリアが枯渇し難くなり、サージピーク電圧を小さくできる。

#### 【0048】

10

20

30

40

50

なお、上記のように、リカバリ状態では、正孔が過度に注入されるとサージピーク電圧が逆に大きくなってしまう。このため、F S層22は、サージピーク電圧が小さくなる適量の正孔が注入されるように、コレクタ層20およびカソード層21との間隔L2が調整された位置に形成されている。

【0049】

(他の実施形態)

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

【0050】

例えば、上記第1実施形態では、第1導電型をN型とし、第2導電型をP型とした例について説明したが、第1導電型をP型とし、第2導電型をN型とすることもできる。

【0051】

また、上記各実施形態において、ベース層12の表層部（すなわち、半導体基板10の一面10a側）に、ベース層12よりも高不純物濃度とされたP<sup>+</sup>型のコンタクト領域を形成するようにしてもよい。

【0052】

そして、上記各実施形態において、F S層22は、半導体基板10の厚さ方向に複数形成されていてもよい。例えば、第1実施形態において、図6に示されるように、F S層22は、半導体基板10の厚さ方向に沿って2つ形成されていてもよい。この場合は、サージピーク電圧が小さくなる適量の正孔が注入されるように、最も半導体基板10の他面10b側に位置するF S層22とコレクタ層20およびカソード層21との間隔L2が上記第1実施形態と同様となるように調整されればよい。

【0053】

さらに、上記各実施形態において、トレンチゲート型の半導体装置ではなく、半導体基板10の一面10a上にゲート電極15が配置されるブレーナ型の半導体装置としてもよい。この場合は、半導体基板10の一面10a上にゲート絶縁膜14を介してゲート電極15が配置されるため、ベース層12のうちの半導体基板10の一面10aを構成する部分がベース層の表面に相当する。

【0054】

また、上記第2実施形態において、複数のキャリア注入層24は、ストライプ状ではなく、例えば、格子状に形成されていてもよい。また、キャリア注入層24は複数ではなく、1つのみ形成されていてもよい。

【符号の説明】

【0055】

1 IGBT領域

1a IGBT素子

2 FWD領域

2a FWD素子

10 半導体基板

11 ドリフト層

12 ベース層

14 ゲート絶縁膜

15 ゲート電極

16 エミッタ領域

18 上部電極（第1電極）

20 コレクタ層

21 カソード層

22 F S層

23 下部電極（第2電極）

10

20

30

40

【 図 1 】

【 図 2 】

【 3 】

【 四 4 】

【図5】

【図6】

---

フロントページの続き

(51) Int.Cl.

F I

H 01 L 27/06

102A

テーマコード(参考)