(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-514419

(P2016-514419A)

(43) 公表日 平成28年5月19日(2016.5.19)

| (51) Int.Cl.                 | F 1         | テーマコード (参考) |

|------------------------------|-------------|-------------|

| <b>H03K 3/037</b> (2006.01)  | H03K 3/037  | Z 5 F 038   |

| <b>H01L 21/822</b> (2006.01) | H01L 27/04  | F 5 J 034   |

| <b>H01L 27/04</b> (2006.01)  | H01L 27/04  | A 5 J 043   |

| <b>H03K 3/356</b> (2006.01)  | H03K 3/356  | Z           |

| <b>H03K 3/3562</b> (2006.01) | H03K 3/3562 | 6 2 5       |

審査請求 未請求 予備審査請求 未請求 (全 27 頁) 最終頁に続く

|               |                              |          |                                                                                                                |

|---------------|------------------------------|----------|----------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2015-561411 (P2015-561411) | (71) 出願人 | 595020643<br>クアアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (86) (22) 出願日 | 平成26年2月26日 (2014. 2. 26)     | (74) 代理人 | 100108855<br>弁理士 蔵田 昌俊                                                                                         |

| (85) 翻訳文提出日   | 平成27年10月22日 (2015.10.22)     | (74) 代理人 | 100109830<br>弁理士 福原 淑弘                                                                                         |

| (86) 國際出願番号   | PCT/US2014/018811            | (74) 代理人 | 100158805<br>弁理士 井関 守三                                                                                         |

| (87) 國際公開番号   | W02014/137714                | (74) 代理人 | 100194814<br>弁理士 奥村 元宏                                                                                         |

| (87) 國際公開日    | 平成26年9月12日 (2014. 9. 12)     |          |                                                                                                                |

| (31) 優先権主張番号  | 13/787,666                   |          |                                                                                                                |

| (32) 優先日      | 平成25年3月6日 (2013.3.6)         |          |                                                                                                                |

| (33) 優先権主張国   | 米国 (US)                      |          |                                                                                                                |

最終頁に続く

(54) 【発明の名称】低リークリテンションレジスタトレイ

## (57) 【要約】

特定の方法は、リテンション信号 (n\_r\_e\_t) を受け取ることを含む。リテンション信号を受け取ることに応えて、この方法は、リテンションレジスタ (300) の不揮発性ステージ (302) において状態情報 (q\_i\_n\_t\_e\_r\_n\_a\_l, 310) を保持することと、リテンションレジスタの揮発性ステージ (356) への電力を低減することとを含む。不揮発性ステージ (302) は、外部電圧源 (V\_d\_d\_e\_x\_t) によって電力供給され得る。揮発性ステージは、内部電圧源 (V\_d\_d\_x) によって電力供給され得る。

FIG. 3

**【特許請求の範囲】****【請求項 1】**

回路であって、

第1のクロック入力を有するトランジスタを含むリテンションステージ、ここでにおいて、前記リテンションステージは外部電圧源によって電力供給される、と、

前記リテンションステージの出力に応答するインバータ、ここでにおいて、前記インバータは内部電圧源によって電力供給される、と、

を備える、回路。

**【請求項 2】**

前記インバータの出力は、第1のリテンションレジスタに与えられる、請求項1に記載の回路。 10

**【請求項 3】**

前記第1のリテンションレジスタは、第1の揮発性領域および第1の不揮発性領域を含み、ここでにおいて、前記第1の不揮発性領域は入力信号としてリテンション信号を受け取る、請求項2に記載の回路。

**【請求項 4】**

前記第1のリテンションレジスタは、第2のリテンションレジスタを含むリテンションレジスタトレイに含まれ、ここでにおいて、前記第2のリテンションレジスタは、第2の揮発性領域および第2の不揮発性領域を含み、ここでにおいて、前記第1のリテンションレジスタは、前記第2のリテンションレジスタに結合される、請求項3に記載の回路。 20

**【請求項 5】**

前記第1の不揮発性領域および前記第2の不揮発性領域は、前記外部電圧源に接続された第1のn型ウェル(n-well)に位置し、ここでにおいて、前記第1の揮発性領域および前記第2の揮発性領域は、前記内部電圧源に接続された第2のn-wellに位置する、請求項4に記載の回路。

**【請求項 6】**

前記第1のリテンションレジスタは、第2のリテンションレジスタを含むリテンションレジスタトレイに含まれ、ここでにおいて、前記インバータの前記出力は、前記第2のリテンションレジスタに提供され、ここでにおいて、前記第1のリテンションレジスタは、前記第2のリテンションレジスタに結合される、請求項2に記載の回路。 30

**【請求項 7】**

前記リテンションステージは、入力としてリテンション信号および反転されたリテンション信号を受け取る、請求項1に記載の回路。

**【請求項 8】**

前記反転されたリテンション信号は、第1のリテンションレジスタがスタンバイモードに入ることを、または前記スタンバイモードを抜け出することをトリガするように構成される、請求項7に記載の回路。

**【請求項 9】**

前記インバータは、p-チャネル金属酸化膜半導体(PMOS)トランジスタおよびn-チャネル金属酸化膜半導体(NMOS)トランジスタを含む、請求項1に記載の回路。 40

**【請求項 10】**

第1のクロック信号を第1のリテンションレジスタの第2のクロック入力へ供給し、および前記第1のクロック信号を第2のリテンションレジスタの第3のクロック入力へ供給するように構成されるクロックゲーティング回路をさらに備え、ここでにおいて、前記第1のリテンションレジスタおよび前記第2のリテンションレジスタは、リテンションレジスタトレイを形成し、ここでにおいて、前記クロックゲーティング回路は前記リテンションレジスタトレイの外部にあり、およびここでにおいて、前記クロックゲーティング回路は、前記外部電圧源によって電力供給される第1のステージと、前記内部電圧源によって電力供給される第2のステージとを含む、請求項1記載の回路。

**【請求項 11】**

10

20

30

40

50

前記第1のステージは、前記リテンションステージを含み、ここにおいて、前記第2のステージは、前記インバータを含む、請求項10に記載の回路。

【請求項12】

装置であって、

クロック入力を有するゲートを含むデータをスイッチングするための手段、ここにおいて、前記データをスイッチングするための手段は外部電圧源によって電力供給される、と、

前記データをスイッチングするための手段の出力を反転するための手段、ここにおいて、前記反転するための手段は内部電圧源によって電力供給される、と、

を備える、装置。

10

【請求項13】

第1のビットを保持するための手段および第2のビットを保持するための手段にクロック信号を供給するための手段をさらに備え、ここにおいて、前記第1のビットを保持するための手段および前記第2のビットを保持するための手段は、データを保持するための手段を形成し、ここにおいて、前記クロック信号を供給するための手段は、前記データを保持するための手段の外部にあり、およびここにおいて、前記クロック信号を供給するための手段は、前記外部電圧源によって電力供給される第1のステージと、前記内部電圧源によって電力供給される第2のステージと、を含む、請求項12に記載の装置。

【請求項14】

前記第1のステージは、前記データをスイッチングするための手段を含み、前記第2のステージは、前記反転するための手段を含む、請求項13に記載の装置。

20

【請求項15】

方法であって、

クロック入力を有するトランジスタを含むリテンションステージにおいてクロック信号を受け取ること、ここにおいて、前記リテンションステージは、外部電圧源によって電力供給される、と、

前記リテンションステージからインバータへ出力を提供すること、ここにおいて、前記インバータは、内部電圧源によって電力供給される、と、

を備える、方法。

30

【請求項16】

前記インバータから第1のリテンションレジスタへ出力を与えることをさらに備える、請求項15に記載の方法。

【請求項17】

前記インバータから第2のリテンションレジスタへ前記出力を与えること、ここにおいて、前記第1のリテンションレジスタおよび前記第2のリテンションレジスタは、リテンションレジストレイを形成し、およびここにおいて、前記第1のリテンションレジスタは、前記第2のリテンションレジスタに結合される、

をさらに備える、請求項16に記載の方法。

【請求項18】

前記リテンションステージにおいて、リテンション信号および反転されたリテンション信号を受け取ることをさらに備える、請求項15に記載の方法。

40

【請求項19】

前記反転されたリテンション信号に基づいて、第1のリテンションレジスタがスタンバイモードに入ること、または前記スタンバイモードから抜け出ることをトリガすること、をさらに備える、請求項18に記載の方法。

【請求項20】

命令を備えるコンピュータ読み取り可能な記憶デバイスであって、前記命令は、プロセッサによって実行されると、前記プロセッサに、

リテンション信号をリテンションステージへ与えることを開始させ、

ここでにおいて、前記リテンションステージは、外部電圧源によって電力供給され、

50

ここにおいて、前記リテンションステージは、クロック信号を受け取るように構成され、

ここにおいて、前記リテンションステージは、インバータへ出力を提供するように構成され、

ここにおいて、前記インバータは、内部電圧源によって電力供給される、

コンピュータ読み取り可能な記憶デバイス。

**【請求項 2 1】**

回路であつて、

第1の不揮発性領域および第1の揮発性領域を含む第1のリテンションレジスタと、

10

第2の不揮発性領域および第2の揮発性領域を含む第2のリテンションレジスタ、ここにおいて、前記第1のリテンションレジスタは前記第2のリテンションレジスタに結合され、ここにおいて、前記第1の不揮発性領域および前記第2の不揮発性領域は、外部電圧源に接続された第1のn型ウェル(n-well)に位置し、およびここにおいて、前記第1の揮発性領域および前記第2の揮発性領域は、内部電圧源に接続された第2のn-wellに位置する、と、

を備える、回路。

**【請求項 2 2】**

前記第1のリテンションレジスタおよび前記第2のリテンションレジスタは、リテンションレジストレイを形成する、請求項2 1に記載の回路。

**【請求項 2 3】**

クロックゲーティング回路が、クロック信号を前記第1のリテンションレジスタへ供給し、および前記クロック信号を前記第2のリテンションレジスタへ供給するように構成され、ここにおいて、前記クロックゲーティング回路は、前記第1のn-wellに位置する、請求項2 2に記載の回路。

20

**【請求項 2 4】**

方法であつて、

リテンション信号を受け取ることに応えて、

リテンションレジスタの不揮発性ステージにおいて状態情報を保持することと、

前記リテンションレジスタの揮発性ステージへの電力を低減することと、

30

を備え、

ここにおいて、前記不揮発性ステージは外部電圧源によって電力供給され、前記揮発性ステージは内部電圧源によって電力供給される、

方法。

**【請求項 2 5】**

前記状態情報は、少なくとも内部データ状態を含む、請求項2 4に記載の方法。

**【請求項 2 6】**

前記揮発性ステージ内に位置するコンポーネントは、前記揮発性ステージへの電力が低減される時、フローティング状態に入る、請求項2 4に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

40

**【0 0 0 1】**

[0001] 本開示は一般に、リーク電流の低減に関する。

**【関連出願の説明】**

**【0 0 0 2】**

[0002] 蓄えられた電源(stored power source)(例えば、バッテリ)によって電力供給される電子デバイス(例えば、モバイルフォン)は、非活動期間の間、電力消費を節約するためにスタンバイモードに置かれ得る。スタンバイモードでは、電子デバイスの回路はオフにされ得、回路に関連する論理状態は失われ得る。しかしながら、いくつかの論理状態(例えば、制御情報)は、電子デバイスがスタンバイモードを抜け出た後に電子デバイスが適切に機能するために、スタンバイモードの間保持されるべきである。そのよう

50

な論理状態は、リテンションレジスタに記憶され得る。複数のリテンションレジスタが連結されてリテンションレジストレイを形成し得る。リテンションレジストレイを駆動する特定の回路は、そのような回路のトランジスタに関連するリーク電流のために、スタンバイモードにおいて電力を消費し得る。リーク電流は、電子デバイスの全体的な電力消費の一因となり、電子デバイスの利用可能な動作時間を低減する。

#### 【発明の概要】

#### 【0003】

[0003] 特定の実施形態では、ある回路は、スタンバイモード（例えば、内部電源がパワーダウンされているモード）中に状態情報を保存するリテンションレジストレイとクロックゲーティング回路とを含む。クロックゲーティング回路とリテンションレジストレイの各々の一部は、内部電源によって電力供給され、クロックゲーティング回路とリテンションレジストレイの各々の一部は、外部電源によって電力供給される。内部電源は、リテンションレジストレイを含むデバイスのある領域の内部にあり得、外部電源は、リテンションレジストレイを含むデバイスのその領域の外部にあり得る。クロックゲーティング回路とリテンションレジストレイは、クロックゲーティング回路とリテンションレジストレイがスタンバイモードに入る時、リーク電流を低減するように構成され得る。それ故に、クロックゲーティング回路、リテンションレジストレイ、またはその両方を含む電子デバイスの利用可能な動作時間は、電子デバイスが蓄えられた電力で動く時、増加し得る。

10

#### 【0004】

[0004] 特定の実施形態では、回路は、第1のクロック入力を有するトランジスタを含むリテンションステージを含む。リテンションステージは、外部電圧源 (external voltage source) によって電力供給され得る。この回路は、リテンションステージの出力に応答するインバータをさらに含む。インバータは、内部電圧源 (internal voltage source) によって電力供給され得る。

20

#### 【0005】

[0005] 別の特定の実施形態では、装置は、データをスイッチングするための手段を含む。データをスイッチングするための手段は、クロック入力を有するゲートを含み得る。データをスイッチングするための手段は、外部電圧源によって電力供給され得る。この装置は、データをスイッチングするための手段の出力を反転するための手段をさらに含む。反転するための手段は、内部電圧源によって電力供給され得る。

30

#### 【0006】

[0006] 別の特定の実施形態では、方法は、リテンションステージにおいてクロック信号を受け取ることを含む。リテンションステージは、クロック入力を有するトランジスタを含み得る。リテンションステージは、外部電圧源によって電力供給され得る。この方法は、リテンションステージからインバータへ出力を提供することをさらに含む。インバータは、内部電圧源によって電力供給され得る。

#### 【0007】

[0007] 別の特定の実施形態では、コンピュータ読み取り可能な記憶デバイスは、プロセッサによって実行されると、プロセッサに、リテンション信号をリテンションステージへ提供することを開始させる命令を含む。リテンションステージは、外部電圧源によって電力供給され得、およびリテンションステージは、クロック信号を受け取るように構成され得る。リテンションステージは、インバータへ出力を与えるように構成され得る。インバータは、内部電圧源によって電力供給され得る。

40

#### 【0008】

[0008] 別の特定の実施形態では、回路は、第1の不揮発性領域と第1の揮発性領域とを含む第1のリテンションレジスタを含む。この回路は、第2の不揮発性領域と第2の揮発性領域とを含む第2のリテンションレジスタをさらに含む。第1のリテンションレジスタは、第2のリテンションレジスタに結合され得る。第1の不揮発性領域および第2の不揮発性領域は、第1のn型ウェル (n-type well) (n-well) に位置し得る。第1

50

の n - well は、外部電圧源に接続され得る。第 1 の揮発性領域および第 2 の揮発性領域は、第 2 の n - well に位置し得る。第 2 の n - well は、内部電圧源に接続され得る。

#### 【 0 0 0 9 】

[0009] 別の特定の実施形態では、ある方法は、リテンション信号を受け取ることを含む。リテンション信号に応えて、この方法は、リテンションレジスタの不揮発性ステージにおいて状態情報を保持すること、およびリテンションレジスタの揮発性ステージへの電力を低減することを含む。不揮発性ステージは、外部電圧源によって電力供給され得る。揮発性ステージは、内部電圧源によって電力供給され得る。

#### 【 0 0 1 0 】

[0010] 開示された実施形態のうちの少なくとも 1 つによって提供される 1 つの特定の利点は、内部電源によって電力供給されるクロックゲーティング回路の一部と外部電源によって電力供給されるクロックゲーティング回路の一部とを有さない回路と比べて、クロックゲーティング回路がスタンバイモードにある場合のクロックゲーティング回路に関連するリーク電流が低減され得ることである。それ故に、クロックゲーティング回路を組み込んだ電子デバイスの利用可能な動作時間が増加し得る。

#### 【 0 0 1 1 】

[0011] 開示された実施形態のうちの少なくとも 1 つによって提供される別の特定の利点は、内部電源によって電力供給されるリテンションレジストレイの一部と外部電源によって電力供給されるリテンションレジストレイの一部とを有さない回路と比べて、リテンションレジストレイがスタンバイモードにある場合のリテンションレジストレイに関連するリーク電流が低減され得ることである。それ故に、リテンションレジストレイを組み込んだ電子デバイスの利用可能な動作時間が増加し得る。

#### 【 0 0 1 2 】

[0012] 開示された実施形態のうちの少なくとも 1 つによって提供される別の特定の利点は、製造過程で少なくとも 2 つのリテンションレジスタの不揮発性領域を合併 (merging) することによって、リテンションレジストレイが電子デバイスの製造の複雑性を低減し得ることである。

#### 【 0 0 1 3 】

[0013] 開示された実施形態のうちの少なくとも 1 つによって提供される別の特定の利点は、製造過程で少なくとも 2 つのリテンションレジスタの揮発性領域を合併することによって、リテンションレジストレイが電子デバイスの製造の複雑性を低減し得ることである。

#### 【 0 0 1 4 】

[0014] 本開示の他の様様、利点、および特徴は、以下のセクション：図面の簡単な説明、詳細な説明、および特許請求の範囲を含む本出願の全体を見直した後に明らかになることになる。

#### 【 図面の簡単な説明 】

#### 【 0 0 1 5 】

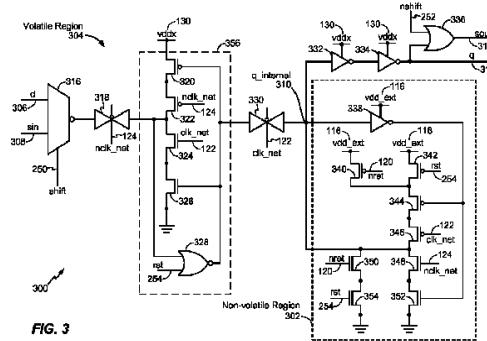

【 図 1 】 [0015] 図 1 は、クロックゲーティング回路の特定の実施形態の図である。

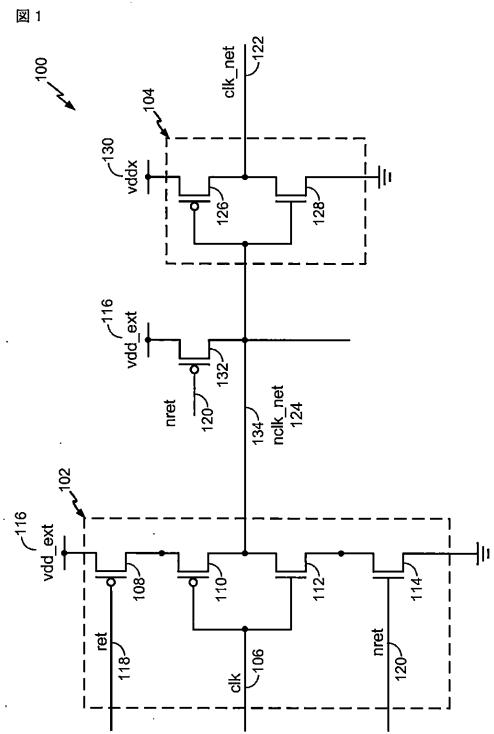

【 図 2 】 [0016] 図 2 は、リテンションレジストレイの特定の実施形態の図である。

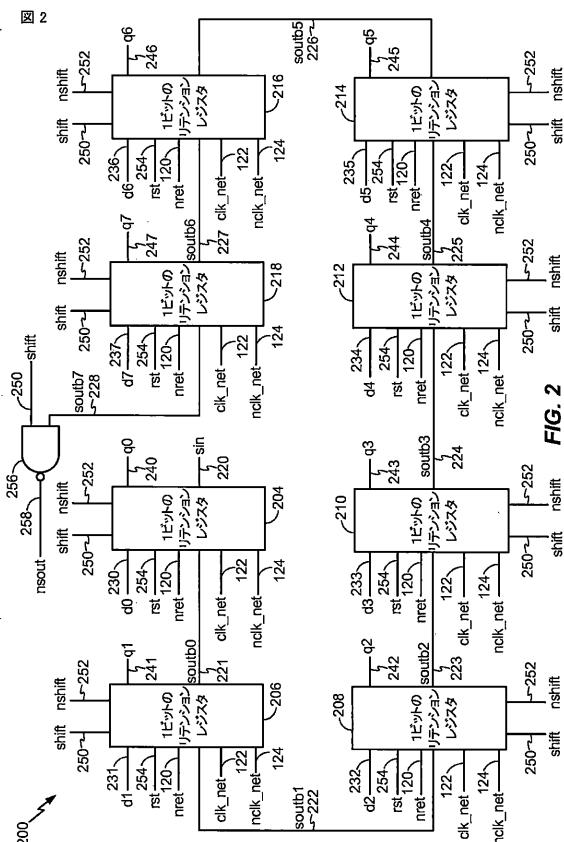

【 図 3 】 [0017] 図 3 は、1 ビットのリテンションレジスタ (one-bit retention register) の特定の実施形態の図である。

【 図 4 】 [0018] 図 4 は、図 3 のリテンションレジスタの複数の機能の特定の実施形態を例示する真理値表である。

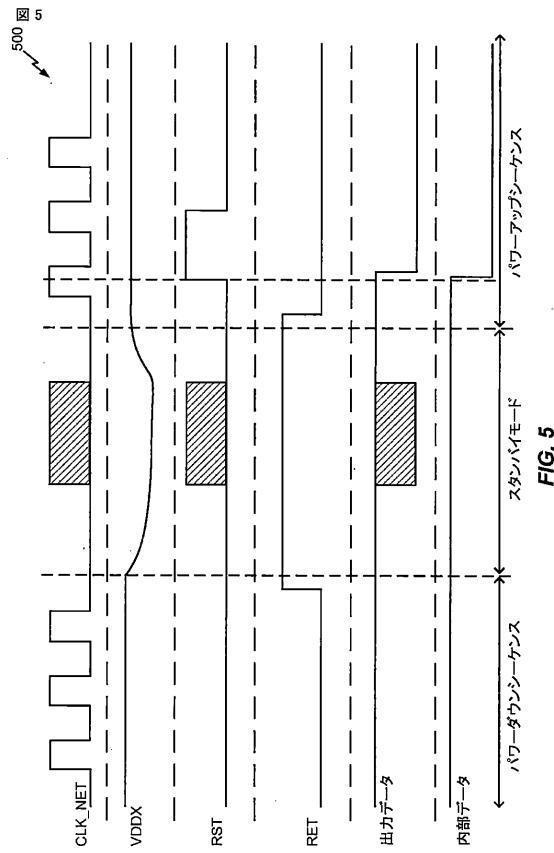

【 図 5 】 [0019] 図 5 は、図 3 のリテンションレジスタのスタンバイモードの特定の実施形態を例示するタイミング図である。

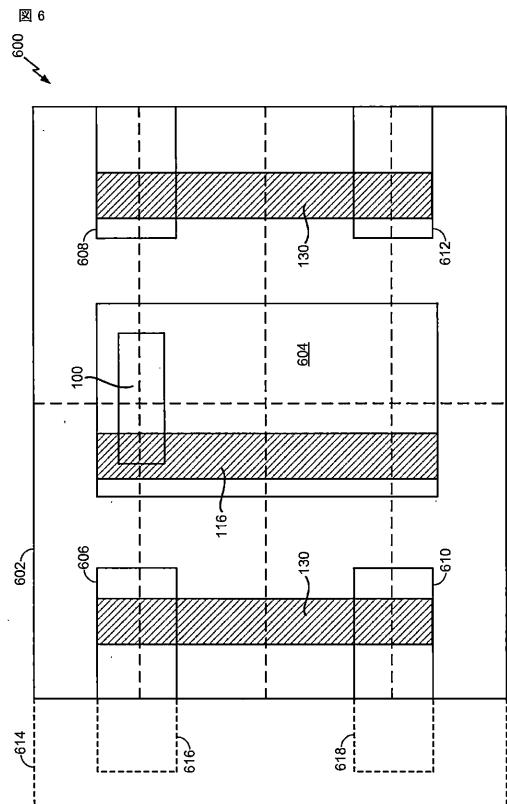

【 図 6 】 [0020] 図 6 は、リテンションレジストレイの特定の実施形態のレイアウト図である。

【 図 7 】 [0021] 図 7 は、クロックゲーティング回路を動作させる方法の特定の実施形態

10

20

30

40

50

を例示する流れ図である。

【図8】[0022] 図8は、リテンションレジスタの動作の特定の実施形態を例示する流れ図である。

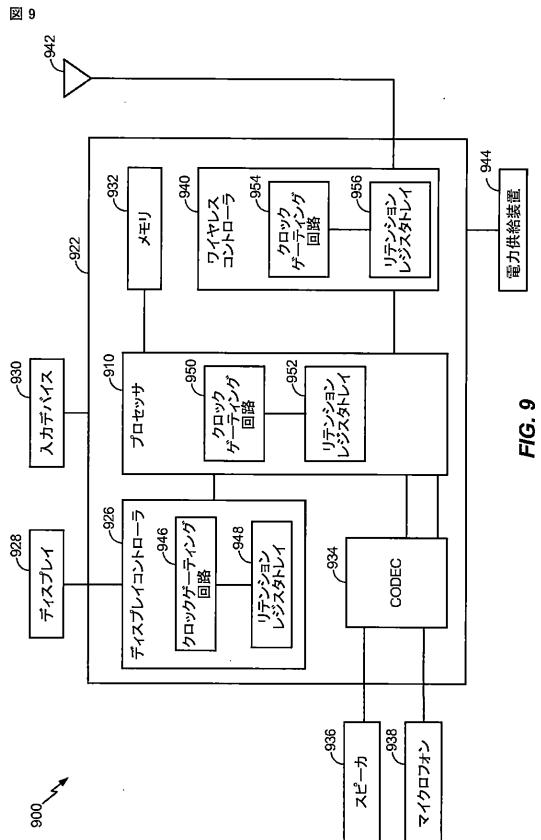

【図9】[0023] 図9は、クロックゲーティング回路およびリテンションレジスタトレイを含む通信デバイスのブロック図である。

#### 【詳細な説明】

##### 【0016】

[0024] 図1に関して、クロックゲーティング回路100の特定の例示的な実施形態が示される。クロックゲーティング回路100は、第1のステージおよび第2のステージを含む。第1のステージは、リテンションステージ102を含み得る。第1のステージは、内部電圧源( $v_{ddx}$ )130よりも高い電圧を有する外部電圧源( $v_{dd\_ext}$ )116によって電力供給され得る。外部電圧源116は、スタンバイモードの間、そのままであり得る。第2のステージは、インバータ104を含み得る。第2のステージは、内部電圧源130によって電力供給され得る。リテンションステージ102における外部電圧源116の使用は、内部電圧源130を使用してリテンションステージ102へ電力供給することに比べて、リテンションステージ102に関連するバルクのリーク電流を低減し得る。10

##### 【0017】

[0025] リテンションステージ102は、入力として、リテンション信号( $r_{et}$ )118、反転されたリテンション信号( $n_{ret}$ )120、および外部クロック信号( $c_{lk}$ )106を受け取り得る。リテンション信号118および反転されたリテンション信号120は、クロックゲーティング回路100の外部の、および図2を参照して説明されるリテンションレジスタトレイ200の外部の、1つ以上の回路によって提供され得る。例えば、リテンション信号118および反転されたリテンション信号120は、プロセッサによるスタンバイモードに入るための決定に基づいて、プロセッサから受け取られ得る。外部クロック信号106は、クロックゲーティング回路100の外部およびリテンションレジスタトレイ200の外部にある1つ以上の回路によって(例えば、水晶発振器から)提供され得る。リテンションステージ102は、データライン134を介して、反転された内部クロック信号( $n_{clk\_net}$ )124をインバータ104へ出力し得る。リテンションステージ102は、n-チャネル金属酸化膜半導体(NMOS)トランジスタスタッカクに結合されたp-チャネル金属酸化膜半導体(PMOS)トランジスタスタッカクを含み得る。PMOSトランジスタスタッカクは、直列に結合された第1のPMOSトランジスタ108および第2のPMOSトランジスタ110を含み得る。NMOSトランジスタスタッカクは、第2のPMOSトランジスタ110と直列に結合された第1のNMOSトランジスタ112および第1のNMOSトランジスタ112と直列に結合された第2のNMOSトランジスタ114を含み得る。リテンション信号118がハイ(すなわち、論理的に高い値(logical high value)に関連する状態にある)であり、および反転されたリテンション信号120がロー(すなわち、論理的に低い値(logical low value)に関連する状態にある)場合、リテンションステージ102は、スタンバイモードに入るよう構成され得、ここでデータライン134は、リテンションステージ102によって、接地から、および外部電圧源116から電気的に絶縁される。リテンション信号118がローであり、反転されたリテンション信号120がハイである場合、リテンションステージ102は、反転された内部クロック信号124として外部クロック信号106の反転を出力し得る。PMOSスタッカクおよびNMOSスタッカクは、自己逆バイアス効果(self-reverse biasing effects)によってリテンションステージ102に関連するリーク電流を低減し得る。203040

##### 【0018】

[0026] 外部電圧源116は、図2を参照してさらに説明されるように、リテンションレジスタトレイ200を含む領域の外部にある電圧源であり得る。外部電圧源116は、リテンション信号118によってイネーブルされるスタンバイモードの間、そのままであ50

り得る。第1のPMOSトランジスタ108のためのバルクの接続および第2のPMOSトランジスタ110のためのバルクの接続は、外部電圧源116に接続され得る。リテンションステージ102における外部電圧源116の使用は、外部電圧源116が内部電圧源130よりも高い電圧を有することにより、およびリテンション信号118が外部電圧源116によって電力供給されることにより、内部電圧源130を使用してリテンションステージ102に電力供給することに比べて、第1のPMOSトランジスタ108に関連するバルクのリーク電流（例えば、ゲートからバルクへのリーク電流）を低減し得る。外部電圧源116は、第1のPMOSトランジスタ108のゲート端子とボディ端子との間の電位の差を低減させ、結果として低減されたバルクリーク電流をもたらし得る。リテンションステージ102における外部電圧源116の使用は、同様の理由で、第2のPMOSトランジスタ110に関連するバルクリーク電流を低減し得る。

10

## 【0019】

[0027] インバータ104は、第3のNMOSトランジスタ128と直列に結合された第3のPMOSトランジスタ126を含み得る。インバータ104は、反転された内部クロック信号124を反転し、内部クロック信号（clk\_net）122を出力するように構成され得る。

## 【0020】

[0028] インバータ104は、内部電圧源130によって電力供給され得る。内部電圧源130は、外部電圧源116から得られ得、外部電圧源116よりも低い電圧値を有し得る。内部電圧源130は、図2を参照してさらに説明されるように、リテンションレジストレイ200を含むデバイスのある領域の内部にあり得る。内部電圧源130は、リテンション信号118がイネーブルされる場合であるスタンバイモードの間、ディスエーブルされ得る。例えば、スタンバイモードの間、内部電圧源130は、内部電圧源130を外部電圧源116から遮断すること（disconnecting）によって、オフにされ得る。インバータ104における内部電圧源130の使用は、第3のPMOSトランジスタ126に関連するサブスレッショルド・リーク電流を低減することによって、インバータ104に関連するリーク電流を低減し得る。

20

## 【0021】

[0029] 第4のPMOSトランジスタ132は、外部電圧源116に接続され得る。第4のPMOSトランジスタ132はまた、データライン134に接続され得る。第4のPMOSトランジスタ132は、スタンバイモードの間、データライン134を外部電圧源116へ結合することによって、反転された内部クロック信号124をハイに（すなわち、論理的に高い値に関連する状態に）設定するように構成されるプルアップデバイスであり得る。結果的に、内部クロック信号122はスタンバイモードの間口一に設定される。

30

## 【0022】

[0030] したがって、クロックゲーティング回路100がスタンバイモードにある間、クロックゲーティング回路100に関連するリーク電流は、低減され得る。それ故に、クロックゲーティング回路100を組み込んだ電子デバイスの利用可能な動作時間は、増加し得る。

## 【0023】

[0031] 図2に関して、リテンションレジストレイ200の特定の実施形態が示される。リテンションレジストレイ200は、代表となるリテンションレジスタ204のような、1つ以上の1ビットのリテンションレジスタを含み得る。8つのリテンションレジスタ204、206、208、210、212、214、216、および218が図2に示されるが、リテンションレジストレイ200は、8つより多くのリテンションレジスタまたは8つより少ないリテンションレジスタを含み得る。リテンションレジストレイ200は、8ビットのデータを記憶するように構成され得る。リテンションレジスタは、反転されたリテンション信号（nret）120に基づいて、スタンバイモードに入るまたはスタンバイモードを抜け出るように構成され得る。図6に関して説明されるように、リテンションレジストレイ200のリテンションレジスタ204-218は、リテンシ

40

50

ヨンレジスタ 204 - 218 の不揮発性領域が单一の n ウエル (n-well) 内に製造され得るよう構成され得る。

#### 【0024】

[0032] リテンションレジスタ 204 は、入力として、図 1 の反転されたリテンション信号 120、内部クロック信号 (clk\_net) 122 および反転された内部クロック信号 (nc1k\_net) 124 と、シフトデータ信号 (sin) 220、データ入力信号 (d0) 230、シフト信号 (shift) 250、反転されたシフト信号 (nshift) 252、ならびにリセット信号 (rst) 254 を受け取るように構成され得る。リテンションレジスタ 204 は、データアウト信号 (q0) 240 またはシフトデータアウト信号 (soutb0) 221 を出力するように構成され得る。内部クロック信号 122 および反転された内部クロック信号 124 は、図 1 のクロックゲーティング回路 100 のようなクロックゲーティング回路によって提供され得る。クロックゲーティング回路 100 は、リテンションレジストレイ 200 に組み込まれ得るか、またはリテンションレジストレイ 200 とは分離され得る。反転されたリテンション信号 120、シフトデータ信号 220、データ入力信号 230、シフト信号 250、反転されたシフト信号 252、およびリセット信号 254 は、リテンションレジストレイ 200 およびクロックゲーティング回路 100 の外部の 1 つ以上の回路によって提供され得る。

10

#### 【0025】

[0033] リテンションレジストレイ 200 の各リテンションレジスタ 204 - 218 は、入力としてデータ入力信号 230 - 237 およびシフトデータ信号 220 - 227 を受け、データアウト信号 240 - 247 およびシフトデータアウト信号 221 - 228 を出力するように構成され得る。リテンションレジスタ 204 - 218 は、シフトデータ信号 220 - 227 として、別のリテンションレジスタからシフトデータアウト信号 220 - 227 を受け取るように構成され得る。それ故に、リテンションレジスタ 204 - 218 は連結され得る。結合されたリテンションレジスタの最後のリテンションレジスタのシフトデータアウト信号（例えば、リテンションレジスタ 218 のシフトデータアウト信号 228）は、リテンショントレイ出力 (nsout) 258 を生成するために使用され得る。例えば、リテンショントレイ出力 258 は、シフト信号 250 およびリテンションレジスタ 218 のシフトデータアウト信号を NAND ゲート 256 へ入力することによって生成され得る。リテンションレジスタ 204 - 218 の入力信号と出力信号の関係は、図 3 を参照してさらに説明され得る。図 2 は、NAND ゲート 256 を示すが、他の論理ゲートまたは切替装置 (switching arrangement) がリテンショントレイ出力 258 を生成するために使用され得る。

20

30

#### 【0026】

[0034] 図 3 に関して、1ビットのリテンションレジスタ 300 の特定の例示的な実施形態が示される。リテンションレジスタ 300 は、図 2 のリテンションレジストレイ 200 のリテンションレジスタ 204 - 218 のうちの 1 つに対応し得る。リテンションレジスタ 300 は、不揮発性領域 302（例えば、スタンバイモードの間電源をオンにされるリテンションレジスタ 300 の一部分）および揮発性領域 304（例えば、スタンバイモードの間電源をオフにされるリテンションレジスタ 300 のある部分）を含み得る。不揮発性領域 302 内に位置するコンポーネントは、外部電圧源 (vdd\_ext) 116 によって電力供給され得る。揮発性領域 304 内に位置するコンポーネントは、内部電圧源 (vddx) 130 によって電力供給され得る。揮発性領域 304 内に位置するコンポーネントは、スタンバイモードの間、浮き状態 (floating state) に入るよう構成され得る。

40

#### 【0027】

[0035] リテンションレジスタ 300 は、入力として、反転されたリテンション信号 (nret) 120、内部クロック信号 (clk\_net) 122、反転された内部クロック信号 (nc1k\_net) 124、シフトデータ信号 (sin) 308、データ入力信号 (d) 306、シフト信号 (shift) 250、反転されたシフト信号 (nshift

50

t ) 252、およびリセット信号 ( r s t ) 254 を受け取るように構成され得る。リテンションレジスタ 300 は、データアウト信号 ( q ) 312 およびシフトデータアウト信号 ( s o u t ) 314 を出力するように構成され得る。内部クロック信号 122 および反転された内部クロック信号 124 は、図 1 のクロックゲーティング回路 100 のようなクロックゲーティング回路によって提供され得る。

#### 【 0028 】

[0036] リテンションレジスタ 300 は、マルチプレクサ 316 において、シフト信号 250 を使用して、データ入力信号 306 またはシフトデータ信号 308 を選択するように構成され得る。マルチプレクサ 316 は、反転された選択されたデータ信号（例えば、データ入力信号 306 の反転またはシフトデータ信号 308 の反転）を第 1 の伝送ゲート 318 へ出力するように構成され得る。データ入力信号 306 は、図 2 のデータ入力信号 230 - 237 のうちの 1 つに対応し得る。シフトデータ信号 308 は、図 2 のシフトデータ信号 220 - 227 のうちの 1 つに対応し得る。マルチプレクサ 316 は、内部電圧源 130 によって電力供給され得る。第 1 の伝送ゲート 318 は、反転された内部クロック信号 124 に応答して、反転された選択されたデータ信号を揮発性リテンションステージ (volatile retention stage) 356 へ与えるように構成され得る。

10

#### 【 0029 】

[0037] 挥発性リテンションステージ 356 は、入力として、内部クロック信号 122、反転された内部クロック信号 124、およびリセット信号 254 を受け取り得る。反転された選択されたデータ信号およびリセット信号 254 は、第 2 の伝送ゲート 330 へ提供される揮発性リテンションステージ 356 の出力を生成するために使用され得る。例えば、揮発性リテンションステージ 356 の出力は、リセット信号 254 および選択されたデータ信号の反転を NOR ゲート 328 へ入力することによって生成され得る。NOR ゲート 328 は、反転された選択されたデータ信号を反転し、リセット信号 254 がローである（すなわち、論理的に低い値に関連する状態にある）場合、選択されたデータ信号を第 2 の伝送ゲート 330 へ与えるように構成され得る。NOR ゲート 328 はまた、リセット信号 254 がハイである（すなわち、論理的に高い値に関連する状態にある）場合、揮発性リテンションステージ 356 の出力がローになるようにし得る。NOR ゲート 328 の出力は、第 1 の PMOS トランジスタ 320 の入力および第 2 の NMOS トランジスタ 326 の入力に結合され得る。NOR ゲート 328 は、内部電圧源 130 によって電力供給され得る。図 3 は、NOR ゲート 328 を示すが、他の論理ゲートまたは切替装置が揮発性リテンションステージ 356 の出力を生成するために使用され得る。揮発性リテンションステージ 356 は、内部電圧源 130 によって電力供給され得る。

20

#### 【 0030 】

[0038] 挥発性リテンションステージ 356 は、第 1 の n - チャネル金属酸化膜半導体 (NMOS) トランジスタスタックに結合された第 1 の p - チャネル金属酸化膜半導体 (PMOS) トランジスタスタックを含む。第 1 の PMOS トランジスタスタックは、直列に結合された第 1 の PMOS トランジスタ 320 および第 2 の PMOS トランジスタ 322 を含み得る。第 1 の NMOS トランジスタスタックは、第 2 の PMOS トランジスタ 322 と直列に結合された第 1 の NMOS トランジスタ 324 と、第 1 の NMOS トランジスタ 324 と直列に結合された第 2 の NMOS トランジスタ 326 を含み得る。第 1 の PMOS トランジスタスタックおよび第 1 の NMOS トランジスタスタックは、反転された内部クロック信号 124 および内部クロック信号 122 に応答して、NOR ゲート 328 の出力を反転するように構成され得る。揮発性リテンションステージ 356 は、選択されたデータ信号を保存し、リセット信号 254 がディスエーブルされ、内部クロック信号 122 がハイである時、選択されたデータ信号を第 2 の伝送ゲート 330 へ伝送するように構成され得る。第 1 の PMOS トランジスタスタックおよび第 1 の NMOS トランジスタスタックは、スタンバイモードの間、自己逆バイアス効果によって揮発性リテンションステージ 356 に関連するリーク電流を低減し得る。

30

40

#### 【 0031 】

10

20

30

40

50

[0039] 第2の伝送ゲート330は、内部クロック信号122に応答して、内部データノード(q\_internal)310へ揮発性リテンションステージ356の出力を伝送するように構成され得る。内部データノード310は、出力インバータのチェーンに、および不揮発性領域302に、結合され得る。出力インバータのチェーンは、直列に結合された第1の出力インバータ332と第2の出力インバータ334とを含み得る。出力インバータのチェーンは、内部電圧源130によって電力供給され得る。図3の出力インバータのチェーンには2つのインバータが示されているが、出力インバータのチェーンは、2つより多くのインバータを含み得る。出力インバータのチェーンは、データアウト信号312として遅延された内部ノード信号を出力するように構成され得る。データアウト信号312は、図2のデータアウト信号240-247のうちの1つに対応し得る。

10

## 【0032】

[0040] 出力インバータのチェーンは、遅延された内部データノード信号を論理ゲートへ提供するようにさらに構成され得る。例えば、出力インバータのチェーンは、遅延された内部データノード信号をORゲート336へ提供するように構成され得る。ORゲート336は、反転されたシフト信号252がイネーブルされる時、シフトデータアウト信号314としてハイ信号(high signal)を出力するように構成され得る。ORゲート336は、反転されたシフト信号252がイネーブルされない時、シフトデータアウト信号314として遅延された内部データノード信号を出力するようにさらに構成され得る。シフトデータアウト信号312は、図2のシフトデータアウト信号221-228に対応し得る。ORゲート336は、内部電圧源130によって電力供給され得る。図3はORゲートを示すが、他の論理ゲートまたは切替装置がシフトデータアウト信号314を生成するために使用され得る。

20

## 【0033】

[0041] 不揮発性領域302は、リテンションレジスタ300がスタンバイモードにある時、データ信号(例えば、内部データノード310の状態)を保存するように構成され得る。不揮発性領域302は、入力として、反転されたリテンション信号120、リセット信号254、内部クロック信号122、および反転された内部クロック信号124を受け取り得る。不揮発性領域302は、外部電圧源116によって電力供給され得る。不揮発性領域302は、第2のPMOSトランジスタスタックへ入力を供給するように構成される不揮発性インバータ338を含み得る。不揮発性インバータ338は、第2のNMOSトランジスタスタックへ入力を供給するようにさらに構成され得る。

30

## 【0034】

[0042] 第2のPMOSトランジスタスタックは、第2のNMOSトランジスタスタックに結合され得る。第2のPMOSトランジスタスタックは、第3のPMOSトランジスタ340、第4のPMOSトランジスタ342、第5のPMOSトランジスタ344、および第6のPMOSトランジスタ346を含み得る。第3のPMOSトランジスタ340および第4のPMOSトランジスタ342のドレインは、第5のPMOSトランジスタ344のソースに結合され得る。第5のPMOSトランジスタは、第6のPMOSトランジスタ346と直列に結合され得る。第2のNMOSトランジスタスタックは、第6のPMOSトランジスタ346と直列に結合された第3のNMOSトランジスタ348を含み得る、および第3のNMOSトランジスタ348と直列に結合された第4のNMOSトランジスタ352を含み得る。第3のNMOSトランジスタ348および第6のPMOSトランジスタ346は、さらに内部データノード310へ結合され得る。不揮発性インバータ338、第2のPMOSトランジスタスタック、および第2のNMOSトランジスタスタックは、リテンションレジスタ300がリセットモードにない場合、内部データノード310における値を保存するように構成され得る。第2のPMOSトランジスタスタックおよび第2のNMOSトランジスタスタックは、リセットモードの間、自己逆バイアス効果によって不揮発性領域302に関連するリーク電流を低減し得る。

40

## 【0035】

[0043] 第2のPMOSトランジスタスタックおよび第2のNMOSトランジスタスタッ

50

ックは、さらに第3のN MOSトランジスタスタックに結合され得る。第3のN MOSトランジスタスタックは、第6のN MOSトランジスタ354と直列に結合された第5のN MOSトランジスタ350を含み得る。第5のN MOSトランジスタ350はさらに、第3のN MOSトランジスタ348、第6のPMOSトランジスタ346、および内部データノード310に結合され得る。第3のN MOSトランジスタスタックは、リテンションレジスタ300がリセットモードにあってスタンバイモードにない時、内部データノード310における値をローに設定するように構成され得る。反転されたリテンション信号120またはリセット信号254がローである場合、内部クロック信号122がハイである時は内部データノード310の状態が保持され得、内部クロック信号122がローである時は不揮発性領域302がフローティング(hi-Z)信号(a floating (hi-Z) signal)を出力し得る。反転されたリテンション信号120およびリセット信号254がハイである場合、内部データノード310における値は、ローにプルダウンされ得る。

#### 【0036】

[0044] 動作中、マルチプレクサ316は、反転された選択されたデータ信号を第1の伝送ゲート318へ出力するように構成され得る。第1の伝送ゲート318は、反転された内部クロック信号124に応答して、反転された選択されたデータ信号を揮発性リテンションステージ356へ提供するように構成され得る。リセット信号254がローである時、揮発性リテンションステージ356は、反転された選択されたデータ信号を保持し、選択されたデータ信号を第2の伝送ゲート330へ提供するように構成され得る。リセット信号254がハイである時、揮発性リテンションステージ356は、ロー値を保持し、そのロー値を第2の伝送ゲート330へ与えるように構成され得る。第2の伝送ゲート330は、内部クロック信号122に応答して、揮発性リテンションステージの出力(例えば、選択されたデータ信号またはロー値)を内部データノード310へ提供するように構成され得る。内部データノード310は、出力インバータのチェーンに、および不揮発性領域302に接続され得る。不揮発性領域302は、リテンションレジスタ300がスタンバイモードにあり、揮発性領域304が電源を供給されていない時、内部データノード310の状態を保持するように構成され得る。不揮発性領域302はさらに、リセット信号254がハイである時、内部データノード310の値をローに設定するように構成され得る。出力インバータのチェーンは、データアウト信号312として遅延された内部ノード信号を出力するように構成され得る。出力インバータのチェーンは、遅延された内部データノード信号を論理ゲートに提供してシフトデータアウト信号314を選択的に出力するようにさらに構成され得る。

#### 【0037】

[0045] したがって、スタンバイモードの間リテンションレジスタ300の揮発性リテンションステージ356に関連するリーク電流が、およびリセットモードの間リテンションレジスタ300の不揮発性領域302に関連するリーク電流が、自己逆バイアス効果によって低減され得る。それ故に、リテンションレジスタ300を組み込んだ電子デバイスの利用可能な動作時間は、電子デバイスが蓄えられた電力で動く時、増加し得る。

#### 【0038】

[0046] 図4は、特定の実施形態に従って、図3のリテンションレジスタ300のようなリテンションレジスタの機能を例示する真理表400である。図4は、データ入力の値ret、d、rst、sin、およびshiftに基づく出力の値qおよびsoutを例示する。機能モードでは、qの値はdの値に等しく、soutの値は1に等しい(すなわち、論理的に高い値に関連する状態にある)。リセットモードでは、rstの値は1に等しく、qの値は0に等しく(すなわち、論理的に低い値に関連する状態にある)およびsoutの値は1に等しい。スキヤンモードでは、shiftの値は1に等しく、qおよびsoutの値はsinの値に等しい。スタンバイモードでは、retの値は1に等しく、内部電圧源(vddx)はオフであり、前のqの値は図3の不揮発性領域302のような不揮発性領域に記憶され、ならびにqおよびsoutの値は使用されない。図3の揮発性領域304内に位置するコンポーネントは、スタンバイモードにおいて揮発性領域304

10

20

30

40

50

への電力が低減される時、図 4において X で表されるフローティング状態（すなわち喪失したドメイン（collapsed domain）によって駆動される値）に入るよう構成され得る。図 4 はまた、内部電圧源（VDDX）がオンであり、RET の値がハイであるいくつかのコーナーケース（corner cases）を例示する。

#### 【0039】

[0047] 図 5 は、図 3 のリテンションレジスタ 300 のようなリテンションレジスタのサンプル動作を例示する。図 5 は、リテンションレジスタ 300 のようなリテンションレジスタのパワーダウンシーケンス、スタンバイモード、およびパワーアップシーケンスの間の、内部クロック信号（CLK\_NET）、内部電圧（VDDX）、リセット信号（RST）、リテンション信号（RET）、データ出力値（出力データ）、および内部データ値（内部データ）のグラフ 500 を例示する。内部クロック信号は、図 3 の内部クロック信号 122 に対応し得る。内部電圧は、図 3 の内部電圧源 130 における電圧に対応し得る。リセット信号は、図 3 のリセット信号 254 に対応し得る。リテンション信号は、図 3 の反転されたリテンション信号 120 の反転に対応し得る。データ出力値は、図 3 のソフトデータアウト信号 314 またはデータアウト信号 312 に対応し得る。内部データ値は、図 3 の内部データノード 310 における値に対応し得る。

10

#### 【0040】

[0048] グラフ 500 に例示されるように、リテンション信号は、リテンションレジスタがスタンバイモードに入る前にハイに設定され得る。続いて、内部電圧が減少し得る。内部クロック信号、リセット信号、およびデータ出力値における値は、スタンバイモードの間使用されない。しかしながら、内部データ値は、スタンバイモードの間保存され得る。

20

#### 【0041】

[0049] リテンションレジスタがスタンバイモードを抜け出る用意をする時、内部電圧が増加し得る。リテンション信号は、内部電圧が安定した後に、ローに設定され得る。データ出力値は、内部データ値を反映し得る。リテンションレジスタがリセット信号を受取る時、リテンションレジスタは、内部データ値およびデータ出力値をローに設定し得る。

#### 【0042】

[0050] 図 6 に関して、リテンションレジスタトレイ 600 の特定の実施形態のレイアウト図が示される。リテンションレジスタトレイ 600 は、図 2 のリテンションレジスタトレイ 200 に対応し得る。リテンションレジスタトレイ 600 は、第 1 の半導体デバイス領域 602 に組み込まれ得る。リテンションレジスタトレイ 600 は、1 つ以上の 1 ビットのリテンションレジスタを含み得る。破線で区切られたエリアに対応する 8 つのリテンションレジスタが、図 6 の第 1 の半導体デバイス領域 602 に示される。他の実施形態では、リテンションレジスタトレイ 600 は、8 つより多くのリテンションレジスタまたは 8 つより少ないリテンションレジスタを含み得る。リテンションレジスタトレイ 600 の各リテンションレジスタは、図 3 のリテンションレジスタ 300 に対応し得る。

30

#### 【0043】

[0051] 第 1 の半導体デバイス領域 602 において、リテンションレジスタトレイ 600 の製造過程で、各リテンションレジスタの不揮発性領域は、第 1 の n 型ウェル（n-well）604 中にグループ化され得る。第 1 の n-well 11604 は、外部電圧源 116 によって電力供給され得る。各リテンションレジスタの不揮発性領域は、図 3 の不揮発性領域 302 に対応し得る。さらに、第 1 の n-well 11604 は、図 1 のクロックゲーティング回路 100 を含み得る。図 6 には、外部電圧源 116 によって電力供給される 1 つの n-well（例えば、第 1 の n-well 11604）が示されるが、他の実施形態では、リテンションレジスタトレイ 600 は、外部電圧源 116 によって電力供給される 1 つより多くの n-well を含み得る。製造の複雑性は、製造過程で、1 つより多くのリテンションレジスタの不揮発性領域を単一の n-well へ合併することによって低減され得る。また、反転された内部クロック信号（例えば、図 1 の反転された内部クロック信

40

50

号 1 2 4 ) および内部クロック信号( 例えば、図 1 の内部クロック信号 1 2 2 ) の配線経路は、複数の n - w e l l に比べて、単一の n - w e l l 内においてよりコンパクトであり得る( すなわち、より少ない電力を使用し、かつより少ない遅延を有する ) 。

#### 【 0 0 4 4 】

[0052] 各リテンションレジスタの揮発性領域は、第 1 の n - w e l l と分離された複数の n - w e l l ( 例えば、第 2 の n - w e l l 6 0 6 、第 3 の n - w e l l 6 0 8 、第 4 の n - w e l l 6 1 0 、および第 5 の n - w e l l 6 1 2 ) に配置され得る。第 1 の n - w e l l 6 0 4 と分離された複数の n - w e l l は、内部電圧源 1 3 0 によって電力供給され得る。各リテンションレジスタの揮発性領域は、図 3 の揮発性領域 3 0 4 に対応し得る。図 6 では、第 2 の n - w e l l 6 0 6 、第 3 の n - w e l l 6 0 8 、第 4 の n - w e l l 6 1 0 、および第 5 の n - w e l l 6 1 2 は各々、2 つのリテンションレジスタによって共有されているが、他の実施形態では、n - w e l l 6 0 6 - 6 1 2 は各々、2 つより多くのリテンションレジスタまたは 2 つより少ないリテンションレジスタの揮発性領域を含み得る。製造の複雑性は、製造過程で、1 つより多くのリテンションレジスタの揮発性領域を単一の n - w e l l へ合併することによって低減され得る。10

#### 【 0 0 4 5 】

[0053] 製造設計制約に従って、第 1 の n - w e l l 6 0 4 は、別の n - w e l l ( 例えば、第 2 の n - w e l l 6 0 6 、第 3 の n - w e l l 6 0 8 、第 4 の n - w e l l 6 1 0 、および第 5 の n - w e l l 6 1 2 ) との間に特定の間隔を空けて配置され得る。さらに、第 2 の半導体デバイス領域 6 1 4 を第 1 の半導体デバイス領域 6 0 2 と隣接して配置することが望ましい可能性がある。第 2 の半導体デバイス領域 6 1 4 は、第 1 の半導体デバイス領域 6 0 2 を含む半導体ダイの一部であり得るか、あるいは第 2 の半導体デバイス領域 6 1 4 は、第 1 の半導体デバイス領域 6 0 2 を含む半導体ダイとは異なる半導体ダイの一部であり得る。第 2 の半導体デバイス 6 1 4 は、1 つ以上の n - w e l l ( 例えば、第 6 の n - w e l l 6 1 6 および第 7 の n - w e l l 6 1 8 ) を含み得る。開示された実施形態のうちの少なくとも 1 つによって提供される 1 つの特定の利点は、n - w e l l を含む第 2 の半導体デバイス領域が、不揮発性領域の設計制約を破ることなく、不揮発性領域を含む第 1 の半導体デバイス領域に隣接して配置され得るように、各不揮発性領域( 例えば、第 1 の n - w e l l 6 0 4 ) を半導体デバイスの端( edge ) からある距離だけ離して配置することによって、設計の複雑性が低減され得ることである。20

#### 【 0 0 4 6 】

[0054] その結果、リテンションレジスタトレイ 6 0 0 に関する製造の複雑性および設計の複雑性が低減され得る。それ故に、リテンションレジスタトレイ 6 0 0 を組み込んだ半導体ダイは、より容易に製造され得る。30

#### 【 0 0 4 7 】

[0055] 図 7 は、クロックゲーティング回路を動作させる方法 7 0 0 の特定の実施形態を例示する流れ図である。1 つの実施形態では、クロックゲーティング回路は、図 1 のクロックゲーティング回路 1 0 0 に対応する。方法 7 0 0 は、7 0 2 において、クロック入力を有するトランジスタを含むリテンションステージにおいてクロック信号を受け取ることを含む。リテンションステージは、外部電圧源によって電力供給され得る。クロックゲーティング回路 1 0 0 のリテンションステージ 1 0 2 は、第 2 の P M O S トランジスタ 1 1 0 または第 1 の N M O S トランジスタ 1 1 2 のようなクロック入力を有するトランジスタにおいて、外部クロック信号 1 0 6 を受け取り得る。リテンションステージ 1 0 2 は、外部電圧源 1 1 6 によって電力供給され得る。方法 7 0 0 はさらに、7 0 4 において、リテンションステージからインバータへ出力を与えることを含み、ここでインバータは、内部電圧源によって電力供給される。例えば、リテンションステージ 1 0 2 は、データライン 1 3 4 を介してインバータ 1 0 4 へ出力を提供し得る。インバータ 1 0 4 は、内部電圧源 1 3 0 によって電力供給され得る。40

#### 【 0 0 4 8 】

[0056] 方法 7 0 0 のインバータの出力は、第 1 のリテンションレジスタへ、または第50

1のリテンションレジスタおよび第2のリテンションレジスタへ与えられ得、ここで第1のリテンションレジスタおよび第2のリテンションレジスタは、リテンションレジスタトレイを形成し、およびここで、第1のリテンションレジスタは、第2のリテンションレジスタに結合される。例えば、図1のインバータ104の出力は、図2のリテンションレジスタ204およびリテンションレジスタ206へ与えられ得、ここで、リテンションレジスタ204およびリテンションレジスタ206はリテンションレジスタトレイ200を形成し、およびここで、リテンションレジスタ204はデータアウト信号(soutb0)221を传送するために使用されるデータラインに沿ってリテンションレジスタ206へ結合される。リテンションステージは、リテンション信号および反転されたリテンション信号を受け取り得る。例えば、リテンションステージ102は、リテンション信号118および反転されたリテンション信号120を受け取り得る。第1のリテンションレジスタは、反転されたリテンション信号に基づいて、スタンバイモードに入る、またはスタンバイモードを抜け出ることをトリガされ得る。

10

## 【0049】

[0057] それ故に、方法700は、例えリテンションステージおよび反転されたリテンションステージが異なる電圧源によって電力供給されていても、クロックゲーティング回路をイネーブルしてクロック信号および反転されたクロック信号を出力する。その結果、クロックゲーティング回路がスタンバイモードにある時、クロックゲーティング回路に関連するリーク電流が低減され得る。したがって、クロックゲーティング回路を組み込んだ電子デバイスの利用可能な動作時間は、電子デバイスが蓄えられた電力で動く時、増加し得る。

20

## 【0050】

[0058] 図8は、リテンションレジスタを動作させる方法800の特定の実施形態を示す流れ図である。1つの実施形態では、リテンションレジスタは図3のリテンションレジスタ300に対応する。方法800は、802において、リテンション信号を受け取ることに応えて、リテンションレジスタの不揮発性ステージにおいて状態情報を保持することを含み、ここで不揮発性ステージは、外部電圧源によって電力供給される。例えば、リテンションレジスタ300は、反転されたリテンション信号120を受け取り得る。反転されたリテンション信号120は、クロックゲーティング回路100の外部の1つ以上の回路およびリテンションレジスタトレイ200によって(例えば、スタンバイモードに入ることの決定に基づいてあるプロセッサから)、提供され得る。反転されたリテンション信号120に応えて、リテンションレジスタ300の不揮発性領域302は、状態情報を保持し得る。状態情報は、少なくとも内部データ状態(例えば、内部データノード310における値)を含み得る。不揮発性領域302は、外部電圧源116によって電力供給され得る。

30

## 【0051】

[0059] 方法800はさらに、804において、リテンションレジスタの揮発性ステージへの電力を低減することを含み、ここで揮発性ステージは、内部電圧源によって電力供給される。例えば、リテンションレジスタ300の揮発性領域304への電力が低減され得る。揮発性領域304は、内部電圧源130によって電力供給され得る。

40

## 【0052】

[0060] 方法800は、リテンションレジスタの揮発性領域への電力が低減される時、リテンションレジスタをイネーブルしてデータを保持し得る。

## 【0053】

[0061] 図7および8の方法は、フィールドプログラマブルゲートアレイ(FPGA)デバイス、特定用途向け集積回路(ASSIC)、処理ユニット(例えば、中央処理装置(CPU))、デジタルシグナルプロセッサ(DSP)、コントローラ、別のハードウェアデバイス、ファームウェアデバイス、またはそれらの任意の組み合わせのような様々なデバイスによって実現され得る。例として、図7および8の方法は、図9を参照してさらに説明されるように、命令を実行する1つ以上のプロセッサによって行われることができる

50

。例示のために、図 7 の方法は、クロックゲーティング回路のリテンションステージヘリテンション信号を発行するように構成されるプロセッサによって開始されることができる。リテンションステージは、外部電圧源によって電力供給され得、およびクロック信号を受け取り、インバータへ出力を提供するように構成され得る。インバータは、内部電圧源によって電力供給され得る。

#### 【0054】

[0062] 図 9 に関して、クロックゲーティング回路およびリテンションレジスタトレイを組み込んでいる通信デバイスの特定の例示的な実施形態のブロック図が描かれ、一般に指定される 900。通信デバイス 900 またはそのコンポーネントは、モバイル局、アクセスポイント、セットトップボックス、エンタテイメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末（PDA）、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイルフォン、セルラフォン、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、タブレット、モニタ、コンピュータモニタ、テレビ、チューナー、無線、衛星無線、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、ビデオプレーヤ、デジタルビデオプレーヤ、デジタルビデオディスク（DVD）プレーヤまたはポータブルデジタルビデオプレーヤのようなデバイス内に含まれ得るか、それらを実現し得るか、またはそれらを含み得、ここで、各々は、図 7 および 8 の方法のうちの 1 つ以上を実行するように構成され得る。1 つの実施形態では、通信デバイス 900 は、図 1 の少なくとも 1 つのクロックゲーティング回路 100 および図 2 の少なくとも 1 つのリテンションレジスタトレイ 200 を含む。

10

20

30

40

#### 【0055】

[0063] 通信デバイス 900 は、メモリ 932 に結合された、デジタルシグナルプロセッサ（DSP）のようなプロセッサ 910 を含む。特定の実施形態では、プロセッサ 910 は、リテンションレジスタトレイ 952（例えば、図 2 のリテンションレジスタトレイ 200）に接続されたクロックゲーティング回路 950（例えば、図 1 のクロックゲーティング回路 100）を含む。例として、メモリ 932 は、ランダムアクセスメモリ（RAM）、磁気抵抗ランダムアクセスメモリ（MRAM：magnetoresistive random access memory）、スピントルクトランスファ MRAM（STT-MRAM：spin-torque transfer MRAM）、フラッシュメモリ、読み出し専用メモリ（ROM）、プログラマブル読み出し専用メモリ（PROM）、消去可能プログラマブル読み出し専用メモリ（EPROM）、レジスタ、ハードディスク、リムーバブルディスク、またはコンパクトディスク読み出し専用メモリ（CD-ROM）のようなメモリデバイスであり得る。メモリデバイスは、プロセッサ（例えば、プロセッサ 910、ディスプレイコントローラ 926、またはワイヤレスコントローラ 940）によって実行されると、プロセッサに、リテンションステージ（例えば、図 1 のリテンションステージ 102）に提供されるリテンション信号を発行させる命令を含み得る。リテンションステージは、外部電圧源（例えば、図 1 の外部電圧源 116）によって電力供給され得、クロック信号（例えば、図 1 の外部クロック信号 106）を受け取るように構成され得、およびインバータ（例えば、図 1 のインバータ 104）へ出力を提供するように構成され得る。インバータは、内部電圧源（例えば、図 1 の内部電圧源 130）によって電力供給され得る。

#### 【0056】

[0064] 通信デバイス 900 は、プロセッサ 910 へ、およびディスプレイ 928 へ結合されたディスプレイコントローラ 926 を含み得る。特定の実施形態では、ディスプレイコントローラ 926 は、リテンションレジスタトレイ 948（例えば、図 2 のリテンションレジスタトレイ 200）に接続されたクロックゲーティング回路 946（例えば、図 1 のクロックゲーティング回路 100）を含む。符号器 / 復号器（CODEC）934 もまた、プロセッサ 910 に結合されることがある。スピーカ 936 およびマイクロフォン 938 は、CODEC 934 へ結合されることがある。ワイヤレスコントローラ 940（例えば、受信機、送信機、またはトランシーバ）は、プロセッサ 910 へおよびアンテナ 942 へ結合されることがある。特定の実施形態では、ワイヤレスコントローラ 9

50

40は、リテンションレジスタトレイ956（例えば、図2のリテンションレジスタトレイ200）に接続されたクロックゲーティング回路954（例えば、図1のクロックゲーティング回路100）を含む。

#### 【0057】

[0065] 説明された実施形態と併せて、ある装置は、データをスイッチングするための手段を含む。データをスイッチングするための手段は、クロック入力を有するゲートを含むことができる。データをスイッチングするための手段は、外部電圧源によって電力供給され得る。1つの実施形態では、プロセッサ910、ディスプレイコントローラ926、またはワイヤレスコントローラ940は、図1のクロックゲーティング回路100に対応するクロックゲーティング回路を含み、およびこのデータをスイッチングするための手段は、クロックゲーティング回路100のリテンションステージ102に対応する。この装置はさらに、データをスイッチングするための手段の出力を反転するための手段を含み得る。反転するための手段は、内部電圧源によって電力供給され得る。例えば、反転するための手段は、図1のクロックゲーティング回路100のインバータ104に対応し得る。

10

#### 【0058】

[0066] 説明された実施形態と併せて、ある装置は、第1のビットを保持するための手段を含む。1つの実施形態では、プロセッサ910、ディスプレイコントローラ926、またはワイヤレスコントローラ940は、図2のリテンションレジスタトレイ200に対応するリテンションレジスタトレイを含み、およびこの第1のビットを保持するための手段は、リテンションレジスタトレイ200のリテンションレジスタ204に対応する。この装置は、第2のビットを保持するための手段をさらに含み得る。例えば、第2のビットを保持するための手段は、リテンションレジスタトレイ200のリテンションレジスタ206に対応し得る。第1のビットを保持するための手段および第2のビットを保持するための手段は、データを保持するための手段を形成し得る。例えば、データを保持するための手段は、リテンションレジスタトレイ200に対応し得る。

20

#### 【0059】

[0067] 説明された実施形態と併せて、ある装置は、第1のビットを保持するための手段および第2のビットを保持するための手段へクロック信号を供給するための手段を含む。1つの実施形態では、プロセッサ910、ディスプレイコントローラ926、またはワイヤレスコントローラ940は、図1のクロックゲーティング回路100に対応するクロックゲーティング回路を含み、およびこのクロック信号を供給するための手段は、図1のクロックゲーティング回路100に対応する。クロック信号を供給するための手段は、データを保持するための手段の外部にあり得る。例えば、クロックゲーティング回路100は、図2のリテンションレジスタトレイ200の外部にあり得る。クロック信号を供給するための手段は、外部電圧源によって電力供給される第1のステージと、内部電圧源によって電力供給される第2のステージとを含む。例えば、クロックゲーティング回路100は、外部電圧源116によって電力供給されるリテンションステージ102と、内部電圧源130によって電力供給されるインバータ104とを含む。

30

#### 【0060】

[0068] 特定の実施形態では、プロセッサ910、ディスプレイコントローラ926、メモリ932、CODEC934、およびワイヤレスコントローラ940は、システムインパッケージまたはシステムオンチップデバイス922に含まれる。特定の実施形態では、入力デバイス930および電力供給装置944は、システムオンチップデバイス922へ結合される。さらに、特定の実施形態では、図9に例示されるように、ディスプレイ928、入力デバイス930、スピーカ936、マイクロフォン938、アンテナ942、および電力供給装置944は、システムオンチップデバイス922の外部にある。しかしながら、ディスプレイ928、入力デバイス930、スピーカ936、マイクロフォン938、アンテナ942、および電力供給装置944の各々は、インターフェースまたはコントローラのようなシステムオンチップデバイス922のコンポーネントに結合することができます。

40

50

## 【0061】

[0069] 当業者は、ここに開示された実施形態に関連して説明された様々な例示的な論理ブロック、構成、モジュール、回路、およびアルゴリズムステップが、電子ハードウェア、プロセッサによって実行されるコンピュータソフトウェア、またはその両方の組み合わせとして実現され得ることをさらに認識するだろう。様々な例示的なコンポーネント、ブロック、構成、モジュール、回路、およびステップは、概してそれらの機能性の観点から上で説明された。このような機能性が、ハードウェアとして実現されるかまたはプロセッサ実行可能な命令として実現されるかは、特定のアプリケーションおよびシステム全体に課せられた設計制約に依存する。当業者は、説明された機能性を特定のアプリケーションごとに様々な方法で実現し得るが、このような実現の決定は、本開示の範囲からの逸脱を生じさせるものとして解釈されるべきではない。

10

## 【0062】

[0070] ここに開示された実施形態に関連して説明されたアルゴリズムまたは方法のステップは、直接的にハードウェアにおいて、プロセッサによって実行されるソフトウェアモジュールにおいて、またはそれら2つの組み合わせにおいて、具現化され得る。ソフトウェアモジュールは、ランダムアクセスメモリ( RAM )、フラッシュメモリ、読み出し専用メモリ( ROM )、プログラマブル読み出し専用メモリ( PROM )、消去可能プログラマブル読み出し専用メモリ( EEPROM (登録商標))、レジスタ、ハードディスク、リムーバブルディスク、コンパクトディスク読み出し専用メモリ( CD - ROM )、あるいは当技術において周知であるその他任意の形態の非一時的な記憶媒体に存在し得る。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み出すことができるよう、および記憶媒体へ情報を書き込むことができるよう、プロセッサに結合されている。別の方では、記憶媒体はプロセッサと一体化され得る。プロセッサおよび記憶媒体は、特定用途向け集積回路(ASIC)内に存在し得る。ASICは、コンピューティングデバイスまたはユーザ端末内に存在し得る。別の方では、プロセッサおよび記憶媒体は、コンピューティングデバイスまたはユーザ端末内の個別のコンポーネントとして存在し得る。

20

## 【0063】

[0071] 開示された実施形態の先の説明は、当業者が開示された実施形態を製造または使用すること可能にするように提供されている。これらの実施形態への様々な修正は、当業者にとって容易に明らかであり、ここに定義された原理は、本開示の範囲から逸脱することなく他の実施形態に適用され得る。それ故に、本開示は、ここに示された実施形態に限定されるようには意図されておらず、以下の特許請求の範囲によって定義されるような原理および新規な特徴と一致する、可能性のある最も広い範囲を与えられることとなる。

30

【図 1】

FIG. 1

【図 2】

【図5】

FIG. 5

【図6】

【図 9】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2014/018811

A. CLASSIFICATION OF SUBJECT MATTER

INV. H03K3/356 H03K3/037 G06F1/32 H03K19/00

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H03K G06F

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                   | Relevant to claim No.       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| X         | US 2006/255849 A1 (CHUN CHRISTOPHER K Y [US]) 16 November 2006 (2006-11-16)<br>abstract; figures 1,2,3<br>paragraphs [0002], [0014], [0015], [0016], [0017]<br>----- | 1-4,6-9,<br>11,15-19<br>20  |

| A         | WO 00/67380 A1 (INTEL CORP [US]; MCDANIEL BART R [US]; CLARK LAWRENCE T [US]) 9 November 2000 (2000-11-09)<br>abstract; figures 3,4,5<br>page 10 - page 14<br>-----  | 1,2,7,8,<br>11,15,<br>18-20 |

| X         | US 2004/266092 A1 (AKSAMIT RANDY J [US]) 30 December 2004 (2004-12-30)<br>abstract; figures 1,2,4,5<br>-----                                                         | 1-9,11,<br>15-20            |

| A         | -----                                                                                                                                                                | -/-                         |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

21 May 2014

11/08/2014

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Mesic, Maté

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2014/018811 |

|---------------------------------------------------|

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                             | Relevant to claim No.  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| A         | US 2009/058484 A1 (RAO BINDU PRABHAKAR [IN] ET AL) 5 March 2009 (2009-03-05)<br><br>abstract; figure 4<br>-----                                                | 1-4,<br>6-11,<br>15-20 |

| A         | WO 2006/127888 A2 (TEXAS INSTRUMENTS INC [US]; GURURAJARAO SUMANTH KATTE [US]; MAIR HUGH) 30 November 2006 (2006-11-30)<br><br>abstract; figures 1,3a<br>----- | 1-11,<br>15-20         |

**INTERNATIONAL SEARCH REPORT**

International application No.

PCT/US2014/018811

**Box No. II Observations where certain claims were found unsearchable (Continuation of Item 2 of first sheet)**

This international search report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.: because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.: because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically:

3.  Claims Nos.: because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

**Box No. III Observations where unity of invention is lacking (Continuation of Item 3 of first sheet)**

This International Searching Authority found multiple inventions in this international application, as follows:

see additional sheet

1.  As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fees, this Authority did not invite payment of additional fees.

3.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:

4.  No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:

1-11, 15-20

**Remark on Protest**

- The additional search fees were accompanied by the applicant's protest and, where applicable, the payment of a protest fee.

- The additional search fees were accompanied by the applicant's protest but the applicable protest fee was not paid within the time limit specified in the invitation.

- No protest accompanied the payment of additional search fees.

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

|                              |

|------------------------------|

| International application No |

| PCT/US2014/018811            |

| Patent document cited in search report |    | Publication date | Patent family member(s) |               | Publication date |

|----------------------------------------|----|------------------|-------------------------|---------------|------------------|

| US 2006255849                          | A1 | 16-11-2006       | NONE                    |               |                  |

| WO 0067380                             | A1 | 09-11-2000       | AU                      | 4481000 A     | 17-11-2000       |

|                                        |    |                  | CN                      | 1354908 A     | 19-06-2002       |

|                                        |    |                  | DE                      | 10084545 B4   | 02-07-2009       |

|                                        |    |                  | DE                      | 10084545 T1   | 11-04-2002       |

|                                        |    |                  | GB                      | 2363685 A     | 02-01-2002       |

|                                        |    |                  | JP                      | 4643025 B2    | 02-03-2011       |

|                                        |    |                  | JP                      | 2002543731 A  | 17-12-2002       |

|                                        |    |                  | US                      | 6166985 A     | 26-12-2000       |

|                                        |    |                  | WO                      | 0067380 A1    | 09-11-2000       |

| US 2004266092                          | A1 | 30-12-2004       | NONE                    |               |                  |

| US 2009058484                          | A1 | 05-03-2009       | NONE                    |               |                  |

| WO 2006127888                          | A2 | 30-11-2006       | CN                      | 101233687 A   | 30-07-2008       |

|                                        |    |                  | US                      | 2006267654 A1 | 30-11-2006       |

|                                        |    |                  | WO                      | 2006127888 A2 | 30-11-2006       |

International Application No. PCT/ US2014/ 018811

**FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210**

This International Searching Authority found multiple (groups of) inventions in this international application, as follows:

1. claims: 1-11, 15-20

retention stage with an inverter

---

2. claims: 12-14

a means for switching data

---

3. claims: 21-26

implementation of a dedicated well structure for a retention register

---

---

フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

H 03 K 3/037 B

(81) 指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,R,S,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,H,R,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(72) 発明者 ピラングディピチャイ、ラマプラサス

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72) 発明者 パテル、プラヤグ・バーヌブハイ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

F ターム(参考) 5F038 CA03 CA05 CD02 CD06 DF01 DF08 DF14 DF17 EZ20

5J034 AB15 CB01 DB03 DB08

5J043 AA12 HH01 JJ04 JJ10 KK02