(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년10월25일

(11) 등록번호 10-1669208

(24) 등록일자 2016년10월19일

(51) 국제특허분류(Int. Cl.)

*H04B 1/54* (2015.01) *H03B 28/00* (2014.01)

*H04B 1/44* (2006.01)

(21) 출원번호 10-2014-7027390

(22) 출원일자(국제) 2013년02월28일

심사청구일자 2015년11월04일

(85) 번역문제출일자 2014년09월29일

(65) 공개번호 10-2014-0130221

(43) 공개일자 2014년11월07일

(86) 국제출원번호 PCT/US2013/028398

(87) 국제공개번호 WO 2013/130866

국제공개일자 2013년09월06일

(30) 우선권주장

13/765,992 2013년02월13일 미국(US)

61/605,285 2012년03월01일 미국(US)

(56) 선행기술조사문헌

US20120263215 A1

US20050078615 A1

US7519332 B1

US0531979 A

(73) 특허권자

**퀄컴 인코포레이티드**

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

(72) 발명자

**나라통, 치우찬**

미국 92121 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

**례옹, 라이 캔**

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

(뒷면에 계속)

(74) 대리인

**특허법인 난액드남**

(74) 대리인

특허법위 낚액드남

전체 청구항 수 : 총 47 항

심사관 : 구영희

(54) 발명의 명칭 무선 디바이스에 대한 시·분할 듀플렉스 모드에서의 주파수 합성기 아키텍처

## (57) 요약

TDD(time division duplex) 모드에서 동작하는 무선 디바이스에 대한 듀얼 주파수 합성기 아키텍처가 개시되었다. 예시적인 설계에서, 무선 디바이스는 제1 및 제2 주파수 합성기들을 포함한다. 제1 주파수 합성기는 수신기에 대한 국부 발진기(LO) 주파수에서 제1/수신 LO 신호를 생성하기 위해 사용되는 제1 발진기 신호를 생성한다. 제2 주파수 합성기는 송신기에 대한 동일한 LO 주파수에서 제2/전송 LO 신호를 생성하기 위해 사용되는 제2 발진기 신호를 생성한다. 2개의 주파수 합성기들은 무선 디바이스가 TDD 모드에서 동작할 때 동일한 LO 주파수에서 수신 및 전송 LO 신호들을 획득하기 위해 자신의 발진기 신호들을 생성한다.

## 대 표 도

(72) 발명자

라우, 순-성

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

파텔, 쉬레니크

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

---

## 명세서

### 청구범위

#### 청구항 1

무선 통신을 위한 장치로서,

수신기에 대해 국부 발진기(L0) 주파수에서 제1 L0 신호를 생성하기 위해 사용되는 제1 발진기 신호를 생성하도록 구성된 제1 주파수 합성기; 및

송신기에 대해 상기 L0 주파수에서 제2 L0 신호를 생성하기 위해 사용되는 제2 발진기 신호를 생성하도록 구성된 제2 주파수 합성기를 포함하고,

상기 제1 및 제2 주파수 합성기들은 상기 장치가 시분할 모드에서 동작할 때 동일한 L0 주파수에서 상기 제1 및 제2 L0 신호들을 획득하기 위해 상기 제1 및 제2 발진기 신호들을 생성하도록 구성되고, 상기 제1 및 제2 주파수 합성기들 중 적어도 하나는 데이터 슬롯의 미드앰블(midamble) 내에서 인에이블되고, 그리고 상기 데이터 슬롯의 미드앰블에서 사용되는 변조 속도는 상기 데이터 슬롯의 다른 부분들에서 사용되는 변조 속도 보다 더 낮은, 무선 통신을 위한 장치.

#### 청구항 2

제1항에 있어서,

상기 시분할 모드에서, 상기 수신기는 제1 시간 구간들 동안 인에이블되고, 상기 송신기는 제2 시간 구간들 동안 인에이블되는, 무선 통신을 위한 장치.

#### 청구항 3

제1항에 있어서,

상기 시분할 모드는 TDD(time division duplex) 모드 및 TD-SCDMA(time division synchronous code division multiple access) 모드 중 하나인, 무선 통신을 위한 장치.

#### 청구항 4

제3항에 있어서,

상기 TDD 모드는 LTE(long term evolution) TDD 모드인, 무선 통신을 위한 장치.

#### 청구항 5

제1항에 있어서,

상기 제1 및 제2 주파수 합성기들은 동일한 발진기 주파수에서 상기 제1 및 제2 발진기 신호들을 생성하도록 구성되는, 무선 통신을 위한 장치.

#### 청구항 6

제1항에 있어서,

상기 제1 주파수 합성기는 제1 발진기 주파수에서 상기 제1 발진기 신호를 생성하도록 구성되고, 상기 제2 주파수 합성기는 상기 제1 발진기 주파수와는 상이한 제2 발진기 주파수에서 상기 제2 발진기 신호를 생성하도록 구성되는, 무선 통신을 위한 장치.

#### 청구항 7

제6항에 있어서,

상기 제1 발진기 주파수는 상기 L0 주파수의 정수배이고, 상기 제2 발진기 주파수는 상기 L0 주파수의 비-정수

배인, 무선 통신을 위한 장치.

### 청구항 8

제6항에 있어서,

상기 제1 발진기 주파수는 상기 L0 주파수의 비-정수배이고, 상기 제2 발진기 주파수는 상기 L0 주파수의 정수 배인, 무선 통신을 위한 장치.

### 청구항 9

제1항에 있어서,

상기 제1 주파수 합성기는 상기 수신기가 인에이블되기 이전에 인에이블되고, 상기 수신기가 디스에이블된 이후 또는 상기 수신기가 디스에이블될 때 디스에이블되며, 상기 제2 주파수 합성기는 상기 송신기가 인에이블되기 이전에 인에이블되고 상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 디스에이블되는, 무선 통신을 위한 장치.

### 청구항 10

제1항에 있어서,

상기 제1 및 제2 주파수 합성기들은 상기 수신기가 인에이블되기 이전에 인에이블되고, 상기 제1 주파수 합성기는 상기 수신기가 디스에이블된 이후 또는 상기 수신기가 디스에이블될 때 디스에이블되고, 상기 제2 주파수 합성기는 상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 디스에이블되는, 무선 통신을 위한 장치.

### 청구항 11

제1항에 있어서,

상기 제1 및 제2 주파수 합성기들은 상기 송신기가 인에이블되기 이전에 인에이블되는, 무선 통신을 위한 장치.

### 청구항 12

제1항에 있어서,

상기 제1 및 제2 주파수 합성기들은 상기 수신기가 인에이블되기 이전에 인에이블되고 상기 수신기가 디스에이블된 이후 또는 상기 수신기가 디스에이블될 때 디스에이블되는, 무선 통신을 위한 장치.

### 청구항 13

제1항에 있어서,

상기 제1 및 제2 주파수 합성기들은 상기 송신기가 인에이블되기 이전에 인에이블되고, 상기 제1 및 제2 주파수 합성기들은 상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 디스에이블되는, 무선 통신을 위한 장치.

### 청구항 14

제1항에 있어서,

상기 제1 주파수 합성기는 상기 수신기가 인에이블될 때 타겟 발진기 주파수에서, 그리고 상기 송신기가 인에이블될 때 상기 타겟 발진기 주파수로부터의 오프셋에서, 상기 제1 발진기 신호를 생성하도록 구성되는, 무선 통신을 위한 장치.

### 청구항 15

제14항에 있어서,

상기 제1 주파수 합성기는 PLL(phase locked loop)을 포함하고, 상기 타겟 발진기 주파수로부터의 오프셋은 상기 PLL 내의 주파수 디바이더 비(frequency divider ratio)를 변경함으로써 획득되는, 무선 통신을 위한 장치.

## 청구항 16

제1항에 있어서,

상기 제2 주파수 합성기는 상기 송신기가 인에이블될 때 타겟 발진기 주파수에서, 그리고 상기 수신기가 인에이블될 때 상기 타겟 발진기 주파수로부터의 오프셋에서 상기 제2 발진기 신호를 생성하도록 구성되는, 무선 통신을 위한 장치.

## 청구항 17

국부 발진기(L0) 신호들을 생성하는 방법으로서,

제1 주파수 합성기를 이용하여 제1 발진기 주파수에서 제1 발진기 신호를 생성하는 단계;

상기 제1 발진기 신호에 기초하여 수신기에 대해 L0 주파수에서 제1 L0 신호를 생성하는 단계;

제2 주파수 합성기를 이용하여 제2 발진기 주파수에서 제2 발진기 신호를 생성하는 단계 – 상기 제2 발진기 신호 주파수는 시분할 모드에서 동작할 때 상기 제1 발진기 주파수와는 상이함 – ;

상기 제2 발진기 신호에 기초하여 송신기에 대해 상기 L0 주파수에서 제2 L0 신호를 생성하는 단계;

데이터 슬롯의 미드앰블 내에서 상기 제1 및 제2 주파수 합성기들 중 적어도 하나를 인에이블하는 단계; 및

상기 데이터 슬롯의 미드앰블에서, 상기 데이터 슬롯의 다른 부분들에서 사용되는 변조 속도보다 더 낮은 변조 속도를 사용하는 단계를 포함하는, 국부 발진기 신호들을 생성하는 방법.

## 청구항 18

제17항에 있어서,

상기 시분할 모드는 TDD(time division duplex) 모드 및 TD-SCDMA(time division synchronous code division multiple access) 모드 중 하나인, 국부 발진기 신호들을 생성하는 방법.

## 청구항 19

제18항에 있어서,

상기 TDD 모드는 LTE(long term evolution) TDD 모드인, 국부 발진기 신호들을 생성하는 방법.

## 청구항 20

제18항에 있어서,

상기 TDD 모드에서 제1 시간 구간들 동안 상기 수신기를 인에이블하는 단계; 및

상기 TDD 모드에서 제2 시간 구간들 동안 상기 송신기를 인에이블하는 단계를 더 포함하는, 국부 발진기 신호들을 생성하는 방법.

## 청구항 21

제17항에 있어서,

상기 제1 발진기 주파수는 상기 L0 주파수의 정수배이고, 상기 제2 발진기 주파수는 상기 L0 주파수의 비-정수배인, 국부 발진기 신호들을 생성하는 방법.

## 청구항 22

제17항에 있어서,

상기 제1 발진기 주파수는 상기 L0 주파수의 비-정수배이고, 상기 제2 발진기 주파수는 상기 L0 주파수의 정수배인, 국부 발진기 신호들을 생성하는 방법.

## 청구항 23

제17항에 있어서,

상기 수신기가 인에이블되기 이전에 상기 제1 주파수 합성기를 인에이블하는 단계;

상기 수신기가 디스에이블된 이후 또는 상기 수신기가 디스에이블될 때 상기 제1 주파수 합성기를 디스에이블하는 단계;

상기 송신기가 인에이블되기 이전에 상기 제2 주파수 합성기를 인에이블하는 단계; 및

상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 상기 제2 주파수 합성기를 디스에이블하는 단계

를 더 포함하는, 국부 발진기 신호들을 생성하는 방법.

#### 청구항 24

제17항에 있어서,

상기 수신기가 인에이블되기 이전에 상기 제1 및 제2 주파수 합성기들을 인에이블하는 단계;

상기 수신기가 디스에이블된 이후 또는 상기 수신기가 디스에이블될 때 상기 제1 주파수 합성기를 디스에이블하는 단계; 및

상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 상기 제2 주파수 합성기를 디스에이블하는 단계를 더 포함하는, 국부 발진기 신호들을 생성하는 방법.

#### 청구항 25

제17항에 있어서,

상기 송신기가 인에이블되기 이전에 상기 제1 및 제2 주파수 합성기들을 인에이블하는 단계를 더 포함하는, 국부 발진기 신호들을 생성하는 방법.

#### 청구항 26

제17항에 있어서,

상기 수신기가 인에이블되기 이전에 상기 제1 및 제2 주파수 합성기들을 인에이블하는 단계; 및

상기 수신기가 디스에이블된 이후 또는 상기 수신기가 디스에이블될 때 상기 제1 및 제2 주파수 합성기들을 디스에이블하는 단계를 더 포함하는, 국부 발진기 신호들을 생성하는 방법.

#### 청구항 27

제17항에 있어서,

상기 송신기가 인에이블되기 이전에 상기 제1 및 제2 주파수 합성기들을 인에이블하는 단계; 및

상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 상기 제1 및 제2 주파수 합성기들을 디스에이블하는 단계를 더 포함하는, 국부 발진기 신호들을 생성하는 방법.

#### 청구항 28

제17항에 있어서,

상기 제1 발진기 신호를 생성하는 단계는:

상기 수신기가 인에이블될 때 타겟 발진기 주파수에서 상기 제1 발진기 신호를 생성하는 단계; 및

상기 송신기가 인에이블될 때 상기 타겟 발진기 주파수로부터의 오프셋에서 상기 제1 발진기 신호를 생성하는 단계를 포함하는, 국부 발진기 신호들을 생성하는 방법.

#### 청구항 29

무선 통신을 위한 장치로서,

제1 발진기 주파수에서 제1 발진기 신호를 생성하기 위한 수단;

상기 제1 발진기 신호에 기초하여 수신기에 대해 국부 발진기(LO) 주파수에서 제1 LO 신호를 생성하기 위한 수단;

시분할 모드에서 동작할 때 상기 제1 발진기 주파수와는 상이한 제2 발진기 주파수에서 제2 발진기 신호를 생성하기 위한 수단;

상기 제2 발진기 신호에 기초하여 송신기에 대해 상기 LO 주파수에서 제2 LO 신호를 생성하기 위한 수단;

데이터 슬롯의 미드앰블 내에서 상기 제1 및 제2 주파수 합성기들 중 적어도 하나를 인에이블하기 위한 수단; 및

상기 데이터 슬롯의 미드앰블에서, 상기 데이터 슬롯의 다른 부분들에서 사용되는 변조 속도보다 더 낮은 변조 속도를 사용하기 위한 수단을 포함하는, 무선 통신을 위한 장치.

### 청구항 30

제29항에 있어서,

상기 시분할 모드는 TDD(time division duplex) 모드 및 TD-SCDMA(time division synchronous code division multiple access) 모드 중 하나인, 무선 통신을 위한 장치.

### 청구항 31

제30항에 있어서,

상기 TDD 모드는 LTE(long term evolution) TDD 모드인, 무선 통신을 위한 장치.

### 청구항 32

제30항에 있어서,

상기 TDD 모드에서 제1 시간 구간들 동안 상기 수신기를 인에이블하기 위한 수단; 및

상기 TDD 모드에서 제2 시간 구간들 동안 상기 송신기를 인에이블하기 위한 수단을 더 포함하는, 무선 통신을 위한 장치.

### 청구항 33

제29항에 있어서,

상기 제1 발진기 주파수는 상기 LO 주파수의 정수배이고, 상기 제2 발진기 주파수는 상기 LO 주파수의 비-정수 배인, 무선 통신을 위한 장치.

### 청구항 34

제29항에 있어서,

상기 제1 발진기 주파수는 상기 LO 주파수의 비-정수배이고, 상기 제2 발진기 주파수는 상기 LO 주파수의 정수 배인, 무선 통신을 위한 장치.

### 청구항 35

제29항에 있어서,

상기 수신기가 인에이블되기 이전에 상기 제1 발진기 신호를 생성하기 위한 수단을 인에이블하기 위한 수단;

상기 수신기가 디스에이블된 이후 또는 상기 수신기가 디스에이블될 때 상기 제1 발진기 신호를 생성하기 위한 수단을 디스에이블하기 위한 수단;

상기 송신기가 인에이블되기 이전에 상기 제2 발진기 신호를 생성하기 위한 수단을 인에이블하기 위한 수단; 및

상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 상기 제2 발진기 신호를 생성하기 위한 수단;

수단을 디스에이블하기 위한 수단을 더 포함하는, 무선 통신을 위한 장치.

### 청구항 36

제29항에 있어서,

상기 수신기가 인에이블되기 이전에 상기 제1 발진기 신호를 생성하기 위한 수단 및 상기 제2 발진기 신호를 생성하기 위한 수단을 인에이블하기 위한 수단;

상기 수신기가 디스에이블된 이후 또는 상기 수신기가 디스에이블될 때 상기 제1 발진기 신호를 생성하기 위한 수단을 디스에이블하기 위한 수단; 및

상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 상기 제2 발진기 신호를 생성하기 위한 수단을 디스에이블하기 위한 수단을 더 포함하는, 무선 통신을 위한 장치.

### 청구항 37

제29항에 있어서,

상기 송신기가 인에이블되기 이전에 상기 제1 및 제2 주파수 합성기들을 인에이블하기 위한 수단을 더 포함하는, 무선 통신을 위한 장치.

### 청구항 38

제29항에 있어서,

상기 수신기가 인에이블되기 이전에 상기 제1 발진기 신호를 생성하기 위한 수단 및 상기 제2 발진기 신호를 생성하기 위한 수단을 인에이블하기 위한 수단; 및

상기 수신기가 디스에이블된 이후 또는 상기 수신기가 디스에이블될 때 상기 제1 발진기 신호를 생성하기 위한 수단 및 상기 제2 발진기 신호를 생성하기 위한 수단을 디스에이블하기 위한 수단을 더 포함하는, 무선 통신을 위한 장치.

### 청구항 39

제29항에 있어서,

상기 송신기가 인에이블되기 이전에 상기 제1 및 제2 주파수 합성기들을 인에이블하기 위한 수단; 및

상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 상기 제1 및 제2 주파수 합성기들을 디스에이블하기 위한 수단을 더 포함하는, 무선 통신을 위한 장치.

### 청구항 40

제29항에 있어서,

상기 제1 발진기 신호를 생성하기 위한 수단은:

상기 수신기가 인에이블될 때 타겟 발진기 주파수에서 상기 제1 발진기 신호를 생성하기 위한 수단; 및

상기 송신기가 인에이블될 때 상기 타겟 발진기 주파수로부터의 오프셋에서 상기 제1 발진기 신호를 생성하기 위한 수단을 포함하는, 무선 통신을 위한 장치.

### 청구항 41

컴퓨터-판독가능한 저장 매체로서,

적어도 하나의 프로세서로 하여금, 제1 주파수 합성기를 이용하여 제1 발진기 주파수에서 제1 발진기 신호의 생성을 지시하게 하기 위한 코드 – 상기 제1 발진기 신호는 수신기에 대해 국부 발진기(L0) 주파수에서 제1 L0 신호를 생성하기 위해 사용됨 –; 및

상기 적어도 하나의 프로세서로 하여금, 제2 주파수 합성기를 이용하여 제2 발진기 주파수에서 제2 발진기 신호의 생성을 지시하게 하기 위한 코드 – 상기 제2 발진기 신호는 송신기에 대해 상기 L0 주파수에서 제2 L0 신호를 생성하기 위해 사용되고, 상기 제2 발진기 신호 주파수는 시분할 모드에서 동작할 때 상기 제1 발진기 주파

수와는 상이함 –;

상기 적어도 하나의 프로세서로 하여금, 데이터 슬롯의 미드앰블 내에서 상기 제1 및 제2 주파수 합성기들 중 적어도 하나를 인에이블하게 하기 위한 코드; 및

상기 적어도 하나의 프로세서로 하여금, 상기 데이터 슬롯의 미드앰블에서, 상기 데이터 슬롯의 다른 부분들에서 사용되는 변조 속도보다 더 낮은 변조 속도를 사용하게 하기 위한 코드를 포함하는, 컴퓨터-판독가능한 저장 매체.

#### 청구항 42

제41항에 있어서,

상기 시분할 모드는 TDD(time division duplex) 모드 및 TD-SCDMA(time division synchronous code division multiple access) 모드 중 하나인, 컴퓨터-판독가능한 저장 매체.

#### 청구항 43

제42항에 있어서,

상기 적어도 하나의 프로세서로 하여금, 상기 TDD 모드에서 제1 시간 구간들 동안 상기 수신기를 인에이블하게 하기 위한 코드; 및

상기 적어도 하나의 프로세서로 하여금, 상기 TDD 모드에서 제2 시간 구간들 동안 상기 송신기를 인에이블하게 하기 위한 코드를 더 포함하는, 컴퓨터-판독가능한 저장 매체.

#### 청구항 44

제42항에 있어서,

상기 TDD 모드는 LTE(long term evolution) TDD 모드인, 컴퓨터-판독가능한 저장 매체.

#### 청구항 45

제41항에 있어서,

상기 적어도 하나의 프로세서로 하여금, 상기 수신기가 인에이블되기 이전에 상기 제1 주파수 합성기를 인에이블하게 하기 위한 코드;

상기 적어도 하나의 프로세서로 하여금, 상기 수신기가 디스에이블된 이후 또는 상기 수신기가 디스에이블될 때 상기 제1 주파수 합성기를 디스에이블하게 하기 위한 코드;

상기 적어도 하나의 프로세서로 하여금, 상기 송신기가 인에이블되기 이전에 상기 제2 주파수 합성기를 인에이블하게 하기 위한 코드; 및

상기 적어도 하나의 프로세서로 하여금, 상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 상기 제2 주파수 합성기를 디스에이블하게 하기 위한 코드를 더 포함하는, 컴퓨터-판독가능한 저장 매체.

#### 청구항 46

제41항에 있어서,

상기 적어도 하나의 프로세서로 하여금, 상기 송신기가 인에이블되기 이전에 상기 제1 및 제2 주파수 합성기들을 인에이블하게 하기 위한 코드를 더 포함하는, 컴퓨터-판독가능한 저장 매체.

#### 청구항 47

제41항에 있어서,

상기 적어도 하나의 프로세서로 하여금, 상기 송신기가 인에이블되기 이전에 상기 제1 및 제2 주파수 합성기들을 인에이블하게 하기 위한 코드; 및

상기 적어도 하나의 프로세서로 하여금, 상기 송신기가 디스에이블된 이후 또는 상기 송신기가 디스에이블될 때 상기 제1 및 제2 주파수 합성기들을 디스에이블하게 하기 위한 코드를 더 포함하는, 컴퓨터-판독가능한 저장 매체.

체.

#### 청구항 48

삭제

#### 청구항 49

삭제

#### 청구항 50

삭제

#### 청구항 51

삭제

### 발명의 설명

#### 기술 분야

[0001] 이 출원은 "FREQUENCY SYNTHESIZER ARCHITECTURE FOR A WIRELESS DEVICE"란 명칭으로 2012년 3월 1일에 출원된 미국 가특허 출원 번호 제61/605,285호에 관한 것이며, 이를 우선권으로 주장한다.

[0002] 본 개시내용은 일반적으로 전자장치에 관한 것이며, 더 구체적으로는 무선 디바이스에 대한 주파수 합성기 아키텍처에 관한 것이다.

### 배경 기술

[0003] 무선 디바이스(예를 들어, 셀룰러 폰 또는 스마트폰)는 무선 통신 시스템과의 양-방향 통신을 위해 데이터를 전송 및 수신할 수 있다. 무선 디바이스는 데이터 전송을 위한 송신기 및 데이터 수신을 위한 수신기를 포함할 수 있다. 데이터 전송을 위해, 송신기는 전송 국부 발진기(LO) 신호를 데이터를 이용하여 변조하여 변조된 라디오 주파수(RF) 신호를 획득하고, 변조된 RF 신호를 증폭하여 적절한 출력 전력 레벨을 가지는 출력 RF 신호를 획득하고, 출력 RF 신호를 안테나를 통해 기지국에 전송할 수 있다. 데이터 수신을 위해, 수신기는 안테나를 통해 수신된 RF 신호를 획득하고, 수신된 RF 신호를 수신 LO 신호를 이용하여 증폭 및 다운컨버팅(downconverter)하고, 다운컨버팅된 신호를 프로세싱하여 기지국에 의해 송신된 데이터를 복원할 수 있다.

[0004] 무선 디바이스는 수신기에 대한 수신 LO 신호 및 송신기에 대한 전송 LO 신호를 생성하기 위한 주파수 합성기를 포함할 수 있다. 주파수 합성기는 수신기 및 송신기의 성능에 대한 큰 영향을 가질 수 있다.

### 발명의 내용

[0005] TDD(time division duplex) 모드에서 동작하는 무선 디바이스에 대한 듀얼 주파수 합성기 아키텍처가 본원에 개시되어 있다. 듀얼 주파수 합성기 아키텍처는 또한 FDD(frequency division duplex) 모드에 대해 사용될 수 있다. TDD에 대해, 다운링크 및 업링크는 동일한 주파수를 공유하고, 2개의 주파수 합성기는 수신기 및 송신기에게 동일한 주파수에서 2개의 LO 신호를 생성하기 위해 사용될 수 있다. FDD에 대해, 다운링크 및 업링크에는 별도의 주파수들이 할당되고, 2개의 주파수 합성기는 수신기와 송신기에 대해 상이한 주파수들에서 2개의 LO 신호들을 생성하기 위해 사용될 수 있다.

[0006] 예시적인 설계에서, 무선 디바이스는 제1 및 제2 주파수 합성기들을 포함한다. 제1 주파수 합성기는 수신기에 대한 LO 주파수에서 제1/수신 LO 신호를 생성하기 위해 사용되는 제1 발진기 신호를 생성한다. 제2 주파수 합성기는 송신기에 대해 동일한 LO 주파수에서 제2/전송 LO 신호를 생성하기 위해 사용되는 제2 발진기 신호를 생성한다. 예를 들어, 각각의 발진기 신호는 디바이더에 의해 주파수에서 분할되고, 대응하는 LO 신호를 획득하기 위해 버퍼링될 수 있다. 제1 및 제2 주파수 합성기들은 무선 디바이스가 TDD 모드에서 동작할 때 동일한 LO 주파수에서 수신 및 전송 LO 신호들을 획득하기 위해 자신의 발진기 신호들을 생성한다. 제1 및 제2 주파수 합성기들은 무선 디바이스가 FDD 모드에서 동작할 때 상이한 LO 주파수들에서 수신 및 전송 LO 신호들을 획득하기 위해 자신의 발진기 신호들을 생성한다.

[0007] 일 설계에서, 제1 및 제2 주파수 합성기들은 TDD 모드에서 동일한 발진기 주파수에서 제1 및 제2 발진기 신호들을 생성하고, 동일한 주파수 디바이더 비는 동일한 LO 주파수에서 수신 및 전송 LO 신호들을 획득하기 위해 제1 및 제2 발진기 신호들에 대해 사용될 수 있다. 또다른 설계에서, 제1 및 제2 주파수 합성기들은 TDD 모드에서 상이한 발진기 주파수들에서 제1 및 제2 발진기 신호들을 생성하고, 상이한 주파수 디바이더 비들이 동일한 LO 주파수에서 수신 및 전송 LO 신호들을 획득하기 위해 제1 및 제2 발진기 신호들에 대해 사용될 수 있다.

[0008] 일 설계에서, 제1 및 제2 주파수 합성기들은 항상 자신의 타겟 발진기 주파수들에서 동작할 수 있다. 또다른 설계에서, 각각의 주파수 합성기는, 다른 주파수 합성기에 대한 교란을 감소시키기 위해, (i) 자신의 연관된 수신기 또는 송신기가 인에이블될 때 자신의 타겟 발진기 주파수에서, 그리고 (ii) 자신의 연관된 수신기 또는 송신기가 디스에이블될 때 자신의 타겟 발진기 주파수로부터의 오프셋에서 동작할 수 있다. 하기에 설명되는 바와 같이, 제1 및 제2 주파수 합성기들은 다양한 방식들로 인에이블되고 디스에이블될 수 있다.

[0009] TDD 모드에서 수신기 및 송신기에 대해 별도의 주파수 합성기들을 사용하는 것은, 하기에 설명되는 바와 같이, 더 적은 그리고/또는 더 작은 베퍼들, 더 낮은 전력 소모, 덜 복잡한 신호 라우팅, 개선된 성능 등과 같은 다양한 장점들을 제공할 수 있다.

[0010] 개시내용의 다양한 양상들 및 특징들이 하기에 더 상세하게 설명된다.

### 도면의 간단한 설명

[0011] 도 1은 상이한 무선 통신 시스템들과 통신할 수 있는 무선 디바이스를 도시한다.

도 2는 도 1의 무선 디바이스의 블록도를 도시한다.

도 3은 하나의 주파수 합성기를 가지는 트랜시버의 블록도를 도시한다.

도 4는 2개의 주파수 합성기들을 가지는 트랜시버의 블록도를 도시한다.

도 5는 주파수 합성기의 블록도를 도시한다.

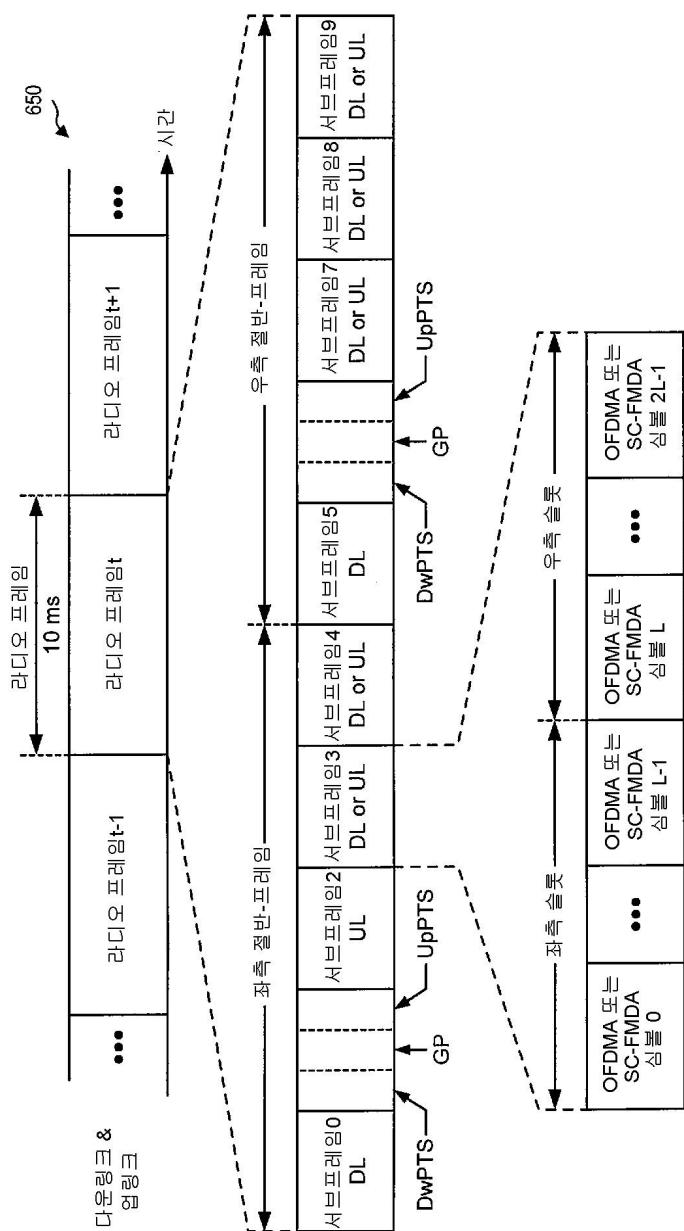

도 6a 및 6b는 2개의 무선 시스템들에 대한 2대의 프레임 구조들을 도시한다.

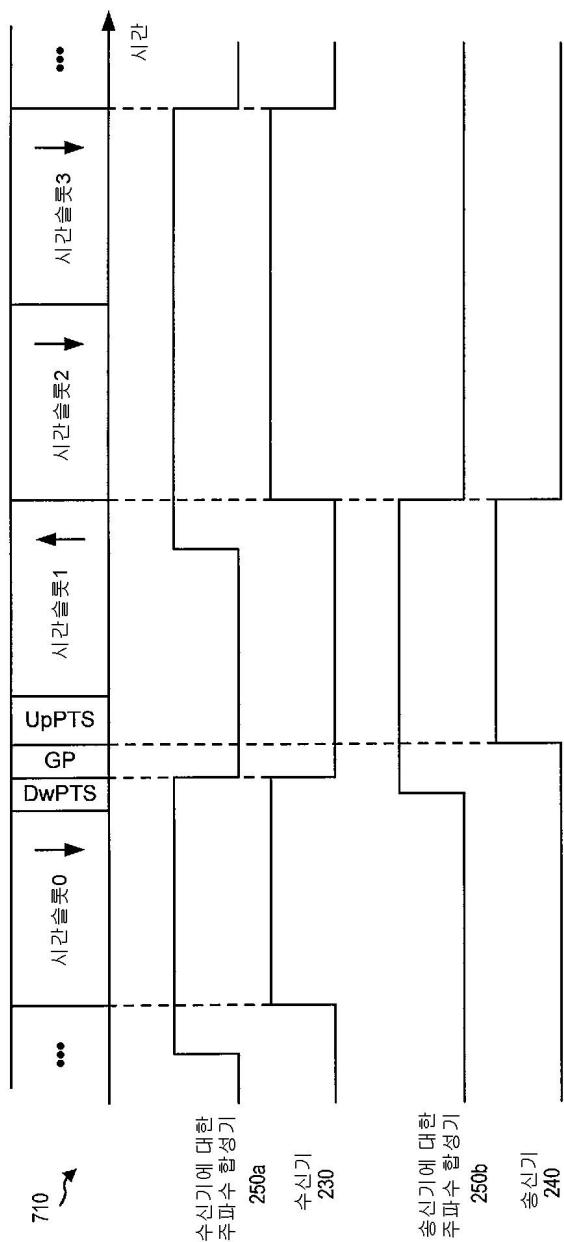

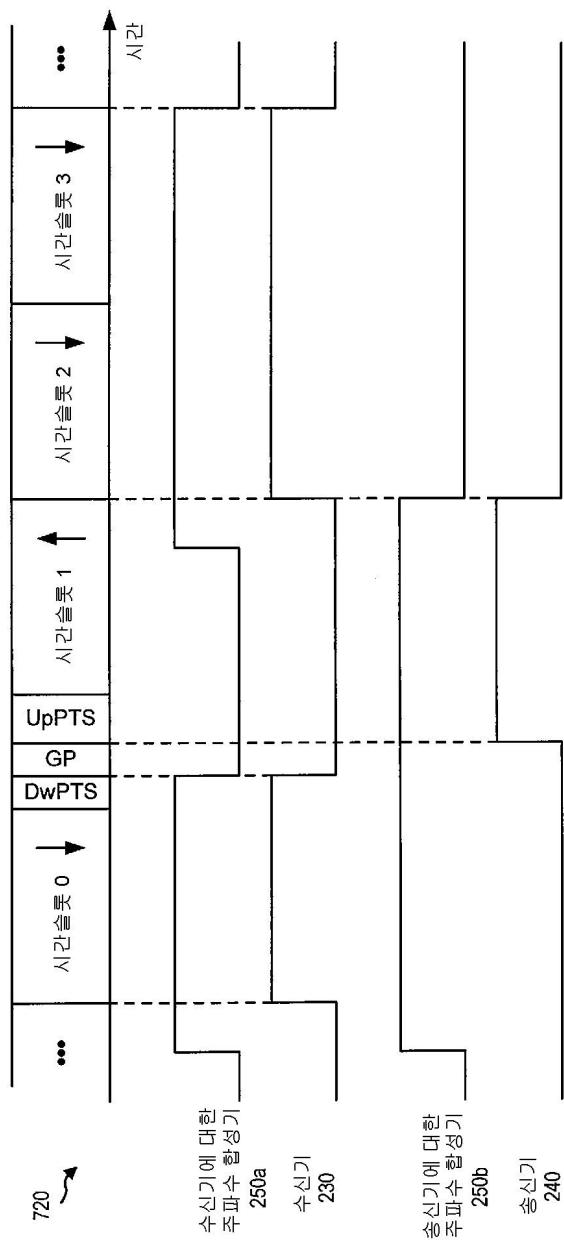

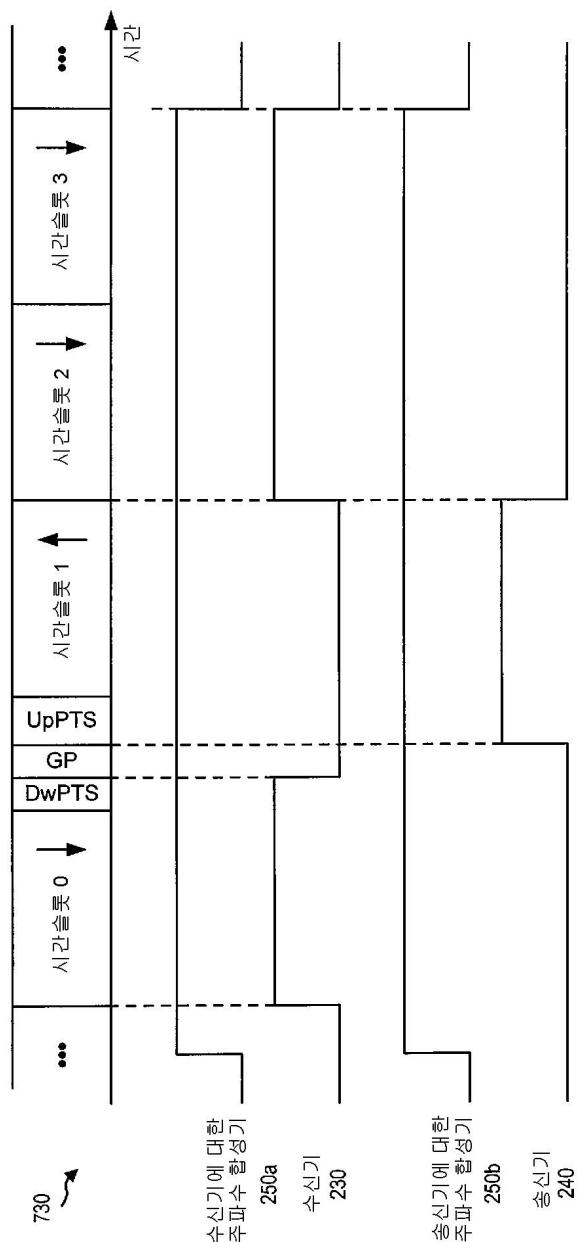

도 7a 내지 7d는 2개의 주파수 합성기들에 대한 4개의 파워-온 시퀀스들을 도시한다.

도 8은 LO 신호들을 생성하기 위한 프로세스를 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0012] 도 1은 상이한 무선 통신 시스템들(120 및 122)과 통신할 수 있는 무선 디바이스(110)를 도시한다. 무선 시스템들(120 및 122)은 각각 CDMA(Code Division Multiple Access) 시스템, GSM(Global System for Mobile Communications) 시스템, LTE(Long Term Evolution) 시스템, WLAN(wireless local area network) 시스템, 또는 일부 다른 무선 시스템일 수 있다. 예를 들어, 무선 시스템들(120 및 122)은 LTE 시스템일 수 있고, LTE FDD(frequency division duplexing) 또는 LTE TDD(time division duplexing)를 포함할 수 있다. 예를 들어, 시스템은 LTE TDD 시스템일 수 있다. CDMA 시스템은 TD-SCDMA(Time Division Synchronous Code Division Multiple Access), WCDMA(Wideband CDMA), cdma2000, 또는 CDMA의 일부 다른 버전을 구현할 수 있다. TD-SCDMA는 또한 UTRA(Universal Terrestrial Radio Access) TDD(Time Division Duplex) 1.28 Mcps 옵션 또는 LCR(Low Chip Rate)로서 지정된다. 간략함을 위해, 도 1은 하나의 기지국(130)과 하나의 시스템 제어기(140)를 포함하는 무선 시스템(120), 및 하나의 기지국(132)과 하나의 시스템 제어기(142)를 포함하는 무선 시스템(122)을 도시한다. 일반적으로, 각각의 무선 시스템은 임의의 개수의 기지국들 및 네트워크 엔티티들의 임의의 세트를 포함할 수 있다.

[0013] 무선 디바이스(110)는 또한 UE(user equipment), 이동국, 단말, 액세스 단말, 가입자 유닛, 스테이션 등으로서 지칭될 수 있다. 무선 디바이스(110)는 셀룰러 폰, 스마트 폰, 태블릿, 무선 모뎀, PDA(personal digital assistant), 핸드헬드 디바이스, 랩톱 컴퓨터, 스마트북, 넷북, 코드리스 폰, WLL(wireless local loop) 스테이션, 블루투스 디바이스 등일 수 있다. 무선 디바이스(110)는 무선 시스템(120 및/또는 122)과 통신할 수도 있다. 무선 디바이스(110)는 또한 방송국들(예를 들어, 방송국(134))로부터 신호들을 수신할 수도 있다. 무선 디바이스(110)는 또한 하나 이상의 GNSS(global navigation satellite systems)에서 위성들(예를 들어, 위성(150))로부터 신호들을 수신할 수도 있다. 무선 디바이스(110)는 LTE, TD-SCDMA, WCDMA, cdma2000, GSM,

802.11 등과 같은 무선 통신에 대한 하나 이상의 라디오 기술들을 지원할 수 있다.

[0014] 무선 디바이스(110)는 다운링크 및 업링크를 통해 무선 시스템(120)에서, 기지국(130, 132)과 통신할 수 있다. 다운링크(또는 순방향 링크)는 기지국으로부터 무선 디바이스로의 통신 링크를 지칭하고, 업링크(또는 역방향 링크)는 무선 디바이스로부터 기지국으로의 통신 링크를 지칭한다.

[0015] 무선 시스템은 TDD 또는 FDD를 활용할 수 있다. TDD에 대해, 다운링크 및 업링크는 동일한 주파수를 공유하고, 다운링크 전송들 및 업링크 전송들은 상이한 시간 기간들에서 동일한 주파수 상에서 송신될 수 있다. FDD에 대해, 다운링크 및 업링크에는 별도의 주파수들이 할당된다. 다운링크 전송들은 하나의 주파수 상에서 송신될 수 있고, 업링크 전송들은 또 다른 주파수에서 송신될 수 있다. TDD를 지원하는 라디오 기술들의 일부 예들은 LTE TDD, TD-SCDMA, GSM 등을 포함한다. FDD를 지원하는 라디오 기술들의 일부 예들은 LTE FDD, WCDMA, cdma2000 등을 포함한다.

[0016] 도 2는 도 1의 무선 디바이스(110)의 예시적인 설계의 블록도를 도시한다. 이러한 예시적인 설계에서, 무선 디바이스(110)는 안테나(210)에 커플링된 트랜시버(220), 주파수 합성기들(250a 및 250b), 및 데이터 프로세서/제어기(280)를 포함한다. 트랜시버(220)는 다수의 주파수 대역들, 다수의 라디오 기술들 등을 지원하기 위해 다수(K)의 수신기들(230a 내지 230k) 및 다수(K)의 송신기들(240a 내지 240k)을 포함한다.

[0017] 도 2에 도시된 예시적인 설계에서, 각각의 수신기(230)는 입력 회로(232), 저잡음 증폭기(LNA)(234), 및 수신 회로(236)를 포함한다. 데이터 수신을 위해, 안테나(210)는 기지국들 및/또는 다른 송신기 스테이션들로부터 신호들을 수신하고, 스위치플렉서/듀플렉서(222)를 통해 라우팅되어 선택된 수신기에 제공되는 수신된 RF 신호를 제공한다. 하기의 설명은, 수신기(230a)가 선택된 수신기라고 가정한다. 수신기(230a) 내에서, 수신된 RF 신호는 입력 회로들(232a)을 통하여 LNA(234a)에 제공된다. 입력 회로들(232a)은 수신 필터, 임피던스 매칭 회로 등을 포함할 수 있다. LNA(234a)는 입력 회로들(232a)로부터 수신된 RF 신호를 증폭시키고, 증폭된 RF 신호를 제공한다. 수신 회로들(236a)은 증폭된 RF 신호를 증폭시키고, 필터링하고 RF에서 베이스밴드로 다운컨버팅하고, 아날로그 입력 신호를 데이터 프로세서(280)에 제공한다. 수신 회로들(236a)은 증폭기들, 필터들, 믹서들, 임피던스 매칭 회로들 등을 포함할 수 있다. 트랜시버(220) 내의 각각의 나머지 수신기(230)는 수신기(230a)와 유사한 방식으로 동작할 수 있다.

[0018] 도 2에 도시된 예시적인 설계에서, 각각의 송신기(240)는 전송 회로들(242a-k), 전력 증폭기들(PA)(244a-k), 및 출력 회로들(246a-k)을 포함한다. 데이터 전송을 위해, 데이터 프로세서(280)는 전송될 데이터를 프로세싱(예를 들어, 인코딩 및 변조)하고, 아날로그 출력 신호를 선택된 송신기에 제공한다. 하기 설명은 송신기(240a)가 선택된 송신기라고 가정한다. 송신기(240a) 내에서, 전송 회로(242a)는 아날로그 출력 신호를 증폭시키고, 필터링하고, 베이스밴드에서 RF로 업컨버팅(upconvert)하고, 변조된 RF 신호를 제공한다. 전송 회로들(242a)은 증폭기들, 필터들, 믹서들, 임피던스 매칭 회로들 등을 포함할 수 있다. 전력 증폭기(244a)는 변조된 RF 신호를 수신하고 증폭시켜서, 적절한 출력 전력 레벨을 가지는 증폭된 신호를 제공한다. 증폭된 신호는 출력 회로들(246a)을 통하여, 스위치플렉서/듀플렉서(222)를 통해 라우팅되어, 안테나(210)를 통해 전송된다. 출력 회로(246a)는 전송 필터, 임피던스 매칭 회로, 지향성 커플러, 듀플렉서 등을 포함할 수 있다.

[0019] 주파수 합성기들(250a 및 250b)은 수신기들(230) 및 송신기들(240)에 대한 L0 신호들을 생성한다. 각각의 주파수 합성기(250)는 VCO(voltage-controlled oscillator), PLL(phase locked loop), 베피들 등을 포함할 수 있다.

[0020] 도 2는 수신기들(230) 및 송신기들(240)의 예시적인 설계를 도시한다. 수신기 및 송신기는 또한 필터들, 임피던스 매칭 회로들 등과 같은, 도 2에 도시되지 않은 다른 회로들을 포함할 수 있다. 트랜시버(220)의 전부 또는 일부가 하나 이상의 아날로그 IC(integrated circuit)들, RF IC(RFIC)들, 믹스된-신호 IC들 등에서 구현될 수 있다. 예를 들어, LNA들(234), 수신 회로들(236a-k), 및 전송 회로들(242)은 RFIC 등일 수 있는 하나의 회로 모듈에서 구현될 수 있다. 스위치플렉서/듀플렉서(222), 입력 회로들(232a-k), 출력 회로들(246a-k) 및 전력 증폭기들(244a-k)은 하이브리드 모듈 등일 수 있는 또 다른 회로 모듈에서 구현될 수 있다. 수신기들(230) 및 송신기들(240) 내의 회로들은 또한 다른 방식들로 구현될 수 있다.

[0021] 데이터 프로세서/제어기(280)는 무선 디바이스(110)에 대한 다양한 기능들을 수행할 수 있다. 예를 들어, 데이터 프로세서(280)는 수신기들(230)을 통해 수신되는 데이터 및 송신기들(240)을 통해 전송되는 데이터에 대한 프로세싱을 수행할 수 있다. 제어기(280)는 스위치플렉서/듀플렉서(222), 입력 회로들(232), LNA들(234), 수신 회로들(236), 전송 회로들(242), 전력 증폭기들(244), 출력 회로들(246), 주파수 합성기들(250), 또는 이들의

결합의 동작을 제어할 수 있다. 메모리(282)는 데이터 프로세서/제어기(280)에 대한 프로그램 코드들 및 데이터를 저장할 수 있다. 데이터 프로세서/제어기(280)는 하나 이상의 ASIC(application specific integrated circuit)들 및/또는 다른 IC들에서 구현될 수 있다.

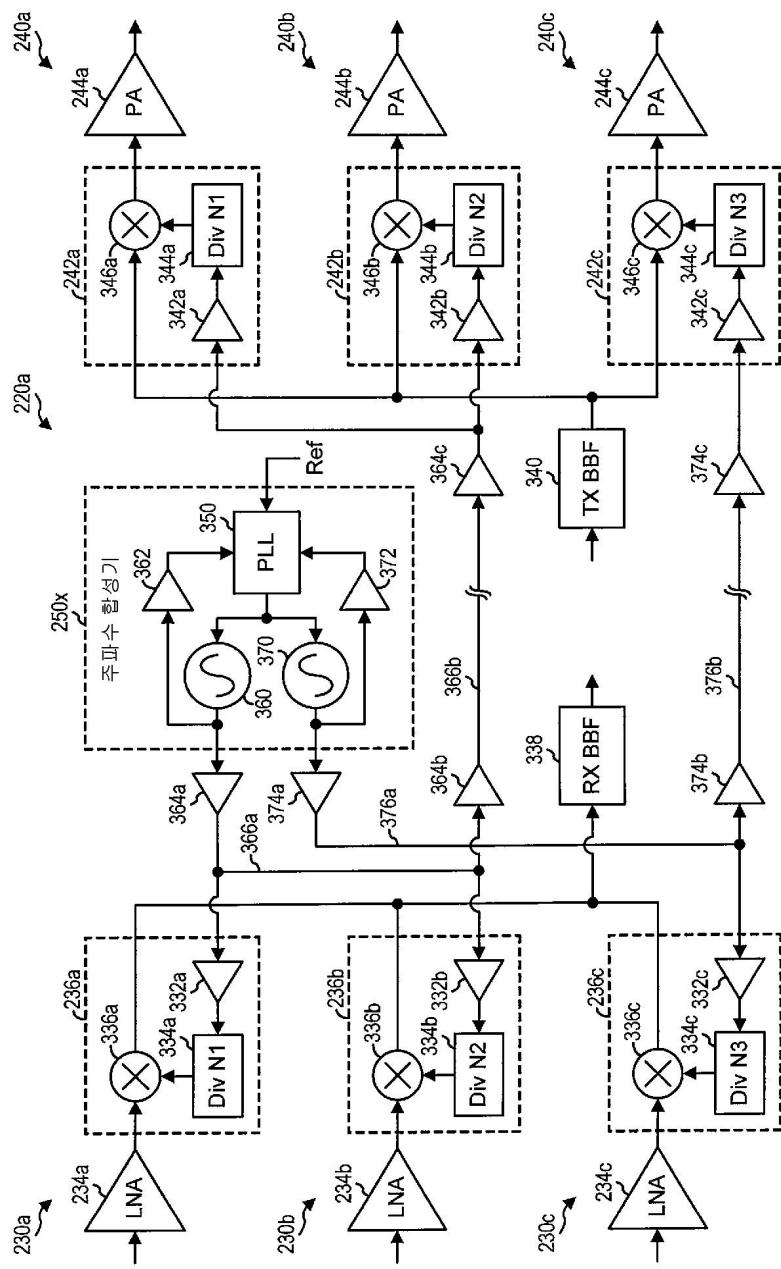

[0022] 도 3은 단일 주파수 합성기(250x)를 통해 TDD를 지원하는 트랜시버(220a)의 블록도를 도시한다. 트랜시버(220a)는 도 2의 트랜시버(220)의 일 예시적인 설계이다. 트랜시버(220a)는 (i) 저 대역에 대한 수신기(230a) 및 송신기(240a), (ii) 중간 대역에 대한 수신기(230b) 및 송신기(240b), 및 (iii) 고 대역에 대한 수신기(230c) 및 송신기(240c)를 포함한다. 각각의 대역은 주파수들의 특정 범위를 커버한다.

[0023] 각각의 수신기(230)는 수신 회로들(236)에 커플링된 LNA(234)를 포함한다. 수신 회로들(236)은 버퍼(332), 주파수 디바이더(334), 및 다운컨버터(336)를 포함한다. 저 대역에 대해, 버퍼(332a)는 저 대역에 대한 VCO 신호를 수신하고 버퍼링하여, 버퍼링된 VCO 신호를 제공한다. 디바이더(334a)는 버퍼링된 VCO 신호를 주파수에서 N의 인자로 분할하여, 저 대역에 대한 수신 LO 신호를 제공하며, 여기서 N은 임의의 값(예를 들어, 정수 또는 소수 값)일 수 있다. N의 값은 각각의 수신 회로(236)에 대해 상이할 수 있다. 예를 들어, 디바이더(334a)는 N1의 인자로 분할될 수 있고, 디바이더(334b)는 N2의 인자로 분할될 수 있고, 디바이더(334c)는 N3의 인자로 분할될 수 있다. 다운컨버터(336)는 LNA(234a)로부터의 입력 RF 신호를 디바이더(334a)로부터의 수신 LO 신호를 이용하여 다운컨버팅하여, 다운컨버팅된 신호를 제공한다. 수신 베이스밴드 필터(RX BBF)(338)는 다운컨버팅된 신호를 필터링하여 아날로그 입력 신호를 제공한다. 일부 구성들에서, 수신 베이스밴드 필터(338)는 저대역 통과 필터(LPF)를 포함한다. 중간 대역 및 고대역에 대한 수신 회로들(236b 및 236c)은 저 대역에 대한 수신 회로들(236a)과 유사한 방식으로 동작한다. 베이스밴드 필터(338)는 수신 회로들(236a, 236b 및 236c)의 출력들에 커플링되고, 이를 수신 회로들(230)에 의해 공유된다.

[0024] 각각의 송신기(240)는 전력 증폭기(244)에 커플링된 전송 회로들(242)을 포함한다. 전송 회로들(242)은 버퍼(342), 주파수 디바이더(344), 및 업컨버터(346)를 포함한다. 전송 베이스밴드 필터(TX BBF)(340)는 전송 회로들(242a, 242b 및 242c)의 입력들에 커플링되고, 이를 전송 회로들에 의해 공유된다. 일부 구성들에서, 전송 베이스밴드 필터(340)는 저대역 통과 필터(LPF)를 포함한다. 베이스밴드 필터(340)는 아날로그 출력 신호를 수신하고 필터링한다. 저 대역에 대해, 버퍼(342a)는 저 대역에 대한 VCO 신호를 수신하고 버퍼링하여, 버퍼링된 VCO 신호를 제공한다. 디바이더(344a)는 버퍼링된 VCO 신호를 주파수에서 N의 인자로 분할하고, 저 대역에 대한 전송 LO 신호를 제공한다. N의 값은 각각의 전송 회로(242)에 대해 상이할 수 있다. 예를 들어, 디바이더(344a)는 N1의 인자로 분할될 수 있고, 디바이더(344b)는 N2의 인자로 분할될 수 있고, 디바이더(344c)는 N3의 인자로 분할될 수 있다. 업컨버터(346a)는 베이스밴드 필터(340)로부터의 필터링된 신호를 디바이더(344a)로부터의 전송 LO 신호를 이용하여 업컨버팅하여, 변조된 RF 신호를 제공한다. 전력 증폭기(244a)는 변조된 RF 신호를 증폭하여, 저 대역에 대한 증폭된 RF 신호를 제공한다. 중간 대역 및 고 대역에 대한 전송 회로들(242b 및 242c)은 저 대역에 대한 전송 회로들(242a)과 유사한 방식으로 동작한다.

[0025] 도 3에 도시된 예시적인 설계에서, 단일 주파수 합성기(250x)는 수신기들(230) 및 송신기들(240) 모두에 대한 VCO 신호들을 생성한다. 주파수 합성기(250x) 내에서, VCO(360)는 저 대역 또는 중간 대역 중 어느 하나에 대한 제1 VCO 신호를 생성하고, 버퍼(362)는 제1 VCO 신호를 버퍼링한다. VCO(370)는 고 대역에 대한 제2 VCO 신호를 생성하고, 버퍼(372)는 제2 VCO 신호를 버퍼링한다. PLL(350)은 버퍼(362)로부터 버퍼링된 제1 VCO 신호를, 버퍼(372)로부터 버퍼링된 제2 VCO 신호를, 그리고 기준 주파수에서 기준(Ref) 신호를 수신한다. PLL(350)은 제1 VCO 신호가 저 대역 또는 중간 대역에서 타겟 VCO 주파수에 있도록 VCO(360)에 대한 제1 제어 신호를 생성한다. PLL(350)은 또한 제2 VCO 신호가 고 대역에서 타겟 VCO 주파수에 있도록 VCO(370)에 대한 제2 제어 신호를 생성한다. PLL(350)에 의해 생성된 제어 신호는 동시적이지 않을 수 있다. 다시 말해, 타겟 주파수가 저/중간 대역들에 있을 때, 제1 제어 신호만 생성될 수 있다. 타겟 주파수가 고 대역에 있을 때, 제2 제어 신호만 생성될 수 있다. 버퍼들(364)은 저 대역 및 중간 대역에 대한 제1 VCO 신호를 버퍼링하고 구동하며, 제1 VCO 신호에 대한 라우팅 트레이스(366)를 따라 위치될 수 있다. 버퍼들(374)은 고 대역에 대한 제2 VCO 신호를 버퍼링하고 구동하며, 제2 VCO 신호에 대한 라우팅 트레이스(376)를 따라 위치될 수 있다.

[0026] 도 3은 주파수 합성기(250x)의 예시적인 설계를 도시한다. 주파수 합성기는 또한 다른 방식들로 구현될 수 있다. 예를 들어, 별도의 VCO가 각각의 대역에 대해 사용될 수 있다. VCO들(360 및 370)은 또한 ICO(current-controlled oscillators), NCO(numerically controlled oscillators) 등으로 대체될 수 있다.

[0027] 도 3에 도시된 예시적인 설계에서, 단일 주파수 합성기(250x)는 수신기들(230) 및 송신기들(240) 모두에 대한 VCO 신호들을 생성하기 위해 사용된다. 저 대역 또는 중간 대역이 선택될 때, VCO(360)는 수신기(230a) 또는

230b) 및 송신기(240a 또는 240b)에 대한 제1 VCO 신호를 생성한다. 고 대역이 선택될 때, VCO(370)는 수신기(230c) 및 송신기(240c)에 대한 제2 VCO 신호를 생성한다.

[0028] 수신기들(230)에 대한 회로들은 송신기들(240)로부터 수신기들(230)로의 커플링을 감소시키기 위해 송신기들(240)에 대한 회로들로부터 가능한 멀리 위치될 수 있다. 주파수 합성기(250x)는 수신기들(230)에 가까이 그리고 송신기들(240)로부터 상대적으로 멀리 위치될 수 있다. VCO들(360 및 370)로부터의 VCO 신호들은 긴 라우팅 트레이스들(366 및 376)을 통해 송신기들(240)에 제공될 수 있다. 베피들(364 및 374)은 라우팅 트레이스들(366 및 376)을 따라 규칙적 간격으로 배치되며, VCO 신호들에 대한 신호 구동을 제공하기 위해 사용될 수 있다.

[0029] 수신기들(230) 및 송신기들(240) 모두에 대한 단일 주파수 합성기(250x)의 사용은 여러 단점들을 가질 수 있다. 먼저, VCO 신호들에 대한 라우팅 트레이스들(366 및 376)은 복잡하며 길 수 있다. 베피들(364 및 374)은 이들 라우팅 트레이스들을 따라 VCO 신호들을 구동하기 위해 라우팅 트레이스들(366 및 376)을 따라 배치될 수 있다. 베피들(364 및 374)은 수신기들(230) 및 송신기들(240) 모두에 대한 VCO 신호들의 신호 충실도를 보존하기 위해 클 수 있고, 따라서, 다운컨버터들(336) 및 업컨버터들(346)에서의 LO 신호들은 양호한 파형을 가질 수 있다. 큰 베피들(364 및 374)은 대량의 전류를 소모할 수 있고, 또한, 큰 영역을 점유할 수 있는데, 이들 모두는 바람직하지 않다. 또한, 베피들(364 및 374)에 대한 전력 그리드들은 복잡할 수 있고, 파라스틱들(parasitics)이 클 수 있다. 이는 심지어 FDD 모드에서도 수신기들(230)과 송신기들(240) 사이에 더 큰 커플링을 초래할 수 있다.

[0030] 둘째, 송신기들(240)의 성능은 송신기들(230) 및 수신기들(240) 모두에 대한 단일 주파수 합성기(250x)의 사용으로 인해 저하될 수 있다. 송신기들(240)에 대한 VCO 신호들에 대한 긴 라우팅 트레이스들(366 및 376)은 미스매치의 경향이 더 클 수 있다. 송신기들(240)에 대한 잔류 측파대(RSB)는 긴 라우팅 트레이스들(366 및 376)의 열악한 매칭으로 인해 열악할 수 있다. 수신기들(230)에 대한 주파수 합성기들(250x)의 더 가까운 배치는 또한 디바이더들(334)이 인에이블/디스에이블될 때 VCO 풀링(pulling)으로 인해 주파수 합성기(250x)가 디바이더들(334)에 의해 더 쉽게 교란되는 결과를 초래할 수 있다. 이러한 교란은, 예를 들어, TDD 모드에서, 수신 LO 회로들이 디스에이블될 때 업링크 구간의 시작에서 전송 LO 신호에서의 더 큰 위상 에러를 초래할 수 있다.

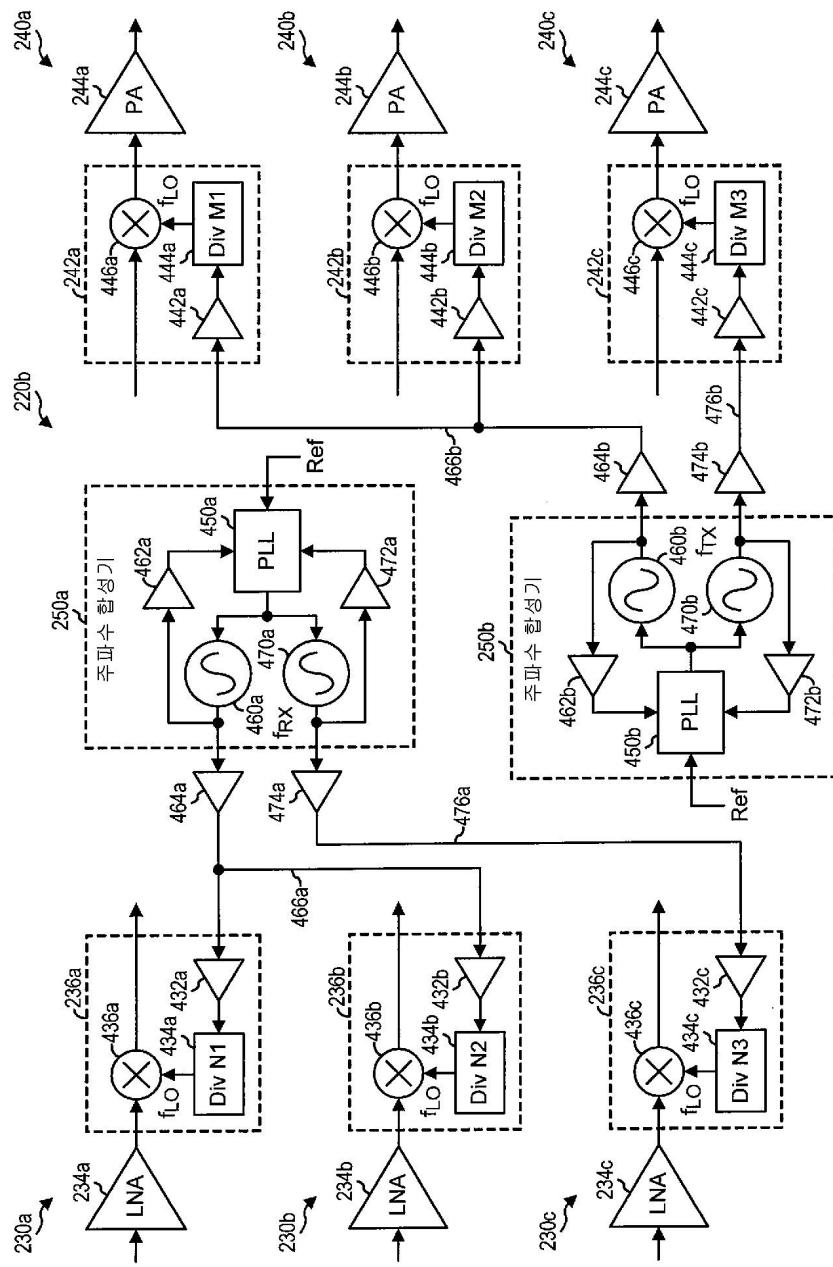

[0031] 도 4는, 2개의 주파수 합성기들(250a 및 250b)을 이용하여 TDD를 지원하는, 트랜시버(220b)의 블록도를 도시한다. 트랜시버(220b)는 도 2에서 트랜시버(220)의 또 다른 예시적인 설계이다. 트랜시버(220b)는 (i) 저 대역에 대한 수신기(230a) 및 송신기(240a), (ii) 중간 대역에 대한 수신기(230b) 및 송신기(240b), 및 (iii) 고 대역에 대한 수신기(230c) 및 송신기(240c)를 포함한다. 각각의 수신기(230)는 수신 회로들(236)에 커플링된 LNA(234)를 포함한다. 수신 회로들(236)은, 도 3의 베피(332a), 주파수 디바이더(334a), 및 다운컨버터(336a)에 대해 전술된 바와 같이 동작할 수 있는, 베피(432), 주파수 디바이더(434), 및 다운컨버터(436)를 포함한다. 각각의 송신기(240)는 전력 증폭기(244)에 커플링된 전송 회로들(242)을 포함한다. 전송 회로들(244)은, 도 3의 베피(342a), 주파수 디바이더(344a), 및 업컨버터(346a)에 대해 전술된 바와 같이 동작할 수 있는, 베피(442), 주파수 디바이더(444), 및 업컨버터(446)를 포함한다.

[0032] 도 4에 도시된 예시적인 설계에서, 주파수 합성기(250a)는 수신기들(230)에 대한 수신 VCO 신호들을 생성하고, 주파수 합성기(250b)는 송신기들(240)에 대한 전송 VCO 신호들을 생성한다. 주파수 합성기(250a)는, 도 3의 VCO들(360 및 370), PLL(350), 및 베피들(362 및 372)에 대해 전술된 것과 유사한 방식으로 동작할 수 있는, 저 대역 또는 중간 대역에 대한 수신 VCO 신호를 생성하는 VCO(460a), 고 대역에 대한 수신 VCO 신호를 생성하는 VCO(470a), VCO들(460a 및 470a)에 대한 제어 신호들을 생성하는 PLL(450a), 베피들(462a 및 472a)을 포함한다. 주파수 합성기(250b)는, 도 3의 VCO들(360 및 370), PLL(350), 및 베피들(362 및 372)에 대해 전술된 것과 유사한 방식으로 동작할 수 있는, 저 대역 또는 중간 대역에 대한 전송 VCO 신호를 생성하는 VCO(460b), 고 대역에 대한 전송 VCO 신호를 생성하는 VCO(470b), VCO들(460b 및 470b)에 대한 제어 신호들을 생성하는 PLL(450b), 및 베피들(462b 및 472b)을 포함한다.

[0033] 베피(464a)는 VCO(460a)로부터의 저 대역 또는 중간 대역에 대한 제1 수신 VCO 신호를 베피링하고 구동한다. 베피(474a)는 VCO(470a)로부터의 고 대역에 대한 제2 수신 VCO 신호를 베피링하고 구동한다. 베피(464b)는 VCO(460b)로부터의 저 대역 또는 중간 대역에 대한 제1 전송 VCO 신호를 베피링하고 구동한다. 베피(474b)는 VCO(470b)로부터의 고 대역에 대한 제2 전송 VCO 신호를 베피링하고 구동한다.

[0034] 도 4는 주파수 합성기들(250a 및 250b)의 예시적인 설계를 도시한다. 주파수 합성기는 또한 전술된 바와 같이, 다른 방식들로 구현될 수 있다.

[0035]

주파수 합성기(250a) 내에서, 어느 하나의 VCO(460a 또는 470a)가 임의의 주어진 순간에 인에이블될 수 있다. 저 대역 또는 중간 대역에서 동작할 때, PLL(450a)은, 제1 수신 VCO 신호가 저 대역 또는 중간 대역에서 타겟 VCO 주파수에 있도록 VCO(460a)에 대한 제어 신호를 생성할 수 있다. 고 대역에서 동작할 때, PLL(450a)은, 제2 수신 VCO 신호가 고 대역에서 타겟 VCO 주파수에 있도록 VCO(470a)에 대한 제어 신호를 생성할 수 있다. 각각의 디바이더(434)는 자신의 수신 VCO 신호를 주파수에서 임의의 적절한 값일 수 있는 N의 인자로 분할할 수 있다. N의 값은 각각의 수신 회로(236)에 대해 상이할 수 있다. 예를 들어, 디바이더(434a)는 N1의 인자로 분할될 수 있고, 디바이더(434b)는 N2의 인자로 분할될 수 있고, 디바이더(434c)는 N3의 인자로 분할될 수 있다. 수신 VCO 신호의 주파수는 다음과 같이 표현될 수 있다:

### 수학식 1

$$f_{RX} = N * f_{LO}$$

[0036]

여기서  $f_{RX}$ 는 수신 VCO 신호의 주파수이고,  $f_{LO}$ 는 LO 주파수, 예를 들어, 수신된 RF 신호의 중심 주파수이다.

[0038]

주파수 합성기(250b) 내에서, 어느 하나의 VCO(460b 또는 470b)가 임의의 주어진 순간에 인에이블될 수 있다. 저 대역 또는 중간 대역에서 동작할 때, PLL(450b)은, 제1 전송 VCO 신호가 저 대역 또는 중간 대역에서 타겟 VCO 주파수에 있도록 VCO(460b)에 대한 제어 신호를 생성할 수 있다. 고 대역에서 동작할 때, PLL(450b)은, 제2 전송 VCO 신호가 고 대역에서 타겟 VCO 주파수에 있도록 VCO(470b)에 대한 제어 신호를 생성할 수 있다. 각각의 디바이더(434)는 자신의 전송 VCO 신호를 주파수에서 임의의 적절한 값일 수 있는 M의 인자로 분할할 수 있다. 전송 VCO 신호의 주파수는 다음과 같이 표현될 수 있다:

### 수학식 2

$$f_{TX} = M * f_{LO}$$

[0039]

여기서,  $f_{TX}$ 는 전송 VCO 신호의 주파수이다.

[0041]

수학식들 (1) 및 (2)에서 보여진 바와 같이, 동일한 LO 주파수  $f_{LO}$ 의 LO 신호들은 TDD 모드에서 수신기들(230) 및 송신기들(240)에 제공될 수 있다. 그러나, 수학식(1)에서의 수신기들(230)에 대한 디바이더 비 N은 수학식(2)에서의 송신기들(240)에 대한 디바이더 비 M과 동일하거나 동일하지 않을 수 있다. 수신기들(230) 및 송신기들(240)에 대한 별도의 주파수 합성기들(250a 및 250b)의 사용은 수신기들(230) 및 송신기들(240)에 대한 동일한 또는 상이한 주파수 디바이더 비들 N 및 M의 사용에 대해 유연성을 허용한다. 하기에 설명되는 바와 같이, 특정 장점들이 수신기들(230) 및 송신기들(240)에 대해 상이한 주파수 디바이더 비들을 사용함으로써 획득될 수 있다.

[0042]

수신기들(230)의 회로들은 송신기들(240)로부터 수신기들(230)로의 커플링을 감소시키기 위해 송신기들(240)에 대한 회로들로부터 가능한 멀리 위치될 수 있다. 주파수 합성기(250a)는 수신기들(230)에 가까이 위치될 수 있고, 주파수 합성기(250b)는 송신기들(240)에 가까이 위치될 수 있다. VCO들(460a 및 470a)로부터의 수신 VCO 신호들은 상대적으로 짧은 라우팅 트레이스들(466a 및 476a)을 통해 수신기들(230)에 제공될 수 있다. 유사하게, VCO들(360b 및 370b)로부터의 전송 VCO 신호들은 상대적으로 짧은 라우팅 트레이스들(466b 및 476b)을 통해 송신기들(240)에 제공될 수 있다.

[0043]

무선 디바이스(110)는 TDD 및 FDD 모드를 모두를 지원할 수 있다. 무선 디바이스(110)는 FDD 모드에서 수신기들(230) 및 송신기들(240)에 대한 상이한 LO 주파수들에서 수신 및 전송 LO 신호들을 생성하기 위한 주파수 합성기들(250a 및 250b)을 포함할 수 있다. 주파수 합성기들(250a 및 250b)은 재사용될 수 있고, 둘 모두 TDD 모드에서 인에이블될 수 있는데, 이는 회로 및 영역 불이익(penalty)이 없는 결과를 초래할 것이다.

[0044]

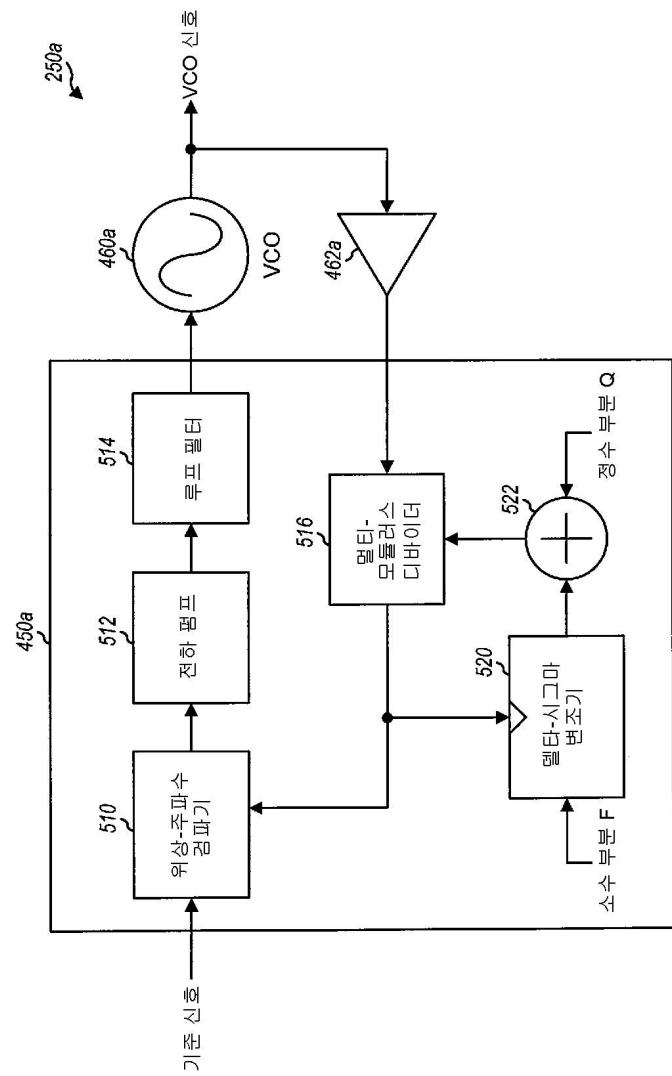

도 5는 도 4의 주파수 합성기(250a)의 예시적인 설계의 블록도를 도시한다. 간략함을 위해 VCO(460a) 및 버퍼(462a)만이 도 5에 도시되고, VCO(470a) 및 버퍼(472a)는 간략함을 위해 생략된다. PLL(450a) 내에서, 위상-

주파수 검파기(510)는  $f_{REF}$ 의 정확한 주파수를 가지는 기준 신호 및 멀티-모듈러스 디바이더(516)로부터의 피드백 신호를 수신한다. 검파기(510)는 피드백 신호의 위상을 기준 신호의 위상과 비교하여, 2개의 입력 신호들 간의 위상 차이/에러를 나타내는 에러 신호를 제공한다. 전하 펌프(512)는 에러 신호를 수신하고, 에러 신호에 비례하는 전류 신호(또는 전하)를 생성한다. 루프 필터(514)는 전류 신호를 필터링하고 제어 신호를 제공한다. VCO(460a)는 제어 신호를 수신하고, 제어 신호에 의해 결정되는  $f_{RX}$ 의 주파수를 가지는 VCO 신호를 생성한다. 버퍼(462a)는 VCO 신호를 버퍼링하고, 버퍼링된 VCO 신호를 제공한다. 디바이더(516)는 버퍼링된 VCO 신호를 주파수에서 L의 디바이더 비로 분할하고, 위상-주파수 검파기(510)에 피드백 신호를 제공한다.

[0045] 디바이더 비 L은 비-정수 값일 수 있고, 정수 부분 Q과 소수 부분 F로 분해될 수 있으며, 여기서,  $L = Q + F$ ,  $Q \geq 1$  및  $1 > F > 0$ 이다. 델타-시그마 변조기(520)는 소수 부분 F를 수신하고 일('1')들 및 제로('0')들의 비트 시퀀스를 생성하며, 1들의 비율은 소수 부분 F에 종속적이다. 그러나, 1들 및 0들은, 양자화 잡음의 대부분이 고 주파수에서 나타나도록 성형되고 루프 필터(514)에 의해 더욱 용이하게 필터링될 수 있도록, 비트 시퀀스에서 분포된다. 합산기(522)는 델타-시그마 변조기(520)로부터의 비트 시퀀스를 정수 부분 Q과 합산하며, 디바이더(516)에 순시 디바이더 비를 제공한다. 순시 디바이더 비는 0 또는 1이 델타-시그마 변조기(520)에 의해 제공되는지에 따라 Q 또는 Q+1 중 어느 하나와 동일할 수 있다.

[0046] 주파수 합성기(250a)는 소수-L 주파수 합성기로서 동작될 수 있다. 소수 디바이더 비 L는 기준 주파수의 레이트에서 Q와 Q+1의 정수 값들 사이의 순시 디바이더 비를 변경/디터링함으로써 획득될 수 있고, 여기서 Q는 L보다 더 작은 가장 큰 정수 값이다. 순시 디바이더 비는 기준 신호의 사이클마다 한번 변경할 수 있다. 순시 디바이더 비의 평균은 소수 디바이더 비 L와 동일하다. 정수 디바이더 비들 Q 및 Q+1의 시퀀스를 이용한 소수 디바이더 비 L의 근사화로부터 초래되는 양자화 잡음은 주파수 합성기(250a)의 폐쇄-루프 대역폭 밖의 고 주파수들에 집중되도록 델타-시그마 변조기(520)에 의해 성형될 수 있다. 양자화 잡음은 이후 주파수 합성기(250a)의 저대역 통과 응답에 의해 필터링될 수 있다.

[0047] 주파수 합성기(250a)는 또한 정수-L 주파수 합성기로서 동작될 수 있다. 이 경우, 델타-시그마 변조기(520)가 제거될 수 있다. 디바이더(516)는 버퍼링된 VCO 신호를 주파수에서 고정된 정수 디바이더 비로 분할할 수 있고, VCO 주파수는 기준 주파수의 정수배, 또는  $f_{VCO} = L * f_{REF}$ 일 수 있다.

[0048] 주파수 합성기들(250a 및 250b)은 TDD 모드에서 수신기들(230) 및 송신기들(240)에 대한 VCO 신호들을 생성할 수 있다. TDD 모드에서, 수학식 (1) 및 (2)에서 보여진 바와 같이, 다운링크에 대한 수신기들(230)에 대한 LO 주파수는 주어진 프레임에서 업링크에 대한 송신기들(240)에 대한 LO 주파수와 동일하다.

[0049] 일 예시적인 설계에서, 주파수 합성기들(250a 및 250b)은 동일한 VCO 주파수에서 VCO 신호들을 생성할 수 있고, 따라서, 수학식 (1) 및 (2)에서  $f_{RX} = f_{TX}$ 이고  $N = M$ 이다. 이 설계는, 트랜시버가 양호한 수신-전송 격리를 가지는 경우 사용될 수 있다.

[0050] 또 다른 예시적인 설계에서, 주파수 합성기들(250a 및 250b)은 상이한 VCO 주파수들에서 VCO 신호들을 생성할 수 있고, 따라서, 수학식 (1) 및 (2)에서  $f_{RX} \neq f_{TX}$ 이고  $N \neq M$ 이다. 이 설계는, 트랜시버가 VCO 풀링을 완화시키기 위해 열악한 수신-전송 격리를 가지는 경우 사용될 수 있는데, 이는 전송 및 수신 VCO들(예를 들어, VCO(360) 및 VCO(370))이 동일한 또는 유사한 주파수에서 발진할 때 중요할 수 있다. 수신기들(230)이 잔류 측파대에 대한 더욱 엄격한 요건들을 가질 수 있기 때문에, 정수 디바이더 비가 수신기들(230)에 대한 디바이더들(434)에 대해 사용될 수 있고, 비-정수 디바이더 비가 송신기들(240)에 대한 디바이더들(444)에 대해 사용될 수 있다. 예를 들어, 2의 디바이더 비를 가지는 디바이더가 더욱 간단하며, 더 양호한 잔류 측파대 성능을 초래할 수 있다. 예를 들어, 2의 디바이더 비(또는  $N = 2$ )가 수신기들(230)에 대해 사용될 수 있고, 1.5의 디바이더 비(또는  $M = 1.5$ )가 송신기들(240)에 대해 사용될 수 있다. 이 경우, 수신 VCO 신호들은 주파수  $off_{RX} = 2 * f_{LO}$ 를 가질 것이고, 전송 VCO 신호들은 주파수  $off_{TX} = 1.5 * f_{LO}$ 를 가질 것이다. 전송 VCO 신호에 대해 1.5의 디바이더 비(및 다른 정수 또는 비-정수 디바이더 비)를 사용함으로써, 다수의 대역들에 대한 VCO 신호들은 넓은 동조 범위를 커버하기 위한 주의 깊은 주파수 플래닝을 가지고 (다수의 VCO들 대신) 단일 VCO를 이용하여 생성될 수 있다. 정수 또는 비-정수 디바이더 비는 도 5의 PLL(450a)에 의해 지원될 수 있다.

[0051] 듀얼 주파수 합성기들(250a 및 250b)이 TDD를 활용한 다양한 무선 시스템들과의 통신을 위해 수신기들(230) 및 송신기들(240)에 대해 사용될 수 있다. 예를 들어, 듀얼 주파수 합성기들(250a 및 250b)은 LTE TDD 시스템들, TD-SCDMA 시스템들 등과의 통신을 위해 사용될 수 있다.

[0052]

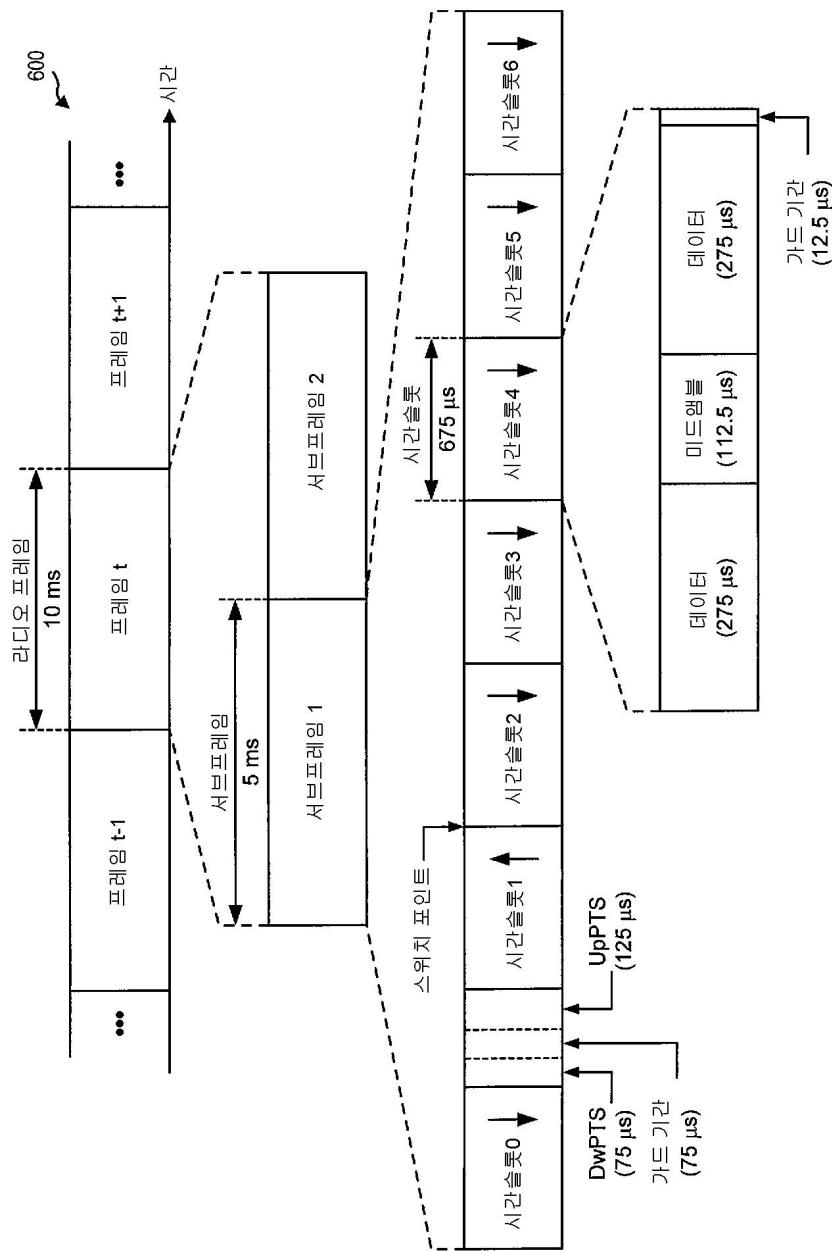

도 6a는 TD-SCDMA에 대한 프레임 구조(600)를 도시한다. 전송 시간선은 프레임들로 구획되어 있고, 각각의 프레임은 SFN(system frame number)에 의해 식별된다. 각각의 프레임은 10밀리초(ms)의 지속기간을 가지며, 2개의 서브프레임들 1 및 2로 구획된다. 각각의 서브프레임은 5ms의 지속기간을 가지며, 7개의 시간슬롯들(0 내지 6), DwPTS(Downlink Pilot Time Slot), UpPTS(Uplink Pilot Time Slot), 및 GP(guard period)로 구획된다. DwPTS, 가드 기간, 및 UpPTS는 시간슬롯 0 이후에 위치된다. 시간슬롯 0은 다운링크에 대해 사용되고, 시간슬롯 1은 업링크에 대해 사용되고, 시간슬롯들(2 내지 6)은, 스위치 포인트에 의해 결정될 때, 다운링크 및/또는 업링크에 대해 사용될 수 있다. 도 6a에 도시된 예에서, 시간슬롯들(2 내지 6)은 다운링크에 대해 사용된다. 각각의 시간슬롯은 675마이크로-초( $\mu$ s)의 지속기간을 가지며 864개 칩들을 커버한다. DwPTS는 75 $\mu$ s의 지속기간을 가지며 96개 칩들을 커버한다. UpPTS는 125 $\mu$ s의 지속기간을 가지며 160개 칩들을 커버한다. DwPTS와 UpPTS 사이의 가드 기간은 75 $\mu$ s의 지속기간을 가지며 96개 칩들을 커버한다.

[0053]

각각의 시간슬롯은 제1 데이터 부분, 미드앰블, 제2 데이터 부분 및 가드 기간을 포함한다. 각각의 데이터 부분은 275 $\mu$ s의 지속기간을 가지며 352개 칩들을 커버한다. 미드앰블은 112.5 $\mu$ s의 지속기간을 가지며 144개 칩들을 커버한다. 시간슬롯의 종단에서의 가드 기간은 12.5 $\mu$ s의 지속기간을 가지며 16개 칩들을 커버한다. 각각의 시간슬롯은 데이터 전송을 위해 하나 또는 다수의 사용자들에게 할당될 수 있다.

[0054]

도 6b는 LTE TDD에 대한 프레임 구조(650)를 도시한다. 전송 시간선은 라디오 프레임들의 유닛들로 구획되고, 각각의 라디오 프레임은 10ms의 지속기간을 가진다. 각각의 라디오 프레임은 0 내지 9의 인덱스들을 가지는 10개의 서브프레임들로 구획된다. LTE는 TDD에 대한 다수의 업링크-다운링크 구성들을 지원한다. 모든 업링크-다운링크 구성들에 대해 서브프레임들(0 및 5)은 다운링크(DL)에 대해 사용되고, 서브프레임(2)은 업링크(UL)에 대해 사용된다. 서브프레임들(3, 4, 7, 8 및 9)은 각각 업링크-다운링크 구성에 따라 다운링크 또는 업링크에 대해 사용될 수 있다. 서브프레임(1)은 다운링크 제어 채널들뿐만 아니라 데이터 전송을 위해 사용되는 DwPTS(Downlink Pilot Time Slot), 전송 없는 GP(Guard Period), 및 RACH(random access channel) 또는 SRS(sound reference signals) 어느 하나에 대해서 사용되는 UpPTS(Uplink Pilot Time Slot)으로 구성된 3개의 특수 필드들을 포함한다. 서브프레임(6)은 업링크-다운링크 구성에 따라 DwPTS만, 또는 모든 3개의 특수 필드들, 또는 다운링크 서브프레임을 포함할 수 있다. DwPTS, 가드 기간, 및 UpPTS는 상이한 서브프레임 구성들에 대해 상이한 지속기간들을 가질 수 있다. DwPTS는 214 $\mu$ s와 857 $\mu$ s 사이의 지속기간을 가질 수 있다. UpPTS는 71 $\mu$ s와 142 $\mu$ s 사이의 지속기간을 가질 수 있다. 가드 기간은 71 $\mu$ s와 714 $\mu$ s 사이의 지속기간을 가질 수 있다.

[0055]

도 6a 및 6b에 도시된 바와 같이, LTE TDD 시스템들 및 TD-SCDMA 시스템들은 다운링크 시간슬롯들과 업링크 시간슬롯들 사이의 고속 스위칭을 가진다. 도 6a의 예에 대해, TD-SCDMA 시스템 내의 서브프레임 내에서, 다운링크-대-업링크 트랜지션은 75 $\mu$ s 가드 기간 내에 발생하고, 업링크-대-다운링크 트랜지션은 시간슬롯의 종단에서 12.5 $\mu$ s 가드 기간 내에서 발생한다.

[0056]

도 6a 및 6b에 도시된 바와 같이, 수신기는 일부 시간 구간들에 대해서만 활성일 수 있고, 송신기는 TDD를 활용하는 무선 시스템과의 통신을 위해 일부 다른 시간 구간 동안 활성일 수 있다. 배터리 전력을 보존하고 가능하게는 성능을 개선하기 위해, 주파수 합성기(250a)는 수신기가 활성일 때 인에이블될 수 있고, 다른 시간들에서 디스에이블될 수 있다. 유사하게, 주파수 합성기(250b)는 송신기가 활성일 때 인에이블될 수 있고, 다른 시간들에서 디스에이블될 수 있다. 주파수 합성기들(250a 및 250b)은 파워-온 시퀀스에 기초하여 인에이블되고 디스에이블될 수 있다.

[0057]

도 7a 내지 7d는 TD-SCDMA 시스템과의 통신을 위해, 주파수 합성기들(250a 및 250b)에 대한 4개의 예시적인 파워-온 시퀀스들을 도시한다. 도 7a 내지 7d에 도시된 예들에서, 무선 디바이스(110)에는 다운링크를 위한 시간슬롯들(0, 2 및 3)이 할당되고, 업링크를 위한 시간 슬롯(1)이 할당된다. 하나의 대역에 대한 하나의 수신기(230) 및 하나의 송신기(240)는 TD-SCDMA 시스템과의 통신을 위해 선택된다. 도 7a에 도시된 바와 같이, 선택된 수신기(230)는 (i) 시간슬롯(0) 및 DwPTS 동안 인에이블되고, (ii) 가드 기간, UpPTS, 시간슬롯(1) 동안 디스에이블되고, (iii) 시간슬롯들(2 및 3) 동안 인에이블되고, (iv) 시간슬롯들(4 내지 6) 동안 디스에이블된다. 선택된 송신기(240)는 (i) 시간슬롯(0), DwPTS, 및 가드 기간 동안 디스에이블되고, (ii) UpPTS 및 시간슬롯(1) 동안 인에이블되고, (iii) 시간슬롯들(2 내지 6) 동안 디스에이블된다.

[0058]

도 7a는 전력 소모를 감소하기 위해 설계된 주파수 합성기들(250a 및 250b)에 대한 예시적인 파워-온 시퀀스(710)를 도시한다. 파워-온 시퀀스(710)에 대해, 주파수 합성기(250a)는 수신기(230)가 인에이블되기 단시간 전에 인에이블되고, 수신기(230)가 디스에이블될 때 디스에이블된다. 유사하게, 주파수 합성기(250b)는 송신기

(240)가 인에이블되기 단시간 전에 인에이블되고, 송신기(240)가 디스에이블될 때 디스에이블된다. 주파수 합성기들(250a 및 250b)은 이들의 VCO 신호들이 수신기(230)와 송신기(240)에 의해 요구되기 이전에 웜업하고 타겟 VCO 주파수에 로크(lock)하기 위해 충분히 일찍 인에이블된다. 주파수 합성기들(250a 및 250b)은 전력 소모를 감소시키기 위해 요구되지 않을 때는 디스에이블되고 파워 오프될 수 있다.

[0059] 도 7b는 수신기(230)에 대한 교란을 감소시키도록 설계된, 주파수 합성기들(250a 및 250b)에 대한 예시적인 파워-온 시퀀스(720)를 도시한다. 높은 변조 차수들이 다운링크 상의 데이터 전송을 위해 지원될 수 있다. 수신기(230)는 높은 변조 차수, 예를 들어, 64 직교 진폭 변조(QAM)의 변조 심볼들을 포함하는 다운링크 신호를 복조할 때 양호한 성능을 달성하기 위해 수신 VCO 신호에서 작은 위상 에러(예를 들어, 5도 미만)를 초래하는 교란만을 견딜 수도 있다. 주파수 합성기(250a)에서의 수신 VCO 신호의 위상은 주파수 합성기(250b)가 파워 온될 때마다 갑자기 변경할 수 있다. 따라서, 주파수 합성기(250b)는 수신기(230)가 인에이블될 때의 시간 구간들 동안이 아니라 충분히 일찍 파워 온 될 수 있다. 도 7b에 도시된 예에서, 주파수 합성기(250b)는 시간슬롯(0) 이전에, 예를 들어, 주파수 합성기(250a)가 인에이블되는 동시에 인에이블된다. 따라서, 주파수 합성기(250b)는 시간슬롯(0) 및 DwPTS 동안 주파수 합성기(250a)에서 수신 VCO 신호의 위상을 교란하지 않는다. 주파수 합성기(250b)는 업링크에 대해 무선 디바이스(110)에 할당된 마지막 시간슬롯인, 시간슬롯(1) 이후에 디스에이블된다. 유사하게, 주파수 합성기(250a)는, 송신기(240)가 인에이블되는 시간 구간들 동안이 아니라, 충분히 일찍 파워 온 될 수 있다.

[0060] 일부 파워-온 시퀀스 구성들(미도시)에서, 전송 또는 수신기 주파수 합성기(250a 및 250b)는 시간슬롯의 미드앰블 내에서 인에이블될 수 있다. 예를 들어, 전송 또는 수신기 주파수 합성기(250a 및 250b)는 데이터 슬롯의 임의의 부분 내에서 인에이블될 수 있다. 미드앰블은 데이터 슬롯의 다른 부분에서 사용되는 변조, 예를 들어, 64 QAM보다 덜 엄격한 변조(예를 들어, 더 낮은 변조 속도), 예를 들어, 직교 위상 시프트 키잉(QPSK)을 사용할 수 있다. 미드앰블 동안 전송 주파수 합성기(250a) 또는 수신기 주파수 합성기(250b)를 인에이블시키는 것은 더 적은 교란, 및 따라서 더 적은 성능 저하를 초래할 수 있다. 예를 들어, QPSK에서, 수신기(230) 또는 송신기(240)는 주파수 합성기(250b)의 파워-온에 의한 더 큰 교란을 견딜 수 있다. 예를 들어, 64QAM은 다운링크 및/또는 업링크에서 사용될 수 있다. 전송 주파수 합성기(250b)는 유발되는 교란을 최소화하기 위해 다운링크의 미드앰블 동안 여전히 인에이블될 수 있다.

[0061] 도 7c는 VCO 풀링을 감소시키도록 설계된 주파수 합성기들(250a 및 250b)에 대한 예시적인 파워-온 시퀀스(730)를 도시한다. 주파수 합성기들(250a 및 250b)과 이들의 신호 경로들 간의 격리는 전체 영역, 레이아웃, 및 트랜시버(220)의 평면도와 같은 다양한 인자들에 종속적일 수 있다. 트랜시버(220)는 열악한 수신-전송 격리를 가질 수 있다. 이러한 경우, VCO 풀링이 발생할 수 있고, 하나의 주파수 합성기의 파워 온은 다른 주파수 합성기의 주파수/위상을 교란시킬 수 있다. 열악한 수신-전송 격리로 인한 VCO 풀링을 완화시키기 위해, 주파수 합성기들(250a 및 250b)은 함께 인에이블될 수 있다. 도 7c에 도시된 예에서, 주파수 합성기들(250a 및 250b)은 둘 모두 시간슬롯(0) 이전에 인에이블되고, 시간슬롯(3)의 종단에서 디스에이블된다. 수신기(230)는 시간슬롯들(0), DwPTS 및 시간슬롯들(2 및 3) 동안만 인에이블된다. 송신기(240)는 UpPTS 및 시간슬롯(1) 동안만 인에이블된다. 주파수 합성기들(250a 및 250b)은 이들의 연관된 수신기(230) 및 송신기(240)보다 더 오래 인에이블되며, 이는 더 높은 전력 소모를 초래할 수 있다. 그러나, VCO 신호들에 대한 긴 라우팅 트레이스들 및 큰 버퍼들은 듀얼 주파수 합성기들(250a 및 250b)을 사용함으로써 회피될 수 있는데, 이는 수신기(230) 및 송신기(240) 모두에 대해 더 낮은 전력 소모와 더 양호한 성능(예를 들어, 더 양호한 잔류 측파대)을 초래할 수 있다.

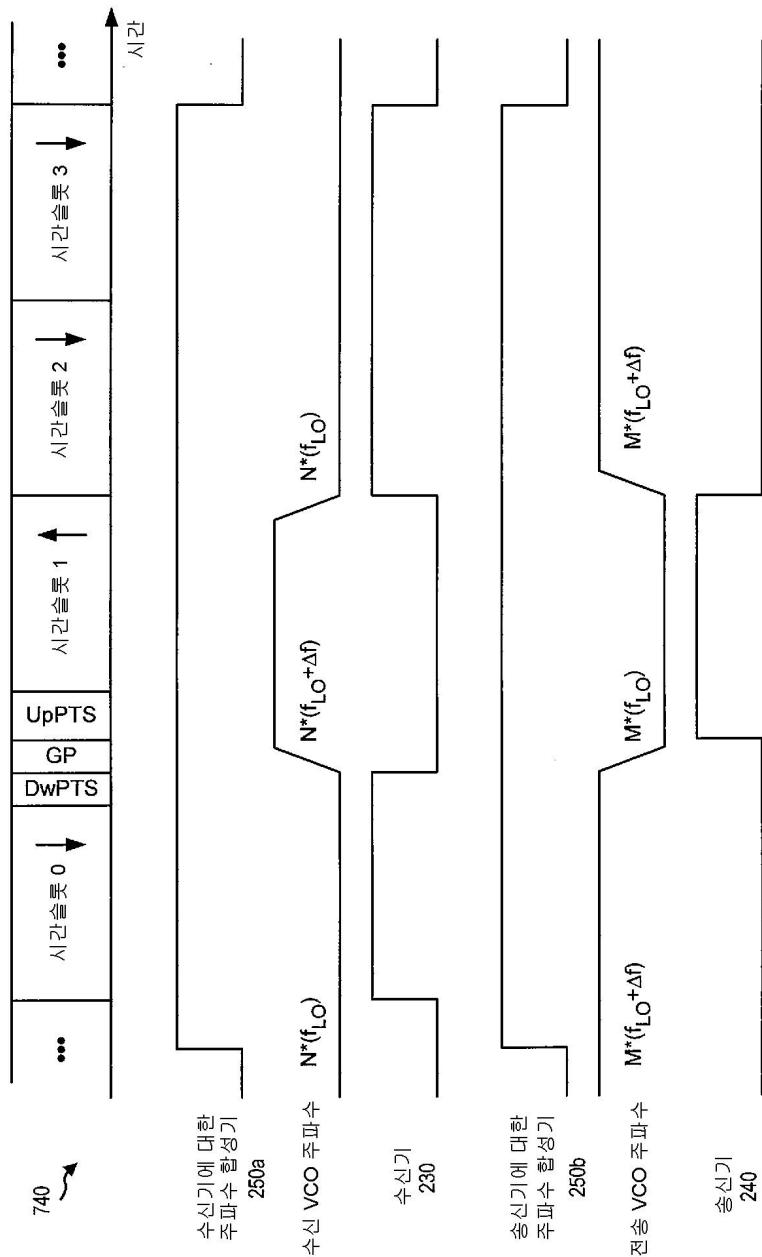

[0062] 도 7d는 위상 잡음 저하를 완화시키도록 설계된, 주파수 합성기들(250a 및 250b)에 대한 예시적인 파워-온 시퀀스(740)를 도시한다. 트랜시버(220) 내의 수신-전송 격리는 열악할 수 있고, 주파수 합성기(250a)에서의 수신 VCO와 주파수 합성기(250b)에서의 전송 VCO 사이의 커플링은 서로의 위상 잡음을 저하시킬 수 있다. 또한, 수신 VCO와 전송 VCO의 주파수들이 서로 너무 가까울 때, 주입 로크(injection lock)가 발생할 수 있다. 주입 로크는 하나의 VCO(예를 들어, 수신 VCO)의 위상 잡음이 다른 VCO(예를 들어, 전송 VCO)의 위상 잡음에 압도적이도록 할 수 있는데, 이는 저하를 초래한다. 다시 말해, 주입 로크는, 하나의 VCO의 위상 잡음이 다른 VCO의 위상 잡음에 압도적일 것이기 때문에 문제이다.

[0063] 위상 잡음 저하를 완화시키는 일 설계에서, 수신 VCO 및 전송 VCO는, 전술된 바와 같이, 상이한 VCO 주파수들에서 동작할 수 있다. 상이한 디바이더 비들은 이후 원하는 LO 주파수에서 수신 및 전송 LO 신호들을 획득하기 위해 수신 및 전송 VCO 신호들에 대해 사용될 수 있다. 예를 들어,  $N = 2$ 의 디바이더 비는 주파수 합성기(250a)로부터의 수신 VCO 신호에 대해 사용될 수 있고,  $M = 1.5$ 의 디바이더 비는 주파수 합성기(250b)로부터의

전송 VCO 신호에 대해 사용될 수 있다.

[0064] 위상 잡음 저하를 완화시키는 또 다른 설계에서, 수신 VCO 주파수는, (i) 수신 VCO 및 전송 VCO가 임의의 주어진 시간에 동일한 주파수에서 동작하지 않고, (ii) 수신 VCO 또는 전송 VCO만이 임의의 주어진 시간에 그의 타겟 VCO 주파수에서 동작하도록, 전송 VCO 주파수로부터 약간 비스듬히 기울어져 있을 수 있다(skew). 도 7d에 도시된 예에서, 주파수 합성기들(250a 및 250b)은 모두 시간슬롯(0) 이전에 인에이블되고, 모두 시간슬롯(3)의 종단에서 디스에이블된다. 주파수 합성기(250a) 내의 수신 VCO는 수신기(230)가 인에이블되는 시간슬롯(0), DwPTS 및 시간슬롯들(2 및 3) 동안  $N * f_{LO}$ 의 타겟 VCO 주파수에서 동작한다. 수신 VCO는 수신기(230)가 디스에이블되는 가드 기간, UpPTS 및 시간슬롯(1) 동안  $N * (f_{LO} + \Delta f)$ 의 비스듬히 기울어진 VCO 주파수에서 동작한다. 주파수 합성기(250b) 내의 전송 VCO는 송신기(240)가 인에이블되는 UpPTS 및 시간슬롯(1) 동안  $M * f_{LO}$ 의 타겟 VCO 주파수에서 동작한다. 전송 VCO는 송신기(240)가 디스에이블되는 시간슬롯(0), DwPTS 및 시간 슬롯들(2 및 3) 동안  $M * (f_{LO} + \Delta f)$ 의 비스듬히 기울어진 VCO 주파수에서 동작한다. 수신 VCO 및 전송 VCO는 동시에(예를 들어, 도 7d에서 도시된 바와 같이) 또는 상이한 시간들에서(도 7d에 미도시됨) 주파수를 스위칭할 수 있다.

[0065] 수신 및 전송 VCO 주파수들은 다양한 방식들로 비스듬히 기울어질 수 있다. 일 예시적인 설계에서, VCO 주파수는 PLL을 리셋하지 않고 소량만큼 PLL의 주파수 디바이더 비(즉, 합성기 주파수 워드)를 동적으로 조정함으로써 비스듬히 기울어질 수 있다. 예를 들어, 도 5의 소수 부분 F는 VCO 주파수에서 작은 변경을 획득하기 위해 작은 값으로 설정될 수 있다. 실행 중인 주파수 합성기의 제한된 주파수 동적 범위로 인해 VCO 주파수에서 작은 편차만이 달성가능할 수 있다. VCO 주파수의 안정화 시간(settling time)은 VCO 주파수에서의 작은 변경으로 인해 상대적으로 짧을 수 있다. 또 다른 예시적인 설계에서, VCO 주파수는 주파수 합성기의 하드 리셋을 통해 비스듬히 기울어질 수 있다. 하드 리셋은 PLL을 일시적으로 파워오프함으로써 달성될 수 있다. 하드 리셋은 PLL을 PLL의 초기 상태(즉, PLL이 처음으로 루크하기 이전에 PLL이 처음 파워 온 할 때 PLL이 있는 상태)로 리셋시킨다. 일부 예시적인 설계들에서, VCO 주파수는 주파수 합성기의 소프트 리셋을 통해 비스듬히 기울어질 수 있다. 소프트 리셋에서, 분할 비는 실시간(on the fly)으로 변경되며, PLL은 주파수 변경에 대해 조정하지만, 파워 다운이 요구되지는 않는다. VCO 주파수에 대한 안정화 시간이 더 길어질 지라도, VCO 주파수의 큰 편차가 달성될 수 있다.

[0066] 도 7a 내지 7d는 TDD 모드에서 수신기 및 송신기에 대한 2개의 주파수 합성기들에 대한 4개의 예시적인 파워-온 시퀀스들을 도시한다. 2개의 주파수 합성기들이 또한 다른 방식들로 인에이블되고 디스에이블될 수 있다. 예를 들어, 하나의 주파수 합성기(예를 들어, 주파수 합성기(250a))는 항상 인에이블될 수 있고, 다른 주파수 합성기는 적절한 경우 인에이블되거나 디스에이블될 수 있다.

[0067] TDD 모드에서 수신기들(230) 및 송신기들(240)에 대한 별도의 주파수 합성기들(250a 및 250b)을 사용하는 것은 다양한 장점들을 제공할 수 있다. 먼저, 더 적은 그리고/또는 더 작은 버퍼들(464 및 474)은 더 적은 로딩을 가지고 더 짧은 거리를 통해 VCO 신호들을 구동하기 위해 사용될 수 있다. 더 적은 그리고/또는 더 작은 버퍼들(464 및 474)은 회로 영역을 절감하고 전력 소모를 감소시킬 수 있다. VCO 신호들에 대한 라우팅 트레이스들(466 및 476)은 더 짧고, 덜 복잡하며, 커플링될 가능성이 더 적을 수 있다.

[0068] 둘째, 더 양호한 성능(예를 들어, 더 양호한 잔류 측파대)이 VCO 신호들에 대한 더 짧은 라우팅 트레이스들(466 및 476)로 인해 수신기들(230) 및 송신기(240)에 대해 달성될 수 있다. 수신기들(230) 및 송신기들(240)에 대한 위상 교란의 더 양호한 억제는, 하기와 설명된 바와 같이, 주파수 합성기들(250a 및 250b)의 적절한 LO 주파수 플랜 및 파워-업 시퀀스를 이용하여 달성될 수 있다. 도 4에 도시된 바와 같이, 더 양호한 수신-전송 격리는 또한, 트랜시버의 수신 부분과 송신 부분 사이에 스위치들 또는 버퍼들이 접속되어 있지 않기 때문에, TDD 및 FDD 모드를 모두에서 달성될 수 있다. 더 양호한 수신-전송 격리는 또한, 주파수 합성기들(250a 및 250b)에 대한 더 적은 교란, 더 적은 VCO 풀링, 및 더 빠른 스위칭 시간을 초래할 수 있다.

[0069] 다른 이익들이 또한 TDD 모드에서 수신기들(230) 및 송신기들(240)에 대한 2개의 주파수 합성기들을 사용함으로써 획득될 수 있다. 예를 들어, LO 주파수가 TDD 모드에서 주어진 프레임에서 수신기들(230)과 송신기들(240) 모두에 대해 동일하기 때문에, VCO 주파수들을 재로크(relock)하기 위한 시간이 요구되지 않는다. 예를 들어, 수신기들(230) 및 송신기들(240)에 대한 주파수 합성기들이 둘 모두 동일한 프레임의 업링크 및 다운링크 내에서 인에이블되기 때문에 이러한 결과가 발생할 수 있다. 상이한 디바이더 비들이 수신기들(230) 및 송신기들(240)에 대해 사용되는 경우, 더 작은 VCO 튜닝 범위가 가능할 수 있다.

[0070] 예시적인 설계에서, 장치(예를 들어, 무선 디바이스, IC, 회로 모듈 등)는 제1 및 제2 주파수 합성기들을 포함할 수 있다. 제1 주파수 합성기(예를 들어, 도 4의 주파수 합성기(250a))는 수신기에 대해 LO 주파수에서 제1 LO 신호(예를 들어, 수신 LO 신호)를 생성하기 위해 사용될 수 있는 제1 발진기 신호(예를 들어, 수신 VCO 신호)를 생성할 수 있다. 제2 주파수 합성기(예를 들어, 주파수 합성기(250b))는 송신기에 대해 동일한 LO 주파수에서 제2 LO 신호(예를 들어, 전송 LO 신호)를 생성하기 위해 사용될 수 있는 제2 발진기 신호(예를 들어, 전송 VCO 신호)를 생성할 수 있다.

[0071] 제1 및 제2 주파수 합성기들은 장치가 TDD 모드에서 동작할 때 동일한 LO 주파수에서 제1 및 제2 LO 신호들을 획득하기 위해 제1 및 제2 발진기 신호들을 생성할 수 있다. TDD 모드에서, 수신기는 제1 시간 구간들 동안 인에이블될 수 있고, 송신기는 제2 시간 구간들 동안 인에이블될 수 있다. 장치는 또한 FDD 모드에서 동작할 수 있다. 이 경우, 제1 및 제2 주파수 합성기들은 상이한 LO 주파수들에서 제1 및 제2 LO 신호들을 획득하기 위해 제1 및 제2 발진기 신호들을 생성할 수 있다.

[0072] 일 설계에서, 제1 및 제2 주파수 합성기들은 동일한 발진기/VCO 주파수에서 제1 및 제2 발진기 신호들을 생성할 수 있다. 이 설계에서, 제1 및 제2 발진기 신호들은 동일한 LO 주파수에서 제1 및 제2 LO 신호들을 획득하기 위해 동일한 디바이더 비로 주파수에서 분할될 수 있다. 또 다른 설계에서, 제1 및 제2 주파수 합성기들은 상이한 발진기/VCO 주파수들에서 제1 및 제2 발진기 신호들을 생성할 수 있다. 제1 발진기 신호는 LO 주파수의 정수배일 수 있는 제1 발진기 주파수에 있을 수 있다. 제2 발진기 신호는 제1 발진기 주파수와는 상이할 수 있는 제2 발진기 주파수에 있을 수 있고 LO 주파수의 비-정수배일 수 있다.

[0073] 제1 및 제2 주파수 합성기들은 다양한 방식들로 인에이블되고 디스에이블될 수 있다. 도 7a에 도시된 일 설계에서, 제1 주파수 합성기는 수신기가 인에이블되기 이전에 인에이블될 수 있고, 수신기가 디스에이블된 이후 또는 수신기가 디스에이블될 때 디스에이블될 수 있다. 제2 주파수 합성기는 송신기가 인에이블되기 이전에 인에이블될 수 있고, 송신기가 디스에이블된 이후 또는 송신기가 디스에이블될 때 디스에이블될 수 있다. 도 7b에 도시된 다른 설계에서, 제1 및 제2 주파수 합성기들은 수신기가 인에이블되기 이전에 인에이블될 수 있다. 제1 주파수 합성기는 수신기가 디스에이블된 이후 또는 수신기가 디스에이블될 때 디스에이블될 수 있다. 제2 주파수 합성기는 송신기가 디스에이블된 이후 또는 송신기가 디스에이블될 때 디스에이블될 수 있다. 도 7c에 도시된 또 다른 설계에서, 제1 및 제2 주파수 합성기들은 수신기가 인에이블되기 이전에 인에이블될 수 있고, 수신기가 디스에이블된 이후 또는 수신기가 디스에이블될 때 디스에이블될 수 있다. 제1 및 제2 주파수 합성기들은 또한 다른 방식들로 인에이블되고 디스에이블될 수 있다.

[0074] 일 설계에서, 제1 주파수 합성기는 수신기가 인에이블될 때 타겟 발진기 주파수(예를 들어,  $N * f_{LO}$ )에서, 그리고 송신기가 인에이블될 때 타겟 발진기 주파수로부터의 오프셋(예를 들어,  $N * (f_{LO} + \Delta f)$ )에서 제1 발진기 신호를 생성할 수 있다. 제1 주파수 합성기는 PLL을 포함할 수 있고, 타겟 발진기 주파수로부터의 오프셋은 PLL 내의 주파수 디바이더 비를 변경함으로써 획득될 수 있다. 일 설계에서, 제2 주파수 합성기는 송신기가 인에이블될 때 타겟 발진기 주파수(예를 들어,  $M * f_{LO}$ )에서, 그리고 수신기가 인에이블될 때 타겟 발진기 주파수로부터의 오프셋(예를 들어,  $M * (f_{LO} + \Delta f)$ )에서 제2 발진기 신호를 생성할 수 있다.

[0075] 도 8은 LO 신호를 생성하기 위한 프로세스(800)의 예시적인 설계를 도시한다. 제1 발진기 신호는 제1 주파수 합성기를 사용하여 생성될 수 있다(812). 수신기에 대한 LO 주파수에서의 제1 LO 신호는 제1 발진기 신호에 기초하여 생성될 수 있다(814). 제2 발진기 신호는 제2 주파수 합성기를 이용하여 생성될 수 있다(816). 송신기에 대한 LO 주파수에서의 제2 LO 신호는 제2 발진기 신호에 기초하여 생성될 수 있다(818).

[0076] 제1 주파수 합성기는 제1 발진기 주파수에서 제1 발진기 신호를 생성할 수 있다. 제2 주파수 합성기는 제2 발진기 주파수에서 제2 발진기 신호를 생성할 수 있다. 일 설계에서, 제1 발진기 주파수는 제2 발진기 주파수와 동일할 수 있고, 동일한 주파수 디바이더 비는 제1 및 제2 LO 신호들을 생성하기 위해 제1 및 제2 발진기 신호들에 대해 사용될 수 있다. 또 다른 설계에서, 제1 발진기 주파수는 제2 발진기 주파수와 상이할 수 있다. 이 설계에서, 제1 발진기 주파수는 LO 주파수의 정수배(예를 들어, 2배)일 수 있고, 제2 발진기 주파수는 LO 주파수의 비-정수배(예를 들어, 1.5배)일 수 있다.

[0077] 제1 및 제2 주파수 합성기들은 전술된 바와 같이, 다양한 방식들로 인에이블되고 디스에이블될 수 있다. 제1 및 제2 주파수 합성기들은 다양한 방식들로 제1 및 제2 발진기 신호들을 생성할 수 있다. 일 설계에서, 제1 및 제2 발진기 신호들은 항상 자신의 타겟 발진기 주파수들에 있을 수 있다. 또 다른 설계에서, 예를 들어, 도 7d에 또한 도시된 바와 같이, 제1 발진기 신호는 수신기가 인에이블될 때 자신의 타겟 발진기 주파수에 있을 수

있고, 송신기가 인에이블될 때 자신의 타겟 발진기 주파수로부터의 오프셋에 있을 수 있다. 예를 들어, 도 7d에 도시된 바와 같이, 제2 발진기 신호는 송신기가 인에이블될 때 자신의 타겟 발진기 주파수에 있을 수 있고, 수신기가 인에이블될 때 자신의 타겟 발진기 주파수로부터의 오프셋에 있을 수 있다.

[0078] 당업자는 정보 및 신호들이 다양한 상이한 기술들 및 기법들 중 임의의 것을 사용하여 표현될 수 있음을 이해할 것이다. 예를 들어, 위 기재 전반에 걸쳐 참조될 수 있는 데이터, 명령들, 커맨드들, 정보, 신호들, 비트들, 심볼들 및 칩들은 전압들, 전류들, 전자기파들, 자기장들 또는 입자들, 광학장들 또는 입자들, 또는 이들의 임의의 결합에 의해 표현될 수 있다.

[0079] 당업자는 본원의 개시내용과 관련하여 설명된 다양한 예시적인 논리 블록들, 모듈들, 회로들 및 알고리즘 단계들이 전자 하드웨어, 컴퓨터 소프트웨어, 또는 이를 모두의 결합으로서 구현될 수 있음을 추가로 인식할 것이다. 하드웨어와 소프트웨어의 이러한 상호교환가능성을 명백하게 예시하기 위해, 다양한 예시적인 컴포넌트들, 블록들, 모듈들, 회로들, 및 단계들이 이들의 기능성의 견지에서 일반적으로 위에 설명되었다. 이러한 기능성이 하드웨어 또는 소프트웨어로서 구현되는지의 여부는 전체 시스템에 부과된 설계 제약들 및 특정 애플리케이션에 의존한다. 당업자는 각각의 특정 애플리케이션에 대해 가변적인 방식들로 설명된 기능성을 구현할 수 있지만, 이러한 구현 결정들이 본 개시내용의 범위로부터의 이탈을 야기하는 것으로서 해석되지 않아야 한다.

[0080] 본원의 개시내용과 관련하여 설명된 다양한 예시적인 논리 블록들, 모듈들, 및 회로들은 범용 프로세서, DSP(digital signal processor), ASIC(application specific integrated circuit), FPGA(field programmable gate array) 또는 다른 프로그래밍가능한 논리 디바이스, 이산 게이트 또는 트랜지스터 논리, 이산 하드웨어 컴포넌트들, 또는 본원에 설명된 기능들을 수행하도록 설계된 이들의 임의의 결합을 이용하여 구현되거나 수행될 수 있다. 범용 프로세서는 마이크로프로세서일 수 있지만, 대안적으로, 프로세서는 임의의 종래의 프로세서, 제어기, 마이크로제어기, 또는 상태 머신일 수 있다. 프로세서는 또한 컴퓨팅 디바이스들의 결합, 예를 들어, DSP와 마이크로프로세서의 결합, 복수의 마이크로프로세서들, DSP 코어와 공조하는 하나 이상의 마이크로프로세서들, 또는 임의의 다른 이러한 구성으로서 구현될 수 있다.

[0081] 본원의 개시내용과 관련하여 설명된 방법 또는 알고리즘의 단계들은 직접 하드웨어에서, 프로세서에 의해 실행되는 소프트웨어 모듈에서, 또는 이를 둘의 결합에서 구현될 수 있다. 소프트웨어 모듈은 RAM(random access memory), 플래시 메모리, ROM(read-only memory), EPROM(erasable programmable read only memory), EEPROM(electrically erasable programmable read only memory), 레지스터들, 하드 디스크, 제거가능한 디스크, CD-ROM, 또는 당해 기술분야에 공지된 임의의 다른 형태의 저장 매체에 상주할 수 있다. 예시적인 저장 매체는, 프로세서가 저장 매체로부터 정보를 판독하고, 저장 매체에 정보를 기록할 수 있도록, 프로세서에 커플링된다. 대안적으로, 저장 매체는 프로세서에 일체화될 수 있다. 프로세서 및 저장 매체는 ASIC에 상주할 수 있다. ASIC은 사용자 단말에 상주할 수 있다. 대안적으로, 프로세서 및 저장 매체는 사용자 단말에서 이산 컴포넌트들로서 상주할 수 있다.

[0082] 하나 이상의 예시적인 설계들에서, 설명된 기능들은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 결합에서 구현될 수 있다. 소프트웨어에서 구현되는 경우, 기능들은 컴퓨터-판독가능한 매체 상에 하나 이상의 명령들 또는 코드로서 저장되거나 이를 통해 전송될 수 있다. 컴퓨터-판독가능한 매체는 한 장소에서 또 다른 장소로의 컴퓨터 프로그램의 이전을 용이하게 하는 임의의 매체를 포함하는 통신 매체와 컴퓨터 저장 매체 모두를 포함한다. 저장 매체는 범용 또는 특수 목적 컴퓨터에 의해 액세스될 수 있는 임의의 가용 매체일 수 있다. 제한이 아닌 예시에 의해, 이러한 컴퓨터-판독가능한 매체는 RAM, ROM, EEPROM, CD-ROM 또는 다른 광학 디스크 저장소, 자기 디스크 저장 또는 다른 자기 저장 디바이스, 또는 명령들 또는 데이터 구조들의 형태로 원하는 프로그램 코드 수단을 반송하거나 저장하기 위해 사용될 수 있고, 범용 또는 특수 목적 컴퓨터, 또는 범용 또는 특수-목적 프로세서에 의해 액세스될 수 있는 임의의 다른 매체를 포함할 수 있다. 또한, 임의의 접속수단이 적절하게 컴퓨터-판독가능한 매체라고 명명된다. 예를 들어, 소프트웨어가 웹사이트, 서버, 또는 다른 원격 소스로부터, 동축 케이블, 광섬유 케이블, 트위스티드 페어, DSL(digital subscriber line), 또는 적외선, 라디오 및 마이크로파와 같은 무선 기술들을 사용하여 전송되는 경우, 동축 케이블, 광섬유 케이블, 트위스티드 페어, DSL, 또는 적외선, 라디오 및 마이크로파와 같은 무선 기술들은 매체의 정의 내에 포함된다. disk 및 disc는, 본원에서 사용된 바와 같이, 컴팩트 disc(CD), 레이저 disc, 광 disc, DVD(digital versatile disc), 플로피 disk 및 블루-레이 disc를 포함하며, 여기서, disk들은 일반적으로 자기적으로 데이터를 재생하는 반면, disc들은 레이저를 이용하여 광학적으로 데이터를 재생한다. 위 항목들의 결합들이 또한 컴퓨터-판독가능한 매체의

범위 내에 포함되어야 한다.

[0083]

개시내용의 이전 기재는 임의의 당업자가 개시내용을 실시하거나 사용할 수 있게 하기 위해 제공된다. 개시내용에 대한 다양한 수정들이 당업자에게 쉽게 명백할 것이며, 본원에 정의된 포괄적 원리들은 개시내용의 사상 또는 범위로부터의 이탈 없이 다른 변형들에 대해 적용될 수 있다. 따라서, 개시내용은 본원에 설명된 예들 및 설계들에 대해 제한되도록 의도되는 것이 아니라, 본원에 개시된 원리들 및 신규한 특징들에 부합하는 가장 넓은 범위에 따라야 한다.

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

도면5

도면 6a

도면6b

도면7a

도면7b

720 ↗

도면7c

## 도면7d

## 도면8