### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2015/094242 A1

(43) International Publication Date 25 June 2015 (25.06.2015)

(51) International Patent Classification: *H01L 27/115* (2006.01)

(21) International Application Number:

PCT/US2013/076221

(22) International Filing Date:

18 December 2013 (18.12.2013)

(25) Filing Language:

English

(26) Publication Language:

English

- (71) Applicant: HEWLETT-PACKARD DEVELOPMENT COMPANY, L.P. [US/US]; Hewlett-Packard Company, 11445 Compaq Center Drive W., Houston, Texas 77070 (US).

- (72) Inventors: GE, Ning; 1501 Page Mill Road, Palo Alto, California 94304-1100 (US). YANG, Jianhua; 1501 Page Mill Road, Palo Alto, California 94304-1100 (US). LI, Zhiyong; 1501 Page Mill Road, Palo Alto, California 94304-1100 (US).

- (74) Agents: COLLINS, David W. et al.; Hewlett-Packard Company, IP Administration MS35, 3404 E. Harmony Road, Fort Collins, Colorado 80528 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY,

BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

### **Declarations under Rule 4.17:**

- as to the identity of the inventor (Rule 4.17(i))

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

#### Published:

— with international search report (Art. 21(3))

(54) Title: NON-VOLATILE MEMORY ELEMENT WITH THERMAL-ASSISTED SWITCHING CONTROL

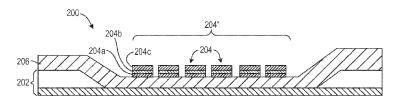

Fig. 2

(57) Abstract: A non-volatile memory element with thermal-assisted switching control is disclosed. The non-volatile memory element is disposed on a thermal inkjet resistor. Methods for manufacturing the combination and methods of using the combination are also disclosed.

1

# NON-VOLATILE MEMORY ELEMENT WITH THERMAL-ASSISTED SWITCHING CONTROL

### **BACKGROUND**

[0001] Non-volatile memory is computer memory that can get back stored information even when not powered. Types of non-volatile memory may include resistive RAM (random access memory) (RRAM or ReRAM), phase change RAM (PCRAM), conductive bridge RAM (CBRAM), ferroelectric RAM (F-RAM), etc.

[0002] Resistance memory elements can be programmed to different resistance states by applying programming energy. After programming, the state of the resistive memory elements can be read and remains stable over a specified time period. Large arrays of resistive memory elements can be used to create a variety of resistive memory devices, including non-volatile solid state memory, programmable logic, signal processing, control systems, pattern recognition devices, and other applications. Examples of resistive memory devices include valence change memory and electrochemical metallization memory, both of which involve ionic motion during electrical switching and belong to the category of memristors.

[0003] Memristors are devices that can be programmed to different resistive states by applying a programming energy, for example, a voltage or current pulse. This energy generates a combination of electric field and thermal effects that can modulate the conductivity of both non-volatile switch and non-linear select functions in a memristive element. After programming, the state of the memristor can be read and remains stable over a specified time period.

### BRIEF DESCRIPTION OF THE DRAWINGS

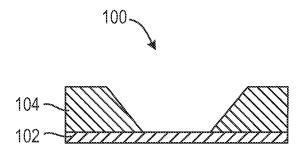

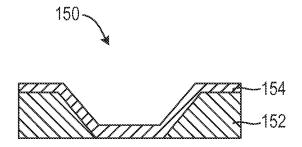

FIGS. 1A and 1B are cross-sectional views of examples of two different thermal inkjet structures employed in the practice of the teachings herein.

- FIG. 2 is a cross-sectional view of a plurality of memristors formed on a thermal element, here, a thermal inkjet structure, according to an example.

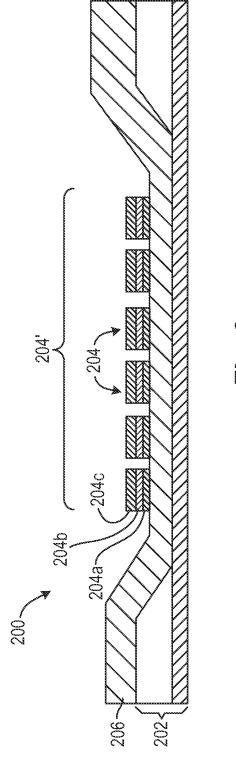

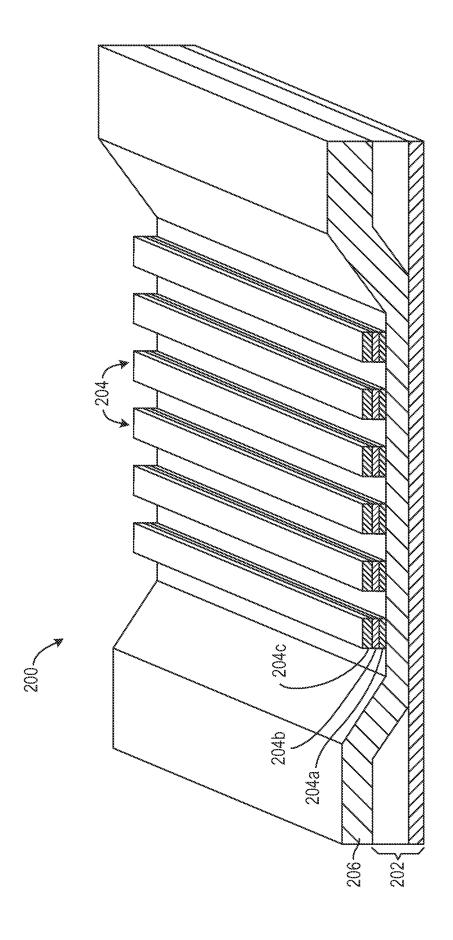

- FIG. 2A is an isometric view of the plurality of memristors formed on the thermal inkjet structure of FIG. 2, according to an example.

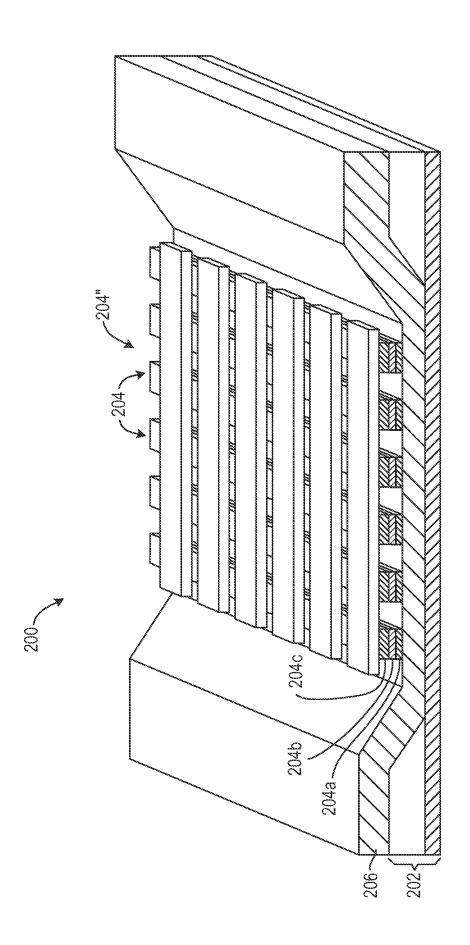

- FIG. 2B is an isometric view of a crossbar employing a plurality of memristors formed on the thermal inkjet structure of FIG. 2, according to an example.

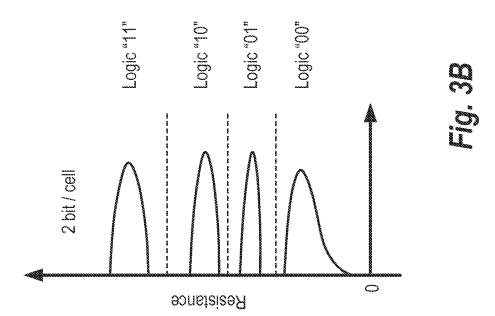

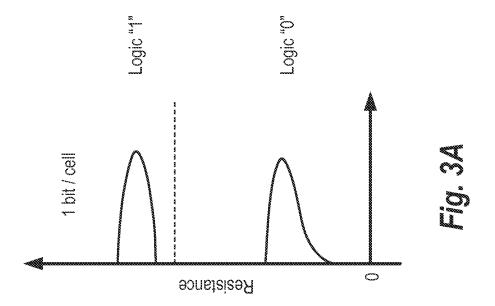

- FIGS. 3A and 3B, each having a vertical axis in resistance, depict the resistance levels of a memristor cell having 1 bit/cell (FIG. 3A) and a memristor cell having 2 bits/cell (FIG. 3B), according to an example.

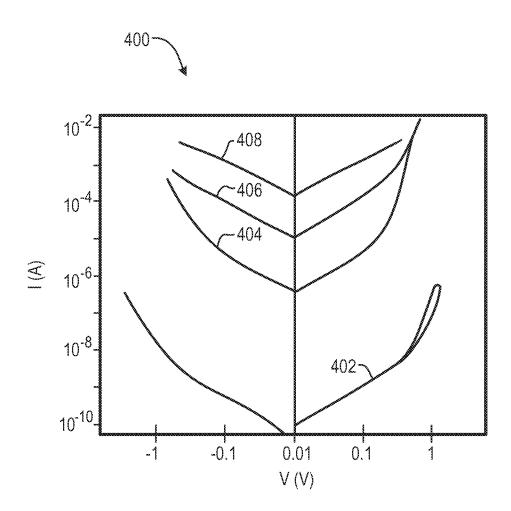

- FIG. 4, on coordinates of current (amps) and voltage (volts), depicts a series of I-V curves for a memristor having 2 bits/cell, according to an example.

### **DETAILED DESCRIPTION**

In the following description, numerous details are set forth to provide an understanding of the examples disclosed herein. However, it will be understood that the examples may be practiced without these details. While a limited number of examples have been disclosed, it should be understood that there are numerous modifications and variations therefrom. Similar or equal elements in the Figures may be indicated using the same numeral.

[0005] As used in the specification and claims herein, the singular forms "a," "an," and "the" include plural referents unless the context clearly dictates otherwise.

**[0006]** As used in this specification and the appended claims, "approximately" and "about" mean a  $\pm 10\%$  variance caused by, for example, variations in manufacturing processes.

**[0007]** In the following detailed description, reference is made to the drawings accompanying this disclosure, which illustrate specific examples in which this disclo-

sure may be practiced. The components of the examples can be positioned in a number of different orientations and any directional terminology used in relation to the orientation of the components is used for purposes of illustration and is in no way limiting. Directional terminology includes words such as "top," "bottom," "front," "back," "leading," "trailing," etc.

**[0008]** It is to be understood that other examples in which this disclosure may be practiced exist, and structural or logical changes may be made without departing from the scope of the present disclosure. Therefore, the following detailed description is not to be taken in a limiting sense. Instead, the scope of the present disclosure is defined by the appended claims.

[0009] Non-volatile memory elements can be used in a variety of applications, such as read-only memory, reprogrammable memory, and other uses where long term persistent storage is required.

**[0010]** Resistive memory elements can be used in a variety of applications, including non-volatile solid state memory, programmable logic, signal processing, control systems, pattern recognition, and other applications.

[0011] As used in the specification and appended claims, the term "resistance memory elements" refers broadly to programmable non-volatile resistors where the switching mechanism involves atomic motion and rearrangement, including valance change memory, electrochemical metallization memory, and others.

[0012] Memristors, or memristive devices, are nano-scale devices that may be used as a component in a wide range of electronic circuits, such as memories, switches, and logic circuits and systems. In a memory structure, a crossbar of memristors may be used. For example, when used as a basis for memories, the memristor may be used to store a bit of information, 1 or 0, corresponding to whether the memristor is in its high or low resistance state (or vice versa). When used as a logic circuit, the memristor may be employed as configuration bits and switches in a logic circuit that resembles a Field Programmable Gate Array, or may be the basis for a wired-logic Programmable Logic Array. It is also possible to use memristors capable of multi-state or analog behavior for these and other applications.

4

[0013] When used as a switch, the memristor may either be in a low resistance (closed) or high resistance (open) state in a cross-point memory. During the last few years, researchers have made great progress in finding ways to make the switching function of these memristors behave efficiently. For example, tantalum oxide (TaO<sub>x</sub>)-based memristors have been demonstrated to have superior endurance over other nano-scale devices capable of electronic switching. In lab settings, tantalum oxide-based memristors are capable of over 10 billion switching cycles.

[0014] A memristor may comprise a switching material, such as TiO<sub>x</sub> or TaO<sub>x</sub>, sandwiched between two electrodes. Memristive behavior is achieved by the movement of ionic species (e.g., oxygen ions or vacancies) within the switching material to create localized changes in conductivity via modulation of a conductive filament between two electrodes, which results in a low resistance "ON" state, a high resistance "OFF" state, or intermediate states. Initially, when the memristor is first fabricated, the entire switching material may be nonconductive. As such, a forming process may be required to form the conductive channel in the switching material between the two electrodes. A known forming process, often called "electroforming", includes applying a sufficiently high (threshold) voltage across the electrodes for a sufficient length of time to cause a nucleation and formation of a localized conductive channel (or active region) in the switching material. The threshold voltage and the length of time reguired for the forming process may depend upon the type of material used for the switching material, the first electrode, and the second electrode, and the device geometry.

[0015] Metal or semiconductor oxides may be employed in memristive devices; examples include either transition metal oxides, such as tantalum oxide, titanium oxide, yttrium oxide, hafnium oxide, niobium oxide, zirconium oxide, or other like oxides, or non-transition metal oxides, such as aluminum oxide, calcium oxide, magnesium oxide, dysprosium oxide, lanthanum oxide, silicon dioxide, or other like oxides. Further examples include transition metal nitrides, such as aluminum nitride, gallium nitride, tantalum nitride, and silicon nitride.

5

[0016] Memristive devices may include a continuous oxide film between the electrodes. Filaments/ionic diffusion are formed in the oxide film between the electrodes in a random fashion, much like lightning, that may take the path of least resistance. This random path causes variations in the memristor I-V characteristics from switching cycle to cycle and especially from device to device. Older memristive or non-volatile resistive memory devices that are either unipolar or bipolar tend to have this random conductive path between the electrodes; that is, the vacancies have to find their own path to the opposite electrodes. This randomness in the conductive channel formation may cause variability in reproducibility and/or reliability issues, which is one of the biggest challenges in the commercialization of these devices.

[0017] Thermal inkjet (TIJ) technology employs a resistor to boil ink to create a vapor "drive" bubble that ejects a droplet of ink involving rapid nucleation and bubble growth. Compatible to the standard CMOS, the TIJ resistor often may employ a high sheet resistivity and a low sheet resistivity dual metal layer deposition, followed by an etching process. FIGS. 1A-1B depict two examples of TIJ structures.

[0018] The TIJ structure 100 shown in FIG. 1A may use a high resistivity alloy, such as TaAl, WSiN, TaAlOx, TiN or other suitable alloy as a lower layer 102, with an upper layer 104 of a low resistivity alloy, such as AlCu on top. In this structure, the bottom layer 102, which has a relatively high sheet resistance of 30 to 120 ohm/sq, may be first deposited. Next, the top layer 104, which has a relatively low sheet resistance of about 0.04 to 0.08 ohm/sq, may be deposited. Following the depositions, a dry etch (to define the resistor width) and a wet or dry etch (Slope Metal Etch (SME)/Dry Resistor Etch (DRE) process to define resistor length) may be applied to define the resistor 100. One of the aspects of the TIJ resistor 100 is that the Temperature Coefficient of Resistance (TCR) is very low and the resistor is very stable with high endurance for hundreds of thousands or millions of ink droplet firings.

[0019] The TIJ structure 150 shown in FIG. 1B may use a multilayer lower layer 152 of TiN/AlCu, with a high resistivity layer 154 of TaAl, WSiN, TaAlOx, TiN or other suitable alloy on top. Again, the lower layer 152 has a relatively high sheet resistance (about 0.04 to 0.08 ohm/sq) and the upper layer 154 has a relatively low sheet resistance (about 425 ohms/sq). Again, a dry etch, followed by a wet or dry etch, may be used to define the resistor 150. As with the resistor depicted in FIG. 1A, an aspect of the TIJ resistor 150 is that the TCR is very low and the resistor is very stable with high endurance.

[0020] Table I below shows the mainstream of the TIJ resistor architecture currently used in TIJ printheads for the resistors 100 and 150 depicted in FIGS. 1A and 1B, respectively.

Property

TaAl

WSiN

Thickness

~95 nm

95 nm

Sheet ρ

30 ohms/sq

425 ohms/sq

Requires anneal

No

Yes

Table I. Properties of TIJ Resistor Structures

To fire the ink droplet from the TIJ, an electrical pulse from a printer may be applied to the resistor. That pulse is typically a 5- to 35-volt square pulse. The duration varies from 1 to 3 μs, depending on the product. During that time, the resistor, underlayers, and the passivation layers (on top of TIJ resistor) between the resistor and ink heat rapidly. The temperature where liquid contacts the passivation layer jumps from 25°C to a minimum of 310°C. Thus, an extremely steep heating rate (about 100 million°C per second) produces a super heat to generate the bubble to push the ink droplet out.

[0022] In accordance with the teachings herein, a thermal element, such as the TIJ resistor, may be used as a heater under a non-volatile memory element array

as shown in FIG. 2. In this manner, the non-volatile memory element may be heated to a certain temperature, which can be tuned through the TIJ resistor resistance, applied voltage, and pulse. The combination of the non-volatile memory element and the TIJ resistor may find application with resistance memory elements, such as memristors, and with phase change memory elements.

[0023] The controlled heating of the non-volatile memory element may be used to accomplish several different tasks, each depending on a different temperature regime.

[0024] The first task involves using heat to control the resistance level for multi-cell applications. Consider that the temperature regime is identified as  $T_1$ . Multi-cell applications are described in further detail below.

[0025] The second task involves using heat to repair a "dead" non-volatile memory element. In the case of a memristor, for example, a dead memristor is in a low resistance state and thus behaves as a conductor. Heating an array of elements may dissolve the conduction channel and may repair a memristor array with many failed devices. Consider that the temperature regime is identified as  $T_2$ .

[0026] The third task involves using heat to heat an array of non-volatile memory elements, such as memristors, up to an elevated temperature and apply an electrical bias to a memristor in a low resistance state to reset the memristor. Consider that the temperature regime is identified as  $T_3$ .

[0027] The fourth task involves minimizing failures caused by the electroforming (or forming) process. The electroforming process may cause failures due to the relatively high voltages applied. Heating the array and applying a forming voltage could result in a reduction in failures, since a lower voltage may be required for the forming process. Consider that the temperature regime is identified as T<sub>4</sub>.

[0028]  $T_2$  may be a relatively high heat, and is the highest of the four regimes. The other temperature regimes are considered with regard to  $T_2$ .

[0029]  $T_1$  may be within a range of about ambient temperature to below  $T_2$ .

[0030]  $T_3$  may be within a range of above ambient temperature to below  $T_2$ .

[0031]  $T_4$  may be within a range of above ambient temperature to below  $T_2$ .

[0032] The foregoing temperature regimes depend on a variety of factors, including the materials of the non-volatile memory element, or memristor. Determination of a particular temperature regime to accomplish a particular task, and for the person skilled in the art, is not considered to be undue experimentation.

[0033] The device 200 depicted in FIG. 2 may include the thermal element, e.g., thermal inkjet resistor, 202, such as either of the TIJ resistors depicted in FIGS. 1A and 1B. Other thermal elements may alternatively be employed. The thermal inkjet resistor may be disposed on a substrate (not shown). The device 200 may further include one or more resistive memory elements 204, such as a memristor. The memristor 204, or, as shown in FIG. 2, an array 204' of memristors 204, may be separated from the TIJ resistor 202 by a passivation layer 206. Examples of materials suitably used as a passivation layer include, but are not limited to, silicon nitride, silicon carbide, silicon dioxide, and the like.

[0034] The memristor 204 may have a structure that includes a bottom electrode 204a, a top electrode 204b, and an active region 204c sandwiched therebetween. Examples of materials for electrodes 204a, 204b include, but are not limited to, aluminum (AI), copper (Cu), platinum (Pt), tungsten (W), gold (Au), titanium (Ti), silver (Ag), ruthenium dioxide (RuO<sub>2</sub>), titanium nitride (TiN), tungsten nitride (WN<sub>2</sub>), tantalum (Ta), tantalum nitride (TaN) or the like. The electrode materials may be the same or different for the two electrodes 204a, 204b. The electrodes 204a 204b may be patterned, if desired. The thickness of the electrodes 204a, 204b may be in the range of about 10 nm to a few micrometers.

[0035] The bottom electrode 204a may be formed on the passivating layer 206 by any of a number of processes, including electroplating, sputtering, evaporation, ALD (atomic layer deposition), co-deposition, chemical vapor deposition, IBAD (ion beam assisted deposition), oxidation of pre-deposited materials, or any other film deposition technology.

[0036] FIGS. 2A and 2B depict two examples of non-volatile memory elements, such as memristors. In FIG. 2A, the elements 204 are individual, while in FIG.

2B, a portion of a crossbar 204" is shown, with the bottom electrodes forming "rows" and the top electrodes forming "columns", the rows being disposed at a non-zero angle with respect to the columns. It may be appreciated that there can be multiple TIJ resistors, each hooked up to same voltage/pulse condition or different, depending on the application.

[0037] A memristor can be used as non-volatile memory (NVM) and it has the capability of multi-level programming (MLP). Consequently, a method of memristor MLP based on ink-jet printing technology may be employed. It is like introducing a third thermal control gate to 2-terminal memristors. The architecture may be used for phase change memories (PCM) or other resistive RAM (RRAM) devices as well.

[0038] The multi-level programming (MLP) technique disclosed herein may reduce the cost-per-bit through multiple states stored in one cell illustrated in FIGS 3A-3B.

[0039] Memristors usually store 1 bit/cell, with a logic "0" and a logic "1", as depicted in FIG. 3A. Although the logic "0" is shown at a lower resistance and the logic "1" is shown at a higher resistance, the definitions may be reversed, with the logic "0" defined at a higher resistance and the logic "1" defined at the lower resistance.

[0040] Using MLP, 2 bits/cell may be stored, with logic "00" at the lowest resistance, logic "01" defined at the next higher resistance, logic "10" defined at the even next higher resistance, and logic "11" defined at the highest resistance. Of course, as with the 1 bit/cell, the definitions may be reversed so that logic "11" is at the lowest resistance and logic "00" is at the highest resistance, etc.

[0041] The combination of electrical bias and elevated temperatures provided by the built-in TIJ heater can better switch the device to a target resistance value, which is critical for multilevel cell applications. For example, ON state 1 may be done at room temperature, ON state 2 may be done at 150°C, and ON state 3 may be done at 300°C, and so forth.

[0042] FIG. 4 is an I-V plot 400, showing the various resistance states achieved at a temperature of 290K and measured at room temperature. Curve 402 represents a virgin state, in which there has not been applied a forming or switching voltage. Curves 404 and 406 represent two intermediate states. Curve 408 represents an ON state.

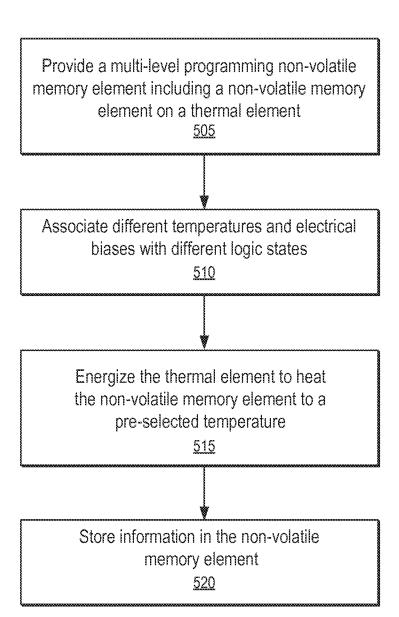

[0043] FIG. 5 is a flow chart, depicting a method of operating a multi-level programming non-volatile memory element 200, according to an example. The method 500 may include providing 505 multi-level programming non-volatile memory element 200, which includes at least one non-volatile memory element, such as a memristor, 204 on a thermal element 202. The method 500 may include further associating 510 different temperatures and electrical biases with different logic states. The method 500 may further include energizing 515 the thermal element to heat the resistive memory element to a pre-selected temperature. The method 500 may further include storing 520 information in the resistive memory element.

[0044] In its most general form, the non-volatile memory element 200 may have multiple states, each associated with a combination of a temperature and electrical bias.

[0045] The heating resistor can be easily incorporated into any standard CMOS process by adding a high resistivity layer and a SME/DRE mask. The additional handle for the local thermal management for memristor devices would act like the third terminal for a transistor (back gate). With the introduction of the heating element as a thermal control gate, the following advantages may be achieved:

[0046] It may be possible to achieve the MLP for memristors with better control using the thermal compared to simply applying different voltages. Further, the distribution of the resistance states may be tighter and the state-to-state resistance gap may be wider for better state differentiation. This may result in a lower bit error rate and an easier sensing scheme to read out the stored information.

11

[0047] In addition to the possibility of realizing multilevel storage, the local temperature control may allow the memristor to operate in a reliable and optimal condition.

[0048] The temperature may be controllable either through voltage or a pulse applied to the resistor, which may lead to design flexibility for the circuit.

# CLAIMS

PCT/US2013/076221

### What is claimed is:

5

15

20

25

30

- 1. A non-volatile memory element with thermal-assisted switching control, wherein the resistive memory element is disposed on a thermal element.

- 2. The non-volatile memory element of claim 1, comprising a memristor.

- 3. The non-volatile memory element of claim 1, wherein the thermal element is a thermal inkjet resistor, the non-volatile memory element further comprising the thermal inkjet resistor, a passivation layer on the thermal inkjet resistor, and the resistive memory element on the passivation layer.

- 4. The non-volatile memory element of claim 3, in which the thermal inkjet resistor comprises a relatively low resistivity electrically conducting material disposed on a relatively high resistivity electrically conducting material.

- 5. The non-volatile memory element of claim 4, in which the thermal inkjet resistor is selected from the group consisting of AlCu on TaAl, AlCu on WSiN, AlCu on TaAlOx, AlCu on TiN, TaAl on TiN/AlCu, WSiN on TiN/AlCu, TaAlOx on TiN/AlCu, and TiN on TiN/AlCu.

- The non-volatile memory element of claim 3, wherein the passivation layer is selected from the group consisting of silicon nitride, silicon carbide, and silicon dioxide.

- 7. The non-volatile memory element of claim 3, wherein the resistive memory element is a memristor having a structure that includes a bottom electrode, an active region, and a top electrode.

- 8. A method of manufacturing a multi-level programming non-volatile memory element, including disposing a non-volatile memory element on a thermal element.

- 9. The method of claim 8, comprising:

5

10

15

20

25

30

providing a thermal inkjet resistor as the thermal element; forming a passivation layer on the thermal inkjet resistor; and forming the non-volatile on the passivation layer.

- 10. The method of claim 9, in which the thermal inkjet resistor comprises a relatively low resistivity electrically conducting material disposed on a relatively high resistivity electrically conducting material.

- 11. The method of claim 10, in which the thermal inkjet resistor is selected from the group consisting of AlCu on TaAl, AlCu on WSiN, AlCu on TaAlOx, AlCu on TiN, TaAl on TiN/AlCu, WSiN on TiN/AlCu, TaAlOx on TiN/AlCu, and TiN on TiN/AlCu.

- 12. The method of claim 9, wherein the passivation layer is selected from the group consisting of silicon nitride, silicon carbide, and silicon dioxide.

- 13. The method of claim 9, wherein the non-volatile memory element is a memristor having a structure that includes a bottom electrode, an active region, and a top electrode.

- 14. A method of operating a multi-level programming non-volatile memory element including a non-volatile memory element on a thermal element, the method including:

- providing the multi-level programming non-volatile memory element including the non-volatile memory element on the thermal element;

- associating different temperatures and electrical biases with different logic states;

energizing the thermal element to heat the non-volatile memory element to a pre-selected temperature; and storing information in the non-volatile memory element.

5

10

15. The method of claim 14 in which the non-volatile memory element has multiple states, each associated with a combination of a temperature and electrical bias.

Fig. 1A

Fig. 1B

Fig. 4

<u>500</u>

Fig. 5

International application No. **PCT/US2013/076221**

## A. CLASSIFICATION OF SUBJECT MATTER

H01L 27/115(2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols) H01L 27/115; H01L 45/00; H01L 21/8247; G11C 11/00; G11C 29/04

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Korean utility models and applications for utility models

Japanese utility models and applications for utility models

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) eKOMPASS(KIPO internal) & Keywords: non-volatile memory, memristor, thermal element, thermal inkjet resistor

### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Х         | US 2011-0261608 A1 (JULIEN BORGHETTI et al.) 27 October 2011<br>See abstract, paragraphs [0017]-[0062] and figures 1-7.           | 8                     |

| Y<br>A    | see abstract, paragraphs [0017] [0002] and Figures 1 7.                                                                           | 1-2<br>3-7,9-15       |

| Y         | KR 10-2011-0050011 A (GWANGJU INSTITUE OF SCIENCE AND TECHNOLOGY) 13 May 2011                                                     | 1-2                   |

| A         | See abstract, paragraphs [0015]-[0064] and figures 1-9g.                                                                          | 3-15                  |

| A         | US 2013-0003438 A1 (CORY MERKEL et al.) 03 January 2013<br>See abstract, paragraphs [0042]-[0049] and figures 1-4, 7.             | 1–15                  |

| A         | US 2011-0182108 A1 (R. STANLEY WILLIAMS et al.) 28 July 2011<br>See abstract, paragraphs [0012], [0015]-[0069] and figures 1A-6B. | 1-15                  |

| A         | US 2013-0250708 A1 (GADIEL SEROUSSI et al.) 26 September 2013 See abstract, paragraphs [0011]-[0026] and figures 1-7.             | 1–15                  |

|           |                                                                                                                                   |                       |

|           |                                                                                                                                   |                       |

|  |  | Further | documents | are lis | sted in | the | continuation | on of | Box | C. |

|--|--|---------|-----------|---------|---------|-----|--------------|-------|-----|----|

|--|--|---------|-----------|---------|---------|-----|--------------|-------|-----|----|

$\times$

See patent family annex.

- \* Special categories of cited documents:

- "A" document defining the general state of the art which is not considered to be of particular relevance

- 'E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- 'O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

- "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

- "&" document member of the same patent family

Date of mailing of the international search report

Date of the actual completion of the international search 30 September 2014 (30.09.2014)

30 September 2014 (30.09.2014)

Name and mailing address of the ISA/KR

()

International Application Division Korean Intellectual Property Office 189 Cheongsa-ro, Seo-gu, Daejeon Metropolitan City, 302-701, Republic of Korea

Facsimile No. +82-42-472-7140

Authorized officer

CHOI, Sang Won

Telephone No. +82-42-481-8291

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No.

# PCT/US2013/076221

| Patent document cited in search report | Publication<br>date | Patent family member(s)                                                                                                        | Publication<br>date                                                                                          |

|----------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| US 2011-0261608 A1                     | 27/10/2011          | US 8605484 B2<br>WO 2010-087833 A1                                                                                             | 10/12/2013<br>05/08/2010                                                                                     |

| KR 10-2011-0050011 A                   | 13/05/2011          | None                                                                                                                           |                                                                                                              |

| US 2013-0003438 A1                     | 03/01/2013          | US 8750065 B2                                                                                                                  | 10/06/2014                                                                                                   |

| US 2011-0182108 A1                     | 28/07/2011          | CN 102265397 A EP 2368268 A1 EP 2368268 A4 EP 2368268 B1 JP 2012-513686 A KR 10-2011-0116005 A US 8605483 B2 WO 2010-074689 A1 | 30/11/2011<br>28/09/2011<br>26/12/2012<br>09/07/2014<br>14/06/2012<br>24/10/2011<br>10/12/2013<br>01/07/2010 |

| US 2013-0250708 A1                     | 26/09/2013          | US 8750062 B2<br>WO 2012-015438 A1                                                                                             | 10/06/2014<br>02/02/2012                                                                                     |