**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>5</sup>

G01R 31/26

(45) 공고일자 1990년04월11일

(11) 공고번호 90-002324

---

|           |               |           |               |

|-----------|---------------|-----------|---------------|

| (21) 출원번호 | 특1986-0002927 | (65) 공개번호 | 특1987-0003393 |

| (22) 출원일자 | 1986년04월16일   | (43) 공개일자 | 1987년04월17일   |

---

|            |                                                 |

|------------|-------------------------------------------------|

| (30) 우선권주장 | 209418 1985년09월20일 일본(JP)                       |

| (71) 출원인   | 미쓰비시전기 주식회사 시끼모리야<br>일본국 토쿄도 지요다구 마루노우치 2쵸메 2-3 |

|          |                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| (72) 발명자 | 다다 데쓰오<br>일본국 효고Ken 이다미시 미즈하라 4쵸메 1번지 미쓰비시전기주식회사<br>엘, 에스, 아이 겐쿠쇼나이<br>마에노 히데시<br>일본국 효고Ken 이다미시 미즈하라 4쵸메 1번지 미쓰비시전기주식회사<br>엘, 에스, 아이 겐쿠쇼나이 |

| (74) 대리인 | 정우훈, 박태경                                                                                                                                    |

**심사관 : 박충범 (책자공보 제1829호)**

---

**(54) 반도체 시험장치**

---

**요약**

내용 없음.

**대표도**

**도1**

**명세서**

[발명의 명칭]

반도체 시험장치

[도면의 간단한 설명]

제 1 도는 본 발명의 일실시예를 표시하는 블록도.

제 2 도는 제 1 도의 실시예에 있어서의 동작의 일례를 설명하기 위한 도면.

제 3 도는 이 발명의 다른 실시예를 표시하는 블록도.

제 4 도는 이 발명의 또 다른 실시예를 표시하는 블록도.

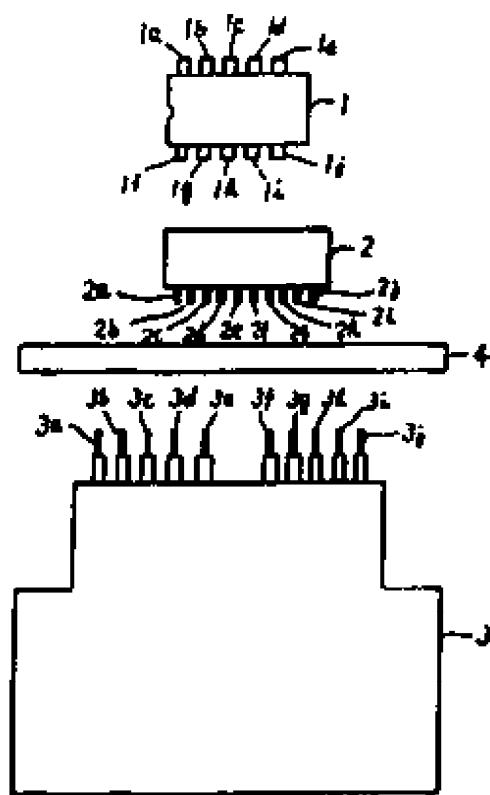

제 5 도는 종래의 반도체시험장치의 일례를 표시하는 외관도.

제 6 도는 제 5 도에 표시하는 종래의 반도체시험장치의 접속관계표시도.

\* 도면의 주요부분에 대한 부호의 설명

1 : DUP

2 : 소켓

3 : 테스터

4 : 로드보드(load board)

1a~1j : DUT(1)의 단자

3a~3j, 3FD, 3FC, 3GND, 3VCC : 포고핀(pogo pin)

GND : 접지

PS : 전원

FV<sub>1</sub>~FV<sub>10</sub>, FG<sub>1</sub>~FG<sub>10</sub> : 기억소자

RV<sub>1</sub>~RV<sub>10</sub>, RG<sub>1</sub>~RG<sub>10</sub> : 릴레이

4a~4j : 로드보드내의 배선

SR<sub>1</sub>~SR<sub>20</sub> : 온, 오프제어신호발생회로

A : 포고핀

R<sub>1</sub>, R<sub>2</sub>, RV, RG : 릴레이

## [발명의 상세한 설명]

이 발명은 반도체시험장치에 관하여 특히 복수개의 단자가 있는 피시험용 반도체장치에 테스트신호를 보내는 동시에 전원계를 접속하여 테스트프로그램에 따라서 해당시험용 반도체장치의 시험을 실시하는 반도체 시험장치에 관한 것이다.

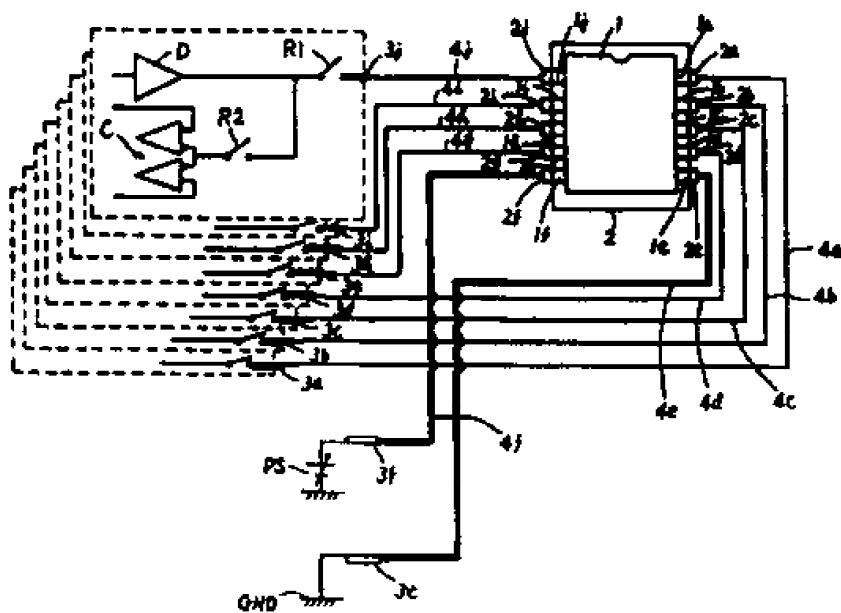

제 5 도는 종래의 반도체장치의 일례를 표시하는 외관도이다. 이 도면에서 이 반도체장치는 미리 정해진 테스트프로그램에 따라 피시험용 반도체장치(이하 DUT라 칭함)(1)의 시험을 실시하는 것이며, 소켓(2)과 테스터(3)와 로드보드(4)로 구성된다. DUT(1)에는 외부기기와의 접속을 도모하기위한 단자(1a)~(1j)가 설치된다. 소켓(2)는 DUT(1)의 착탈이 자유롭게 구성되어 있으며 DUT(1)의 단자(1a)~(1j)와 동수의 단자(2a)~(2j)가 설치된다. 또한 소켓(2)에 장착된 DUT(1)의 단자(1a)~(1j)와 소켓(2)의 단자(2a)~(2j)는 1대1의 상태로 되어있다. 반도체시험장치 본체가되는 테스터(3)은 DUT(1)과의 사이의 테스트신호의 수수(授授) 및 전원의 수수를 행하는 것이며 이 테스트 신호 및 전원을 입출력하기 위한 단자(3a)~(3j)가 설치된다. 또 이 단자(3a)~(3j)는 통상 포고핀(3a)~(3j)로 지정하고 있으므로 이 명세서에는 이 명칭을 사용한다. 로드보드(4)는 소켓(2)와 테스터(3)사이의 접속을 도모하기 위한 것으로 테스터(3)로부터의 테스트신호 및 전원을 소켓(2)의 단자(2a)~(2j)에 정확히 전하는 구조로 되어있다.

상기와 같은 반도체시험장치로는 테스터(3)로부터 DUT(1)로의 신호인가는 예를들면 포고핀(3j)→로드보드(4)상의 배선→단자(2j)→단자(1j)로 전달되며 DUT(1)로부터의 출력은 그 경로의 역순으로 되어 테스터(3)으로 전달된다.

제 6 도는 제 5 도에 표시하는 반도체시험장치의 접속관계를 표시하는 도면이다. 이 도면에서 테스터(3)의 내부에는 각포핀에 대응하여 점선으로 표시하는 핀전자카드가 설치된다. 이 핀전자카드는 카드형상의 기판에 여러가지 회로를 실장한것이며 예를 들면 드라이버(D)와 비교회로(C)와 릴레이(R<sub>1</sub>) 및 (R<sub>2</sub>)으로 형성된다. 드라이버(D)는 신호출력경로에 삽입되어있으며 비교회로(C)는 신호입력경로에 삽입되어 있다.

릴레이(R<sub>1</sub>) 및 (R<sub>2</sub>)는 드라이버(D) 및 비교회로(C)와 각 포고핀사이의 접속관계를 절환하기 위한으로 테스트프로그램에 의하여 그 온,오프(ON,OFF)가 제어된다. 또 테스터(3)의 내부에는 전원(PS)와 접지(GND)가 설치된다.

이예에서는 전원(PS)는 포고핀(3f)에 접속되어 접지(GND)는 포고핀(3e)에 접속된다.

접지(GND)는 접지전위를 부가하기위한 전원이며 전원(PS)는 접지전위와는 다른전위를 부가하기위한 전원이므로 이 명세서에서는 전원(PS) 및 접지(GND)를 포함하여 전원계로 취급하는 것으로 한다.

또한 테스터(3)에는 상기 구성이외에도 상기 테스트프로그램을 기억하는 기억장치나 테스트신호발생장치 등이 설치되지만 이 발명과는 직접 관계가 없으므로 그도시 및 설명을 생략한다. 로드보드(4)에는 포고핀(3a)~(3j)와 소켓(2)의 단자(2a)~(2j)의 전기적 접속을 실시하기 위한 배선(4a)~(4j)가 설치된다. 여기서 DUT(1)로의 전원공급은 전원(PS) 포고핀(3f) 배선(4f) 단자(2f) 단자(1f) 또는 접지(GND) 포고핀(3e) 배선(4e) 단자(2e) 단자(1e)의 경로가 된다. 통상 이들의 전원경로는 로드보드(4)상에는 와이어링(wiring)접속 되어있고 고정경로로 되어있다.

이상과같이 종래의 반도체시험장치에서는 전원계 접속경로는 고정으로 되어있었다. 그러나 DUT(1)은 온단자(1e) 및 (1f)가 전원단자로서 반드시 사용되는 것은 아니고 기타의 단자가 전원단자로서 사용되는 경우도 있다. 그 때문에 시험을 실시하는 DUT(1)의 종류가 상이하면 그에따라 전원계 접속경로의 배선경로를 변경하지 않으면 안되며 범용성이 없다는 문제점이 있었다. 이러한 문제를 해소하기 위하여 배선관계를 다르게한 복수의 로드보드(4)를 미리 준비해두고, DUT(1)의 종류에 따라 적절한 로드보드(4)를 선택하여 시험을 실시하는 일도 고려될 수 있다. 그러나 이러한 방법으로는 DUT(1)의 종류가 상이할때마다 로드보드를 교체하지 않으면 안되어 불편하다.

또 복수조의 로드보드를 준비하지않으면 안되며 시험비용이 증가하게된다. 이 발명은 상기와같은 문제점을 해소하기 위한 것으로서 적어도 패키지형상이 동일한 DUT에 대하여는 로드보드를 교체하는 일없이 임의로 전원계 접속경로를 변경가능하며 따라서 범용성이 풍부하고 또한 시험비용을 절감할 수 있는 반도체시험장치를 제공하는 것을 목적으로 한다.

이 발명에 관한 반도체시험장치는 테스트프로그램에 부가된 접속관계지정 프로그램에 의하여 테스트신호와 피시험용 반도체장치의 단자와의 접속관계를 임의로 절환하는 동시에 전원과 피시험용 반도체장치의 단자의 접속관계를 임의로 절환하도록 한것이다.

이 발명의 테스트신호절환수단은 테스트프로그램에 부가된 접속관계지정 프로그램을 받아서 테스트신호와 피시험용 반도체장치의 단자의 접속관계를 절환한다. 또 전원계 절환수단은 상기 접속관계지정프로그램을 받아서 전원계와 피시험용 반도체장치의 접속관계를 절환한다.

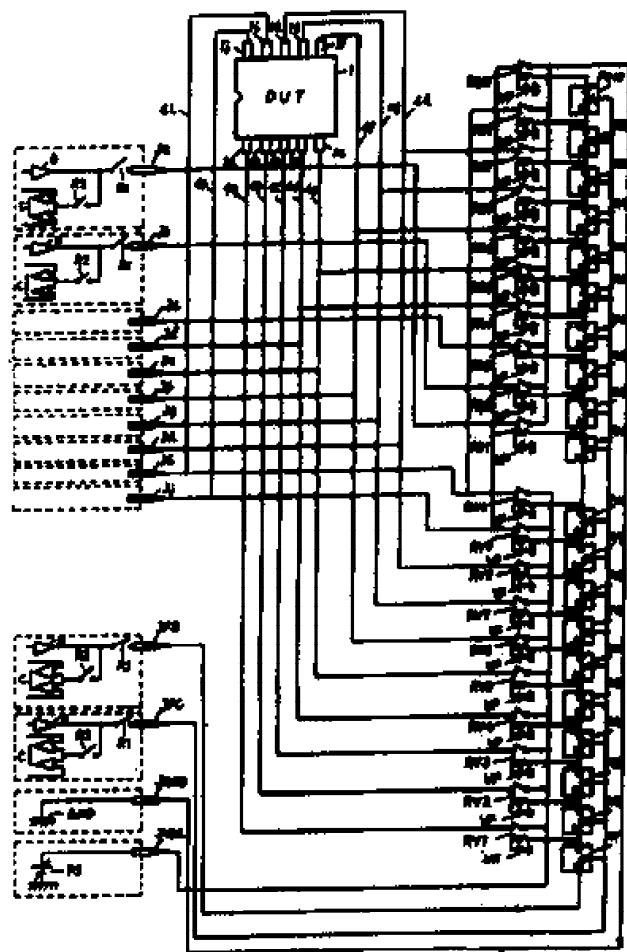

제 1 도는 이 발명의 일실시예를 표시하는 블록도이며 이 도면에서 테스터에는 포고핀(3a)~(3j)에 부가하여 포고핀 3FD, 3FC, 3GND, 3VCC가 설치된다.

포고핀(3a)~(3j)는 테스트신호의 입출력을 실시하는 것이다. 또 포고핀(3FD) 및 (3FC)는 테스트프로그램에 포함되는 접속관계 지정프로그램에 기초하여 후술하는 기억소자 설정용의 직렬식데이터와 쉬프트클럭(shift clock)를 출력하기 위한 것이다.

또 포고핀(3GND) 및 (3VCC)는 테스터내부의 전원계와 외부기기의 접속을 도모하기 위한 것이다.

테스터내부에는 상기 포고핀(3a)~(3j), (3FD)~(3FC)의 각각에 대응하여 같은 구성의 핀전자카드가 설

치된다.

이들 핀전자카드는 상술의 제 6 도와 같이 드라이버(D), 비교회로(C), 릴레이( $R_1$ ) 및 ( $R_2$ )등이 실장되는 것이다.

또 테스터의 내부에는 포고핀(3GND)와 접지(GND)를 접속하기 위한 핀 전자카드가 설치되며 또 포고핀(3VCC)와 전원(PS)를 접속하기 위한 핀전자카드가 설치된다.

한편 로드보드에는 제 6 도의 경우와같이 배선(4a)~(4j)이 설치된다. 이들 배선 (4a)~(4j)는 제 5 도에 표시하는 소켓(2)를 통하여 DUT(1)의 단자(1a)~(1j)와 각각 접속된다.

또 본설시예의 로드보드에는 DUT(1)의 단자(1A)~(1j)마다 기억소자( $FG_1$ )~( $FG_{10}$ ), ( $FV_1$ )~( $FV_{10}$ )과 릴레이( $R_1$ )~( $R_{10}$ ), ( $RV_1$ )~( $RV_{10}$ )이 설치된다.

기억소자( $FG_1$ )~( $FG_{10}$ ) 및 릴레이( $RG_1$ )~( $RG_{10}$ )은 테스터내부의 접지(GND)와 DUT(1)의 단자(1a)~(1j)의 접속관계를 절환하기 위한 것이다.

또 기억소자( $FV_1$ )~( $FV_{10}$ ) 및 릴레이( $RV_1$ )~( $RV_{10}$ )은 테스터내부의 전원(PS)와 DUT(1)의 단자(1a)~(1j)의 접속관계를 절환하기 위한 것이다.

기억소자 ( $FV_1$ )~( $FV_{10}$ ), ( $FG_1$ )~( $FG_{10}$ )에는 예를들면 플립플롭이 사용된다. 이들 기억소자( $FV_1$ )~( $FV_{10}$ ), ( $FG_1$ )~( $FG_{10}$ )은 그 순번으로 계속 접속되어 소위 쉬프트레지스터를 구성하고 있다. 각 기억소자의 클럭단자(CA)에는 상기 포고핀(3FC)로부터 쉬프트클럭이 입력된다.

상기 쉬프트레지스터는 이 쉬프트클럭을 동기하여 쉬프트동작을 수행한다.

상기 쉬프트클럭의 초단이 되는 기억소자( $FV_1$ )의 데이터단자에는 상기 포고핀(3FD)에서 전원계의 접속관계를 지정하기위한 직렬식데이터가 부여된다.

각 기억소자의 Q출력은 다음단의 기억소자로 송출된다. 또 기억소자( $FV_1$ )~( $FV_{10}$ )의 Q출력은 각각 릴레이( $RV_1$ )~( $RV_{10}$ )의 작동코일의 일단에 부여되면 기억소자( $FG_1$ )~( $FG_{10}$ )의 출력은 각각 릴레이( $RG_1$ )~( $RG_{10}$ )의 작동코일의 일단에 부여된다.

각 작동코일의 타단에는 릴레이작동봉 전원(VF)가 접속된다. 따라서 각 릴레이는 대응의 기억소자의 Q출력이 영(0)일때 작동코일에 전류가 흘러 온 즉 폐로상태로 되며 대응의 Q출력이 1일때 작동코일로의 전원공급이 정지되어 오프 즉 개로상태가 된다.

릴레이( $RG_1$ )~( $RG_{10}$ )의 개폐지점의 한쪽단자에는 포고핀(3GND)가 공통 접속된다. 또 릴레이( $RD_1$ )~( $RD_{10}$ )의 개폐접점의 다른쪽단자는 각각 상기 배선(4a)~(4j)와 접속된다.

한편 릴레이( $RV_1$ )~( $RV_{10}$ )의 각 개폐접점의 한쪽단자는 포고핀(3VCC)과 공통접속되고 각 개폐접점의 다른쪽단자는 각각 배선(4a)~(4j)와 접속된다.

다음에 제 1 도의 실시예의 동작을 설명한다. 우선 전원계 접속경로 형성회로를 구성하는 기억소자군( $FV_1$ )~( $FV_{10}$ ), ( $FG_1$ )~( $FG_{10}$ )의 논리상태를 결정하기 위하여 테스터의 포고핀(3FC)에서 쉬프트클럭이 출력되어 포고핀(3FD)에서 전원계의 접속관계를 지정하기위한 직렬식데이터가 출력된다. 또한 포고핀(3FD)에서 출력되는 직렬식데이터에는 포고핀(3FC)에서 출력되는 쉬프트클럭에 동기하여 출력된다. 출력되는 직렬식데이터는 기억소자( $FV_1$ )의 데이터소자(DA)에 부여되어 먼저 최초의 비트가 기억소자( $FV_1$ )에 기억된다. 그후 기억소자( $FV_1$ )에는 순차후속의 비트의 데이터에 부여되지만 먼저 부여된 데이터는 포고핀(3FC)로부터의 쉬프트클럭에 동기하여 순차 다음 단계의 기억소자로 쉬프트되어간다. 그래서 직렬식데이터의 선두비트가 최종단의 기억소자( $FG_{10}$ )에 기억된곳에서 직렬식데이터의 출력이 정지되어 각각 기억소자로의 데이터설정이 종료된다. 여기서 예를들면 DUT(1)의 단자(1f)를 테스터내부의 전원(PS)와 접속하는 경우에 관하여 설명한다.

이 경우 기억소자( $FV_1$ )~( $FV_{10}$ )중에서 기억소자  $FV_6$ 의 Q출력단이 영이되도록 데이터가 설정되며 또한 기억소자 ( $FG_1$ )~( $FG_{10}$ )중 기억소자( $FG_6$ )의 Q출력만이 1이되도록 데이터가 설정된다. 이에 의하여 릴레이( $RV_6$ )이 온이되고 단자(1f)와 테스터내부의 전원(PS)가 접속된다. 또 릴레이( $RG_6$ )가 오프로되어 단자(1f)와 테스터내부의 접지(GND)가 접속되지않게 된다.

또한 포고핀(3f)에 접속된 테스터내부의 핀전자카드에 있어서 릴레이( $R_1$ )이 오프되어 단자(1f)와 테스터내부의 신호라인과의 접속도 차단된다. 따라서 단자(1f)는 테스터내부에 전원(PS)에만 접속되게 된다.

다음에 DUT(1)의 단자(1e)와 테스터내부의 접지(GND)와를 접속하는 경우에 관하여 설명한다. 이 경우 기억소자( $FV_1$ )~( $FV_{10}$ )중 기억소자( $FV_5$ )의 Q출력만 1이 되도록 데이터가 설정된다.

이에 의하여 릴레이( $RV_5$ )가 오프로되어 단자(1e)와 테스터내부의 전원(PS)의 접속이 차단되는 동시에 릴레이( $RG_5$ )가 온이되어 단자(1e)와 테스터내부의 접지(GND)가 접속된다.

또한 동시에 포고핀(3e)에 접속된 핀전자카드에 있어서의 릴레이( $R_1$ )이 오프되어 단자(1f)와 테스터내부의 신호라인의 접속이 차단된다. 따라서 단자(1e)는 접지(GND)하고만 접속된다.

또한 제 2 도에는 단자(1f)와 전원(PS)를 접속하는 경우, 단자(1e)와 접지(GND)와를 접속하는 경우,

단자(1d)와 포고핀(3d)에 연결되는 신호라인을 접속하는 경우에 있어서의 각 기억소자의 Q출력과 각 릴레이의 온, 오프상태의 관계를 표시해 놓는다.

이상 몇가지 예를 들어서 제 1 도의 동작을 설명하였지만 기타의 접속관계에 관하여 상기와 같은 방법으로 실시되는 것이다.

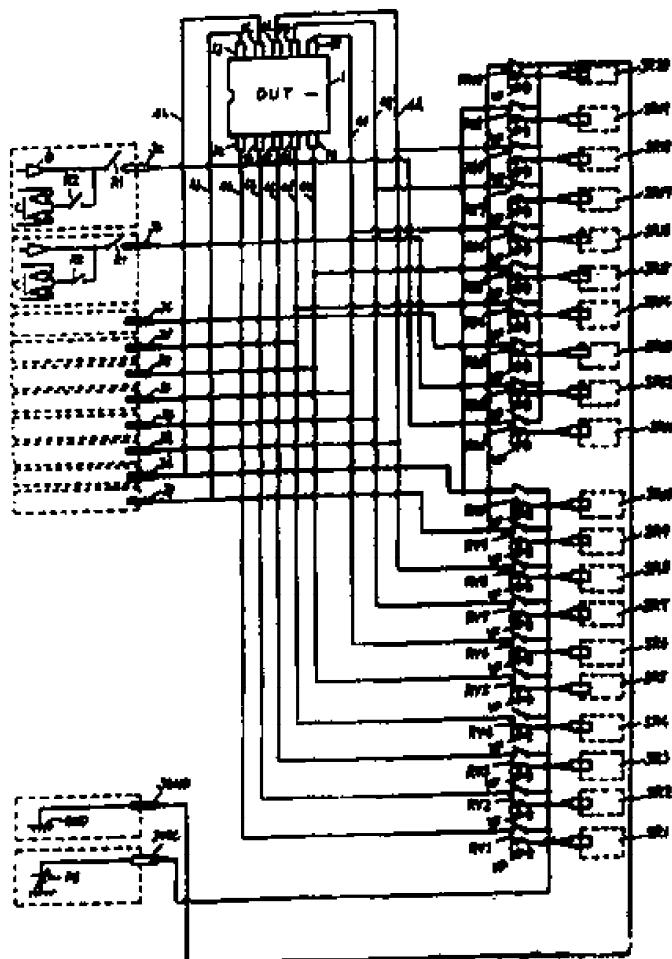

제 1 도의 실시예에서는  $(RV_1) \sim (RV_{10}), (RG_1) \sim (RG_{10})$ 의 온, 오프를 기억소자( $FV_1) \sim (FV_{10}), (FG_1) \sim (FG_{10})$ 의 논리출력상태로 제어시켰지만, 제 3 도에 표시한바와같이 테스터내부에 온, 오프제어신호발생회로  $(SR_1) \sim (SR_{20})$ 를 설치하여, 이들 온, 오프제어신호발생회로 발생되는 제어신호에 의하여 직접 각 릴레이( $(RV_1) \sim (RV_{10}), (RG_1) \sim (RG_{10})$ )의 온, 오프를 제어하도록 하여도된다.

이 경우 온, 오프제어신호발생회로( $SR_1) \sim (SR_{20})$ )에서 발생되는 온, 오프제어신호는 적어도 DUT(1)의 테스트가 종료될때까지는 그 출력상태를 보지해둘 필요가 있다.

또, 제 1 도 및 제 3 도의 실시예에서는 DUT(1)의 단자(1a)~(1f)와 테스터 내부에 전원계와의 접속 관계를 절환하기 위한 수단을 모두 로드보드상에 작성하였지만 테스터내부의 편전자카드내 이들의 기능을 설치할 수도 있다.

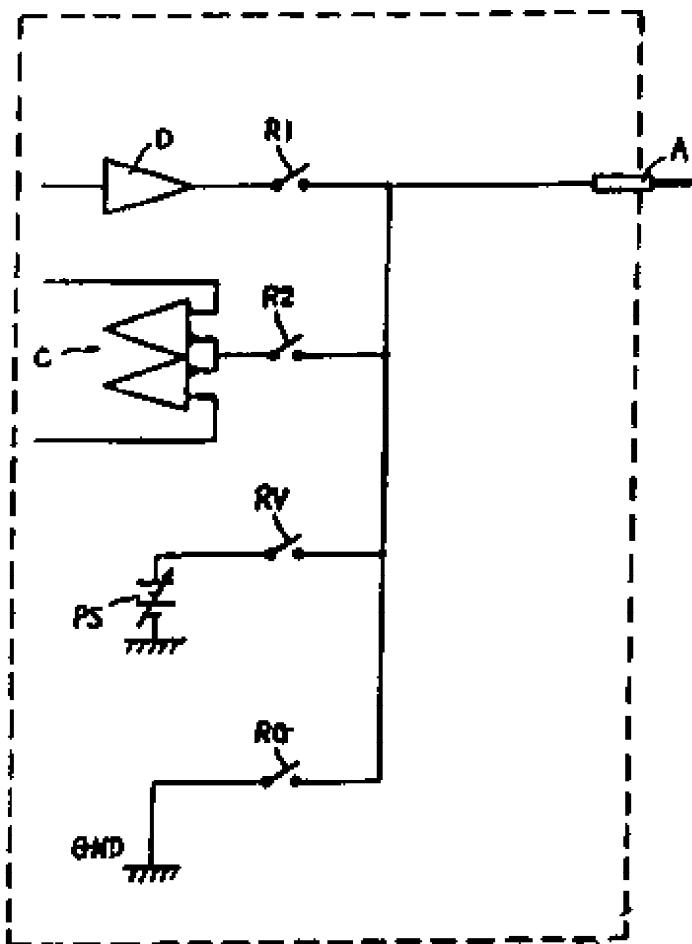

예를 들면 제 4 도에 표시한대로 각 포고핀(A)(제 1 도의 포고핀(3a)~(3j)에 대응한다)에 접속되는 편전자카드내에 전원(PS)와 접지(GND)를 설치한다.

또 전원(PS)와 포고핀(A)사이에 릴레이(RV)를 삽입하여, 접지(GND)와 포고핀(A)사이에 릴레이(RG)를 삽입한다. 그래서 테스트프로그램내에 부가된 접속관계 지정프로그램에 의하여 릴레이( $(R_1)(R_2)(RV)(RG)$ )의 온, 오프를 제어한다. 즉 릴레이( $R_1$ )에 의하여 포고핀(A)와 드라이버(D)의 접속상태를 제어하여 릴레이( $R_2$ )에 의하여 포고핀(A)와 비교회로(C)의 접속상태를 제어하고 릴레이(RV)에 의하여 포고핀(A)과 전원(PS)의 접속상태를 제어하며 릴레이(RG)에 의하여 포고핀(A)와 접지(GND)의 접속상태를 제어한다.

이에 의하여 포고핀(A)는 드라이버(D)를 포함하는 출력신호라인, 비교회로(C)를 포함하는 입력신호라인, 전원(PS), 접지(GND)와 각각 독립적으로 접속, 차단이 제어된다.

이상과 같이 본 발명에 의하면 테스트프로그램에 부가된 접속관계 지정프로그램에 의하여 피시험용 반도체장치의 단자와 전원계의 접속상태를 임의로 절환할수가 있으므로 동일 패키지형상의 피시험용 반도체장치이면은 로드보드를 교환하는 일없이 시험을 실시할수가 있다.

따라서 범용성이 우수하고 또한 시험비용을 삼감할수 있는 반도체시험장치를 제공할수가 있다.

## (57) 청구의 범위

### 청구항 1

복수개의 단자(1a~1j)가 있는 피시험용 반도체장치(1)에 테스트 신호를 부여하는 동시에 전원계(PS, GND)를 접속하고 미리 정해진 테스트 프로그램에 따라서 해당피시험용 반도체장치(1)의 시험을 실시하는 반도체시험장치이며, 상기 테스트프로그램에는 상기 테스트신호 및 전원계(PS, GND)와 상기 피시험용 반도체장치(1)의 단자(1a~1j)의 접속관계를 지정하기위한 접속관계 지정프로그램(제 2 도)이 부가되며, 상기 접속관계 지정프로그램(제 2 도)을 받아서 상기 테스트신호와 상기 피시험용 반도체장치(1)의 단자(1a~1j)의 접속관계를 절환하기위한 테스트신호절환수단(C)(D)( $R_1(R_2)$ ) 및 상기 접속관계 지정프로그램(제 2 도)을 받아서 상기 전원계(PS, GND)와 상기 피시험용 반도체장치(1)의 단자(1a~1j)와의 접속관계를 절환하기위한 전원계통 절환수단( $(RG_1) \sim (RG_{10}), (RV_1 \sim RV_{10})(VF)(FG_1 \sim FG_{10}), (FV_1 \sim FV_{10})$ )을 구비한 반도체시험장치.

### 청구항 2

제 1 항에 있어서, 반도체시험장치는 반도체시험장치본체(3)와, 상기 반도체시험장치본체(3) 및 상기 피시험용 반도체장치(1)가 착탈자재하여 또한 상기 반도체시험장치본체(3)와 상기 피시험용 반도체장치(1)의 접속을 도모하기 위한 배선이 장착된 접속수단(2)(4)으로 구성되고, 상기 테스트신호절환수단(C)(D)( $R_1(R_2)$ )은 상기 반도체시험장치본체(3)에 실시되며, 상기 전원계절환수단( $(RG_1) \sim (RG_{10}), (RV_1 \sim RV_{10})(VF)(FG_1 \sim FG_{10}), (FV_1 \sim FV_{10})$ )은 상기 접속수단(2)(4)에 설치되는 반도체시험장치.

### 청구항 3

제 2 항에 있어서, 상기 전원계절환수단( $(RG_1) \sim (RG_{10}), (RV_1 \sim RV_{10})(VF)(FG_1 \sim FG_{10}), (FV_1 \sim FV_{10})$ )은 상기 피시험용반도체장치(1)의 단자(1a~1j)마다 설치되며 상기 접속관계 지정프로그램에 의하여 그 기억상태가 2치(置)적으로 절환되는 기억소자( $FG_1 \sim FG_{10}), (FV_1 \sim FV_{10})$ )와, 상기 피시험용반도체장치(1)의 단자(1a~1j)마다 설치되어 상기 기억소자( $FG_1 \sim FG_{10}), (FV_1 \sim FV_{10})$ )의 출력에 의하여, 온, 오프가 절환되었 상기 피시험용반도체장치(1)의 단자(1a~1j)와 상기 전원계(PS)(GND)의 접속을 선택적으로 절환하는 릴레이회로( $(RG_1) \sim RG_{10}), (RV_1 \sim RV_{10})(VF)$ )를 포함하는 반도체시험장치.

### 청구항 4

제 3 항에 있어서, 상기 전원계(PS)(GND)는 접지전위(電位)를 부여하기위한 전원(GND)과 접지전위와는 상이한 전위를 부여하기위한 전원(PS)의 2계통이 설치되고, 상기 기억소자( $FG_1 \sim FG_{10}), (FV_1 \sim FV_{10})$ ) 및 릴레이회로( $(RG_1) \sim RG_{10})(VF)$ )는 상기 2계통의 전원(PS)(GND)에 대응하여 각각 2조식 설치되는 반도체

시험장치.

### 청구항 5

제 2 항에 있어서, 상기 반도체시험장치 본체(3)는 상기 접속관계 지정프로그램에 따라서 상기 피시험용 반도체장치(1)의 단자(1a~1j)와 상기 전원계(PS)(GND)사이의 접속관계를 절환 제어하기 위한 절환제어신호를 발생하며, 상기 전원계절환수단( $RG_1 \sim (RG_{10})$ ,  $(RV_1 \sim RV_{10})$ (VF)( $FG_1 \sim FG_{10}$ ),  $(FV_1 \sim FV_{10})$ )은 상기 피시험용 반도체장치(1)의 단자(1a~1j)마다 설치되어, 상기 절환제어신호를 수신하여 그 온, 오프가 제어되고, 그에 따라서 상기 피시험용 반도체장치(1)의 단자(1a~1j)와 상기 전원계(PS)(GND)의 접속을 선택적으로 절환하는 릴레이회로( $RG_1 \sim (RG_{10})$ ,  $(RV_1 \sim RV_{10})$ (VF))하는 반도체시험장치.

### 청구항 6

제 5 항에 있어서 상기 전원계(PS)(GND)는 접지전위를 부여하기 위한 전원(GND)과 접지전위와는 상이한 전위를 부여하기 위한 전원(PS)의 2계통이 설치되고, 상기 릴레이회로( $RG_1 \sim (RG_{10})$ ,  $(RV_1 \sim RV_{10})$ (VF))는 상기 2계통의 전원(PS)(GND)에 대응하여 각각 2조식 설치되는 반도체시험장치.

### 청구항 7

제 1 항에 있어서, 반도체시험장치본체(3)와, 상기 반도체시험장치본체(3) 및 상기 피시험용반도체장치(1)가 착탈자재하며, 또한 반도체시험장치본체(3)와 피시험용 반도체장치(1)와의 접속을 도모하기 위한 배선(4a~4f)이 실시된 접속수단(2)(4)으로 구성되며, 상기 테스트신호절환수단(C)(D)( $R_1$ )( $R_2$ ) 및 전원계 절환수단( $RG_1 \sim (RG_{10})$ ,  $(RV_1 \sim RV_{10})$ (VF)( $FG_1 \sim FG_{10}$ ),  $(FV_1 \sim FV_{10})$ )은 모두 상기 반도체시험장치본체(3)에 설치되는 반도체시험장치.

### 청구항 8

제 7 항에 있어서, 상기 반도체시험장치본체(3)에는 상기 피시험용 반도체장치(1)의 단자(1a~1f)마다 테스트신호 수수회로(C)(D)와 전원계회로(GND)(PS)가 형성되고, 상기 테스트신호절환수단(C)(D)( $R_1$ )( $R_2$ )은 상기 접속관계 지정프로그램에 따라 상기 각 테스트신호수수회로(C)(D)와 피시험용 반도체장치(1)의 단자(1a~1j)사이의 접속 및 차단하는 제 1의 스위치수단( $R_1$ )( $R_2$ )을 포함하며 상기 전원계절환수단( $RG_1 \sim (RG_{10})$ ,  $(RV_1 \sim RV_{10})$ (VF)( $FG_1 \sim FG_{10}$ ),  $(FV_1 \sim FV_{10})$ )은 상기 전원계회로(GND)(PS)와 상기 피시험용 반도체장치(1)의 단자(1a~1j)간의 접속 및 차단하는 제 2의 스위치수단( $RG_1 \sim RG_{10}$ ),  $(RV_1 \sim RV_{10})$ (VF)( $FG_1 \sim FG_{10}$ ),  $(FV_1 \sim FV_{10})$ )을 포함하는 반도체시험장치.

### 청구항 9

제 8 항에 있어서, 상기 전원계회로는 접지전위를 부여하기 위한 전원(GND)과 접지전위와는 상이한 전위를 부여하기 위한 전위(PS)의 2계통이 설치되고, 상기 각 제 2의 스위치수단( $RG_1 \sim (RG_{10})$ ,  $(RV_1 \sim RV_{10})$ ( $FG_1 \sim FG_{10}$ ),  $(FV_1 \sim FV_{10})$ )은 상기 2계통의 전원(GND)(PS)에 대응하여 각각 2조식 설치되는 반도체시험장치.

## 도면

도면1

도면2

| DUT 단자 | 주석                 | 기匣호자 회로와 연결되는<br>설비 회로 | 설비 회로 단자, 회로 구조       |

|--------|--------------------|------------------------|-----------------------|

| 11     | 전원                 | FV6회로에 D1과 FV6회로에 Q11  | RVS가 6 R6가 22 R11이 22 |

| 14     | 점지                 | FV5회로에 Q11, FV5회로에 Q10 | RVS가 32 R6가 6 R14가 22 |

| 15     | 32.768kHz<br>(2.1) | FV5회로에 Q10, FV6회로에 Q10 | RVS가 22 R6가 22 R14가 6 |

도면3

도면4

도면5

도면6