(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0134125

(43) 공개일자 2010년12월22일

(51) Int. Cl.

G09G 3/30 (2006.01)

(21) 출원번호 10-2010-7025898

(22) 출원일자(국제출원일자) 2009년04월17일

심사청구일자 없음

(85) 번역문제출일자 2010년11월18일

(86) 국제출원번호 PCT/CA2009/000502

(87) 국제공개번호 WO 2009/127065

국제공개일자 2009년10월22일(30) 우선권주장

61/046,256 2008년04월18일 미국(US)

(71) 출원인

이그니스 이노베이션 인크.

캐나다 온타리오 키치너 스위트

1020 프레데릭 스트리트 22

(72) 발명자

나단 애로키아

영국 캠브릿지 씨비3 0디엘 헌팅던 로드 189

차지 지 레자

캐나다 온타리오 엔브리 2에스3 워털루 켈소 드

라이브 463

알렉산더 스텝판

캐나다 온타리오 엔3비 2엔1 엘미라 아서 스트립

에스 91

(74) 대리인

신정건, 김태홍

전체 청구항 수 : 총 28 항

(54) 발광 소자 디스플레이에 대한 시스템 및 구동 방법

**(57) 요 약**

발광 소자 디스플레이, 그의 픽셀 회로 및 그의 구동 기술이 제공된다. 픽셀은 발광 소자 및 복수의 트랜지스터를 포함한다. 구동 트랜지스터를 통한 발광 소자에의 전류가 조정되는 구동 방식에 따라 바이어스 전류 및 프로그래밍 전압 데이터가 픽셀 회로에 제공된다.

**대 표 도** - 도24

## 특허청구의 범위

### 청구항 1

픽셀 회로에 있어서,

발광 소자;

상기 발광 소자에 픽셀 전류를 제공하기 위한 구동 트랜지스터 - 상기 구동 트랜지스터는 게이트 단자, 상기 발광 소자에 연결된 제1 단자, 및 제2 단자를 가짐 - ;

프로그래밍 접합 데이터를 제공하는 데이터 라인과 상기 구동 트랜지스터의 게이트 단자 사이에 제공된 스토리지 커뮤니케이터;

상기 구동 트랜지스터의 게이트 단자와 상기 구동 트랜지스터의 제1 단자 사이에 제공된 제1 스위치 트랜지스터; 및

프로그래밍 사이클 동안 상기 구동 트랜지스터의 제1 단자에 바이어스 전류를 제공하는 바이어스 라인과 상기 구동 트랜지스터의 제1 단자 사이에 제공된 제2 스위치 트랜지스터를 포함하는 픽셀 회로.

### 청구항 2

청구항 1에 있어서, 상기 제1 스위치 트랜지스터의 게이트 단자와 상기 제2 스위치 트랜지스터의 게이트 단자는 단일 선택 라인에 의해 동작되는 것인 픽셀 회로.

### 청구항 3

청구항 1에 있어서, 상기 제2 스위치 트랜지스터는 바이어스 라인에 연결된 제1 단자 및 상기 발광 소자와 상기 구동 트랜지스터 사이의 접속 노드에 연결된 제2 단자를 포함하는 것인 픽셀 회로.

### 청구항 4

청구항 1에 있어서, 상기 프로그래밍 접합 데이터는 상이한 그레이 스케일에 대한 상이한 전류 레벨의 전류를 분배하기 위한 복수의 접합 신호를 포함하는 것인 픽셀 회로.

### 청구항 5

청구항 1에 있어서, 상기 발광 소자는 유기 발광 다이오드를 포함하는 것인 픽셀 회로.

### 청구항 6

청구항 1에 있어서, 상기 트랜지스터들 중 적어도 하나는 박막 트랜지스터인 것인 픽셀 회로.

### 청구항 7

청구항 1에 있어서, 상기 트랜지스터는 폴리 실리콘, 나노/마이크로(결정질) 실리콘, 비정질 실리콘, CMOS, 유기 반도체, 금속 유기 기술, 또는 이들의 조합을 사용하여 구현되는 것인 픽셀 회로.

### 청구항 8

청구항 1에 있어서, 상기 픽셀 회로는 능동 매트릭스 어레이를 형성하는 것인 픽셀 회로.

### 청구항 9

픽셀 회로에 있어서,

발광 소자;

제1 단자 및 제2 단자를 갖는 스토리지 커뮤니케이터;

상기 발광 소자에 픽셀 전류를 제공하는 구동 트랜지스터 - 상기 구동 트랜지스터는 게이트 단자, 상기 스토리

지 커패시터의 제1 단자에 연결된 제1 단자, 상기 발광 소자에 연결된 제2 단자를 가짐 - ;

제1 선택 라인에 의해 동작되며, 프로그래밍 전압 데이터를 제공하는 데이터 라인과 상기 스토리지 커패시터의 제2 단자 사이에 제공된 제1 스위치 트랜지스터;

상기 제1 선택 라인에 의해 동작되며, 프로그래밍 사이클 동안 상기 구동 트랜지스터의 제1 단자에 바이어스 전류를 제공하는 바이어스 라인과 상기 스토리지 커패시터의 제1 단자 사이에 제공된 제2 스위치 트랜지스터; 및

상기 픽셀 회로를 방출 모드(emission mode)로 설정하는 방출 제어 회로를 포함하는 픽셀 회로.

#### 청구항 10

청구항 9에 있어서, 상기 방출 제어 회로는,

상기 구동 트랜지스터의 제1 단자와 제1 포텐셜 사이에 연결된 제3 스위치 트랜지스터;

상기 스토리지 커패시터의 제2 단자와 상기 구동 트랜지스터의 게이트 단자 사이에 연결된 제4 스위치 트랜지스터; 및

상기 구동 트랜지스터의 게이트 단자와 제2 포텐셜 사이에 연결된 제5 스위치 트랜지스터를 포함하는 것인 픽셀 회로.

#### 청구항 11

청구항 10에 있어서, 상기 제3 및 제4 스위치 트랜지스터는 제2 선택 라인에 의해 동작되고, 상기 제5 스위치 트랜지스터는 상기 제1 선택 라인에 의해 동작되는 것인 픽셀 회로.

#### 청구항 12

청구항 9에 있어서, 상기 프로그래밍 전압 데이터는 상이한 그레이 스케일에 대한 상이한 전류 레벨의 전류를 분배하기 위한 복수의 전압 신호를 포함하는 것인 픽셀 회로.

#### 청구항 13

청구항 9에 있어서, 상기 발광 소자는 유기 발광 다이오드를 포함하는 것인 픽셀 회로.

#### 청구항 14

청구항 9에 있어서, 상기 트랜지스터들 중 적어도 하나는 박막 트랜지스터인 것인 픽셀 회로.

#### 청구항 15

청구항 9에 있어서, 상기 트랜지스터는 폴리 실리콘, 나노/마이크로 (결정질) 실리콘, 비정질 실리콘, CMOS, 유기 반도체, 금속 유기 기술, 또는 이들의 조합을 사용하여 구현되는 것인 픽셀 회로.

#### 청구항 16

청구항 9에 있어서, 상기 픽셀 회로는 능동 매트릭스 어레이를 형성하는 것인 픽셀 회로.

#### 청구항 17

디스플레이 시스템에 있어서,

각각이 청구항 1에 정의된 것인 복수의 픽셀 회로를 갖는 픽셀 어레이;

픽셀 회로를 선택하는 제1 구동기;

상기 프로그래밍 전압 데이터를 제공하는 제2 구동기; 및

상기 바이어스 라인에 대해 동작하는 전류 소스를 포함하는 디스플레이 시스템.

#### 청구항 18

청구항 17에 있어서, 상기 전류 소스는,

기준 전류에 기초하여 상기 바이어스 라인에 대해 동작하는 보정된 전류 미러(calibrated current mirror);

전압을 상기 바이어스 전류로 변환시키는 전압-전류 변환기

중 적어도 하나를 포함하는 것인 디스플레이 시스템.

#### 청구항 19

청구항 17에 있어서, 상기 전류 소스는 메모리에 저장된 데이터를 통하여 보정되는 것인 디스플레이 시스템.

#### 청구항 20

디스플레이 시스템에 있어서,

각각이 청구항 9에 정의된 것인 복수의 픽셀 회로를 갖는 픽셀 어레이;

픽셀 회로를 선택하는 제1 구동기;

상기 프로그래밍 전압 데이터를 제공하는 제2 구동기; 및

상기 바이어스 라인에 대해 동작하는 전류 소스를 포함하는 디스플레이 시스템.

#### 청구항 21

청구항 20에 있어서, 상기 전류 소스는,

기준 전류에 기초하여 상기 바이어스 라인에 대해 동작하는 보정된 전류 미러;

전압을 상기 바이어스 전류로 변환하기 위한 전압-전류 변환기

중 적어도 하나를 포함하는 것인 디스플레이 시스템.

#### 청구항 22

청구항 20에 있어서, 상기 전류 소스는 메모리에 저장된 데이터를 통하여 보정되는 것인 디스플레이 시스템.

#### 청구항 23

픽셀 회로를 구동하는 방법에 있어서,

상기 픽셀 회로는 발광 소자에 픽셀 전류를 제공하는 구동 트랜지스터, 데이터 라인에 연결된 스토리지 커패시터, 및 상기 스토리지 커패시터와 상기 구동 트랜지스터의 게이트 단자에 연결된 스위치 트랜지스터를 가지며, 상기 방법은,

프로그래밍 사이클에서, 픽셀 회로를 선택하고, 상기 구동 트랜지스터와 상기 발광 소자 사이의 접속에 바이어스 전류를 제공하고, 상기 데이터 라인으로부터 상기 픽셀 회로에 프로그래밍 전압 데이터를 제공하는 것을 포함하는 것인, 픽셀 회로의 구동 방법.

#### 청구항 24

픽셀 회로를 구동하는 방법에 있어서,

상기 픽셀 회로는 발광 소자에 픽셀 전류를 제공하는 구동 트랜지스터, 데이터 라인에 연결된 스위치 트랜지스터, 및 상기 스토리지 커패시터를 가지며, 상기 방법은,

프로그래밍 사이클에서, 픽셀 회로를 선택하고, 상기 구동 트랜지스터의 제1 단자에 바이어스 전류를 제공하고, 상기 데이터 라인으로부터 상기 스토리지 커패시터의 제1 단자에 프로그래밍 전압 데이터를 제공하고 - 상기 스토리지 커패시터의 제2 단자는 상기 구동 트랜지스터의 제1 단자에 연결되어 있고, 상기 구동 트랜지스터의 제2 단자는 상기 발광 소자에 연결되어 있음 - ,

구동 사이클에서, 상기 픽셀 회로에 방출 모드를 설정하는 것을 포함하는 것인, 픽셀 회로의 구동 방법.

#### 청구항 25

청구항 1에 있어서, 상기 바이어스 전류는 미리 결정된 고정 전류인 것인 픽셀 회로.

## 청구항 26

청구항 9에 있어서, 상기 바이어스 전류는 미리 결정된 고정 전류인 것인 픽셀 회로.

## 청구항 27

청구항 23에 있어서, 상기 바이어스 전류는 미리 결정된 고정 전류인 것인 픽셀 회로의 구동 방법.

## 청구항 28

청구항 24에 있어서, 상기 바이어스 전류는 미리 결정된 고정 전류인 것인 픽셀 회로의 구동 방법.

## 명세서

### 기술 분야

[0001] 본 발명은 발광 소자 디스플레이(light emitting device display)에 관한 것으로, 보다 상세하게는 발광 소자 디스플레이에 대한 구동 기술에 관한 것이다.

### 배경 기술

[0002] 최근 비정질 실리콘(a-Si), 폴리실리콘, 유기, 또는 기타 구동 백플레인 기술을 이용한 능동 매트릭스 유기 발광 다이오드(AMOLED; active-matrix organic light-emitting diode) 디스플레이가 능동 매트릭스 액정 디스플레이 이상의 이점으로 인해 점점 더 관심을 끌고 있다. 예를 들어 a-Si 백플레인을 사용한 AMOLED 디스플레이 는 다양한 기관들의 사용을 넓히는 저온 제조를 포함하는 이점을 갖고 플렉서블 디스플레이를 실현 가능하게 하며, 그의 저비용 제조가 확립되어 있고 넓은 시야각을 갖는 고해상도 디스플레이를 산출한다.

[0003] AMOLED 디스플레이는 픽셀들의 행 및 열 어레이를 포함하며, 각각 행 및 열 어레이로 정렬되어 있는 유기 발광 다이오드(OLED; organic light-emitting diode) 및 백플레인 전자부품을 갖는다. OLED는 전류 구동 소자 (current driven device)이므로, AMOLED의 픽셀 회로는 정확하고 일정한 구동 전류를 제공할 수 있어야 한다.

[0004] AMOLED 디스플레이를 구동하는데 채용된 하나의 방법은 전류로 직접 AMOLED 픽셀을 프로그래밍하는 것이다. 그러나, OLED가 필요로 하는 작은 전류가 큰 기생 커패시턴스와 결합되어, 전류 프로그래밍된 AMOLED 디스플레이의 프로그래밍의 정착 시간(settling time)을 불리하게 증가시킨다. 또한, 외부 구동기(driver)가 필요한 전류를 정확하게 공급하도록 설계하는 것이 어렵다. 예를 들어, CMOS 기술에서, 트랜지스터는 OLED가 필요로 하는 작은 전류를 제공하도록 서브문턱(sub-threshold) 체제로 작업하여야 하는데, 이는 이상적이지 못하다. 따라서, 전류 프로그래밍된 AMOLED 픽셀 회로를 사용하기 위하여, 적합한 구동 방식이 추구된다.

[0005] 전류 스케일링(current scaling)은 OLED가 필요로 하는 작은 전류와 연관된 문제들을 관리하는데 사용될 수 있는 하나의 방법이다. 전류 미러(current mirror) 픽셀 회로에서는, 미러 트랜지스터에 비교하여 더 작은 구동 트랜지스터를 가짐으로써 OLED를 통과하는 전류가 스케일링될 수 있다. 그러나, 이 방법은 기타 전류 프로그래밍된 픽셀 회로에는 적용 가능하지 않다. 또한, 2개의 미러 트랜지스터를 리사이징(resizing)함으로써 부정합(mismatch)의 영향이 증가된다.

### 발명의 내용

#### 해결하려는 과제

[0006] 본 발명의 목적은 기존의 시스템의 단점을 중 적어도 하나를 없애거나 완화시키는 방법 및 시스템을 제공하는 것이다.

#### 과제의 해결 수단

[0007] 본 발명의 양상에 따르면, 픽셀 회로에 있어서, 발광 소자, 상기 발광 소자에 픽셀 전류를 제공하기 위한 구동 트랜지스터, 프로그래밍 전압 데이터를 제공하는 데이터 라인과 상기 구동 트랜지스터의 게이트 단자 사이에 제공된 스토리지 커패시터(storage capacitor), 상기 구동 트랜지스터의 게이트 단자와 상기 발광 소자 사이에 제공된 제1 스위치 트랜지스터, 및 프로그래밍 사이클(programming cycle) 동안 상기 구동 트랜지스터의 제1 단자에 바이어스 전류를 제공하는 바이어스 라인과 상기 발광 소자 사이에 제공된 제2 스위치 트랜지스터를 포함하

는 픽셀 회로가 제공된다.

[0008] 본 발명의 부가적인 양상에 따르면, 픽셀 회로에 있어서, 발광 소자, 스토리지 커패시터, 상기 발광 소자에 픽셀 전류를 제공하는 구동 트랜지스터, 제1 선택 라인에 의해 동작되는 복수의 제1 스위치 트랜지스터 - 상기 제1 스위치 트랜지스터의 하나는 프로그래밍 전압 데이터를 제공하는 데이터 라인과 상기 스토리지 커패시터 사이에 제공됨 - , 제2 선택 라인에 의해 동작되는 복수의 제2 스위치 트랜지스터 - 상기 제2 스위치 트랜지스터의 하나는 프로그래밍 사이클 동안 상기 구동 트랜지스터의 제1 단자에 바이어스 전류를 제공하는 바이어스 라인과 상기 구동 트랜지스터 사이에 제공됨 - , 및 상기 픽셀 회로를 방출 모드(emission mode)로 설정하는 방출 제어 회로를 포함하는 픽셀 회로가 제공된다.

[0009] 본 발명의 부가적인 양상에 따르면, 디스플레이 시스템에 있어서, 복수의 픽셀 회로를 갖는 픽셀 어레이, 픽셀 회로를 선택하는 제1 구동기, 프로그래밍 전압 데이터를 제공하는 제2 구동기, 및 바이어스 라인에 대해 동작하는 전류 소스를 포함하는 디스플레이 시스템이 제공된다.

[0010] 본 발명의 부가적인 양상에 따르면, 발광 소자에 픽셀 전류를 제공하는 구동 트랜지스터, 데이터 라인에 연결된 스토리지 커패시터, 및 상기 스토리지 커패시터와 상기 구동 트랜지스터의 게이트 단자에 연결된 스위치 트랜지스터를 갖는 픽셀 회로를 구동하는 방법이 제공된다. 상기 방법은, 프로그래밍 사이클에서, 픽셀 회로를 선택하고, 상기 구동 트랜지스터와 상기 발광 소자 사이의 접속에 바이어스 전류를 제공하고, 상기 데이터 라인으로부터 상기 픽셀 회로에 프로그래밍 전압 데이터를 제공하는 것을 포함한다.

[0011] 본 발명의 부가적인 양상에 따르면, 발광 소자에 픽셀 전류를 제공하는 구동 트랜지스터, 데이터 라인에 연결된 스위치 트랜지스터, 및 상기 스위치 트랜지스터와 상기 구동 트랜지스터에 연결된 스토리지 커패시터를 갖는 픽셀 회로를 구동하는 방법이 제공된다. 상기 방법은, 프로그래밍 사이클에서, 픽셀 회로를 선택하고, 상기 구동 트랜지스터의 제1 단자에 바이어스 전류를 제공하고, 상기 데이터 라인으로부터 상기 스토리지 커패시터의 제1 단자에 프로그래밍 전압 데이터를 제공하고 - 상기 스토리지 커패시터의 제2 단자는 상기 구동 트랜지스터의 제1 단자에 연결되어 있고, 상기 구동 트랜지스터의 제2 단자는 상기 발광 소자에 연결되어 있음 - , 구동 사이클(driving cycle)에서, 상기 픽셀 회로에 방출 모드를 설정하는 것을 포함한다.

[0012] 이러한 본 발명의 개요가 반드시 본 발명의 모든 특징들을 기술하는 것은 아니다.

[0013] 첨부 도면과 함께 바람직한 실시예의 다음의 상세한 설명을 검토하여 본 발명의 기타 양상 및 특징이 당해 기술 분야에서의 숙련자에게 용이하게 명백할 것이다.

### 발명의 효과

[0014] 본 발명에 따르면, 발광 소자 디스플레이에 대한 시스템 및 구동 방법을 제공할 수 있다.

### 도면의 간단한 설명

[0015] 본 발명의 이들 및 기타 특징이 첨부 도면을 참조한 다음의 설명으로부터 보다 명백해질 것이다.

도 1은 본 발명의 실시예에 따른 픽셀 회로를 도시하는 도면이다.

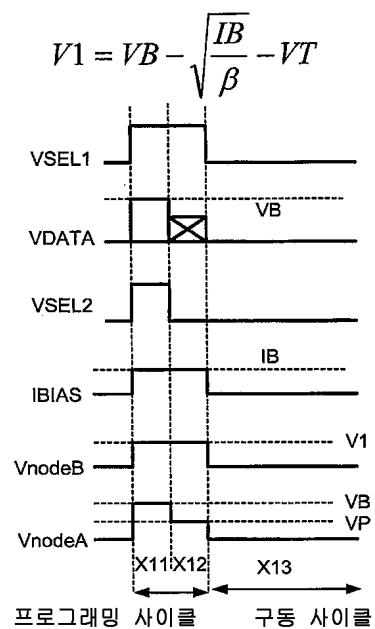

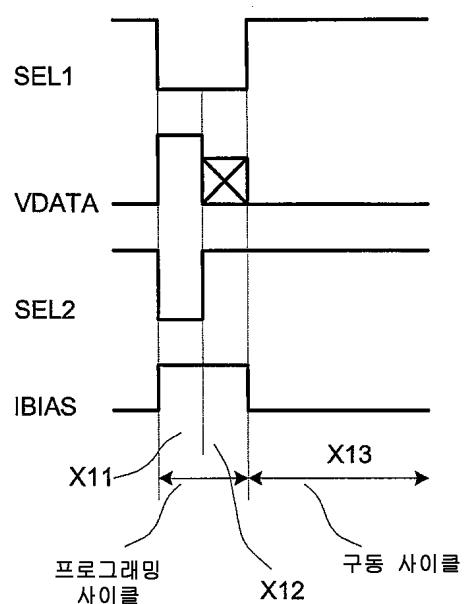

도 2는 도 1의 픽셀 회로에 인가되는 예시적인 과형을 도시하는 타이밍도이다.

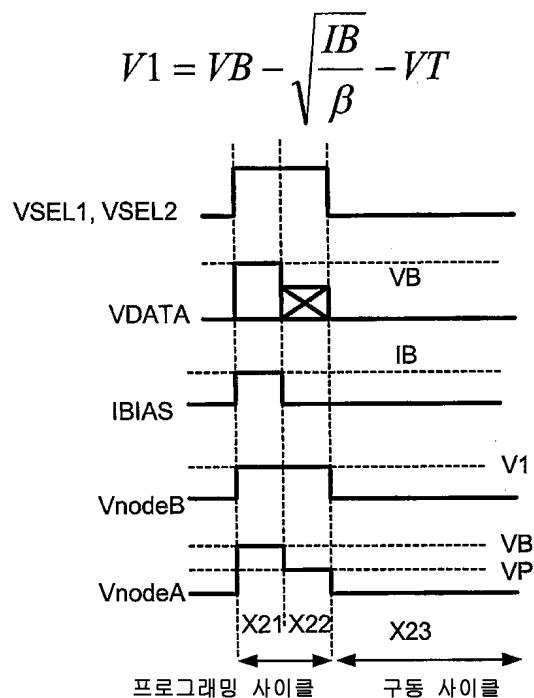

도 3은 도 1의 픽셀 회로에 인가되는 부가의 예시적인 과형을 도시하는 타이밍도이다.

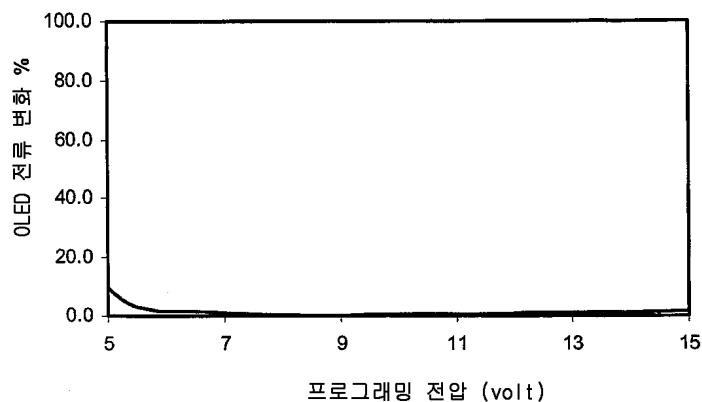

도 4는 도 1의 픽셀 회로의 전류 안정성을 도시하는 그래프이다.

도 5는 p형 트랜지스터를 가지며 도 1의 픽셀 회로에 대응하는 픽셀 회로를 도시하는 도면이다.

도 6은 도 5의 픽셀 회로에 인가되는 예시적인 과형을 도시하는 타이밍도이다.

도 7은 도 5의 픽셀 회로에 인가되는 부가의 예시적인 과형을 도시하는 타이밍도이다.

도 8은 본 발명의 부가적인 실시예에 따른 픽셀 회로를 도시하는 도면이다.

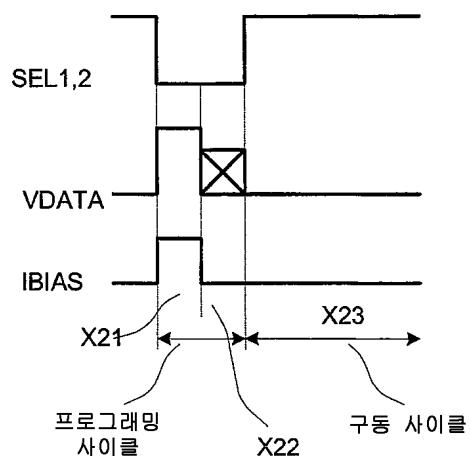

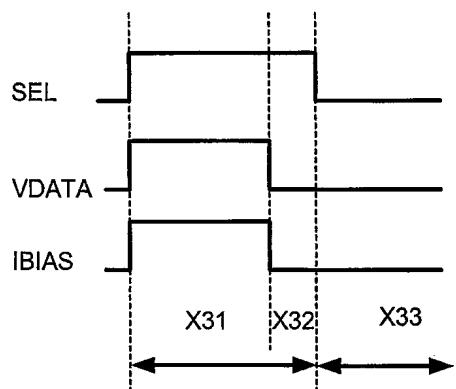

도 9는 도 8의 픽셀 회로에 인가되는 예시적인 과형을 도시하는 타이밍도이다.

도 10은 p형 트랜지스터를 가지며 도 8의 픽셀 회로에 대응하는 픽셀 회로를 도시하는 도면이다.

도 11은 도 10의 픽셀 회로에 인가되는 예시적인 과형을 도시하는 타이밍도이다.

도 12는 본 발명의 실시예에 따른 픽셀 회로를 도시하는 도면이다.

도 13은 도 12의 디스플레이에 인가되는 예시적인 파형을 도시하는 타이밍도이다.

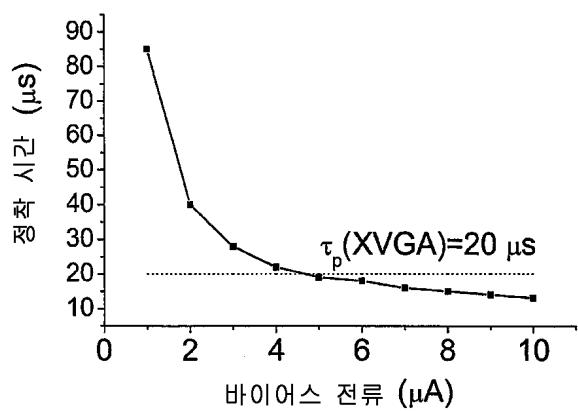

도 14는 다양한 바이어스 전류들에 대한 CBVP 픽셀 회로의 정착 시간을 도시하는 그래프이다.

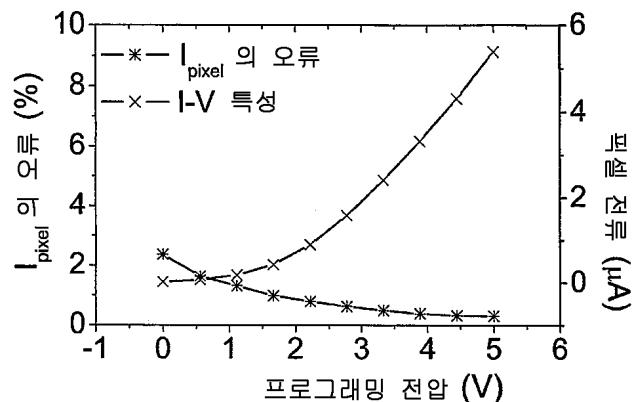

도 15는 CBVP 픽셀 회로의 I-V 특성 뿐만 아니라 픽셀 전류에 유도되는 총 오류를 도시하는 그래프이다.

도 16은 p형 트랜지스터를 가지며 도 12의 픽셀 회로에 대응하는 픽셀 회로를 도시하는 도면이다.

도 17은 도 16의 디스플레이에 인가되는 예시적인 파형을 도시하는 타이밍도이다.

도 18은 본 발명의 부가적인 실시예에 따른 VBCP 픽셀 회로를 도시하는 도면이다.

도 19는 도 18의 픽셀 회로에 인가되는 예시적인 파형을 도시하는 타이밍도이다.

도 20은 p형 트랜지스터를 가지며 도 18의 픽셀 회로에 대응하는 VBCP 픽셀 회로를 도시하는 도면이다.

도 21은 도 20의 픽셀 회로에 인가되는 예시적인 파형을 도시하는 타이밍도이다.

도 22는 CBVP 픽셀 회로를 갖는 디스플레이 어레이에 대한 구동 메커니즘을 도시하는 도면이다.

도 23은 VBCP 픽셀 회로를 갖는 디스플레이 어레이에 대한 구동 메커니즘을 도시하는 도면이다.

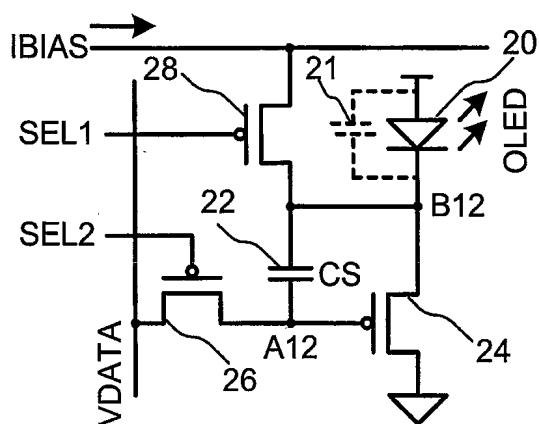

도 24는 본 발명의 부가적인 실시예에 따른 픽셀 회로를 도시하는 도면이다.

도 25는 도 24의 픽셀 회로에 인가되는 예시적인 파형을 도시하는 타이밍도이다.

도 26은 본 발명의 부가적인 실시예에 따른 픽셀 회로를 도시하는 도면이다.

도 27은 도 26의 픽셀 회로에 인가되는 예시적인 파형을 도시하는 타이밍도이다.

도 28은 CBVP 픽셀 회로를 갖는 디스플레이 시스템의 부가적인 예를 도시하는 도면이다.

도 29는 CBVP 픽셀 회로를 갖는 디스플레이 시스템의 부가적인 예를 도시하는 도면이다.

도 30은 간단한 2-TFT 픽셀 회로를 사용한 디스플레이에 대해 공간적 부정합이 미치는 영향을 나타내는 사진이다.

도 31은 전압 프로그래밍된 회로를 사용한 디스플레이에 대해 공간적 부정합이 미치는 영향을 나타내는 사진이다.

도 32는 CBVP 픽셀 회로를 사용한 디스플레이에 대해 공간적 부정합이 미치는 영향을 나타내는 사진이다.

### 발명을 실시하기 위한 구체적인 내용

[0016]

본 발명의 실시예들은 유기 발광 다이오드(OLED) 및 구동 박막 트랜지스터(TFT; thin film transistor)를 갖는 픽셀을 사용하여 설명된다. 그러나, 픽셀은 OLED가 아닌 다른 임의의 발광 소자를 포함할 수 있고, 픽셀은 TFT가 아닌 다른 임의의 구동 트랜지스터를 포함할 수 있다. 본 명세서에서 "픽셀 회로"와 "픽셀"은 상호 교환적으로 사용될 수 있다는 것을 유의한다.

[0017]

이제 전류 바이어싱된 전압 프로그래밍된(CBVP; current-biased voltage-programmed) 구동 방식을 포함하는 픽셀에 대한 구동 기술에 대해 상세하게 기재된다. CBVP 구동 방식은 전압을 사용하여 다양한 그레이 스케일(gray scales)을 제공하고(전압 프로그래밍), 바이어스를 사용하여 프로그래밍을 가속화하고 문턱 전압 시프트(threshold voltage shift) 및 OLED 전압 시프트와 같은 픽셀의 시간 의존적(time dependent) 파라미터를 보상한다.

[0018]

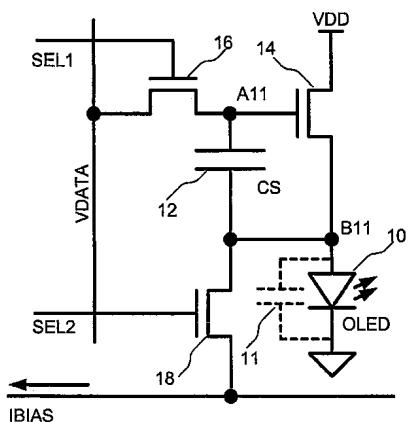

도 1은 본 발명의 실시예에 따른 픽셀 회로(200)를 도시한다. 픽셀 회로(200)는 아래에서 설명되는 바와 같은 CBVP 구동 방식을 채용한다. 도 1의 픽셀 회로(200)는 OLED(10), 스토리지 커패시터(12), 구동 트랜지스터(14), 및 스위치 트랜지스터(16 및 18)를 포함한다. 각각의 트랜지스터는 게이트 단자, 제1 단자 및 제2 단자를 갖는다. 본 명세서에서, "제1 단자"(제2 단자")는 드레인 단자 또는 소스 단자(소스 단자 또는 드레인 단자)일 수 있지만, 이에 한정되는 것은 아니다.

[0019]

트랜지스터(14, 16 및 18)는 n형 TFT 트랜지스터이다. 픽셀 회로(200)에 적용되는 구동 기술은 또한 도 5에 도

시된 바와 같은 p형 트랜지스터를 갖는 상보형(complementary) 픽셀 회로에도 적용 가능하다.

[0020] 트랜지스터(14, 16 및 18)는 비정질 실리콘, 나노/마이크로 결정질 실리콘, 폴리 실리콘, 유기 반도체 기술(예를 들어, 유기 TFT), NMOS 기술, 또는 CMOS 기술(예를 들어, MOSFET)을 사용하여 제조될 수 있다. 복수의 픽셀 회로(200)가 AMOLED 디스플레이 어레이를 형성할 수 있다.

[0021] 2개의 선택 라인 SEL1 및 SEL2, 신호 라인 VDATA, 바이어스 라인 IBIAS, 전압 공급 라인 VDD, 및 공통 접지(common ground)가 픽셀 회로(200)에 제공된다. 도 1에서, 공통 접지는 OLED 상부 전극을 위한 것이다. 공통 접지는 픽셀 회로의 일부가 아니며, OLED(10)가 형성될 때 최종 단계에 형성된다.

[0022] 구동 트랜지스터(14)의 제1 단자는 전압 공급 라인 VDD에 접속된다. 구동 트랜지스터(14)의 제2 단자는 OLED(10)의 애노드 전극에 접속된다. 구동 트랜지스터(14)의 게이트 단자는 스위치 트랜지스터(16)를 통하여 신호 라인 VDATA에 접속된다. 스토리지 커패시터(12)는 구동 트랜지스터(14)의 제2 단자와 게이트 단자 사이에 접속된다.

[0023] 스위치 트랜지스터(16)의 게이트 단자는 제1 선택 라인 SEL1에 접속된다. 스위치 트랜지스터(16)의 제1 단자는 신호 라인 VDATA에 접속된다. 스위치 트랜지스터(16)의 제2 단자는 구동 트랜지스터(14)의 게이트 단자에 접속된다.

[0024] 스위치 트랜지스터(18)의 게이트 단자는 제2 선택 라인 SEL2에 접속된다. 트랜지스터(18)의 제1 단자는 OLED(10)의 애노드 전극 및 스토리지 커패시터(12)에 접속된다. 스위치 트랜지스터(18)의 제2 단자는 바이어스 라인 IBIAS에 접속된다. OLED(10)의 캐소드 전극은 공통 접지에 접속된다.

[0025] 트랜지스터(14 및 16) 및 스토리지 커패시터(12)는 노드 A11에 접속된다. OLED(10), 스토리지 커패시터(12) 및 트랜지스터(14 및 18)는 B11에 접속된다.

[0026] 픽셀 회로(200)의 동작은 복수의 프로그래밍 사이클을 갖는 프로그래밍 단계 및 하나의 구동 사이클을 갖는 구동 단계를 포함한다. 프로그래밍 단계 동안, 노드 B11은 구동 트랜지스터(14)의 문턱 전압의 음(negative)으로 대전되고, 노드 A11은 프로그래밍 전압 VP로 대전된다.

[0027] 그 결과, 구동 트랜지스터(14)의 게이트-소스 전압은:

$$VGS = VP - (-VT) = VP + VT \quad (1)$$

[0029] 이며, 여기에서 VGS는 구동 트랜지스터(14)의 게이트-소스 전압을 나타내고, VT는 구동 트랜지스터(14)의 문턱 전압을 나타낸다. 이 전압은 구동 단계에서 커패시터(12)를 온(on) 상태로 유지시키며, 그 결과 구동 단계에서 OLED(10)를 통해 원하는 전류의 흐름을 일으킨다.

[0030] 픽셀 회로(200)의 프로그래밍 및 구동 단계에 대해 상세하게 기재된다. 도 2는 도 1의 픽셀 회로(200)에 적용되는 하나의 예시적인 동작 프로세스를 예시한다. 도 2에서, VnodeB는 노드 B11의 전압을 나타내고, VnodeA는 노드 A11의 전압을 나타낸다. 도 2에 도시된 바와 같이, 프로그래밍 단계는 2개의 동작 사이클 X11, X12를 가지며, 구동 단계는 하나의 동작 사이클 X13을 갖는다.

[0031] 제1 동작 사이클 X11: 선택 라인 SEL1과 SEL2 둘 다 하이(high)이다. 바이어스 전류 IB는 바이어스 라인 IBIAS를 통하여 흐르고, VDATA는 바이어스 전압 VB로 간다.

[0032] 그 결과, 노드 B11의 전압은:

$$VnodeB = VB - \sqrt{\frac{IB}{\beta}} - VT \quad (2)$$

[0034] 이며, 여기에서 VnodeB는 노드 B11의 전압을 나타내고, VT는 구동 트랜지스터(14)의 문턱 전압을 나타내고,  $\beta$ 는  $IDS = \beta (VGS - VT)^2$ 에 의해 주어진 TFT의 전류-전압 (I-V) 특성의 계수를 나타낸다. IDS는 구동 트랜지스터(14)의 드레인-소스 전류를 나타낸다.

[0035] 제2 동작 사이클 X12: SEL2가 로우(low)이고 SEL1이 하이인 동안, VDATA가 프로그래밍 전압 VP로 간다. OLED(20)의 커패시턴스(11)가 크기 때문에, 이전 사이클에서 발생된 노드 B11의 전압은 그대로 유지된다.

[0036] 따라서, 구동 트랜지스터(14)의 게이트-소스 전압을 다음과 같이 알 수 있다:

$$VGS = VP + \Delta VB + VT \quad (3)$$

$$\Delta VB = \sqrt{\frac{IB}{\beta}} - VB \quad (4)$$

[0039] (4)에 기초하여 VB가 적절하게 선택될 때  $\Delta VB$ 는 0이다. 구동 트랜지스터(14)의 게이트-소스 전압, 즉  $VP+VT$ 가 스토리지 커패시터(12)에 저장된다.

[0040] 제3 동작 사이클 X13: IBIAS가 로우로 간다. SEL1은 0으로 간다. 스토리지 커패시터(12)에 저장된 전압이 구동 트랜지스터(14)의 게이트 단자에 인가된다. 구동 트랜지스터(14)는 온이다. 구동 트랜지스터(14)의 게이트-소스 전압은 스토리지 커패시터(12)에 저장된 전압 이상을 낸다. 따라서, OLED(10)를 통한 전류는 구동 트랜지스터(14)의 문턱 전압의 시프트 및 OLED 특성에 관계없어진다.

[0041] 도 3은 도 1의 픽셀 회로(200)에 적용되는 부가의 예시적인 동작 프로세스를 예시한다. 도 3에서, VnodeB는 노드 B11의 전압을 나타내고, VnodeA는 노드 A11의 전압을 나타낸다.

[0042] 프로그래밍 단계는 2개의 동작 사이클 X21, X22를 갖고, 구동 단계는 하나의 동작 사이클 X23을 갖는다. 제1 동작 사이클 X21은 도 2의 제1 동작 사이클 X11과 동일하다. 제3 동작 사이클 X33은 도 2의 제3 동작 사이클 X13과 동일하다. 도 3에서, 선택 라인 SEL1 및 SEL2는 동일한 타이밍을 갖는다. 따라서, SEL1 및 SEL2는 공통 선택 라인에 접속될 수 있다.

[0043] 제2 동작 사이클 X22: SEL1 및 SEL2는 하이이다. 스위치 트랜지스터(18)는 온이다. IBIAS를 통해 흐르는 바이어스 전류 IB는 0이다.

[0044] 구동 트랜지스터(14)의 게이트-소스 전압은 상기 기재한 바와 같이  $VGS=VP+VT$ 일 수 있다. 구동 트랜지스터(14)의 게이트-소스 전압, 즉  $VP+VT$ 는 스토리지 커패시터(12)에 저장된다.

[0045] 도 4는 도 1의 픽셀 회로(200)에 대한 시뮬레이션 결과 및 도 2의 과정을 도시한다. 결과에는, 대부분의 프로그래밍 전압에 대하여, 구동 트랜지스터(예를 들어, 도 1의 14)의 2V VT-시프트로 인한 OLED 전류의 변화가 거의 0 퍼센트임을 보여준다. 문턱 전압과 같은 시뮬레이션 파라미터는, 낮은 프로그래밍 전압에서 시프트가 높은 비율을 가짐을 보여준다.

[0046] 도 5는 p형 트랜지스터를 갖는 픽셀 회로(202)를 도시한다. 픽셀 회로(202)는 도 1의 픽셀 회로(200)에 대응한다. 픽셀 회로(202)는 도 6 및 도 7에 도시된 바와 같은 CBVP 구동 방식을 채용한다. 픽셀 회로(202)는 OLED(20), 스토리지 커패시터(22), 구동 트랜지스터(24), 및 스위치 트랜지스터(26 및 28)를 포함한다. 트랜지스터(24, 26 및 28)는 p형 트랜지스터이다. 각각의 트랜지스터는 게이트 단자, 제1 단자 및 제2 단자를 갖는다.

[0047] 트랜지스터(24, 26 및 28)는 비정질 실리콘, 나노/마이크로 결정질 실리콘, 폴리 실리콘, 유기 반도체 기술(예를 들어, 유기 TFT), PMOS 기술, 또는 CMOS 기술(예를 들어, MOSFET)을 사용하여 제조될 수 있다. 복수의 픽셀 회로(202)가 AMOLED 디스플레이 어레이를 형성할 수 있다.

[0048] 2개의 선택 라인 SEL1 및 SEL2, 신호 라인 VDATA, 바이어스 라인 IBIAS, 전압 공급 라인 VDD, 및 공통 접지가 픽셀 회로(202)에 제공된다.

[0049] 트랜지스터(24 및 26) 및 스토리지 커패시터(22)는 노드 A12에 접속된다. OLED(20)의 캐소드 전극, 스토리지 커패시터(22) 및 트랜지스터(24 및 28)는 B12에 접속된다. OLED 캐소드가 픽셀 회로(202)의 다른 소자들에 접속되므로, 이는 임의의 OLED 제조와의 접점을 보장한다.

[0050] 도 6은 도 5의 픽셀 회로(202)에 적용되는 하나의 예시적인 동작 프로세스를 예시한다. 도 6은 도 2에 대응한다. 도 7은 도 5의 픽셀 회로(202)에 적용되는 부가의 예시적인 동작 프로세스를 예시한다. 도 7은 도 3에 대응한다. 도 6 및 도 7의 CBVP 구동 방식은 도 2 및 도 3의 IBIAS 및 VDATA와 유사한 IBIAS 및 VDATA를 사용한다.

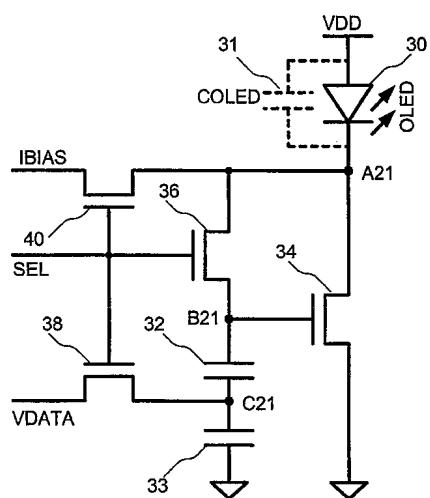

[0051] 도 8은 본 발명의 실시예에 따른 픽셀 회로(204)를 도시한다. 픽셀 회로(204)는 상기 기재한 바와 같은 CBVP 구동 방식을 채용한다. 도 8의 픽셀 회로(204)는 OLED(30), 스토리지 커패시터(32 및 33), 구동 트랜지스터

(34), 및 스위치 트랜지스터(36, 38 및 40)를 포함한다. 각각의 트랜지스터(34, 35 및 36)는 게이트 단자, 제1 단자 및 제2 단자를 포함한다. 이 픽셀 회로(204)는 픽셀 회로(200)의 방식과 동일한 방식으로 동작한다.

[0052] 트랜지스터(34, 36, 38 및 40)는 n형 TFT 트랜지스터이다. 픽셀 회로(204)에 적용되는 구동 기술은 도 10에 도시된 바와 같은 p형 트랜지스터를 갖는 상보형 픽셀 회로에도 적용 가능하다.

[0053] 트랜지스터(34, 36, 38 및 40)는 비정질 실리콘, 나노/마이크로 결정질 실리콘, 폴리 실리콘, 유기 반도체 기술(예를 들어, 유기 TFT), NMOS 기술, 또는 CMOS 기술(예를 들어, MOSFET)을 사용하여 제조될 수 있다. 복수의 픽셀 회로(204)가 AMOLED 디스플레이 어레이를 형성할 수 있다.

[0054] 선택 라인 SEL, 신호 라인 VDATA, 바이어스 라인 IBIAS, 전압 라인 VDD, 및 공통 접지가 픽셀 회로(204)에 제공된다.

[0055] 구동 트랜지스터(34)의 제1 단자는 OLED(30)의 캐소드 전극에 접속된다. 구동 트랜지스터(34)의 제2 단자는 접지에 접속된다. 구동 트랜지스터(34)의 게이트 단자는 스위치 트랜지스터(36)를 통하여 그의 제1 단자에 접속된다. 스토리지 커패시터(32 및 33)는 직렬로 이루어지며, 구동 트랜지스터(34)의 게이트와 접지 사이에 접속된다.

[0056] 스위치 트랜지스터(36)의 게이트 단자는 선택 라인 SEL에 접속된다. 스위치 트랜지스터(36)의 제1 단자는 구동 트랜지스터(34)의 제1 단자에 접속된다. 스위치 트랜지스터(36)의 제2 단자는 구동 트랜지스터(34)의 게이트 단자에 접속된다.

[0057] 스위치 트랜지스터(38)의 게이트 단자는 선택 라인 SEL에 접속된다. 스위치 트랜지스터(38)의 제1 단자는 신호 라인 VDATA에 접속된다. 스위치 트랜지스터(38)의 제2 단자는 스토리지 커패시터(32 및 33)의 접속 단자(즉, 노드 C21)에 접속된다.

[0058] 스위치 트랜지스터(40)의 게이트 단자는 선택 라인 SEL에 접속된다. 스위치 트랜지스터(40)의 제1 단자는 바이어스 라인 IBIAS에 접속된다. 스위치 트랜지스터(40)의 제2 단자는 OLED(30)의 캐소드 단자에 접속된다. OLED(30)의 애노드 전극은 VDD에 접속된다.

[0059] OLED(30), 트랜지스터(34, 36, 및 40)는 노드 A21에서 접속된다. 스토리지 커패시터(32) 및 트랜지스터(34 및 36)는 노드 B21에서 접속된다.

[0060] 픽셀 회로(204)의 동작은 복수의 프로그래밍 사이클을 갖는 프로그래밍 단계, 및 하나의 구동 사이클을 갖는 구동 단계를 포함한다. 프로그래밍 단계 동안, 제1 스토리지 커패시터(32)는 구동 트랜지스터(34)의 문턱 전압에 프로그래밍 전압 VP를 더한 값으로 대전되며, 제2 스토리지 커패시터(33)는 0으로 대전된다.

[0061] 그 결과, 구동 트랜지스터(34)의 게이트-소스 전압은:

$$VGS = VP + VT \quad (5)$$

[0063] 이며, 여기에서 VGS는 구동 트랜지스터(34)의 게이트-소스 전압을 나타내고, VT는 구동 트랜지스터(34)의 문턱 전압을 나타낸다.

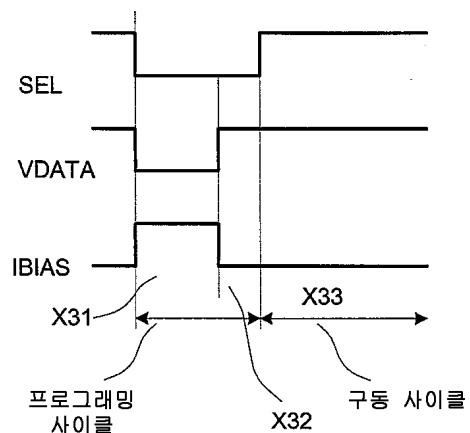

[0064] 픽셀 회로(204)의 프로그래밍 및 구동 단계에 대해 상세하게 기재된다. 도 9는 도 8의 픽셀 회로(204)에 적용되는 하나의 예시적인 동작 프로세스를 예시한다. 도 9에 도시된 바와 같이, 프로그래밍 단계는 2개의 동작 사이클 X31, X32를 가지며, 구동 단계는 하나의 동작 사이클 X33을 갖는다.

[0065] 제1 동작 사이클 X31: 선택 라인 SEL은 하이이다. 바이어스 전류 IB는 바이어스 라인 IBIAS를 통해 흐르고, VDATA는 VB-VP로 가며, 여기에서 VP는 프로그래밍 전압이고 VB는 다음에 의해 주어진다:

$$VB = \sqrt{\frac{IB}{\beta}} \quad (6)$$

[0067] 그 결과, 제1 커패시터(32)에 저장된 전압은:

$$VC1 = VP + VT \quad (7)$$

[0069] 이며, 여기에서 VC1은 제1 스토리지 커패시터(32)에 저장된 전압을 나타내고, VT는 구동 트랜지스터(34)의 문턱

전압을 나타내며,  $\beta$ 는  $IDS = \beta(VGS - VT)^2$ 에 의해 주어진 TFT의 전류-전압(I-V) 특성의 계수를 나타낸다.  $IDS$ 는 구동 트랜지스터(34)의 드레인-소스 전류를 나타낸다.

[0070] 제2 동작 사이클: SEL이 하이인 동안, VDATA는 0이고, IBIAS는 0으로 간다. OLED(30)의 커패시턴스(31)와 바이어스 라인 IBIAS의 기생 커패시턴스가 크기 때문에, 이전 사이클에서 발생된 노드 B21의 전압 및 노드 A21의 전압은 변하지 않은 채 유지된다.

[0071] 따라서, 구동 트랜지스터(34)의 게이트-소스 전압을 다음과 같이 알 수 있다:

$$VGS = VP + VT \quad (8)$$

[0073] 여기에서,  $VGS$ 는 구동 트랜지스터(34)의 게이트-소스 전압을 나타낸다.

[0074] 구동 트랜지스터(34)의 게이트-소스 전압은 스토리지 커패시터(32)에 저장된다.

[0075] 제3 동작 사이클 X33: IBIAS는 0으로 간다. SEL은 0으로 간다. 노드 C21의 전압은 0으로 간다. 스토리지 커패시터(32)에 저장된 전압은 구동 트랜지스터(34)의 게이트 단자에 인가된다. 구동 트랜지스터(34)의 게이트-소스 전압은 스토리지 커패시터(32)에 저장된 전압 이상을 낸다. 구동 트랜지스터(34)의 전류가 주로 그의 게이트-소스 전압에 의해 정의된다는 것을 고려하면, OLED(30)를 통한 전류는 구동 트랜지스터(34)의 문턱 전압의 시프트 및 OLED 특성에 관계없어진다.

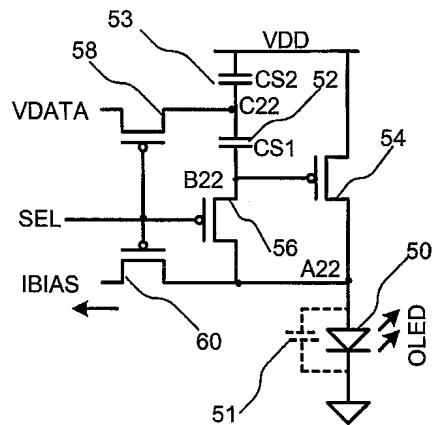

[0076] 도 10은 p형 트랜지스터를 갖는 픽셀 회로(206)를 도시한다. 픽셀 회로(206)는 도 8의 픽셀 회로(204)에 대응한다. 픽셀 회로(206)는 도 11에 도시된 바와 같은 CBVP 구동 방식을 채용한다. 도 10의 픽셀 회로(206)는 OLED(50), 스토리지 커패시터(52 및 53), 구동 트랜지스터(54), 및 스위치 트랜지스터(56, 58, 및 60)를 포함한다. 트랜지스터(54, 56, 58 및 60)는 p형 트랜지스터이다. 각각의 트랜지스터는 게이트 단자, 제1 단자 및 제2 단자를 갖는다.

[0077] 트랜지스터(54, 56, 58 및 60)는 비정질 실리콘, 나노/마이크로 결정질 실리콘, 폴리 실리콘, 유기 반도체 기술(예를 들어, 유기 TFT), PMOS 기술, 또는 CMOS 기술(예를 들어, MOSFET)을 사용하여 제조될 수 있다. 복수의 픽셀 회로(206)가 AMOLED 디스플레이 어레이를 형성할 수 있다.

[0078] 2개의 선택 라인 SEL1 및 SEL2, 단일 라인 VDATA, 바이어스 라인 IBIAS, 전압 공급 라인 VDD, 및 공통 접지가 픽셀 회로(206)에 제공된다. 공통 접지는 도 1의 공통 접지와 동일한 것일 수 있다.

[0079] OLED(50)의 애노드 전극, 트랜지스터(54, 56, 및 60)는 노드 A22에서 접속된다. 스토리지 커패시터(52) 및 트랜지스터(54 및 56)는 노드 B22에서 접속된다. 스위치 트랜지스터(58), 및 스토리지 커패시터(52 및 53)는 노드 C22에서 접속된다.

[0080] 도 11은 도 10의 픽셀 회로(206)에 적용되는 하나의 예시적인 동작 프로세스를 예시한다. 도 11은 도 9에 대응한다. 도 11에 도시된 바와 같이, 도 11의 CBVP 구동 방식은 도 9의 IBIAS 및 VDATA와 유사한 IBIAS 및 VDATA를 사용한다.

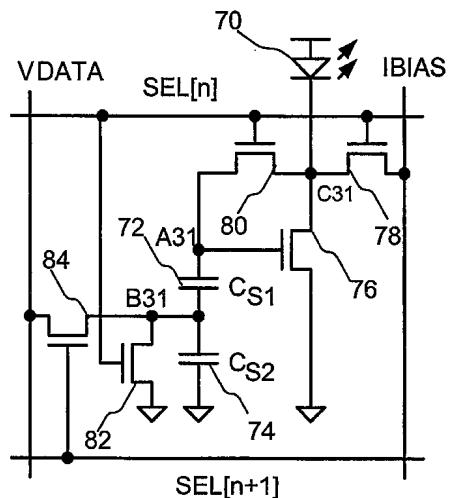

[0081] 도 12는 본 발명의 실시예에 따른 디스플레이(208)를 도시한다. 디스플레이(208)는 아래에 기재된 바와 같은 CBVP 구동 방식을 채용한다. 도 12에서, 2개의 행 및 1개의 열과 연관된 소자가 예로서 도시되어 있다. 디스플레이(208)는 2개보다 많은 수의 행 및 1개보다 많은 수의 열을 포함할 수 있다.

[0082] 디스플레이(208)는 OLED(70), 스토리지 커패시터(72 및 73), 트랜지스터(76, 78, 80, 82, 및 84)를 포함한다. 트랜지스터(76)는 구동 트랜지스터이다. 트랜지스터(78, 80, 및 84)는 스위치 트랜지스터이다. 각각의 트랜지스터(76, 78, 80, 82 및 84)는 게이트 단자, 제1 단자 및 제2 단자를 포함한다.

[0083] 트랜지스터(76, 78, 80, 82 및 84)는 n형 TFT 트랜지스터이다. 픽셀 회로(208)에 적용되는 구동 기술은 도 16에 도시된 바와 같은 p형 트랜지스터를 갖는 상보형 픽셀 회로에도 적용 가능하다.

[0084] 트랜지스터(76, 78, 80, 82 및 84)는 비정질 실리콘, 나노/마이크로 결정질 실리콘, 폴리 실리콘, 유기 반도체 기술(예를 들어, 유기 TFT), NMOS 기술, 또는 CMOS 기술(예를 들어, MOSFET)을 사용하여 제조될 수 있다. 디스플레이(208)는 AMOLED 디스플레이 어레이를 형성할 수 있다. CBVP 구동 방식과 디스플레이(208)의 조합은 대면적 고해상도 AMOLED 디스플레이를 제공한다.

[0085] 트랜지스터(76 및 80)와 스토리지 커패시터(72)는 노드 A31에서 접속된다. 트랜지스터(82 및 84)와 스토리지

커패시터(72 및 74)는 B31에서 접속된다.

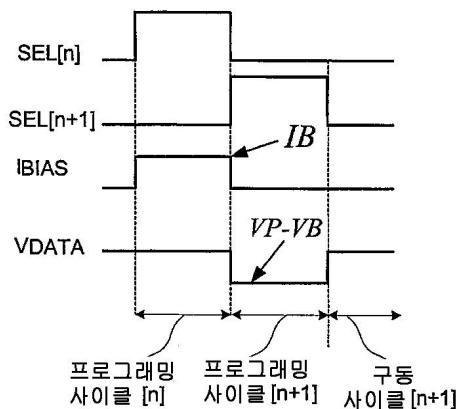

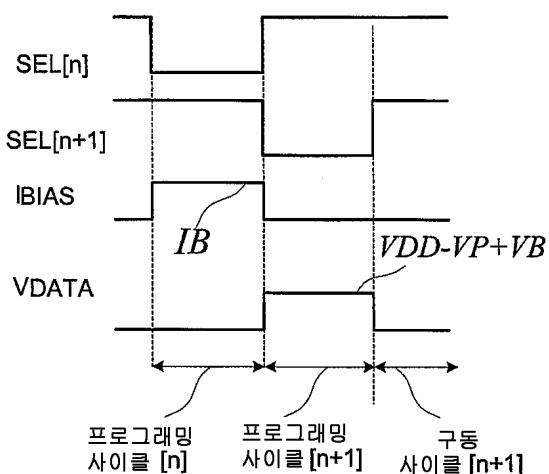

[0086] 도 13은 도 12의 디스플레이(208)에 적용되는 하나의 예시적인 동작 프로세스를 예시한다. 도 13에서, "프로그래밍 사이클[n]"은 디스플레이(208)의 행 [n]에 대한 프로그래밍 사이클을 나타낸다.

[0087] 2개의 연속하는 행들(n과 n+1) 사이에 프로그래밍 시간이 공유된다. n번째 행의 프로그래밍 사이클 동안, SEL[n]은 하이이고, 바이어스 전류 IB는 트랜지스터(78 및 80)를 통하여 흐르고 있다. 노드 A31에서의 전압은, 노드 B31에서의 전압이 0인 동안,  $(IB/\beta)1/2+VT$ 로 자가 조정되며(self-adjusted), 여기에서 VT는 구동 트랜지스터(76)의 문턱 전압을 나타내고,  $\beta$ 는  $IDS = \beta(VGS - VT)^2$ 에 의해 주어진 TFT의 전류-전압(I-V) 특성의 계수를 나타내며, IDS는 구동 트랜지스터(76)의 드레인-소스 전류를 나타낸다.

[0088] (n+1)번째 행의 프로그래밍 사이클 동안, VDATA는 VP-VB로 변한다. 그 결과, 노드 A31에서의 전압은  $VB = (IB/\beta)1/2$ 인 경우 VP+VT로 변한다. 모든 픽셀에 대하여 일정한 전류가 쓰이므로, IBIAS 라인은 변함없이 적절한 전압을 가지며, 그리하여 라인을 미리 대전시킬(pre-charge) 필요가 없어짐에 따라, 프로그래밍 시간이 더 짧아지고 전력 소모가 더 적어진다. 더 중요하게는, 노드 B31의 전압은 n 번째 행의 프로그래밍 사이클의 시작에서 VP-VB로부터 0으로 변한다. 따라서, 노드 A31에서의 전압은  $(IB/\beta)1/2+VT$ 로 변하고, 이미 그의 최종 값으로 조정되며, 빠른 정착 시간을 유도한다.

[0089] 다양한 바이어스 전류에 대하여 CBVP 픽셀 회로의 정착 시간이 도 14에 나타나 있다. 여기에서는 작은 전류가 IB로서 사용될 수 있으며, 그 결과 전력 소모가 적어진다.

[0090] 도 15는 CBVP 픽셀 회로의 I-V 특성 뿐만 아니라, 구동 트랜지스터(예를 들어, 도 12의 76)의 문턱 전압의 2-V 시프트로 인해 픽셀 전류에 유도된 총 오류를 도시한다. 결과는 픽셀 전류에 있어서 2% 미만의 총 오류를 나타낸다.  $IB=4.5\ \mu A$  임을 유의한다.

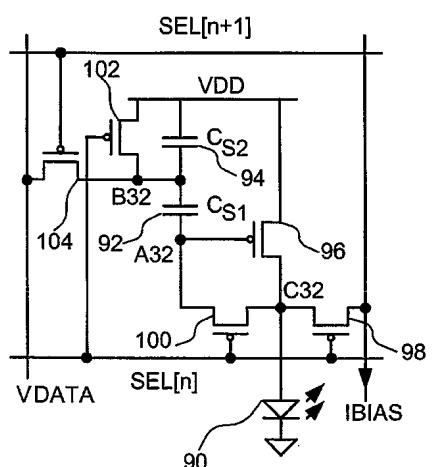

[0091] 도 16은 p형 트랜지스터를 갖는 디스플레이(210)를 도시한다. 디스플레이(210)는 도 12의 디스플레이(208)에 대응한다. 디스플레이(210)는 도 17에 도시된 바와 같은 CBVP 구동 방식을 채용한다. 도 12에서, 2개의 행 및 1개의 열과 연관된 소자가 예로서 도시되어 있다. 디스플레이(210)는 2개보다 많은 수의 행 및 1개보다 많은 수의 열을 포함할 수 있다.

[0092] 디스플레이(210)는 OLED(90), 스토리지 커패시터(92, 및 94), 및 트랜지스터(96, 98, 100, 102 및 104)를 포함한다. 트랜지스터(96)는 구동 트랜지스터이다. 트랜지스터(100 및 104)는 스위치 트랜지스터이다. 트랜지스터(24, 26 및 28)는 p형 트랜지스터이다. 각각의 트랜지스터는 게이트 단자, 제1 단자 및 제2 단자를 갖는다.

[0093] 트랜지스터(96, 98, 100, 102, 및 104)는 비정질 실리콘, 나노/마이크로 결정질 실리콘, 폴리 실리콘, 유기 반도체 기술(예를 들어, 유기 TFT), PMOS 기술, 또는 CMOS 기술(예를 들어, MOSFET)을 사용하여 제조될 수 있다. 디스플레이(210)는 AMOLED 디스플레이 어레이를 형성할 수 있다.

[0094] 도 16에서, 구동 트랜지스터(96)는 OLED(90)의 애노드 전극과 전압 공급 라인 VDD 사이에 접속된다.

[0095] 도 17은 도 16의 디스플레이(210)에 적용되는 하나의 예시적인 동작 프로세스를 예시한다. 도 17은 도 13에 대응한다. 도 17의 CBVP 구동 방식은 도 13의 IBIAS 및 VDATA와 유사한 IBIAS 및 VDATA를 사용한다.

[0096] CBVP 구동 방식에 따라, 그의 문턱 전압 및 OLED 전압과 무관하도록 구동 트랜지스터에 제공된 오버드라이브(overdrive) 전압이 발생된다.

[0097] 픽셀 소자(들)의 특성(들)의 시프트(들)(예를 들어, 연장된 디스플레이 동작 하의 발광 소자의 열화 및 구동 트랜지스터의 문턱 전압 시프트)는, 스토리지 커패시터에 저장된 전압에 의해 그리고 그것을 구동 트랜지스터의 게이트에 인가함으로써, 보상된다. 따라서, 픽셀 회로는 시프트의 어떠한 영향 없이 발광 소자를 통하여 안정적인 전류를 제공할 수 있으며, 이는 디스플레이 동작 수명을 향상시킨다. 또한, 회로 단순성으로 인해, 종래의 픽셀 회로보다 더 높은 생산 수율, 더 적은 제조 비용 및 더 높은 해상도를 보장한다.

[0098] 상기 기재된 픽셀 회로의 정착 시간은 종래의 픽셀 회로보다 훨씬 더 작으므로, 고해상도 TV와 같은 대면적 디스플레이에 적합하지만, 이는 또한 소형 디스플레이 면적을 배제하는 것은 아니다.

[0099] CBVP 픽셀 회로(예를 들어, 200, 202 또는 204)를 갖는 디스플레이 어레이를 구동하기 위한 구동기는 픽셀 회로

데이터를 전압으로 변환한다는 것을 유의한다.

[0100] 이제 전압 바이어싱된 전류 프로그래밍된(VBCP; voltage-biased current-programmed) 구동 방식을 포함하는 픽셀에 대한 구동 기술이 상세하게 기재된다. VBCP 구동 방식에서, 미러 트랜지스터를 리사이징하지 않고 픽셀 전류가 스케일링 다운된다. VBCP 구동 방식은 전류를 사용하여 다양한 그레이 스케일을 제공하고(전류 프로그래밍), 바이어스를 사용하여 프로그래밍을 가속화하고 문턱 전압 시프트와 같은 픽셀의 시간 의존적 파라미터를 보상한다. 구동 트랜지스터의 단자들 중 하나는 가상 접지(virtual ground) VGND에 접속된다. 가상 접지의 전압을 변경함으로써, 픽셀 전류 IB는 구동기록에서 프로그래밍 전류 IP에 더해지고, 그 다음 가상 접지의 전압을 변경함으로써 픽셀 회로로의 프로그래밍 전류로부터 바이어스 전류가 제거된다.

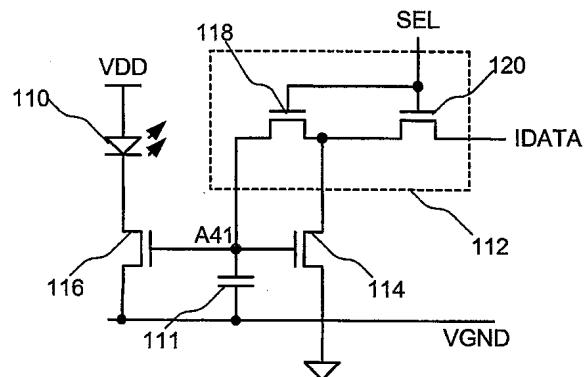

[0101] 도 18은 본 발명의 부가적인 실시예에 따른 픽셀 회로(212)를 도시한다. 픽셀 회로(212)는 상기 기재한 바와 같은 VBCP 구동 방식을 채용한다. 도 18의 픽셀 회로(212)는 OLED(110), 스토리지 커패시터(111), 스위치 네트워크(112) 및 미러 트랜지스터(114 및 116)를 포함한다. 미러 트랜지스터(114 및 116)는 전류 미러를 형성한다. 트랜지스터(114)는 프로그래밍 트랜지스터이다. 트랜지스터(116)는 구동 트랜지스터이다. 스위치 네트워크(112)는 스위치 트랜지스터(118 및 120)를 포함한다. 각각의 트랜지스터(114, 116, 118 및 120)는 게이트 단자, 제1 단자 및 제2 단자를 갖는다.

[0102] 트랜지스터(114, 116, 118 및 120)는 n형 TFT 트랜지스터이다. 픽셀 회로(212)에 적용된 구동 기술은 또한 도 20에 도시된 바와 같은 p형 트랜지스터를 갖는 상보형 픽셀 회로에도 적용 가능하다.

[0103] 트랜지스터(114, 116, 118 및 120)는 비정질 실리콘, 나노/마이크로 결정질 실리콘, 폴리 실리콘, 유기 반도체 기술(예를 들어, 유기 TFT), NMOS 기술, 또는 CMOS 기술(예를 들어, MOSFET)을 사용하여 제조될 수 있다. 복수의 픽셀 회로(212)가 AMOLED 디스플레이 어레이를 형성할 수 있다.

[0104] 선택 라인 SEL, 신호 라인 IDATA, 가상 접지 라인 VGND, 전압 공급 라인 VDD, 및 공통 접지가 픽셀 회로(150)에 제공된다.

[0105] 트랜지스터(116)의 제1 단자는 OLED(110)의 캐소드 전극에 접속된다. 트랜지스터(116)의 제2 단자는 VGND에 접속된다. 트랜지스터(114)의 게이트 단자, 트랜지스터(116)의 게이트 단자, 및 스토리지 커패시터(111)는 접속 노드 A41에 접속된다.

[0106] 스위치 트랜지스터(118 및 120)의 게이트 단자는 SEL에 접속된다. 스위치 트랜지스터(120)의 제1 단자는 IDATA에 접속된다. 스위치 트랜지스터(118 및 120)는 트랜지스터(114)의 제1 단자에 접속된다. 스위치 트랜지스터(118)는 노드 A41에 접속된다.

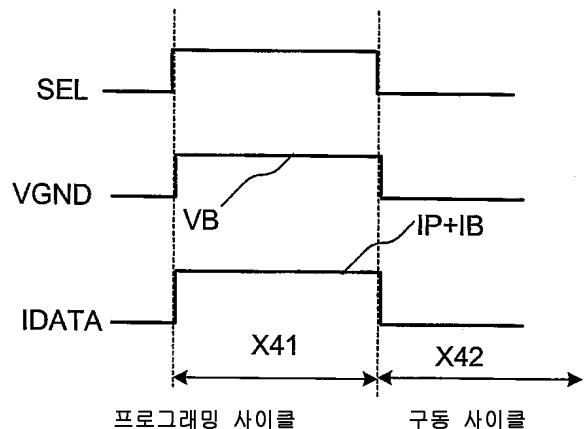

[0107] 도 19는 도 18의 픽셀 회로(212)에 대한 예시적인 동작을 예시한다. 도 18 및 도 19를 참조하여, 픽셀 회로(212)에 적용되는 전류 스케일링 기술에 대해 상세하게 기재된다. 픽셀 회로(212)의 동작은 프로그래밍 사이클 X41, 및 구동 사이클 X42를 갖는다.

[0108] 프로그래밍 사이클 X41: SEL은 하이이다. 따라서, 스위치 트랜지스터(118 및 120)는 온이다. VGND는 바이어스 전압 VB로 간다. 전류 (IB+IP)가 IDATA를 통하여 제공되며, 여기에서 IP는 프로그래밍 전류를 나타내고, IB는 바이어스 전류를 나타낸다. (IB+IP)와 동일한 전류가 스위치 트랜지스터(118 및 120)를 통과한다.

[0109] 구동 트랜지스터(116)의 게이트-소스 전압은 다음으로 자가 조정된다:

$$VGS = \sqrt{\frac{IP + IB}{\beta}} + VT \quad (9)$$

[0110] 여기에서, VT는 구동 트랜지스터(116)의 문턱 전압을 나타내고,  $\beta$ 는  $IDS = \beta(VGS - VT)^2$ 에 의해 주어진 TFT의 전류-전압(I-V) 특성의 계수를 나타낸다. IDS는 구동 트랜지스터(116)의 드레인-소스 전류를 나타낸다.

[0111] 스토리지 커패시터(111)에 저장된 전압은:

$$VCS = \sqrt{\frac{IP + IB}{\beta}} - VB + VT \quad (10)$$

[0112]이며, 여기에서 VCS는 스토리지 커패시터(111)에 저장된 전압을 나타낸다.

[0115] 구동 트랜지스터(116)의 하나의 단자가 VGND에 접속되므로, 프로그래밍 시간 동안 OLED(110)를 통하여 흐르는 전류는:

$$I_{pixel} = IP + IB + \beta \cdot (VB)^2 - 2\sqrt{\beta} \cdot VB \cdot \sqrt{(IP + IB)} \quad (11)$$

[0117]이고,  $I_{pixel}$ 은 OLED(110)를 통하여 흐르는 픽셀 전류를 나타낸다.

[0118]  $IB \gg IP$ 인 경우, 픽셀 전류  $I_{pixel}$ 은 다음과 같이 쓸 수 있다:

$$I_{pixel} = IP + (IB + \beta \cdot (VB)^2 - 2\sqrt{\beta} \cdot VB \cdot \sqrt{IB}) \quad (12)$$

[0120]  $VB$ 는 다음과 같이 적절하게 선택된다:

$$VB = \sqrt{\frac{IB}{\beta}} \quad (13)$$

[0122] 픽셀 전류  $I_{pixel}$ 은 프로그래밍 전류  $IP$ 와 동일하게 된다. 따라서, 이는 프로그래밍 사이클 동안의 원치 않는 방출을 피한다.

[0123] 리사이징이 요구되지 않으므로, 전류-미리 픽셀 회로에서 2개의 미리 트랜지스터 사이의 보다 나은 정합을 얻을 수 있다.

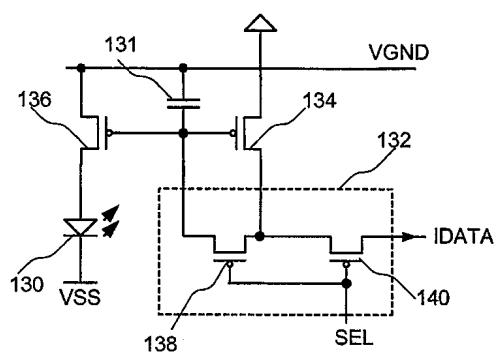

[0124] 도 20은 p형 트랜지스터를 갖는 픽셀 회로(214)를 도시한다. 픽셀 회로(214)는 도 18의 픽셀 회로(212)에 대응 한다. 픽셀 회로(214)는 도 21에 도시된 바와 같이 VBCP 구동 방식을 채용한다. 픽셀 회로(214)는 OLED(130), 스토리지 커패시터(131), 스위치 네트워크(132), 및 미리 트랜지스터(134 및 136)를 포함한다. 미리 트랜지스터(134 및 136)는 전류 미러를 형성한다. 트랜지스터(134)는 프로그래밍 트랜지스터이다. 트랜지스터(136)는 구동 트랜지스터이다. 스위치 네트워크(132)는 스위치 트랜지스터(138 및 140)를 포함한다. 트랜지스터(134, 136, 138 및 140)는 p형 TFT 트랜지스터이다. 각각의 트랜지스터(134, 136, 138 및 140)는 게이트 단자, 제1 단자, 및 제2 단자를 갖는다.

[0125] 트랜지스터(134, 136, 138 및 140)는 비정질 실리콘, 나노/마이크로 결정질 실리콘, 폴리 실리콘, 유기 반도체 기술(예를 들어, 유기 TFT), PMOS 기술, 또는 CMOS 기술(예를 들어, MOSFET)을 사용하여 제조될 수 있다. 복수의 픽셀 회로(214)가 AMOLED 디스플레이 어레이를 형성할 수 있다.

[0126] 선택 라인 SEL, 신호 라인 IDATA, 가상 접지 라인 VGND, 및 전압 공급 라인 VSS가 픽셀 회로(214)에 제공된다.

[0127] 트랜지스터(136)는 OLED(130)의 캐소드 전극과 VGND 사이에 접속된다. 트랜지스터(134)의 게이트 단자, 트랜지스터(136)의 게이트 단자, 스토리지 커패시터(131) 및 스위치 네트워크(132)는 노드 A42에서 접속된다.

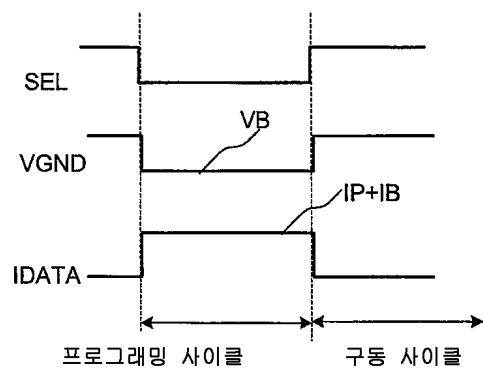

[0128] 도 21은 도 20의 픽셀 회로(214)에 대한 예시적인 동작을 예시한다. 도 21은 도 19에 대응한다. 도 21의 VBCP 구동 방식은 도 19의 IDATA 및 VGND와 유사한 IDATA 및 VGND를 사용한다.

[0129] 픽셀 회로(212 및 214)에 적용된 VBCP 기술은 전류 미러 유형 픽셀 회로가 아닌 다른 다른 전류 프로그래밍 픽셀 회로에 적용 가능하다.

[0130] 예를 들어, VBCP 기술은 AMOLED 디스플레이에 사용하기에 적합하다. VBCP 기술은 전류 프로그래밍된 픽셀 회로 디스플레이, 예를 들어 AMOLED 디스플레이의 정착 시간을 향상시킨다.

[0131] VBCP 픽셀 회로(예를 들어, 212, 214)를 갖는 디스플레이 어레이를 구동하기 위한 구동기는 픽셀 휘도 데이터를 전류로 변환한다는 것을 유의한다.

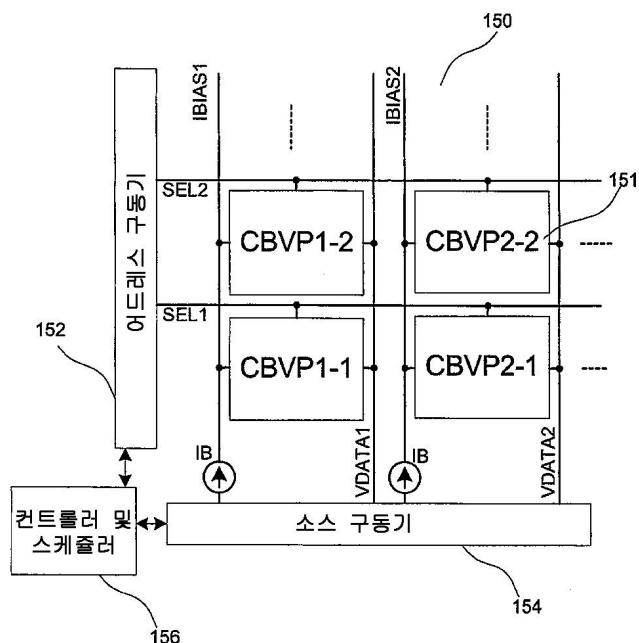

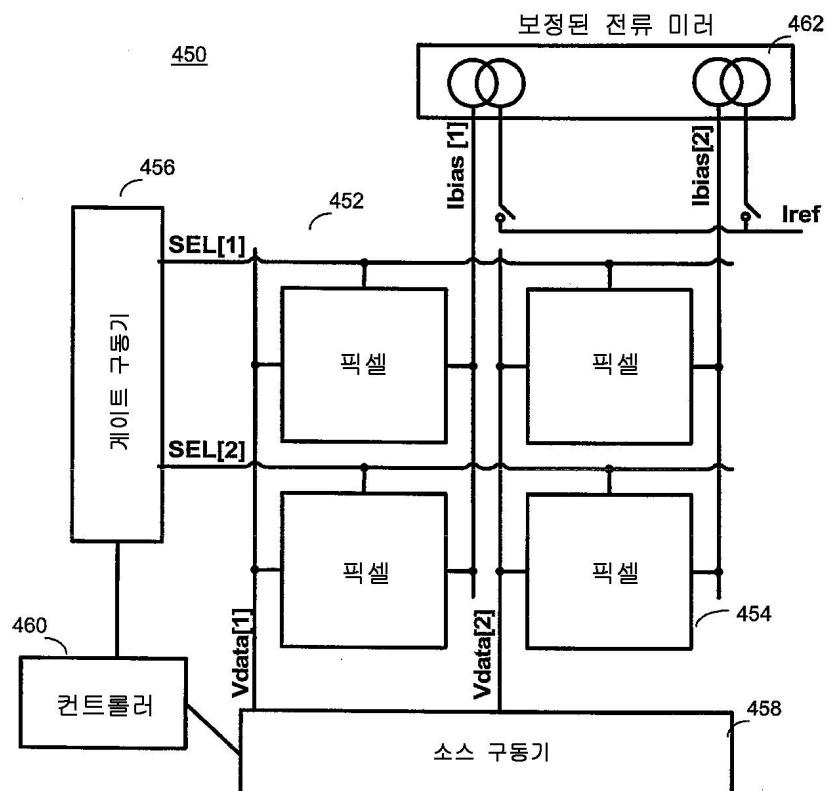

[0132] 도 22는 복수의 CBVP 픽셀 회로(151)(CBVP1-1, CBVP1-2, CBVP2-1, CBVP2-2)를 갖는 디스플레이 어레이(150)에 대한 구동 메커니즘을 도시한다. CBVP 픽셀 회로(151)는 CBVP 구동 방식이 적용 가능한 픽셀 회로이다. 예를 들어, CBVP 픽셀 회로(151)는 도 1, 도 5, 도 8, 도 10, 도 12, 또는 도 16에 도시된 픽셀 회로일 수 있다. 도 22에서, 4개의 CBVP 픽셀 회로(151)가 예로서 도시되어 있다. 디스플레이 어레이(150)는 4개보다 더 많거나 4개보다 더 적은 수의 CBVP 픽셀 회로(151)를 가질 수 있다.

[0133] 디스플레이 어레이(150)는 복수의 CBVP 픽셀 회로(151)가 행 및 열로 정렬되어 있는 AMOLED 디스플레이이다. 어레이 구조에서 공통 열 픽셀들 사이에 VDATA1(또는 VDATA2) 및 IBIAS1(또는 IBIAS2)가 공유되며, 공통 행 픽

셀들 사이에 SEL1(또는 SEL2)이 공유된다.

- [0134] SEL1 및 SEL2는 어드레스 구동기(address driver)(152)를 통하여 구동된다. VDATA1 및 VDATA2는 소스 구동기(154)를 통하여 구동된다. IBIAS1 및 IBIAS2도 또한 소스 구동기(154)를 통하여 구동된다. 컨트롤러 및 스케줄러(156)는 프로그래밍, 보정(calibration) 및 디스플레이 어레이를 동작시키기 위한 기타 동작의 제어 및 스케줄링을 위해 제공되며, 이는 상기 기재한 바와 같은 CBVP 구동 방식에 대한 제어 및 스케줄을 포함한다.

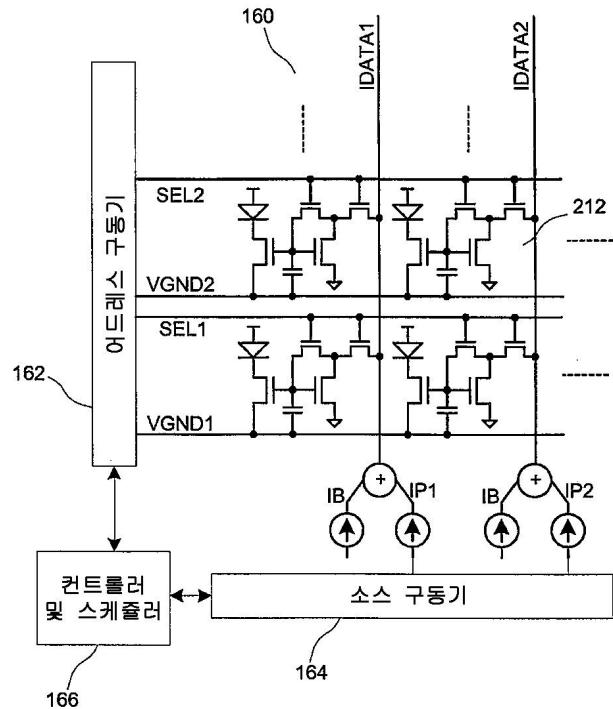

- [0135] 도 23은 복수의 VBCP 픽셀 회로를 갖는 디스플레이 어레이(160)에 대한 구동 메커니즘을 도시한다. 도 23에서, 도 18의 픽셀 회로(212)가 VBCP 픽셀 회로의 예로서 도시되어 있다. 그러나, 디스플레이 어레이(160)는 기재된 VBCP 구동 방식이 적용 가능한 임의의 기타 픽셀 회로를 포함할 수 있다.

- [0136] 도 23의 SEL1 및 SEL2는 도 18의 SEL에 대응한다. 도 23의 VGND1 및 VGND2는 도 18의 VDATA에 대응한다. 도 23의 IDATA1 및 IDATA2는 도 18의 IDATA에 대응한다. 도 23에서, 4개의 VBCP 픽셀 회로가 예로서 도시되어 있다. 디스플레이 어레이(160)는 4개보다 더 많거나 4개보다 더 적은 수의 VBCP 픽셀 회로를 가질 수 있다.

- [0137] 디스플레이 어레이(160)는 복수의 VBCP 픽셀 회로가 행 및 열로 정렬되어 있는 AMOLED 디스플레이이다. 어레이 구조에서 공통 열 픽셀들 사이에 IDATA1(또는 IDATA2)가 공유되며, 공통 행 픽셀들 사이에 SEL1(또는 SEL2) 또는 VGND1(또는 VGND2)이 공유된다.

- [0138] SEL1, SEL2, VGND1 및 VGND2는 어드레스 구동기(162)를 통하여 구동된다. IDATA1 및 IDATA는 소스 구동기(164)를 통하여 구동된다. 컨트롤러 및 스케줄러(166)는 프로그래밍, 보정 및 디스플레이 어레이를 동작시키기 위한 기타 동작의 제어 및 스케줄링을 위해 제공되며, 이는 상기 기재한 바와 같은 VBCP 구동 방식에 대한 제어 및 스케줄을 포함한다.

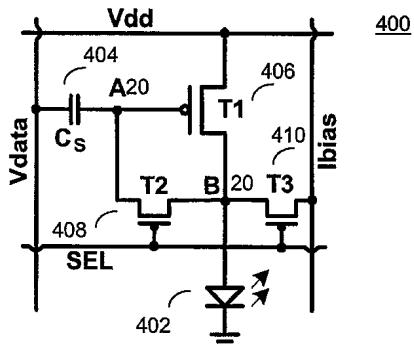

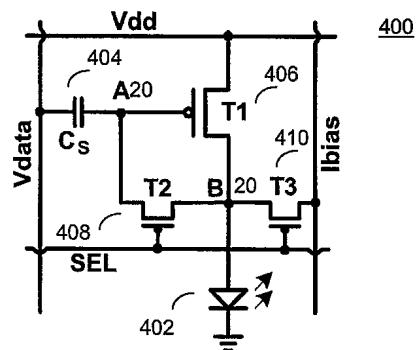

- [0139] 도 24는 본 발명의 부가적인 실시예에 따른 픽셀 회로(400)를 도시한다. 도 24의 픽셀 회로(400)는 3-TFT 전류 바이어싱된 전압 프로그래밍된 픽셀 회로이며, CBVP 구동 방식을 채용한다. 구동 방식은 부정합을 보상함으로써 디스플레이 수명 및 수율을 개선한다.

- [0140] 픽셀 회로(400)는 OLED(402), 스토리지 커패시터(404), 구동 트랜지스터(406), 및 스위치 트랜지스터(408 및 410)를 포함한다. 각각의 트랜지스터는 게이트 단자, 제1 단자 및 제2 단자를 갖는다. 트랜지스터(406, 408, 및 410)는 p형 TFT 트랜지스터이다. 픽셀 회로(400)에 적용된 구동 기술은 또한, n형 트랜지스터를 가지며 당해 기술 분야에서의 통상의 지식을 가진 자가 이해할 상보형 픽셀 회로에 적용 가능하다.

- [0141] 트랜지스터(406, 408 및 410)는 폴리 실리콘, 나노/마이크로(결정질) 실리콘, 비정질 실리콘, CMOS, 유기 반도체, 금속 유기 기술, 또는 이들의 조합을 사용하여 구현될 수 있다. 복수의 픽셀 회로(400)가 능동 매트릭스 어레이를 형성할 수 있다. 픽셀 회로(400)에 적용된 구동 방식은 능동 매트릭스 디스플레이에서의 시간 및 공간적 비균일성을 보상한다.

- [0142] 선택 라인 SEL, 신호 라인 Vdata, 바이어스 라인 Ibias, 및 전압 공급 라인 Vdd가 픽셀 회로(400)에 접속된다. 바이어스 라인 Ibias는 수명, 전력, 및 디바이스 성능과 균일성과 같은 디스플레이 사양에 기초하여 정의되는 바이어스 전류(Ibias)를 제공한다.

- [0143] 구동 트랜지스터(406)의 제1 단자는 전압 공급 라인 Vdd에 접속된다. 구동 트랜지스터(406)의 제2 단자는 노드 B20에서 OLED(402)에 접속된다. 커패시터(404)의 하나의 단자는 신호 라인 Vdata에 접속되고, 커패시터(404)의 다른 단자는 노드 A20에서 구동 트랜지스터(406)의 게이트 단자에 접속된다.

- [0144] 스위치 트랜지스터(408 및 410)의 게이트 단자는 선택 라인 SEL에 접속된다. 스위치 트랜지스터(408)는 노드 A20와 노드 B20 사이에 접속된다. 스위치 트랜지스터(410)는 노드 B20와 바이어스 라인 Ibias 사이에 접속된다.

- [0145] 픽셀 회로(400)에 대하여, 미리 결정된 고정된 전류(Ibias)가 트랜지스터(410)를 통해 제공되어 모든 공간 및 시간적 비균일성을 보상하고, 다양한 그레이 스케일에 요구되는 다양한 전류 레벨의 전류를 분배하는데 전압 프로그래밍이 사용된다.

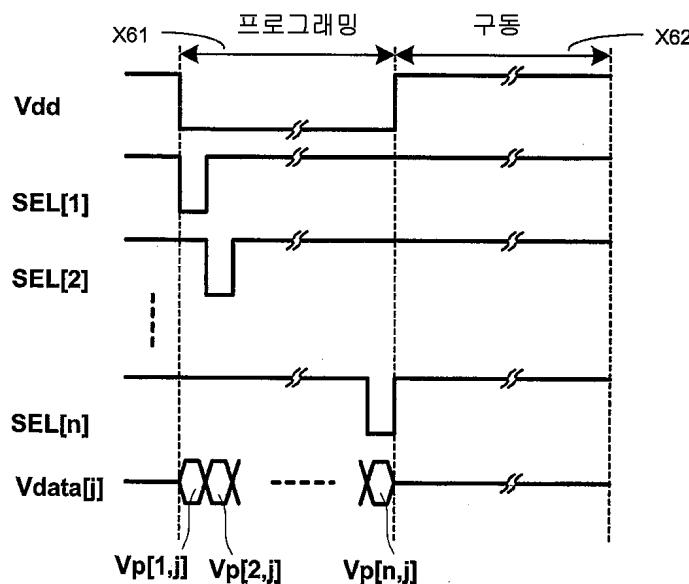

- [0146] 도 25에 도시된 바와 같이, 픽셀 회로(400)의 동작은 프로그래밍 단계 X61 및 구동 단계 X62를 포함한다. 도 25의 Vdata[j]는 도 24의 Vdd에 대응한다. 도 25의 Vp[k,j](k=1,2,...,n)는 Vdata[j] 상의 k 번째 프로그래밍 전압을 나타내며, 여기에서 "j"는 열 번호이다.

- [0147] 도 24 및 도 25를 참조하여, 프로그래밍 사이클 X61 동안, SEL은 로우이며, 그리하여 스위치 트랜지스터(408 및

410)는 온이다. 바이어스 전류 Ibias가 바이어스 라인 Ibias를 통하여 픽셀 회로(400)에 인가되고, 구동 트랜지스터(406)의 게이트 단자는 모든 전류가 구동 트랜지스터(406)의 소스-드레인을 통과할 수 있도록 자가 조정된다. 이 사이클에서, Vdata는 픽셀의 그레이 스케일에 관련된 프로그래밍 전압을 갖는다. 구동 사이클 X62 동안, 스위치 트랜지스터(408 및 410)는 오프(off)이고, 전류는 구동 트랜지스터(406) 및 OLED(402)를 통과한다.

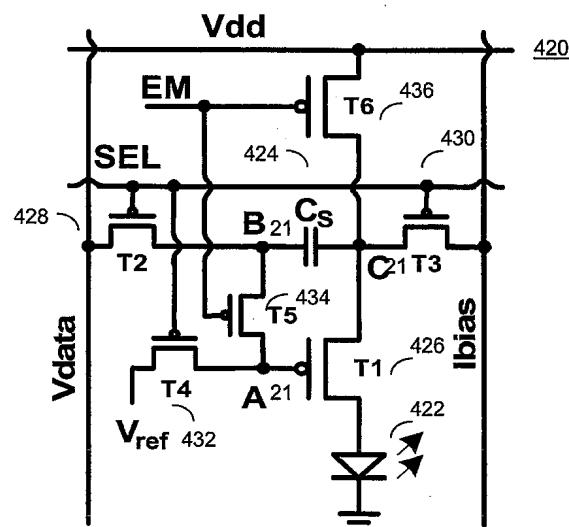

[0148] 도 26은 본 발명의 부가적인 실시예에 따른 픽셀 회로(420)를 도시하는 도면이다. 도 26의 픽셀 회로(420)는 6-TFT 전류 바이어싱된 전압 프로그래밍된 픽셀 회로이며, 방출 제어(emission control)와 함께 CBVP 구동 방식을 채용한다. 이 구동 방식은 부정합을 보상함으로서 디스플레이 수명 및 수율을 개선한다.

[0149] 픽셀 회로(420)는 OLED(422), 스토리지 커패시터(424), 및 트랜지스터(426-436)를 포함한다. 각각의 트랜지스터는 게이트 단자, 제1 단자 및 제2 단자를 갖는다. 트랜지스터(426-436)는 p형 TFT 트랜지스터이다. 픽셀 회로(420)에 적용된 구동 기술은 또한, n형 트랜지스터를 가지며 당해 기술 분야에서의 통상의 지식을 가진 자라면 이해할 상보형 픽셀 회로에 적용 가능하다.

[0150] 트랜지스터(426-436)는 폴리 실리콘, 나노/마이크로(결정질) 실리콘, 비정질 실리콘, CMOS, 유기 반도체, 금속 유기 기술, 또는 이들의 조합을 사용하여 구현될 수 있다. 복수의 픽셀 회로(420)가 능동 매트릭스 어레이를 형성할 수 있다. 픽셀 회로(420)에 적용된 구동 방식은 능동 매트릭스 어레이에서의 시간 및 공간적 비균일성을 보상한다.

[0151] 하나의 선택 라인 SEL, 신호 라인 Vdata, 바이어스 라인 Ibias, 전압 공급 라인 Vdd, 기준 전압 라인 Vref, 및 방출 신호 라인 EM이 픽셀 회로(420)에 접속된다. 바이어스 라인 Ibias는 수명, 전력 및 디바이스 성능과 균일성과 같은 디스플레이 사양에 기초하여 정의되는 바이어스 전류(Ibias)를 제공한다. 기준 전압 라인 Vref는 기준 전압(Vref)을 제공한다. 기준 전압 Vref는 그레이 스케일 및/또는 콘트라스트 비(contrast ratio)를 포함할 수 있는 디스플레이 사양 및 바이어스 전류 Ibias에 기초하여 결정될 수 있다. 신호 라인 EM은 픽셀 회로(420)를 온시키는 방출 신호 EM을 제공한다. 픽셀 회로(420)는 방출 신호 EM에 기초하여 방출 모드로 간다.

[0152] 트랜지스터(426)의 게이트 단자, 트랜지스터(432)의 하나의 단자, 및 트랜지스터(434)의 하나의 단자가 노드 A21에서 접속된다. 커패시터(424)의 하나의 단자, 트랜지스터(428)의 하나의 단자 및 트랜지스터(434)의 다른 단자가 노드 B21에서 접속된다. 커패시터(424)의 다른 단자, 트랜지스터(430)의 하나의 단자, 트랜지스터(436)의 하나의 단자, 및 트랜지스터(426)의 하나의 단자가 노드 C21에서 접속된다. 트랜지스터(430)의 다른 단자가 바이어스 라인 Ibias에 접속된다. 트랜지스터(432)의 다른 단자가 기준 전압 라인 Vref에 접속된다. 선택 라인 SEL은 트랜지스터(428, 430, 및 432)의 게이트 단자에 접속된다. 선택 라인 EM은 트랜지스터(434, 및 436)의 게이트 단자에 접속된다. 트랜지스터(426)는 구동 트랜지스터이다. 트랜지스터(428, 430, 432, 434 및 436)는 스위칭 트랜지스터이다.

[0153] 픽셀 회로(420)에 대하여, 미리 결정된 고정된 전류(Ibias)가 트랜지스터(430)를 통하여 제공되며, 기준 전압 Vref가 트랜지스터(426)의 게이트 단자에 트랜지스터(432)를 통해 인가되고, 프로그래밍 전압 VP가 스토리지 커패시터(424)의 다른 단자(즉, 노드 B21)에 트랜지스터(428)를 통해 인가된다. 여기에서, 트랜지스터(426)의 소스 전압(즉, 노드 C21의 전압)은 바이어스 전류가 트랜지스터(426)를 통해 갈 수 있도록 자가 조정될 것이며, 그리하여 모든 공간 및 시간적 비균일성을 보상한다. 또한, 다양한 그레이 스케일에 대해 요구되는 다양한 전류 레벨의 전류를 분배하는데 전압 프로그래밍이 사용된다.

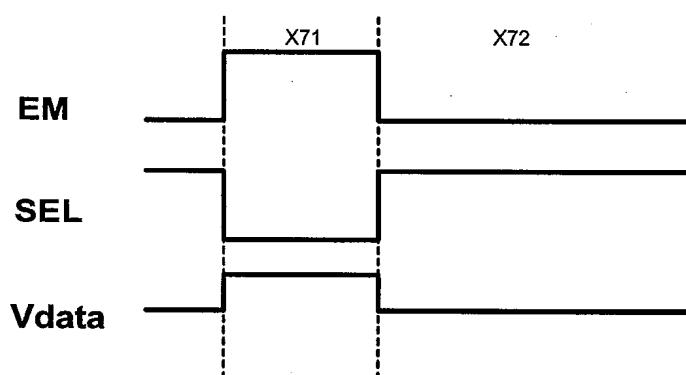

[0154] 도 27에 도시된 바와 같이, 픽셀 회로(420)의 동작은 프로그래밍 단계 X71 및 구동 단계 X72를 포함한다.

[0155] 도 26 및 도 27을 참조하면, 프로그래밍 사이클 X71 동안, SEL은 루우이며, 그리하여 트랜지스터(428, 430 및 432)는 온이고, 고정된 바이어스 전류가 Ibias 라인으로 인가되며, 트랜지스터(426)의 소스는 모든 전류가 트랜지스터(426)의 소스-드레인을 통과할 수 있도록 자가 조정된다. 이 사이클에서, Vdata는 픽셀의 그레이 스케일에 관련된 프로그래밍 전압을 갖고, 커패시터(424)는 프로그래밍 전압 및 부정합 보상을 위해 전류에 의해 발생된 전압을 저장한다. 구동 사이클 X72 동안, 트랜지스터(428, 430 및 432)는 오프이며, 트랜지스터(434 및 436)는 방출 신호 EM에 의해 온이다. 이 구동 사이클 X72 동안, 트랜지스터(426)는 OLED(422)에 대하여 전류를 제공한다.

[0156] 도 25에서는, 전체 디스플레이가 프로그래밍되고, 그 다음에 불이 켜진다(방출 모드로 감). 이와 대조적으로, 도 27에서는, 각각의 행이 방출 신호 EM을 사용함으로써 프로그래밍 후에 불이 켜질 수 있다.

[0157] 도 25 및 도 27의 동작에 있어서, 바이어스 라인은 미리 결정된 고정된 바이어스 전류를 제공한다. 그러나, 바

이어스 전류 Ibias는 조정 가능할 수 있고, 바이어스 전류 Ibias는 디스플레이의 동작 동안 조정될 수 있다.

[0158] 도 28은 CBVP 구동 방식의 구현을 위한 어레이 구조를 갖는 디스플레이 시스템의 예를 도시한다. 도 28의 디스플레이 시스템(450)은 복수의 픽셀(454)을 갖는 픽셀 어레이(452), 게이트 구동기(456), 소스 구동기(458) 및 구동기(456 및 458)를 제어하기 위한 컨트롤러(460)를 포함한다. 게이트 구동기(456)는 어드레스(선택) 라인(예를 들어, SEL[1], SEL[2]...)에 대해 동작한다. 소스 구동기(458)는 데이터 라인(예를 들어, Vdata[1], Vdata[2], ...)에 대해 동작한다. 디스플레이 시스템(450)은 기준 전류 Iref를 사용하여 바이어스 라인(예를 들어, Ibias[1], Ibias[2]...)에 대해 동작하는 보정된 전류 미러 블록(462)을 포함한다. 블록(462)은 각각이 대응하는 Ibias에 대한 것인 복수의 보정된 전류 미러를 포함한다. 기준 전류 Iref는 보정된 전류 미러 블록(462)에 스위치를 통해 제공될 수 있다.

[0159] 픽셀 회로(454)는 도 24의 픽셀 회로(400) 또는 도 26의 픽셀 회로(420)와 동일한 것일 수 있으며, 여기에서 SEL[i](i=1,2,...)는 도 24 또는 도 26의 SEL에 대응하고, Vdata[j](j=1,2,...)는 도 24 또는 도 26의 Vdata에 대응하고, Ibias[j](j=1,2,...)는 도 24 또는 도 26의 Ibias에 대응한다. 픽셀 회로(454)로서 도 26의 픽셀 회로(420)를 사용할 때, 게이트 구동기(456)와 같은 디스플레이의 주변 장치에서의 구동기는 각각의 방출 라인 EM을 제어한다.

[0160] 도 28에서, 전류 미러는 기준 전류 소스를 이용해 보정된다. 패널의 프로그래밍 사이클(예를 들어, 도 25의 X61, 도 27의 X71) 동안, 보정된 전류 미러(블록 462)는 바이어스 라인 Ibias에 전류를 제공한다. 이들 전류 미러는 패널의 에지에서 제조될 수 있다.

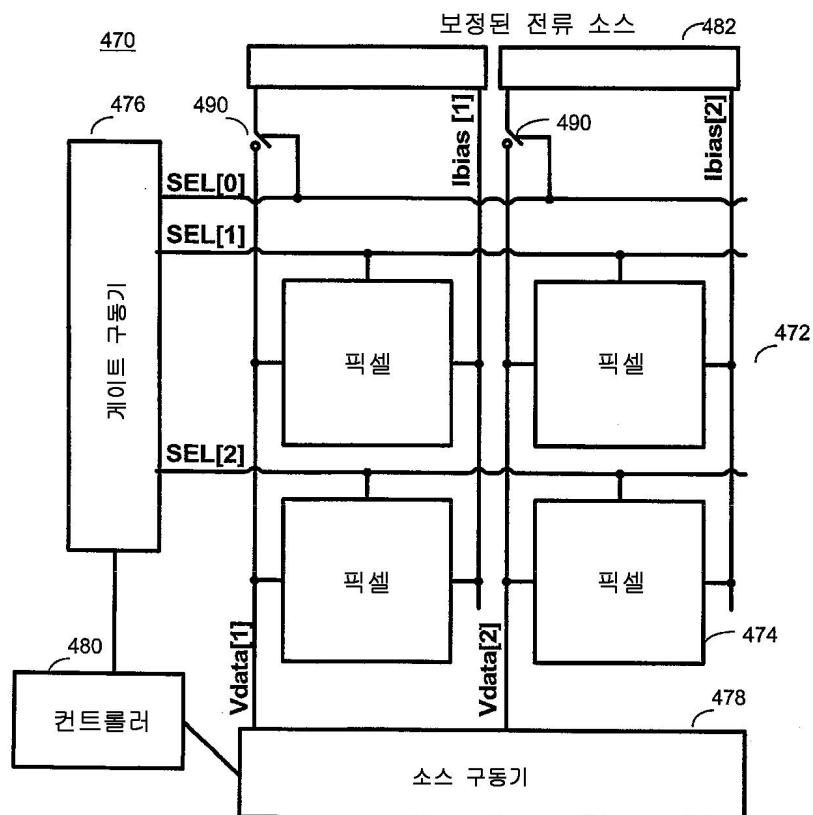

[0161] 도 29는 CBVP 구동 방식의 구현을 위한 어레이 구조를 갖는 디스플레이 시스템의 다른 예를 도시한다. 도 29의 디스플레이 시스템(470)은 복수의 픽셀(474), 게이트 구동기(476), 소스 구동기(478), 및 구동기(476 및 478)를 제어하기 위한 컨트롤러(480)를 갖는 픽셀 어레이(472)를 포함한다. 게이트 구동기(476)는 어드레스(선택) 라인(예를 들어, SEL[0], SEL[1], SEL[2], ...)에 대해 동작한다. 소스 구동기(478)는 데이터 라인(예를 들어, Vdata[1], Vdata[2], ...)에 대해 동작한다. 디스플레이 시스템(470)은 Vdata 라인을 사용하여 바이어스 라인(예를 들어, Ibias[1], Ibias[2]...)에 대해 동작하기 위한 보정된 전류 소스 블록(482)을 포함한다. 블록(482)은 각각이 Ibias 라인에 대하여 제공되는 것인 복수의 보정된 전류 소스를 포함한다.

[0162] 픽셀 회로(474)는 도 24의 픽셀 회로(400) 또는 도 26의 픽셀 회로(420)와 동일한 것일 수 있으며, 여기에서 SEL[i](i=1,2,...)은 도 24 또는 도 26의 SEL에 대응하고, Vdata[j](j=1,2,...)는 도 24 또는 도 26의 Vdata에 대응하고, Ibias[j](j=1,2,...)는 도 24 또는 도 26의 Ibias에 대응한다. 픽셀 회로(474)로서 도 26의 픽셀 회로(420)를 사용할 때, 게이트 구동기(456)와 같은 디스플레이의 주변장치에서의 구동기는 각각의 방출 라인 EM을 제어한다.

[0163] 각각의 전류 소스(482)는 Vdata 라인을 통한 전압을 전류로 변환하는 전압-전류 변환기를 포함한다. 선택 라인들 중 하나는 Vdata 라인을 전류 소스(482)로 접속시키는 스위치(490)를 동작시키는데 사용된다. 이 예에서, 어드레스 라인 SEL[0]은 스위치(490)를 동작시킨다. 전류 소스(482)는 디스플레이의 하나의 행으로서 취급된다(즉, 0번째 행). 전류 소스(482)에서의 Vdata 라인 상의 전압의 변환 후에, Vdata 라인은 디스플레이의 실제 픽셀 회로(474)를 프로그래밍하는데 사용된다.

[0164] 전류 소스 각각에 관련된 전압은 공장에서 추출되어 메모리(예를 들어, 플래시, EEPROM, 또는 PROM)에 저장된다. 이 전압(보정된 전압)은 각각의 전류 소스에 대하여 그들 부정합으로 인해 상이할 수 있다. 각 프레임의 시작에서, 모든 전류 소스(482)가 동일한 전류를 제공하도록, 전류 소스(482)는 저장된 보정된 전압을 사용하여 소스 구동기(478)를 통해 프로그래밍된다.

[0165] 도 28에서, 바이어스 전류(Ibias)는 기준 전류 Iref를 이용해 전류 미러(462)에 의해 발생된다. 그러나, 도 28의 시스템(450)은 Ibias를 발생시키는데 전류 소스(482)를 사용할 수 있다. 도 29에서, 바이어스 전류(Ibias)는 Vdata 라인으로써 전류 소스(482)의 전류 변환기에 의해 발생된다. 그러나, 도 29의 시스템(470)은 도 28의 전류 미러(462)를 사용할 수 있다.

[0166] 상이한 구동 방식을 사용한 패널들의 이미지 품질에 대해 공간적 부정합이 미치는 영향이 도 30 내지 도 32에 나타나 있다. 종래의 2-TFT 픽셀 회로를 구비한 디스플레이의 이미지는 문턱 전압 부정합 및 이동성 변동 둘 다의 단점을 갖는다(도 30). 한편, 바이어스 라인 Ibias 없는 전압 프로그래밍된 픽셀 회로는 문턱 전압 부정합의 영향을 제어할 수 있지만, 이동성 변동의 단점을 가질 수 있는 반면(도 31), 실시예에서의 전류 바이어싱된 전압 프로그래밍된(CBVP) 구동 방식은 이동성 및 문턱 전압 변동 둘 다의 영향을 제어할 수 있다(도 32).

[0167]

본 발명은 하나 이상의 실시예에 관련하여 기재되었다. 그러나, 당해 기술 분야에서의 숙련자라면 청구항에 정의된 본 발명의 범위로부터 벗어나지 않고서 다수의 변형 및 수정이 일어날 수 있다는 것이 명백할 것이다.

### 부호의 설명

[0168]

400: 픽셀 회로

402: 유기 발광 다이오드(OLED)

404: 스토리지 커패시터

406: 구동 트랜지스터

408, 410: 스위치 트랜지스터

### 도면

#### 도면1

200

## 도면2

## 도면3

도면4

도면5

202

도면6

도면7

도면8

204

도면9

## 도면10

206

도면11

도면12

208

도면13

도면14

도면15

도면16

210

도면17

도면18

212

도면19

도면20

214

도면21

도면22

300

도면23

302

도면24

도면25

도면26

도면27

## 도면28

CBVP 구동 방식의 구현을 위한 어레이 구조의 예

## 도면29

CBVP 구동 방식의 구현을 위한 어레이 구조의 부가적인 예

도면30

도면31

도면32