(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6361290号

(P6361290)

(45) 発行日 平成30年7月25日(2018.7.25)

(24) 登録日 平成30年7月6日(2018.7.6)

(51) Int.Cl.

F 1

|             |             |                  |             |             |             |

|-------------|-------------|------------------|-------------|-------------|-------------|

| <b>G06T</b> | <b>3/00</b> | <b>(2006.01)</b> | <b>G06T</b> | <b>3/00</b> | <b>700</b>  |

| <b>G06T</b> | <b>1/60</b> | <b>(2006.01)</b> | <b>G06T</b> | <b>1/60</b> | <b>450D</b> |

| <b>H04N</b> | <b>5/74</b> | <b>(2006.01)</b> | <b>H04N</b> | <b>5/74</b> | <b>D</b>    |

請求項の数 7 (全 25 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2014-112522 (P2014-112522)  |

| (22) 出願日  | 平成26年5月30日 (2014.5.30)        |

| (65) 公開番号 | 特開2015-228056 (P2015-228056A) |

| (43) 公開日  | 平成27年12月17日 (2015.12.17)      |

| 審査請求日     | 平成29年5月22日 (2017.5.22)        |

|           |                                              |

|-----------|----------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区新宿四丁目1番6号 |

| (74) 代理人  | 110000752<br>特許業務法人朝日特許事務所                   |

| (72) 発明者  | 林 賢<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内         |

審査官 大西 宏

最終頁に続く

(54) 【発明の名称】 画像処理装置、表示装置および画像処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

r 行 c 列の画素を有する表示部に表示される画像を処理する画像処理装置であって、前記画像のうち k 1 行分のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、隣り合う少なくとも 2 画素のデータを記憶する第 1 記憶部と、前記画像のうち k 2 行分 (k 1 および k 2 は、 $0 \leq k_1 < (k_1 + k_2) < r$  を満たす自然数であり、 $0 \leq k_2 < r - k_1$  ) のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、前記第 1 記憶部にデータが記憶されている画素とは異なる行において隣り合う少なくとも 2 画素のデータを記憶する第 2 記憶部と、

前記 r 行 c 列の画素のうち処理対象となる対象画素のデータを、前記第 1 記憶部および前記第 2 記憶部において当該対象画素に対応するオフセットベクトルにより示される位置に対応する記憶領域に記憶されている複数の画素のデータを用いて補正を行う補正部とを有し、

前記画像の少なくとも一部が 1 行おきに、互い違いに、前記第 1 記憶部および前記第 2 記憶部に分割されて記憶される

画像処理装置。

## 【請求項 2】

前記オフセットベクトルにより示される位置が前記第 1 記憶部の第 1 記憶領域に記憶されている画素および前記第 2 記憶部の第 2 記憶領域に記憶されている画素の間の位置だつ

た場合、前記補正部は、当該第1記憶領域および当該第2記憶領域に記憶されているデータを用いて、前記補正を行う

ことを特徴とする請求項1に記載の画像処理装置。

**【請求項3】**

前記オフセットベクトルにより示される位置が前記第1記憶部の2つの記憶領域に記憶されている2つの画素の間に対応する位置だった場合、前記補正部は、当該2つの記憶領域から順次読み出されたデータを用いて、前記補正を行う

ことを特徴とする請求項1または2に記載の画像処理装置。

**【請求項4】**

直近の単位期間において前記補正部が用いたデータを記憶するキャッシュ記憶部を有し

、前記対象画素が、前記直近の単位期間から1画素分移動した場合、前記補正部は、前記キャッシュ記憶部に記憶されているデータ、並びに前記第1記憶部および前記第2記憶部のいずれかに記憶されているデータを用いて前記補正を行う

ことを特徴とする請求項1ないし3のいずれか一項に記載の画像処理装置。

**【請求項5】**

前記第1記憶部にデータが記憶されている画素と同じ行において当該画素と隣り合う画素を含み、互いに隣り合う少なくとも2画素のデータを記憶する第3記憶部と、

前記第2記憶部にデータが記憶されている画素と同じ行において当該画素と隣り合う画素を含み、互いに隣り合う少なくとも2画素のデータを記憶する第4記憶部と

を有し、

前記画像の一部が2列おきに、互い違いに、前記第1記憶部および前記第3記憶部に分割されて記憶され、

前記画像の残りが2列おきに、互い違いに、前記第2記憶部および前記第4記憶部に分割されて記憶され、

前記補正部は、前記対象画素のデータを、前記第1記憶部、前記第2記憶部、前記第3記憶部、および前記第4記憶部において当該対象画素に対応するオフセットベクトルにより示される位置に対応する記憶領域に記憶されている複数の画素のデータを用いて前記補正を行う

ことを特徴とする請求項1ないし4のいずれか一項に記載の画像処理装置。

**【請求項6】**

r行c列の画素を有する表示部と、

前記表示部に表示される画像のうち $k_1$ 行分のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、隣り合う少なくとも2画素のデータを記憶する第1記憶部と、

前記画像のうち $k_2$ 行分( $k_1$ および $k_2$ は、 $0 \leq k_1 < (k_1 + k_2) < r$ を満たす自然数であり、 $0 \leq k_2 < r - k_1$ を満たす自然数である)のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、前記第1記憶部にデータが記憶されている画素とは異なる行において隣り合う少なくとも2画素のデータを記憶する第2記憶部と、

前記r行c列の画素のうち処理対象となる対象画素のデータを、前記第1記憶部および前記第2記憶部において当該対象画素に対応するオフセットベクトルにより示される位置に対応する記憶領域に記憶されている複数の画素のデータを用いて補正を行う補正部と

を有し、

前記画像の少なくとも一部が1行おきに、互い違いに、前記第1記憶部および前記第2記憶部に分割されて記憶される

表示装置。

**【請求項7】**

r行c列の画素を有する表示部に表示される画像を処理する画像処理方法であって、

前記画像のうち $k_1$ 行分のデータに相当する複数の記憶領域を有し、当該複数の記憶領

10

20

30

40

50

域の各々に、隣り合う少なくとも 2 画素のデータを第 1 記憶部に記憶するステップと、前記画像のうち  $k_2$  行分 ( $k_1$  および  $k_2$  は、 $0 \leq k_1 < (k_1 + k_2) < r$  を満たす自然数であり、 $0 \leq k_1 < (k_1 + k_2) < r$  を満たす自然数であり、 $0 \leq k_1 < (k_1 + k_2) < r$  を満たす自然数である) のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、前記第 1 記憶部にデータが記憶されている画素とは異なる行において隣り合う少なくとも 2 画素のデータを第 2 記憶部に記憶するステップと、

前記  $r$  行  $c$  列の画素のうち処理対象となる対象画素のデータを、前記第 1 記憶部および前記第 2 記憶部において当該対象画素に対応するオフセットベクトルにより示される位置に対応する記憶領域に記憶されている複数の画素のデータを用いて補正を行うステップとを有し、

前記画像の少なくとも一部が 1 行おきに、互い違いに、前記第 1 記憶部および前記第 2 記憶部に分割されて記憶される

画像処理方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像を補正する技術に関する。

【背景技術】

【0002】

プロジェクターにおいては、スクリーンと投写系との位置関係が理想的な状態からずれると、スクリーンに投写される画像が歪む。この歪みを解消するため、入力映像に対してこれと逆の歪みを与える画像処理が用いられている。この画像処理は入力映像のうち処理対象の画素に対して、この画素に対応するオフセットベクトルで指定される位置にある他の画素のデータを参照して行われる。この場合において、オフセットベクトルの成分が整数でないときは、オフセットベクトルで指定される位置の周囲の 4 画素のデータを参照して、画像処理が行われる。

【0003】

4 画素のデータを用いて画像処理を行うには、当然のことながら 4 画素分のデータをメモリーから読み出す必要がある。すなわち、1 つの RAM に 4 回アクセスする必要があり、データの読み出しに 4 クロック分の時間がかかるてしまう。例えば、オフセットベクトルの成分が整数である場合と比較すると、データの読み出しに 4 倍の時間がかかるてしまい、その分、映像信号出力が遅くなってしまう。

【0004】

特許文献 1 は、垂直方向の 2 画素のデータを用いてズーム画像を生成するため、画像クロックの 2 倍のクロックレートでメモリーにアクセスする技術を開示している。

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】特開平 10 - 336573 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献 1 に記載の技術においては、高速のクロックを生成する必要があり、画像処理回路が高コストになってしまうという問題があった。

【0007】

これに対し本発明は、メモリーアクセス用の高速クロックを用いずに、補正に用いられるデータを得る時間を短縮する技術を提供する。

【課題を解決するための手段】

【0008】

本発明は、 $r$  行  $c$  列の画素を有する表示部に表示される画像を処理する画像処理装置で

10

20

30

40

50

あって、前記画像のうち  $k_1$  行分のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、隣り合う少なくとも 2 画素のデータを記憶する第 1 記憶部と、前記画像のうち  $k_2$  行分 ( $k_1$  および  $k_2$  は、 $0 \leq k_1 + k_2 < r$  を満たす自然数であり、 $0 \leq k_1 + k_2 < r$  は前記表示部に対してあらかじめ設定されたオフセット最大値である) のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、前記第 1 記憶部にデータが記憶されている画素とは異なる行において隣り合う少なくとも 2 画素のデータを記憶する第 2 記憶部と、前記  $r$  行  $c$  列の画素のうち処理対象となる対象画素のデータを、前記第 1 記憶部および前記第 2 記憶部において当該対象画素に対応するオフセットベクトルにより示される位置に対応する記憶領域に記憶されている複数の画素のデータを用いて補正を行う補正部とを有する画像処理装置を提供する。

10

#### 【0009】

この画像処理装置によれば、メモリーアクセス用の高速クロックを用いずに、補正に用いられるデータを得る時間を短縮することができる。

#### 【0010】

前記オフセットベクトルにより示される位置が前記第 1 記憶部の第 1 記憶領域に記憶されている画素および前記第 2 記憶部の第 2 記憶領域に記憶されている画素の間の位置だった場合、前記補正部は、当該第 1 記憶領域および当該第 2 記憶領域に記憶されているデータを用いて、前記補正を行ってもよい。

#### 【0011】

この画像処理装置によれば、オフセットベクトルにより示される位置が第 1 記憶部の第 1 記憶領域に記憶されている画素および第 2 記憶部の第 2 記憶領域に記憶されている画素の間の位置であった場合も補正をすることができる。

20

#### 【0012】

前記オフセットベクトルにより示される位置が前記第 1 記憶部の 2 つの記憶領域に記憶されている 2 つの画素の間に對応する位置だった場合、前記補正部は、当該 2 つの記憶領域から順次読み出されたデータを用いて、前記補正を行ってもよい。

#### 【0013】

この画像処理装置によれば、オフセットベクトルにより示される位置が第 1 記憶部の 2 つの記憶領域に記憶されている 2 つの画素の間に對応する位置であった場合も補正をすることができる。

30

#### 【0014】

この画像処理装置は、直近の単位期間において前記補正部が用いたデータを記憶するキャッシュ記憶部を有し、前記対象画素が、前記直近の単位期間から 1 画素分移動した場合、前記補正部は、前記キャッシュ記憶部に記憶されているデータ、並びに前記第 1 記憶部および前記第 2 記憶部のいずれかに記憶されているデータを用いて前記補正を行ってもよい。

#### 【0015】

この画像処理装置によれば、キャッシュ記憶部を用いない場合と比較してよりデータ読み出しの時間を短縮することができる。

#### 【0016】

この画像処理装置は、前記第 1 記憶部にデータが記憶されている画素と同じ行において当該画素と隣り合う画素を含み、互いに隣り合う少なくとも 2 画素のデータを記憶する第 3 記憶部と、前記第 2 記憶部にデータが記憶されている画素と同じ行において当該画素と隣り合う画素を含み、互いに隣り合う少なくとも 2 画素のデータを記憶する第 4 記憶部とを有し、前記補正部は、前記対象画素のデータを、前記第 1 記憶部、前記第 2 記憶部、前記第 3 記憶部、および前記第 4 記憶部において当該対象画素に対応するオフセットベクトルにより示される位置に対応する記憶領域に記憶されている複数の画素のデータを用いて補正を行ってもよい。

40

#### 【0017】

この画像処理装置によれば、第 3 記憶部および第 4 記憶部を用いない場合と比較してよ

50

りデータ読み出しの時間を短縮することができる。

**【0018】**

また、本発明は、 $r$  行  $c$  列の画素を有する表示部と、前記表示部に表示される画像のうち  $k_1$  行分のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、隣り合う少なくとも 2 画素のデータを記憶する第 1 記憶部と、前記画像のうち  $k_2$  行分 ( $k_1$  および  $k_2$  は、 $0 \leq k_1 + k_2 < r$  を満たす自然数であり、 $0 \leq k_1 + k_2 < r$  は前記表示部に対してあらかじめ設定されたオフセット最大値である) のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、前記第 1 記憶部にデータが記憶されている画素とは異なる行において隣り合う少なくとも 2 画素のデータを記憶する第 2 記憶部と、前記  $r$  行  $c$  列の画素のうち処理対象となる対象画素のデータを、前記第 1 記憶部および前記第 2 記憶部において当該対象画素に対応するオフセットベクトルにより示される位置に対応する記憶領域に記憶されている複数の画素のデータを用いて補正を行う補正部とを有する表示装置を提供する。10

**【0019】**

この表示装置によれば、メモリーアクセス用の高速クロックを用いずに、補正に用いられるデータを得る時間を短縮することができる。

**【0020】**

さらに、本発明は、 $r$  行  $c$  列の画素を有する表示部に表示される画像を処理する画像処理方法であって、前記画像のうち  $k_1$  行分のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、隣り合う少なくとも 2 画素のデータを第 1 記憶部に記憶するステップと、前記画像のうち  $k_2$  行分 ( $k_1$  および  $k_2$  は、 $0 \leq k_1 + k_2 < r$  を満たす自然数であり、 $0 \leq k_1 + k_2 < r$  は前記表示部に対してあらかじめ設定されたオフセット最大値である) のデータに相当する複数の記憶領域を有し、当該複数の記憶領域の各々に、前記第 1 記憶部にデータが記憶されている画素とは異なる行において隣り合う少なくとも 2 画素のデータを第 2 記憶部に記憶するステップと、前記  $r$  行  $c$  列の画素のうち処理対象となる対象画素のデータを、前記第 1 記憶部および前記第 2 記憶部において当該対象画素に対応するオフセットベクトルにより示される位置に対応する記憶領域に記憶されている複数の画素のデータを用いて補正を行うステップとを有する画像処理方法を提供する。20

**【0021】**

この画像処理方法によれば、メモリーアクセス用の高速クロックを用いずに、補正に用いられるデータを得る時間を短縮することができる。30

**【図面の簡単な説明】**

**【0022】**

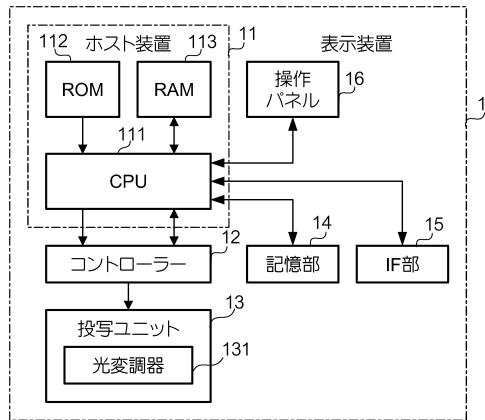

【図 1】一実施形態に係る表示装置 1 の構成を示すブロック図。

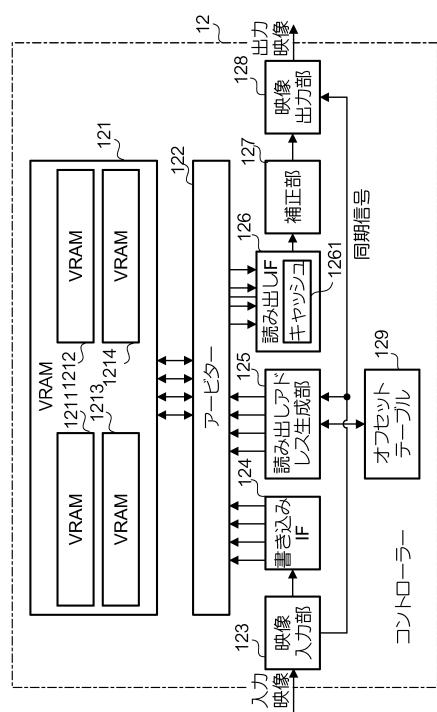

【図 2】コントローラー 1 2 の構成を示す図。

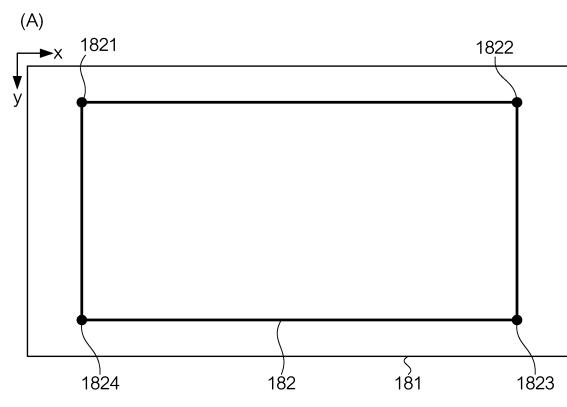

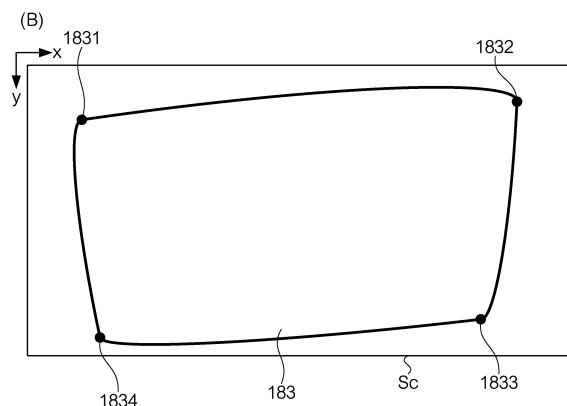

【図 3】投写される画像の歪みを例示する図。

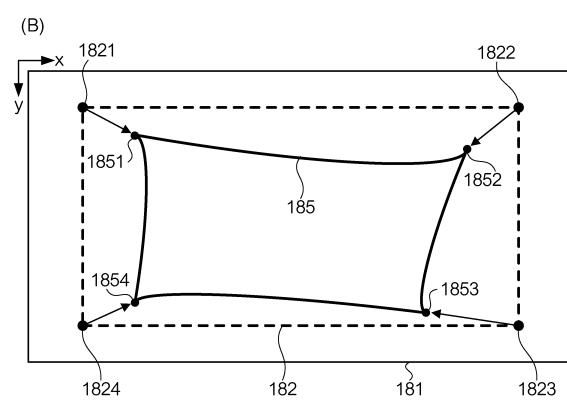

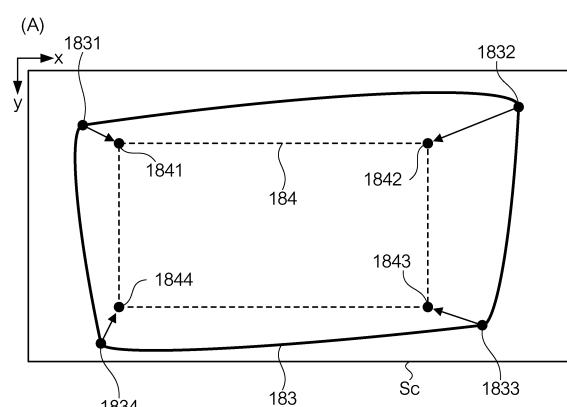

【図 4】補正後の目標となる図形 1 8 4 を例示する図。

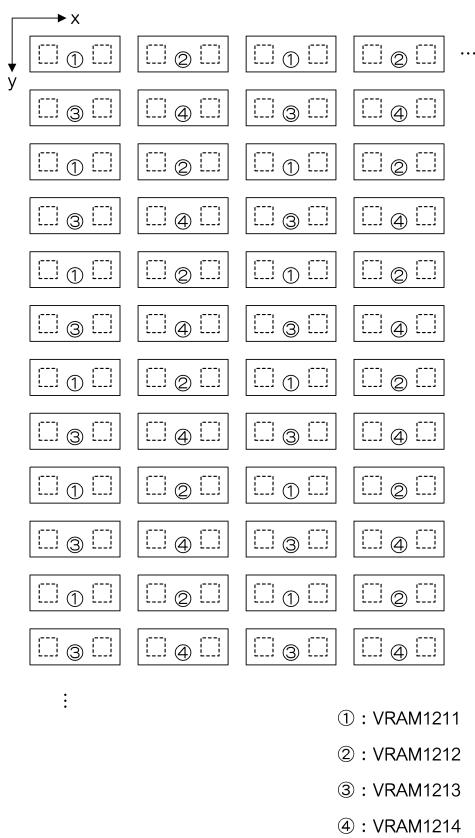

【図 5】記憶領域の割り当てを例示する図。

【図 6】記憶領域の割り当ての具体例を示す図。

【図 7】オフセットベクトルが指す位置  $P_d$  を例示する図。

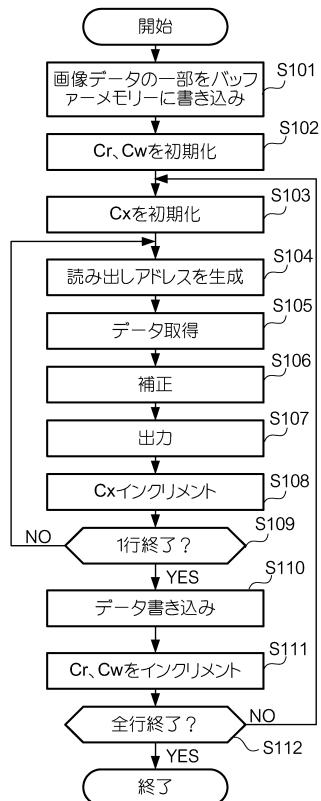

【図 8】表示装置 1 の動作を示すフローチャート。

【図 9】ステップ S 1 0 4 における読み出しあドレス生成処理の詳細を示す図。

【図 10】キャッシュ 1 2 6 1 の構成を例示する図。

【図 11】補正に用いられる画素を例示する図。

【図 12】動作例 1 を示す図。

【図 13】動作例 2 を示す図。

【図 14】動作例 3 を示す図。

【図 15】動作例 4 を示す図。

【図 16】 $C_r = 1$  および  $C_w = 1 2 1$  の状態を示す図。40

50

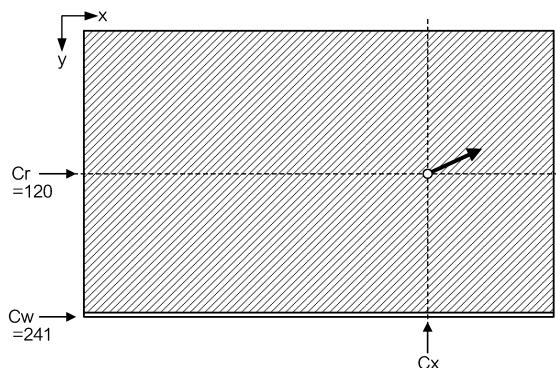

【図17】Cr = 120およびCw = 241の状態を示す図。

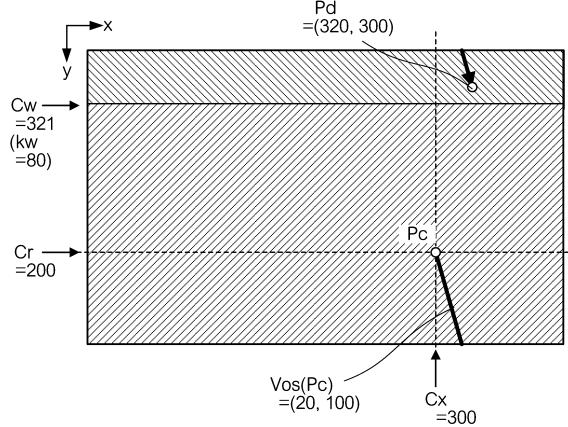

【図18】Cr = 200およびCw = 321の状態を示す図。

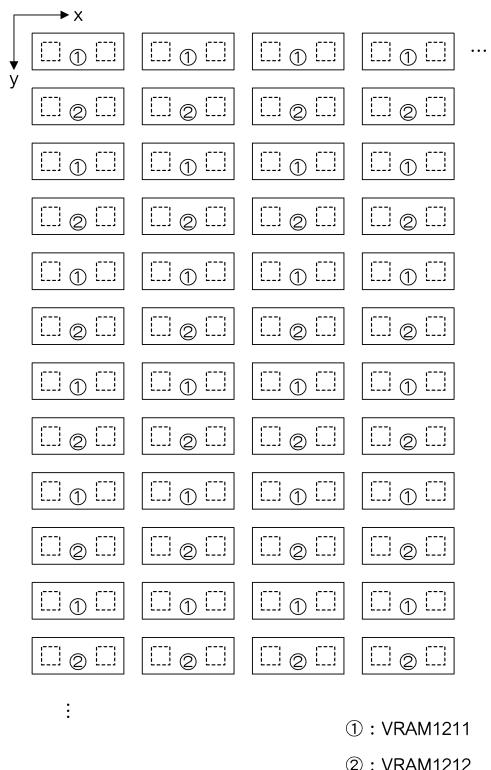

【図19】2つのフレームバッファーへの記憶領域の割り当てを例示する図。

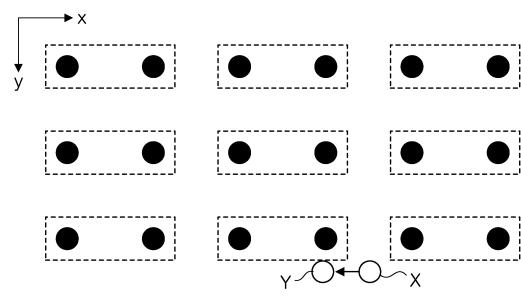

【図20】変形例4に係る位置Pdの補正を例示する図。

【発明を実施するための形態】

【0023】

#### 1. 構成

図1は、一実施形態に係る表示装置1の構成を示すブロック図である。表示装置1は、例えば、自動車、電車、または飛行機のフロントガラスに画像を投写する投写型の表示装置、いわゆるHUD(Head-Up Display)である。表示装置1が自動車に用いられる場合、投写される画像は、例えば、カーナビゲーションの画面または各種計器(例えば速度計や回転計)の測定結果を示す画像である。10

【0024】

表示装置1は、ホスト装置11と、コントローラー12と、投写ユニット13と、記憶部14と、IF部15と、操作パネル16とを有する。

【0025】

ホスト装置11は、表示装置1の他の構成要素を制御する。ホスト装置11は、CPU(Central Processing Unit)111と、ROM(Read Only Memory)112と、RAM(Random Access Memory)113とを有する。CPU111は、表示装置1の各部を制御する制御装置である。ROM112は、各種プログラムおよびデータを記憶した不揮発性の記憶装置である。RAM113は、データを記憶する揮発性の記憶装置であり、CPU111が処理を実行する際のワークエリアとして機能する。20

【0026】

コントローラー12は、投写ユニット13を制御する装置である。この例で、コントローラー12は、入力された映像信号(以下「入力映像信号」という)に所定の画像処理を施す画像処理装置として機能する。コントローラー12は、画像処理を施した映像信号を、投写ユニット13に出力する。

【0027】

投写ユニット13は、画像処理が施された映像信号に従って、スクリーンに画像を投写する。投写ユニット13は、光源、光変調器131、および光学系、並びにこれらの駆動回路を有する(光変調器131以外は図示略)。光源は、高圧水銀ランプ、ハロゲンランプ、若しくはメタルハライドランプなどのランプ、またはLED(Light Emitting Diode)若しくはレーザーダイオードなどの固体光源である。光変調器131は、光源から照射された光を映像信号に応じて変調する装置であり、例えば液晶パネルまたはDMD(Digital Mirror Device)等の表示部を有する。光変調器131は、r行c列のマトリクス状に配置された画素を有し、画素毎に光を変調する。光学系は、光変調器により変調された光をスクリーンに投写する素子であり、例えばレンズおよびプリズムを有する。30

【0028】

記憶部14は、データおよびプログラムを記憶する不揮発性の記憶装置、例えばHDD(Hard Disk Drive)またはSSD(Solid State Drive)である。記憶部14は、例えば、カーナビゲーションを実行するためのプログラムおよび地図データを記憶している。ホスト装置11は、記憶部14に記憶されているプログラムおよびデータを用いてカーナビゲーションの画像を生成し、後段の回路に出力する。40

【0029】

IF部15は、外部装置(例えば各種計器)と信号またはデータの送受信を仲介するインターフェースである。IF部15は、外部装置と信号またはデータの送受信をするための端子を有する。

【0030】

操作パネル16は、ユーザーが表示装置1に対し指示を入力するための入力装置であり、例えば、キーパッド、ボタン、またはタッチパネルを含む。50

**【0031】**

図2は、コントローラー12の構成を示す図である。コントローラー12は、VRAM(Video RAM)121と、アービター122と、映像入力部123と、書き込みIF124と、読み出しアドレス生成部125と、読み出しIF126と、補正部127と、映像出力部128と、オフセットテーブル129とを有する。

**【0032】**

VRAM121は、全部でk行分の画像データを記憶する記憶領域を有し、フレームバッファーとして用いられるメモリー(記憶部)である。ここで、kは、

$$0 \leq k \leq r \dots (1)$$

を満たす自然数である。Omaxは、用いられる光変調器131に応じてあらかじめ設定されたオフセット最大値である。オフセット最大値については後述する。10

**【0033】**

VRAM121は、詳細には、VRAM1211、VRAM1212、VRAM1213、およびVRAM1214の4つのフレームバッファー(第1～第4記憶部の一例)を有する。VRAM1211、VRAM1212、VRAM1213、およびVRAM1214を区別する必要が無いときは、VRAM121と記載する。VRAM1211、VRAM1212、VRAM1213、およびVRAM1214は、それぞれ、k<sub>1</sub>、k<sub>2</sub>、k<sub>3</sub>、およびk<sub>4</sub>行分のデータを記憶する記憶領域を有する。なお、k<sub>1</sub>、k<sub>2</sub>、k<sub>3</sub>、およびk<sub>4</sub>は、k<sub>1</sub>+k<sub>2</sub>+k<sub>3</sub>+k<sub>4</sub>=kを満たす自然数である。また、k<sub>1</sub>=k<sub>2</sub>=k<sub>3</sub>=k<sub>4</sub>であることが好ましい。20

**【0034】**

VRAM1211～1214の各々は、複数の単位記憶領域に区分されている。各単位記憶領域は、アドレスにより特定される。各単位記憶領域には、行方向において隣り合う(一連の)少なくとも2つの画素のデータが記憶される。すなわち、あるアドレスで特定される記憶領域には、行方向において隣り合う一連の少なくとも2画素のデータがパッキングされて記憶されており、データの読み出しおよび書き込みはこれら複数の画素を単位として行われる。

**【0035】**

本実施形態において、各単位記憶領域には、隣り合う2つの画素のデータが記憶されている。例えば、1画素のデータが24ビットである場合には、単位記憶領域は48ビットの記憶容量を有する。上位24ビットにはx座標が小さい画素のデータが、下位24ビットにはx座標が大きい画素のデータが記憶されている。なお、VRAM1211～1214の記憶領域と画素との関係については後述する。30

**【0036】**

なおVRAM121は、必ずしも全体でk行c列の記憶領域を有していなくてもよい。VRAM121はk行c列よりも多くの記憶領域を有していてもよい。この場合、VRAM121の一部の記憶領域をブロック分割して用いることができる。あるいは、ハードウェアとしては単一のRAMの記憶領域を4つに分割して、それぞれVRAM1211～1214として用いてもよい。また、図2ではコントローラー12がVRAM121を内蔵している例を示したが、VRAM121はコントローラー12の外部に設けられてもよい。40

**【0037】**

アービター122は、VRAM121へアクセスする権利を調停する回路である。

**【0038】**

映像入力部123は、ホスト装置11から映像信号(「入力映像信号」という)を受け付ける。映像入力部123は、入力映像信号を、書き込みIF124に出力する。

**【0039】**

書き込みIF124は、入力映像信号をデータとしてVRAM121に書き込む。このとき、書き込みIF124は、VRAM121の記憶領域のうち、ライトカウンターで指定される行に対応する記憶領域にデータを書き込む。ライトカウンターは、データの書き50

込みが行われる行を指定するパラメーターである。書き込み I F 1 2 4 は、ライトカウンターを記憶するためのレジスター（記憶部）を有している（図示略）。

#### 【 0 0 4 0 】

読み出しアドレス生成部 1 2 5 は、処理対象画素のデータの補正に用いられるデータが記憶されている記憶領域を示すアドレス（以下「読み出しアドレス」という）を生成する。読み出しアドレス生成部 1 2 5 は、リードカウンターおよびオフセットベクトルを用いて読み出しアドレスを生成する。リードカウンターは、データ読み出しの基準となる行を指定するパラメーターである。読み出しアドレス生成部 1 2 5 は、リードカウンターを記憶するためのレジスター（記憶部）を有している（図示略）。オフセットベクトルは、オフセットテーブル 1 2 9 から得られる。オフセットテーブル 1 2 9 は、オフセットベクトルが記録されたテーブルを記憶したメモリーである。オフセットベクトルについては後述する。

10

#### 【 0 0 4 1 】

読み出し I F 1 2 6 は、V R A M 1 2 1 からデータを読み出す。この例で、1つのアドレスで指定される記憶領域には、隣り合う2つの画素のデータが含まれている。読み出し I F 1 2 6 は、読み出したデータのうち、画像処理に用いるデータを、補正部 1 2 4 に出力する。

#### 【 0 0 4 2 】

また、読み出し I F 1 2 6 は、キャッシュ 1 2 6 1 を有する。キャッシュ 1 2 6 1 は、既に V R A M 1 2 1 から読み出したデータを一時記憶するメモリー（キャッシュ記憶部の一例）である。

20

#### 【 0 0 4 3 】

補正部 1 2 7 は、データの補正を行う。補正部 1 2 7 は、V R A M 1 2 1 に記憶されているデータのうち読み出しアドレス生成部 1 2 5 が生成したアドレスで指定される記憶領域に記憶されているデータを用いて補正する。補正の具体的方法については後述する。

#### 【 0 0 4 4 】

映像出力部 1 2 8 は、補正部 1 2 7 により補正されたデータを、映像信号として、後段の投写ユニット 1 3 に出力する。

#### 【 0 0 4 5 】

なお、図示は省略したが、コントローラー 1 2 はこれ以外にも、ホスト装置 1 1 との間でデータおよび命令の送受信をするインターフェースを有する。

30

#### 【 0 0 4 6 】

### 2. 歪み補正の概要

図 3 は、投写される画像の歪みを例示する図である。図 3 ( A ) は光変調器 1 3 1 に表示される画像を、図 3 ( B ) はスクリーン S c に投写される画像を例示している。光変調器 1 3 1 は、表示領域 1 8 1 を有する。この例では、表示領域 1 8 1 に長方形 1 8 2 が表示されている。表示領域 1 8 1 に表示されている長方形 1 8 2 に応じて、スクリーン S c には図形 1 8 3 が投写されている。投写ユニット 1 3 の光学系とスクリーンとの位置関係が理想的であれば図形 1 8 3 は長方形になるはずであるが、この例では光学系とスクリーンとの位置関係が理想状態からずれており、図形 1 8 3 は長方形から歪んでいる。図形 1 8 3 は、長方形 1 8 2 の頂点に対応する点 1 8 3 1 、 1 8 3 2 、 1 8 3 3 、および 1 8 3 4 を有する。以下、この歪みを解消する方法の概要を説明する。

40

#### 【 0 0 4 7 】

図 4 は、補正後の目標となる図形 1 8 4 を例示する図である。図 4 ( A ) はスクリーン S c 上における図形 1 8 4 を示している。スクリーン S c 上において、図形 1 8 4 は、例えば、( i ) 所定の向き（例えば、鉛直方向および水平方向）の辺を有し、( i i ) 長方形 1 8 2 と同じ縦横比を有し、かつ( i i i ) 図形 1 8 4 の基準位置と図形 1 8 3 の基準位置が所定の位置関係にある（例えば、図形 1 8 4 の重心と図形 1 8 3 の重心とが一致する）という条件を満たす図形である。図形 1 8 4 は、頂点 1 8 4 1 、 1 8 4 2 、 1 8 4 3 、および 1 8 4 4 を有する。なお図形 1 8 4 は、補正後の画像の面積を最大にする観点か

50

ら、さらに(i v)図形183に内接する、という条件を満たすことが好ましい。図4の例では、図形183および図形184を見やすくするために、条件(i v)は満たしていない。

#### 【0048】

説明を簡単にするため、まず図形183の点1831、1832、1833、および1834だけを考える。補正後の形状を図形184とするには、これらの点を、それぞれ、頂点1841、1842、1843、および1844に移動すればよい。すなわち、補正後の頂点1841のデータ(例えば階調値)は、点1831のデータを参照すればよい。ここで、補正後の点(例えば頂点1841)を基準としたときに、参照すべき補正前の点(例えば点1831)を示すベクトルをオフセットベクトル(オフセットベクター)という。頂点1841、1842、1843、および1844は、それぞれ異なる点1831、1832、1833、および1834を参照するので、オフセットベクトルは各点で定義される。

#### 【0049】

この考え方は図形184の頂点だけでなく、表示領域181の全ての点(すなわち全ての画素)について適用できる。例えば、単なる長方形ではなく格子状のパターンを投写すれば、各格子のずれを用いてオフセットベクトルを定義することができる。

#### 【0050】

オフセットベクトルは、投写ユニット13の光学系とスクリーンとの位置関係が決まれば一意に定まる。例えば、投写ユニット13に所定のテストパターンを投写させ、投写された画像をカメラで撮影して解析することにより、オフセットベクトルを決定することができる。例えば自動車のHUDとして用いる場合のように、投写ユニット13を設置すればスクリーンとの位置関係がその後変わらないときは、決定されたオフセットベクトルをメモリーに記憶しておき、補正の時はこれを参照すればよい。

#### 【0051】

図4(B)は、光変調器131上における図形185を示している。このように、図形183と逆の歪みを与えた画像を表示すれば、歪みが補正された図形184がスクリーンScに表示される。

#### 【0052】

ここで、表示領域181上の画素P(x, y)におけるオフセットベクトルをVos(x, y)と表す。なお、ここでは、図中の左上端の画素の座標を(0, 0)と定義し、右方向および下方向をx軸およびy軸の正方向と定義する。画素P(x, y)の補正後のデータDr(P)は、補正前のデータDoを用いて以下のように表される。

$$Dr(P(x, y)) = Do(P(x, y) + Vos(x, y)) \dots (2)$$

#### 【0053】

オフセットベクトルの大きさをオフセット量という。x方向およびy方向のそれぞれにおけるオフセットベクトルの大きさを、x方向のオフセット量およびy方向のオフセット量という。オフセットベクトルの向きによって、オフセット量は正負いずれの値も取り得る。

#### 【0054】

オフセット量は光学系とスクリーンとの位置関係によって決まるが、例えば自動車向けのように用途が決められている場合、オフセット量の取り得る範囲はある程度限定される。想定されるオフセット量の最大値を、オフセット最大値という。オフセット最大値は正負両方向に対してそれぞれ個別に設定されてもよいし、单一のオフセット最大値が正負両方向に共通に設定されてもよい。

#### 【0055】

なおオフセット最大値がリードカウンターの進行方向に対して正方向および負方向の双方について個別に設定されていた場合、式(1)におけるOmaxは、これら2つの値のうち大きい方の値を有する。

#### 【0056】

10

20

30

40

50

なお、画素  $P(x, y)$  は現実の画素なので  $x$  および  $y$  は整数であるが、オフセットベクトル  $V_{os}$  の成分は整数でなくてもよい。オフセットベクトル  $V_{os}$  の成分が整数でない場合、オフセットベクトル  $V_{os}$  が指す位置は画素そのものではなく、複数の画素の間の点である。このデータの処理に関し、まず、VRAM121へのデータの割り当てについて説明する。

#### 【0057】

図5は、記憶領域の割り当てを例示する図である。破線の四角は画素を示している。この例で、入力映像のデータは、2行4列の8画素を単位として、VRAM121の単位記憶領域が割り当てられている。具体的には、これらの8画素は、行方向に隣り合う2画素（単位記憶領域の容量）を単位として、2行2列の4つの領域に分割される。このうち、左上の領域のデータはVRAM1211に、右上の領域のデータVRAM1212に、左下の領域のデータはVRAM1213に、右下の領域のデータはVRAM1214に、それぞれ記憶されている。10

#### 【0058】

VRAM121の各々において、第  $j$  行第  $i$  列の単位記憶領域を  $A(i, j)$  と表すと、VRAM1211の単位記憶領域  $A(s, t)$  には、画素  $P(4s, 2t)$  および画素  $P(4s+1, 2t)$  のデータが記憶される。VRAM1212の単位記憶領域  $A(s, t)$  には、画素  $P(4s+2, 2t)$  および画素  $P(4s+3, 2t)$  のデータが記憶される。VRAM1213の単位記憶領域  $A(s, t)$  には、画素  $P(4s, 2t+1)$  および画素  $P(4s+1, 2t+1)$  のデータが記憶される。VRAM1214の単位記憶領域  $A(s, t)$  には、画素  $P(4s+2, 2t+1)$  および画素  $P(4s+3, 2t+1)$  のデータが記憶される。20

#### 【0059】

図6は、記憶領域の割り当ての具体例を示す図である。例えば、VRAM1211の単位記憶領域  $A(0, 0)$  には、画素  $P(0, 0)$  および画素  $P(1, 0)$  のデータが、単位記憶領域  $A(1, 0)$  には、画素  $P(4, 0)$  および画素  $P(5, 0)$  のデータが、それぞれ記憶される。VRAM1212の単位記憶領域  $A(0, 0)$  には、画素  $P(2, 0)$  および画素  $P(3, 0)$  のデータが、単位記憶領域  $A(1, 0)$  には、画素  $P(6, 0)$  および画素  $P(7, 0)$  のデータが、それぞれ記憶される。例えば、VRAM1213の単位記憶領域  $A(0, 0)$  には、画素  $P(0, 1)$  および画素  $P(1, 1)$  のデータが、単位記憶領域  $A(1, 0)$  には、画素  $P(4, 1)$  および画素  $P(5, 1)$  のデータが、それぞれ記憶される。VRAM1214の単位記憶領域  $A(0, 0)$  には、画素  $P(2, 1)$  および画素  $P(3, 1)$  のデータが、単位記憶領域  $A(1, 0)$  には、画素  $P(6, 1)$  および画素  $P(7, 1)$  のデータが、それぞれ記憶される。30

#### 【0060】

図7は、オフセットベクトルが指す位置  $P_d$  を例示する図である。位置  $P_d$  の  $x$  座標  $x_d$  および  $y$  座標  $y_d$  がいずれも整数でない場合、位置  $P_d$  の周囲には4つの画素が存在する。これら4つの画素を、参照画素  $P_1(x_1, y_1)$ 、 $P_2(x_2, y_2)$ 、 $P_3(x_3, y_3)$ 、および  $P_4(x_4, y_4)$  という。なお、これらの座標は、

$$x_2 = x_1 + 1$$

$$y_2 = y_1$$

$$x_3 = x_1$$

$$y_3 = y_1 + 1$$

$$x_4 = x_2$$

$$y_4 = y_3$$

$$x_1 \leq x_d < x_2$$

$$y_1 \leq y_d < y_2 \quad \dots (3)$$

を満たす。

#### 【0061】

再び図6を参照する。例えば、参照画素  $P_1 \sim P_4$  が、(0, 0)、(1, 0)、(0

40

50

, 1)、および(1, 1)であった場合、VRAM1211の単位記憶領域A(0, 0)に記憶されているデータ(P(0, 0)およびP(1, 0)のデータ)およびVRAM1213の単位記憶領域A(0, 0)に記憶されているデータ(P(0, 1)およびP(1, 1)のデータ)が読み出される。この場合は、メモリーへのアクセスは2回であり、1画素ずつのデータにアクセスする場合と比較してメモリーへのアクセス回数は半分で済む。

#### 【0062】

例えば、参照画素P1～P4が、(3, 1)、(4, 1)、(3, 2)、および(4, 2)の間にあった場合、VRAM1211の単位記憶領域A(1, 1)に記憶されているデータ(P(4, 2)およびP(5, 2)のデータ)、VRAM1212の単位記憶領域A(0, 1)に記憶されているデータ(P(2, 2)およびP(3, 2)のデータ)、VRAM1213の単位記憶領域A(1, 0)に記憶されているデータ(P(4, 1)およびP(5, 1)のデータ)、およびVRAM1214の単位記憶領域A(0, 0)に記憶されているデータ(P(2, 1)およびP(3, 1)のデータ)が読み出される。この場合は、メモリーへのアクセスは4回である。

#### 【0063】

なおこの場合、キャッシュ1261に記憶されているデータを用いることにより、VRAM121へのアクセス回数を減らすことができる。詳細は後述する。

#### 【0064】

3. 動作

以下、表示装置1の動作例を説明する。ここでは、光変調器131が、WVGA相当の解像度を有する例を用いて説明する。すなわち、光変調器131は、480行800列の画素を有する( $r = 480$ 、 $c = 800$ )。オフセット最大値は120に設定されている( $O_{max} = 120$ )。VRAM121は、241行分のデータを記憶するための記憶領域を有する。なお、241行分とは、オフセット最大値(この例では120行)の2倍に、処理対象画素(この例では1行)の記憶領域を加算した値である。オフセットテーブル129は、各画素のオフセットベクトルを記憶している。

#### 【0065】

##### 3 - 1. 概要

図8は、表示装置1の動作を示すフローチャートである。

30

#### 【0066】

ステップS101において、書き込みIF124は、画像データの一部を、VRAM121に書き込む。ここで書き込まれるデータは、オフセット最大値に相当する量のデータ、この例では、120行分のデータである。すなわち、書き込みIF124は、画像データのうち第1行から第120行までのデータを、VRAM121に書き込む。

#### 【0067】

VRAM121は、第1～241行の記憶領域を有している。ステップS101においては、第1～120行の記憶領域に画像データが書き込まれる。

#### 【0068】

ステップS102において、読み出しアドレス生成部125および書き込みIF124は、それぞれ、リードカウンターCrおよびライトカウンターCwを初期化する。この例では、Cr = 1、Cw = Omax + Cr = 121に初期化される。リードカウンターCrおよびライトカウンターCwは、画像データ上の行の位置を示すカウンターであり、この例では、いずれも1～480の値をとる。なお、ライトカウンターCwとリードカウンターCrとの差は、少なくとも正方向側のオフセット最大値よりも大きい。

40

#### 【0069】

ステップS103において、読み出しアドレス生成部125および補正部127はxCOUNTER-Cxを初期化する。xCOUNTER-Cxは、処理対象の画素を特定するためのパラメーターである。読み出しアドレス生成部125および補正部127はそれぞれ個別にxCOUNTER-Cxを保持しているが、これらは同期信号で同期している。この例では、Cx

50

= 1 に初期化される。以下、補正対象の画素を画素  $P_c$  と表す。画素  $P_c$  の座標は、(  $C_x, C_r$  ) である。

#### 【0070】

ステップ S 104において、読み出しアドレス生成部 125は、読み出しアドレスを生成する。画素  $P_c$  を基準としてオフセットベクトル  $V_{os}$  が指す位置を、位置  $P_d$  と表す。位置  $P_d$  の座標 ( $x_d, y_d$ ) は、次式 (4) で表される。

$$(x_d, y_d) = P_c + V_{os} \dots (4)$$

位置  $P_d$  ( $x_d, y_d$ ) のデータは、VRAM 121において、第  $k_d$  行の記憶領域に記憶されている。読み出しアドレス生成部 125は、次式 (5) を用いて読み出しアドレス  $k_d$  を計算する。

10

$$k_d = y_d \pmod k \dots (5)$$

例えば、 $k = 241$  の場合において  $y_d = 1 \sim 241$  のときは、 $k_d = y_d$  である。 $y_d = 243$  の場合、 $k_d = 2$  である。

#### 【0071】

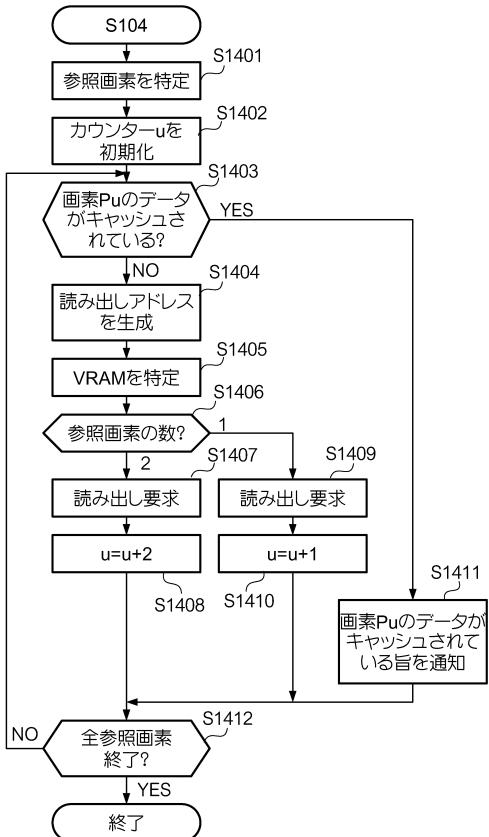

図9は、ステップ S 104における読み出しアドレス生成処理の詳細を示す図である。

#### 【0072】

ステップ S 1401において、読み出しアドレス生成部 125は、参照画素を特定する。

#### 【0073】

ステップ S 1402において、読み出しアドレス生成部 125は、カウンター  $u$  を初期化する。カウンター  $u$  は、画素  $P_1 \sim P_4$  のうち対象となる画素を特定するカウンターである。ここでは  $u = 1$  に初期化される。

20

#### 【0074】

ステップ S 1403において、読み出しアドレス生成部 125は、画素  $P_u$  のデータがキャッシュ 1261に記憶されているか判断する。キャッシュ 1261には、前回の補正に用いられた画素のデータが、その画素の座標とともに記憶されている。画素  $P_u$  のデータがキャッシュ 1261に記憶されていると判断された場合 (S 1403 : YES) 、読み出しアドレス生成部 125は、処理をステップ S 1411に移行する。画素  $P_u$  のデータがキャッシュ 1261に記憶されていないと判断された場合 (S 1403 : NO) 、読み出しアドレス生成部 125は、処理をステップ S 1404に移行する。

30

#### 【0075】

ステップ S 1404において、読み出しアドレス生成部 125は、画素  $P_u$  に対応する読み出しアドレスを生成する。読み出しアドレス生成部 125は、次式 (6) および (7) を用いて読み出しアドレスの  $x$  座標  $x_r$  および  $y$  座標  $y_r$  生成する。

$$x_r = \text{quotient}(4, x_u) - 1 \dots (6)$$

$$y_r = \text{quotient}(2, y_u) - 1 \dots (7)$$

なお、 $\text{quotient}(m, n)$  は、 $n$  を  $m$  で除した商を示す。

#### 【0076】

ステップ S 1405において、読み出しアドレス生成部 125は、以下の条件 (8) ~ (11) を用いて、画素  $P_u$  のデータが記憶されている VRAM を特定する。

40

$$\text{mod}(x_u, 4) = 0 \text{ or } 1 \text{ の場合、VRAM } 1211 \text{ or } 1213 \dots (8)$$

$$\text{mod}(x_u, 4) = 2 \text{ or } 3 \text{ の場合、VRAM } 1212 \text{ or } 1214 \dots (9)$$

$$\text{mod}(y_u, 2) = 0 \text{ の場合、VRAM } 1211 \text{ or } 1212 \dots (10)$$

$$\text{mod}(y_u, 2) = 1 \text{ の場合、VRAM } 1213 \text{ or } 1214 \dots (11)$$

#### 【0077】

ステップ S 1406において、読み出しアドレス生成部 125は、読み出しアドレスで指定される単位記憶領域に含まれる参照画素の数を判断する。カウンター  $u$  が奇数の場合において  $\text{mod}(x_u, 2) = 0$  のときは、読み出しアドレス生成部 125は、読み出しアドレス ( $x_r, y_r$ ) で指定される単位記憶領域に、画素  $P_u$  および  $P_{u+1}$  の 2 つの参照画素のデータが含まれると判断する。カウンター  $u$  が奇数の場合において  $\text{mod}(x_u, 2) = 1$  のときは、読み出しアドレス生成部 125は、読み出しアドレス ( $x_r, y_r$ ) で指定される単位記憶領域に、画素  $P_u$  および  $P_{u+1}$  の 2 つの参照画素のデータが含まれると判断する。

50

) = 1 のときは、読み出しアドレス生成部 125 は、読み出しアドレス ( $x_r, y_r$ ) で指定される単位記憶領域に、1つの参照画素(画素  $P_u$ )のデータが含まれると判断する(残り 1 画素のデータは、補正には用いられない)。読み出しアドレス ( $x_r, y_r$ ) で指定される単位記憶領域に含まれる参照画素の数が 2 つである場合 (S1406 : 2)、読み出しアドレス生成部 125 は、処理をステップ S1407 に移行する。読み出しアドレス ( $x_r, y_r$ ) で指定される単位記憶領域に含まれる参照画素の数が 1 つである場合 (S1406 : 1)、読み出しアドレス生成部 125 は、処理をステップ S1409 に移行する。

#### 【0078】

ステップ S1407において、読み出しアドレス生成部 125 は、VRAM121 に対しデータの読み出し要求を出力する。読み出し要求は、ステップ S1405 で特定された VRAM に対して出力される。また、読み出し要求は、読み出しアドレスおよび画素  $P_1 \sim P_4$  のうちそのアドレスにデータが記憶されている 2 つの画素の識別子を含む。10

#### 【0079】

ステップ S1408において、読み出しアドレス生成部 125 は、カウンター  $u$  を更新する。ここでは、 $u = u + 2$  としてカウンター  $u$  を更新する。

#### 【0080】

ステップ S1409において、読み出しアドレス生成部 125 は、VRAM121 に対しデータの読み出し要求を出力する。読み出し要求は、ステップ S1405 で特定された VRAM に対して出力される。また、読み出し要求は、読み出しアドレスおよび画素  $P_1 \sim P_4$  のうちそのアドレスにデータが記憶されている 1 つの画素の識別子を含む。20

#### 【0081】

ステップ S1410において、読み出しアドレス生成部 125 は、カウンター  $u$  を更新する。ここでは、 $u = u + 1$  としてカウンター  $u$  を更新する。

#### 【0082】

ステップ S1411において、読み出しアドレス生成部 125 は、画素  $P_u$  のデータがキャッシュ 1261 に記憶されている旨の情報を、読み出し IF126 に出力する。

#### 【0083】

ステップ S1412において、読み出しアドレス生成部 125 は、画素  $P_1 \sim P_4$  の全てについて処理が完了したか判断する。画素  $P_1 \sim P_4$  の全てについて処理が完了したと判断された場合 (S1412 : YES)、読み出しアドレス生成部 125 は、ステップ S104 の処理を終了する。画素  $P_1 \sim P_4$  のうち処理されていない画素があると判断された場合 (S1412 : NO)、読み出しアドレス生成部 125 は、処理をステップ S1403 に移行する。30

#### 【0084】

再び図 8 を参照する。ステップ S105において、読み出し IF126 は、VRAM121 からデータを取得する。ステップ S1407 または S1409 で読み出しアドレス生成部 125 から出力された読み出し要求は、アービタ-122 を介して VRAM121 に出力される。VRAM121 は、指定されたアドレスの記憶領域からデータを読み出し、アービタ-122 を介して読み出し IF126 に出力する。40

#### 【0085】

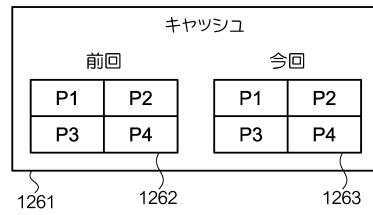

図 10 は、キャッシュ 1261 の構成を例示する図である。この例で、キャッシュ 1261 は、記憶領域 1262 および記憶領域 1263 を有する。記憶領域 1262 および記憶領域 1263 は、それぞれ、2 行 2 列の 4 画素分のデータを記憶する。記憶領域 1262 および記憶領域 1263 の一方には前回の補正に用いられたデータが、他方には今回の補正に用いられるデータが記憶される。ここでは説明を簡単にするため、記憶領域 1262 に前回のデータが、記憶領域 1263 に今回のデータが記憶される例を説明する。

#### 【0086】

読み出し IF126 は、取得したデータから参照画素のデータを抽出する。VRAM121 から出力されるデータには、そのデータに含まれる参照画素の識別子が付加されてい50

る。そのデータに参照画素  $P_1$  および  $P_2$  のデータが含まれることが示されている場合、読み出し IF 126 は、上位 24 ビットのデータを  $P_1$  のデータとして、下位 24 ビットを  $P_2$  のデータとして抽出する。そのデータに参照画素  $P_1$  のみのデータが含まれることが示されている場合、読み出し IF 126 は、下位 24 ビットのデータを  $P_1$  のデータとして抽出する。そのデータに参照画素  $P_2$  のみのデータが含まれることが示されている場合、読み出し IF 126 は、上位 24 ビットのデータを  $P_2$  のデータとして抽出する。そのデータに参照画素  $P_3$  および  $P_4$  のデータが含まれることが示されている場合、読み出し IF 126 は、上位 24 ビットのデータを  $P_3$  のデータとして、下位 24 ビットを  $P_4$  のデータとして抽出する。そのデータに参照画素  $P_3$  のみのデータが含まれることが示されている場合、読み出し IF 126 は、下位 24 ビットのデータを  $P_3$  のデータとして抽出する。そのデータに参照画素  $P_4$  のみのデータが含まれることが示されている場合、読み出し IF 126 は、上位 24 ビットのデータを  $P_4$  のデータとして抽出する。

10

#### 【0087】

読み出し IF 126 は、抽出した参照画素のデータを記憶領域 1263 に書き込む。

#### 【0088】

なお、キャッシュ 1261 に画素  $P_u$  のデータが記憶されていることが読み出しあドレス生成部 125 から通知された場合、読み出し IF 126 は、記憶領域 1262 から画素  $P_u$  のデータを読み出し、読み出したデータを記憶領域 1263 に書き込む。

#### 【0089】

図 9 のフローで参照画素  $P_1 \sim P_4$  について処理が完了すると、それに応じて、記憶領域 1263 には参照画素  $P_1 \sim P_4$  のデータが書き込まれる。読み出し IF 126 は、記憶領域 1263 に記憶されているデータを、補正部 127 に出力する。その後、読み出し IF 126 は、記憶領域 1263 に記憶されているデータを、記憶領域 1262 にコピーする。

20

#### 【0090】

ステップ S106において、補正部 127 は、式(2)を用いて画素  $P_c$  のデータを補正する。

#### 【0091】

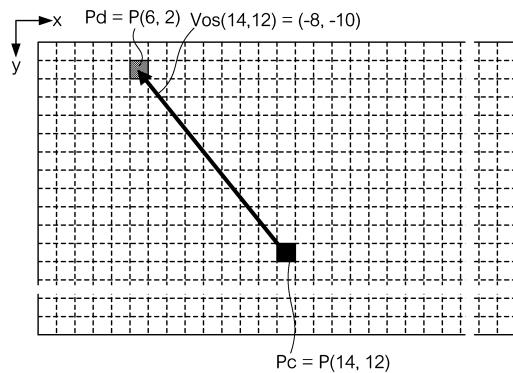

図 11 は、補正に用いられる画素を例示する図である。この例では、 $P_c = P(14, 12)$  であり、 $Vos(14, 12) = (-8, -10)$  である。式(4)から、

30

$P_d = (6, 2) \dots (12)$

である。式(2)とあわせて、

$$Dr(14, 12) = Do(6, 2) \dots (13)$$

が得られる。

#### 【0092】

再び図 8 を参照する。ステップ S107 において、映像出力部 128 は、補正部 127 により補正された画素  $P_c$  のデータを後段の回路（例えば光変調器 131 の駆動回路）に出力する。

#### 【0093】

ステップ S108 において、読み出しあドレス生成部 125 および補正部 127 は、 $\times$  カウンター  $C_x$  をインクリメントする。

40

#### 【0094】

ステップ S109 において、補正部 127 は、1 行分の処理が完了したか、すなわち、 $C_x = 801$  となったか判断する。まだ 1 行分の処理が完了していないと判断された場合 (S109: NO)、補正部 127 は、処理をステップ S104 に移行する。1 行分の処理が完了したと判断された場合 (S109: YES)、補正部 127 は、処理をステップ S110 に移行する。

#### 【0095】

ステップ S110 において、書き込み IF 124 は、ライトカウンター  $C_w$  で指定される行のデータを、VRAM 121 に書き込む。ライトカウンター  $C_w$  で指定される行のデ

50

ータは、V R A M 1 2 1において第 k w 行の記憶領域に書き込まれる。k w は次式(14)により計算される。

$$k w = C w \text{ (mod } k) \dots (14)$$

例えば、k = 2 4 1の場合においてC w = 1 ~ 2 4 1のときは、k w = C wである。C w = 2 4 3の場合、k w = 2である。

#### 【0096】

ステップS 1 1 1において、読み出しアドレス生成部1 2 5および書き込みI F 1 2 4は、カウンターC r およびC wをインクリメントする。

#### 【0097】

ステップS 1 1 2において、読み出しアドレス生成部1 2 5は、全ての行について処理が完了したか、すなわち、C r = 4 8 0となつたか判断する。まだ全ての行について処理が完了していないと判断された場合(S 1 1 2 : N O)、読み出しアドレス生成部1 2 5は、処理をステップS 1 0 3に移行する。全ての行について処理が完了したと判断された場合(S 1 1 2 : Y E S)、コントローラー1 2は、図8の処理を終了する。10

#### 【0098】

なおここでは1枚(1フレーム)の画像のみを処理する例を説明したが、動画を処理する場合、複数フレームの画像を連続して処理してもよい。例えば、第 i フレームについて処理をしている場合において、C w > rとなつたときは、ライトカウンターC wを初期化し、第(i + 1)フレームのデータをV R A M 1 2 1に書き込んでもよい。この場合において、C r > rとなつたときは、リードカウンターC rを初期化し、第(i + 1)フレームのデータの処理を開始する。20

#### 【0099】

以上で説明したように、本実施形態によれば、補正に用いられる画素を含む行を選択してラインバッファに記憶する構成と比較して、処理の負荷を低減することができる。また、リードカウンターとライトカウンターとは同じスピードで行送りされるので、リードがライトを追い越す(書き込みが終わる前の画像データを誤って読み出してしまう)ことはない。

#### 【0100】

また、本実施形態によれば、本発明を用いない構成(図1の例でコントローラー1 2を有さない構成)に対し、ホスト装置1 1と投写ユニット1 3(光変調器1 3 1)との間に本実施形態に係るコントローラー1 2を設ければよく、歪み補正に対応していないシステムに簡単に低成本で歪み補正の機能を導入することができる。30

#### 【0101】

##### 3 - 2 . 動作例

以下、より具体的な動作例を説明する。

#### 【0102】

##### 3 - 2 - 1 . データ読み出しの例

ここでは、V R A M 1 2 1 1 ~ 1 2 1 4からのデータの読み出しの例を説明する。

#### 【0103】

##### 3 - 2 - 1 - 1 . 動作例 1

図12は動作例1を示す図である。この例では、参照画素P<sub>1</sub> ~ P<sub>4</sub>が、(0, 0)、(1, 0)、(0, 1)、および(1, 1)である例を説明する。なおこの例では、キャッシュ1 2 6 1に参照画素のデータは記憶されていない。この場合、V R A M 1 2 1 1の単位記憶領域A(0, 0)およびV R A M 1 2 1 3の単位記憶領域A(0, 0)から読み出したデータを用いて補正が行われる。図において、読み出されるデータには丸印が付されている。40

#### 【0104】

##### 3 - 2 - 1 - 2 . 動作例 2

図13は動作例2を示す図である。この例では、参照画素P<sub>1</sub> ~ P<sub>4</sub>が、(1, 0)、(2, 0)、(1, 1)、および(2, 1)である例を説明する。なおこの例では、キャ50

ツシユ 1261 に参照画素のデータは記憶されていない。この場合、VRAM1211 の単位記憶領域 A (0, 0)、VRAM1212 の単位記憶領域 A (0, 0)、VRAM1213 の単位記憶領域 A (0, 0)、および VRAM1214 の単位記憶領域 A (0, 0) から読み出したデータを用いて補正が行われる。

#### 【0105】

##### 3 - 2 - 1 - 3 . 動作例 3

図 14 は動作例 3 を示す図である。この例では、参照画素 P<sub>1</sub> ~ P<sub>4</sub> が、(3, 1)、(4, 1)、(3, 2)、および (4, 2) である例を説明する。なおこの例では、キャッシュ 1261 に参照画素のデータは記憶されていない。この場合、VRAM1211 の単位記憶領域 A (1, 1)、VRAM1212 の単位記憶領域 A (0, 1)、VRAM1213 の単位記憶領域 A (1, 0)、および VRAM1214 の単位記憶領域 A (0, 0) から読み出したデータを用いて補正が行われる。

10

#### 【0106】

##### 3 - 2 - 1 - 4 . 動作例 4

図 15 は動作例 4 を示す図である。この例では、前回補正時の参照画素 P<sub>1</sub> ~ P<sub>4</sub> が、(0, 0)、(1, 0)、(0, 1)、および (1, 1) であり、かつ、今回補正時の参照画素 P<sub>1</sub> ~ P<sub>4</sub> が、(1, 0)、(2, 0)、(1, 1)、(2, 1) である。キャッシュ 1261 には、画素 (0, 0)、(1, 0)、(0, 1)、および (1, 1) のデータが記憶されている。この場合、VRAM1212 の単位記憶領域 A (0, 0) および VRAM1214 の単位記憶領域 A (0, 0) から読み出したデータ、並びにキャッシュ 1261 に記憶されているデータが用いられる。この場合、VRAM121 へ 2 回アクセスすれば、補正に用いられるデータを得ることができる。

20

#### 【0107】

オフセットベクトルは画素毎に定義されるが、隣り合う画素でオフセットベクトルが大きく異なることは少ない。すなわち、今回補正時の参照画素は、前回補正時の参照画素から 1 画素分だけ移動しているケースがほとんどである。したがって、キャッシュ 1261 を用いることにより、VRAM121 へのアクセス回数を大幅に低減することができる。

#### 【0108】

##### 3 - 2 - 1 - 5 . 動作例 5

この例では、参照画素 P<sub>1</sub> ~ P<sub>4</sub> が、(0, -1)、(1, -1)、(0, 0)、および (1, 0) である例を説明する。すなわち、参照画素 P<sub>1</sub> および P<sub>2</sub> は、元の画像データ（以下「元データ」という）の範囲外の画素である。元データの範囲外の画素のデータとしては、所定値のデータが用いられる。所定値のデータは、読み出し IF126 内のレジスター（図示略）に記憶されている。参照画素が元データの範囲外であった場合、読み出しアドレス生成部 125 は、その旨を読み出し IF126 に通知する。

30

#### 【0109】

##### 3 - 2 - 1 - 6 . 動作例 6

この例では、参照画素 P<sub>1</sub> ~ P<sub>4</sub> が、(0, -2)、(1, -2)、(0, -1)、および (1, -1) である例を説明する。すなわち、すべての参照画素が元データの範囲外の画素である。すべての参照画素が元データの範囲外であった場合、読み出しアドレス生成部 125 は、その旨を読み出し補正部 127 に通知する。この場合、補正部 127 は、補正（補間演算）を行わず、所定値をそのまま処理対象画素のデータとして出力する。

40

#### 【0110】

なお、動作例 4 ~ 6 のように、キャッシュ 1261 またはレジスターからデータを読み出している期間はアービタ 122 から VRAM121 にアクセスしていないので、他の装置（例えばホスト装置 11）から VRAM121 にアクセスすることができる。

#### 【0111】

##### 3 - 2 - 2 . VRAM121 へのデータ書き込み / 読み出しの例

ここでは、VRAM121 に対するデータの書き込みおよび読み出しの例を説明する。ここでは説明の便宜上、VRAM1211 ~ 1214 を区別せず、単一の VRAM121

50

として説明する。

**【0112】**

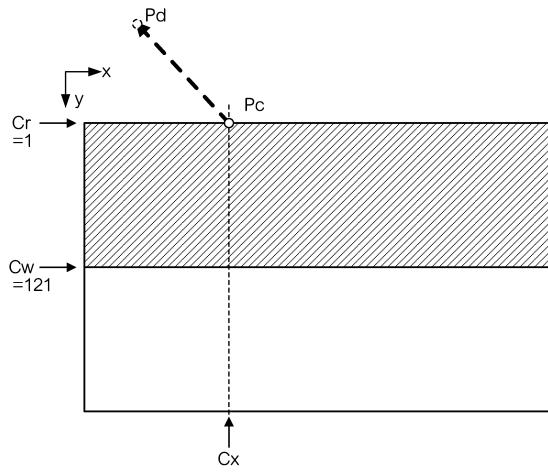

図16は、 $C_r = 1$ および $C_w = 121$ の状態（ステップS107）を示す図である。図は、VRAM121の状態を示している。ハッチングされた部分は、第1～120行のデータが記憶されていることを示している。白抜きの部分は、データが記憶されていない（ヌル値が記憶されている）ことを示している。

**【0113】**

この例で、オフセットベクトル $V_{os}(P_c)$ のx成分およびy成分はともに負である。すなわち、参照画素は元データにおいて存在しない画素である。この場合、補正部127は、補正後のデータを所定の値（例えばヌル値または黒に相当する階調）にする。図16では便宜的に、 $V_{os}$ および $P_d$ を破線で示し、元データにおいて存在しない画素を参照していることを示している。10

**【0114】**

図17は、 $C_r = 120$ および $C_w = 241$ の状態（ステップS107）を示す図である。このとき、VRAM121の第1～241行の記憶領域には、画像の第1～241行のデータが記憶されている。

**【0115】**

図18は、 $C_r = 200$ および $C_w = 321$ の状態（ステップS107）を示す図である。このとき、VRAM121の第1～80行の記憶領域には、画像の第242～321行のデータが記憶されている。VRAM121の第81～241行の記憶領域には、画像の第81～241行のデータが記憶されている。この例で、 $P_c = (300, 200)$ 、 $V_{os}(P_c) = (20, 100)$ である。これらを式(4)に代入して20

$$P_d = (320, 300) \dots (15)$$

が得られる。式(5)から

$$k_d = 59 \dots (16)$$

であるので、参照画素 $P_u$ のデータは、VRAM121の第59行の記憶領域に記憶されている。

**【0116】**

VRAM121においては、リードカウンターの進行方向に対し正方向および負方向の双方において、オフセット最大値分の行数のデータが記憶されているので、補正に用いるデータを読み出すことができる。30

**【0117】**

#### 4. 変形例

本発明は上述の実施形態に限定されるものではなく、種々の変形実施が可能である。以下、変形例をいくつか説明する。以下の変形例のうち2つ以上のものが組み合わせて用いられてもよい。

**【0118】**

##### 4-1. 変形例 1

VRAM121に含まれるフレームバッファーの数は4つに限定されない。例えば、VRAM121は、2つのフレームバッファーを有していてもよい。40

**【0119】**

図19は、2つのフレームバッファー（VRAM1211およびVRAM1212）を用いる場合の記憶領域の割り当てを例示する図である。VRAM1211の単位記憶領域A(s, t)には、画素 $P(2s, 2t)$ および画素 $P(2s+1, 2t)$ のデータが記憶される。VRAM1212の単位記憶領域A(s, t)には、画素 $P(2s, 2t+1)$ および画素 $P(2s+1, 2t+1)$ のデータが記憶される。

**【0120】**

この場合、参照画素 $P_1 \sim P_4$ が例えば、(1, 0)、(2, 0)、(1, 1)、および(2, 1)であった場合、单一のフレームバッファーに順次2回アクセスする必要がある。すなわち、データの読み出しに2クロックを要する。しかし、フレームバッファーの50

分割数が少なくなるため、回路規模をより縮小できる。

**【0121】**

また、VRAM121は複数のフレームバッファーを含まず、単一のフレームバッファーとして機能してもよい。

**【0122】**

4-2. 变形例2

補正に用いられる参照画素の数は4つに限定されない。例えば、オフセットベクトルが指す位置 $P_d$ の周辺 $m$ 行 $n$ 列の( $m \times n$ )個の画素が参照画素として用いられてもよい。例えば、オフセットベクトルが指す位置 $P_d$ の周辺4行4列の16個の画素が参照画素として用いられてもよい。

10

**【0123】**

4-3. 变形例3

VRAM121の記憶容量は、 $k$ 行分に限定されない。1フレームの全画素分、すなわち $r$ 行分の記憶領域を有していてもよい。この場合、VRAM121の容量は大きくなるが、リードカウンターおよびライトカウンターによる読み出しおよび書き込みの制御は不要になる。

**【0124】**

4-4. 变形例4

オフセットベクトルが指す位置 $P_d$ が、パッキングされていない2つの画素の間にに入った場合、パッキングされた2つの画素の間に位置 $P_d$ をずらす補正が行われてもよい。この補正がなければVRAM121に4回のアクセスが必要であるが、この補正をすればVRAM121へのアクセスは2回で済む。

20

**【0125】**

図20は、変形例4に係る位置 $P_d$ の補正を例示する図である。点Xが補正前の位置 $P_d$ を、点Yが補正後の位置 $P_d$ を示している。

**【0126】**

また、図19の例において、位置 $P_d$ が、パッキングされていない2つの画素の間にに入った場合、パッキングされた2つの画素の間に位置 $P_d$ をずらす補正が行われてもよい。この補正をすれば、1つのフレームバッファーへのアクセスは1回で済むので1クロックでデータを読み出すことができる。

30

**【0127】**

4-5. 变形例5

読み出しIF126はキャッシュ1261を有していないなくてもよい。

**【0128】**

4-6. 变形例6

オフセットベクトル $V_{os}$ は、理論的には全ての画素 $P(x, y)$ について定義することが可能であるが全ての画素 $P(x, y)$ についてオフセットベクトルを記憶すると多くのメモリー容量が必要になる場合には、記憶しておくオフセットベクトルを間引いてよい。例えば、行方向および列方向ともに2画素毎にオフセットベクトルをオフセットテーブル129に記憶しておくと、3行3列の9個の画素のうち4隅の画素のみオフセットベクトルが記憶されていることになる。このとき、オフセットベクトルが記憶されていない画素に関しては、近接する、オフセットベクトルが記憶されている画素のオフセットベクトルを用いた補間により、その画素のオフセットベクトルを算出する。

40

**【0129】**

例えば、 $V_{os}(1, 1) = (p_1, q_1)$ および $V_{os}(1, 3) = (p_2, q_2)$ がオフセットテーブル129に記憶されており、 $V_{os}(1, 2)$ がオフセットテーブル129に記憶されていないときは、

$$\begin{aligned} V_{os}(1, 2) &= \{V_{os}(1, 1) + V_{os}(1, 3)\} / 2 \\ &= [\{(p_1 + p_2) / 2\}, \{(q_1 + q_2) / 2\}] \dots (17) \end{aligned}$$

)

50

により V o s ( 1 , 2 ) が算出される。

**【 0 1 3 0 】**

4 - 7 . 变形例 7

V R A M 1 2 1 の記憶容量は、実施形態で説明したものに限定されない。例えば、オフセット最大値がリードカウンターの進行方向に対して正方向および負方向の双方について個別に設定されていた場合、正方向のオフセット最大値、負方向のオフセット最大値、および処理対象画素の記憶領域を加算した値に相当する行数の記憶領域を有していてもよい。具体的には、正方向のオフセット最大値  $O^+_{\max} = 120$  、負方向のオフセット最大値  $O^-_{\max} = 80$  、処理対象の画素数が 1 の場合、V R A M 1 2 1 は、 $201 (= 120 + 80 + 1)$  行分の記憶領域を有していればよい。このとき、ライトカウンター C w の値は、次式 ( 1 8 ) のように、リードカウンター C r に対して、負方向のオフセット最大値分ずらしておけばよい。

10

$$C_w = C_r + O^-_{\max} \dots ( 1 8 )$$

**【 0 1 3 1 】**

4 - 8 . 他の変形例

表示装置 1 は H U D に限定されない。表示装置 1 は、いわゆる通常のプロジェクターであってもよい。この場合において、プロジェクターのキーストーン補正に本発明が適用されてもよい。特に、いわゆるピコプロジェクターのような小型のプロジェクターにおいて有効である。

**【 0 1 3 2 】**

20

表示装置 1 および表示装置 1 の各部の構成は、図 1 および図 2 で例示したものに限定されない。実施形態では、ハードウェア（コントローラー 1 2 ）が図 8 のフローを実行する例を説明したが、ホスト装置 1 1 の C P U 1 1 1 が、プログラムに従って図 8 のフローを実行してもよい。この場合、コントローラー 1 2 は無くてもよい。また、実施形態においてはリードカウンターおよびライトカウンターが読み出しアドレス生成部 1 2 5 および書き込み I F 1 2 4 のレジスターに記憶される例を説明したが、これらのカウンターは V R A M 1 2 1 等、他の記憶装置に記憶されてもよい。

**【 0 1 3 3 】**

C P U 1 1 1 が実行するプログラムは、磁気記録媒体（磁気テープ、磁気ディスク（H D D 、 F D (Flexible Disk) ) など）、光記録媒体（光ディスク（C D (Compact Disk) ）、 D V D (Digital Versatile Disk) ) など）、光磁気記録媒体、半導体メモリ（フラッシュ R O M など）などのコンピューター読取り可能な記録媒体に記憶した状態で提供されてもよい。また、このプログラムは、インターネットのようなネットワーク経由でダウンロードされてもよい。

30

**【 0 1 3 4 】**

本発明は、表示装置以外の電子機器、例えば撮像装置に適用されてもよい。例えば、デジタルスチルカメラ、デジタルビデオカメラ、ドライブレコーダーにおける補正に、本発明が適用されてもよい。

**【 符号の説明 】**

**【 0 1 3 5 】**

40

1 ... 表示装置、 1 1 ... ホスト装置、 1 1 1 ... C P U 、 1 1 2 ... R O M 、 1 1 3 ... R A M 、

1 2 ... コントローラー、 1 2 1 ... V R A M 、 1 2 1 1 ... V R A M 、 1 2 1 2 ... V R A M 、

1 2 1 3 ... V R A M 、 1 2 1 4 ... V R A M 、 1 2 2 ... アービター、 1 2 3 ... 映像入力部、

1 2 4 ... 書き込み I F 、 1 2 5 ... 読み出しアドレス生成部、 1 2 6 ... 読み出し I F 、 1 2

6 1 ... キャッシュ、 1 2 7 ... 補正部、 1 2 8 ... 映像出力部、 1 2 9 ... オフセットテーブル

、 1 3 ... 投写ユニット、 1 3 1 ... 光変調器、 1 4 ... 記憶部、 1 5 ... I F 部、 1 6 ... 操作パネル、

1 8 1 ... 表示領域、 1 8 2 ... 長方形、 1 8 2 1 ~ 1 8 2 4 ... 頂点、 1 8 3 ... 図形、

1 8 3 1 ~ 1 8 3 4 ... 点、 1 8 4 ... 図形、 1 8 4 1 ~ 1 8 4 4 ... 点、 1 8 5 ... 図形、 1 8

5 1 ~ 1 8 5 4 ... 点

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

VRAM1211

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (0, 0) (1, 0)     | (4, 0) (5, 0)     | ... | (796, 0) (797, 0)     |

| (0, 2) (1, 2)     | (4, 2) (5, 2)     |     |                       |

|                   |                   |     |                       |

| (0, 478) (1, 478) | (4, 478) (5, 478) |     | (796, 478) (797, 478) |

VRAM1212

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (2, 0) (3, 0)     | (6, 0) (7, 0)     | ... | (798, 0) (799, 0)     |

| (2, 2) (3, 2)     | (6, 2) (7, 2)     |     |                       |

|                   |                   |     |                       |

| (2, 478) (3, 478) | (6, 478) (7, 478) |     | (798, 478) (799, 478) |

VRAM1213

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (0, 1) (1, 1)     | (4, 1) (5, 1)     | ... | (796, 1) (797, 1)     |

| (0, 3) (1, 3)     | (4, 3) (5, 3)     |     |                       |

|                   |                   |     |                       |

| (0, 479) (1, 479) | (4, 479) (5, 479) |     | (796, 479) (797, 479) |

VRAM1214

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (2, 1) (3, 1)     | (6, 1) (7, 1)     | ... | (798, 1) (799, 1)     |

| (2, 3) (3, 3)     | (6, 3) (7, 3)     |     |                       |

|                   |                   |     |                       |

| (2, 479) (3, 479) | (6, 479) (7, 479) |     | (798, 479) (799, 479) |

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

| VRAM1211          |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (0, 0) (1, 0)     | (4, 0) (5, 0)     | ... | (796, 0) (797, 0)     |

| (0, 2) (1, 2)     | (4, 2) (5, 2)     |     |                       |

| (0, 478) (1, 478) | (4, 478) (5, 478) |     | (796, 478) (797, 478) |

| VRAM1212          |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (2, 0) (3, 0)     | (6, 0) (7, 0)     | ... | (798, 0) (799, 0)     |

| (2, 2) (3, 2)     | (6, 2) (7, 2)     |     |                       |

| (2, 478) (3, 478) | (6, 478) (7, 478) |     | (798, 478) (799, 478) |

| VRAM1213          |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (0, 1) (1, 1)     | (4, 1) (5, 1)     | ... | (796, 1) (797, 1)     |

| (0, 3) (1, 3)     | (4, 3) (5, 3)     |     |                       |

| (0, 479) (1, 479) | (4, 479) (5, 479) |     | (796, 479) (797, 479) |

| VRAM1214          |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (2, 1) (3, 1)     | (6, 1) (7, 1)     | ... | (798, 1) (799, 1)     |

| (2, 3) (3, 3)     | (6, 3) (7, 3)     |     |                       |

| (2, 479) (3, 479) | (6, 479) (7, 479) |     | (798, 479) (799, 479) |

【図13】

| VRAM1211          |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (0, 0) (1, 0)     | (4, 0) (5, 0)     | ... | (796, 0) (797, 0)     |

| (0, 2) (1, 2)     | (4, 2) (5, 2)     |     |                       |

| (0, 478) (1, 478) | (4, 478) (5, 478) |     | (796, 478) (797, 478) |

| VRAM1212          |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (2, 0) (3, 0)     | (6, 0) (7, 0)     | ... | (798, 0) (799, 0)     |

| (2, 2) (3, 2)     | (6, 2) (7, 2)     |     |                       |

| (2, 478) (3, 478) | (6, 478) (7, 478) |     | (798, 478) (799, 478) |

| VRAM1213          |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (0, 1) (1, 1)     | (4, 1) (5, 1)     | ... | (796, 1) (797, 1)     |

| (0, 3) (1, 3)     | (4, 3) (5, 3)     |     |                       |

| (0, 479) (1, 479) | (4, 479) (5, 479) |     | (796, 479) (797, 479) |

| VRAM1214          |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (2, 1) (3, 1)     | (6, 1) (7, 1)     | ... | (798, 1) (799, 1)     |

| (2, 3) (3, 3)     | (6, 3) (7, 3)     |     |                       |

| (2, 479) (3, 479) | (6, 479) (7, 479) |     | (798, 479) (799, 479) |

【図14】

VRAM1211

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (0, 0) (1, 0)     | (4, 0) (5, 0)     | ... | (796, 0) (797, 0)     |

| (0, 2) (1, 2)     | (4, 2) (5, 2)     |     |                       |

| (0, 478) (1, 478) | (4, 478) (5, 478) |     | (796, 478) (797, 478) |

VRAM1212

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (2, 0) (3, 0)     | (6, 0) (7, 0)     | ... | (798, 0) (799, 0)     |

| (2, 2) (3, 2)     | (6, 2) (7, 2)     |     |                       |

| (2, 478) (3, 478) | (6, 478) (7, 478) |     | (798, 478) (799, 478) |

VRAM1213

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (0, 1) (1, 1)     | (4, 1) (5, 1)     | ... | (796, 1) (797, 1)     |

| (0, 3) (1, 3)     | (4, 3) (5, 3)     |     |                       |

| (0, 479) (1, 479) | (4, 479) (5, 479) |     | (796, 479) (797, 479) |

VRAM1214

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (2, 1) (3, 1)     | (6, 1) (7, 1)     | ... | (798, 1) (799, 1)     |

| (2, 3) (3, 3)     | (6, 3) (7, 3)     |     |                       |

| (2, 479) (3, 479) | (6, 479) (7, 479) |     | (798, 479) (799, 479) |

【図15】

VRAM1211

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (0, 0) (1, 0)     | (4, 0) (5, 0)     | ... | (796, 0) (797, 0)     |

| (0, 2) (1, 2)     | (4, 2) (5, 2)     |     |                       |

| (0, 478) (1, 478) | (4, 478) (5, 478) |     | (796, 478) (797, 478) |

VRAM1212

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (2, 0) (3, 0)     | (6, 0) (7, 0)     | ... | (798, 0) (799, 0)     |

| (2, 2) (3, 2)     | (6, 2) (7, 2)     |     |                       |

| (2, 478) (3, 478) | (6, 478) (7, 478) |     | (798, 478) (799, 478) |

VRAM1213

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (0, 1) (1, 1)     | (4, 1) (5, 1)     | ... | (796, 1) (797, 1)     |

| (0, 3) (1, 3)     | (4, 3) (5, 3)     |     |                       |

| (0, 479) (1, 479) | (4, 479) (5, 479) |     | (796, 479) (797, 479) |

VRAM1214

|                   |                   |     |                       |

|-------------------|-------------------|-----|-----------------------|

| (2, 1) (3, 1)     | (6, 1) (7, 1)     | ... | (798, 1) (799, 1)     |

| (2, 3) (3, 3)     | (6, 3) (7, 3)     |     |                       |

| (2, 479) (3, 479) | (6, 479) (7, 479) |     | (798, 479) (799, 479) |

キヤツシユ1261

|        |        |

|--------|--------|

| (0, 0) | (1, 0) |

| (0, 1) | (1, 1) |

【図16】

【図18】

【図17】

【図19】

【図20】

① : VRAM1211

② : VRAM1212

---

フロントページの続き

(56)参考文献 特開2011-244220(JP,A)

特開2013-243616(JP,A)

特開2004-048368(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 0 6 T      1 / 0 0 - 1 / 4 0

G 0 6 T      1 / 6 0

G 0 6 T      3 / 0 0 - 5 / 5 0

G 0 6 T      9 / 0 0 - 9 / 4 0

H 0 4 N      5 / 6 6 - 5 / 7 4