(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4573987号

(P4573987)

(45) 発行日 平成22年11月4日(2010.11.4)

(24) 登録日 平成22年8月27日(2010.8.27)

(51) Int.Cl.

F 1

H05B 41/32

(2006.01)

H05B 41/32

J

G03B 15/03

(2006.01)

G03B 15/03

X

G03B 15/05

(2006.01)

G03B 15/05

請求項の数 3 (全 8 頁)

(21) 出願番号

特願2000-317883 (P2000-317883)

(22) 出願日

平成12年10月18日 (2000.10.18)

(65) 公開番号

特開2002-124394 (P2002-124394A)

(43) 公開日

平成14年4月26日 (2002.4.26)

審査請求日

平成19年10月1日 (2007.10.1)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 大塚 元太

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 土屋 正志

最終頁に続く

(54) 【発明の名称】 閃光装置

## (57) 【特許請求の範囲】

## 【請求項 1】

放電管の光強度を検出する光強度検出手段と、放電管の発光を制御する発光制御回路と、光強度検出手段の出力値が第1の値より、大きくなると発光を停止させる信号を発光制御回路へ出力し、前記第1の値よりも小さな第2の値より、小さくなると発光を開始させる信号を発光制御回路へ出力する、フラット発光制御回路を備えたフラット発光が可能な閃光装置において、

フラット発光開始から所定の時間の間ににおける前記第1の値と前記第2の値の差を、その後における前記第1の値と前記第2の値の差よりも大きくすることを特徴とする閃光装置。

## 【請求項 2】

第1の値とは、フラット発光時の波高値であり、第2の値とは、フラット発光時の発光のリップル幅を決めるヒステリシス値であることを特徴とする請求項1に記載の閃光装置。

## 【請求項 3】

前記第2の値のみが可変であることを特徴とする請求項1又は2に記載の閃光装置。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、フラット発光が可能な閃光装置の改良に関するものである。

## 【0002】

## 【従来の技術】

従来より、フォーカルプレーンシャッターがスリット露光する場合（高速シャッタ時）でもほぼ均一な発光強度で発光を持続するフラット発光が可能な閃光装置は知られている。又、撮影に先立ち、予備発光をおこない、その後その測光結果に基づき、本発光を行う閃光装置においての予備発光においても、予備発光の測光精度等の関係でフラット発光を用いる装置は、特開昭54-128734号公報に開示されている。この種の閃光装置においては、フラット発光の光強度を発光開始から終了まで一定に保つ必要があり、発光開始から終了まである一定の値と光強度検出手段より出力される値を比較し、発光制御を行っていた。又、予備発光時の光強度は、省エネの観点からも小さい方が望まれている。

10

## 【0003】

しかしながら、前記公知例における発光制御回路では、発光強度が少ない状態においても、放電管の放電電流をほぼ所定値に保つことは可能ではあるが、発光開始初期段階において閃光放電管内の放電アークが管全体に広がらず発光周波数が高くなり、発光制御回路の素子の破壊を招いたり、発光強度が不安定になりやすいという課題はあった。

## 【0004】

この課題を解決する為に、特開平9-80594号公報においては、発光開始より所定時間とそれ以降の時間で発光強度を変える手段を用いている。

## 【0005】

又、特開平10-48715号公報においては、発光開始より所定時間とそれ以降の時間で発光検出手段の応答性を変える手段を用いている。

20

## 【0006】

## 【発明が解決しようとする課題】

しかしながら、特開平9-80594号公報においては、発光強度を可変にさせる為、予備発光時の発光において、光強度の違いが生じ発光開始より測光を行うと特定の測光出力を得る事が難しい。

## 【0007】

又、特開平10-48715号公報においては、発光検出部に容量を付加させることで、発光検出手段の応答性を可変させる事を行っているが、ある特定の応答性の変化のみ可能であり、発光強度が異なった場合（波高値が変わった場合）に対し適切な応答遅れを施す事は難しく、又、発光開始後の複数区間において応答遅れ手段が必要で有る場合には、付加させる回路が複数必要となりコストアップの要因となる。

30

## 【0008】

## 【課題を解決するための手段】

請求項1に記載の発明は、放電管の光強度を検出する光強度検出手段と、放電管の発光を制御する発光制御回路と、光強度検出手段の出力値が第1の値より、大きくなると発光を停止させる信号を発光制御回路へ出力し、前記第1の値よりも小さな第2の値より、小さくなると発光を開始させる信号を発光制御回路へ出力する、フラット発光制御回路を備えたフラット発光可能な閃光装置において、フラット発光開始から所定の時間の間ににおける前記第1の値と前記第2の値の差を、その後における前記第1の値と前記第2の値の差よりも大きくする閃光装置を提供するものである。

40

## 【0012】

## 【発明の実施の形態】

以下、図面に基づいて、本発明の実施形態について詳細を説明する。

ここでは、発光開始後に所定時間とそれ以降でリップル幅を決定する波高値設定回路とヒステリシス設定回路を変える時のフラット発光制御についての実施形態について説明する。

## 【0013】

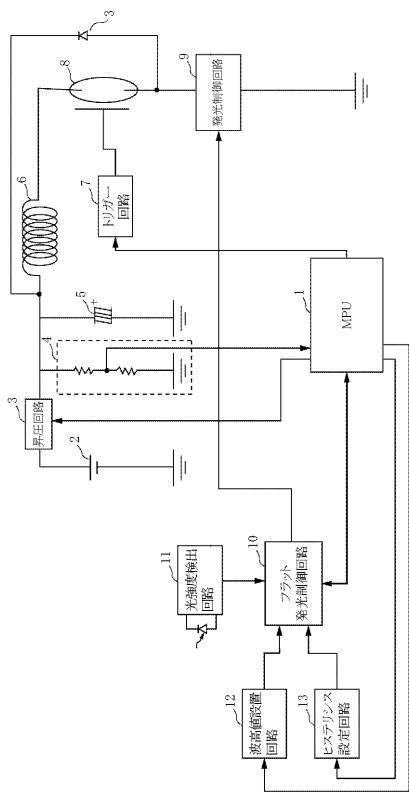

図1は本発明を実現するための、閃光装置における全体のシステム構成を示す。

1は充電、発光等の各モジュールを制御する制御回路としてのMPUである。5は発光の

50

為の電気エネルギーを蓄積する為のメインコンデンサであり、このメインコンデンサ 5 に対しバッテリー 2 より充電を行う為の昇圧回路 3 がバッテリー 1 とメインコンデンサ 5 間に接続されている。又、充電を所定の電圧で終了させる為に、MPU 1 は充電電圧をモニタするモニタ回路 4 の出力値が所定の値に達すると昇圧回路 3 のイネーブル信号を OFFさせ、充電を終了させる。更に、8 はメインコンデンサの電気エネルギーを光りに変換する放電管であり、7 は放電管を励起状態にさせるトリガー回路、9 は MPU の信号とフラット発光制御回路からの出力をもとに放電管の発光制御をおこなう発光制御回路であり、IGBT 等の高電流制御が可能なトランジスタと、そのゲートに対するバッファ回路等で構成されている。また 6 はメインコンデンサと放電管の陽極間に接続されるコイルであり、30 はアノード側を陰極に、カソード側をメインコンデンサの陽極側に接続したダイオードである。

10

#### 【 0 0 1 4 】

また、11 は光強度検出回路であり、放電管 8 が放つ光を光電変化しその光強度を電圧値として出力する回路である。又、12 は波高値設定回路であり、MPU から出力されるデジタル値を所定の電圧として出力する D/A コンバータ回路であり、この回路ではフラット発光時の波高値を決定する。また、13 はヒステリシス設定回路であり、MPU から出力されるデジタル値を所定の電圧として出力する D/A コンバータ回路であり、この回路ではフラット発光時のリップル幅、つまりヒステリシス幅を決定する。10 はフラット発光制御回路であり、波高値設定回路からの出力値とヒステリシス設定回路からの出力値の 2 つの値に対して、光強度検出回路からの出力値を比較し、それに基づいた信号を発光制御回路に出力する回路である。又、この制御のイネーブル信号として MPU 1 に接続されている。

20

#### 【 0 0 1 5 】

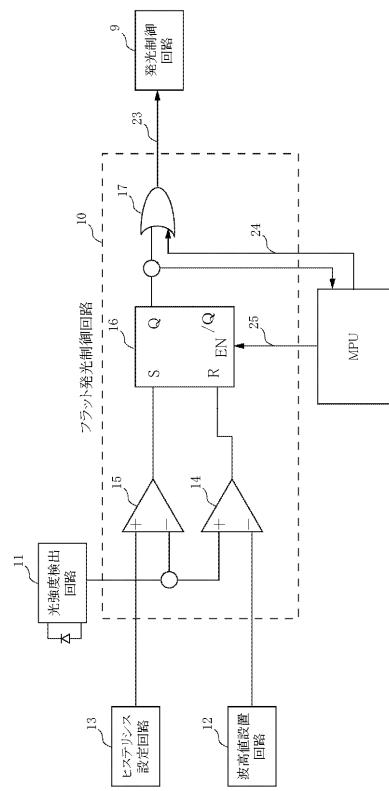

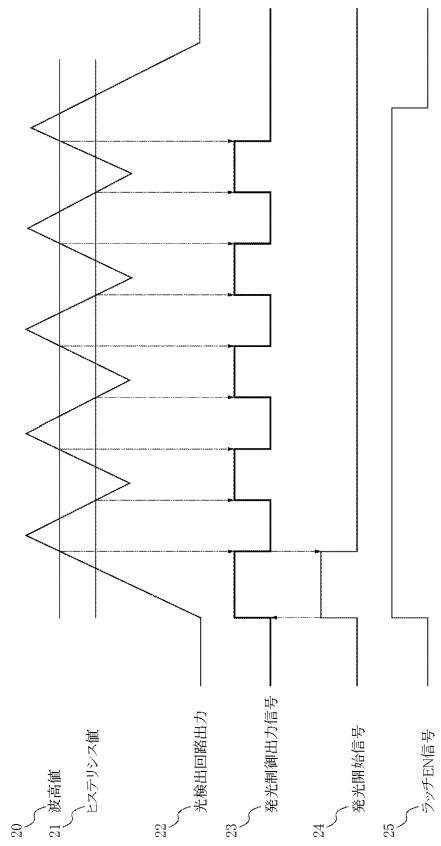

次に、フラット発光時の動作原理について、図 1、図 2 (図1のフラット発光制御回路の構成を示す)、図 3 (動作説明図) を用いて説明を行う。

発光開始においては、MPU 1 からの信号により、トリガー回路を駆動させ放電管を励起状態にさせると共にフラット発光制御回路の OR 回路 17、ラッチ回路 16 に発光開始信号 24、ラッチ EN 信号 25 として、high レベル信号、を出力させ、フラット発光制御回路は、発光制御回路に対し high レベル信号を出力することで、発光開始を行う。発光開始後、つぎに、光検出回路の出力値が波高値設定回路に設定された値 20 を越えると、コンパレータ 14 が high レベル信号を出力し、ラッチ 16 はリセットされ low レベル信号を出力する。この最初のラッチ回路の low レベル信号により、発光開始信号 24 は low レベル信号を出力しつづける様に MPU は発光開始信号 24 の制御を行う。この結果、フラット発光制御回路は、発光制御回路 9 に low レベル信号を出力し発光を停止させる。発光停止状態となると、コイル 6 に溜まったエネルギーが放電管 ダイオードの経路で放電されるので、発光強度は、発光制御回路が発光停止状態になってから少し遅れて下がり始める。そして、発光の強度が下がり光検出回路の出力値が、波高値 20 を下回るとコンパレータ 14 が動作しラッチ 16 のリセットを解除する。更に、光強度が下がり光検出回路の出力値が、ヒステリシス設定回路で設定したヒステリシス値を下回るとコンパレータ 15 が動作し、ラッチ 16 をセットし OR 回路に high レベル信号出力し、発光制御回路を動作させ、再び発光を開始する。発光開始状態となると、メインコンデンサのエネルギーがコイル 放電管 発光制御回路の経路で放電される為、発光強度は、発光制御回路が発光開始状態になってから少し遅れて立ち上がり始める。以上の様にして、フラット発光制御の動作が繰り返され、この動作は、MPU よりラッチ 16 の EN 端子に low レベル信号を出力するまで動作し続ける。

30

#### 【 0 0 1 6 】

次に、発光開始中にフラット発光のリップル幅を変更を行う制御について述べる。

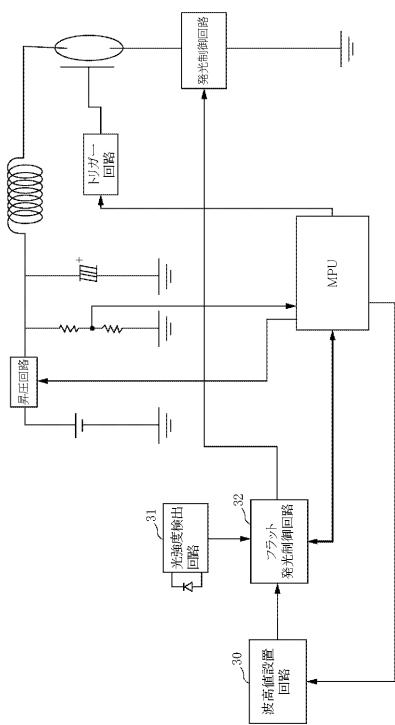

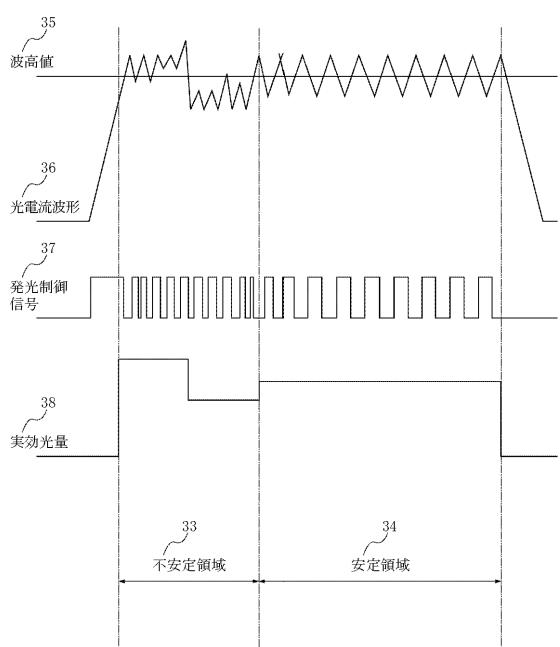

図 5 は、図 4 の従来回路において、フラット発光においては波高値を決める回路のみを設置した場合の例である。この様に波高値設定回路 30 によるある 1 つの基準でのみ放電管に対しフラット発光の制御を行うと、光検出回路 31 による光電流波形 36 に示すように

40

50

、発光開始初期段階において閃光放電管内の放電アークが管全体に広がらず、不安定領域33の様に、発光周波数が高くなる結果、発光制御回路へ高周波的なドライブ信号を出力することになり、発光制御回路の素子を破壊させる等の問題が起こる。又、光電流波形30が安定しない為、38に示すように実際の実効的な光量が、不安定領域33においては、フラットでなくなるという問題が生じる。

【0017】

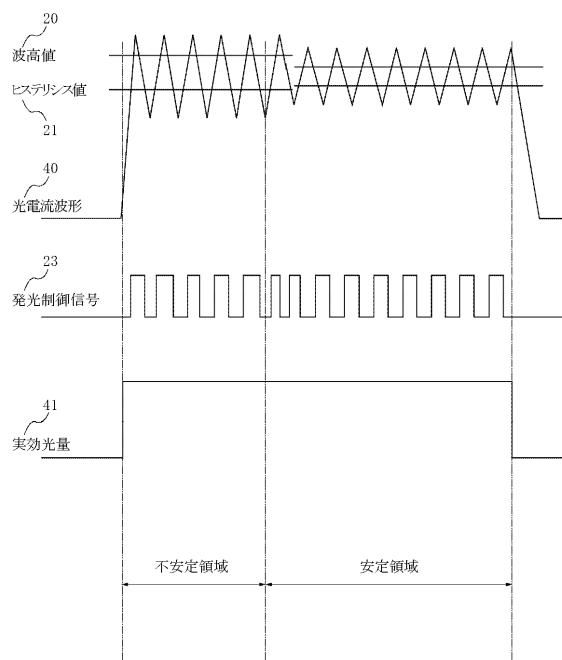

図6は、発光開始後所定時間の放電管の不安定領域のみ、波高値設定回路、ヒストリシス設定回路の値を安定領域の値と変化させて制御を行う本発明の実施形態である。この実施形態においては、発光開始後所定時間の不安定領域のみ、波高値20、ヒストリシス値21間の値を安定領域のそれよりも大きくなるように、且つ、そのセンター値を安定領域における実効的な光量レベルとするように、波高値20、ヒストリシス値21を図1の波高値設置回路12及びヒストリシス設定回路13により設定しフラット発光制御を行う。この様な制御を行うことで、光検出回路11における光電流波形40に示すように、発光開始後の放電管の不安定領域においては低周波でありリップル幅が幾分増える光波形を発生させることになるが、発光周波数を上げ発光制御回路の素子破壊を招く事無く、また発光開始から終了まで、41に示すように実効的な光量においてフラットな光波形を出力する事が可能となる。

10

【0018】

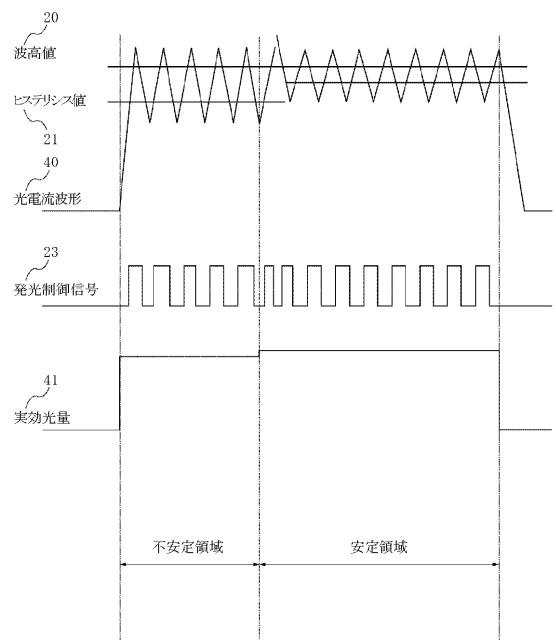

図7は、発光開始後所定時間の放電管の不安定領域のみ、ヒストリシス設定回路の値のみを安定領域の値と変化させて制御を行う本発明の他の実施形態である。この実施形態においては、発光開始後所定時間の不安定領域のみ、ヒストリシス値21の値を安定領域のそれよりも小さくなるように図1のヒストリシス設定回路13により設定し、フラット発光制御を行う。この様な制御を行うことで、光電流波形40に示すように、発光開始後の放電管の不安定領域においては低周波となりリップル幅が幾分増える光波形を発生させることになりが、発光周波数を上げ発光制御回路の素子破壊を招く事が無くなる。また、41に示すように発光開始後所定時間の不安定領域の実効的な光量レベルは安定領域に対して多少変わるが、前述の図6の実施形態の様に、発光途中で波高値、ヒストリシス値の2つのD/Aコンバータの出力値を変化させることなく、1つのD/Aコンバータの出力変化のみで行え、発光途中以降の安定領域のみの光を使用するシステムにおいては、必要充分な手段と言える。

20

【0019】

【発明の効果】

以上説明したように、本発明によれば、フラット発光を制御する時の波高値設定回路の他にヒストリシス設定回路を設け、その波高値とヒストリシス値の差をフラット発光が不安定になりやすい領域において、安定領域よりも大きくなるように設定する事で、フラット発光開始から発光が不安定になり易い領域においても、安定した発光を行う事が可能になり、発光開始から終了まで、実効的な光量がフラットな光波形を出力させる事が可能となる。また、発光周波数が安定領域以上にあがることなく、高い発光周波数により、発光制御回路の素子を破壊する懸念が無くなる。

30

【図面の簡単な説明】

40

【図1】本発明における全体のシステム構成。

【図2】本発明におけるフラット発光制御回路。

【図3】本発明におけるフラット発光制御時のタイミングチャート。

【図4】従来における全体のシステム構成。

【図5】従来におけるフラット発光時の光出力波形図。

【図6】本発明の実施形態におけるフラット発光時の光出力波形図。

【図7】本発明の他の実施形態におけるフラット発光時の光出力波形図。

【符号の説明】

1 MPU

8 放電管

50

## 9 発光制御回路

- 1 0 フラット発光制御回路

- 1 1 光強度検出回路

- 1 2 波高値設置回路

- 1 3 ヒステリシス設定回路

【 四 1 】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開昭55-129327(JP,A)

特開昭60-150038(JP,A)

特開平03-235932(JP,A)

特開平10-048715(JP,A)

(58)調査した分野(Int.Cl., DB名)

H05B 41/32

G03B 15/05