# (12) United States Patent

# Yamaji et al.

#### US 7,171,572 B2 (10) Patent No.:

#### (45) Date of Patent: Jan. 30, 2007

## (54) INFORMATION PROCESSING APPARATUS, INFORMATION PROCESSING METHOD, AND PROGRAM

(75) Inventors: Hidenori Yamaji, Tokyo (JP); Masami

Hosaka, Nagano (JP); Akihiro Miyano,

Tokyo (JP)

Assignee: Sony Corporation, Tokyo (JP)

Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 563 days.

Appl. No.: 10/750,816

(22)Filed: Jan. 5, 2004

**Prior Publication Data** (65)

US 2005/0022043 A1 Jan. 27, 2005

#### (30)Foreign Application Priority Data

Jan. 8, 2003 ...... 2003-001721

(51) Int. Cl. G06F 1/30 (2006.01)G06F 1/32 (2006.01)

- **U.S. Cl.** ...... 713/320; 713/340

- Field of Classification Search ...... 713/300, 713/320, 322, 323, 330, 340 See application file for complete search history.

#### (56)References Cited

### U.S. PATENT DOCUMENTS

| 2003/0226043 | A1* | 12/2003 | Hicok 713/300                  |

|--------------|-----|---------|--------------------------------|

| 2004/0044914 | A1* | 3/2004  | $Gedeon  \dots \qquad 713/300$ |

| 2005/0102544 | A1* | 5/2005  | Brewer et al 713/320           |

### \* cited by examiner

Primary Examiner—Dennis M. Butler (74) Attorney, Agent, or Firm—Oblon, Spivak, McClelland, Maier & Neustadt, P.C.

#### (57)ABSTRACT

An information processing apparatus having a processor is disclosed. The apparatus includes power monitoring means for monitoring power consumed by the information processing apparatus. The power monitoring means further outputs a power limit request demanding a limit to the power when the power being monitored exceeds a predetermined threshold. The apparatus also includes first setting means for setting a first control for limiting an availability factor of the processor as a limit to the power when the power monitoring means outputs the power limit request; second setting means for setting a second control for limiting the availability factor of the processor as a limit to the power when the power monitoring means outputs the power limit request; first controlling means for executing the first control set by the first setting means; and second controlling means for executing the second control set by the second setting means.

## 17 Claims, 19 Drawing Sheets

ETHER CONTROLLER ETHER CONNECTOR 46 POWER SUPPLY UNIT POWER MONITORING UNIT JOG DIAL  $\sim$ 36  $\sim$ 37  $\sim$ 40 PC CARD INTERFACE CONTROLLER **KEYBOARD** SLOT 52 \_35 51 PARALLEL TERMINAL CACHE MEMORY MOUSE I /0 I NTERFACE IEEE1394 INTERFACE RAM ~13 1EEE1394 PORT က SER I AL TERMINAL B10S ~30 33 Б Б ~18 72 SOUTH BRIDGE  $\sim$ 54  $\sim$ 53 NORTH Bridge CPU 55 SURROUND CONTROLLER VIDEO CONTROLLER 19 58 5 57 56 ~24 23~ USB CONNECTOR COMMUNICATION MEMORY STICK SLOT STICK CD-ROM DRIVE MICROPHONE **SPEAKERS** MODEM **BLUET00TH** 읖 VGA CC MEMORY 28~  $26^{\sim}$ 20∼

POWER SUPPLY UNIT TIMER 104 41 REGISTER STPCLK# GENERATION UNIT SOUTH BRIDGE POWER MONITORING UNIT  $\infty$ 03 POWER LIMIT SETTING (THRM#) 42 POWER LIMIT REQUESTED **REGISTER** 102  $\sim 112$ CONTROLLER PRELIMINARY POWER LIMIT SETTING STPCKL# TIMER TIMER 72 40 PRELIMINARY POWER LIMIT REQUESTED/PRELIMINARY POWER LIMIT CANCELLATION REQUESTED (SCI) ONGOING PRELIMINARY POWER LIMIT ACKNOWLEDGED CPU PRELIMINARY POWER LIMIT SETTING, POWER LIMIT AMOUNT SETTING PRELIMINARY POWER LIMIT SETTING THROTTLING CONTROL UNIT 84 SOFTWARE PROGRAMS  $\sim$  93 **83 65** ~82 TEMPERATURE SENSOR ACP I LAYER OS **1**00 ACPI MULTISTAGE VOLTAGE SCALING CONTROL UNIT MSR AML 91 81 85 86.

- 1 G 4

| <b>_</b>                        |                                                                                                                                     | 1                                                                          |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| POWER LIMIT CONTROL             | BY CONTROLLER 40                                                                                                                    | THROTTLING CONTROL                                                         |

| PRELIMINARY POWER LIMIT CONTROL | BY USE OF AML 91 OR BIOS 30<br>(THE START AND STOP OF CONTROL ARE<br>TRIGGERED WHEN SCI OR SMI IS<br>SIGNALED BY THE CONTROLLER 40) | THROTTLING CONTROL<br>CONTROL BY TCC<br>MULTISTAGE VOLTAGE SCALING CONTROL |

| CONTROL NAME                    | POWER LIMIT<br>SETTING UNIT                                                                                                         | DESCRIPTION<br>OF POWER<br>LIMIT                                           |

F I G. 5

YES 2 9S~ 6S > **S**5 88 TURN ON POWER LIMIT SETTING (THRM#) TURN ON POWER LIMIT SETTING (THRM#) POWER LIMIT SETTING (THRM#) ON? COUNTER OF POWER LIMIT CONTROL ZERO ON YES T I MER? 2 INITIALIZE COUNTER OF POWER LIMIT CONTROL TIMER 27 **\$4** . ω . DECREMENT POWER LIMIT CONTROL TIMER **PROCESS** END OF YES START POWER LIMITING PROCESS BY CONTROLLER \$22  $\sim$  S3 Š SETT ING (THRM#) ON? POWER LIMIT REQUEST INPUT? END OF PROCESS DESIGNATED? POWER LIMIT 2 2 2

CLEAR SIGNALED FLAG \$33 INITIALIZE COUNTER OF PRELIMINARY POWER LIMIT CONTROL TIMER POWER LIMIT CONTROL TIMER INITIALIZE COUNTER OF PRELIMINARY \$27 ACTIVATE PRELIMINARY POWER ⊢LIMITING MECHANISM SET SIGNALED FLAG **\$26** 531 YES တ CANCEL REQUEST SIGNALED? PRELIMINARY POWER LIMIT SIGNAL PRELIMINARY POWER LIMIT CANCEL REQUEST SIGNAL PRELIMINARY POWER LIMIT REQUEST ட \$29 2 \$25 **S30** 2 2 9 9 PRELIMINARY POWER LIMITING MECHANISM ACTIVATED? END OF PROCESS DESIGNATED? 2 START PRELIMINARY

POWER LIMITING

PROCESS BY CONTROLLER POWER LIMIT SETTING (THRM#) CHANGED? SIGNALED FLAG SET? POWER LIMIT SETTING (THRM#) ON? END OF PROCESS , YES YES ( , YES \$22\$24<sub>></sub> S28>

**Se3** 2 OF PROCESS END OF PROCESS DESIGNATED? YES END 898 **869** 2 PRELIMINARY POWER LIMIT CANCEL REQUEST SIGNALED? CANCEL PRELIMINARY POWER LIMIT SETTING YES щ ~S65 **998 267** -S61 **S**62 \$64 2 9 SIGNAL ONGOING PRELIMINARY POWER LIMIT ACKNOWLEDGMENT TO CONTROLLER ELAPSE SET POWER LIMIT AMOUNT SUBJECT TO THROTTLING CONTROL START PRELIMINARY POWER LIMITING PROCESS BY AML(BIOS) SCI (SMI) PRELIMINARY POWER LIMIT PRELIMINARY POWER LIMIT REQUEST SIGNALED? 2 TIME REQUEST SIGNALED BY FROM CONTROLLER? YES YES **PREDETERMINED** SET ALLOW

F I G. 13

F I G. 15

F I G. 17

## INFORMATION PROCESSING APPARATUS, INFORMATION PROCESSING METHOD, AND PROGRAM

## BACKGROUND OF THE INVENTION

The present invention relates to an information processing apparatus, an information processing method, and a program. More particularly, the invention relates to an information processing apparatus, an information processing 10 method, and a program for controlling the amount of power consumed by an information processing apparatus to an actually required level in a manner permitting easy standardization of techniques for such power management and enabling simple transport of the techniques from one apparatus to another without running the risk of quality defects.

Recent years have witnessed a dramatic increase in CPU (central processing unit) capabilities. The upsurge in performance has been accompanied by the proportionately boosted maximum consumption of power by the CPUs.

In practice, however, there are few occasions on which the CPU runs in an operating state requiring maximum power dissipation. In most cases (i.e., in normal operating state), the latest CPUs consume approximately the same level of power as their predecessors.

Under these circumstances, it has become more difficult than ever to design a power supplying apparatus (also called the power supply unit hereunder) for powering information processing apparatuses each carrying one of such highperformance CPUs.

To design a typical power supply unit requires taking into consideration the maximum power consumption of an apparatus coupled with the power supply unit. More specifically, the power supply unit is designed to deal with the putative case where the CPU incorporated in an information processing apparatus, on-board chips, internal drives, and any devices connected to external device connectors of the apparatus operate all at once at their maximum capacity.

Taking the estimated maximum power dissipation requirement into account in its design, the power supply unit 40 tends to be large-sized and costly when implemented.

Obviously, the bulky, expensive power supply unit is not suited for use on board a portable information processing apparatus such as a mobile computer or a notebook-size personal computer (hereunder, referred to simply as the 45 notebook PC as needed).

As mentioned above, there are few occasions on which the CPU is made to run at capacity consuming the maximum level of power. That means the power supply unit designed simply to address maximum power dissipation tends to be 50 redundant in its performance.

On the other hand, if the power supply unit is designed merely to deal with a steady level of power consumption by the CPU in its normal operating state without regard to the possible maximum level of power consumption, then the 55 unit is subject to an excess supply of power when the CPU runs close to its capacity.

In the face of such an excess supply of power, the power supply unit stops its feed of power to prevent quality defects. In that case, the information processing apparatus utilizing 60 the power supply unit is abruptly deprived of power and becomes incapable of remaining consistent in its processing. In other words, data losses can occur.

It follows that devising a better power supply unit is not enough; it is also necessary to come up with techniques for 65 reducing the level of power consumption by the information processing apparatus itself. Some of such techniques have 2

been proposed in the past. For example, Japanese Patent Laid-open No. 2000-172387 (called the Reference 1 hereunder) discloses a method for switching operation modes of the CPU to reduce power consumption of an information processing apparatus whenever the maximum power consumption level of the apparatus is predicted to exceed a predetermined threshold value.

According to the method disclosed by the Reference 1, the maximum power consumption of the information processing apparatus is a value calculated predictively on the basis of a base load and CPU operation status specific to the apparatus in question. As one disadvantage of the method, the base load and the CPU type vary from one model of information processing apparatus to another, so that a dedicated set of predictive techniques is needed for each model. That means it takes time and effort to transport the techniques for power consumption control between different models of information processing apparatuses. This amounts to a considerable difficulty in standardizing the techniques.

According to the method of the Reference 1, it is necessary to effect power management in keeping with very large values of power limit so that quality defects will not occur even under the most rigorous conditions. This results in a power management scheme subject to a far severer amount of power limit than is actually needed. As another disadvantage of the method, the proposed power management scheme leads to an acute degradation in performance of the information processing apparatus under power limit control.

Furthermore, with the method of the Reference 1 in use, it takes time to switch operation modes of the CPU for power management (for example, it takes a delay time of two seconds for Intel Corporation's throttling mode actually to come into effect following a designated switchover to that mode). As a further disadvantage of the disclosed method, the delay time can hamper the effort to limit power consumption to a managed level in time. That means there is a possibility of quality defects taking place.

# SUMMARY OF THE INVENTION

The present invention has been made in view of the above circumstances and provides an apparatus, a method and a program for controlling the amount of power consumed by an information processing apparatus to an actually required level in a manner permitting easy standardization of techniques for such power management and enabling simple transport of the techniques from one apparatus to another without running the risk of quality defects.

According to the first aspect of the present invention, there is provided an information processing apparatus having a processor, including:

power monitoring means for monitoring power consumed by the information processing apparatus, the power monitoring means further outputting a power limit request demanding a limit to the power when the power being monitored exceeds a predetermined threshold;

first setting means for setting a first control for limiting an availability factor of the processor as a limit to the power when the power monitoring means outputs the power limit request;

second setting means for setting a second control for limiting the availability factor of the processor as a limit to the power when the power monitoring means outputs the power limit request;

first controlling means for executing the first control set by the first setting means; and

second controlling means for executing the second control set by the second setting means.

According to the second aspect of the present invention, there is provided an information processing method for use with an information processing apparatus having a processor, the information processing method including the steps of:

monitoring power consumed by the information processing apparatus, the power monitoring step further generating a power limit request demanding a limit to the power when 10 the power being monitored exceeds a predetermined threshold:

firstly setting a first control for limiting an availability factor of the processor as a limit to the power when the power monitoring step generates the power limit request; 15

secondly setting a second control for limiting the availability factor of the processor as a limit to the power when the power monitoring step generates the power limit request;

firstly controlling execution of the first control set in the first setting step; and

secondly controlling execution of the second control set in the second setting step.

According to the third aspect of the present invention, there is provided a program for use with an information processing apparatus which includes:

a processor;

- a power monitoring unit for monitoring power consumed by the information processing apparatus, the power monitoring unit further outputting a power limit request demanding a limit to the power when the power being monitored 30 exceeds a predetermined threshold;

- a first controlling mechanism for executing a first control for limiting an availability factor of the processor as a limit to the power;

- a second controlling mechanism for executing a second 35 control for limiting the availability factor of the processor as a limit to the power; and

- a microcomputer for passing data to and from the first controlling mechanism via a first interface implemented as hardware and to and from the second controlling mechanism 40 via a second interface implemented as software;

the program being executed by the microcomputer and including the steps of:

firstly setting the first control for the first controlling mechanism via the first interface when the power monitoring 45 unit outputs the power limit request; and

secondly setting the second control for the second controlling mechanism via the second interface when the power monitoring unit outputs the power limit request.

Through the use of the information processing apparatus, 50 information processing method, and program according to the invention, the level of power consumed by the information processing apparatus including a processor is kept monitored. When the power being monitored is found to have exceeded a predetermined threshold, a power limit 55 request is output to demand a limit to the power. Given the power limit request, a first and a second control are set and executed so as to limit the availability factor of the processor.

The information processing apparatus of this invention 60 may execute the above controls based on a current flowing inside the apparatus, on a current flowing outside the apparatus, or on currents that are comprehensively detected flowing in and out of the apparatus.

The inventive arrangements described above execute con- 65 trols to manage the power consumption of the information processing apparatus, particularly in such a manner as to

4

limit the amount of power consumed by the apparatus to an actually required level while permitting easy standardization of the techniques of such power management and enabling simple transport of the techniques from one apparatus to another without running the risk of quality defects.

Other objects, features and advantages of the invention will become more apparent upon a reading of the following description and appended drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 is a block diagram showing a typical structure of an information processing apparatus embodying this invention:

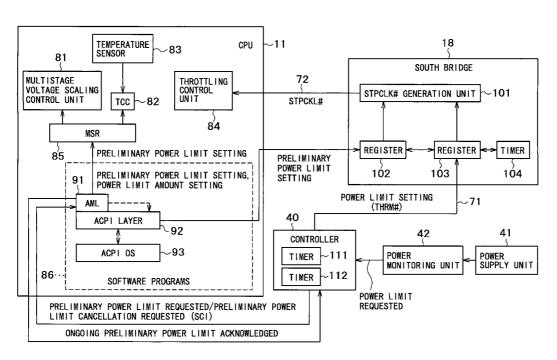

- FIG. 2 is a function block diagram depicting a typical structure of a power limit control block in the information processing apparatus of FIG. 1;

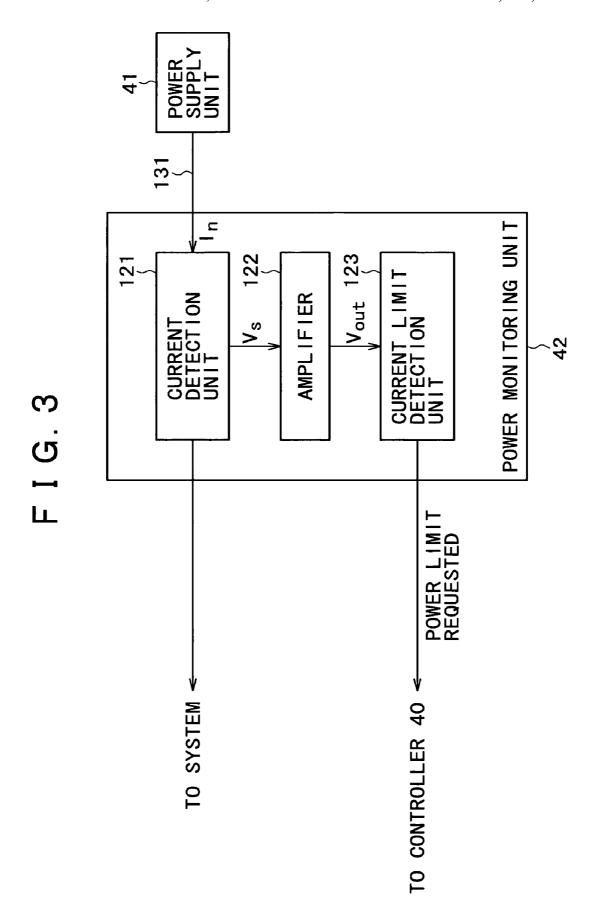

- FIG. 3 is a block diagram illustrating a detailed structure of a power monitoring unit included in FIG. 2;

- FIG. 4 is a tabular view explaining a two-stage power limit control scheme constituted by a preliminary power limit control in the first stage and a power limit control in the second stage;

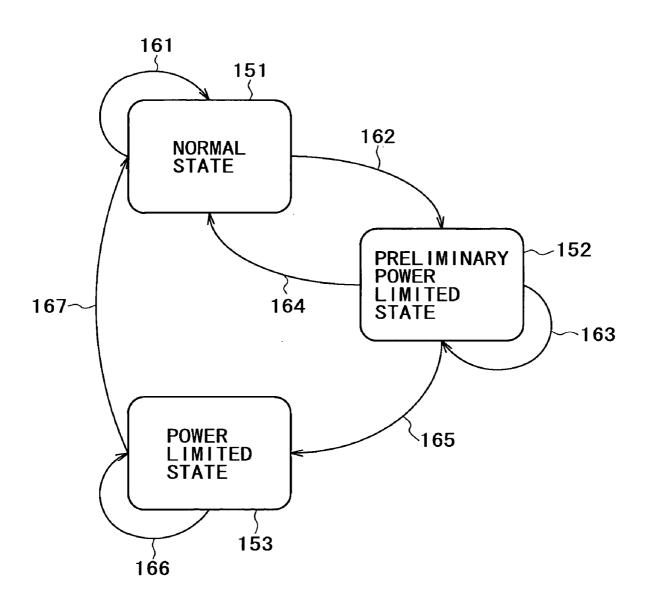

- FIG. 5 is a state transition diagram depicting transitions of the operating state of the power limit control block in FIG. 2.

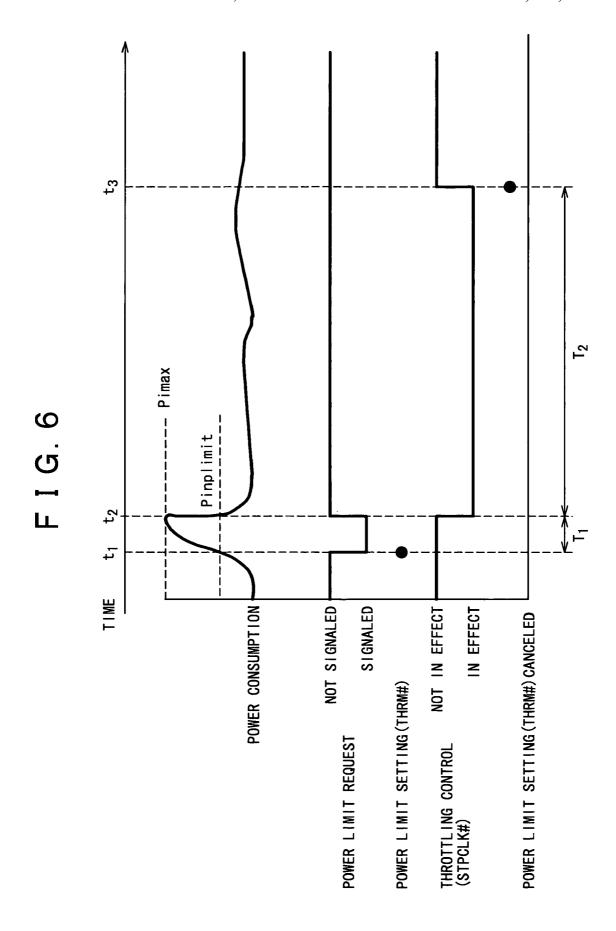

- FIG. 6 is a timing chart indicating how the power limit control of the second stage typically takes place as part of the two-stage power limit control scheme executed by the power limit control block in FIG. 2;

- FIG. 7 is a timing chart sketching how the preliminary power limit control in the first stage typically takes place as part of the two-stage power limit control scheme executed by the power limit control block in FIG. 2;

- FIG. **8** is a flowchart of steps constituting a power limiting process performed by a controller in the power limit control block of FIG. **2**;

- FIG. 9 is a flowchart of steps constituting a preliminary power limiting process carried out by the controller in the power limit control block of FIG. 2;

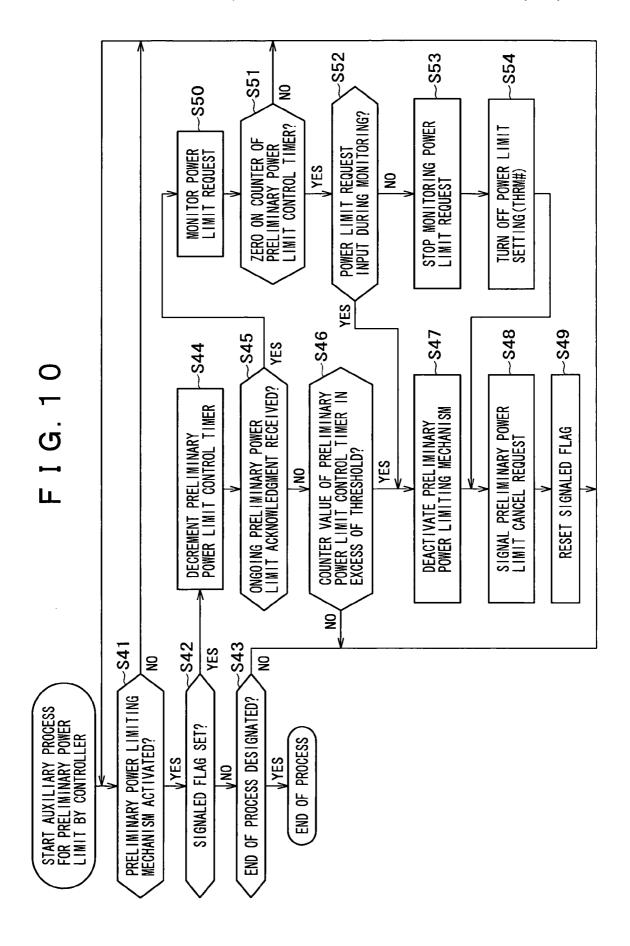

- FIG. 10 is a flowchart of steps constituting an auxiliary process for preliminary power limit by the controller in the power limit control block of FIG. 2;

- FIG. 11 is a flowchart of steps constituting a preliminary power limiting process performed by AML (or by BIOS) in the power limit control block of FIG. 2;

- FIG. 12 is an arrow diagram showing a first case of processing relations between the controller, AML (or BIOS), and a south bridge in the power limit control block of FIG. 2;

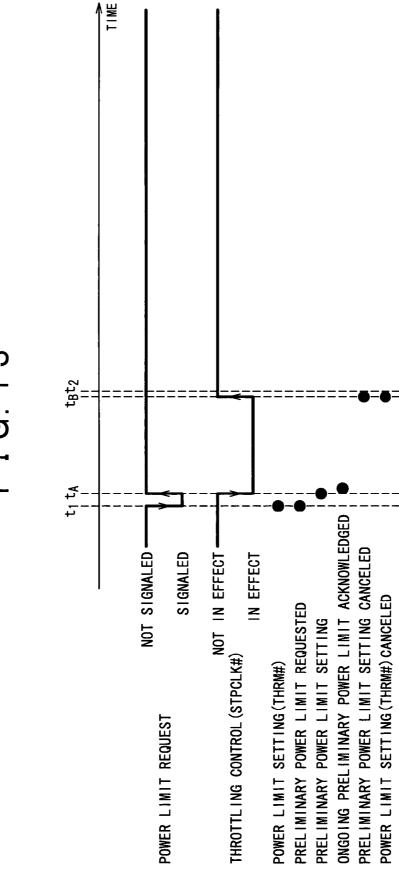

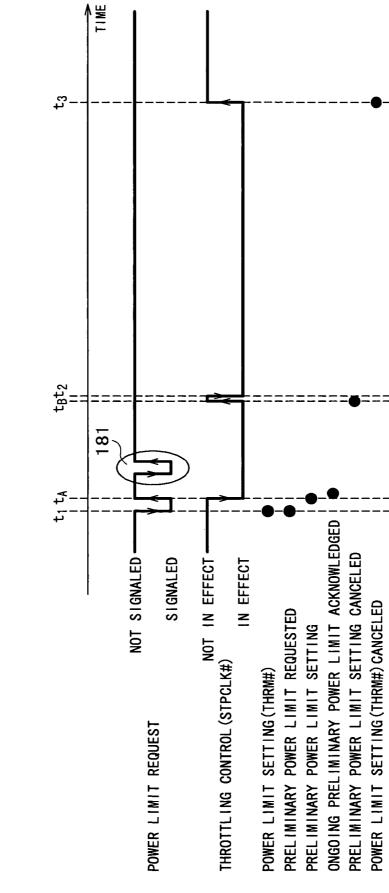

- FIG. 13 is a timing chart applicable to the processing of the first case shown in the arrow diagram of FIG. 12;

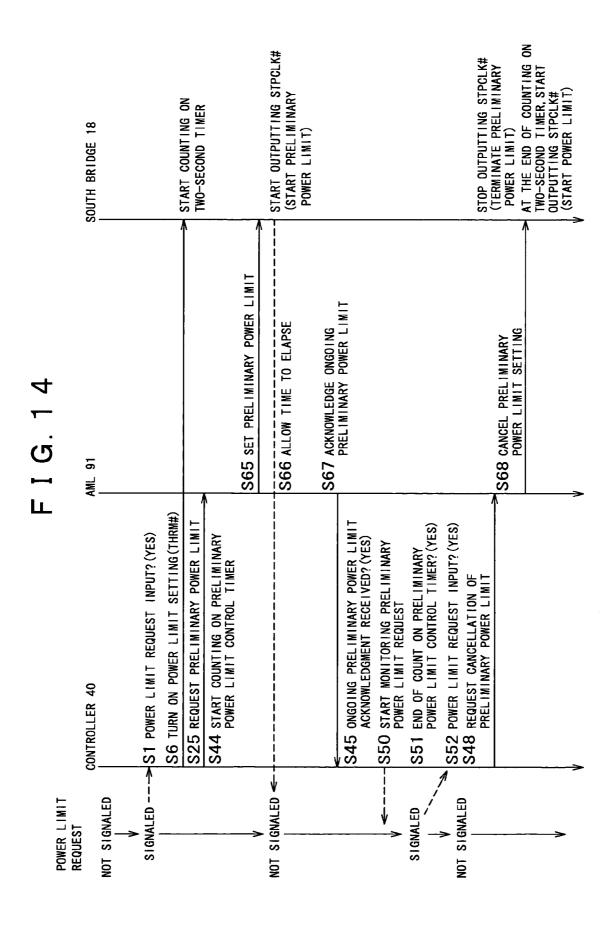

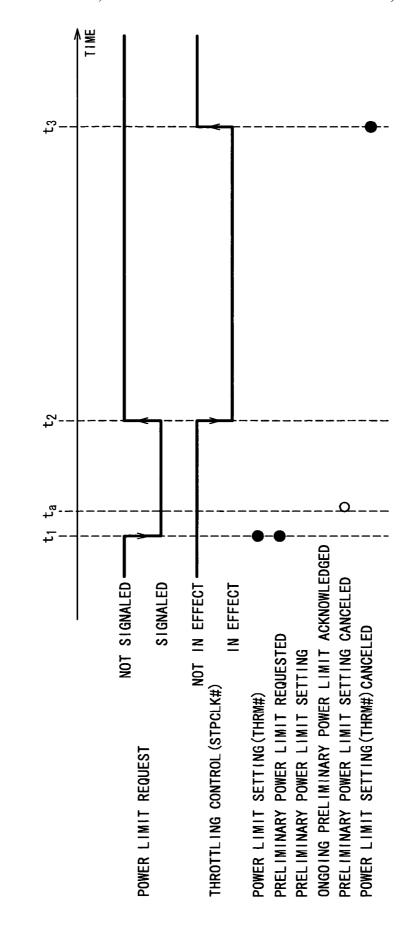

- FIG. 14 is an arrow diagram depicting a second case of processing relations between the controller, AML (or BIOS), and the south bridge in the power limit control block of FIG. 2;

- FIG. 15 is a timing chart applicable to the processing of the second case depicted in the arrow diagram of FIG. 14;

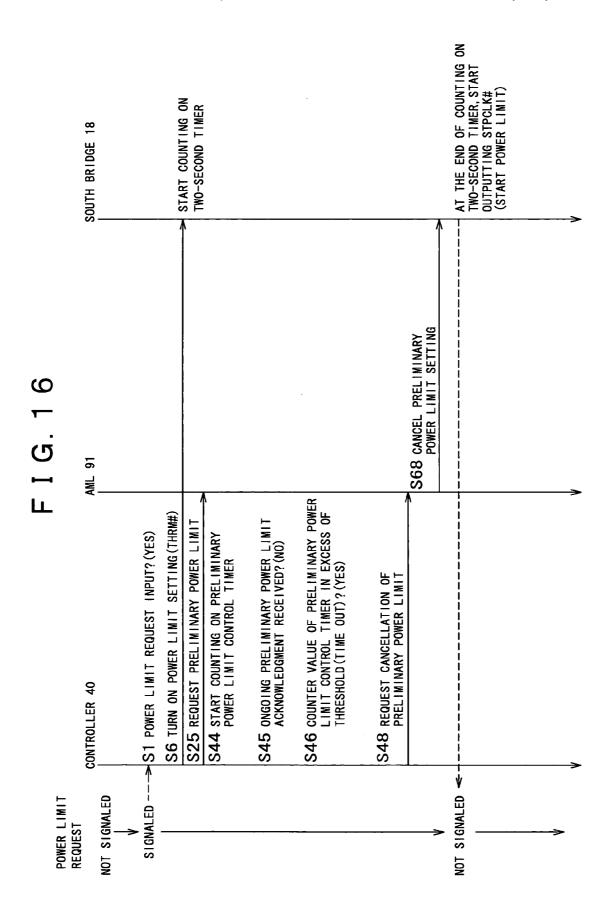

- FIG. 16 is an arrow diagram presenting a third case of processing relations between the controller, AML (or BIOS), and the south bridge in the power limit control block of FIG. 2:

- FIG. 17 is a timing chart applicable to the processing of the third case presented in the arrow diagram of FIG. 16;

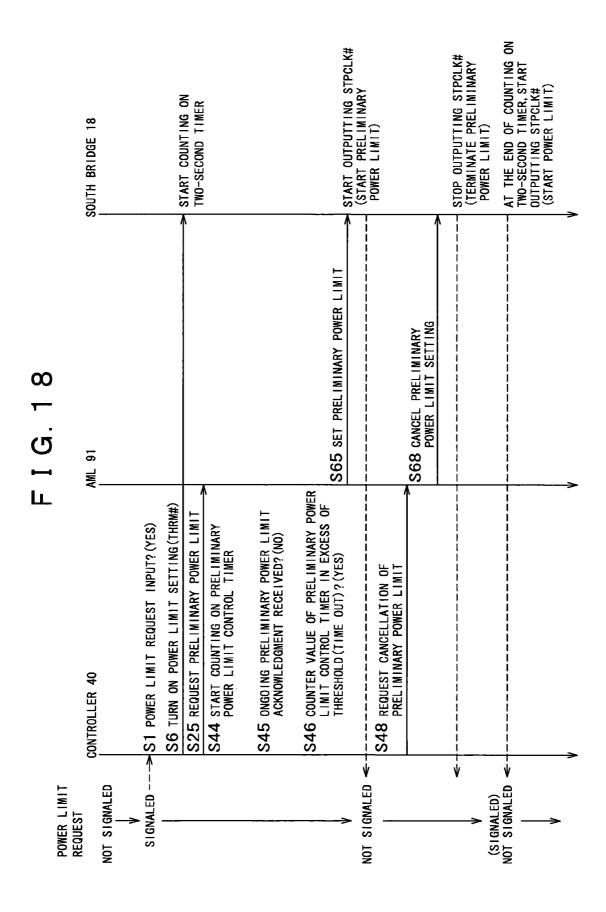

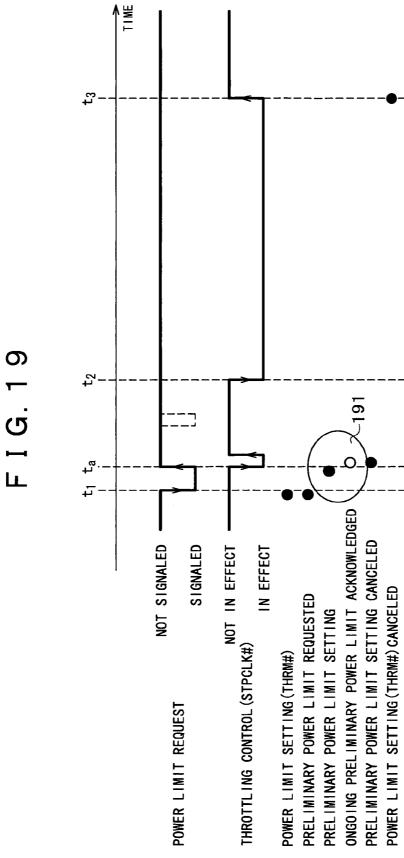

FIG. 18 is an arrow diagram indicating a fourth case of processing relations between the controller, AML (or BIOS), and the south bridge in the power limit control block of FIG. 2; and

FIG. 19 is a timing chart applicable to the processing of 5 the fourth case indicated in the arrow diagram of FIG. 18.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

FIG. 1 shows a typical structure of an information processing apparatus 1 embodying this invention.

In the information processing apparatus 1 of FIG. 1, a CPU 11 is constituted illustratively by a Pentium (registered trademark) processor from Intel Corporation and is connected to a front side bus (FSB) 54. The FSB 54 is connected to a north bridge 14 which has an accelerated graphics port (AGP) 55 and is linked to a bus 53 (or to a hub interface 53 in an Intel arrangement).

The north bridge 14 is illustratively composed of an AGP 20 host bridge controller 440BX from Intel Corporation, providing control over a RAM (random access memory, working as a main memory in this setup) 13. The north bride 14 also controls a video controller 15 through the AGP 55. The video controller 15 provides control over a display unit such 25 as an LCD (liquid crystal display) 16 or a VGA (video graphics array) display 17 (called the VGA 17 hereunder).

Upon receipt of data (image or text data) from the CPU 11, the video controller 15 either generates images corresponding to the received data or stores the received data 30 unmodified into an internal video memory (not shown) The video controller 15 causes the LCD 16 or VGA 17 to display the images corresponding to the image data held in the video memory. Given data from the video controller 15, the LCD 16 or VGA 17 displays the applicable images or text.

The north bridge 14 is also connected to a cache memory 12. The cache memory 12 is made up of memory cells capable of executing read and write operations faster than the RAM 13 (e.g., static RAM (SRAM)). As such, the cache memory 12 caches (temporarily stores) the programs or data 40 being used by the CPU 11.

The CPU 11 has its own primary cache inside which operates even faster than the cache memory 12. The primary cache is under control of the CPU 11 itself.

The RAM 13 is constituted illustratively by a DRAM 45 (dynamic RAM) and stores the programs to be executed by the CPU 11 or the data necessary for the CPU 11 to work with. Specifically, upon completion of a start-up, the RAM 13 receives and accommodates the OS (operating system), Internet-related programs, etc., loaded from an HDD 27.

The OS is a program that controls the basic functions of a computer, exemplified by Windows (registered trademark) XP from Microsoft Corporation or Mac OS (registered trademark) from Apple Computer Incorporated.

The north bridge 14 is further connected to a south bridge 55 18 through the hub interface 53. The south bridge, constituted illustratively by PIIX4E from Intel Corporation, controls various I/O (input/output) components such as an AC97 link bus 56, a USB bus 57, and a device coupled to an IDE bus 58.

More specifically, the AC97 link bus **56** is connected to a modem **20** and a surround controller **19**. The modem **20**, connected to a public switched network, conducts communication processes by way of the public switched network or the Internet (neither shown). The surround controller **19** is 65 connected to a microphone **21** and speakers **22**. In operation, the surround controller **19** captures sounds through the

6

microphone 21 and generates data corresponding to the captured sounds. The surround controller 19 further drives the speakers 22 to output sounds.

The USB bus 57 linked to the south bridge 18 is coupled with a USB connector 23 that permits connection of various USB devices. The USB bus 57 also provides connection between a Memory Stick (registered trademark) slot 24 and a Bluetooth communication unit 26. The Memory Stick slot 24 is loaded with a Memory Stick 25.

The Memory Stick 25 is a flash memory card developed by Sony Corporation, i.e., this applicant. The Memory Stick is made up of flash memory cells forming a nonvolatile memory known as an EEPROM (electrically erasable and programmable read only memory), housed in a thin, small-size plastic case measuring 21.5 mm by 50 mm by 2.8 mm. The memory card has a 10-pin terminal that permits read and write operations of diverse data such as images, voice and music to and from the memory. The Bluetooth communication unit 26 conducts communications based on the Bluetooth standard.

The IDE bus **58** linked to the south bridge **18** is connected to a hard disc drive (HDD) **27**. The IDE bus **58** is further connected electrically to a so-called IDE device such as a CD-ROM (compact disc-read only memory) drive **28**.

The south bridge 18 is capable of causing the CPU 11 to execute what is known as throttling control via a signal line 72. The primary objective of the throttling control is to reduce heating of the CPU 11. More specifically, the throttling control involves driving the CPU 11 on and off so as to lower the clock frequency equivalently (i.e., driving the CPU 11 intermittently to reduce the mean clock frequency). In other words, the throttling control amounts to limiting the availability factor of the CPU 11 thereby managing CPU power consumption.

The south bridge **18** is also connected to a PCI (Peripheral Component Interconnect) bus **51** and an LPC (low pin count) bus **52**.

The LPC bus **52** is connected to a BIOS (Basic Input Output System) **30**, an I/O (input/output) interface **31**, and a controller **40**.

The BIOS 30 is a group of programs making up a collection of basic operating instructions. As such, the BIOS 30 is stored illustratively in a ROM (read only memory), not shown. In operation, the BIOS 30 controls data passing (input and output) between the OS or application programs on the one hand and peripheral devices on the other hand.

The I/O interface 31 is connected to a parallel terminal 32 and a serial terminal 33. Data are exchanged through the I/O interface 31 with devices connected to these terminals.

The controller 40 is connected to such input devices as a jog dial 43, a keyboard 44, and a mouse 45. The controller 40 is further connected to a power monitoring unit 42.

The controller 40 is constituted illustratively by a microcomputer controlling the input devices like the jog dial 43, keyboard 44 and mouse 45.

With this embodiment of the invention, the controller 40 is connected to the south bridge 18 via a signal line 71 formed as part of hardware. As will be discussed later, the controller 40 sets the above-mentioned throttling control for the south bridge 18 based on the result of monitoring by the power monitoring unit 42. In this case, the signal line 71 transmits to the south bridge 18 a signal which is output by the controller 40 and which is needed for the setting of the throttling control.

Also with this embodiment, controls other than the throttling control may be effected to limit the availability factor of the CPU 11 in order to limit the power consumption of the

information processing apparatus 1. The controls may be set illustratively by software programs. The controller 40 also performs processes requesting the software programs to set the controls. Details of the processes will be described later.

A power supply unit **41** is a device that feeds power to the information processing apparatus **1** as a whole. In this example, the power supply unit **41** may be constituted illustratively by an AC (alternating current) power supply adapter or by a battery.

The power monitoring unit 42 monitors the power which, supplied by the power supply unit 41, is actually consumed by the information processing apparatus 1. The result of the monitoring is sent from the power monitoring unit 42 to the controller 40. The power monitoring unit 42 will be discussed later in more detail with reference to FIG. 3.

The PCI bus **51** is connected to an IEEE (Institute of Electrical and Electronics Engineers) 1394 interface **34**, a PC card interface **36**, and an Ether controller **46**.

The IEEE 1394 interface **34** sends and receives data based on the IEEE 1394 standard (i.e., in the form of packetized data) through an IEEE 1394 port **35**.

The PC card interface **36** supplies the CPU **11** or RAM **13** with the data sent from a device (card, not shown) inserted in a slot **37**. The PC card interface **36** also forwards the data 25 coming from the CPU **11** to the card inserted in the slot **37**.

As shown in FIG. 1, the slot 37 is connected with a drive 38 when necessary. In this case, the drive 38 is coupled to the PCI bus 51 through the slot 37 and PC card interface 36. The drive 38 is loaded with a magnetic disc 61, an optical disc 62, a magneto-optical disc 63, or a semiconductor memory 64. The drive 38 reads data from the loaded recording medium, and feeds the retrieved data to the RAM 13. The drive 38 further records the data generated by the CPU 11 to the magnetic disc 61, optical disc 62, magneto-optical disc 63, or semiconductor memory 64 loaded in the drive 38.

The Ether controller **46** communicates with another information processing apparatus, not shown, via a network such as a LAN (local area network) connected to an Ether connector **47**.

As mentioned earlier, CPUs having high frequencies and operating at relatively high levels of power consumption have come into general use in recent years. Also gaining widespread use are information processing apparatuses in the form of mobile computers and notebook-size PCs. Because these apparatuses are supposed to be used in portable fashion, the power supply unit 41 for use therewith is not to be limited to an AC power supply adapter; the unit 41 may also be implemented as a battery arrangement.

Under these circumstances, if a CPU 11 having a high frequency and running at an elevated level of power consumption is to be incorporated into the notebook-size PC (i.e., information processing apparatus 1), measures need to be taken to lower the overall power consumption of the apparatus 1 in order to prolong the life of the battery and to reduce the battery size.

These measures adopted by the information processing apparatus 1 of this invention involve detecting a total current 60 (i.e., an actually flowing current) consumed by the apparatus 1 so as to determine whether the detected current level exceeds a predetermined threshold. If the threshold is found exceeded, the availability factor of the CPU 11 is limited (i.e., the clock frequency is lowered), whereby the power 65 consumption of the apparatus 1 is controlled. This type of control is called the power limit control in this specification.

8

The power limit control will be shown hereunder implemented by, but not limited to, the above-mentioned throttling control.

In this example, the start of the throttling control is triggered by a signal (power control request shown in FIG. 2, to be described later) output by the power monitoring unit 42. If the power monitoring unit 42 is constituted by hardware and incorporated in the information processing apparatus 1, the setup eliminates the need for the OS, application programs and control tables which were needed conventionally to output the trigger. This means that one of the problems discussed in connection with the prior art is resolved by the inventive arrangement. That is, the techniques for power limit control are easily standardized and transported between different models of information processing apparatuses.

However, when the power monitoring unit 42 outputs the signal to trigger the start of the throttling control (power control request in FIG. 2, to be described later), the throttling control is not started immediately; the control is started upon elapse of a predetermined time period set forth for the south bridge 18 (e.g., two seconds specified for the south bridge 18 from Intel Corporation).

In other words, simply carrying out the throttling control does not resolve the other problems of the prior art discussed earlier, i.e., acute degradation in performance of the information processing apparatus under power limit control, and the possibility of quality defects taking place.

These problems are addressed by the inventive information processing apparatus 1 resorting to what is called multistage power limit control, whereby the power consumption of the apparatus 1 is limited to an actually needed level even as quality defects are prevented.

With this embodiment, the multistage power limit control is implemented illustratively in two stages for purpose of simplification and illustration. In the description that follows, power limit control in the first stage (i.e., initially executed power limit control) is called the preliminary power limit control, and power limit control in the second stage (i.e., power limit control performed after the preliminary power limit control has started) is called the power limit control.

What follows is a description of how the preliminary power limit control and the power limit control are illustratively carried out. It should be noted that the ensuing specificities are provided merely to give some illustrations; they may be implemented otherwise.

Three alternatives are available as the preliminary power limit control: throttling control, TCC (thermal control circuit) control, and multistage voltage scaling control. One of the three controls is used selectively. The TCC control and multistage voltage scaling control will each be described later in more detail. For the power limit control, the throttling control is adopted.

FIG. 2 is a function block diagram depicting a detailed structure of the major components for executing the preliminary power limit control and the power limit control in the information processing apparatus 1 of FIG. 1.

For purpose of simplification and illustration, the components shown in FIG. 2 are assumed to constitute a single device called a power limit control block.

The power limit control block is made up of the CPU 11, south bridge 18, controller 40, power supply unit 41, and power monitoring unit 42.

The power supply unit **41**, illustratively composed of an AC power adapter or a battery, feeds power to the information processing apparatus **1** (FIG. **1**). The target entity

powered by the power supply unit **41** is called the system. That is, the system refers to the information processing apparatus **1** as a whole.

The power supply unit **41** is subject to such design specifications as the rated power, peak power, peak power duration, and duty rate (i.e., rate of the period in which system power consumption remain below the rated power, to the period in which system power consumption exceeds the rated power) stipulated for the unit.

The power monitoring unit 42, implemented illustratively 10 by hardware, monitors the level of power supplied from the power supply unit 41 to the system. When the power being monitored is found to have exceeded a predetermined threshold, the power monitoring unit 42 outputs to the controller 40 a signal requesting execution of the preliminary power limit control and power limit control (the latter is executed only when needed). The signal is called the power limit request.

FIG. 3 illustrates a detailed structure of the power monitoring unit 42 included in FIG. 2. The power monitoring unit 20 42 is described below in detail with reference to FIG. 3.

In FIG. 3, the power supply unit 41 feeds all currents that are consumed by the system (information processing apparatus 1) through a power transmission line 131 and a power detection unit 121. That is, the power transmission line 131 25 is laid out inside the system in such a manner that the entire system is fed with the necessary currents through the line.

The current detection unit 121 is implemented illustratively as a detecting resistor. A current In flowing over the power transmission line 131 is detected as a voltage across 30 the detecting resistor. That is, the current detection unit 121 detects the current In as the voltage Vs given by the following expression (1):

$$Vs = In \times Rs$$

(1)

where, Rs denotes the resistance value of the detecting resistor in the current detection unit 121.

An amplifier 122, constituted illustratively by an operational amplifier, amplifies by a gain G the voltage Vs detected by the current detection unit 121 (i.e., the voltage value is multiplied by the value G). The result of the amplification is output as a voltage Vout to a current limit detection unit 123. The output voltage from the amplifier 122 is given by the following expression (2):

$$Vout=G \times Vs$$

(2)

where, G stands for a suitable integer (20 for this example). The power limit detection unit 123 inputs the output voltage Vout from the amplifier 122, and calculates the level 50 of the current In flowing over the power transmission line 131 (i.e., the current consumed by the system) based on the voltage Vout. If the calculated level of the current In is found to have exceeded a predetermined limiting level (corresponding to a limiting value of the current In), then the 55 power limit detection unit 123 outputs a power limit request to the controller 40.

More specifically, since the power supply unit 41 is generally implemented as a constant voltage source, it is possible to calculate the power consumed by the system (i.e., 60 the information processing apparatus 1 of FIG. 1 as a whole) on the basis of the current In flowing through the power transmission line 131.

Thus if the current In actually flowing over the power transmission line **131** at a given point in time is found to 65 have exceeded a current (called a limiting current linplimit) corresponding to the rated power (called the limiting power

10

Pinplimit for use as a limiting value) of the power supply unit 41, then the power limit detection unit 123 determines that the power being consumed by the system has exceeded the limiting power Pinplimit at that point in time, and outputs the power limit request to the controller 40 accordingly.

Between the limiting power Pinplimit and the limiting current Iinplimit exists the relationship defined by the following expression (3):

where, Vin stands for the output voltage of the power supply unit 41.

Returning to FIG. 2, the controller 40 detects the power limit request output by the power monitoring unit 42. With the request detected, the controller 40 sets the power limit control (of the second stage) to a register 103 of the south bridge 18 through the signal line 71 formed as hardware. In other words, the signal line 71 serves as a hardware interface between the controller 40 and the south bridge 18.

In the description that follows, the signal which is needed for the setting of the power limit control and which is transmitted over the signal line 71 will be called a power limit setting. For the south bridge from Intel Corporation, the power limit setting is specifically called THRM#.

As will be discussed later, when the controller 40 outputs a power limit setting (THRM#), the throttling control is not carried out immediately (i.e., the signal STPCLK# for triggering execution of the throttling control, to be described later, is not output immediately). That is, the throttling control is performed after a predetermined time period (e.g., two seconds specified for the south bridge 18 from Intel Corporation) has elapsed (i.e., the signal STPCLK# is output).

It follows that, where the power limit control (throttling control) alone is executed based on the power limit setting (THRM#), two of the problems associated with the prior art (acute degradation in performance of the information processing apparatus under power limit control, and the possibility of quality defects taking place) are not resolved as mentioned above.

To address the problems, the controller **40** of this invention outputs the power limit setting (THRM#) to the south bridge **18** while signaling at about the same time to AML (ACPI machine language) **91** a piece of information for requesting execution of the preliminary power limit control (simply called the preliminary power limit request hereunder) by use of an SCI (system control interrupt).

What follows is a description of the SCI and AML in view of their relevance to this invention.

For example, of the operating systems released so far by Microsoft Corporation, Windows (registered trademark) 98 and subsequent versions support an interface with peripherals called ACPI (Advanced Configuration and Power Interface). The operating systems supporting ACPI are called an ACPI OS each. Illustratively in the setup of FIG. 2, the ACPI OS is represented by an ACPI OS 93.

Application programs that run under the ACPI OS and software programs that control data passing (input and output) to and from peripheral devices are collectively referred to as the ACPI layer. In FIG. 2, for example, the ACPI layer is represented by an ACPI layer 92 that controls the south bridge 18 and controller 40 as peripherals.

The ACPI layer **92** varies from one type of information processing apparatus to another. This constraint is circumvented by a program called AML (a compiled description

language) in the BIOS 30 (FIG. 1). AML permits data passing (input and output) to and from peripherals regardless of the apparatus type (i.e., independent of the ACPI layer type), and is loaded and executed as needed. In the setup of FIG. 2, AML is represented by the above-mentioned AML 5 91 which acts as a software interface with peripherals.

Control by the AML 91 is effected using an interruption called SCI. On detecting an SCI, the AML 91 identifies the peripheral device that has issued it (controller 40 in this example), and carries out the control corresponding to the 10 detected SCI.

More specifically, suppose that the AML 91 has detected an SCI from the controller 40 and has determined that the SCI corresponds to the above-mentioned preliminary power limit request. In that case, the AML 91 sets the preliminary 15 power limit control (power limit control of the first stage), to be described later in more detail. The information necessary for setting the preliminary power limit control is simply called a preliminary power limit control setting.

In the setup of FIG. 2, the CPU 11 carries out software 20 programs 86 in the ACPI environment as described. The software programs 86 include the ACPI OS 93, AML 91 and ACPI layer 92 for controlling data passing to and from peripheral devices (south bridge 18 and controller 40), and application programs (not shown) that run under the ACPI 25 OS 93.

In a non-ACPI environment (i.e., an environment under an OS other than the ACPI OS), data passing (input and output) to and from the peripheral devices is controlled by the BIOS 30 (FIG. 1). In this case, the interruption corresponding to the SCI of ACPI is called an SMI (system management interrupt). Thus in the non-ACPI environment, not shown, an OS other than the ACPI OS is used; the BIOS 30 takes the place of the AML 91 and ACPI layer 92; and a preliminary power limit request and a preliminary power 35 control upon detecting a signal called STPCLK#, to be limit cancel request are issued through the use of SMIs, not SCIs.

After setting the preliminary power limit control, the AML 91 signals the controller 40 that the preliminary power limit control has been set. Specifically, the AML 91 gives an 40 acknowledgment in response to the preliminary power limit request coming from the controller 40. The acknowledging response is called an ongoing preliminary power limit acknowledgment (ACK).

The controller 40 has two timers 111 and 112. The timer 45 111, used for the power limit control (in the second stage), measures the time to cancel the power limit control. The timer 112 for the preliminary power limit control (in the first stage) measures the time to cancel the preliminary power limit control. How the timers 111 and 112 are used will be 50 discussed later in more detail.

The CPU 11 has a multistage voltage scaling control unit 81, a TCC (thermal control circuit) 82, and a throttling control unit 84. These components serve to limit the availability factor of the CPU 11 (i.e., to reduce the clock 55 frequency).

The multistage voltage scaling control unit 81 carries out multistage voltage scaling control, which involves controlling the voltage for the CPU 11 over multiple stages in keeping with clock frequencies.

More specifically, the power consumption of the CPU 11 is in proportion to its clock frequency (i.e., availability factor of the CPU 11). The power consumption of the CPU 11 is also proportional to the square of the voltage applied to the CPU 11. That means lowering the voltage fed to the CPU 11 65 reduces the clock frequency of the CPU 11 (i.e., decreases the availability factor of the CPU 11). This is the operating

12

principle for the multistage voltage scaling control. From among a number of stages of voltages set beforehand for application to the CPU 11 under this control scheme, the voltage corresponding to a desired clock frequency of the CPU 11 (availability factor) is selected and fed to the CPU

What is noticeable about the multistage voltage scaling control is that multiplying by 1/n the voltage applied to the CPU 11 translates into the CPU clock frequency (availability factor) being multiplied not by 1/n but by 1/n squared  $(1/n^2)$ . That is, compared with the throttling control or TCC control (to be discussed later), the multistage voltage scaling control provides a significantly high controlling effect (i.e., in terms of the ratio of a decline in the availability factor of the CPU 11 to the setting (the decrease in the voltage under the multistage voltage scaling control).

The multistage voltage scaling control is given various names by manufacturers: SpeedStep (trademark) by Intel Corporation, PowerNow (trademark) by Advance Micro Devices Incorporated (AMD), and LongRun (trademark) by Transmate Corporation.

The TCC 82 constitutes a temperature managing mechanism in combination with a temperature sensor 83 embedded in the chip to measure the chip temperature. When the measurement of the temperature sensor 83 exceeds a predetermined temperature, the TCC 82 stops the operation of the CPU 11 at fixed intervals in order to reduce the heating. The operation results in a reduction of the power consumption by the CPU 11.

Such control executed by the TCC 82 is called the TCC control in this specification. The TCC control is called On-Demand CC by Intel Corporation.

The throttling control unit 84 carries out the throttling described later.

The CPU 11 also has a model-specific register (MSR) 85. The MSR 85 has information set thereto which is needed to specify execution of the multistage voltage scaling control or the TCC control.

For example, if the multistage voltage scaling control is selected as the preliminary power limit control, the AML 91 sets to the MSR 85 the information necessary for executing the multistage voltage scaling control as the preliminary power limit control. In turn, the MSR 85 instructs the multistage voltage scaling control unit 81 to perform the multistage voltage scaling control.

As another example, if the TCC control is selected as the preliminary power limit control, the AML 91 sets to the MSR 85 the information needed to carry out the TCC control. In turn, the MSR 85 instructs the TCC 82 to execute the TCC control.

What happens when the throttling control is selected as the preliminary power limit control will be discussed later.

The south bridge 18 has an STPCLK# generation unit 101, registers 102 and 103, and a timer 104. These components are provided to have the CPU 11 (more specifically, the throttling control unit 84) execute the throttling control.

The STPCLK# generation unit 101 generates a signal (called STPCLK# as mentioned above) for instructing the throttling control unit 84 of the CPU 11 to carry out the throttling control. The generated signal is output to the throttling control unit 84 over the signal line 72 formed as hardware.

The STPCLK# generation unit 101 receives an STPCLK# generation command (called the generation command here-

under) from the register 102 or 103. In response, the STPCLK# generation unit 101 starts generating the signal STPCLK#

As long as the generation command is being input, the STPCLK# generation unit 101 keeps outputting the signal 5 STPCLK# (i.e., to let the throttling control unit 84 carry out the throttling control continuously). When the input of the generation command is stopped, the STPCLK# generation unit stops outputting the signal STPCLK# (causing the throttling control unit 84 to stop the throttling control).

Illustratively, if the throttling control is selected as the preliminary power limit control, the AML 91 writes "ON" or "OFF" to the register 102 as preliminary power limit setting. As soon as "ON" is written to the register 102, the register 102 outputs the generation command to the STPCLK# 15 generation unit 101. As soon as "OFF" is written to the register 102, the register 102 stops outputting the generation command.

On the other hand, if the power monitoring unit 42 outputs a power limit request, the controller 40 writes "ON" or 20 "OFF" to the register 103 as power limit setting (THRM#). With "ON" written therein, the register 103 does not output a generation command immediately and thereby allows the timer 104 to start counting. When the timer 104 has counted a predetermined time period (two seconds for the south 25 bridge 18 from Intel Corporation), with "ON" still held in the register 103, the register 103 outputs a generation command to the STPCLK# generation unit 101. Thereafter, the register 103 stops outputting the generation command as soon as "OFF" is written thereto.

The information set to the registers 102 and 103 is described here as "ON" or "OFF" for purpose of simplification and illustration. In practice, a "0" (Low level) or a "1" (High level) may be written corresponding to the "ON" or "OFF" information respectively. What is written to the 35 registers 102 and 103 is not limited to "ON" or "OFF" and "0" or "1"; any other suitable information may be set to the registers for the purpose.

In the description that follows, writing "ON" or "OFF" to the register 102 or 103 may be referred to as setting the 40 register on or off respectively, where appropriate.

The generation command output by the register 102 takes precedence over that which is output by the register 103.

The tabular view of FIG. 4 summarizes what has been discussed so far. That is, FIG. 4 sketches functionally the 45 power limit control block of the invention for setting the preliminary power limit control and the power limit control, along with an outline of the features of power management implemented thereby.

In the power limit control block structured as shown in 50 FIG. 2, the power monitoring unit 42 formed as hardware outputs a power limit request. The output of the request triggers in a substantially instantaneous manner the execution of the preliminary power limit control (multistage voltage scaling control, TCC control, or throttling control). 55 Thereafter, upon elapse of a predetermined time period (two seconds for the south bridge from Intel Corporation), the power limit control (throttling control) is carried out. This procedure makes it possible to limit the power consumption by the information processing apparatus to an actually 60 needed amount while preventing quality defects taking place. That means the problems discussed earlier in connection with the prior art are now resolved.

If the AML 91 does not cancel the preliminary power limit control, both the preliminary power limit control and the 65 power limit control will be carried out concurrently. In such a case, the combined effect (i.e., reduction in the availability

14

factor of the CPU 11) equals the effect of the preliminary power limit control being multiplied by that of the power limit control. The concurrent execution of the two kinds of control should be pursued actively if it is desired to maximize the control effect.

However, too much effect can lead to a degradation in performance of the information processing apparatus 1 under power limit control. That is, one of the problems discussed in conjunction with the prior art can reemerge and 10 remain unresolved.

In that case, the controller **40** using an SCI may signal to the AML **90** a request for canceling the preliminary power limit control before the power limit control is started (the request is called a preliminary power limit cancel request). On receiving the preliminary power limit cancel request, the AML **91** immediately cancels the preliminary power limit control and thereby stops execution of the preliminary power limit control. The concurrent execution of the preliminary power limit control and the power limit control is thus avoided.

If the preliminary power limit control and the power limit control are the throttling control each, it is not mandatory to signal the preliminary power limit cancel request before the start of the power limit control. Still, in the present embodiment of the invention, the preliminary power limit cancel request is signaled to the AML 91 before the start of the power limit control regardless of the type of the preliminary power control limit being implemented.

The transitions of the operating state of the power limit control block in FIG. 2 will now be described with reference to FIG. 5. What is shown in FIG. 5 is one example of state transitions that the power limit control block undergoes.

As shown in FIG. 5, the power limit control block is in one of three states: a normal state 151, a preliminary power limited state 152, or a power limited state 153.

The normal state 151 refers to a state in which the power limit control block carries out neither the preliminary power limit control nor the power limit control.

The preliminary power limited state 152 is a state in which the power limit control block executes the preliminary power limit control.

The power limited state 153 is a state where the power limit control block performs the power limit control.

It will be appreciated that the example in FIG. 5 is one in which the power limit control and the preliminary power limit control are not carried out simultaneously.

When a certain condition (called a state transition control) is fulfilled, a transition takes place from one state to another (or the currently effective state remains unchanged) among the normal state 151, preliminary power limited state 152, and power limited state 153.

In the example of FIG. 5, state transition conditions are indicated by arrows numbered 161 through 167 each denoting a possible transition from one state to another among the normal state 151, preliminary power limited state 152, and power limited state 153.

Illustratively, suppose that the initial state (state in effect when the power supply unit 41 has started powering the system, i.e., information processing apparatus 1 of FIG. 1) is the normal state 151 and that this is the state the power limit control block initially finds itself in.

On the above assumption, the power monitoring unit 42 does not output a power limit request unless and until the power being monitored exceeds a predetermined threshold. While the power level remains below the threshold, the controller 40 determines that the state transition condition 161 is satisfied and causes accordingly the power limit

control block to make a transition from the normal state 151 to the normal state 151 (i.e., the initial state remains unchanged).

If the power being monitored is found to exceed the threshold, the power monitoring unit 42 outputs the power limit request to the controller 40. In this case, the controller 40 determines that the state transition condition 162 is fulfilled and causes accordingly the power limit control block to make a transition from the normal state 151 to the preliminary power limited state 152.

When the power limit control block enters the preliminary power limited state 152, the controller 40 sets execution of the first control (i.e., power limit control) to reduce the availability factor of the CPU 11 thereby limiting the consumed power. That is, the power limit setting (THRM#) is 15 set to "ON."

In turn, the register 103 causes the timer 104 to start counting. At this point, the register 103 does not yet output the generation command to the STPCLK# generation unit 101, so that the power limit control (throttling control) is not 20 carried out

Meanwhile, the AML 91 recognizes the output of the power limit request from the power monitoring unit 42 upon receipt of a preliminary power limit request (SCI) from the controller 40. The-AML 91 then generates information, that 25 is, preliminary power limit setting, for setting execution of the second control (i.e., preliminary power limit control), whereby the availability factor of the CPU 11 is reduced to limit the power consumption.

After signaling the preliminary power limit request (SCI) 30 to the AML 91, the controller 40 causes the preliminary power limit control timer 112 to start counting.

In the setup of FIG. 2, any one of the three controls is selectively usable as the preliminary power limit control: multistage voltage scaling control performed by the multistage voltage scaling control unit 81, TCC control by the TCC 82, or throttling control by the throttling control unit 84

For example, if the multistage voltage scaling control is to be used as the preliminary power limit control, the AML 91 40 sets to the MSR 85 the setting information for executing the multistage voltage scaling control. In turn, the MSR 85 issues a control start command to the multistage voltage scaling control unit 81. Given the start command, the multistage voltage scaling control unit 81 carries out the 45 multistage voltage scaling control as instructed by the AML 91

As another example, if the TCC control is to be used as the preliminary power limit control, the AML 91 sets to the MSR 85 the setting information for executing the TCC 50 control. In turn, the MSR 85 issues a control start command to the TCC 82. Given the start command, the TCC 82 performs the TCC control as instructed by the AML 91.

As yet another example, if the throttling control is to be used as the preliminary power limit control, the AML 91 sets 55 the setting information for executing the throttling control. More specifically, the AML 91 writes "ON" to the register 102 of the south bridge 18. In turn, the register 102 outputs a generation command to the STPCLK# generation unit 101. Given the generation command, the STPCLK# generation ounit 101 generates a signal STPCLK# and sends the generated signal to the throttling control unit 84 over the signal line 72. On detecting the signal STPCLK#, the throttling control unit 84 carries out the throttling control as instructed by the AML 91.

As described, when the power monitoring unit 42 outputs the power limit request (thereby bringing the power limit 16

control block into the preliminary power limited state 152), the preliminary power limit control is executed almost instantaneously.

When the power monitoring unit 42 outputs the power limit request, the power limit setting (THRM#) is set to "ON." But the register 103 does not output the generation command to the STPCLK# generation unit 101 until a predetermined time period elapses on the timer 104 (two seconds for the south bridge 18 from Intel Corporation). That is, the power limit control is not performed immediately upon output of the power limit request from the power monitoring unit 42; the control is executed only after the timer 104 has finished its counting.

When canceling the preliminary power limit control, the controller 40 signals a preliminary power limit cancel request to the AML 91 by use of an SCI. In other words, the preliminary power limit control remains in effect unless and until the controller 40 signals the preliminary power limit cancel request to the AML 91 using the SCI. As illustrated, the state transition condition 163 is a condition requiring that the preliminary power limit cancel request not be signaled. As long as the state transition condition 163 is being met, the power limit control block is thus in transition from the preliminary power limited state 152 to the preliminary power limited state remains unchanged).

When the controller 40 signals the preliminary power limit cancel request to the AML 91 by use of the SCI, the preliminary power limit control is brought to and end. That means the power limit control block makes a transition from the preliminary power limited state 152 either to the normal state 151 or to the power limited state 153.

That is, if the controller 40 determines that the preliminary power limit control currently in effect has succeeded, the controller 40 using the SCI signals the preliminary power limit cancel request to the AML 91 and cancels the power limit control as well (by setting the power limit setting (THRM#) to "OFF"). In such a case, the state transition condition 164 is found to be met, so that the power limit control block makes a transition from the preliminary power limited state 152 to the normal state 151.

At that point, the register 103 causes the timer 104 to stop its counting and to initialize its counter. That is, the power limit control is not carried out when the preliminary power limit control having been executed so far is found to have succeeded.

On the other hand, if the controller 40 determines that the preliminary power limit control in execution so far has failed, the controller 40 signals a preliminary power limit cancel request to the AML 91 using an SCI. At this point, it should be noted, the power limit control is not canceled (i.e., the power limit setting (THRM#) remains on). Thus the state transition condition 165 is found to be met, so that the power limit control block makes a transition from the preliminary power limited state 152 to the power limited state 153.

The timer 104 terminates its counting in the south bridge 18 thereafter (upon elapse of two seconds for the south bridge from Intel Corporation). At this point, the register 103 outputs a generation command to the STPCLK# generation unit 101. Given the generation command, the STPCLK# generation unit 101 generates STPCLK# and outputs the generated signal to the throttling control unit 84 over the signal line 72. On detecting the signal STPCLK#, the throttling control unit 84 carries out the throttling control (power limit control) based on the power limit setting (THRM#).

Whether or not the preliminary power limit control has been successful is determined by this embodiment illustratively in accordance with the following criteria:

With the preliminary power limit control under execution, the controller 40 keeps monitoring the output of a power 5 limit request from the power monitoring unit 42. If no power limit request has been detected during execution of the preliminary power limit control (i.e., from the time an ongoing preliminary power limit acknowledgment was detected until the preliminary power limit control timer 112 10 ends its counting), then the controller 40 determines that the preliminary power limit control carried out so far has been successful

On the other hand, if even a single power limit request has been detected during execution of the preliminary power <sup>15</sup> limit control, the controller **40** determines that the preliminary power limit control performed so far has failed.

If no ongoing preliminary power limit acknowledgment has been output (i.e., detected) by the AML 91 during the predetermined time period (counted by the preliminary <sup>20</sup> power limit control timer 112), the controller 40 also determines that the preliminary power limit control has been unsuccessful.

The count time of the preliminary power limit control timer 112 will be described later in more detail.

When the power limit control block goes into the power limited state 153, the power limit control (throttling control based on the power limit setting (THRM#)) is carried out as described above.

At this point, the power limit control timer 111 is still counting (the time at which to start counting will be discussed later). At the end of the counting by the timer 111, the controller 40 cancels the power limit control. More specifically, the controller 40 sets the power limit setting (THRM#) to "OFF." This causes the register 103 to stop outputting the generation command. On detecting the absence of the generation command, the STPCLK# generation unit 101 stops outputting the signal STPCLK#. When detecting the absence of the signal STPCLK#, the throttling control unit 84 terminates execution of the power limit control (i.e., throttling control based on the power limit setting (THRM#)).

Thus the state transition condition 166 is a condition which, after the power limit control block enters the power limited state 153, requires that the power limit control timer 111 keep counting. While the state transition condition 166 is being met, the power limit control block makes a transition from the power limited state 153 to the power limited state 153 (i.e., the current state remains unchanged).

The state transition condition 167, on the other hand, is a condition requiring that the time limit control timer 111 terminate its counting. When the state transition condition 167 is met, the power limit control block makes a transition from the power limited state 153 to the normal state 151.

The count time of the power limit control timer 111 will be discussed later in more detail.

Described below with reference to FIGS. 6 and 7 are: the count time of the power limit control timer 111, the count time of the preliminary power limit control timer 112, the 60 duration of the power limit control, and the duration of the preliminary power limit control, in connection with the power limit control block (FIG. 2).

FIG. 6 is a timing chart for explaining the duration of the power limit control and the count, time of the power limit 65 control timer 111. In other words, FIG. 6 is a timing chart in effect when the preliminary power limit control is not carried

18

out (only the throttling control based on the power limit setting (THRM#) is executed).

In FIG. 6, the time axis is shown at the top of the chart. From the time axis down, the following are graphically illustrated: the power consumption of the system (the information processing apparatus 1 in FIG. 1 as a whole), the presence or absence of the power limit request from the poser monitoring unit 42, the power limit setting (THRM#) (the time at which the controller 40 writes "ON" to the register 103 through the signal line 71), the execution or inexecution of the throttling control (the presence or absence of STPCLK# output by the STPCLK# generation unit 101), and the cancellation of the power limit setting (THRM#) (the time at which the controller 40 writes "OFF" to the register 103 via the signal line 71).

In FIG. 6, "Pinplimit" denotes a power limit threshold (rated power for the power supply unit 41 in this case), and "Pimax" represents a peak power level rated for the power supply unit 41.

As shown in FIG. 6, it is assumed illustratively that the level of power consumption exceeds the power limit "Pinplimit" at a time t1. At that point in time, the power monitoring unit 42 detects the excess and outputs a power limit request to the controller 40 accordingly.

In the description that follows, the power limit request, STPCLK# and other signals may be said to be turned on or off when output or not output, respectively.

When the power limit request is turned on, the controller 40 sets the power limit setting (THRM#) to "ON." That is, the power limit setting (THRM#) is timed to be in effect when the power limit request is turned on (at about time t1 in the example of FIG. 6).

The south bridge **18** outputs STPCLK# to the throttling control unit **84** of the CPU **11** via the signal line **72** at a time **t2**, upon elapse of a delay time T**1** after the power limit setting (THRM#) is set to "ON" (count time of the timer **104**, illustratively two seconds specified for the south bridge **18** from Intel Corporation) On detecting the signal STP-CLK#, the throttling control unit **84** starts executing the throttling control. The throttling control is maintained as long as the signal STPCLK# is being detected. In other words, when the signal STPCLK# is turned on (at time **t2** in FIG. **6**), the throttling control is initiated. While the signal STPCLK# is being on, the throttling control remains in effect.

As described, the throttling control (power limit control) is started as per the power limit setting (THRM#) at the time t2 upon elapse of the delay time T1 following the time t1 at which the power consumption of the system (information processing apparatus 1) exceeded the power limit "Pinplimit" (to be precise, following the time at which the power limit setting (THRM#) was set to "ON" and the timer 104 started its counting). In other words, if the preliminary power limit control is not carried out, an uncontrolled state emerges (where the throttling control is not performed as per the power limit setting (THRM#)) between the time t1 and the time t2. That means the power consumption of the system (information processing apparatus 1) can stay above the power limit "Pinplimit" for some time.

However, the rated voltage (i.e., power limit "Pinplimit") stipulated in the design specification of the power supply unit 41 is restricted by the heating of the unit 41. For that reason, the power consumption is managed not in accordance with instantaneous values of power consumption but on the basis of a mean power level over a fixed time period. That is, even if the level of power consumption momentarily exceeds the power limit "Pinplimit," the phenomenon is

considered to fall within tolerance of the design specification for the power supply unit **41** as long as the mean power level between the rated peak power "Pimax" and the duty rate remains below the power limit "Pinplimit."

It follows that the design specification of the power 5 supply unit **41** is met if the throttling control (power limit control) is continued based on the power limit setting (THRM#) during the time T2, i.e., a time period during which the consumed power falls within the rated power. The time period T2 is established in accordance with the time 10 period T1 during which the power consumption may exceed the rated power (power limit "Pinplimit"), and on the basis of the duty rate (i.e., the rate of the time during which the consumed power remains within the rated power, to the time during which the consumed power exceeds the rated power). 15 That is, with the throttling control continued, the mean power during the times T1 and T2 combined (i.e., heating value of the power supply unit **41**) remains below the power limit "Pinplimit" which is the rated power.

More specifically, if the duty rate is 10 percent (i.e., the 20 ratio of the time during which the consumed power remains within the rated power to the time during which the consumed power exceeds the rated power is 9 to 1), if the delay time T1 is two seconds (applicable to the south bridge 18 from Intel Corporation), and if the peak power "Pimax" 25 continues during the delay time T1 (two seconds), then the time period T2 during which the power limit control should be maintained (called the power limit continuation time T2) is at least nine times the delay time T2, i.e., 18 seconds (=9×T1=9×2 sec.) or longer.

The power limit continuation time T2 may be used illustratively as the count time of the power limit control timer 111 for the controller 40. (It should be noted, as will be discussed later, that the count time of the power limit control timer 111 is not limited to the power limit continuation time T2.) In this case, the power limit control timer 111 starts counting at the time t2 at which the power limit request is turned off, keeps counting during the power limit continuation time T2, and terminates the counting operation at a time t3, i.e., at the end of the power limit continuation time T2 following the time t2, is the time at which to cancel the power limit setting (THRM#).

At the time t3 (after the power limit control timer 111 has counted the power limit continuation time T2), the controller 45 40 signals cancellation of the power limit control to the south bridge 18 over the signal line 71, whereby the power limit setting (THRM#) is set to "OFF." This causes the south bridge 18 to stop outputting STPCLK#. On detecting the absence of the signal STPCLK#, the throttling control unit 50 84 stops the throttling control. That is, when the signal STPCLK# is turned off (at time t3 in the example of FIG. 6), the throttling control (power limit control) based on the power limit setting (THRM#) is brought to an end.

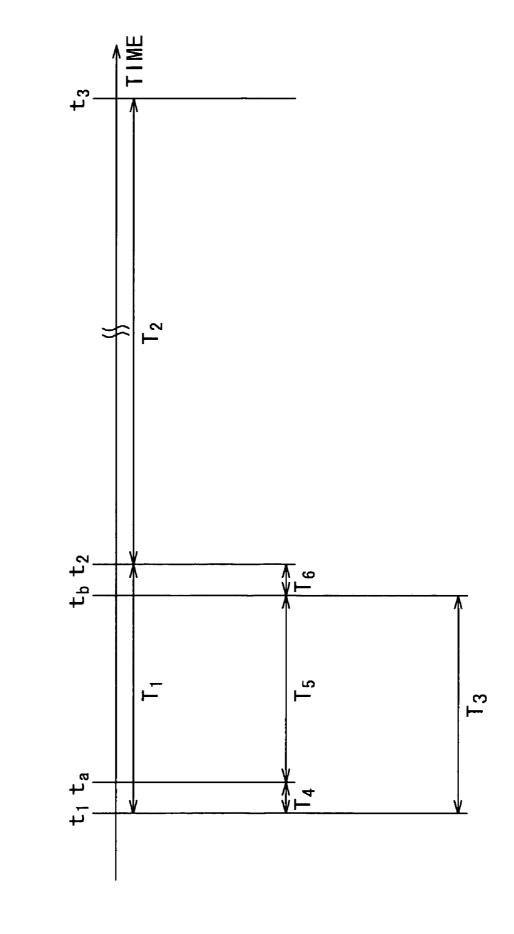

FIG. 7 is a timing chart for explaining the duration of the 55 preliminary power limit control and the count time of the preliminary power limit control timer 112.

In FIG. 7, the horizontal line represents the time axis, the same as that in FIG. 6. On this time axis, a time t1 stands for the time at which the power limit request is turned on; a time 60 t2 denotes the time at which the power limit control (throttling control based on the power limit setting (THRM#)) is started; and a time t3 represents the time at which the power limit control is terminated.

Since the preliminary power limit control and the power 65 limit control are not allowed to take place concurrently as mentioned above, the preliminary power limit control needs

20

to end before the start of the power limit control. That is, the preliminary power limit control is to be executed between the time t1 and the time t2.

The preliminary power limit control is thus terminated at a time tb, with a time period T6 allowed in before the time t2 at which the power limit control is to be started, as shown in FIG. 7. The allowed time T6 may not be restricted to a specific period of time, but may be set illustratively to 0.2 seconds for this example.

As a result, the preliminary power limit control lasts during the time period T3. In this case, the time period T3 is given as 1.8 seconds (T3=T1-T6=2-0.2 sec.).

It should be noted that if the mean power level between the rated peak power "Pimax" and the duty rate does not exceed the power limit "Pinplimit," then the design specification of the power supply unit 41 is considered to be complied with. Thus if the duty rate is set to 10 percent as in the case of FIG. 6, the design specification of the power supply unit 41 is complied with provided the preliminary power limit control is performed for a time period T5 which is at least 90 percent of the time period T3 (T5=T3×0.9=1.8×0.9=1.62 sec. for this example).

In other words, what is only needed is that a time lag (delay time) from the time the controller **40** signals a preliminary power limit request to the AML **90** using an SCI at about the time t**1** until the preliminary power limit control is actually started falls within a time period T**4** which is 10 percent of the time period T**3** (T**4**=T**3**×0.1=1.8×0.1=0.18 sec.). That is, the design specification of the power supply unit **41** is complied with if the preliminary power limit control is started between the time t**1** and the time ta that is later than the time t**1** by the time period T**4**.

The preliminary power limit control timer 112 starts counting at about the time t1 at which the preliminary power limit request (SCI) is signaled, and terminates the counting operation at the time tb at which the preliminary power limit control is scheduled to end. That means the time period T3 equals the count time of the preliminary power limit control timer 112.

The controller 40 monitors the count value on the timer 112 for preliminary power limit control, as described above. If an ongoing preliminary power limit acknowledgment is not output from the AML 41 past the time ta (i.e., after the preliminary power limit control timer 112 has counted the time period T4), the controller 40 determines that the preliminary power limit control has failed. That is, even if the preliminary power limit control is started past the time ta, it is difficult to ensure the duty rate. That means it is impossible to comply with the design specification of the power supply unit 41; hence the preliminary power limit control is considered a failure.

At the time tb (at which the preliminary power limit control timer 112 finishes counting the time period T3), the controller 40 determines whether or not the preliminary power limit control has succeeded on the basis of the presence or absence of a power limit request throughout the duration of the control (i.e., from the time the preliminary power limit control acknowledgment was detected until the time tb was reached).

Described below with reference to the flowcharts of FIGS. 8 through 11 is how control processing of the power limit control block in FIG. 2 takes place. More specifically, typical control processes performed successively by the controller 40 and AML 91 constituting a power limit setting unit in the power limit control block are to be described individually.

The steps making up the preliminary power limit control process to be described below are the same regardless of any one of the above-described control types being adopted for the preliminary power limit control. Illustratively, the throttling control is assumed to be implemented here for the 5 preliminary power limit control.

The preliminary power limit control and the power limit control are not allowed to be executed simultaneously as mentioned earlier. The preliminary power limit control is to be followed by the power limit control.