(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7573354号

(P7573354)

(45)発行日 令和6年10月25日(2024.10.25)

(24)登録日 令和6年10月17日(2024.10.17)

(51)国際特許分類

|         |                 |         |      |         |

|---------|-----------------|---------|------|---------|

| G 0 9 G | 3/20 (2006.01)  | G 0 9 G | 3/20 | 6 2 3 A |

| G 0 9 G | 3/3275(2016.01) | G 0 9 G | 3/20 | 6 1 2 U |

| H 1 0 K | 50/10 (2023.01) | G 0 9 G | 3/20 | 6 3 1 U |

| H 1 0 K | 59/00 (2023.01) | G 0 9 G | 3/20 | 6 4 1 P |

|         |                 | G 0 9 G | 3/20 | 6 4 2 B |

請求項の数 12 (全19頁) 最終頁に続く

(21)出願番号 特願2018-189497(P2018-189497)

(22)出願日 平成30年10月4日(2018.10.4)

(65)公開番号 特開2020-60605(P2020-60605A)

(43)公開日 令和2年4月16日(2020.4.16)

審査請求日 令和3年9月28日(2021.9.28)

審判番号 不服2023-3524(P2023-3524/J1)

審判請求日 令和5年3月1日(2023.3.1)

(73)特許権者 502161508

シナプティクス インコーポレイテッド

アメリカ合衆国, 95131 カリフォ

ルニア州, サンノゼ, マッケイ ドラ

イブ 1109

(74)代理人 100205350

弁理士 狩野 芳正

(72)発明者 織尾 正雄

東京都中野区中野4丁目10番2号 シ

ナプティクス・ジャパン合同会社内

降旗 弘史

東京都中野区中野4丁目10番2号 シ

ナプティクス・ジャパン合同会社内

(72)発明者 能勢 崇

東京都中野区中野4丁目10番2号 シ

最終頁に続く

(54)【発明の名称】 表示ドライバ、表示装置及び表示パネルの駆動方法

## (57)【特許請求の範囲】

## 【請求項1】

複数の電源端子と、前記複数の電源端子から同一の電源電圧を受け取るように構成された複数の画素とを備える表示パネルに表示される画像に対応する画像データに基づいて第1電圧データを生成するように構成された画像処理回路部と、前記表示パネルにおける前記画素の位置に応じて前記画素について位置依存ゲインを生成し、前記画素で消費される電流の前記表示パネル全体についての和である総電流と前記位置依存ゲインとにに基づいて、前記画素について補償ゲインを生成するように構成された補償回路部と、

前記第1電圧データを前記補償ゲインに基づいて補正することで第2電圧データを生成するように構成された電圧データ生成部と、

前記第2電圧データに基づいて前記画素に駆動電圧を書き込むように構成された駆動回路部

とを備える表示ドライバであって、

前記画素の位置と前記位置依存ゲインとの間の複数の対応関係が、前記総電流の異なる電流値にそれぞれに対応する複数のLUTの値として当該表示ドライバに保存され、

前記補償回路部が、

前記総電流のシミュレーション値を算出し、

前記総電流の前記シミュレーション値に基づく前記複数のLUTに保存された値の補間により、前記位置依存ゲインを算出する

ように更に構成された

表示ドライバ。

【請求項 2】

前記補償ゲインは、前記表示パネルに含まれる電源配線における電圧降下を補償するよ

うに生成される

請求項 1 に記載の表示ドライバ。

【請求項 3】

前記補償回路部は、

前記総電流に応じて前記表示パネルの複数のセグメントのそれぞれについてエリアゲ

インを生成し、

前記エリアゲインと前記位置依存ゲインとに基づいて前記複数のセグメントのそれぞ

れの各画素の前記補償ゲインを算出する

ように構成された

請求項 1 に記載の表示ドライバ。

【請求項 4】

前記電圧データ生成部は、前記第 2 電圧データに記述された電圧値を、前記第 1 電圧デ

ータに記述された電圧値と前記補償ゲインとの積として算出するように更に構成された

請求項 3 に記載の表示ドライバ。

【請求項 5】

前記補償回路部は、前記総電流の前記シミュレーション値に応じて前記エリアゲインを

生成する

ように更に構成された

請求項 3 に記載の表示ドライバ。

【請求項 6】

前記補償回路部は、

前記表示パネルの複数のセグメントのそれぞれについて、前記複数のセグメントのそれ

ぞれに配置された画素のサブセットに流れる電流のシミュレーション値の和を算出し、

前記複数のセグメントのそれぞれについて算出された前記和に基づいて、前記総電流

の前記シミュレーション値を算出する

ように更に構成された

請求項 5 に記載の表示ドライバ。

【請求項 7】

前記補償回路部は、

第 1 フレーム期間において、前記複数のセグメントのうちの第 1 セグメントに配置さ

れた画素の一又は複数に駆動電圧が書き込まれるとき、

前記第 1 セグメント及び前記第 1 フレーム期間において未だ駆動電圧が書き込まれて

いない一又は複数セグメントについて、前フレーム期間に表示された画像に対応する前記

画像データに基づいて算出された一以上の和と、

前記第 1 フレーム期間において既に駆動電圧が書き込まれたセグメントについて、前

記第 1 フレーム期間に表示される画像に対応する前記画像データに基づいて算出された一

以上の和と

に基づいて、前記総電流の前記シミュレーション値を算出するように構成された

請求項 6 に記載の表示ドライバ。

【請求項 8】

前記補償回路部は、前記第 1 セグメントについて算出された前記総電流の前記シミュ

レーション値に基づいて得られる前記エリアゲインと、前記第 1 セグメントと異なるセグ

メントについて算出された前記総電流の前記シミュレーション値に基づいて得られる前記エ

リアゲインとを、前記第 1 セグメントに配置された前記画素の位置に基づいて補間するこ

とで、前記第 1 セグメントに配置された画素についての前記補償ゲインの生成に用いる前

記エリアゲインを生成するように更に構成された

10

20

30

40

50

請求項 7 に記載の表示ドライバ。

【請求項 9】

複数の電源端子と、前記複数の電源端子から同一の電源電圧が供給される複数の画素とを備える表示パネルと、

前記表示パネルに表示される画像に対応する画像データに基づいて第 1 電圧データを生成する画像処理回路部と、

前記表示パネルにおける前記画素の位置に応じて前記画素について位置依存ゲインを生成し、前記画素で消費される電流の前記表示パネル全体についての和である総電流と前記位置依存ゲインとに基づいて、前記画素について補償ゲインを生成する補償回路部と、

前記第 1 電圧データを前記補償ゲインに基づいて補正することで第 2 電圧データを生成する電圧データ生成部と、

前記第 2 電圧データに応じて前記画素に駆動電圧を書き込む駆動回路部とを備え、

前記画素の位置と前記位置依存ゲインとの間の複数の対応関係が、前記総電流の異なる電流値にそれぞれに対応する複数の LUT の値として前記補償回路部に保存され、

前記補償回路部が、

前記総電流のシミュレーション値を算出し、

前記総電流の前記シミュレーション値に基づく前記複数の LUT に保存された値の補間により、前記位置依存ゲインを算出する

ように更に構成された

表示装置。

【請求項 10】

前記補償回路部は、

前記総電流に応じて前記表示パネルの複数のセグメントのそれぞれについてエリアゲインを生成し、

前記複数のセグメントのそれぞれについて生成された前記エリアゲインと前記位置依存ゲインとから前記複数のセグメントのそれぞれの各画素の前記補償ゲインを算出するように構成された

請求項 9 に記載の表示装置。

【請求項 11】

複数の電源端子と、前記複数の電源端子から同一の電源電圧が供給される複数の画素とを備える表示パネルに表示される画像に対応する画像データから第 1 電圧データを生成することと、

補償回路部により、前記表示パネルにおける前記画素の位置に応じて前記画素について位置依存ゲインを生成することと、

前記補償回路部により、前記画素で消費される電流の前記表示パネル全体についての和である総電流と前記位置依存ゲインとに応じて、前記画素について補償ゲインを生成することと、

前記第 1 電圧データを前記補償ゲインに基づいて補正することで第 2 電圧データを生成することと、

前記第 2 電圧データに応じて前記画素に駆動電圧を書き込むこととを含み、

前記画素の位置と前記位置依存ゲインとの間の複数の対応関係が、前記総電流の異なる電流値にそれぞれに対応する複数の LUT の値として前記補償回路部に保存され、

前記補償ゲインを生成することが、

前記総電流のシミュレーション値を算出することと、

前記総電流の前記シミュレーション値に基づく前記複数の LUT に保存された値の補間により、前記位置依存ゲインを算出することと、

とを含む

表示パネルの駆動方法。

10

20

30

40

50

## 【請求項 1 2】

前記第 2 電圧データを生成することは、

前記総電流に基づいて前記表示パネルの複数のセグメントのそれぞれについてエリアゲインを生成することと、

前記複数のセグメントのそれぞれについて生成された前記エリアゲインと前記位置依存ゲインとに基づいて前記複数のセグメントのそれぞれの各画素の前記補償ゲインを算出することと、

前記第 1 電圧データと前記補償ゲインとに基づいて前記第 2 電圧データを生成することとを含む

請求項 1 1 に記載の表示パネルの駆動方法。

10

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本開示は、表示ドライバ、表示装置及び表示パネルの駆動方法に関する。

## 【背景技術】

## 【0 0 0 2】

ある種の表示パネル、例えば、O L E D (organic light emitting diode) 表示パネルでは、電源配線を介して各画素回路に電源電圧が供給される。このような構成の表示パネルは、例えば表示パネルの電源配線において生じる電圧降下に起因して、画像にムラが生じ得る。

20

## 【発明の概要】

## 【0 0 0 3】

一実施形態では、表示ドライバが、表示パネルに表示される画像に対応する画像データから第 1 電圧データを生成する画像処理回路部と、前記表示パネルに配置される画素で消費される総電流と前記表示パネルにおける前記画素の位置とに応じて、前記画素のそれぞれについて補正值を生成する補償回路部と、前記第 1 電圧データを前記補正值に応じて補正することで第 2 電圧データを生成する電圧データ生成部と、前記第 2 電圧データに応じて前記画素に駆動電圧を書き込む駆動回路部とを備えている。

## 【0 0 0 4】

一実施形態では、表示装置が、複数の電源端子と、前記複数の電源端子から電源電圧が供給される画素とを備える表示パネルと、前記表示パネルに表示される画像に対応する画像データから第 1 電圧データを生成する画像処理回路部と、前記表示パネルに設けられる前記画素で消費される総電流と前記表示パネルにおける前記画素の位置とに応じて、前記画素のそれぞれについて補正值を生成する補償回路部と、前記第 1 電圧データを前記補正值に応じて補正することで第 2 電圧データを生成する電圧データ生成部と、前記第 2 電圧データに応じて前記画素に駆動電圧を書き込む駆動回路部とを備えている。

30

## 【0 0 0 5】

一実施形態では、表示パネルの駆動方法が、複数の電源端子と、前記複数の電源端子から電源電圧が供給される画素とを備える表示パネルに表示される画像に対応する画像データから第 1 電圧データを生成することと、前記表示パネルに設けられる前記画素で消費される総電流と前記表示パネルにおける前記画素の位置とに応じて、前記画素のそれぞれについて補正值を生成することと、前記第 1 電圧データを前記補正值に応じて補正することで第 2 電圧データを生成することと、前記第 2 電圧データに応じて前記画素に駆動電圧を書き込むことを含む。

40

## 【図面の簡単な説明】

## 【0 0 0 6】

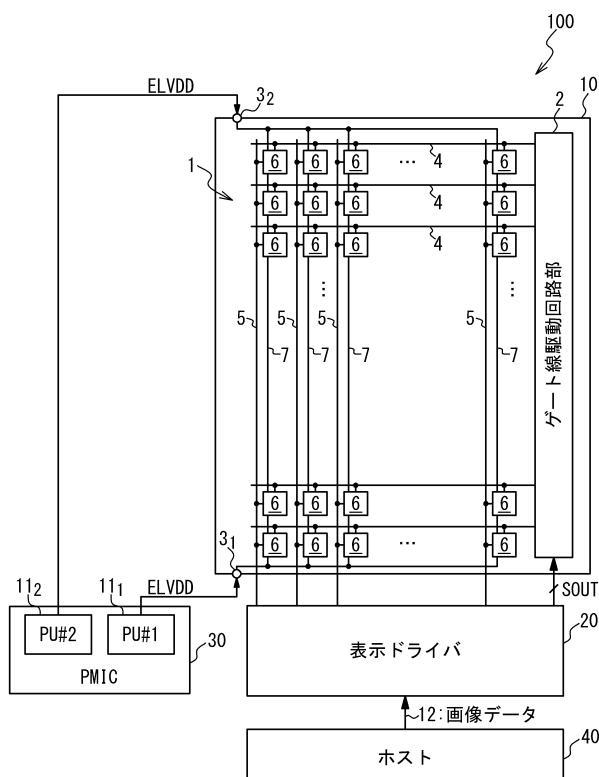

【図 1】一実施形態における表示装置の構成を示している。

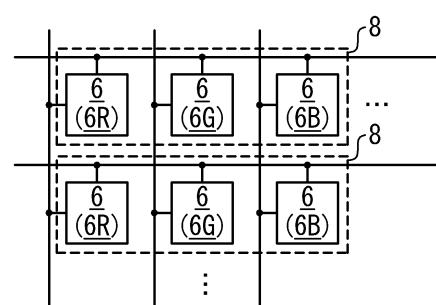

【図 2】一実施形態における画素の構成を示している。

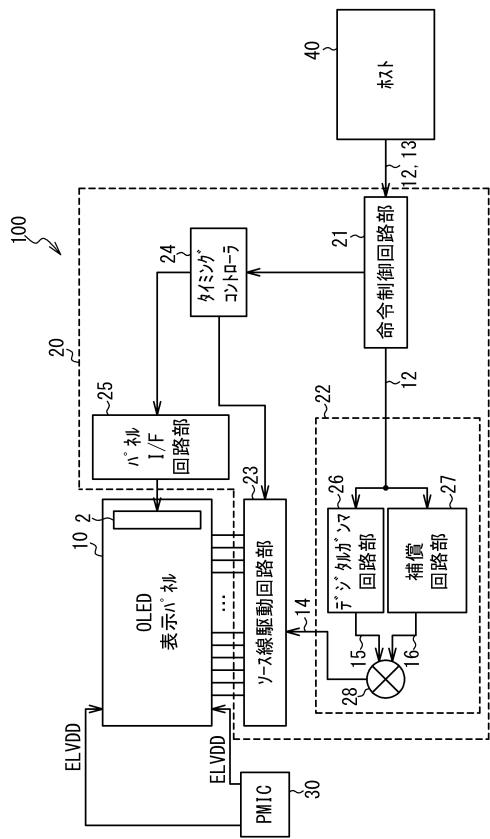

【図 3】一実施形態における表示ドライバの構成を示している。

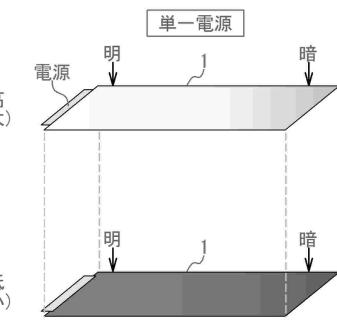

【図 4】単一電源から表示パネルに電源電圧が供給される場合の明暗パターンの例を示し

50

ている。

【図5】2つの電源から表示パネルに電源電圧が供給される場合の明暗パターンの例を示している。

【図6】一実施形態における補償回路部の構成を示している。

【図7】一実施形態における画素アレイの構成を示している。

【図8】一実施形態における累積回路部の構成を示している。

【図9A】一実施形態における累積回路部の動作を示している。

【図9B】一実施形態における累積回路部の動作を示している。

【図9C】一実施形態における累積回路部の動作を示している。

【図10】一実施形態における表示装置の構成を示している。

【発明を実施するための形態】

【0007】

以下、添付図面を参照しながら本開示の様々な実施形態を説明する。以下において、同一又は類似の構成要素は、同一又は対応する参照符号によって参照される。また、同一の構成要素を互いに区別する場合、参照符号に添字が付されることがある。

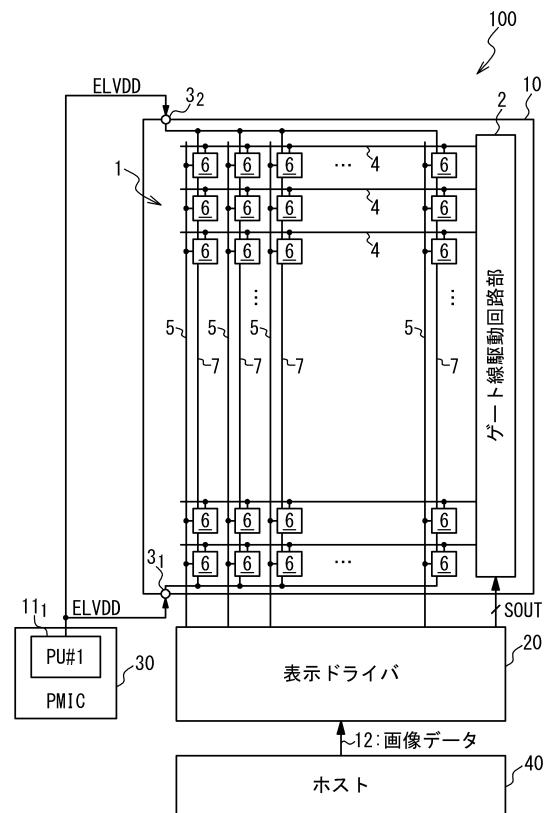

【0008】

図1に示す一実施形態では、表示装置100が、表示パネル10と、表示ドライバ20とを備えている。表示パネル10は、例えば、OLED (organic light emitting diode) 表示パネルである。

【0009】

一実施形態では、表示パネル10は、画素アレイ1とゲート線駆動回路部2とを備えている。画素アレイ1には、ゲート線4とソース線5と画素回路6と電源配線7とが配置されている。各画素回路6は、対応するゲート線4及びソース線5に接続されている。ゲート線駆動回路部2は、表示ドライバ20から受け取ったゲート制御信号SOUTに応じてゲート線4を駆動するように構成されている。

【0010】

一実施形態では、表示パネル10は、複数の、図1の構成では2つの電源端子31、32を有している。各電源配線7の一端は電源端子31に接続され、他端は電源端子32に接続される。2つの電源端子31、32のそれぞれには、電源電圧ELVDDがパワーマネジメントIC(PMIC)30から供給される。パワーマネジメントIC30には電源111、112が集積化されている。電源111、112は、パワーマネジメントIC30とは別になっていてもよい。電源111、112は、それぞれ、電源端子31、32に電源電圧ELVDDを供給する。一実施形態では、電源111、112は、それから出力される電源電圧ELVDDが同一の電圧レベルを有するように制御される。

【0011】

一実施形態では、各画素回路6は、電源配線7を介して電源電圧ELVDDが供給され、供給された電源電圧ELVDDを用いて動作するように構成されている。一実施形態では、画素回路6のそれぞれは、OLED素子を有している。OLED素子は、電源電圧ELVDDが供給される電源端子から、該OLED素子を介して、回路接地に駆動電流が流れることによって、発光する。

【0012】

電源111、112が、同一の電圧レベルの電源電圧ELVDDを生成するように設計されている場合でも、画素回路6に実際に供給される電源電圧ELVDDの電圧レベルは、電源配線7において発生する電圧降下に起因して画素回路6毎に異なり得る。画素回路6に実際に供給される電源電圧ELVDDの電圧レベルのバラツキは、表示パネル10に表示される画像におけるムラの原因になり得る。

【0013】

図2に示す一実施形態では、表示パネル10の各画素8は、赤色(R)を表示する画素回路6と、緑色(G)を表示する画素回路6と、青色(B)を表示する画素回路6とを備えている。赤色(R)、緑色(G)、青色(B)を表示する画素回路6はそれぞれ、R副

10

20

30

40

50

画素、G副画素、B副画素として用いられ、以下において、R副画素6R、G副画素6G、B副画素6Bと記載することがある。一実施形態では、各画素8のR副画素6R、G副画素6G、B副画素6Bは、同一のゲート線4に接続されている。なお、各画素8は、赤色、緑色、青色以外の色を表示する追加の副画素を備えていてもよい。また、色の組合せはこれらに限定されない。

#### 【0014】

一実施形態では、表示ドライバ20は、ホスト40から画像データ12を受け取り、該画像データに応じた画像が表示パネル10に表示されるように表示パネル10を駆動する。一実施形態では、表示ドライバ20は、集積回路(ΙC)として構成される。

#### 【0015】

図3に示す一実施形態では、表示ドライバ20は、命令制御回路部21と、画像処理回路部22と、ソース線駆動回路部23と、タイミングコントローラ24と、パネルインターフェース回路部25とを備えている。

#### 【0016】

一実施形態では、命令制御回路部21は、ホスト40から受け取った画像データ12を画像処理回路部22に転送する。一実施形態では、命令制御回路部21は、インターフェースとして動作する。一実施形態では、命令制御回路部21は、ホストから受け取った制御データ13に応じて、タイミングコントローラ24を制御する。

#### 【0017】

一実施形態では、画像処理回路部22は、受け取った画像データ12に対してデジタル画像処理を行い、電圧データ14を生成する。生成される電圧データ14は、各画素8の各画素回路6に書き込むべき駆動電圧の電圧レベルを記述する。

#### 【0018】

一実施形態では、ソース線駆動回路部23は、画像処理回路部22から受け取った電圧データ14に応じてソース線5を駆動し、表示パネル10の各画素回路6に所望の電圧レベルを有する駆動電圧を書き込む。

#### 【0019】

一実施形態では、タイミングコントローラ24は、表示ドライバ20の各回路部のタイミング制御を行う。

#### 【0020】

一実施形態では、パネルインターフェース回路部25は、タイミングコントローラ24による制御の下、ゲート制御信号SOUTを生成し、生成したゲート制御信号SOUTを表示パネル10のゲート線駆動回路部2に供給する。

#### 【0021】

一実施形態による図3の構成では、画像処理回路部22は、デジタルガンマ回路部26と、補償回路部27と、出力電圧データ生成回路部28とを備えている。

#### 【0022】

一実施形態では、デジタルガンマ回路部26は、画像データ12から、規定されたガンマ特性で画像を表示するために各画素8の各画素回路6に書き込むべき駆動電圧の電圧レベルを指定する電圧データ15を生成する。

#### 【0023】

一実施形態では、デジタルガンマ回路部26で生成された電圧データ15を、電源配線7において発生する電圧降下が補償されるように補正することで、ソース線駆動回路部23に供給される電圧データ14が生成される。この電圧データ14は、実際に画素回路6を駆動するために用いられる。以下において、ソース線駆動回路部23に供給される電圧データ14が電圧降下が補償されたものであることを明確にするために、電圧データ14を補償後電圧データ14と記載する。補償後電圧データ14を用いて表示パネル10を駆動することで、画像のムラの発生が抑制される。

#### 【0024】

一実施形態では、補償回路部27は、電圧データ15の補正に用いられる補正值を生成

10

20

30

40

50

する。一実施形態では、補償回路部 27 により生成される補正值は、補償ゲイン 16 を含む。補正值と補償ゲイン 16 の生成については、後に詳細に説明する。

#### 【 0 0 2 5 】

一実施形態では、出力電圧データ生成回路部 28 は、補償回路部 27 によって生成された補正值に応じて、デジタルガンマ回路部 26 で生成された電圧データ 15 を補正して、補償後電圧データ 14 を生成する。一実施形態では、出力電圧データ生成回路部 28 は、デジタルガンマ回路部 26 で生成された電圧データ 15 に補償回路部 27 で生成された補償ゲイン 16 を乗じることで、ソース線駆動回路部 23 に供給される補償後電圧データ 14 を生成する。一実施形態では、補償後電圧データ 14 に記述された、各画素 8 の各画素回路 6 に供給すべき駆動電圧を指定する電圧値は、電圧データ 15 に記述された、各画素 8 の各画素回路 6 について指定された電圧値に、当該画素 8 について生成された補償ゲイン 16 の値を乗じた積として算出される。

#### 【 0 0 2 6 】

一実施形態では、表示ドライバ 20 又は画像処理回路部 22 は、他のデジタル画像処理を行う画像処理モジュール又は回路部を含んでいてもよい。一実施形態では、画像データ 12 に該他のデジタル画像処理を行うことで生成された画像データが、画像データ 12 の代わりにデジタルガンマ回路部 26 及び補償回路部 27 に供給されてもよい。

#### 【 0 0 2 7 】

上記のように、表示パネル 10 の電源配線 7 において発生する電圧降下を補償するような補正值、一実地形態では補償ゲイン 16 を用いることで、画像におけるムラの発生を有効に抑制する。以下では、一実施形態による補償回路部 27 による補正值（例えば補償ゲイン 16）の生成について説明する。

#### 【 0 0 2 8 】

図 4 に示すように、表示パネル 10 に単一の電源から電源電圧 E<sub>LVD</sub> が供給される場合では、表示パネル 10 に表示される画像の明るさによらず、ほぼ同様の明暗パターンが現れる。例えば、表示パネル 10 の電源に近い領域は明るく、遠い領域は暗くなる。

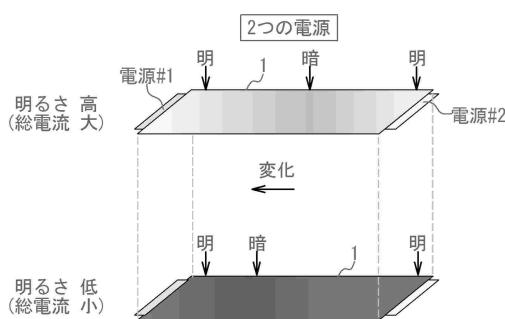

#### 【 0 0 2 9 】

一方、図 5 に示すように、表示パネル 10 に、複数の電源、例えば 2 つ又はそれ以上の電源から電源電圧 E<sub>LVD</sub> が供給される場合では、表示パネル 10 に表示される画像の明るさに依存して明暗パターンが変化し得る。この現象は、各電源の特性の相違に起因し得る。表示パネル 10 に表示される画像の明るさは、表示パネル 10 の画素 8 において消費される総電流に対応する。一実施形態において、「総電流」とは、表示パネル 10 の各画素 8 の各画素回路 6 において消費される電流の表示パネル 10 全体についての和である。表示パネル 10 に表示される画像の明るさが明るいほど、表示パネル 10 の画素 8 において消費される総電流は大きくなる。このように総電流が変化するとき、各電源の特性の相違に起因して各電源が異なる挙動を示すと、総電流の大きさに依存して明暗パターンが変化する。

#### 【 0 0 3 0 】

一実施形態では、補償回路部 27 は、表示パネル 10 に複数の電源、図 1 では 2 つの電源 11<sub>1</sub>、11<sub>2</sub> から電源電圧が供給される場合に、電源配線 7 において発生する電圧降下が適正に補償されるように、電圧データ 15 の補正に用いられる補正值、即ち、補償後電圧データ 14 の生成に用いられる補償ゲイン 16 を生成するように構成される。

#### 【 0 0 3 1 】

一実施形態では、補償回路部 27 は、表示パネル 10 の画素 8 において消費される総電流と各画素 8 の位置とに応じて、各画素 8 について補正值を生成する。一実施形態では、補償回路部 27 は、表示パネル 10 の画素 8 において消費される総電流のシミュレーション値を算出し、算出したシミュレーション値と画素 8 の位置とに応じて、画素 8 のそれについて補正值を生成する。出力電圧データ生成回路部 28 は、生成された補正值を用いてデジタルガンマ回路部 26 から受け取った電圧データ 15 を補正することで補償後電圧データ 14 を生成する。生成された補償後電圧データ 14 は、ソース線駆動回路部 23

に供給される。これによれば、電源配線 7 において発生する電圧降下を適正に補償することができる。

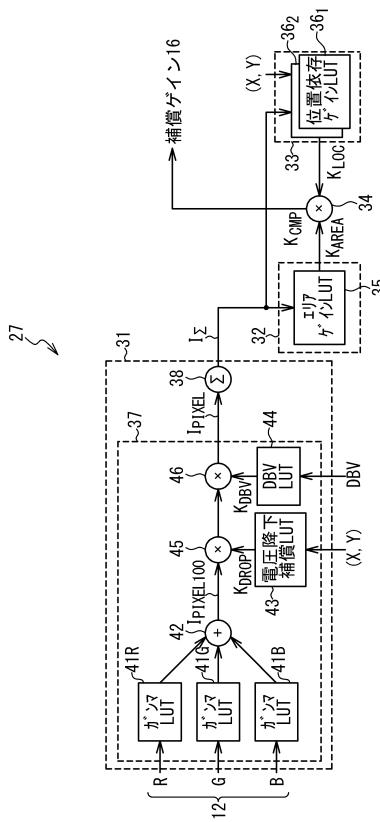

【 0 0 3 2 】

図 6 に示す一実施形態では、補償回路部 27 は、総電流算出回路部 31 と、エリアゲイン生成回路部 32 と、位置依存ゲイン生成回路部 33 と、補償ゲイン算出回路部 34 とを備えている。

【 0 0 3 3 】

一実施形態では、総電流算出回路部 31 は、表示パネル 10 の画素 8 において消費される総電流のシミュレーション値  $I_s$  を算出する。該画素 8 に含まれる画素回路 6、一実施形態では OLED 素子を流れる電流は、各画素 8 の輝度に対応しているので、表示パネル 10 の画素 8 の輝度の総和を表す値を、表示パネル 10 の画素 8 において消費される総電流のシミュレーション値として算出してもよい。シミュレーション値  $I_s$  の算出については、後に詳細に説明する。

10

【 0 0 3 4 】

一実施形態では、エリアゲイン生成回路部 32 は、総電流のシミュレーション値  $I_s$  からエリアゲイン  $K_{AREA}$  を生成する。一実施形態では、エリアゲイン生成回路部 32 は、総電流のシミュレーション値  $I_s$  とエリアゲイン  $K_{AREA}$  との対応関係を表す対応情報を有しており、該対応情報を用いてエリアゲイン  $K_{AREA}$  を生成してもよい。電源配線 7 において発生する電圧降下は、表示パネル 10 の画素 8 において消費される総電流に依存しており、エリアゲイン  $K_{AREA}$  は、電圧降下のうち総電流に依存する成分を補償するため 20 に用いられる。

20

【 0 0 3 5 】

一実施形態では、エリアゲイン生成回路部 32 は、エリアゲイン LUT (lookup table) 35 を備える。この場合、対応情報は、エリアゲイン LUT 35 の値として保持される。エリアゲイン生成回路部 32 は、シミュレーション値  $I_s$  の値を参照して、エリアゲイン LUT 35 に対してテーブルルックアップを行うことにより、エリアゲイン  $K_{AREA}$  を生成する。

【 0 0 3 6 】

他の実施形態では、エリアゲイン生成回路部 32 は、総電流のシミュレーション値  $I_s$  に対してデジタル演算を行って、エリアゲイン  $K_{AREA}$  を算出するように構成されてもよい。この場合、対応情報は、該デジタル演算に用いられる演算式を決める情報として、エリアゲイン生成回路部 32 に保持されてもよい。

30

【 0 0 3 7 】

一実施形態では、位置依存ゲイン生成回路部 33 は、対象の画素 8 の位置 (X, Y) に応じて位置依存ゲイン  $K_{LOC}$  を生成する。一実施形態では、位置依存ゲイン生成回路部 33 は、対象の画素 8 の位置 (X, Y) と位置依存ゲイン  $K_{LOC}$  との対応関係を表す対応情報を有し、該対応情報を用いて位置依存ゲイン  $K_{LOC}$  を生成する。

【 0 0 3 8 】

一実施形態では、位置依存ゲイン  $K_{LOC}$  と対象の画素 8 の位置 (X, Y) との対応関係は、総電流のシミュレーション値  $I_s$  に依存する。これによれば、電源配線 7 における電圧降下が、総電流の大きさに依存して明暗パターンが変化するようなものである場合についても、適正に電圧降下を補償し、画像におけるムラを有効に抑制することができる。

40

【 0 0 3 9 】

一実施形態では、位置依存ゲイン生成回路部 33 は、総電流の第 1 電流値について位置依存ゲイン  $K_{LOC}$  と対象の画素 8 の位置 (X, Y) との対応関係を表す第 1 対応情報と、総電流の第 2 電流値について位置依存ゲイン  $K_{LOC}$  と対象の画素 8 の位置 (X, Y) との対応関係を表す第 2 対応情報とを有し、該第 1 対応情報及び第 2 対応情報を用いて位置依存ゲイン  $K_{LOC}$  を生成する。一実施形態では、位置依存ゲイン生成回路部 33 は、下記の手順により位置依存ゲイン  $K_{LOC}$  を算出する。

( 1 ) 対象の画素 8 の位置 (X, Y) と第 1 対応情報とから、第 1 電流値に対応する位置

50

依存ゲインを生成する。

(2) 対象の画素8の位置(X, Y)と第2対応情報とから、第2電流値に対応する位置依存ゲインを生成する。

(3) 総電流のシミュレーション値I<sub>1</sub>に応じて第1電流値に対応する位置依存ゲインと第2電流値に対応する位置依存ゲインとを補間することで、最終的に算出すべき位置依存ゲインK<sub>LOC</sub>を算出する。

#### 【0040】

一実施形態では、第1電流値は、総電流のシミュレーション値I<sub>1</sub>が取り得る最大の電流値であり、第2電流値は、総電流のシミュレーション値I<sub>1</sub>が取り得る最小の電流値である。

10

#### 【0041】

一実施形態では、位置依存ゲイン生成回路部33は、位置依存ゲインLUT36<sub>1</sub>、36<sub>2</sub>を備える。位置依存ゲインLUT36<sub>1</sub>は、第1電流値について、対象の画素8の各位置(X, Y)に対応する位置依存ゲインK<sub>LOC</sub>を記述し、位置依存ゲインLUT36<sub>2</sub>は、第2電流値について、対象の画素8の各位置(X, Y)に対応する位置依存ゲインK<sub>LOC</sub>を記述する。この場合、上記の第1対応情報は、位置依存ゲインLUT36<sub>1</sub>の値として保持され、第2対応情報は、位置依存ゲインLUT36<sub>2</sub>の値として保持される。

#### 【0042】

一実施形態では、位置依存ゲイン生成回路部33は、下記の手順により位置依存ゲインK<sub>LOC</sub>を算出する。

20

(1) 対象の画素8の位置(X, Y)を参照して、位置依存ゲインLUT36<sub>1</sub>に対してテーブルルックアップを行うことにより、第1電流値に対応する位置依存ゲインを生成する。

(2) 対象の画素8の位置(X, Y)を参照して、位置依存ゲインLUT36<sub>2</sub>に対してテーブルルックアップを行うことにより、第2電流値に対応する位置依存ゲインを生成する。

(3) 総電流のシミュレーション値I<sub>1</sub>に応じて、第1電流値に対応する位置依存ゲインと第2電流値に対応する位置依存ゲインとを補間することで、最終的に算出すべき位置依存ゲインK<sub>LOC</sub>を算出する。

30

#### 【0043】

一実施形態では、補償ゲイン算出回路部34は、エリアゲインK<sub>AREA</sub>と位置依存ゲインK<sub>LOC</sub>とから補償ゲイン16を算出する。一実施形態では、補償ゲイン算出回路部34は、エリアゲインK<sub>AREA</sub>と位置依存ゲインK<sub>LOC</sub>との積K<sub>CMP</sub>として補償ゲイン16を算出する。

#### 【0044】

このようにして生成された補償ゲイン16は、出力電圧データ生成回路部28に送られ、補償後電圧データ14の生成に用いられる。一実施形態では、或る画素8に対応する補償後電圧データ14の生成において、当該画素8に対応する補償後電圧データ14は、当該画素8について算出された補償ゲイン16を当該画素8について算出された電圧データ15に乘じることで算出される。

40

#### 【0045】

一実施形態では、位置依存ゲイン生成回路部33は、互いに異なる電流値について、対象の画素8の各位置(X, Y)に対応する位置依存ゲインK<sub>LOC</sub>を記述する3以上のLUTを備える。この場合、位置依存ゲイン生成回路部33は、当該3以上のLUTのテーブルルックアップによって得られた位置依存ゲインの補間により、最終的に算出すべき位置依存ゲインK<sub>LOC</sub>を算出する。

#### 【0046】

また、上記のような構成の補償回路部27は、位置依存ゲインLUT36<sub>1</sub>、36<sub>2</sub>として同一内容のLUTを用いることで、単一の電源から電源電圧E<sub>L</sub>V<sub>DD</sub>が供給される表示パネル10における電圧降下の補償を行うことも可能である。

50

## 【0047】

一実施形態では、総電流算出回路部31は、画素電流算出回路部37と、累積回路部38とを備える。

## 【0048】

一実施形態では、画素電流算出回路部37は、対象の画素8の画像データ12と、該画素8の位置(X, Y)と、ディスプレイ輝度値DBVとから、各画素8において消費される電流のシミュレーション値 $I_{PIXEL}$ を算出する。ディスプレイ輝度値DBVは、表示パネル10に表示される画像の明るさを指定する値であり、一実地形態では、ユーザによる操作に応じてホスト40によって指定されてもよく、また、ホスト40によって指定されたディスプレイ輝度値に基づいて表示ドライバ20の内部で決定されてもよい。表示パネル10を観察するユーザにより、画像の明るさの調節が求められた場合、ユーザによる入力デバイスの操作に応じてディスプレイ輝度値DBVが調節されてもよい。各画素8の輝度は、該画素8に含まれる画素回路6、例えばOLED素子を流れる電流に対応しているので、各画素8の輝度を表す値を、各画素8において消費される電流のシミュレーション値 $I_{PIXEL}$ として算出してもよい。

10

## 【0049】

一実施形態では、画素電流算出回路部37は、ガンマLUT41R、41G、41Bと、加算器42と、電圧降下補償LUT43と、ディスプレイ輝度値LUT44と、乗算器45、46とを備える。

20

## 【0050】

一実施形態では、各画素8の画像データ12は、R副画素6Rの階調値Rと、G副画素6Gの階調値Gと、B副画素6Bの階調値Bとを含んでおり、ガンマLUT41R、41G、41Bと加算器42は、ディスプレイ輝度値DBVが特定値である場合、例えば最大値である場合において各画素8を流れる電流 $I_{PIXEL100}$ を階調値R、G、Bから算出するために用いられる。

30

## 【0051】

一実施形態では、ガンマLUT41Rは、ディスプレイ輝度値DBVが該特定値、例えば最大値である場合について、階調値RとR副画素6Rを流れる電流との対応関係を記述する。階調値Rを参照してガンマLUT41Rに対してテーブルルックアップを行うことにより、R副画素6Rを流れる電流が算出される。同様に、ガンマLUT41Gは、ディスプレイ輝度値DBVが該特定値である場合について、階調値GとG副画素6Gを流れる電流との対応関係を記述する。階調値Gを参照してガンマLUT41Gに対してテーブルルックアップを行うことにより、G副画素6Gを流れる電流が得られる。また、ガンマLUT41Bは、ディスプレイ輝度値DBVが該特定値である場合について、階調値BとB副画素6Bを流れる電流との対応関係を記述する。階調値Bを参照してガンマLUT41Bに対してテーブルルックアップを行うことにより、B副画素6Bを流れる電流が得られる。

30

## 【0052】

一実施形態では、加算器42は、ガンマLUT41R、41G、41Bを用いて算出されたR副画素6R、G副画素6G及びB副画素6Bを流れる電流を加算することで、ディスプレイ輝度値DBVが該特定値である場合において対象の画素8を流れる電流 $I_{PIXEL100}$ を算出する。

40

## 【0053】

一実施形態では、電圧降下補償LUT43は、画素8の位置(X, Y)と電圧降下補償ゲイン $K_{DROP}$ との対応関係を記述する。画素8の位置(X, Y)を参照して電圧降下補償LUT43に対してテーブルルックアップを行うことにより、電圧降下補償ゲイン $K_{DROP}$ が得られる。電圧降下補償ゲイン $K_{DROP}$ は、電源配線7における電圧降下が画素8を流れる電流に及ぼす影響を補償するために用いられる。

## 【0054】

一実施形態では、ディスプレイ輝度値LUT44は、ディスプレイ輝度値DBVとDB

50

V 依存ゲイン  $K_{DBV}$  との対応関係を記述する。ディスプレイ輝度値  $DBV$  を参照してディスプレイ輝度値  $LUT44$  に対してテーブルルックアップを行うことにより、 $DBV$  依存ゲイン  $K_{DBV}$  が得られる。 $DBV$  依存ゲイン  $K_{DBV}$  は、画素 8 を流れる電流のディスプレイ輝度値  $DBV$  に対する依存性を表す。

#### 【0055】

一実施形態では、乗算器 45、46 は、対象の画素 8 について算出された電流  $I_{PIXE}_L$  に、電圧降下補償ゲイン  $K_{DROP}$  及び  $DBV$  依存ゲイン  $K_{DBV}$  を乗じることで、各画素 8 を流れる電流のシミュレーション値  $I_{PIXEL}$  を算出する。

#### 【0056】

一実施形態では、累積回路部 38 は、表示パネル 10 の全画素 8 についてシミュレーション値  $I_{PIXEL}$  を累積することで総電流のシミュレーション値  $I$  を算出する。 10

#### 【0057】

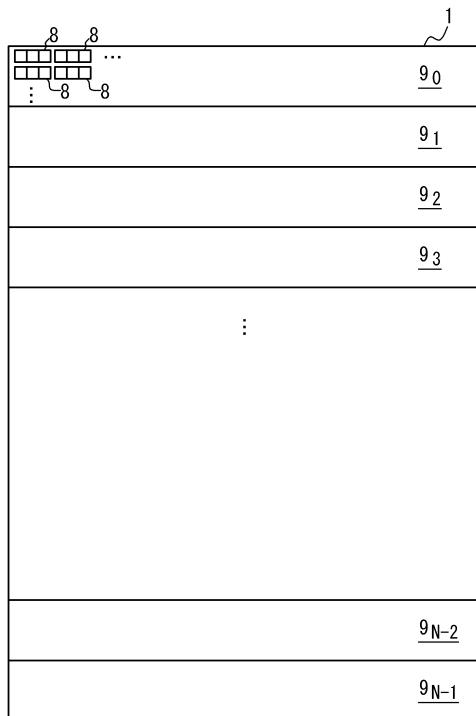

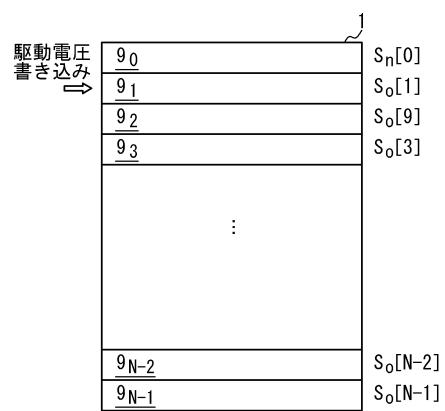

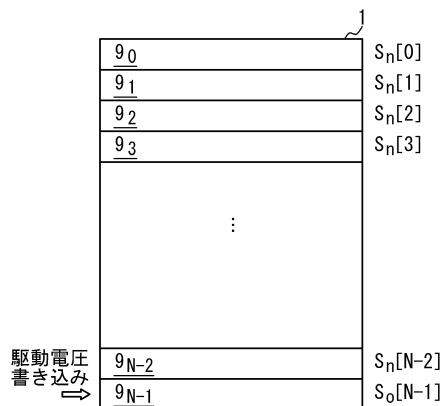

図 7 に示す一実施形態では、画素アレイ 1 が  $N$  個のセグメント  $9_0 \sim 9_{N-1}$  に区分され、累積回路部 38 がセグメント  $9_0 \sim 9_{N-1}$  のそれぞれに位置する画素 8 を流れる電流のシミュレーション値  $I_{PIXEL}$  の和  $s[0] \sim s[N-1]$  を保持するように構成される。ここで、 $N$  は、2 以上の整数であり、和  $s[i]$  は、セグメント  $9_i$  に位置する画素 8 を流れる電流のシミュレーション値  $I_{PIXEL}$  の和である。図 7 において、X 軸は、ゲート線 4 が延伸する方向に規定されており、X 軸の方向は、「水平方向」と呼ばれる。Y 軸は、ソース線 5 が延伸する方向に規定されており、Y 軸の方向は、「垂直方向」と呼ばれる。セグメント  $9_0 \sim 9_{N-1}$  は、垂直方向、即ち、ソース線 5 が延伸する方向に並んで配置されている。セグメント  $9_0 \sim 9_{N-1}$  のそれぞれは、複数の水平ラインを含んでいる。ここで、水平ラインとは、水平方向に並んだ画素 8、即ち、一のゲート線 4 に接続された画素 8 である。 20

#### 【0058】

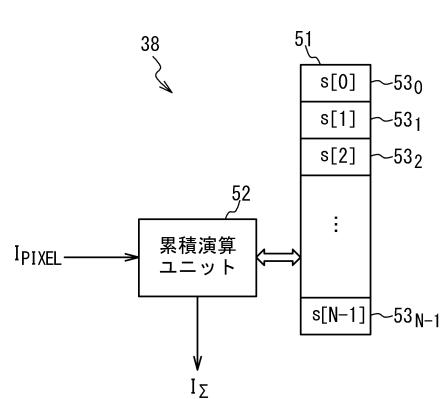

一実施形態では、図 8 に示すように、累積回路部 38 が、メモリ 51 と累積演算ユニット 52 とを備えている。一実施形態では、メモリ 51 は、セグメント  $9_0 \sim 9_{N-1}$  に対応するメモリ領域  $53_0 \sim 53_{N-1}$  を備えている。メモリ領域  $53_0 \sim 53_{N-1}$  は、それぞれ、セグメント  $9_0 \sim 9_{N-1}$  について算出されたシミュレーション値  $I_{PIXEL}$  の和  $s[0] \sim s[N-1]$  を保存するために用いられる。累積演算ユニット 52 は、画素電流算出回路部 37 から各画素 8 において消費される電流のシミュレーション値  $I_{PIXEL}$  を逐次に受け取り、セグメント  $9_0 \sim 9_{N-1}$  のそれぞれについてシミュレーション値  $I_{PIXEL}$  を累積することでシミュレーション値  $I_{PIXEL}$  の和  $s[0] \sim s[N-1]$  を算出する。累積演算ユニット 52 は、更に、メモリ領域  $53_0 \sim 53_{N-1}$  に保存された和  $s[0] \sim s[N-1]$  から、表示パネル 10 の画素 8 において消費される総電流のシミュレーション値  $I$  を算出する。 30

#### 【0059】

一実施形態では、或るフレーム期間（現フレーム期間）においてセグメント  $9_i$  に位置する画素 8 に駆動電圧を書き込むとき、累積回路部 38 は、該駆動電圧を指定する補償後電圧データ 14 の算出に用いられる総電流のシミュレーション値  $I$  を、メモリ領域  $53_0 \sim 53_{N-1}$  に保存されたシミュレーション値  $I_{PIXEL}$  の和  $s[0] \sim s[N-1]$  の和として算出する。ただし、駆動電圧の画素 8 への書き込みが現に行われているセグメント  $9_i$ 、及び、現フレーム期間において未だ駆動電圧が書き込まれていないセグメント  $9_{i+1} \sim 9_{N-1}$  については、前フレーム期間に表示された画像に対応する画像データ 12 から算出された和  $s[i] \sim s[N-1]$  が、総電流のシミュレーション値  $I$  の算出に用いられる。一方、現フレーム期間において既に駆動電圧が書き込まれているセグメント  $9_0 \sim 9_{i-1}$  については、現フレーム期間に表示される画像に対応する画像データ 12 から算出された和  $s[0] \sim s[i-1]$  が、総電流のシミュレーション値  $I$  の算出に用いられる。 40

#### 【0060】

以下では、前フレーム期間に表示された画像に対応する画像データ 12 から算出された

和  $s[0] \sim s[N-1]$  を、和  $s_o[0] \sim s_o[N-1]$  と表記し、現フレーム期間に表示される画像に対応する画像データ 12 から算出された和  $s[0] \sim s[N-1]$  を、和  $s_n[0] \sim s_n[N-1]$  と表記する。また、このようにして算出された総電流のシミュレーション値  $I$  を、セグメント  $9_i$  についての総電流のシミュレーション値  $I$  と呼ぶ。

【0061】

$i = 0$  である場合、即ち、図 9 A に示すように、現フレーム期間において、上端のセグメント  $9_0$  に位置する画素 8 に駆動電圧を書き込む場合、一実施形態では、セグメント  $9_0$  についての総電流のシミュレーション値  $I$  が、下記式(1)に従って算出される。

【数1】

$$I_{\Sigma} = \sum_{k=0}^{N-1} s_o[k] \quad (1)$$

10

【0062】

$i = 0$  である場合、即ち、図 9 B、図 9 C に示すように、現フレーム期間においてセグメント  $9_0$  以外のセグメント  $9_i$  に位置する画素 8 に駆動電圧を書き込む場合、一実施形態では、セグメント  $9_i$  についての総電流のシミュレーション値  $I$  は、下記式(2)に従って算出される。

20

【数2】

$$I_{\Sigma} = \sum_{k=0}^{i-1} s_n[k] + \sum_{k=i}^{N-1} s_o[k] \quad (2)$$

30

【0063】

例えば、 $i = 1$  である場合、即ち、図 9 B に示すように、上から 2 番目のセグメント  $9_1$  に位置する画素 8 に駆動電圧を書き込む場合、一実施形態では、セグメント  $9_1$  についての総電流のシミュレーション値  $I$  は、下記式(3)に従って算出され。

【数3】

$$I_{\Sigma} = \sum_{k=0}^0 s_n[k] + \sum_{k=1}^{N-1} s_o[k] \quad (3)$$

40

【0064】

また、図 9 C に示すように、下端に位置するセグメント  $9_{N-1}$  に位置する画素 8 に駆動電圧を書き込む場合、一実施形態では、セグメント  $9_{N-1}$  についての総電流のシミュレーション値  $I$  は、下記式(4)に従って算出される。

【数4】

50

$$I_{\Sigma} = \sum_{k=0}^{N-2} s_n[k] + \sum_{k=N-1}^{N-1} s_o[k] \quad (4)$$

10

## 【0065】

一実施形態では、累積回路部38は、更に、セグメント9<sub>0</sub>～9<sub>N-1</sub>のそれぞれについて、セグメント9<sub>0</sub>～9<sub>N-1</sub>の画素8を流れる電流のシミュレーション値PIXELの和s[0]～s[N-1]を算出する。一実施形態では、累積回路部38は、或るフレーム期間において、或るセグメント9<sub>i</sub>に位置する画素8を流れる電流のシミュレーション値PIXELの和s[i]を算出した場合、セグメント9<sub>i</sub>についての総電流のシミュレーション値I<sub>Σ</sub>を算出した後で、算出した和s[i]を対応するメモリ領域53<sub>i</sub>に書き込む。これは、上記のように、駆動電圧の画素8への書き込みが現に行われているセグメント9<sub>i</sub>については、前フレーム期間に表示された画像に対応する画像データ12から算出された和s<sub>o</sub>[i]が、セグメント9<sub>i</sub>についての総電流のシミュレーション値I<sub>Σ</sub>の算出に用いられるからである。

20

## 【0066】

このような動作によれば、累積回路部38に設けられるメモリの容量を抑制しながら、総電流のシミュレーション値I<sub>Σ</sub>を算出することができる。算出された総電流のシミュレーション値I<sub>Σ</sub>は、エリアゲイン生成回路部32に送られ、エリアゲインKAREAの生成に用いられる。一実施形態では、エリアゲイン生成回路部32は、算出された総電流のシミュレーション値I<sub>Σ</sub>を参照してエリアゲインLUT35に対してテーブルルックアップを行うことでエリアゲインKAREAを生成する。

## 【0067】

セグメント9<sub>0</sub>～9<sub>N-1</sub>について算出されたシミュレーション値PIXELの和s[0]～s[N-1]から、上記のようにして総電流のシミュレーション値I<sub>Σ</sub>が算出される場合、一実施形態では、エリアゲイン生成回路部32が、エリアゲインKAREAの生成において、対象の画素8のY軸方向（ソース線5が延伸する方向）における位置に応じた補間を行うように構成される。これは、セグメント9の境界におけるエリアゲインKAREAの変動を抑制するために有効である。一実施形態では、エリアゲイン生成回路部32は、セグメント9<sub>i</sub>について算出された総電流のシミュレーション値I<sub>Σ</sub>から生成したエリアゲインKAREA\_Cと、直前にセグメント9<sub>i-1</sub>（ただし、i=0である場合、セグメント9<sub>N-1</sub>）について算出された総電流のシミュレーション値I<sub>Σ</sub>から生成されたエリアゲインKAREA\_Pとを、対象の画素8のY軸方向における位置に応じて補間することで、対象の画素8の補償後電圧データ14の算出に最終的に用いられるエリアゲインKAREAを算出する。

30

## 【0068】

一実施形態では、エリアゲイン生成回路部32は、或るセグメント9<sub>i</sub>の上からj番目の水平ラインに位置する画素8について最終的に用いられるエリアゲインKAREAを、下記式（5）に従って算出する。

## 【数5】

40

50

$$K_{AREA} = \{K_{AREA\_P} \times (M - j) + K_{AREA\_C} \times j\} / M \quad (5)$$

ここで、Mは、セグメント $9_0 \sim 9_{N-1}$ のそれぞれに含まれる水平ラインの数である。

【0069】

図10に示す実施形態では、パワーマネジメントIC30の電源111が、2つの電源端子31、32に電源電圧ELVDDを供給している。このような構成においても、上述された手法による電圧降下の補償は有効である。図10に示す構成においても、パワーマネジメントIC30の出力から電源端子31、32までの配線抵抗の相違等の要因により、図1に示す2つの電源111、112から電源端子31、32に電源電圧ELVDDを供給する構成と同様に、表示パネル10に表示される画像の明るさに依存して明暗パターンが変化し得る。よって、図3に示す表示ドライバ20を、図10に示す構成の表示装置100に適用することは、電源配線7において生じる電圧降下に起因する画像のムラの抑制に有効である。表示パネル10に3以上の電源端子が設けられ、パワーマネジメントIC30の電源111が、該3以上の電源端子に電源電圧ELVDDを供給する場合についても同様である。

【0070】

以上には、本開示の様々な実施形態が具体的に記述されているが、本開示技術は、様々な変更と共に実施可能である。例えば、上記実施形態は、OLED表示パネル以外にも、各画素回路に電源電圧が供給されている構成の様々な表示パネルに適用可能である。

【符号の説明】

【0071】

|                    |            |    |

|--------------------|------------|----|

| 100                | ：表示装置      | 10 |

| 1                  | ：画素アレイ     |    |

| 2                  | ：ゲート線駆動回路部 |    |

| 31、32              | ：電源端子      | 30 |

| 4                  | ：ゲート線      |    |

| 5                  | ：ソース線      |    |

| 6                  | ：画素回路      |    |

| 6B                 | ：B副画素      |    |

| 6G                 | ：G副画素      |    |

| 6R                 | ：R副画素      |    |

| 7                  | ：電源配線      |    |

| 8                  | ：画素        |    |

| $9_0 \sim 9_{N-1}$ | ：セグメント     |    |

| 10                 | ：表示パネル     | 40 |

| 111、112            | ：電源        |    |

| 12                 | ：画像データ     |    |

| 13                 | ：制御データ     |    |

| 14                 | ：補償後電圧データ  |    |

| 15                 | ：電圧データ     |    |

| 16                 | ：補償ゲイン     |    |

| 20                 | ：表示ドライバ    |    |

| 21                 | ：命令制御回路部   |    |

| 22                 | ：画像処理回路部   |    |

| 23                 | ：ソース線駆動回路部 | 50 |

- 2 4 : タイミングコントローラ

2 5 : パネルインターフェース回路部

2 6 : デジタルガンマ回路部

2 7 : 補償回路部

2 8 : 出力電圧データ生成回路部

3 0 : パワーマネジメント I C

3 1 : 総電流算出回路部

3 2 : エリアゲイン生成回路部

3 3 : 位置依存ゲイン生成回路部

3 4 : 補償ゲイン算出回路部

3 5 : エリアゲイン L U T

3 6 1, 3 6 2 : 位置依存ゲイン L U T

3 7 : 画素電流算出回路部

3 8 : 累積回路部

4 0 : ホスト

4 1 R, 4 1 G, 4 1 B : ガンマ L U T

4 2 : 加算器

4 3 : 電圧降下補償 L U T

4 4 : ディスプレイ輝度値 L U T

4 5 : 乗算器

4 6 : 乗算器

5 1 : メモリ

5 2 : 累積演算ユニット

5 3 0 ~ 5 3 N - 1 : メモリ領域

10

20

30

40

【図面】

【図 1】

【図 2】

50

【図3】

〔 四 4 〕

10

20

【図5】

【 図 6 】

30

40

50

【図 7】

【図 8】

10

20

【図 9 A】

【図 9 B】

30

40

50

【図 9 C】

【図 10】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

F I

G 0 9 G 3/3275

H 0 5 B 33/14 A

H 1 0 K 59/00

ナプティクス・ジャパン合同会社内

合議体

審判長 濱野 隆

審判官 中塚 直樹

審判官 佐々木 祐

## (56)参考文献

米国特許出願公開第 2 0 1 0 / 0 1 4 9 1 6 2 ( U S , A 1 )

特開 2 0 0 9 - 1 5 1 0 4 2 ( J P , A )

特開 2 0 0 7 - 2 4 8 8 3 8 ( J P , A )

## (58)調査した分野 (Int.Cl. , D B 名)

G09G 3/00-3/38

H01L 51/50