(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7245016号**

**(P7245016)**

(45)発行日 令和5年3月23日(2023.3.23)

(24)登録日 令和5年3月14日(2023.3.14)

(51)国際特許分類

F I

|         |                  |         |        |

|---------|------------------|---------|--------|

| H 0 4 N | 25/76 (2023.01)  | H 0 4 N | 25/76  |

| H 0 4 N | 25/766 (2023.01) | H 0 4 N | 25/766 |

| H 0 4 N | 25/70 (2023.01)  | H 0 4 N | 25/70  |

請求項の数 17 (全21頁)

(21)出願番号 特願2018-178080(P2018-178080)

(22)出願日 平成30年9月21日(2018.9.21)

(65)公開番号 特開2020-53722(P2020-53722A)

(43)公開日 令和2年4月2日(2020.4.2)

審査請求日 令和3年9月17日(2021.9.17)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110003281

弁理士法人大塚国際特許事務所

小林 昌弘

東京都大田区下丸子3丁目30番2号

(72)発明者 キヤノン株式会社内

審査官 鈴木 明

最終頁に続く

(54)【発明の名称】 光電変換装置および撮像システム

**(57)【特許請求の範囲】****【請求項1】**

各々が複数の光電変換部を有する複数のブロックが複数の列および複数の行を構成するように配置された第1基板と、

前記複数のブロックの各々の前記複数の光電変換部から信号を読み出すための処理回路の少なくとも一部が配置された第2基板と、を備え、

前記処理回路は、前記複数のブロックの各々の前記複数の光電変換部を駆動するための複数の駆動信号線を駆動するように構成され、

前記複数の駆動信号線は、各々が前記複数のブロックのうち行方向に並んだ少なくとも2つのブロックに対して共通に割り当てられた複数の第1信号線と、各々が前記複数のブロックのうちの1つのブロックに対して個別に割り当てられた複数の第2信号線と、を含み、

前記処理回路は、互いに異なる露光時間を与えるための複数の露光時間信号線と、各々が前記複数の第2信号線のうちの1つの第2信号線に対応する複数の選択回路とを含み、

前記複数の選択回路の各々は、前記複数の露光時間信号線にそれぞれ供給される複数の露光時間信号から1つの露光時間信号を選択して前記複数の第2信号線のうち対応する第2信号線に供給する、

ことを特徴とする光電変換装置。

**【請求項2】**

前記複数の第1信号線は、前記第1基板に配置され、

前記処理回路は、前記第1基板に配置され前記複数の第1信号線を駆動する垂直走査回路を含む、

ことを特徴とする請求項1に記載の光電変換装置。

**【請求項3】**

前記複数の第2信号線は、前記第1基板および前記第2基板に配置され、

前記複数の選択回路は、前記第2基板に配置されている、

ことを特徴とする請求項1又は2に記載の光電変換装置。

**【請求項4】**

前記複数の露光時間信号線は、前記第2基板に配置されている、

ことを特徴とする請求項3に記載の光電変換装置。

10

**【請求項5】**

前記複数の選択回路を制御する複数の選択信号線が前記第2基板に配置されている、

ことを特徴とする請求項4に記載の光電変換装置。

**【請求項6】**

前記複数の露光時間信号線は、前記複数の行の各々が延びている方向に延びていて、

前記複数の選択信号線は、前記複数の列の各々が延びている方向に延びていて、

ことを特徴とする請求項5に記載の光電変換装置。

**【請求項7】**

前記処理回路は、前記複数の選択回路と前記複数の第2信号線との間に各々配置され、

前記複数の選択回路から出力される複数の信号の振幅を大きくする複数の電圧振幅変換回路を更に含む、

20

ことを特徴とする請求項1乃至6のいずれか1項に記載の光電変換装置。

**【請求項8】**

前記複数の電圧振幅変換回路は、前記第2基板に配置されている、

ことを特徴とする請求項7に記載の光電変換装置。

**【請求項9】**

前記複数のブロックの各々は、複数の単位回路を含み、各単位回路は、光電変換部と、電荷電圧変換部と、前記光電変換部から前記電荷電圧変換部に電荷を転送する転送部と、を含み、

前記第2信号線は、前記転送部を駆動する転送信号線を含む、

30

ことを特徴とする請求項1乃至8のいずれか1項に記載の光電変換装置。

**【請求項10】**

前記複数のブロックの各々は、複数の単位回路を含み、各単位回路は、光電変換部と、ゲインを変更するゲイン変更部と、を含み、

前記第2信号線は、前記ゲイン変更部にゲインを設定するゲイン設定信号線を含む、

ことを特徴とする請求項1乃至8のいずれか1項に記載の光電変換装置。

**【請求項11】**

前記複数の露光時間信号線は、第1露光時間を与えるための露光時間信号線と、前記第1露光時間より長い第2露光時間を与えるための露光時間信号線とを含む、

ことを特徴とする請求項1乃至10のいずれか1項に記載の光電変換装置。

40

**【請求項12】**

前記複数の露光時間信号線は互いに平行な方向に延在する部分を有する、

ことを特徴とする請求項1乃至11のいずれか1項に記載の光電変換装置。

**【請求項13】**

各々が複数の光電変換部を有する複数のブロックが複数の列および複数の行を構成するように配置された第1基板と、

前記複数のブロックの各々の前記複数の光電変換部から信号を読み出すための処理回路の少なくとも一部が配置された第2基板と、を備え、

前記処理回路は、前記複数のブロックの各々の前記複数の光電変換部を駆動するための複数の駆動信号線を駆動するように構成され、

50

前記複数の駆動信号線は、各々が前記複数のブロックのうち行方向に並んだ少なくとも 2 つのブロックに対して共通に割り当てられた複数の第 1 信号線と、各々が前記複数のブロックのうちの 1 つのブロックに対して個別に割り当てられた複数の第 2 信号線と、を含み、前記処理回路は、複数の伝達線と、各々が前記複数の第 2 信号線のうちの 1 つの第 2 信号線に対応する複数の選択回路とを含み、

前記複数の選択回路の各々は、前記複数の伝達線にそれぞれ供給される複数の駆動信号から 1 つの駆動信号を選択して前記複数の第 2 信号線のうち対応する第 2 信号線に供給し、

前記複数のブロックの各々は、複数の単位回路を含み、各単位回路は、光電変換部と、前記光電変換部で発生した電荷に応じた信号とランプ信号とを比較する比較回路と、を含み、

10

前記第 2 信号線は、前記ランプ信号を伝達する比較信号線を含む、

ことを特徴とする光電変換装置。

#### 【請求項 1 4】

各単位回路は、前記光電変換部をリセットするリセット部を更に含み、

前記第 1 信号線は、前記リセット部を駆動する信号線を含む、

ことを特徴とする請求項 9 乃至 1 3 のいずれか 1 項に記載の光電変換装置。

#### 【請求項 1 5】

前記複数の第 2 信号線は、第一の第 2 信号線と、第二の第 2 信号線とを含み、

前記第一の第 2 信号線は、前記複数のブロックのうちの 1 つのブロックにおける 1 つの行に配置された光電変換部に割り当てられ、前記 1 つのブロックのうち他の光電変換部には割り当てられておらず、

20

前記第二の第 2 信号線は、前記複数のブロックのうちの他の 1 つのブロックにおける 1 つの行に配置された光電変換部に割り当てられ、前記他の 1 つのブロックのうち他の光電変換部には割り当てられていない、

ことを特徴とする請求項 1 乃至 1 4 のいずれか 1 項に記載の光電変換装置。

#### 【請求項 1 6】

請求項 1 乃至 1 5 のいずれか 1 項に記載の光電変換装置と、

前記光電変換装置から出力される信号を処理する処理部と、

を備えることを特徴とする撮像システム。

#### 【請求項 1 7】

30

請求項 1 6 に記載の撮像システムと、

前記撮像システムから出力される信号を処理する集積回路と、

を備えることを特徴とする移動体。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

本発明は、光電変換装置および撮像システムに関する。

##### 【背景技術】

##### 【0 0 0 2】

特許文献 1 には、第 1 基板および第 2 基板を積層して構成されるイメージセンサが記載されている。第 1 基板には、複数の画素が搭載され、第 2 基板には、画素または画素群をそれぞれの積分時間に適合させるコンポーネントが搭載される。ここで、第 2 基板には、第 1 基板の作動信号を生成する行列を形成する複数の素子が配列され、各素子は、積分時間のパラメータを格納するメモリと、基準の積分時間ベースおよび積分時間のパラメータをもとに作動信号を生成する回路とを有する。各行の素子には、バスを介して、基準の積分時間ベースが供給される。

40

##### 【先行技術文献】

##### 【特許文献】

##### 【0 0 0 3】

【文献】特開 2 0 1 2 - 1 5 1 8 4 7 号公報

50

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

特許文献1に記載されたイメージセンサは、積分時間を画素または画素群ごとに設定することができる。しかし、該イメージセンサでは、第2基板の各素子に、積分時間のパラメータを格納するメモリと、基準の積分時間ベースおよび積分時間のパラメータをもとに作動信号を生成する回路とを備える必要があるので、構成が複雑化する。

**【0005】**

本発明は、複数の単位回路で構成されるブロック毎に個別の制御を行う機能をより単純な構成で実現するために有利な技術を提供する。

10

**【課題を解決するための手段】****【0006】**

本発明の1つの側面は、光電変換装置に係り、前記光電変換装置は、各々が複数の光電変換部を有する複数のブロックが複数の列および複数の行を構成するように配置された第1基板と、前記複数のブロックの各々の前記複数の光電変換部から信号を読み出すための処理回路の少なくとも一部が配置された第2基板と、を備え、前記処理回路は、前記複数のブロックの各々の前記複数の光電変換部を駆動するための複数の駆動信号線を駆動するように構成され、前記複数の駆動信号線は、各々が前記複数のブロックのうち行方向に並んだ少なくとも2つのブロックに対して共通に割り当てられた複数の第1信号線と、各々が前記複数のブロックのうちの1つのブロックに対して個別に割り当てられた複数の第2信号線と、を含み、前記処理回路は、互いに異なる露光時間を与えるための複数の露光時間信号線と、各々が前記複数の第2信号線のうちの1つの第2信号線に対応する複数の選択回路とを含み、前記複数の選択回路の各々は、前記複数の露光時間信号線にそれぞれ供給される複数の露光時間信号から1つの露光時間信号を選択して前記複数の第2信号線のうち対応する第2信号線に供給する。

20

**【発明の効果】****【0007】**

本発明によれば、複数の単位回路で構成されるブロック毎に個別の制御を行う機能をより単純な構成で実現するために有利な技術が提供される。

30

**【図面の簡単な説明】****【0008】**

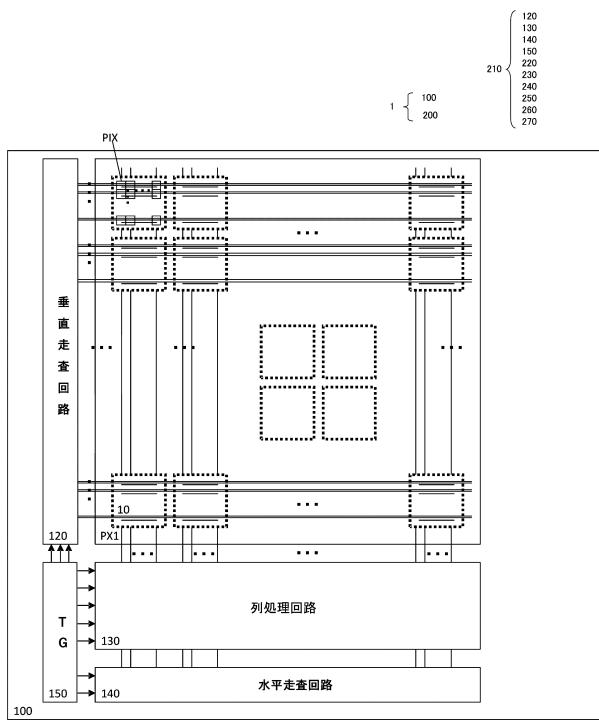

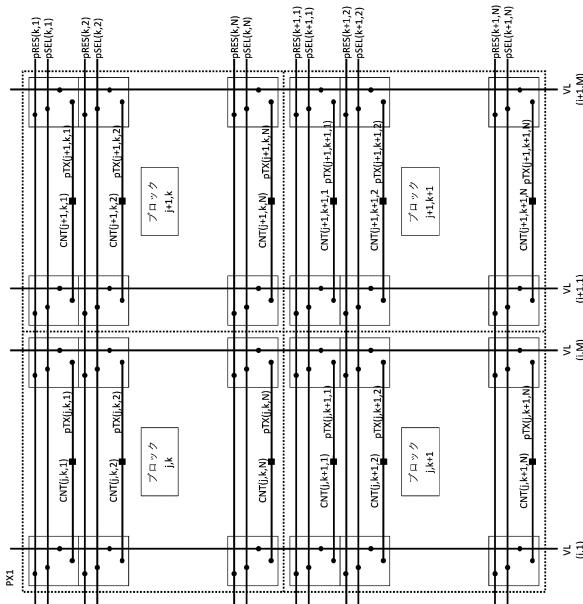

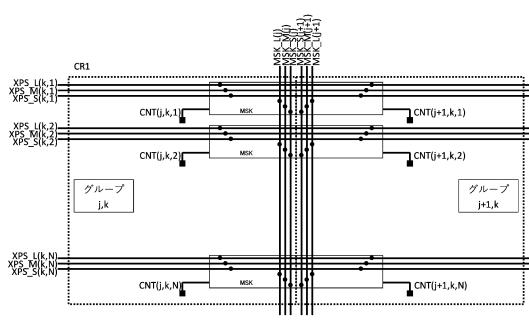

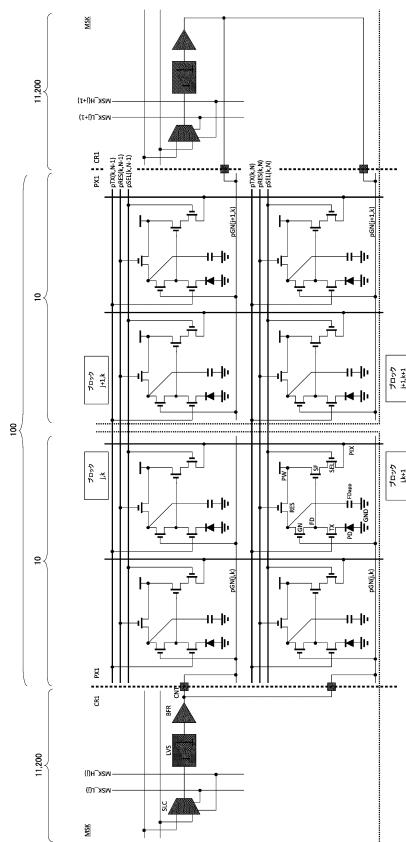

【図1A】本発明の第1実施形態の光電変換装置の一部を構成する第1基板の平面図。

【図1B】本発明の第1実施形態の光電変換装置の他の一部を構成する第2基板の平面図。

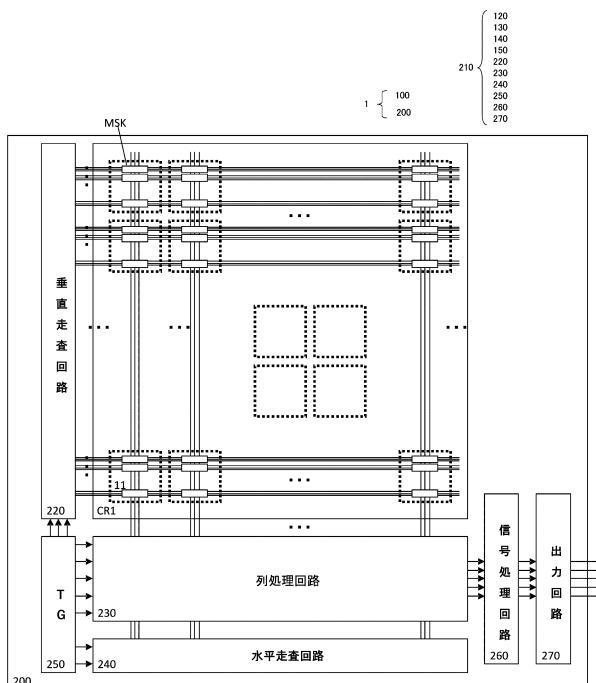

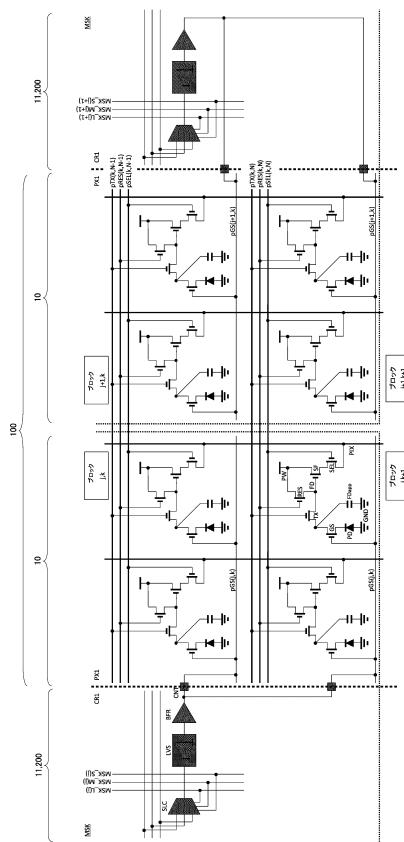

【図2】単位回路アレイ(画素アレイ)の構成例を示す図。

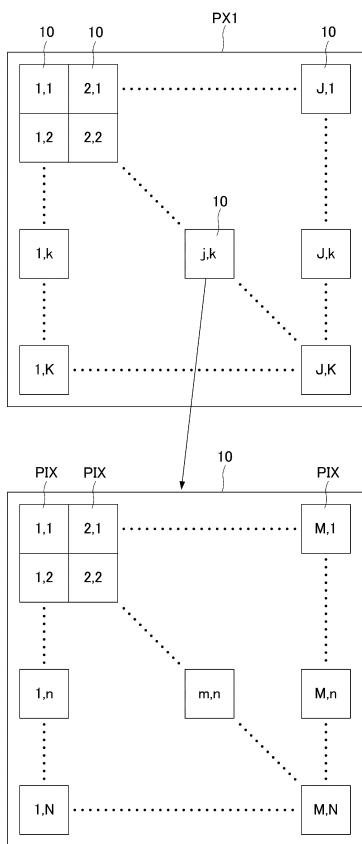

【図3】第1基板に配置された第1ブロックおよび第2基板に配置された第2ブロックの構成例、ならびに、第1ブロックと第2ブロックとの接続例を示す図。

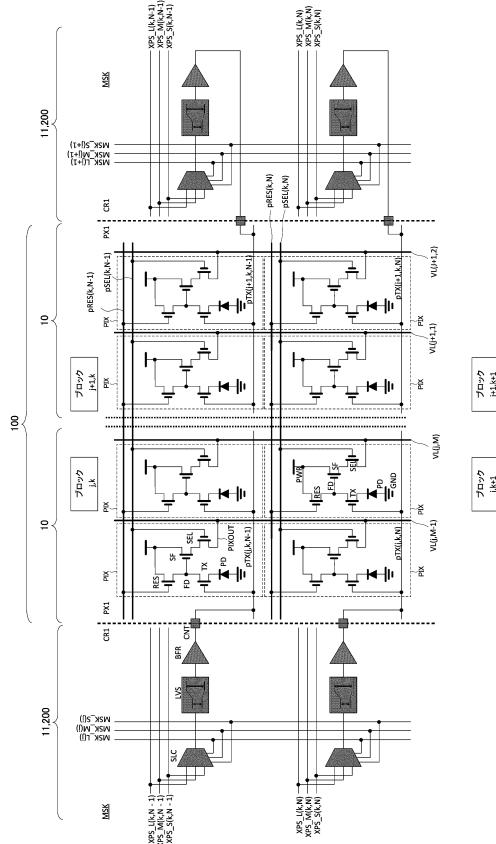

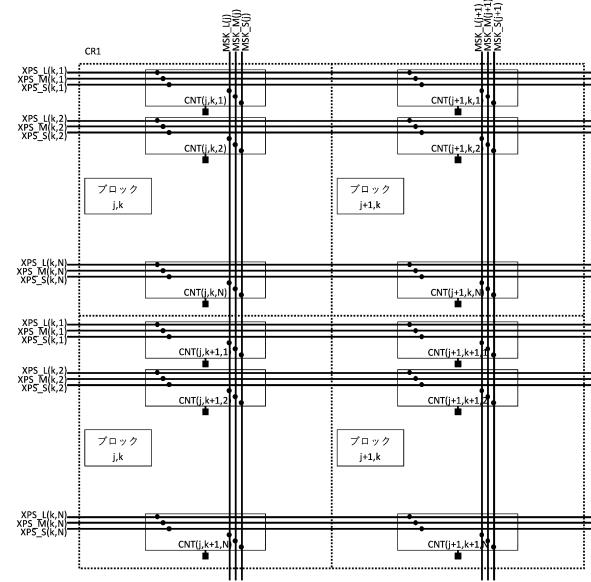

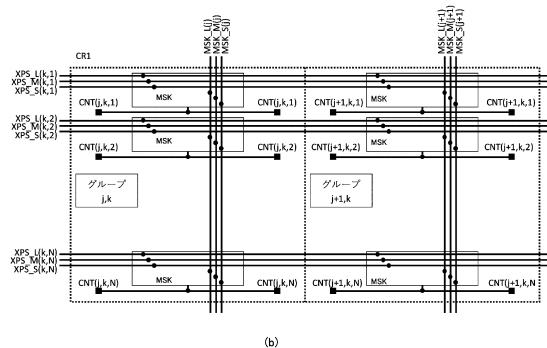

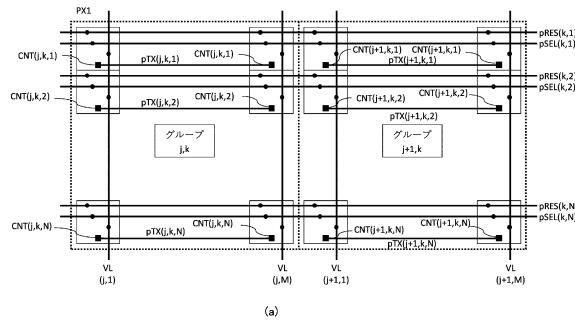

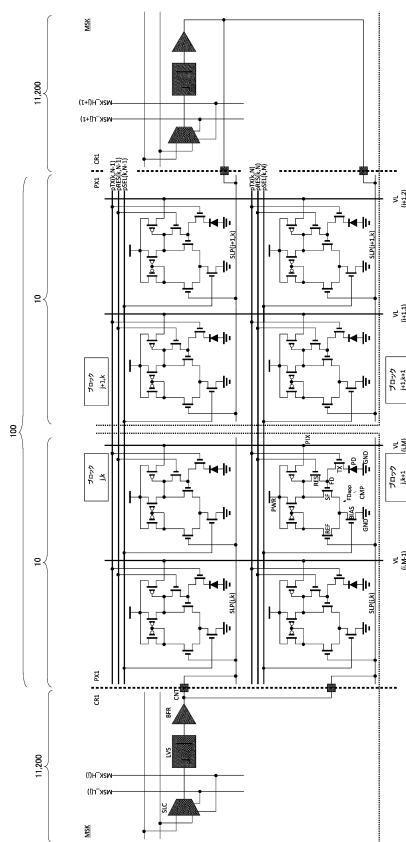

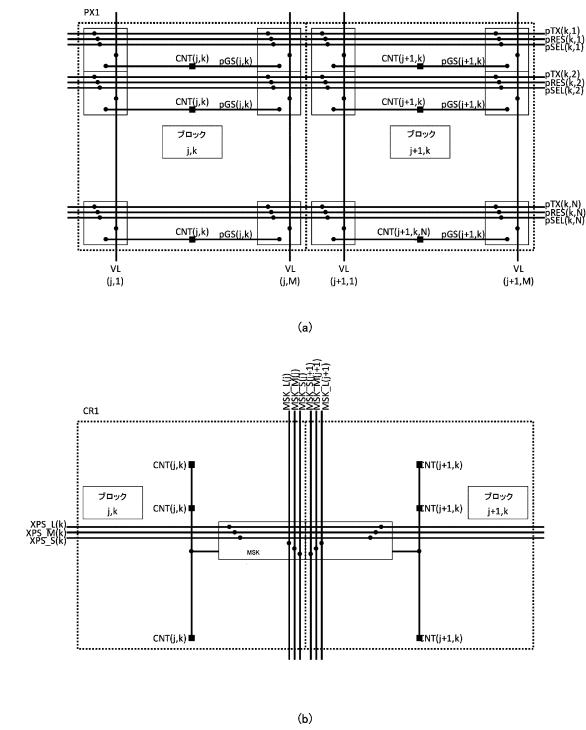

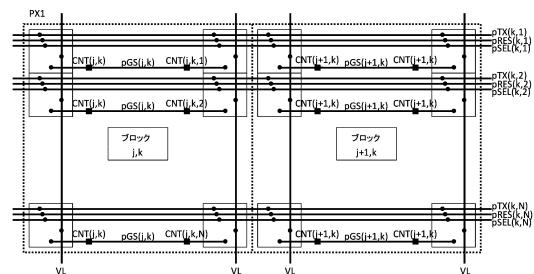

【図4A】第1基板の単位回路アレイにおける2列×2行の第1ブロックに配置される駆動信号線pTXを示す平面図。

【図4B】第2基板の補助回路アレイにおける2列×2行の第2ブロックに配置される露光時間信号線XPS\_\*および露光時間選択線MSK\_\*を示す平面図。

40

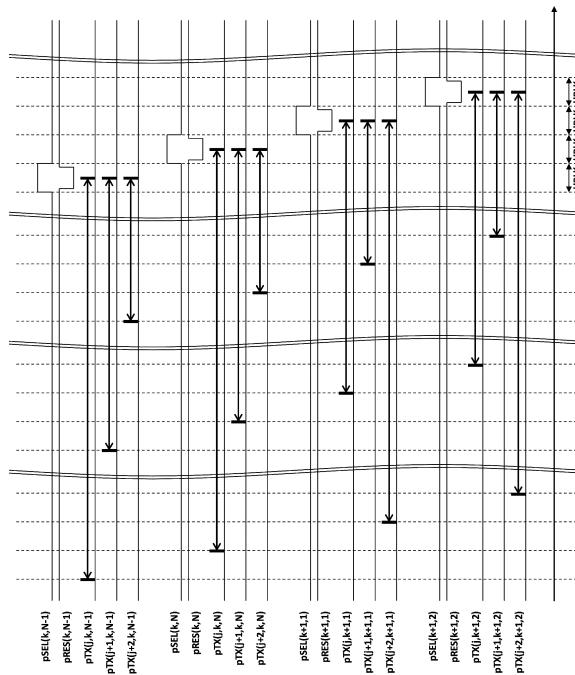

【図5】光電変換装置における駆動タイミングの一例を示す図。

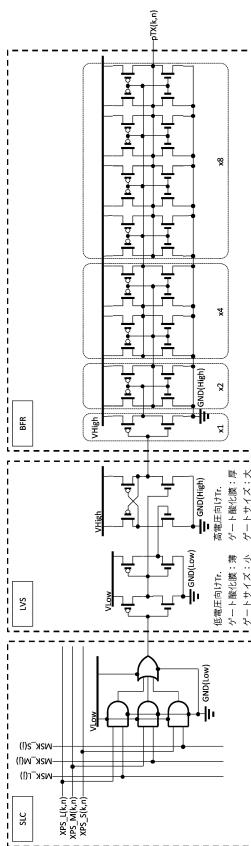

【図6】マスク回路の構成例を示す図。

【図7】本発明の第2実施形態の光電変換装置の構成の一部を示す図。

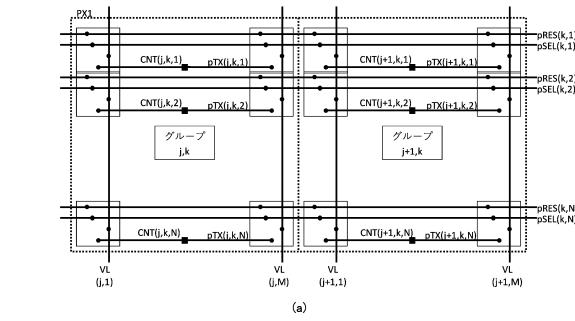

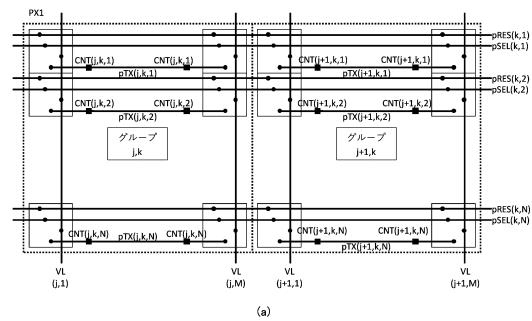

【図8】本発明の第2実施形態の光電変換装置の変形例の構成の一部を示す図。

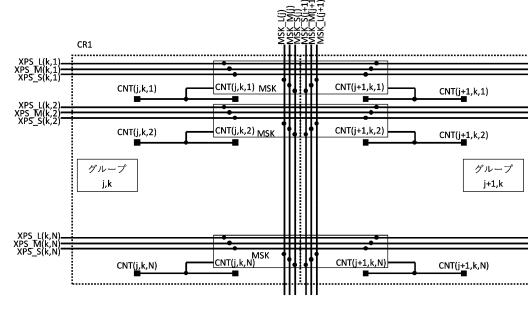

【図9】本発明の本発明の第3実施形態の光電変換装置の構成の一部を示す図。

【図10】本発明の第3実施形態の光電変換装置の変形例の構成の一部を示す図。

【図11】本発明の第4実施形態の光電変換装置の構成の一部の構成を示す図。

【図12】本発明の第5実施形態の光電変換装置の構成の一部の構成を示す図。

【図13】本発明の第6実施形態の光電変換装置の構成の一部の構成を示す図。

【図14】マスク回路の配置例を示す図。

50

- 【図15】マスク回路の他の配置例を示す図。

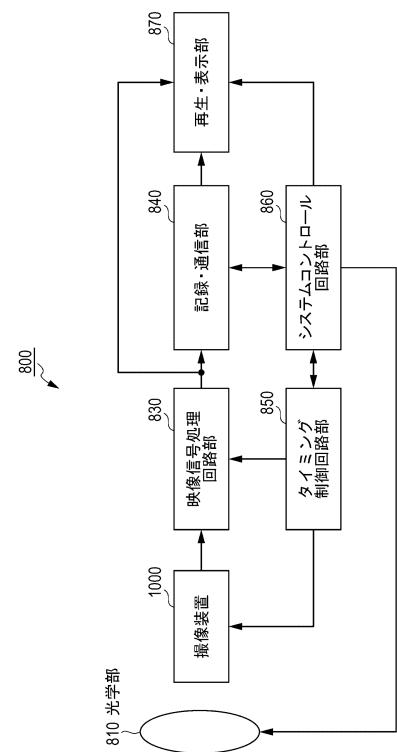

- 【図16】撮像システムの構成例を示す図。

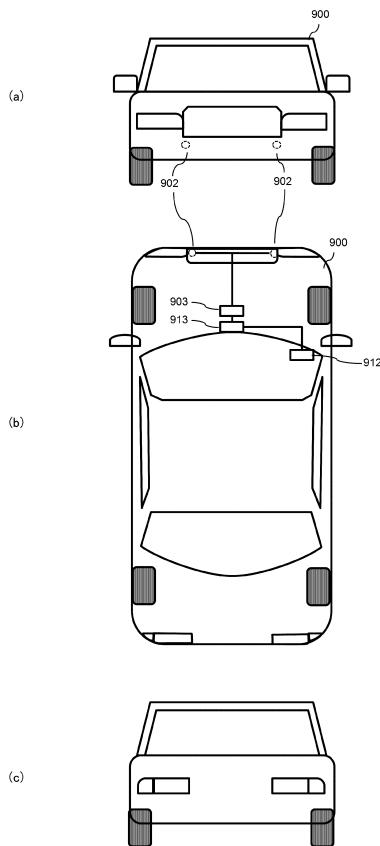

- 【図17】本発明の一実施形態の移動体を示す図。

- 【図18】本発明の一実施形態の移動体を示す図。

- 【発明を実施するための形態】

【0009】

以下、添付図面を参照しながら本発明をその例示的な実施形態を通して説明する。本発明に係る光電変換装置1は、例えば、MOSイメージセンサ等の固体撮像装置として、あるいは、距離画像または距離情報等を検出する測距装置として具体化されうるが、これらに限定されるものではない。

10

【0010】

図1Aは、本発明の第1実施形態の光電変換装置1の一部を構成する第1基板100の平面図であり、図1Bは、本発明の第1実施形態の光電変換装置1の他の一部を構成する第2基板200の平面図である。本発明の第1実施形態の光電変換装置1は、第1基板100と第2基板200とを積層して構成される。第1基板100の回路素子と第2基板100の回路素子とは、後述の接続部CNTを介して電気的に接続されうる。ここでは、第1基板100および第2基板200によって光電変換装置1が構成される例を説明するが、光電変換装置1は、3以上の基板の積層体で構成されてもよい。また、図1Aおよび図1Bは、光電変換装置1を構成する回路素子群を第1基板100および第2基板200に分配した一例を示すものに過ぎず、複数の基板への回路素子群の分配方法は、この例に限定されるものではない。例えば、図1Bに示された第2基板200に設けられた出力回路270は、図1Aの第1基板100に示された第1基板100に設けられてもよい。

20

【0011】

第1基板100には、複数の列(ブロック列)および複数の行(ブロック行)を構成するよう行列状に配列された複数の第1ブロック10(図1Aにおいて、点線の矩形で示された回路)が配置されうる。換言すると、各行(ブロック行)は、2以上の第1ブロック10で構成され、各列(ブロック列)は、2以上の第1ブロック10で構成されうる。各第1ブロック10は、複数の単位回路PIXを含みうる。各第1ブロック10における複数の単位回路PIXは、複数の列(単位回路列)および複数の行(単位回路行)を構成するように配置されうる。各単位回路PIXは、1つの光電変換部を含む。よって、単位回路アレイPX1は、複数の列および複数の行を構成するように複数の光電変換部が配列されたアレイであるものとしても理解される。なお、ブロック列および単位回路列がそれぞれ延びる方向は、互いに同じであり、ブロック行および単位回路行がそれぞれ延びる方向も、互いに同じである。行は、後述の垂直走査回路120、220によって駆動される信号が延びる方向であり、列は、後述の垂直信号線VLが延びる方向である。垂直走査回路120、220は、複数の行を順に走査あるいは選択する回路である。

30

【0012】

第2基板200には、複数の第1ブロック10の各々の複数の単位回路(画素)PIX(光電変換部)から信号を読み出すための処理回路210の少なくとも一部が配置されうる。第2基板200には、複数の列(ブロック列)および複数の行(ブロック行)を構成するよう行列状に配列された複数の第2ブロック11(図1Bにおいて、点線の矩形で示された回路)が配置されうる。換言すると、各行(ブロック行)は、2以上の第2ブロック11で構成され、各列(ブロック列)は、2以上の第2ブロック11で構成さうる。ここで、1つの第1ブロック10に1つの第2ブロック11が対応するように複数の第2ブロック11が配置されている。第2ブロック11は、それに対応する第1ブロック10の複数の単位回路PIX(光電変換部)からの信号の読み出しを行うための回路(読み出しを制御するための回路)を含む。複数の列(ブロック列)および複数の行(ブロック行)を構成するよう行列状に配列された複数の第2ブロック11は、補助回路アレイCR1を構成する。各第2ブロック11は、例えば、マスク回路MSKを含みうる。図1Aにおける隣接する第1ブロック10間の境界と、図1Bにおける隣接する第2ブロック11

40

50

間の境界とは、互いに同一であってもよいし、互いに異なってもよい。

#### 【0013】

複数の第1ブロック10の各々の複数の光電変換部から信号を読み出すための処理回路210は、例えば、第1、第2垂直走査回路120、220、第1、第2タイミング発生回路150、250、第1、第2列処理回路130、230を含みうる。また、複数の第1ブロック10の各々の複数の光電変換部から信号を読み出すための処理回路は、更に、第1、第2水平走査回路140、240、信号処理回路260および出力回路270を含みうる。

#### 【0014】

第1、第2垂直走査回路120、220は、単位回路アレイPX1に配置された複数の行（複数の単位回路PIXで構成されるアレイにおける行）を所定の順に選択し駆動する。この例では、第1、第2垂直走査回路120、220は、それぞれ第1基板100、第2基板200に配置される。第1、第2タイミング発生回路150、250は、第1、第2垂直走査回路120、220、第1、第2列処理回路130、230、第1、第2水平走査回路140、240にタイミング信号を供給する。

10

#### 【0015】

第1、第2列処理回路130、230は、単位回路PX1に配置された複数の行の単位回路PIXで構成される）のうち第1、第2垂直走査回路120、220によって選択された1行分の単位回路PIXから信号を読み出して処理する。第1、第2列処理回路130、230は、例えば、増幅回路、相関二重サンプリング回路、AD変換回路等を含みうる。この例では、第1、第2列処理回路130、230は、それぞれ第1基板100、第2基板200に配置される。

20

#### 【0016】

第1、第2水平走査回路140、240は、第1、第2列処理回路130、230によって処理された1行分の単位回路PX1の信号を所定の順に選択し信号処理回路260に提供する。この例では、第1、第2水平走査回路140、240は、それぞれ第1基板100、第2基板200に配置される。信号処理回路260は、第1、第2水平走査回路140、240によって選択された信号を処理し出力回路270に供給する。出力回路270は、信号処理回路260から供給される信号を所定の順に出力する。この例では、信号処理回路260および出力回路270は、第2基板200に配置されている。

30

#### 【0017】

図2には、単位回路アレイ（画素アレイ）PX1の構成例が示されている。第1基板100には、J個の列（ブロック列）およびK個の行（ブロック行）を構成するように行列状に配列された複数の第1ブロック10が配置されうる。換言すると、各行（ブロック行）は、J個の第1ブロック10で構成され、各列（ブロック列）は、K個の第1ブロック10で構成されうる。各ブロック10は、複数の単位回路PIXを含みうる。各第1ブロック10における複数の単位回路PIXは、M個の列およびN個の行を構成するように配置されうる。単位回路アレイPX1は、J×M個の列およびK×N個の行を構成するよう配列されたJ×M×K×N個の単位回路PIXで構成される。各単位回路PIXは、1つの光電変換部を含む。よって、単位回路アレイPX1は、J×M個の列およびK×N個の行を構成するよう配列されたJ×M×K×N個の光電変換部が配列された光電変換アレイであるものとしても理解される。

40

#### 【0018】

図3には、第1基板100に配置された第1ブロック10および第2基板200に配置された第2ブロック11の構成例、ならびに、第1ブロック10と第2ブロック11との接続例が示されている。ここでは、簡単化のために、2列×2行で配置された各第1ブロック10が示されている。図3において、各第2ブロック11は、マスク回路MSKを含む。第1ブロック10の入力端子と第2ブロック11との出力端子とは、接続部CNTを介して電気的に接続されている。

#### 【0019】

50

各単位回路（画素）P IXは、光電変換部PDと、電荷電圧変換部FDと、光電変換部PDから電荷電圧変換部FDに電荷を転送する転送部TXとを含みうる。また、各単位回路P IXは、電荷電圧変換部FDの電位に応じた信号を垂直信号線VL（を介して列処理回路130、230）に出力する増幅部SFを含みうる。また、各単位回路P IXは、電荷電圧変換部FDの電位をリセットするリセット部RESを含みうる。また、各単位回路P IXは、当該各単位回路P IXを選択状態にするための選択部SELを含みうる。転送部TX、増幅部SF、リセット部RES、選択部SELは、トランジスタで構成されうる。

#### 【0020】

転送部TXは、転送信号線p TXを介してゲート（制御端子）にアクティブルレベルの信号が供給されることによって導通（オン）し、光電変換部PDの電荷を電荷電圧変換部FDに転送する。ここで、単位回路アレイPX1における行を示すために、転送信号線p TXは、p TX(x, y, z)という形式でも表現される。リセット部RESは、リセット信号線p RESを介してゲート（制御端子）にアクティブルレベルの信号が供給されることによって導通し、電荷電圧変換部FDの電位をリセット電位にリセットする。ここで、単位回路アレイPX1における行を示すために、リセット信号線p RESは、p RES(x, y, z)という形式でも表現される。選択部SELは、選択信号線p SELを介してゲート（制御端子）にアクティブルレベルの信号が供給されることによって導通し、それが属する単位回路P IXを選択状態にする。選択信号線p SELは、単位回路アレイPX1における行を示すために、p SEL(x, y, z)という形式でも表現される。

#### 【0021】

転送信号線p TX、リセット信号線p RES、選択信号線p SELは、それぞれ単位回路P IX（光電変換部PD）を駆動するための複数の駆動信号線の1つである。複数の駆動信号線は、複数の第1信号線と、複数の第2信号線とを含みうる。複数の第1信号線は、例えば、複数の行にそれぞれ設けられた複数のリセット信号線p RES、および、複数の行にそれぞれ設けられた複数の選択信号線p SELを含みうる。複数の第2信号線は、複数のブロック10にそれぞれ設けられた複数の転送信号線p TXを含みうる。複数の第1信号線は、各々が複数のブロック10のうち行方向に並んだ少なくとも2つのブロック10（ここでは、1行分のブロック10）に対して共通に割り当てられた信号線である。複数の第2信号線は、各々が複数のブロック10のうちの1つのブロック10に対して個別に割り当てられた信号線である。

#### 【0022】

単位回路P IXの構成は、図3に示される構成に限定されるものではなく、例えば、複数の光電変換部PDによって電荷電圧変換部FDが共有されてもよい。あるいは、選択部SELを設ける代わりに、電荷電圧変換部FDのリセット電圧を制御することによって、単位回路P IXの選択／非選択が実現されてもよい。また、単位回路P IXを構成する回路素子の一部は、第2基板200に配置されてもよい。また、垂直信号線VLは、第2基板200に配置されてもよい。

#### 【0023】

第1実施形態の光電変換装置1では、光電変換部PDの露光時間（電荷蓄積時間）を各行（単位回路行）についてブロック10毎に制御する転送信号線p TXが設けられている。このような構成によれば、ブロック毎に適正な露光時間を設定することができる。例えば、被写体の明るい部分からの光線が入射するブロック10では、光電変換部PDがすぐに飽和してしまうことを避けるために、短い露光時間が設定されうる。一方、被写体の暗い部分からの光が入射するブロック10では、電荷の蓄積数を増やすために、長い露光時間が設定されうる。

#### 【0024】

この例では、例えば、各行のブロック10の数がJ個であれば、各行に対してJ個の転送信号線p TXが設けられる。他の観点において、単位回路アレイPX1におけるブロック10の数がJ×K個であり、ブロック10内の行数がNであれば、J×K×N個の転送信号線p TXが設けられる。ここで、2以上の光電変換部PD（あるいは単位回路P IX

10

20

30

40

50

) で 1 つのブロック 10 を構成することによって、転送信号線 p TX の個数を減らし、光電変換装置 1 の構成を簡単化することができる。

#### 【 0 0 2 5 】

ブロック 10 毎の露光時間の決定は、例えば、先行するフレーム(画像)における各ブロック 10 に対応する領域の輝度に基づいて、例えば、光電変換装置 1 の信号処理回路 260 によって行われる。あるいは、ブロック 10 毎の露光時間の決定は、光電変換装置 1 の外部の装置で行われ、その決定に基づく情報が光電変換装置 1 に提供されてもよい。また、先行するフレーム(画像)における各ブロック 10 に対応する領域の輝度に加えて、被写体が動体であるか、静止物であるかが考慮されてもよい。考慮される輝度は、ブロック毎の平均値であってもよいし、最頻値またはピーク値であってもよい。

10

#### 【 0 0 2 6 】

ここで、説明の便宜のために、複数のブロック 10 のうちの個別のブロック 10 を示すために、第 j 列、第 k 行に配置されたブロックを 10(j, k) のように座標を用いて表現する。駆動信号線については、第 k 行のブロック 10(\*, k) における第 n 行の単位回路 PIX の選択信号線 p SEL、リセット信号線 p SEL をそれぞれ p SEL(k, n)、p RES(k, n) のように表現する。同様に、ブロック 10(j, k) のうち第 n 行の転送信号線 p TX を p TX(j, k, n) のように表現する。また、垂直出力線 VL に関しては、j 列のブロック 10(j, \*) に属する画素のうち第 m 列の垂直出力線 VL を VL(j, m) のように表現する。また、ブロック 10(j, k) に設けられた接続部 CNT を CNT(j, k) のように表現する。

20

#### 【 0 0 2 7 】

図 4 A は、第 1 基板 100 の単位回路アレイ PX 1 における 2 列 × 2 行の第 1 ブロック 10 に配置される駆動信号線 p TX を示す図である。図 4 B は、第 2 基板 200 の補助回路アレイ CR 1 における 2 列 × 2 行の第 2 ブロック 11 に配置される露光時間信号線 XPS\_\* および露光時間選択線 MSK\_\* を示す図である。

#### 【 0 0 2 8 】

単位回路アレイ PX 1において、選択部 SEL を駆動する駆動信号線である選択信号線 p SEL、リセット部 RES を駆動する駆動信号線であるリセット信号線 p RES が行方向に並んだ複数のブロック 10 に跨って延びている。また、単位回路アレイ PX 1において、垂直出力線 VL が列方向に並んだ複数のブロック 10 に跨って延びている。一方、補助回路アレイ CR 1 において、複数の伝達線としての複数の露光時間信号線 XPS\_L、XPS\_M、XPS\_S で構成されるグループが、単位回路 PIX で構成される行毎に、行方向に延びるように配置されている。露光時間信号線 XPS\_L は、長露光用の信号線であり、露光時間信号線 XPS\_M は、中露光用の信号線であり、中露光用 XPS\_S は、短露光用の信号線である。また、ブロック 10 每に露光時間を選択するための露光時間選択線 MSK\_L、MSK\_M、MSK\_S で構成されるグループが、ブロック 11 で構成される列(ブロック例)毎に、列方向に延びるように配置されている。露光時間選択線 MSK\_L は、長露光用の選択線、露光時間選択線 MSK\_M は、中露光用の選択線、露光時間選択線 MSK\_S は、短露光用の選択線である。露光時間信号線 XPS\_\* と選択線 MSK\_\* とを使ってマスク回路 MSK において選択(生成)された駆動信号(転送信号)が接続部 CNT を介して転送信号線 p TX に供給される。つまり、この例では、電気的なノードとしては、マスク回路 MSK の出力端子と、そのマスク回路 MSK に対応する単位回路 PIX における転送部 TX の入力端子とが、転送信号線 p TX によって電気的に接続されている。

30

#### 【 0 0 2 9 】

露光時間は、光電変換部 PD から電荷電圧変換部 FD への電荷の転送タイミングを制御する転送信号線 p TX によって制御される。したがって、各行の単位回路 PIX(光電変換部 PD) の露光時間を各行(単位回路行)のブロック 10 每に制御するために、転送部 TX を制御する転送信号線 p TX が各行(単位回路行)のブロック 10 每に配置されている。選択信号線 p SEL およびリセット信号線 p RES は、各行の単位回路 PIX(光電変

40

50

換部 P D ) に対して共通に割り当てられている。

#### 【 0 0 3 0 】

また、単位回路 P I X における入出力信号の信号ノイズ比を高めるために、単位回路 P I X では、例えば第 2 基板 2 0 0 に配置される回路で用いられる電源電圧、電圧振幅高い電源電圧、電圧振幅が採用されうる。具体的には、図 4 A 、図 4 B に示される構成においては、単位回路 P I X を駆動するための駆動信号線 p S E L 、 p R E S 、 p T X と単位回路 P I X からの信号が出力される垂直出力線 V L は、高い電圧振幅で駆動されうる。一方で、単位回路 P I X を直接には駆動しない露光時間振動 X P S \_ \* および選択線 M S K \_ \* は、高い電圧振幅で駆動される必要はない。そこで、マスク回路 M S K において決定された駆動タイミングに従う転送信号を高い電圧振幅に変換し、その高い電圧振幅で転送信号線 p T X を駆動すればよい。

10

#### 【 0 0 3 1 】

また、転送信号線 p T X の電位が他の信号線との容量カップリングにより変動した場合、光電変換部 P D からの電荷漏れや光電変換部 P D への暗電流などのノイズ混入の原因となり、画質を低下させる可能性がある。この観点からも、転送部 T X を駆動する転送信号線 p T X は、複数のブロック 1 0 を跨がないように配置されることが好ましい。さらに、転送信号線 p T X の駆動タイミングを決定するための露光時間信号線 X P S \_ \* と選択信号線 M S K \_ \* とは低い電圧振幅で動作し、容量カップリングによる電圧変動を抑えることが好ましい。マスク回路 M S K は、以上の観点から、選択信号線 M S K \_ \* に従って露光時間信号線 X P S \_ \* を選択する選択回路 S L C の出力の振幅を電圧振幅変換回路 L V S で大きくし、更にバッファ回路 B F R でバッファリングした後に、転送信号線 p T X を駆動する。

20

#### 【 0 0 3 2 】

また、図 3 、図 4 A 、図 4 B に示すように複数の基板上の配線部に単位回路 P I X の駆動線を振り分けて配置することで、基板毎に電圧振幅に合わせて適切な製造方法を選択することができる。また、各単位回路 P I X 当たりの駆動信号線を減らし、配線間隔を広げることで、製造工程時のパーティクルなどによる短絡で欠陥が生じるリスクを低減しうる。

#### 【 0 0 3 3 】

図 5 には、光電変換装置 1 における駆動タイミングの一例が示されている。各行の単位回路 P I X の光電変換部 P D は、読み出しタイミング H B L K に先立って、転送部 T X を介してリセット部 R E S によってリセットされる。リセットされてから読み出しタイミング H B L K で転送部 T X によって光電変換部 P D から電荷電圧変換部 F D に電荷が転送されるまでの時間が各光電変換部 P D の露光時間（電荷蓄積時間）である。本実施形態では、各行においてブロック 1 0 毎に露光時間を設定することができる。

30

#### 【 0 0 3 4 】

ここで、ブロック 1 0 ( j , k ) の第 n 行の単位回路 P I X の露光時間 X P S と読み出タイミング H B L K をそれぞれ X P S ( j , k , n ) 、 H B L K ( j , k , n ) と定義する。図 5 においては、 H B L K ( j , k , n ) と H B L K ( j + 1 , k , n ) は同時刻であるため、 j , j + 1 を省略し、 H B L K ( k , n ) としている。

#### 【 0 0 3 5 】

ブロック 1 0 ( j , k ) 、 1 0 ( j + 1 , k ) 、 1 0 ( j + 2 , k ) がそれぞれ低輝度、中輝度、高輝度であると判定されたとする。この時、それぞれ露光時間は、 X P S ( j , k , n ) が最も長く ( t L ) 、 X P S ( j + 1 , k , n ) が中程度 ( t M ) 、 X P S ( j + 2 , k , n ) が最も短くなる ( t S ) 。例えば、 t L は約 1 6 . 6 ミリ秒 ( 約 1 / 6 0 秒 ) 、 t M は約 1 ミリ秒 ( 約 1 / 1 0 0 0 秒 ) 、 t S は約 6 2 . 5 マイクロ秒 ( 約 1 / 1 6 0 0 0 秒 ) である。第 k 行のブロック 1 0 ( \* , k ) のうち第 ( N - 1 ) 行の転送信号線 p T X ( j , k , N - 1 ) 、 p T X ( j + 1 , k , N - 1 ) 、 p T X ( j + 2 , k , N - 1 ) は、まず、それぞれ t L ( k , N - 1 ) 、 t M ( k , N - 1 ) 、 t S ( k , N - 1 ) で導通状態となる。この時、それぞれの光電変換部 P D がリセットされる。その後、 H B L K ( k , N - 1 ) でそれぞれの光電変換部 P D から信号の読み出しが行われる。第

40

50

N行の転送信号線  $p_{TX}(j, k, N)$ 、 $p_{TX}(j+1, k, N)$ 、 $p_{TX}(j+2, k, N)$ は、それぞれ  $t_L(k, N)$ 、 $t_M(k, N)$ 、 $t_S(k, N)$ で導通状態となる。次に、次の行のブロック  $10(j, k+1)$ 、 $10(j+1, k+1)$ 、 $10(j+2, k+1)$ がそれぞれ中輝度、低輝度、高輝度と判定されたとする。この時、転送信号線  $p_{TX}(j, k+1, 1)$ 、 $p_{TX}(j+1, k+1, 1)$ 、 $p_{TX}(j+2, k+1, 1)$ は、それぞれ  $t_M(k+1, 1)$ 、 $t_S(k+1, 1)$ 、 $t_L(k+1, 1)$ で導通状態となる。続いて、転送信号線  $p_{TX}(j, k+1, 2)$ 、 $p_{TX}(j+1, k+1, 2)$ 、 $p_{TX}(j+2, k+1, 2)$ は、それぞれ  $t_M(k+1, 2)$ 、 $t_S(k+1, 2)$ 、 $t_L(k+1, 2)$ でオン状態となる。このように、順次に露光動作（蓄積動作）および読み出動作がなされる。露光時間（電荷蓄積時間）は、これに限るものではなく、適宜に変更可能である。上記の例では、3種類の露光時間が設定されているが、4以上の露光時間が設定されてもよい。 $t_L$ 、 $t_M$ 、 $t_S$ は、上記の例より短い時間であってもよいし、長い時間であってもよい。

#### 【0036】

図5では、駆動信号  $p_{SEL}$ 、 $p_{RES}$ の駆動パルスが矩形の波形を有するように示されているが、実際には、駆動パルスは、配線抵抗や駆動素子の容量、カップリング容量等により、その波形が鈍る。波形の鈍りは、露光時間の線形性のずれや光電変換部PDからの信号の読み出動作時の電荷転送の速度などに影響を与える。露光時間の線形性のずれが大きい場合は、短いシャッタースピードで撮像装置を動作させることができず、電荷転送速度が遅い場合には光電変換装置1のフレームレートを速くすることができなくなる。すなわち、光電変換装置1の性能を高くすることが困難になる。したがって、図3の例のように、転送信号線  $p_{TX}$ によって駆動される複数の転送部  $TX$ を適切に駆動するために、バッファ回路  $BFR$ が転送信号線  $p_{TX}$ の近傍に設置されることが好ましい。

#### 【0037】

図6は、マスク回路  $MSK$ の構成例を示す図である。マスク回路  $MSK$ は、選択回路  $SLC$ 、電圧振幅変換回路  $LVS$ およびバッファ回路  $BFR$ を含みうる。選択回路  $SLC$ は、複数の露光時間信号線  $XPS_*$ に供給されている複数の露光時間信号のうち選択信号線  $MSK_*$ に供給されている選択信号によって選択される露光時間信号の波形を出力する。電圧振幅変換回路  $LVS$ は、選択回路  $SLC$ から出力される露光時間信号の電圧振幅を大きくした信号を出力する。バッファ回路  $BFR$ は、電圧振幅変換回路  $LVS$ から出力される信号の電圧振幅と同じ電圧振幅を有する露光時間信号を出力する。バッファ回路  $BFR$ は、それによって駆動される転送部  $TX$ の個数に応じた駆動能力を有する。

#### 【0038】

図6のマスク回路  $MSK$ は、複数の伝達線（露光時間信号線）からの1つの伝達線の選択、電圧振幅の変換、バッファリングの機能を有する。これらの機能が得られれば、他の構成が採用されてもよい。例えば、電圧振幅変換回路に関しては、高電圧振幅用と低電圧振幅用のGNDレベルとして、同一のものを用いてもよいし、GNDレベルに負電圧を用いるための回路を追加してもよい。また、バッファ回路に関しては、倍率が変更される。

#### 【0039】

第1実施形態によれば、ブロック  $10$ 毎に光電変換部PDの露光時間（電荷蓄積時間）を設定可能な光電変換装置1を単純な構成で実現することができる。つまり、第1実施形態によれば、複数の単位回路で構成されるブロック毎に個別の制御を行う機能をより単純な構成で実現することができる。例えば、複数の露光時間信号線（伝達線）にそれぞれ供給される複数の駆動信号から選択回路  $SLC$ によって選択された1つの駆動信号線によってブロック  $10$ 毎に露光時間を個別に制御することができる。このような構成によれば、ブロック  $10$ 毎に露光時間を示す情報を格納するメモリが不要である。また、第1実施形態によれば、ブロック  $10$ 毎に個別に露光時間信号線を設ける構成に比べて信号線の数を削減することができる。これは、例えば、信号線間のカップリング容量を低減し、設計の自由度を向上させたり、光電変換部の配列密度を向上させたりするため有利である。

#### 【0040】

10

20

30

40

50

図7は、本発明の第2実施形態の光電変換装置1の構成の一部を示す図である。第2実施形態は、第1実施形態の変形例を提供する。第2実施形態として言及しない事項は、第1実施形態に従う。図4A、図4Bに示された例では、バッファ回路BFRでバッファリングされ転送信号線PTX(j, k, n)に供給される転送信号は、ブロック10(j, k)の列方向に略中央で接続部CNTを介してブロック10(j, k)に供給される。ブロック(j, k)において、接続部CNTに近い単位回路PIXと、接続部CNTから離れた単位回路PIX(ブロック(j, k)の端部に位置する単位回路PIX)とでは、受信する転送信号の鈍り方が異なりうる。これは、転送信号線が伝達される経路の長さによる負荷(寄生容量)の差によって生じうる。

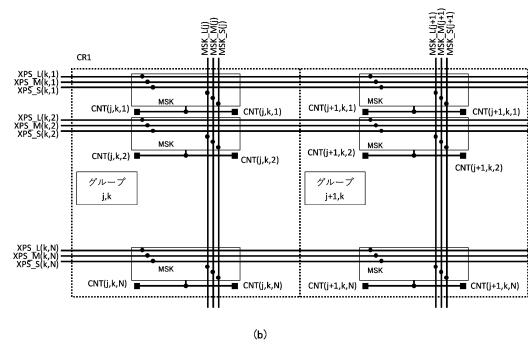

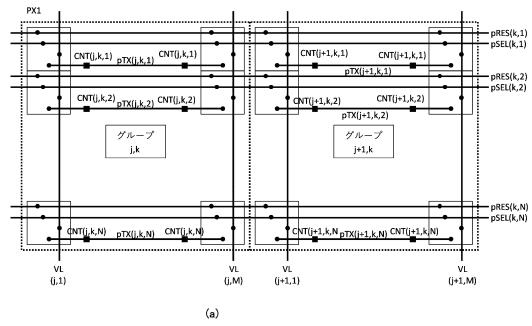

#### 【0041】

10

図7に示された第2実施形態では、ブロック10における接続部CNTの配置と個数が図4A、図4Bに示された第1実施形態と異なる。第2実施形態では、補助回路アレイCR1では、バッファ回路BFRから出た転送信号線が分岐し、ブロック(j, k)の端部でそれぞれ接続部CNTを介して、単位回路アレイPX1に接続される。このような構成により、寄生抵抗による転送信号の鈍りを低減することができる。図7に示された構成では、ブロック(j, k)の中央部で転送信号が最も鈍る可能性がある。図8には、図7に示された構成の変形例が示されている。図8に示された構成例では、2つの接続部CNTを中央部側に寄せることによって、転送信号の鈍りが均一化されている。

#### 【0042】

20

第2実施形態では、1つの信号を伝達するための信号経路が2つの分岐路に分離され、2つの接続部CNTが設けられた例が示されているが、そのような信号経路が3つ以上の分岐路に分岐され、3つ以上の接続部CNTが設けられてもよい。

#### 【0043】

30

図9は、本発明の第3実施形態の光電変換装置1の構成の一部を示す図である。第3実施形態は、第1実施形態の変形例を提供する。第3実施形態として言及しない事項は、第1実施形態に従う。上記のマスク回路MSKは、CMOS回路によって構成される。CMOS回路は、PMOSトランジスタおよびNMOSトランジスタで構成され、ウェルが形成された後にソース・ドレインが形成される。異なる電圧振幅を有する回路を形成する場合には、それぞれのためのウェルが形成される。したがって、マスク回路MSKは、複数のウェルを有しうる。ブロック10(n, k)毎にマスク回路MSKを個別に配置すると一つ一つのウェルが小さなりうる。すると、サージなどの影響でウェルの電位が変動し、画質が低下する可能性や、寄生サイリスタがオンすることで素子を破壊するような大電流が流れる可能性がある。

#### 【0044】

図9に示された第3実施形態では、行方向に隣接するブロック10の対において、マスク回路MSKを折り返し配置で構成することで、個々のウェルを大きくし、電位変動に強いウェルが形成される。更に、図10に示されるように、第3実施形態と第2実施形態とを組み合わせて、駆動パルスの鈍りを低減することも有効である。

#### 【0045】

40

ここでは行方向に隣接するブロック10の対においてマスク回路MSKを折り返し配置とする構成を述べたが、列方向に隣接するグループ1の対においてマスク回路MSKを折り返し配置としてもよい。また、折り返し配置ではなく、複数のブロック10内の複数のマスク回路MSKを共通のウェルを使って構成してもよい。

#### 【0046】

図11は、本発明の第4実施形態の光電変換装置1の構成の一部を示す図である。第4実施形態として言及しない事項は、第1乃至第3実施形態のいずれかに従う。第4実施形態では、単位回路(画素)PIXの構成が第1実施形態において例示した構成と異なる。第4実施形態として例示する単位回路PIXは、負荷容量FDappと、ゲインを変更するゲイン変更部GNとを有する。ゲイン変更部GNは、ゲイン設定信号線pGN(第2信号線)がアクティブルレベルに駆動されることに応じて電荷電圧変換部FDに付加容量FDa

50

$p_{pp}$  を接続する。これによって増幅部 SF の入力ノードの容量が増加し、単位回路 PIX のゲインが低下する。電荷電圧変換部 FD に付加容量 F Dapp が接続されゲインが低い状態（低ゲインモード）は、階調性を向上させるために有利である。逆に、ゲイン変更部 GN は、ゲイン設定信号線 p G N（第 2 信号線）がインアクティブルレベルに駆動されることに応じて電荷電圧変換部 FD から付加容量 F Dapp を切り離す。これによって増幅部 SF の入力ノードの容量が減少し、単位回路 PIX のゲインが増加する。電荷電圧変換部 FD の電位をリセット部 RES によってリセットするときは、リセット部 RES の他、ゲイン変更部 GN も導通状態にされる。ゲインの切り替えは、2 段階に限定されるものではなく、3 段階以上であってもよい。

#### 【0047】

10

また、第 4 実施形態では、マスク回路 MSK によって制御する対象が露光時間からゲイン変更部 GN に変更されている。ただし、2 種類のマスク回路を設けて、露光時間およびゲイン変更部 GN の双方が該 2 種類のマスク回路によってそれぞれ制御されてもよい。

#### 【0048】

第 4 実施形態では、第 1 実施形態のように単位回路 PIX の行毎に転送信号 p TX を制御する必要がないので、1 つのブロック 10 に 1 つのマスク回路 MSK が配置されればよい。第 4 実施形態においても、複数の単位回路で構成されるブロック毎に個別の制御を行う機能をより単純な構成で実現することができる。

#### 【0049】

20

図 12 は、本発明の第 5 実施形態の光電変換装置 1 の構成の一部を示す図である。第 5 実施形態として言及しない事項は、第 1 乃至第 4 実施形態のいずれかに従う。第 5 実施形態では、単位回路(画素) PIX がグローバルシャッター機能を有する。具体的には、第 5 実施形態の単位回路 PIX は、第 1 実施形態として例示された単位回路 PIX に対して、グローバルシャッタートランジスタ GS および保持部 ST が付加されている。また、第 5 実施形態では、マスク回路 MSK によって制御する対象が転送信号線 p TX からシャッター駆動線 p GS に変更され、シャッター駆動線 p GS の制御によってブロック 10 每に露光時間が制御される。

#### 【0050】

第 5 実施形態では、単位回路アレイ PX 1 の全ての行（換言すると、単位回路アレイ PX 1 の全ての単位回路 PIX）において、光電変換部 PD から保持部 ST に同時に電荷が転送される。保持部 ST に転送され保持部 ST によって保持された電荷は、行毎に転送部 TX によって電荷電圧変換部 FD に転送され、該電荷に対応する信号が行毎に読み出される。

30

#### 【0051】

第 1 実施形態では、露光時間を制御するために転送信号線 p TX を行毎（かつブロック 10 毎）に制御する必要があるが、第 5 実施形態は、露光時間がシャッター駆動線 p GS によって制御される。したがって、第 5 実施形態では、1 つのブロック 10 に対して 1 つのマスク回路 MSK が設けられればよく、回路構成を単純にすることができる。第 5 実施形態においても、複数の単位回路で構成されるブロック毎に個別の制御を行う機能をより単純な構成で実現することができる。

40

#### 【0052】

図 13 は、本発明の第 6 実施形態の光電変換装置 1 の構成の一部を示す図である。第 6 実施形態として言及しない事項は、第 1 乃至第 5 実施形態のいずれかに従う。第 6 実施形態では、単位回路(画素) PIX は、光電変換によって生じた信号と比較信号 S LP を比較する比較回路 CMP を有し、比較回路 CMP による比較の結果を垂直信号線 VL に出力する。また、第 6 実施形態では、マスク回路 MSK によって制御する対象が転送信号線 p TX から比較信号線 S LP に変更されている。比較回路 CMP は、例えば、増幅部 SF を構成の一部とする差動増幅回路で構成されうる。

#### 【0053】

第 6 実施形態の単位回路 PIX では、比較信号線 S LP の電圧が電荷電圧変換部 FD の

50

電圧よりも高い場合には垂直出力線 V L に L レベルが出力され、比較信号 S L P の電圧が電荷電圧変換部 F D の電圧よりも低くなると、垂直出力線 V L に H レベルが出力される。比較信号 S L P として単位時間毎に徐々に電圧が低下していくランプ信号を使うと、垂直出力線 V L が L レベルから H レベルに変化するまでの時間に基づいて、電荷電圧変換部 F D の電圧レベルをデジタル信号値に変換することができる。単位回路 P I X にメモリを設けて、該メモリにデジタル信号が一時的に格納されてもよい。

#### 【 0 0 5 4 】

複数のランプ信号を発生し、それらの間で単位時間毎の変化量を異ならせておくと、デジタル信号値に変換する際の変換精度を変化させることができる。例えば、単位回路 P I X が飽和するような変動の大きな信号の場合には、変換精度は低下するものの、より短い時間でデジタル信号値に変換することができるランプ信号が選択されうる。使用するランプ信号をブロック 1 0 毎に決定することにより、変換に要する時間を延ばさずにダイナミックレンジの広い電圧レベルを取り扱うことができる。10

#### 【 0 0 5 5 】

第 6 実施形態においても、複数の単位回路で構成されるブロック毎に個別の制御を行う機能をより単純な構成で実現することができる。

#### 【 0 0 5 6 】

図 1 4 は、1 つのブロック 1 0 に 1 つのマスク回路 M S K が設けられ、行方向に隣接するブロック 1 0 の対においてマスク回路 M S K が折り返し配置で構成された例を示している。図 1 5 は、1 つのブロック 1 0 に 1 つのマスク回路 M S K が設けられ、行方向および列方向に隣接するブロック 1 0 の組においてマスク回路 M S K が折り返し配置で構成された例を示している。20

#### 【 0 0 5 7 】

次に、図 1 6 を参照しながら本発明の実施形態に係る撮像システムについて説明する。撮像システム 8 0 0 は、例えば、光学部 8 1 0 、撮像装置 1 0 0 0 、映像信号処理回路部 8 3 0 、記録・通信部 8 4 0 、タイミング制御回路部 8 5 0 、システムコントロール回路部 8 6 0 、及び再生・表示部 8 7 0 を含む。撮像装置 1 0 0 0 は、上記の各実施形態で説明した光電変換装置 1 が適用された固体撮像装置である。

#### 【 0 0 5 8 】

レンズなどの光学系である光学部は 8 1 0 、被写体からの光を撮像装置 1 0 0 0 の、複数の画素が 2 次元状に配列された画素アレイに結像させ、被写体の像を形成する。撮像装置 1 0 0 0 は、タイミング制御回路部 8 5 0 からの信号に基づくタイミングで、画素部に結像された光に応じた信号を出力する。30

#### 【 0 0 5 9 】

撮像装置 1 0 0 0 から出力された信号は、映像信号処理部である映像信号処理回路部 8 3 0 に入力され、映像信号処理回路部 8 3 0 が、プログラムなどによって定められた方法に従って、入力された電気信号に対して A D 変換などの処理を行う。映像信号処理回路部での処理によって得られた信号は画像データとして記録・通信部 8 4 0 に送られる。記録・通信部 8 4 0 は、画像を形成するための信号を再生・表示部 8 7 0 に送り、再生・表示部 8 7 0 に動画や静止画像が再生・表示させる。記録通信部は、また、映像信号処理回路部 8 3 0 (処理部) からの信号を受けて、システムコントロール回路部 8 6 0 とも通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。40

#### 【 0 0 6 0 】

システムコントロール回路部 8 6 0 は、撮像システムの動作を統括的に制御するものであり、光学部 8 1 0 、タイミング制御回路部 8 5 0 、記録・通信部 8 4 0 、及び再生・表示部 8 7 0 の駆動を制御する。また、システムコントロール回路部 8 6 0 は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラムなどが記録される。また、システムコントロール回路部 8 6 0 は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内で供給する。具体的な例としては、読み出す行やリセットする行の変更、電子ズームに伴う画角の変更や、電子防振

に伴う画角のずらしなどである。

#### 【0061】

タイミング制御回路部850は、制御部であるシステムコントロール回路部860による制御に基づいて撮像装置1000及び映像信号処理回路部830の駆動タイミングを制御する。

#### 【0062】

図17には、上記の各実施形態の撮像装置が組み込まれた移動体の一例としての自動車900の構成が示されている。図17(a)は前方から見た自動車900、図17(b)は上方から見た自動車900、図17(c)を後方から見た自動車900を模式的に示している。自動車900は、上記の各実施形態で説明した光電変換装置1が適用された撮像装置902を備える。また、自動車900は、特定用途向け集積回路(ASIC: Application Specific Integrated Circuit)903、警報装置912、主制御部913を備える。

10

#### 【0063】

警報装置912は、撮像装置902、車両センサ、制御ユニットなどから異常を示す信号を受けたときに、運転手へ向けて警告を行う。主制御部913は、撮像装置902、車両センサ、制御ユニットなどの動作を統括的に制御する。なお、自動車900が主制御部913を備えていなくてもよい。この場合、撮像装置902、車両センサ、制御ユニットが通信ネットワークを介して制御信号の送受を行う(例えばCAN規格)。

20

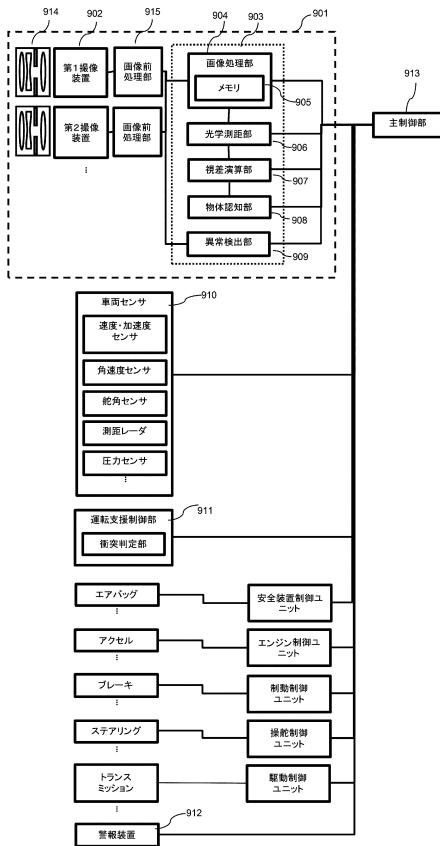

#### 【0064】

図18は、自動車900のシステム構成を示すブロック図である。自動車900は、第1の撮像装置902と第2の撮像装置902を含む。第1の撮像装置902と第2の撮像装置902とによってステレオカメラが構成されている。撮像装置902には、光学部914により被写体像が結像される。撮像装置902から出力された画素信号は、画像前処理部915によって処理され、そして、特定用途向け集積回路903に伝達される。画像前処理部915は、光信号VSとノイズ信号VNとの差分を求める演算や、同期信号付加などの処理を行う。

30

#### 【0065】

特定用途向け集積回路903は、画像処理部904、光学測距部906、視差演算部907、物体認知部908、異常検出部909を備えうる。画像処理部904は、画素信号を処理して画像信号を生成する。また、画像処理部904は、画像信号の補正や欠陥補完を行う。画像処理部904は、画像信号を一時的に保持するメモリ905を備える。メモリ905は、既知の撮像装置902の欠陥画素の位置を記憶していてもよい。前述の演算部20は、画像処理部904が有していてもよい。

#### 【0066】

光学測距部906は、画像信号を用いて被写体の合焦または測距を行う。視差演算部907は、視差画像の被写体照合(ステレオマッチング)を行う。物体認知部908は、画像信号を解析して、自動車、人物、標識、道路などの被写体の認知を行う。

40

#### 【0067】

異常検出部909は、撮像装置902の故障、あるいは、誤動作を検知する。異常検出部909は、故障や誤動作を検知した場合には、主制御部913へ異常を検知したこと示す信号を送る。異常検出部909は、前述の演算部20の機能を有していてもよい。

#### 【0068】

自動車900は、車両センサ910および運転支援部911を含む。車両センサ910は、速度・加速度センサ、角速度センサ、舵角センサ、測距レーダ、圧力センサなどを含みうる。

#### 【0069】

運転支援部911は、衝突判定部を含む。衝突判定部は、光学測距部906、視差演算部907、物体認知部908からの情報に基づいて、物体との衝突可能性があるか否かを判定する。光学測距部906や視差演算部907は、対象物までの距離情報を取得する距

50

離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。

#### 【0070】

運転支援部911が他の物体と衝突しないように自動車900を制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。

#### 【0071】

自動車900は、さらに、エアバッグ、アクセル、ブレーキ、ステアリング、トランスミッション等の走行に用いられる駆動部を具備する。また、自動車900は、それらの制御ユニットを含む。制御ユニットは、主制御部913の制御信号に基づいて、対応する駆動部を制御する。

10

#### 【0072】

上記のように自動車900に本発明の撮像装置あるいは撮像システムを搭載して運転支援や自動運転を行う場合、複数の撮像装置あるいは撮像システムが用いられる。この時、撮像装置あるいは撮像システム毎に温度信号出力部の素子の特性がばらついていると、撮像装置間で想定する温度が異なり、運転支援や自動運転が正常に行えないことがある。また、自動車900の運転支援や自動運転では、正確性が要求されるため、温度測定に要求される制度も高い。

20

#### 【0073】

本発明の撮像装置あるいは撮像システムを用いることで、温度測定の精度を向上させることができ、運転支援や自動運転の正確性を高めることができる。

#### 【0074】

本実施例に用いられた撮像システムは、自動車に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

#### 【符号の説明】

#### 【0075】

30

1：光電変換装置、100：第1基板、200：第2基板、210：処理回路、pRES：リセット信号線（第1信号線）、pSEL：選択信号線（第1信号線）、pTX：転送信号線（第2信号線）、10：ブロック

40

50

【図面】

【図 1 A】

【図 1 B】

10

20

30

40

【図 2】

【図 3】

50

【図 4 A】

【図4B】

【 図 5 】

【 四 6 】

10

20

30

40

50

【図7】

【図8】

10

20

【図9】

【図10】

30

40

50

【図 1 1】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

- (56)参考文献      特開2010-021697(JP,A)

特開2012-151847(JP,A)

特開2012-100219(JP,A)

特開2006-148284(JP,A)

- (58)調査した分野 (Int.Cl., DB名)

H04N 25/00 - 25/79