(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년02월28일

(11) 등록번호 10-1121600

(24) 등록일자 2012년01월29일

(51) Int. Cl.

H01L 21/336 (2006.01)

(21) 출원번호 10-2007-7015942

(22) 출원일자(국제출원일자) 2005년10월04일

심사청구일자 2010년09월30일

(85) 번역문제출일자 2007년07월12일

(65) 공개번호 10-2007-0087046

(43) 공개일자 2007년08월27일

(86) 국제출원번호 PCT/US2005/035505

(87) 국제공개번호 WO 2006/065324

국제공개일자 2006년06월22일

(30) 우선권주장

11/012,553 2004년12월15일 미국(US)

(56) 선행기술조사문현

EP0305975 A

US20040099888 A1

US5869856 A

전체 청구항 수 : 총 53 항

심사관 : 나용수

(54) 소스 영역 아래에 매립된 N-타입 및 P-타입 영역들을 가지는 트랜지스터들 및 그 제조 방법들

### (57) 요 약

본 발명은 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀을 제공한다. MESFET의 단위 셀은 소스, 드레인 및 게이트를 포함한다. 게이트는 소스와 드레인 사이에서 n-타입 도전성 채널층 상에 배치된다. p-타입 도전성 영역은 소스 아래에서 제공되고 드레인을 향하여 신장하는 일단을 가진다. p-타입 도전성 영역은 n-타입 도전성 채널층과 이격되고 소스와 전기적으로 연결된다. n-타입 도전성 영역은 소스 아래의 p-타입 도전성 영역 상에 제공되고 p-타입 도전성 영역의 상기 일단을 지나서 신장하지 않으면서 드레인 영역을 향하여 신장한다. 관련된 MESFETs의 제조방법들이 또한 제공된다.

대 표 도 - 도1

## 특허청구의 범위

### 청구항 1

금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀로서,

소스 영역, 드레인 영역, 및 상기 소스 영역과 상기 드레인 영역 사이에 있고 n-타입 도전성 채널층 상에 있는 게이트 콘택을 가지는 MESFET;

상기 소스 영역 아래에 있고 상기 드레인 영역을 향하여 신장하는 일단(end)을 가지고, 상기 n-타입 도전성 채널층과 이격되어 있고 상기 소스 영역과 전기적으로 연결되는 p-타입 도전성 영역; 및

상기 p-타입 도전성 영역의 상기 일단을 지나서 신장하지 않으면서 상기 드레인 영역을 향하여 신장하고 상기 소스 영역의 아래에 상기 소스 영역으로부터 이격되고 상기 p-타입 도전성 영역 상에 있는 n-타입 도전성 영역

을 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

### 청구항 2

제1항에 있어서, 상기 p-타입 도전성 영역은 제1 p-타입 도전성 영역을 포함하고, 상기 단위 셀은 상기 제1 p-타입 도전성 영역의 캐리어 농도보다 작은 캐리어 농도를 가지고, 상기 제1 p-타입 도전성 영역의 상기 일단에서 상기 게이트 콘택의 아래까지 신장하는 제2 p-타입 도전성 영역을 더 포함하여, 상기 제1 및 제2 p-타입 도전성 영역들이 상기 n-타입 도전성 영역의 두 개의 표면들 상에 제공되는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

### 청구항 3

제2항에 있어서,

상기 게이트 콘택은 제1 측벽 및 제2 측벽을 가지고, 상기 제1 측벽은 상기 소스 영역에 인접하고 상기 제2 측벽은 상기 드레인 영역에 인접하며; 그리고

상기 제2 p-타입 도전성 영역은 상기 제1 p-타입 도전성 영역의 상기 일단에서 상기 게이트 콘택의 상기 제2 측벽을 지나서 신장하지 않으면서 상기 게이트 콘택의 상기 제2 측벽까지 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

### 청구항 4

제2항에 있어서,

상기 게이트 콘택은 제1 측벽 및 제2 측벽을 가지고, 상기 제1 측벽은 상기 소스 영역에 인접하고 상기 제2 측벽은 상기 드레인 영역에 인접하며; 그리고

상기 제2 p-타입 도전성 영역은 상기 제1 p-타입 도전성 영역의 상기 일단에서 상기 게이트 콘택의 상기 제1 및 제2 측벽들 사이까지 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

### 청구항 5

제1항에 있어서, 상기 p-타입 도전성 영역을 노출하고 상기 소스 영역에 인접하는 콘택 비아 홀을 더 포함하고, 상기 n-타입 도전성 영역은 상기 p-타입 도전성 영역의 상기 일단을 지나서 신장하지 않으면서 상기 p-타입 도전성 영역의 상기 노출된 부분에서부터 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

### 청구항 6

제1항에 있어서, 기판을 더 포함하고, 상기 MESFET는 상기 기판 상에 있고 상기 n-타입 도전성 영역은 상기 기판의 내부로(into) 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

### 청구항 7

제6항에 있어서, 상기 n-타입 도전성 영역은 상기 기판의 내부로 500Å에서 1500Å까지 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 8**

제7항에 있어서, 상기 n-타입 도전성 영역은 상기 기판의 내부로 1000Å보다 작게 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 9**

제6항에 있어서, 상기 기판은 실리콘 카바이드(SiC) 기판을 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 10**

제1항에 있어서, 베피층을 더 포함하고, 상기 MESFET는 상기 베피층 상에 제공되고 상기 n-타입 도전성 영역은 상기 베피층의 내부로 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 11**

제10항에 있어서, 상기 n-타입 도전성 영역은 상기 베피층의 내부로 500Å에서 1500Å까지 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 12**

제11항에 있어서, 상기 n-타입 도전성 영역은 상기 베피층의 내부로 1000Å보다 작게 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 13**

제1항에 있어서, 상기 n-타입 도전성 영역은 상기 p-타입 도전성 영역에 의해 공핍되는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 14**

제1항에 있어서:

상기 게이트 콘택은 제1 측벽 및 제2 측벽을 가지고, 상기 제1 측벽은 상기 소스 영역에 인접하고 상기 제2 측벽은 상기 드레인 영역에 인접하며; 그리고

상기 n-타입 도전성 영역은 상기 소스 영역의 아래에서부터 상기 게이트 콘택의 상기 제1 측벽을 지나서 신장하지 않으면서 상기 게이트 콘택의 상기 제1 측벽까지 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 15**

제1항에 있어서, 상기 n-타입 도전성 영역은 드레인 콘택의 아래까지 신장하지 않으면서 소스 콘택 및/또는 상기 소스 영역의 아래에서부터 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 16**

제1항에 있어서, 실리콘 카바이드(SiC) 기판을 더 포함하고, 상기 p-타입 도전성 영역은 상기 SiC 기판 상에 배치되고, 상기 n-타입 도전성 채널층은 n-타입 도전성 SiC를 포함하고, 상기 p-타입 도전성 영역은 p-타입 도전성 SiC를 포함하고, 상기 n-타입 도전성 영역은 n-타입 도전성 SiC를 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 17**

제1항에 있어서, 기판을 더 포함하고, 상기 p-타입 도전성 영역은 상기 기판 상에 배치되고, 상기 기판은 갈륨 아세나이드(GaAs) 또는 갈륨 나이트라이드(GaN)를 포함하고, 상기 채널층은 GaAs 또는 GaN을 포함하고, 상기 p-타입 도전성 영역은 p-타입 도전성 GaAs 또는 p-타입 도전성 GaN을 포함하고 그리고 상기 n-타입 도전성 영역은 n-타입 도전성 GaAs 또는 n-타입 도전성 GaN을 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 18**

제1항에 있어서, 상기 n-타입 도전성 채널층의 캐리어 농도보다 더 큰 캐리어 농도를 가지고 상기 소스 영역 및 상기 드레인 영역을 정의하는 상기 n-타입 도전성 채널층 내의 SiC의 주입된 n-타입 도전성 영역들을 더 포함하고, 상기 소스 및 드레인 영역들 상에 제1 및 제2 오믹 콘택들이 각각 배치되는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 19**

제1항에 있어서, 상기 게이트 콘택은 상기 n-타입 채널층 내에(in) 배치되는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 20**

제19항에 있어서, 상기 게이트 콘택은 상기 n-타입 채널층 내의 단일 리세스에 배치되는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 21**

제19항에 있어서, 상기 게이트 콘택은 상기 n-타입 채널층 내의 이중 리세스에 배치되는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 22**

제1항에 있어서, 상기 MESFET는 실리콘 카바이드(SiC) MESFET를 포함하고, 상기 n-타입 도전성 채널층은 n-타입 도전성 SiC의 채널층을 포함하고, 상기 p-타입 도전성 영역은 p-타입 도전성 SiC 영역을 포함하고 그리고 상기 n-타입 도전성 영역은 n-타입 도전성 SiC 영역을 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀.

**청구항 23**

금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법으로서,

소스 영역, 드레인 영역, 및 상기 소스 영역과 상기 드레인 영역 사이에 있고 n-타입 도전성 채널층 상에 있는 게이트 콘택을 가지는 MESFET을 형성하는 단계;

상기 소스 영역 아래에 있고 상기 드레인 영역을 향하여 신장하는 일단을 가지고, 상기 n-타입 도전성 채널층과 이격되어 있고 상기 소스 영역과 전기적으로 연결되는 p-타입 도전성 영역을 형성하는 단계; 및

상기 p-타입 도전성 영역의 상기 일단을 지나서 신장하지 않으면서 상기 드레인 영역을 향하여 신장하고 상기 소스 영역의 아래에 상기 소스 영역으로부터 이격되고 상기 p-타입 도전성 영역 상에 있는 n-타입 도전성 영역을 형성하는 단계

를 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

**청구항 24**

제23항에 있어서, 상기 p-타입 도전성 영역을 형성하는 단계는 제1 p-타입 도전성 영역을 형성하는 단계를 포함하고, 상기 방법은 상기 제1 p-타입 도전성 영역의 캐리어 농도보다 작은 캐리어 농도를 가지고, 상기 제1 p-타입 도전성 영역의 상기 일단에서 상기 게이트 콘택의 아래까지 신장하는 제2 p-타입 도전성 영역을 형성하는 단계를 더 포함하여, 상기 제1 및 제2 p-타입 도전성 영역들이 상기 n-타입 도전성 영역의 두 개의 표면들 상에 제공되는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

**청구항 25**

제24항에 있어서,

상기 게이트 콘택은 제1 측벽 및 제2 측벽을 가지고, 상기 제1 측벽은 상기 소스 영역에 인접하고 상기 제2 측벽은 상기 드레인 영역에 인접하며; 그리고

상기 제2 p-타입 도전성 영역은 상기 제1 p-타입 도전성 영역의 상기 일단에서 상기 게이트 콘택의 상기 제2 측

벽을 지나서 신장하지 않으면서 상기 게이트 콘택의 상기 제2 측벽까지 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 26

제24항에 있어서,

상기 게이트 콘택은 제1 측벽 및 제2 측벽을 가지고, 상기 제1 측벽은 상기 소스 영역에 인접하고 상기 제2 측벽은 상기 드레인 영역에 인접하며; 그리고

상기 제2 p-타입 도전성 영역은 상기 제1 p-타입 도전성 영역의 상기 일단에서 상기 게이트 콘택의 상기 제1 및 제2 측벽들 사이까지 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 27

제23항에 있어서, 상기 p-타입 도전성 영역을 노출하고 상기 소스 영역에 인접하는 콘택 비아 홀을 형성하는 단계를 더 포함하고, 상기 n-타입 도전성 영역은 상기 p-타입 도전성 영역의 상기 일단을 지나서 신장하지 않으면서 상기 p-타입 도전성 영역의 상기 노출된 부분에서부터 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 28

제23항에 있어서, 상기 MESFET를 형성하는 단계는 기판 상에 상기 MESFET를 형성하는 단계를 포함하고 상기 n-타입 도전성 영역을 형성하는 단계는 상기 기판의 내부로 신장하는 상기 n-타입 도전성 영역을 형성하는 단계를 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 29

제28항에 있어서, 상기 n-타입 도전성 영역은 상기 기판의 내부로 500Å에서 1500Å까지 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 30

제29항에 있어서, 상기 n-타입 도전성 영역은 상기 기판의 내부로 1000Å보다 작게 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 31

제28항에 있어서, 상기 기판은 실리콘 카바이드(SiC) 기판을 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 32

제23항에 있어서, 상기 MESFET를 형성하는 단계는 베퍼층 상에 상기 MESFET를 형성하는 단계를 더 포함하고, 상기 n-타입 도전성 영역을 형성하는 단계는 상기 베퍼층의 내부로 신장하는 상기 n-타입 도전성 영역을 형성하는 단계를 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 33

제32항에 있어서, 상기 n-타입 도전성 영역은 상기 베퍼층의 내부로 500Å에서 1500Å까지 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 34

제33항에 있어서, 상기 n-타입 도전성 영역은 상기 베퍼층의 내부로 1000Å보다 작게 신장하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 35

제23항에 있어서, 상기 n-타입 도전성 영역은 상기 p-타입 도전성 영역에 의해 공핍되는 금속-반도체 필드-효과

트랜지스터(MESFET)의 형성 방법.

### 청구항 36

제23항에 있어서,

상기 게이트 콘택은 제1 측벽 및 제2 측벽을 가지고, 상기 제1 측벽은 상기 소스 영역에 인접하고 상기 제2 측벽은 상기 드레인 영역에 인접하며; 그리고

상기 n-타입 도전성 영역을 형성하는 단계는 상기 소스 영역의 아래에서부터 상기 게이트 콘택의 상기 제1 측벽을 지나서 신장하지 않으면서 상기 게이트 콘택의 상기 제1 측벽까지 신장하는 상기 n-타입 도전성 영역을 형성하는 단계를 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 37

제23항에 있어서, 상기 n-타입 도전성 영역을 형성하는 단계는 드레인 콘택의 아래까지 신장하지 않으면서 소스 콘택 및/또는 상기 소스 영역의 아래에서부터 신장하는 상기 n-타입 도전성 영역을 형성하는 단계를 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 38

제23항에 있어서, 실리콘 카바이드(SiC) 기판을 형성하는 단계를 더 포함하고, 상기 p-타입 도전성 영역을 형성하는 단계는 상기 SiC 기판 상의 상기 p-타입 도전성 영역을 형성하는 단계를 포함하고, 상기 n-타입 도전성 채널층을 형성하는 단계는 n-타입 도전성 SiC 채널층을 형성하는 단계를 포함하고, 상기 p-타입 도전성 영역을 형성하는 단계는 p-타입 도전성 SiC 영역을 형성하는 단계를 포함하고, 상기 n-타입 도전성 영역을 형성하는 단계는 n-타입 도전성 SiC 영역을 형성하는 단계를 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 39

제23항에 있어서, 기판을 형성하는 단계를 더 포함하고, 상기 p-타입 도전성 영역을 형성하는 단계는 상기 기판 상의 상기 p-타입 도전성 영역을 형성하는 단계를 포함하고, 상기 기판은 갈륨 아세나이드(GaAs) 또는 갈륨 나이트라이드(GaN)를 포함하고, 상기 채널층은 GaAs 또는 GaN을 포함하고, 상기 p-타입 도전성 영역은 p-타입 도전성 GaAs 또는 p-타입 도전성 GaN을 포함하고 그리고 상기 n-타입 도전성 영역은 n-타입 도전성 GaAs 또는 n-타입 도전성 GaN을 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 40

제23항에 있어서,

상기 n-타입 도전성 채널층의 캐리어 농도보다 더 큰 캐리어 농도를 가지고 상기 소스 영역 및 상기 드레인 영역을 정의하는 상기 n-타입 도전성 채널층 내의 SiC의 주입된 n-타입 도전성 영역들을 형성하는 단계; 및

상기 소스 및 드레인 영역들 상에 제1 및 제2 오믹 콘택들을 각각 형성하는 단계를 더 포함하는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 41

제23항에 있어서, 상기 게이트 콘택은 상기 n-타입 채널층 내에(in) 배치되는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 42

제41항에 있어서, 상기 게이트 콘택은 상기 n-타입 채널층 내의 단일 리세스에 배치되는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

### 청구항 43

제41항에 있어서, 상기 게이트 콘택은 상기 n-타입 채널층 내의 이중 리세스에 배치되는 금속-반도체 필드-효과 트랜지스터(MESFET)의 형성 방법.

**청구항 44**

트랜지스터의 단위 셀로서,

소스 영역, 드레인 영역, 및 상기 소스 영역과 상기 드레인 영역 사이에 있고 n-타입 도전성 채널층 상에 있는 게이트 콘택을 가지는 트랜지스터;

상기 소스 영역 아래에 있고 상기 드레인 영역을 향하여 신장하는 일단을 가지고, 상기 n-타입 도전성 채널층과 이격되어 있고 상기 소스 영역과 전기적으로 연결되는 p-타입 도전성 영역; 및

상기 p-타입 도전성 영역의 상기 일단을 지나서 신장하지 않으면서 상기 드레인 영역을 향하여 신장하고 상기 소스 영역의 아래에 상기 소스 영역으로부터 이격되고 상기 p-타입 도전성 영역 상에서 신장하는 n-타입 도전성 영역

을 포함하는 트랜지스터의 단위 셀.

**청구항 45**

제44항에 있어서, 상기 p-타입 도전성 영역을 노출하고 상기 소스 영역에 인접하는 콘택 비아 홀을 더 포함하고, 상기 n-타입 도전성 영역은 상기 p-타입 도전성 영역의 상기 일단을 지나서 신장하지 않으면서 상기 p-타입 도전성 영역의 상기 노출된 부분에서부터 신장하는 트랜지스터의 단위 셀.

**청구항 46**

제44항에 있어서, 상기 트랜지스터는 기판 상에 있고, 상기 n-타입 도전성 영역은 상기 기판의 내부로 신장하는 트랜지스터의 단위 셀.

**청구항 47**

제46항에 있어서, 상기 n-타입 도전성 영역은 상기 기판의 내부로 500Å에서 1500Å까지 신장하는 트랜지스터의 단위 셀.

**청구항 48**

제47항에 있어서, 상기 n-타입 도전성 영역은 상기 기판의 내부로 1000Å보다 작게 신장하는 트랜지스터의 단위 셀.

**청구항 49**

제46항에 있어서, 상기 기판은 실리콘 카바이드(SiC) 기판을 포함하는 트랜지스터의 단위 셀.

**청구항 50**

제44항에 있어서, 상기 트랜지스터는 베퍼층 상에 제공되고 상기 n-타입 도전성 영역은 상기 베퍼층의 내부로 신장하는 트랜지스터의 단위 셀.

**청구항 51**

제50항에 있어서, 상기 n-타입 도전성 영역은 상기 베퍼층의 내부로 500Å에서 1500Å까지 신장하는 트랜지스터의 단위 셀.

**청구항 52**

제51항에 있어서, 상기 n-타입 도전성 영역은 상기 베퍼층의 내부로 1000Å보다 작게 신장하는 트랜지스터의 단위 셀.

**청구항 53**

제44항에 있어서, 상기 n-타입 도전성 영역은 공핍되는 트랜지스터의 단위 셀.

**명세서**

## 기술 분야

[0001] 본 발명은 마이크로 전자공학적 소자들에 관한 것이고 더욱 상세하게는 트랜지스터들, 예를 들어 금속-반도체 필드-효과 트랜지스터들(MESFETs)에 관한 것이다.

## 배경 기술

[0002] 라디오 주파수들, S-밴드 및 X-밴드와 같은 고주파수들에서 동작하는 동안 고전력 처리 능력을 요구하는 전기 회로들이 최근에 더욱 널리 사용되고 있다. 고전력, 고주파수 회로들이 증가하기 때문에, 더 높은 전력 부하들을 여전히 처리할 수 있으면서 라디오 주파수들 및 그 이상에서 신뢰성 있게 동작할 수 있는 트랜지스터들에 대한 요구가 대응하여 증가되고 있다. 이전에, 바이폴라 트랜지스터들 및 전력 금속-산화물 반도체 필드 효과 트랜지스터들(MOSFETs)이 고전력 어플리케이션들에 대하여 사용되어 왔으나 그러한 소자들의 전력 처리 능력은 더 높은 동작 주파수들에서는 제한될 수 있다. 접합 필드-효과 트랜지스터들(JFETs)이 통상적으로 고주파수 어플리케이션들에서 사용되었지만 이전에 알려진 JFETs의 전력 처리 능력은 또한 제한될 수 있다.

[0003] 금속-반도체 필드 효과 트랜지스터들(MESFETs)이 고주파수 어플리케이션들에 대하여 개발되고 있다. 다수 캐리어들만이 전류를 운반하기 때문에 고주파수 어플리케이션들에 대하여 MESFET 구조가 더 바람직할 수 있다. 감소된 게이트 커패시턴스가 게이트 입력의 더 빠른 스위칭 시간을 허용하기 때문에 MESFET 설계가 MOSFET 설계보다 더 바람직할 수 있다. 따라서, 비록 모든 필드-효과 트랜지스터들은 전류를 운반하기 위하여 다수 캐리어들만을 사용하지만, MESFET의 쇼트키 게이트 구조는 MESFET가 고주파수 어플리케이션들에 더욱 바람직하도록 만들 수 있다.

[0004] 구조의 형태에 더하여, 그리고 아마도 더욱 근본적으로, 트랜지스터를 형성하는 반도체 물질의 특성들이 또한 동작 파라미터들에 영향을 미친다. 트랜지스터의 동작 파라미터들에 영향을 미치는 특성들 중에, 포화 전자 드리프트 속도, 전기 브레이크다운 전계 및 열전도도는 트랜지스터의 고주파수 및 고전력 특성들에 가장 큰 영향을 미칠 수 있다.

[0005] 전자 이동도는 전기장의 존재하에 포화 속도까지 전자가 얼마나 빨리 가속되는가를 측정한 것이다. 그 밖에, 더 낮은 필드를 가지면서 더 많은 전류가 발달될 수 있고, 결국은 필드가 인가될 때 더 빠른 응답 시간이 구현될 수 있으므로 높은 전자 이동도를 가지는 반도체 물질들이 바람직하다. 포화 전자 드리프트 속도는 반도체 물질에서 전자가 얻을 수 있는 최대 속도이다. 더 높은 속도는 소스에서 드레인까지 더 짧은 시간으로 이동할 수 있기 때문에 높은 포화 전자 드리프트 속도들을 가지는 물질들이 고주파수 어플리케이션들에 대하여 바람직할 수 있다.

[0006] 전기적 브레이크다운 필드(Electric breakdown field)는 쇼트키 접합의 브레이크다운과 소자의 게이트를 관통하는 전류가 갑자기 증가하는 시점의 필드 강도이다. 더 큰 전기장들은 일반적으로 물질의 주어진 치수에 의해 유지될 수 있으므로, 높은 전기적 브레이크다운 필드 물질은 고전력, 고주파수 트랜지스터들에 대하여 바람직할 수 있다. 전자들이 더 작은 전기장들보다 더 큰 전기장들에 의해 더 빨리 가속되므로 더 큰 전기장들은 더 빠른 파도 전류들(transients)을 허용한다.

[0007] 열 전도도는 반도체 물질이 열을 발산하는 능력이다. 전형적인 동작들에서, 모든 트랜지스터들은 열을 생성한다. 즉, 작은 시그널 트랜지스터들보다 고전력 및 고주파수 트랜지스터들은 일반적으로 더 많은 양의 열을 생성한다. 반도체 물질의 온도가 증가함에 따라, 온도의 증가에 따른 캐리어 이동도의 감소에 기인하여 접합 누설 전류들은 일반적으로 증가하고 필드 효과 트랜지스터를 관통하는 전류는 일반적으로 감소한다. 따라서, 열이 반도체에서 발산된다면, 상기 물질은 더 낮은 온도에서 유지되고 더 낮은 누설 전류들을 가지면서 더 큰 전류들을 운반할 수 있다.

[0008] 고주파수 MESFETs는 그들의 높은 전자 이동도들 때문에 갈륨 아세나이드(GaAs)와 같은 n-타입 III-V 화합물들로 제조될 수 있다. 비록 이러한 소자들은 증가된 동작 주파수들과 알맞게 증가된 전력 처리 능력을 제공하지만, 이러한 물질들의 비교적 낮은 브레이크다운 전압 및 더 낮은 열전도도는 고전력 어플리케이션들에서 그들의 유용성을 제한한다.

[0009] 실리콘 카바이드(SiC)는 실리콘(Si) 또는 GaAs로부터 제조되는 소자들보다 더 높은 온도, 더 높은 전력 및 더 높은 주파수에서 동작할 수 있는 전자공학적 소자들의 제조를 이론적으로 허용하는 우수한 물리적 및 전자공학적 특성들을 가지는 것으로 오랫동안 알려져 왔다. 약  $4 \times 10^6$  V/cm의 높은 전기적 브레이크다운 필드, 약

$2.0 \times 10^7 \text{ cm/sec}$ 의 높은 포화 전자 드리프트 속도 및 약  $4.9 \text{ W/cm}^2 \text{ K}$ 의 높은 열전도도는 SiC가 고주파수, 고전력 어플리케이션들에 적합할 수 있다는 것을 나타낸다.

[0010] 실리콘 카바이드의 채널층들을 가지는 MESFETs는 실리콘 기판들 상에 제조되고 있다(예를 들어, Suzuki 등이 발명한 미국 특허 번호 4,762,806 및 Kondoh 등이 발명한 미국 특허 번호 4,757,028을 참조). MESFET의 반도체 층들이 에피택셜이기 때문에, 각 에피택셜층이 그 위에 성장하는 층은 소자의 특성들에 영향을 미친다. 따라서, Si 기판 상에 성장되는 SiC 에피택셜층은 일반적으로 다른 전기적 및 열적 특성들을 가지고 다른 기판 상에 성장되는 SiC 에피택셜층과 동일하다. 미국 특허 번호 4,762,806 및 4,757,028에 기술된 Si 기판 상의 SiC 소자들은 개선된 열적 특성들을 나타내지만, Si 기판의 사용은 일반적으로 그러한 소자들이 열을 방출하는 능력을 제한한다. 더욱이, Si 상에 SiC의 성장은 일반적으로 소자가 동작중일 때 높은 누설 전류에 이르게 하는 에피택셜층들 내의 결함들을 유발한다.

[0011] 다른 MESFETs는 SiC 기판들을 사용하여 개발되어 왔다. 1990년 6월 19일에 출원되고 지금은 포기된 미국 특허 출원 Ser. No. 07/540,488은 SiC 기판 상에 성장된 SiC의 에피택셜층들을 가지는 SiC MESFET을 기술하는데, 상기 출원의 내용은 인용되어 여기에서 완전히 통합된다. SiC 기판들 상에 성장된 에피택셜층들의 개선된 결정 수준에 기인하여 이러한 소자들은 이전의 소자들보다 개선된 열적 특성들을 나타낸다. 그러나, 고전력 및 고주파수를 구현하기 위하여 SiC의 더 낮은 전자 이동도의 제한들을 극복하는 것이 필요하다.

[0012] 유사하게, Palmour가 발명하고 공동으로 양도된 미국 특허 번호 5,270,554는 SiC의  $n^+$  영역들 상에 형성된 소스 및 드레인 콘택트 및 채널이 형성되는 n-타입 층과 기판 사이의 선택적으로 저농도로 도핑된 에피택셜층을 가지는 SiC MESFET를 기술한다. Sriram 등이 발명한 미국 특허 번호 5,925,895도 또한 고주파수 동작에 대한 MESFET의 성능을 감소시킬 수 있는 "표면 효과들"을 극복하는 것으로 기술되는 구조 및 SiC MESFET을 기술한다. Sriram 등은 또한 p-타입 버퍼층 뿐만 아니라  $n^+$  소스 및 드레인 콘택트 영역들을 사용하는 SiC MESFETs를 기술한다. SiC MESFETs는 또한 Lipkin 등이 발명한 미국 특허 번호 6,686,616에 기술된다.

[0013] 더욱이, 통상적인 SiC FET 구조들은 FET의 전체의 동작 범위 동안, 즉 완전히 열린 채널에서부터 거의 핀치-오프 전압까지, 유사한 도전 타입의 저농도로 도핑된 영역에 의해 게이트로부터 매우 얇은 고농도로 도핑된 채널(델타 도핑된 채널) 오프셋을 사용함으로써, 일정한 특성들을 제공할 수 있다. 델타 도핑된 채널들은 2000년 MRS 가을 심포지움에서 Yokogawa 등에 의한 *Electronic Properties of Nitrogen Delta-Doped Silicon Carbide Layers*라는 제목의 논문 및 2000년 MRS 가을 심포지움에서 Konstantinov 등에 의한 *Investigation of Lo-Hi-Lo and Delta Doped Silicon Carbide Structure*라는 제목의 논문에서 상세하게 기술된다. 그러나, SiC MESFETs에서 더 개선될 수 있다.

[0014] 예를 들어, SiC MESFETs는 만약 그들이 고효율, 고전력, 높은 선형 라디오 주파수(RF) 어플리케이션들에서 사용된다면 높은 브레이크다운 전압들 및 상대적으로 낮은 누설 전류들을 가진다는 것이 중요할 수 있다. 높은 브레이크다운 전압들을 제공하기 위한 시도로, 바나듐 도핑된 반유전성 SiC와 같은 높게 보상된 기판들을 가지는 소자들이 제공되고 있다. 이러한 소자들은 전형적으로 낮은 누설 전류를 뿐만 아니라 적절한 브레이크다운 전압들을 제공하지만, 기판 내의 원하지 않는 트래핑 효과들에 기인하여 소자 성능을 희생할 수 있다. 더욱이, FET의 채널 하에 고농도로 도핑된 p-타입 층들을 가지는 소자들이 제공되고 있으며 우수한 전자 한정(confinement)과 낮은 누설 전류들을 제공함에 있어 성공적이다. 그러나, 이러한 소자들은 소자의 RF 성능을 열화시킬 수 있는 과도한 와류(parasitics)를 일반적으로 포함한다. 따라서, 존재하는 SiC FET 소자들이 소자의 다른 성능 특성들을 희생하지 않고 개선된 브레이크다운 전압들을 제공할 수 있도록 존재하는 SiC FET 소자들에 대하여 더 개선들이 이루어 질 수 있다.

### 발명의 상세한 설명

[0015] 본 발명은 정부의 지원으로 완성되었다. 정부는 이 발명에 일정 권리를 가진다.

[0016] 본 발명의 어떠한 실시예들은 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀을 제공한다. 상기 금속-반도체 필드-효과 트랜지스터(MESFET)의 단위 셀은 소스 영역, 드레인 영역 및 게이트 콘택트를 포함한다. 상기 게이트 콘택트는 상기 소스 영역과 상기 드레인 영역 사이에 있고 n-타입 도전성 채널층 상에 있다. p-타입 도전성 영역이 상기 소스 영역 아래에 제공되고 상기 드레인 영역을 향하여(into) 신장하는 일단을 가진다. 상기 p-타입 도전성 영역은 상기 n-타입 도전성 채널층과 이격되어 있고 상기 소스 영역과 전기적으로 연결된다. n-타입 도전성 영역이 상기 소스 영역의 아래의 상기 p-타입 도전성 영역 상에 제공되고 상기 p-타입 도전성 영역의 상

기 일단을 지나서 신장하지 않으면서 상기 드레인 영역을 향하여 신장한다.

[0017] 본 발명의 다른 실시예들에서, 상기 p-타입 도전성 영역은 제1 p-타입 도전성 영역을 포함할 수 있다. 상기 단위 셀은 상기 제1 p-타입 도전성 영역의 캐리어 농도보다 작은 캐리어 농도를 가지는 제2 p-타입 도전성 영역을 더 포함할 수 있다. 상기 제2 p-타입 도전성 영역은 상기 제1 p-타입 도전성 영역의 상기 일단에서 상기 게이트 콘택의 아래까지 신장하여, 상기 제1 및 제2 p-타입 도전성 영역들이 상기 n-타입 도전성 영역의 두 개의 표면들 상에 제공된다. 상기 게이트 콘택은 제1 측벽 및 제2 측벽을 가지고, 상기 제1 측벽은 상기 소스 영역에 인접하고 상기 제2 측벽은 상기 드레인 영역에 인접한다. 본 발명의 어떠한 실시예들에서, 상기 제2 p-타입 도전성 영역은 상기 제1 p-타입 도전성 영역의 상기 일단에서 상기 게이트 콘택의 상기 제2 측벽을 지나서 신장하지 않으면서 상기 게이트 콘택의 상기 제2 측벽까지 신장하거나 상기 게이트 콘택의 상기 제1 및 제2 측벽들 사이까지 신장할 수 있다.

[0018] 본 발명의 또 다른 실시예들에서, 상기 p-타입 도전성 영역을 노출하는 콘택 비아 홀이 상기 소스 영역에 인접하여 제공된다. 상기 n-타입 도전성 영역은 상기 p-타입 도전성 영역의 상기 일단을 지나서 신장하지 않으면서 상기 p-타입 도전성 영역의 상기 노출된 부분에서부터 신장할 수 있다. 상기 MESFET는 실리콘 카바이드(SiC) 기판과 같은 기판 상에 제공될 수 있고, 상기 n-타입 도전성 영역은 상기 기판의 내부로(into) 신장할 수 있다. 상기 n-타입 도전성 영역은 상기 기판의 내부로 약 500Å에서 약 1500Å까지 신장할 수 있지만, 일반적으로 상기 기판의 내부로 약 1000Å보다 작게 신장한다.

[0019] 본 발명의 어떠한 실시예들에서, 상기 MESFET는 상기 베퍼층 상에 제공될 수 있고, 상기 n-타입 도전성 영역은 상기 베퍼층의 내부로(into) 신장할 수 있다. 상기 n-타입 도전성 영역은 상기 베퍼층의 내부로 약 500Å에서 약 1500Å까지 신장할 수 있지만, 일반적으로 상기 베퍼층의 내부로 약 1000Å보다 작게 신장한다. 본 발명의 어떠한 실시예들에서, 상기 n-타입 도전성 영역은 상기 p-타입 도전성 영역에 의해 실질적으로 공핍될 수 있다.

[0020] 본 발명의 어떠한 실시예들에서, 상기 게이트 콘택은 제1 측벽 및 제2 측벽을 가질 수 있고, 상기 제1 측벽은 상기 소스 영역에 인접하고 상기 제2 측벽은 상기 드레인 영역에 인접한다. 상기 n-타입 도전성 영역은 상기 소스 영역의 아래에서부터 상기 게이트 콘택의 상기 제1 측벽을 지나서 신장하지 않으면서 상기 게이트 콘택의 상기 제1 측벽까지 신장할 수 있다. 본 발명의 어떠한 실시예들에서, 상기 n-타입 도전성 영역은 드레인 콘택의 아래까지 신장하지 않으면서 소스 콘택 및/또는 상기 소스 영역의 아래에서부터 신장할 수 있다.

[0021] 본 발명의 다른 실시예들에서, 기판은 실리콘 카바이드(SiC) 기판일 수 있고, 상기 p-타입 도전성 영역은 상기 SiC 기판 상에 배치될 수 있다. 상기 n-타입 도전성 채널층은 n-타입 도전성 SiC를 포함할 수 있고, 상기 p-타입 도전성 영역은 p-타입 도전성 SiC를 포함할 수 있고, 그리고 상기 n-타입 도전성 영역은 n-타입 도전성 SiC를 포함할 수 있다.

[0022] 본 발명의 또 다른 실시예들에서, 기판이 제공될 수 있고, 상기 p-타입 도전성 영역은 상기 기판 상에 배치될 수 있다. 상기 기판은 갈륨 아세나이드(GaAs) 또는 갈륨 나이트라이드(GaN)를 포함할 수 있고, 상기 채널층은 GaAs 또는 GaN을 포함할 수 있고, 상기 p-타입 도전성 영역은 p-타입 도전성 GaAs 또는 p-타입 도전성 GaN일 수 있고 그리고 상기 n-타입 도전성 영역은 n-타입 도전성 GaAs 또는 n-타입 도전성 GaN일 수 있다.

[0023] 본 발명의 어떠한 실시예들에서, 상기 n-타입 도전성 채널층의 캐리어 농도보다 더 큰 캐리어 농도를 가지고 상기 소스 영역 및 상기 드레인 영역을 정의하는 상기 n-타입 도전성 채널층 내에 SiC의 주입된 n-타입 도전성 영역들이 제공될 수 있다. 상기 소스 및 드레인 영역들 상에 제1 및 제2 오믹 콘택들이 각각 배치될 수 있다. 상기 게이트 콘택은 상기 n-타입 채널층 내에(in) 배치될 수 있다. 상기 게이트 콘택은 상기 n-타입 채널층 내의 단일 또는 이중 리세스에 배치될 수 있다.

[0024] 본 발명이 MESFETs에 대하여 우선적으로 앞에서 설명되었지만, 다른 형태의 트랜지스터들 및 트랜지스터들, 특히 MESFETs,의 제조방법들이 또한 제공된다.

## 실시예

[0032] 본 발명은 그 실시예들이 도시되어 있는 첨부된 도면들을 참고로 하여 이하에서 더욱 상세하게 기술된다. 본 발명은, 그러나, 많은 다른 형태들로 구체화될 수 있고 여기에서 기술되는 실시예들에 한정하여 해석되어서는 안된다. 오히려, 이러한 실시예들은 이러한 발명의 내용이 철저하고 완전해지도록, 그리고 당업자들에게 발명의 범위를 충분히 전달하기 위하여 제공된다. 도면들에서는, 층들 및 영역들의 크기 및 상대적인 크기들이 명확성을 위해 과장될 수 있다. 하나의 요소 또는 층이 다른 요소 또는 층의 "상에(on)" 존재하거나 다른 요소 또는

층에 "연결되어" 또는 "결합되어"라고 언급될 때는, 그것은 다른 요소 또는 층의 직접 상에 존재할 수 있거나, 다른 요소 또는 층에 직접 연결될 수 있거나 또는 직접 결합될 수 있으며 또는 중간에 개재하는 요소들 또는 층들이 존재할 수 있다고 이해될 수 있다. 반대로, 하나의 요소가 다른 요소 또는 층의 "직접 상에" 존재한다고 다른 요소 또는 층에 "직접 연결되어" 또는 "직접 결합되어"라고 언급될 때는, 중간에 개재하는 요소들 또는 층들이 존재하지 않는다. 여기에서 사용될 때, "및/또는"이라는 용어는 관련된 기재 항목들의 하나 또는 그 이상의 어떠한 그리고 모든 조합들을 포함한다. 본 발명에 걸쳐서, 동일한 참조번호들은 동일한 요소들을 참조한다.

[0033] 제1 및 제2라는 용어들이 다양한 영역들, 층들 및/또는 부분들을 기술하기 위하여 여기에서 사용되더라도 이러한 영역들, 층들 및/또는 부분들은 이러한 용어들에 의해 제한되어서는 안 된다는 것이 이해될 수 있다. 이러한 용어들은 하나의 영역, 층 또는 부분을 다른 영역, 층 또는 부분과 구별하기 위하여 사용될 뿐이다. 따라서, 본 발명의 취지에서 벗어나지 않으면서 아래에서 기술되는 제1 영역, 층 또는 부분은 제2 영역, 층 또는 부분으로 명명될 수 있고, 유사하게 제2 영역, 층 또는 부분은 제1 영역, 층 또는 부분으로 명명될 수 있다.

[0034] 더욱이, "하부의" 또는 "바닥" 및 "상부의" 또는 "정상"과 같은 상대적인 용어들은 도면들에서 도해되는 것처럼 하나의 요소의 다른 요소들에 대한 관계를 기술하기 위하여 여기에서 사용될 수 있다. 상대적인 용어들은 도면들에서 묘사되는 방향에 부가하여 소자의 다른 방향들을 포함하고자 하는 것이라고 이해될 수 있다. 예를 들어, 도면들에서의 소자가 뒤집힌다면, 다른 요소들의 "하부의" 면에 존재한다고 기술되는 요소들은 상기 다른 요소들의 "상부의" 면들에 방향을 가질 수 있다. 따라서, "하부의"라는 전형적인 용어는 도면의 특정한 방향에 의존하여 "하부의" 및 "상부의" 방향 모두를 포함할 수 있다. 유사하게, 도면들 중의 하나에서의 소자가 뒤집힌다면, 다른 요소들"의 아래에" 또는 다른 요소들"의 바로 아래에" 있다고 기술되는 요소들은 상기 다른 요소들"의 위에" 방향을 가질 수 있다. 따라서, "의 아래에 또는 "의 바로 아래에"라는 전형적인 용어들은 위에 및 아래에의 두 방향을 포함할 수 있다.

[0035] 본 발명의 실시예들은 여기에서 본 발명의 이상화된 실시예들을 개요적으로 도해하는 단면도들을 참조하여 설명된다. 그래서, 예를 들어, 제조 기술들 및/또는 공차들의 결과로 도면들의 형태들에서의 변동들이 예상될 수 있다. 따라서, 본 발명의 실시예들은 여기에서 도해되는 영역들의 특별한 형태들에 한정하여 해석되어서는 안되고, 예를 들어, 제조에서 기인하는 형태들의 변동들을 포함하여야 한다. 예를 들어, 사각형으로 도해되는 주입된 영역은 통상적으로 원형 또는 곡선의 형태들을 가질 수 있고 그리고/또는 주입된 영역의 가장자리에서는 주입된 영역에서 주입되지 않은 영역까지 2개의 변화보다는 주입 농도의 그래디언트를 가질 수 있다. 마찬가지로, 주입에 의해 형성되는 매립 영역은 상기 매립 영역과 표면 사이에 관통하여 주입이 발생하는 영역에서 어떠한 주입을 귀착한다. 따라서, 도면들에서 도해되는 영역들은 본질적으로 개요적이고, 그들의 형태들은 소자의 영역의 정확한 형태를 도해하기 위함이 아니고 본 발명의 범위를 한정하기 위함이 아니다.

[0036] 여기에서 사용되는 용어는 단지 특별한 실시예들을 기술하기 위한 것이며 발명을 한정하기 위한 것이 아니다. 여기에서 사용될 때, 문맥이 다르게 명시하지 않는다면 단수의 표현들은 복수의 표현들도 또한 포함하고자 하는 것이다. 본 명세서에서 "포함한다" 및/또는 "포함하는"이라는 용어들이 사용될 때는, 언급된 특징들, 정수들, 단계들, 동작들, 요소들 및/또는 구성성분들의 존재를 명기하는 것이며, 하나 또는 그 이상의 다른 특징들, 정수들, 단계들, 동작들, 요소들, 구성성분들 및/또는 그들의 집합의 존재 또는 추가를 배제하는 것이 아니라는 것을 나아가 이해할 수 있다.

[0037] 다르게 정의되지 않는다면, 여기에서 사용되는 모든 용어들(공학적 및 과학적 용어들을 포함하는)은 본 발명이 속하는 기술분야의 보통의 기술을 가진 자에 의해 통상적으로 이해되는 동일한 의미를 가진다. 통상적으로 사용되는 사전들에서 정의되는 용어들과 같은 용어들은 관련 기술분야의 문장에서의 그들의 의미와 일치하는 의미를 가지는 것으로 해석되어야 하고, 여기에서 명시적으로 정의하지 않는 한 이상적 또는 지나치게 형식적인 의미로 해석되어서는 안된다.

[0038] 여기에서 사용되는 것처럼 "오믹 콘택"이라는 용어는 관련된 임피던스가 본질적으로 임피던스=V/I의 관계로 주어지는 콘택을 언급하며, 여기에서 본질적으로 모든 기대되는 동작 주파수들(즉, 오믹 콘택에 관련된 임피던스는 본질적으로 모든 동작 주파수들에서 동일하다) 및 전류들에서, I는 전류이고 V는 콘택을 가로지르는 전압이다.

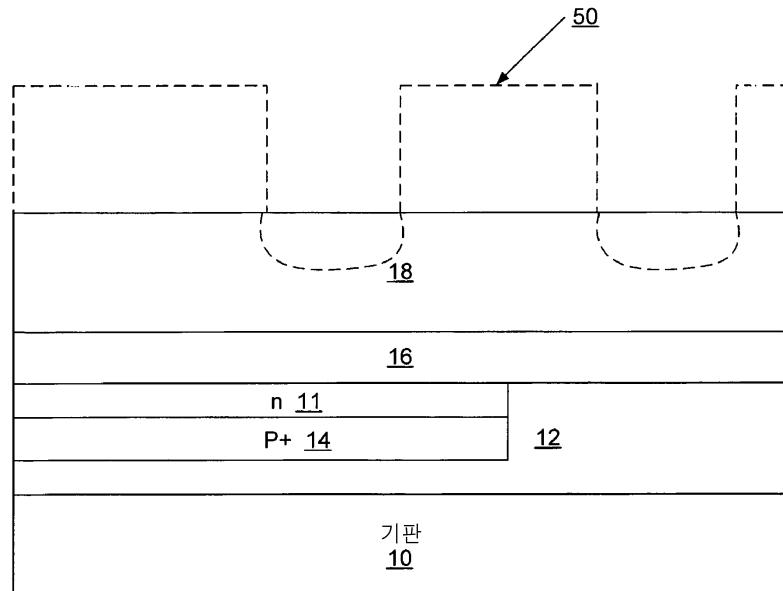

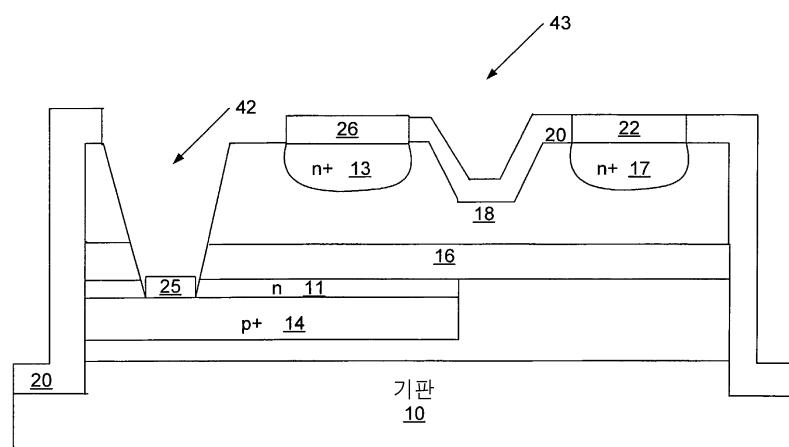

[0039] 본 발명의 실시예들은 이제 아래에서 본 발명의 다양한 실시예들과 본 발명의 실시예들을 제조하는 다양한 공정들을 도해하는 도 1 내지 7을 참고로 하여 상세하게 설명될 것이다. 본 발명의 어떠한 실시예들에 따른 트랜지스터들, 예를 들어, 금속-반도체 필드 효과 트랜지스터들(MESFETs)은 MESFET의 드레인 영역들을 향하여 신장하는 양단(ends)을 가지고 MESFET의 소스 영역들 아래의 p-타입 도전성(conductivity) 영역들을 가지면서 제공될

수 있다. 소스 영역들 아래의 p-타입 도전성 영역들을 가지는 MESFETs는 *Transistor Having Buried P-Type Layers Beneath The Source Region And Methods Of Fabricating The Same*이라는 명칭으로 2003년 11월 26일에 출원되고 공동으로 양도된 미국 특허출원공개 번호 2004/0099888에서 설명되는데, 상기 발명의 내용은 전부 설명된 것처럼 여기에 인용하여 여기에 통합된다. 상기 미국출원에서 설명된 것처럼, 예를 들어 매립된 p-타입 도전성 영역의 존재는 소자의 다른 성능 특성들과 절충하지 않고 개선된 브레이크다운 전압들을 가지는 소자들을 제공할 수 있다.

[0040] 베피층을 관통하는 전류량을 감소하게 하고 소자 효율 및 이득을 개선하기 위하여 채널 영역과 가능한 가까운 매립 p-타입 도전성 영역을 가지는 것이 바람직하다. 그러나 채널에 가까운 근처에 p-타입 도전성 영역을 위치시키는 것은 게이트-소스 영역들뿐만 아니라 게이트 콘택 아래의 채널에서 공핍(depletion)을 유발할 수 있다. 이러한 영역들에서의 공핍은 소자 전류 및/또는 성능의 감소를 유발할 수 있다. 채널의 증가된 두께에 의해 유발되는 게이트-드레인 영역에 존재할 수 있는 더 높은 전하 밀도에 기인하여 소자의 브레이크다운 전압이 낮아질 수 있으므로, 채널의 두께를 증가시키는 것은 이러한 문제에 대한 적절한 해답이 될 수 없다. 따라서, 본 발명의 어떠한 실시예들은 p-타입 도전성 영역과 n-타입 도전성 채널 영역 사이에 있는 p-타입 도전성 영역 상의 n-타입 도전성 영역을 제공한다. 본 발명의 어떠한 실시예들에서는, n-타입 도전성 영역은 p<sup>+</sup> 영역에 의해 완전히 공핍될 수 있다, 즉, 도전성이 아닐 수 있다. p-타입 도전성 영역 상의 n-타입 도전성 영역의 추가는 게이트 영역까지의 소스 아래의 채널 영역의 두께를 선택적으로 증가시킬 수 있다. 따라서, 여기에서 더 상세하게 설명되는 것처럼 채널 영역의 가까운 영역에 p-타입 도전성 영역이 형성될 때 p-타입 도전성 영역 상의 n-타입 도전성 영역의 존재는 채널 공핍의 발생 가능성을 감소시킬 수 있다.

[0041] 여기에서 더 상세하게 설명되는 것처럼, 본 발명의 어떠한 실시예들에 따른 트랜지스터들은, 예를 들어, 코드 분할 다중 접속(CDMA) 및/또는 광대역 CDMA(WCDMA)와 같은 복소 변조 설계를 사용하는 기지국에 대한 전력 증폭기들과 같은 고효율 선형 전력 증폭기들에 유용할 수 있다.

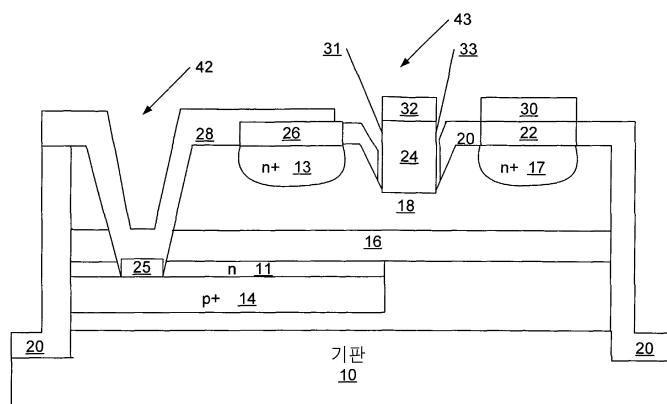

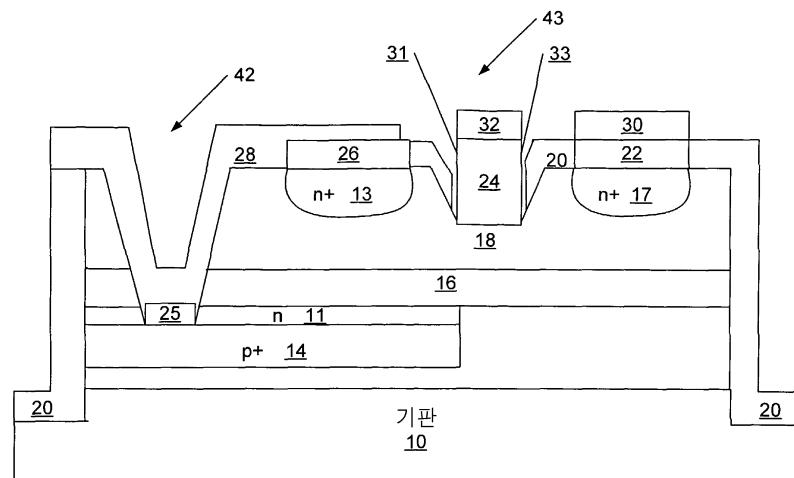

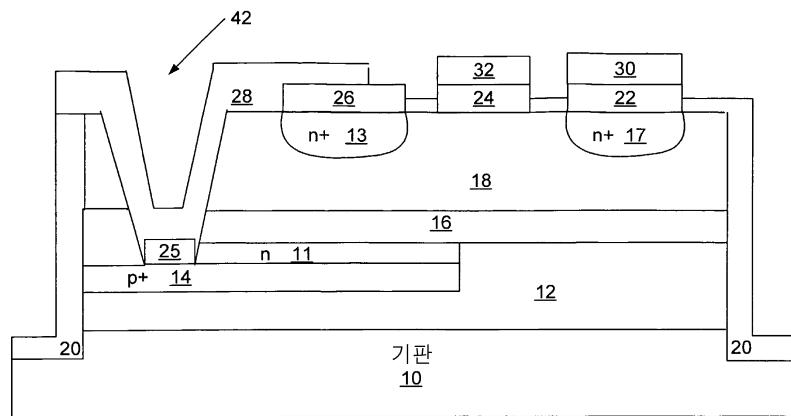

[0042] 도 1을 참조하면, 본 발명의 실시예들에 따른 트랜지스터들, 예를 들어 MESFETs이, 이제 상세하게 설명된다. 도 1에서 도시한 것처럼, 기판(10)이 제공된다. 기판(10)은 p-타입 또는 n-타입 도전성이거나 또는 반-절연성(semi-insulating)의 단결정 벌크 실리콘 카바이드(SiC) 기판일 수 있다. p-타입 또는 n-타입의 기판(10)은 매우 저농도로 도핑될 수 있다. 기판은 6H, 4H, 15R 또는 3C 실리콘 카바이드를 포함할 수 있다. 본 발명이 여기에서 SiC 기판을 기준으로 하여 설명되지만, 본 발명은 SiC에 한정되어서는 안된다. 예를 들어, 어떠한 실시예들에서는, 기판(10)은 본 발명의 범위를 벗어나지 않으면서 또한, 예를 들어, 갈륨 아세나이드(GaAs) 또는 갈륨 나이트라이드(GaN)를 포함할 수 있다.

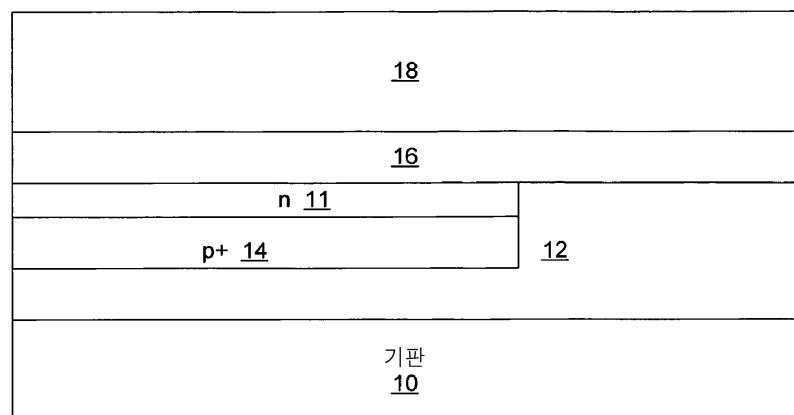

[0043] 예를 들어, p-타입 실리콘 카바이드의 선택적인 베피층(12)이 기판(10) 상에 제공될 수 있다. 베피층(12)은 6H, 4H, 15R 또는 3C 폴리타입의 p-타입 도전성 실리콘 카바이드로 형성될 수 있다. 베피층(12)은, 예를 들어, 약 0.5x10<sup>15</sup> cm<sup>-3</sup>에서 약 3.0x10<sup>15</sup> cm<sup>-3</sup> 까지의 캐리어 농도를 가질 수 있다. 적당한 도편트들은 알루미늄, 봉소 및/또는 갈륨을 포함한다. 베피층(12)은 약 2.0 μm의 두께를 가질 수 있다. 베피층(12)이 앞에서 p-타입 실리콘 카바이드로 설명되었지만, 본 발명은 이러한 구성에 한정되지 않는다. 대신, 베피층(12)은 도핑되지 않은 실리콘 카바이드(즉, 의도적으로 도핑되지 않은) 또는 매우 낮은 농도로 도핑된 n-타입 도전성 실리콘 카바이드일 수 있다. 매우 낮은 농도로 도핑된 n-타입 실리콘 카바이드가 베피층(12)에 사용된다면, 베피층(12)의 캐리어 농도는 바람직하게는 약 5.0x10<sup>14</sup> cm<sup>-3</sup> 보다 낮다.

[0044] 도 1에서 더 도해되는 것처럼, 소자의 드레인 영역을 향하여 신장하는 일단(an end)을 가지는 p<sup>+</sup> 영역(14)이 소자의 소스 영역 아래에 제공된다. 여기에서 사용될 때, "p<sup>+</sup>" 또는 "n<sup>+</sup>"는 동일한 또는 다른 층 또는 기판의 인접한 또는 다른 영역들에 존재하는 것보다 더 높은 캐리어 농도들에 의해 정의되는 영역들을 언급한다. p<sup>+</sup> 영역들을 가지는 트랜지스터들 및 그의 제조 방법들은 2003년 11월 26일에 출원되고 공동으로 양도된 미국 특허출원공개 번호 2004/0099888에서 설명된 것처럼 여기에서 설명되고, 따라서 여기에서는 상세하게 설명되지 않는다.

[0045] p<sup>+</sup> 영역(14)은 p-타입 도전성, 예를 들어, p-타입 도전성 실리콘 카바이드의 영역이다. p<sup>+</sup> 영역(14)에 대하여, 약 1.0x10<sup>18</sup> cm<sup>-3</sup>에서 약 1.0x10<sup>20</sup> cm<sup>-3</sup> 까지의 캐리어 농도들이 적합할 수 있지만, 가능한 높은 캐리어 농도들이 바람직하다. 캐리어 농도는 p<sup>+</sup> 영역(14)에 걸쳐서 일정하지 않을 수 있으나, 캐리어 농도는 그 상에 오직 콘택의 형성을 촉진하기 위하여 p<sup>+</sup> 영역(14)의 표면에서 가능한 높은 것이 바람직하다. 본 발명의 어떠한 실시예들에

서는,  $p^+$  도전성 영역(14)이 도 3에서 도해된 것처럼 기판(10) 내에 제공될 수 있다.  $p^+$  도전성 영역(14)은, 예를 들어, 베피층(12) 또는 기판(10)으로 약  $0.4\mu\text{m}$  신장할 수 있다. 소스 영역 아래의  $p^+$  도전성 영역(14)의 존재는 소소에서 전자 인젝션(injection)을 방지할 수 있고, 따라서, 개선된 브레이크다운 전압을 제공하는 것이 가능할 수 있다. 더욱이,  $p^+$  도전성 영역(14)이 드레인 영역의 아래까지 신장하지 않는 사실은 소자로의 와류의 도입을 방지할 수 있고, 따라서 소자 성능은 영향을 받지 않을 수 있다.

[0046] 도 1에서 더 도해되는 것처럼, n-타입 도전성 영역(11)이  $p^+$  영역(14) 상에 제공된다. n-타입 도전성 영역(11)이 트랜지스터의 소스 영역(13) 아래에 제공되고 드레인 영역을 향하여 신장하는  $p^+$  영역(14)의 일단을 지나서 (beyond) 신장하지 않으면서  $p^+$  영역(14) 상에 신장한다. 즉, 본 발명의 어떠한 실시예들에서는 n-타입 도전성 영역(11)이  $p^+$  영역(14) 상에서  $p^+$  영역(14)의 제1 일단에서  $p^+$  영역(14)의 제2 일단(드레인을 향하여 신장하는 일단)까지 신장할 수 있다. 여기에서 사용되는 것처럼,  $p^+$  영역(14)이 더 이상 n-타입 도전성 영역(11)의 공핍을 유발하지 않는다면 n-타입 도전성 영역(11)은  $p^+$  영역(14)을 지나서 신장한다. 본 발명의 어떠한 실시예들에서는, n-타입 도전성 영역(11)은 n-타입 도전성 SiC, 예를 들어, 6H, 4H, 15R 또는 3C 폴리타입 SiC 일 수 있다. n-타입 도전성 영역(11)은 베피층(12, 만약 제공된다면) 또는 기판(10)으로 약  $500\text{\AA}$ 에서 약  $1500\text{\AA}$ 까지 신장할 수 있다. 본 발명의 어떠한 실시예들에서는, n-타입 도전성 영역(11)은 베피층(12) 또는 기판(10)으로 약  $1000\text{\AA}$ 보다 작게 신장한다. 앞에서 설명한 것처럼, n-타입 도전성 영역은 p-n 접합의 내부의 포텐셜(built in potential)에 의해 실질적으로 공핍될 수 있다. 따라서, 실질적으로 공핍된 n-타입 도전성 영역(11)은 게이트 영역까지 선택적으로 소스 아래의 채널 영역의 두께 및 도전성을 증가시킬 수 있다. 본 발명의 어떠한 실시예들에서는 n-타입 도전성 영역(11)이 완전히 공핍될 수 있다.

[0047] 본 발명의 어떠한 실시예들에서는, n-타입 도전성 영역(11)이 소스 콘택(26)의 아래에서부터 및/또는  $n^+$  소스 영역(13)의 아래에서부터 게이트 콘택(24)의 제1 측벽(31)을 지나서 신장하지 않으면서 게이트 콘택(24)의 제1 측벽(31)까지 더 신장할 수 있다.

[0048] 본 발명의 어떠한 실시예들에서는, 제1 p-타입 도전성 영역( $p^+$  영역, 14)의 캐리어 농도보다 낮은 캐리어 농도를 가지는 제2 p-타입 도전성 영역(21)이 도 6에서 도해된 것처럼 제공될 수 있다. 거기에서 도해된 것처럼, 제2 p-타입 도전성 영역(21)은 n-타입 도전성 영역(11)의 두 표면들 상에 제1 및 제2 p-타입 도전성 영역들(14 및 21)이 제공될 수 있도록 제1 p-타입 도전성 영역(14)의 일단에서부터 게이트 콘택(24)의 아래까지 신장할 수 있다. 앞에서 설명된 것처럼, 게이트 콘택(24)은 제1 측벽(31) 및 제2 측벽(33)을 가진다. 제1 측벽(31)은 소스 영역(13) 근처에 있고, 제2 측벽(33)은 드레인 영역(17) 근처에 있다. 제2 p-타입 도전성 영역(21)은 제1 p-타입 도전성 영역(14)의 일단에서부터 게이트 콘택의 제2 측벽을 지나서 신장하지 않으면서 게이트 콘택(24)의 제2 측벽(33)까지 신장할 수 있으며 또는 제1 p-타입 도전성 영역(14)의 일단에서부터 게이트 콘택(24)의 제1 측벽(31) 및 제2 측벽(33) 사이까지 신장할 수 있다. 일반적으로, 제2 p-타입 도전성 영역(21)은 게이트 콘택(24)의 제1 측벽(31) 및 제2 측벽(33) 사이의 약 절반 정도로 신장한다. 본 발명의 어떠한 실시예들에서는, 제2 p-타입 도전성 영역(21)은 제1 p-타입 도전성 영역(14)까지 자기 정렬(self align)될 수 있다.

[0049] 도 1을 다시 참조하면, 베피층(12)은 기판(10)과 제2 베피층(16) 사이에 위치될 수 있다. 제2 베피층(16)은, 예를 들어, 약  $1.0 \times 10^{15} \text{ cm}^{-3}$ 에서 약  $5 \times 10^{16} \text{ cm}^{-3}$  까지의 캐리어 농도를 가지는 p-타입 실리콘 카바이드일 수 있다. p-타입 실리콘 카바이드 베피층(16)은 또한 약  $1000\text{\AA}$ 보다 작은 두께를 가질 수 있다. 본 발명의 어떠한 실시예들에서는, 베피층(16)이 생략될 수 있다. 제2 베피층(16)이 앞에서 p-타입 도전성 실리콘 카바이드인 것으로 기술되지만, 본 발명은 이러한 구성을 한정되지는 않는다는 것이 이해될 수 있다. 대신으로, 예를 들어, 제2 베피층(16)이 n-타입 도전성, 예를 들어 베피층(12)에 대하여 앞에서 설명된 것처럼 매우 저농도로 도핑된 n-타입 도전성 SiC 또는 도핑되지 않은 SiC로 될 수 있다. 본 발명의 어떠한 실시예들에서는, 제2 베피층(16)이 도 3에서 도해된 것처럼 기판(10) 상에 직접(directly) 제공될 수 있다.

[0050] n-타입 도전성 채널층(18)이 도 1에서 도해된 것처럼, 제2 베피층(16) 상에 제공된다. n-타입 도전성 채널층(18)은 6H, 4H, 15R 또는 3C 폴리타입의 n-타입 도전성 실리콘 카바이드로 형성될 수 있다. n-타입 도전성 채널층은, 예를 들어, 상이한 캐리어 농도들을 가지는 n-타입 도전성 실리콘 카바이드의 하나 또는 그 이상의 층들을 포함할 수 있다. 예를 들어, n-타입 도전성 채널층(18)은 도 4에서 도해된 것처럼 제1 n-타입 도전성 채널층

(15) 및 제2 n-타입 도전성 채널층(19)을 포함할 수 있다. 대신으로, n-타입 도전성 채널층(18)은 *Delta Doped Silicon Carbide Metal-Semiconductor Field Effect Transistors Having a Gate Disposed in a Double Recess Structure*라는 명칭으로 Sriram이 발명하고 2001년 10월 24일에 출원되고 공동으로 양도된 미국 특허 출원 공개 번호 US2003/0075719에서 상세하게 설명된 바와 같이 n-타입 도전성 SiC의 제1, 제2 및 제3 층들을 포함할 수 있는데, 상기 발명의 내용은 전부 설명된 것처럼 여기에 인용하여 통합된다.

[0051] 도 1에서 상세히 도해된 것처럼, 각각 소자의 소스 영역과 드레인 영역을 정의하는 n<sup>+</sup> 영역들(13 및 17)이 제공된다. 소스 및 드레인 영역들(13 및 17)은 일반적으로 n-타입 도전성 실리콘 카바이드이고 n-타입 도전성 채널층(18)보다 더 큰 캐리어 농도들을 가진다. 소스 및 드레인 영역들(13 및 17)에 대하여, 약 1x10<sup>19</sup> cm<sup>-3</sup>의 캐리어 농도가 적합할 수 있지만 가능한 한 높은 캐리어 농도들이 바람직하다.

[0052] 오믹 콘택들(26 및 22)이 주입된 소스 및 드레인 영역들(13 및 17) 상에 각각 제공되고 소스 콘택(26)과 드레인 콘택(22)을 제공하도록 이격된다. 오믹 콘택(25)이 p<sup>+</sup> 콘택(25)을 제공하도록 p<sup>+</sup> 도전성 영역(14)상에 제공된다. 오믹 콘택들(25, 26 및 22)은 니켈 또는 다른 적당한 금속들로 형성될 수 있다. p<sup>+</sup> 도전성 영역(14)은, 예를 들어, p<sup>+</sup> 오믹 콘택(25)을 소스 콘택(26)에 전기적으로 연결함으로써 소스 영역(13)과 동일한 포텐셜에서 유지된다. 산화막과 같은 절연층(20)이 소자의 노출된 표면 상에 더 제공될 수 있다.

[0053] 도 1에서 더 상세하게 도해된 것처럼, 제1 리세스(43) 및 콘택 비아 홀(42)이 제공된다. 제1 리세스(43)가 소스 및 드레인 영역들(13 및 17) 사이에서 제공된다. 제1 리세스(43)가 n-타입 도전성 채널층(18)을 향하여 신장하고 n-타입 도전성 채널층(18)을 노출한다. 콘택 비아 홀(42)이 소스 영역(13)에 인접하여 제공되고 적어도 p<sup>+</sup> 영역(14)의 일부를 노출하도록 n-타입 도전성 영역(11)을 관통하여 신장한다. 앞에서 설명한 것처럼, n-타입 도전성 영역(11)은, p<sup>+</sup> 도전성 영역(14) 상을, p<sup>+</sup> 도전성 영역(14)의 하나의 일단에서부터, 드레인을 향하여 신장하는 p<sup>+</sup> 도전성 영역(14)의 제2 일단을 지나서 신장하지 않으면서, 신장할 수 있다.

[0054] 게이트 콘택(24)이 소스 영역(13) 및 드레인 영역(17) 사이의 제1 리세스(43)에 제공될 수 있다. 게이트 콘택(24)이 크롬, 백금, 백금 실리사이드, 니켈 및/또는 TiWN으로 형성될 수 있지만 쇼트키 효과를 얻을 수 있도록 당업자에게 잘 알려진 금과 같은 다른 금속들도 사용될 수 있다. 쇼트키 게이트 콘택(24)은 일반적으로 삼층 구조를 가진다. 그러한 구조는 크롬(Cr)의 높은 접착력에 기인하여 이점을 가질 수 있다. 예를 들어, 게이트 콘택(24)은 n-타입 도전성 채널층(18)과 접촉하는 크롬(Cr)의 제1 게이트층을 선택적으로 포함할 수 있다. 게이트 콘택(24)은 백금(Pt) 및 금(32) 또는 다른 높은 도전성 금속으로 구성된 오버레이어(overlayer)(32)를 더 포함할 수 있다. 대신으로, 게이트 콘택(24)은 n-타입 도전성 채널층(18) 상의 제1 리세스(43) 내에 니켈로 구성된 제1층을 포함할 수 있다. 게이트 콘택(24)은 니켈로 구성된 제1층 상에 금으로 구성된 층을 포함하는 오버레이어를 더 포함할 수 있다.

[0055] 도 1에서 더 상세하게 도해된 것처럼, 금속 오버레이어들(28, 30 및 32)는 소스 콘택(26) 및 p<sup>+</sup> 콘택(25), 드레인 콘택(22) 및 게이트 콘택(24) 상에 각각 제공될 수 있다. 오버레이어들(28, 30 및 32)는 금, 은, 알루미늄, 백금 및/또는 구리일 수 있다. 다른 적합한 높은 도전성 금속들이 오버레이어에 대하여 또한 사용될 수 있다. 더욱이, 금속 오버레이어(28)는 p<sup>+</sup> 영역(14)의 p<sup>+</sup> 콘택(25)을 소스 콘택(26)과 전기적으로 연결할 수 있다.

[0056] 도 2a 내지 2h는 본 발명의 어떠한 실시예들에 따른 트랜지스터들의 제조를 도해한다. 도 2a에서 도시된 것처럼, 선택적인 베퍼층(12)이 기판(10) 상에 성장되거나 또는 증착(deposit)될 수 있다. 기판(10)은 반-절연성 기판, p-타입 기판 또는 n-타입 기판일 수 있다. 기판(10)은 매우 저농도로 도핑될 수 있다. 기판(10)이 반-절연성이라면 Carter등이 발명하고 "Semi-insulating Silicon Carbide Without Vanadium Domination"이란 명칭으로 공동으로 양도된 미국 특허 번호 6,218,680에 설명된 것처럼 제조될 수 있고, 상기 발명의 내용은 전부 설명된 것처럼 여기에 인용하여 통합된다. 반-절연성 기판들을 제공하는 다른 기술들이 또한 사용될 수 있다. 베퍼층(12)은 약 3.0x10<sup>15</sup> cm<sup>-3</sup> 이하의, 하지만 일반적으로 1.0x10<sup>15</sup> cm<sup>-3</sup> 이하의 캐리어 농도를 가지는 p-타입 도전성 실리콘 카바이드로 될 수 있다. 대신으로, 베퍼층(12)은 n-타입 실리콘 카바이드 또는 도핑되지 않은 실리콘 카바이드일 수 있다.

[0057] 도 2a에서 더 상세하게 도해된 것처럼, 마스크(45)가 p<sup>+</sup> 영역(14)을 주입하기 위하여 형성될 수 있다. p<sup>+</sup> 영역(14)은 일반적으로 예를 들어, 알루미늄, 봉소 및/또는 갈륨의 이온 주입에 의해 형성된다. 이온 주입은 도 2b

에서 도해된 것처럼  $p^+$  영역(14)을 형성하기 위해 마스크(45)에 의해 덮혀지지 않는 영역들 상에서 수행될 수 있다. 그러므로, 이온들은  $p$ -타입 도전성, 예를 들어,  $p$ -타입 도전성 실리콘 카바이드의 고농도로 도핑된 영역을 제공하기 위해, 존재한다면, 베피층(12), 또는 기판(10)의 부분들에 주입된다.  $p$ -타입 도전성의 고농도로 도핑된 영역이 베피층(12) 또는 기판(10) 내부로 약  $0.4\mu\text{m}$  신장할 수 있다. 도 2b에서 더욱 상세하게 도해된 것처럼, 마스크(45)가  $n$ -타입 도전성 영역(11)을 주입하기 위하여 사용될 수도 있다.  $n$ -타입 도전성 영역(11)은 일반적으로 예를 들어, 질소 또는 인의 이온 주입에 의해 형성될 수 있다. 이온 주입은 도 2b에서 도해된 것처럼  $n$ -타입 도전성 영역(11)을 형성하기 위해 마스크(45)에 의해 덮혀지지 않는 영역 상에 수행될 수 있다.  $n$ -타입 도전성 영역(11)은 존재한다면 베피층(12) 또는 기판(10)의 내부로 약  $500\text{\AA}$ 에서 약  $1500\text{\AA}$ 까지 신장할 수 있지만, 존재한다면 베피층(12) 또는 기판(10)의 내부로 일반적으로 약  $1000\text{\AA}$ 보다 작게 신장한다.

[0058]  $p$ -타입 도편트들 및  $n$ -타입 도편트들의 주입 이후에 주입들을 활성화하기 위해 고온의 어닐링이 수반된다. 본 발명의 어떠한 실시예들에서,  $n$ -타입 및  $p$ -타입 도편트들이 동시에 어닐링될 수 있다. 적합한 어닐링 온도들은 약  $1300$ 에서 약  $1600^\circ\text{C}$ 까지일 수 있으며, 일반적으로 약  $1500^\circ\text{C}$ 이다.

[0059] 도 2b에서 도시된 것처럼, 제2 베피층(16) 및  $n$ -타입 도전성 채널층(18)은 베피층(12) 상에 성장되거나 증착된다. 베피층(12)이 포함되지 않는다면 제2 베피층(16) 및  $n$ -타입 도전성 채널층(18)은 기판(10) 상에 성장되거나 또는 증착될 수 있다는 것이 이해될 수 있다. 도 2b에 도해된 것처럼 제2 베피층(16)은 베피층(12) 상에 형성되고  $n$ -타입 도전성 채널층(18)은 제2 베피층(16) 상에 형성될 수 있다. 제2 베피층(16)은 약  $1000\text{\AA}$ 보다 작은 두께를 가지도록 형성되고 앞에서 설명된 것처럼 본 발명의 어떠한 실시예들에서는 생략될 수 있다.

[0060] 도 2c에서 도해된 것처럼, 마스크(50)가 소스 영역과 드레인 영역을 각각 정의하는  $n^+$  영역들(13 및 17)을 주입하기 위해 형성될 수 있다. 소스 및 드레인 영역들(13 및 17)은 일반적으로 예를 들어 질소(N) 또는 인(P)의 이온 주입과 이후에 수반되는 고온 어닐링에 의해 형성된다. 적합한 어닐링 온도들은 약  $1100$ 에서 약  $1600^\circ\text{C}$ 일 수 있다. 도 2d에서 도해된 것처럼  $n^+$  영역들(13 및 17)을 형성하기 위해 마스크(50)에 의해 덮혀지지 않는 영역들 상에 이온 주입이 수행될 수 있다. 따라서, 이온들이  $n$ -타입 도전성 채널(18)보다 더 높은 캐리어 농도들을 가지는  $n$ -타입 도전성, 예를 들어,  $n$ -타입 도전성 SiC의 고농도로 도핑된 영역들을 제공하기 위해  $n$ -타입 도전성 채널층(18)의 일부분들에 주입된다. 일단 주입되면, 주입을 활성화하기 위해 도편트들이 어닐링될 수 있다.

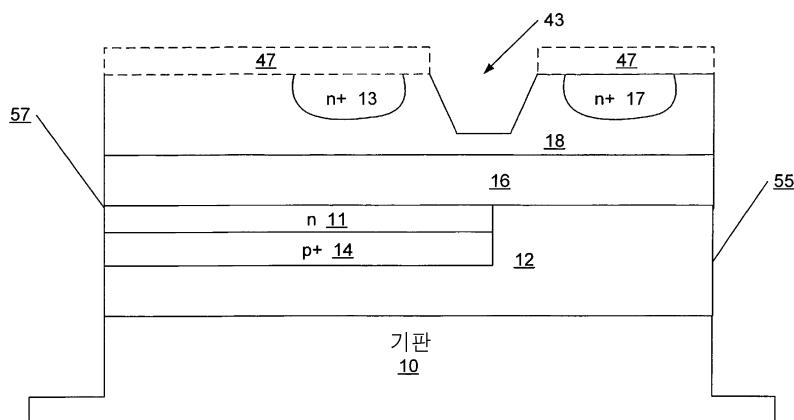

[0061] 도 2d에서 도시된 것처럼, 기판(10), 베피층(12),  $p^+$  영역(14), 제2 베피층(16) 및  $n$ -타입 도전성 채널층(18)이 분리 메사(isolation mesa)를 형성하기 위해 식각될 수 있다. 메사는 트랜지스터의 주변을 정의하는 기판(10), 베피층(12),  $p^+$  영역(14), 제2 베피층(16) 및  $n$ -타입 도전성 채널층(18)에 의해 정의되는 측벽들(55, 57)을 가진다.

[0062] 메사의 측벽들은  $p^+$  도전성 영역(14)을 지나 아래로 신장한다. 메사는 도 2d에서 도시된 것처럼 소자의 기판(10)을 향하여 신장하도록 형성될 수 있다. 메사는 소자에서의 전류 흐름을 메사까지 제한하고 소자의 커페시턴스를 감소시키도록 소자의 공핍 영역을 지나 신장할 수 있다. 앞에서 설명된 소자를 반응성 이온 식각하여 메사가 형성될 수 있지만, 당업자에게 알려진 다른 방법들이 메사를 형성하기 위해 사용될 수 있다. 더욱이, 메사가 사용되지 않는다면 소자는 양성자 충격(proton bombardment), 상쇄하는 원자들로 카운터도핑(counterdoping with compensating atoms) 또는 당업자들에게 알려진 다른 방법들과 같은 다른 방법들을 사용하여 분리될 수 있다.

[0063] 어떠한 실시예들에서는 제2 베피층(16) 및  $n$ -타입 도전성 채널층(18)만이 도 4에서 도시된 것처럼 분리 메사를 형성하도록 식각될 수 있다. 이러한 실시예들에서는, 측벽들(55, 57)이 제2 베피층(16) 및  $n$ -타입 도전성 채널층(18)에 의해 정의되는데, 이것은 트랜지스터의 주변을 정의한다. 여기에서 제공되는 도면들은 분리 메사의 예시적인 실시예들을 설명할 뿐이고 본 발명의 실시예들은 여기에서 도해된 것들에 한정되지 않는다는 것이 이해될 것이다. 예를 들어, 본 발명의 범위에서 벗어나지 않으면서 분리 메사는 제2 베피층(16)을 향하여 신장하지 않을 수 있다.

도 2d는 MESFET의 제1 리세스(43)의 형성을 더 도해한다. 제1 리세스(43)는 마스크(47)를 형성하고 그 다음에 마스크(47)에 따라 제1 리세스(43)를 형성하도록  $n$ -타입 도전성 채널층(18)을 통하여 식각함으로써 형성될 수 있다. 제1 리세스(43)는 건식 또는 습식 식각 공정과 같은 식각 공정에 의해 형성될 수 있다. 예를 들어, 제1 리세스(43)는 건식 식각, 예를 들어, 전자 사이클로트론 공명(ECR) 또는 유도 결합 플라즈마(ICP) 식각에 의해

형성될 수 있다. 마스크(47)는 제거될 수 있다.

[0064] 도 2e는 앞에서 설명한 것처럼 제1 리세스(43)가 형성된 후에 절연막층(20), 예를 들어, 산화막층의 형성을 도해한다. 절연막층(20)은 현존하는 구조의, 즉 분리 메사, 소스 및 드레인 영역들(13 및 17), n-타입 도전성 채널층(18) 상 및 제1 리세스(43) 내의, 노출된 표면 위에 성장되거나 증착될 수 있다.

[0065] 도 2f를 지금 참조하면, 콘택 윈도우(contact window)들이 절연막층(20)을 관통하여 소스 및 드레인 영역들(13 및 17)까지 식각될 수 있다. 다음에 니켈이 소스 및 드레인 콘택들(26 및 22)을 각각 증착하기 위해 증발(evaporate)될 수 있다. 도 2f에 도해되는 것처럼 오믹 콘택들(26 및 22)을 형성하기 위해 니켈은 어닐링될 수 있다. 그러한 증착 및 어닐링 공정은 당업자들에게 알려져 있는 통상적인 기술들을 사용하여 수행될 수 있다. 예를 들어, 오믹 콘택들(26 및 22)은 약 950°C에서 약 1100°C까지의 온도에서 약 2분동안 어닐링될 수 있다. 그러나, 다른 시간들 및 온도들이 또한 사용될 수 있다. 예를 들어, 30초에서 약 10분까지의 시간들을 받아들일 수 있다. 도 2g에서 더 도해되는 것처럼, 소스 및 드레인 콘택들(26 및 22)이 형성된 후에, 콘택 윈도우(41)가 고농도로 도핑된 p<sup>+</sup> 영역(14) 위의 절연막층(20) 내에 식각될 수 있다.

[0066] 본 발명의 어떠한 실시예들에서, 오믹 콘택들은 *Silicon-Rich Nickel Silicide Ohmic Contacts for SiC Semiconductor Devices*라는 명칭으로 2004년 7월 6일에 출원된 공동으로 양도된 미국 특허 출원 일련 번호 \_에 설명된 콘택들과 동일하거나 유사할 수 있는데, 상기 발명의 내용은 전부 설명된 것처럼 여기에 인용하여 통합된다.

[0067] 도 2g에 도해된 것처럼, MESFET의 콘택 비아 홀(42)이 형성될 수 있다. 콘택 비아 홀(42)이 절연막층(20) 내의 윈도우(41)에 의해 정의되는 MESFET의 부분에서 식각될 수 있다. 콘택 비아 홀(42)을 형성하도록 n-타입 도전성 채널층(18), 제2 버퍼층(16)(만일 존재한다면) 및 n-타입 도전성 영역(11)이 p<sup>+</sup> 도전성 영역(14)을 노출하도록 관통하여 식각될 수 있다. 식각 공정은, 예를 들어, 건식 또는 습식 식각 공정일 수 있다. 도 2g에서 더 도해된 것처럼, p<sup>+</sup> 콘택(25)을 증착하도록 니켈 및/또는 알루미늄-티타늄(AlTi)이 증발될 수 있다. 니켈은 오믹 콘택(25)을 형성하도록 어닐링될 수 있다. 그러한 증착 및 어닐링 공정은 당업자들에게 알려진 통상적인 기술들을 사용하여 수행될 수 있다. 예를 들어, 오믹 콘택(25)이 약 600°C에서 약 1050°C까지의 온도에서 어닐링될 수 있다.

[0068] 도 2h는 게이트 콘택(24) 및 오버레이어들(28, 30 및 32)의 형성을 도해한다. 예를 들어, 절연막(20) 내에 윈도우가 열릴 수 있고 크롬으로 구성된 층이 제1 리세스(43) 내에 증착될 수 있다. 일반적으로, 크롬층은 증발 증착에 의해 형성된다. 게이트 구조는 다음에 백금 및 금의 증착에 의해 완성될 수 있다. 더 도해되는 것처럼, 소스 콘택(26) 및 p<sup>+</sup> 콘택은 단일 오버레이어(28)를 공유하는데, 이것은 소스를 고농도로 도핑된 p-타입 도전성 영역(14)과 전기적으로 연결한다.

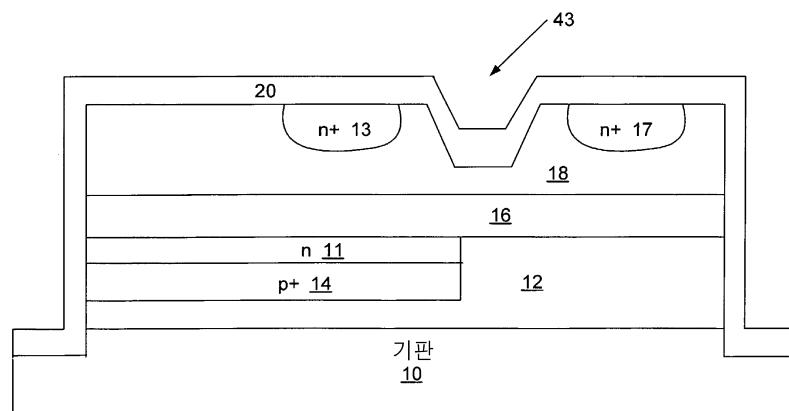

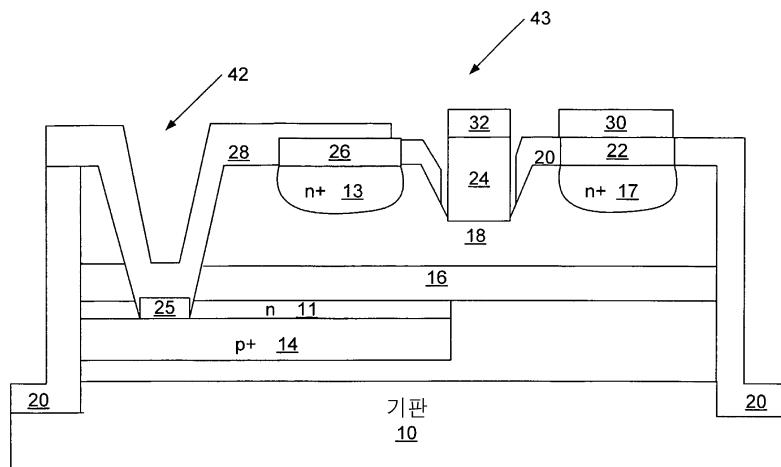

[0069] 도 3을 이제 참조하면, 본 발명의 다른 실시예들에 따른 트랜지스터의 단면도가 설명된다. 동일한 참조번호는 앞에서 설명된 도면들에서 동일한 요소들을 언급하고, 따라서, 이러한 요소들의 상세한 설명들은 생략될 수 있다. 도 3에서 도시된 것처럼, 본 발명의 어떠한 실시예들에서, p<sup>+</sup> 도전성 영역(14) 및 n-타입 도전성 영역은 기판(10) 내에 제공될 수 있다.

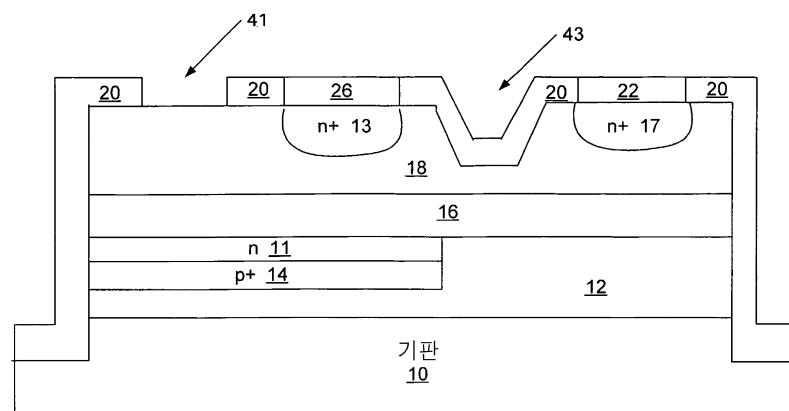

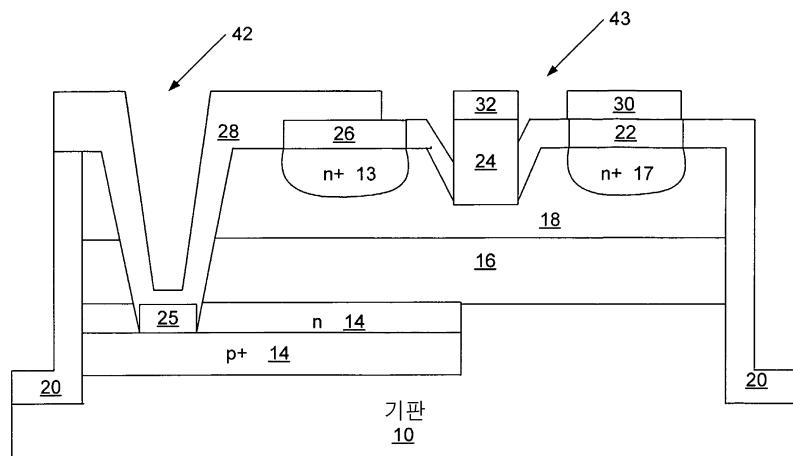

[0070] 도 4를 이제 참조하면, 본 발명의 다른 실시예들에 따른 트랜지스터의 단면도가 설명된다. 동일한 참조번호는 앞에서 설명된 도면들에서 동일한 요소들을 언급하고, 따라서, 이러한 요소들의 상세한 설명들은 생략될 수 있다. 도 4에서 도시된 것처럼, 본 발명의 어떠한 실시예들은 단일(single) 리세스(43) 대신에 이중(double) 리세스 구조를 포함할 수 있다. 도 4에서 도해된 것처럼, 이중 리세스 구조의 제1 리세스(53)는 제1 리세스(53)를 위한 마스크를 형성하고 마스크에 따라 제1 리세스(53)를 형성하기 위해 제1 n-타입 도전성 채널층(19)을 관통하여 식각함으로써 형성될 수 있다. 제1 리세스(53)가 형성된 후에 절연층이 형성될 수 있다. 도 2f에서 도해된 것처럼 오믹 콘택들을 형성한 이후에, 이중 리세스 구조의 제2 리세스(54)가 제2 리세스를 위한 제2 마스크를 형성하고 마스크에 따라 리세스를 식각함으로써 형성될 수 있다. 제2 리세스(54)를 형성하기 위하여 제2 n-타입 도전성 채널층(15)이 예를 들어, 약 600Å의 거리만큼 내부로 식각될 수 있다. 이중 리세스 구조를 제조하는 방법들이 Sriram등이 발명하고 공동으로 양도된 미국 특허 출원 일련번호 10/136,456에 더욱 상세하게 설명된다.

[0071] 도 5를 이제 참조하면, 본 발명의 또 다른 실시예들에 따른 MESFET의 단면도가 설명된다. 동일한 참조번호들은 앞에서 설명된 도면들에서 동일한 요소들을 언급하고, 따라서, 이러한 요소들의 상세한 설명들은 생략될 수 있다. 도 5에서 도해된 것처럼, 게이트 콘택(24)이 n-타입 도전성 채널층(18) 상에 배치되고 단일 또는 이중 리세

스에는 배치되지 않는다.

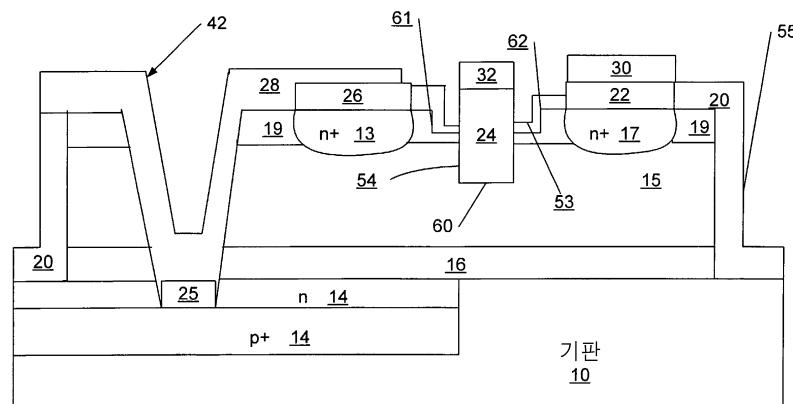

[0072] 도 6을 이제 참조하면, 본 발명의 어떠한 실시예들에 따른 MESFET의 단면도가 설명된다. 동일한 참조번호들은 앞에서 설명된 도면들에서 동일한 요소들을 언급하고, 따라서, 이러한 요소들의 상세한 설명들은 생략될 수 있다. 도 6에서 도해된 것처럼, 제1 p-타입 도전성 영역( $p^+$  영역, 14)의 캐리어 농도보다 더 작은 캐리어 농도를 가지는 제2 p-타입 도전성 영역(21)이 제공된다. 거기에서 더 도해되는 것처럼, 제1 및 제2 p-타입 도전성 영역들(14 및 21)이 n-타입 도전성 영역(11)의 두 개의 표면들 상에서 제공되도록 제2 p-타입 도전성 영역(21)이 제1 p-타입 도전성 영역(14)의 일단에서부터 게이트 콘택(24)의 아래까지 신장할 수 있다. 앞에서 설명된 것처럼, 게이트 콘택(24)은 제1 측벽(31) 및 제2 측벽(33)을 가진다. 제1 측벽(31)은 소스 영역(13)에 인접하고 제2 측벽(33)은 드레인 영역(17)에 인접한다. 제2 p-타입 도전성 영역(21)은 제1 p-타입 도전성 영역(14)의 일단에서부터 게이트 콘택의 제2 측벽을 지나서 신장하지 않으면서 게이트 콘택(24)의 제2 측벽(33)까지 신장할 수 있거나 또는 제1 p-타입 도전성 영역(14)의 일단에서부터 게이트 콘택(24)의 제1 측벽(31)과 제2 측벽(33) 사이까지 신장할 수 있다. 일반적으로, 제2 p-타입 도전성 영역은 게이트 콘택(24)의 제1 측벽(31)과 제2 측벽(33) 사이의 약 절반까지 신장한다.

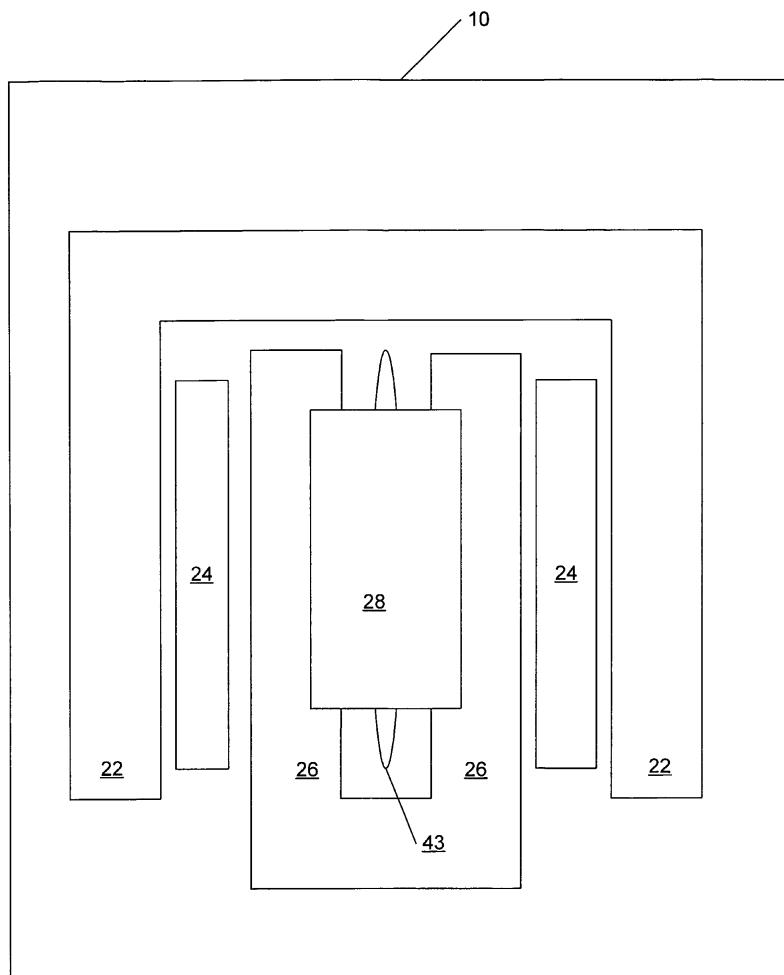

[0073] 이제 도 7을 참조하면, 본 발명의 어떠한 실시예들에 따른 MESFETs의 평면도(top view)가 설명된다. 도 7에서 도해되는 것처럼, 복수개의 단위 셀들이 기판(10) 상에 제공된다. 게이트 콘택(24)이 소스 콘택(26)과 드레인 콘택(22) 사이에 위치한다. 도 7에서 도해되는 것처럼, 소스 콘택들(26) 및 드레인 콘택들(22)이 서로 맞물린다. 오버레이어(28)가 소스 콘택(26)과 콘택 비아 홀(43)에 배치되는  $p^+$  콘택(미도시)을 통하여  $p^+$  영역(미도시)을 전기적으로 연결한다.

[0074] 본 발명이 특별한 층들, 영역들 및 리세스들을 가지는 특별한 MESFETs에 대하여 앞에서 설명되지만, 본 발명의 실시예들이 앞에서 설명된 MESFETs에 한정되지 않는다는 것이 이해될 수 있다. 본 발명의 실시예들에 따른 소스 영역 아래의 p-타입 및 n-타입 도전성 영역들은 다른 타입의 트랜지스터들로 구체화될 수 있다. 예를 들어, 본 발명의 실시예들에 따른 p-타입 도전성 영역은 *Silicon Carbide Metal Semiconductor Field Effect Transistors*라는 명칭으로 Allen등이 발명하고 공동으로 양도된 미국 특허 번호 6,686,616에 기술된 MESFETs로 구체화될 수 있고, 상기 발명의 내용은 전부 설명된 것처럼 여기에 인용하여 여기에 통합된다.

[0075] 본 발명이 SiC MESFETs에 대하여 앞에서 설명되지만, 본 발명은 SiC MESFETs에 한정되지 않는다. 예를 들어, 본 발명의 실시예들에 따른 MESFETs는, 예를 들어, 갈륨 아세나이드(GaAs) MESFETs 또는 갈륨 나이트라이드(GaN) MESFETs일 수 있다. 특히, 본 발명이 GaAs MESFETs에 관하여 기술되면, p-타입 도전성 영역들은 p-타입 도전성 GaAs 영역들일 수 있고, n-타입 도전성 채널층들은 n-타입 도전성 GaAs층들 등일 수 있다. 더욱이, 본 발명의 어떠한 실시예들에 따른 MESFETs은, 예를 들어, SiC MESFET MMICs, GaN HEMTs, GaN HEMT MMICs, GaAs MESFETs, GaAs MESFET MMICs, GaAs HEMTs, GaAs HEMT MMICs, GaAs pHEMTs, GaAs pHEMT MMICs 등일 수 있다.

[0076] 도면들 및 명세서에서, 발명의 일반적인 바람직한 실시예들이 개시되고, 비록 특정한 용어들이 사용되더라도, 그들은 일반적이고 기술적인 의미로 사용되며 한정의 목적으로 사용되지 않으며, 발명의 범위는 다음의 청구범위에서 기술된다.

### 산업상 이용 가능성

[0077] 본 발명에 의해 개선된 트랜지스터 및 그의 형성방법을 구현할 수 있다.

### 도면의 간단한 설명

[0025] 도 1은 본 발명의 어떠한 실시예들에 따른 트랜지스터의 단면도이다.

[0026] 도 2a 내지 2h는 본 발명의 어떠한 실시예들에 따른 트랜지스터들을 제조하는 공정 단계들을 도해한다.

[0027] 도 3은 본 발명의 다른 실시예들에 따른 트랜지스터의 단면도이다.

[0028] 도 4는 본 발명의 또 다른 실시예들에 따른 트랜지스터의 단면도이다.

[0029] 도 5는 본 발명의 어떠한 실시예들에 따른 트랜지스터의 단면도이다.

[0030] 도 6은 본 발명의 다른 실시예들에 따른 트랜지스터의 단면도이다.

[0031] 도 7은 본 발명의 어떠한 실시예들에 따른 트랜지스터의 평면도이다.

## 도면

## 도면1

## 도면2a

## 도면2b

도면2c

도면2d

도면2e

도면2f

도면2g

## 도면2h

## 도면3

## 도면4

## 도면5

## 도면6

도면7