(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-267366

(P2009-267366A)

(43) 公開日 平成21年11月12日(2009.11.12)

(51) Int.Cl.

HO1L 21/8247 (2006.01)

HO1L 29/788 (2006.01)

HO1L 29/792 (2006.01)

HO1L 27/115 (2006.01)

F 1

HO1L 29/78 371

HO1L 27/10 434

テーマコード(参考)

5FO83

5F1O1

審査請求 未請求 請求項の数 11 O L (全 15 頁)

(21) 出願番号 特願2009-30450 (P2009-30450)

(22) 出願日 平成21年2月12日 (2009.2.12)

(31) 優先権主張番号 特願2008-96373 (P2008-96373)

(32) 優先日 平成20年4月2日 (2008.4.2)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 302062931

NECエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080816

弁理士 加藤 朝道

(72) 発明者 張 紫園

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

F ターム(参考) 5F083 EP02 EP18 EP22 EP23 EP43

EP44 EP45 EP48 EP49 EP50

EP53 EP56 EP57 GA21 GA25

GA27 JA03 JA05 JA19 JA60

MA06 MA16 MA19 MA20 PR12

PR21 PR33

最終頁に続く

(54) 【発明の名称】半導体記憶装置及びその製造方法

## (57) 【要約】

【課題】メモリセルにおけるゲート絶縁膜(トンネル絶縁膜)の改善によってデバイスの動作の信頼性を向上させること。

【解決手段】シリコン基板1とゲート電極4の間に、シリコン基板1側から順にシリコン酸化膜3f、シリコン窒化膜3d、シリコン酸化膜3bが積層した絶縁膜3が介在した半導体記憶装置であって、シリコン酸化膜3fとシリコン窒化膜3dの間の界面、シリコン窒化膜3dとシリコン酸化膜3bの間の界面、及びシリコン酸化膜3bとゲート電極4の間の界面の全ての界面に水素吸蔵膜3a、3c、3eが介在する。

【選択図】図1

(実施例1)

## 【特許請求の範囲】

## 【請求項 1】

シリコン基板とゲート電極の間に、前記シリコン基板側から順に第1シリコン酸化膜、シリコン窒化膜、第2シリコン酸化膜が積層した絶縁膜が介在した半導体記憶装置であつて、

前記第1シリコン酸化膜と前記シリコン窒化膜の間の界面、前記シリコン窒化膜と前記第2シリコン酸化膜の間の界面、及び前記第2シリコン酸化膜と前記ゲート電極の間の界面の全て又は少なくとも1つの界面に水素吸蔵膜が介在することを特徴とする半導体記憶装置。

## 【請求項 2】

シリコン基板とゲート電極の間に、前記シリコン基板側から順に第1シリコン酸化膜、シリコン窒化膜、第2シリコン酸化膜が積層した絶縁膜が介在した半導体記憶装置であつて、

前記シリコン窒化膜と前記第2シリコン酸化膜の間の界面、及び前記第2シリコン酸化膜と前記ゲート電極の間の界面のそれぞれに水素吸蔵膜が介在することを特徴とする半導体記憶装置。

## 【請求項 3】

前記水素吸蔵膜は、 $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜であることを特徴とする請求項1又は2記載の半導体記憶装置。

## 【請求項 4】

前記水素吸蔵膜の水素濃度は、 $3 \times 10^{19} \text{ atom/cm}^3$ より高いことを特徴とする請求項1乃至3のいずれか一に記載の半導体記憶装置。

## 【請求項 5】

シリコン基板の表面にシリコン酸化膜を成膜する工程と、

前記シリコン酸化膜を窒化して $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜を形成する工程と、

を含むことを特徴とする半導体記憶装置の製造方法。

## 【請求項 6】

シリコン酸化膜上にシリコン窒化膜を成膜する工程と、

前記シリコン窒化膜の表面を酸化して $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜を形成する工程と、

を含むことを特徴とする半導体記憶装置の製造方法。

## 【請求項 7】

前記シリコン酸化膜の表面を窒化して $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜を形成する工程と、

前記シリコン窒化酸化膜上にシリコン酸化膜を成膜する工程と、

を含むことを特徴とする半導体記憶装置の製造方法。

## 【請求項 8】

シリコン基板の表面に第1シリコン酸化膜を成膜する工程と、

前記第1シリコン酸化膜上にシリコン窒化膜を成膜する工程と、

前記シリコン窒化膜の表面を酸化して $\text{Si}_2\text{N}_2\text{O}$ を含む第1シリコン窒化酸化膜を形成する工程と、

前記シリコン窒化膜と第1シリコン窒化酸化膜の間に、前記第1シリコン窒化酸化膜側から順に、第2シリコン酸化膜と、 $\text{Si}_2\text{N}_2\text{O}$ を含む第2シリコン窒化酸化膜とを形成する工程と、

を含むことを特徴とする半導体記憶装置の製造方法。

## 【請求項 9】

前記第1シリコン窒化酸化膜を形成する工程では、前記シリコン窒化膜の表面を大気に触れさせ、 $\text{N}_2$ 又は $\text{Ar}$ 雰囲気中で900以上かつ1150以下の温度でアニールすることにより前記第1シリコン窒化酸化膜を形成することを特徴とする請求項8記載の半

10

20

30

40

50

導体記憶装置の製造方法。

【請求項 10】

前記第2シリコン酸化膜、前記第2シリコン窒化酸化膜を形成する工程では、H<sub>2</sub> / O<sub>2</sub>を含むガスによる湿式酸化を行うことによって前記第2シリコン酸化膜、前記第2シリコン窒化酸化膜を形成することを特徴とする請求項8又は9記載の半導体記憶装置の製造方法。

【請求項 11】

前記第1シリコン窒化酸化膜を形成する工程の後、前記第2シリコン酸化膜、前記第2シリコン窒化酸化膜を形成する工程を行うまでの大気中での引き置き時間は、7時間以内であることを特徴とする請求項8乃至10のいずれか一に記載の半導体記憶装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、不揮発性メモリセルを有する半導体記憶装置及びその製造方法に関し、特に、メモリセルにおいてONO膜よりなるゲート絶縁膜（トンネル絶縁膜）を有する半導体記憶装置及びその製造方法に関する。

【背景技術】

【0002】

不揮発性メモリセルにおいて、シリコン基板とゲート電極の間に介在するゲート絶縁膜（トンネル絶縁膜）には、チャージをトラップすることができるONO膜（シリコン酸化膜／シリコン窒化膜／シリコン酸化膜）が広く用いられている。ONO膜に関して以下のようないかで述べる。

【0003】

例えば、特許文献1では、基板上にボトム酸化物膜と窒化物膜を成膜した後、パターン化し、その後、ラジカル酸化剤を含む雰囲気中で急速熱酸化することでパターン化された表面及び側壁上に酸化皮膜を形成する技術が開示されている。これにより、加工時間を短縮し、熱負荷を減少した信頼性を有するONO構造が得られるとしている。

【0004】

特許文献2では、シリコン膜を酸化する酸化工程と、該酸化工程の後に、チャンバ内を減圧状態にする工程と、前記チャンバに窒素化作用を有する気体を供給しながら、酸化されたシリコン膜を窒化する窒化工程とを有する酸化膜の作製方法において、前記窒化工程時の水の濃度を1ppm以上10ppm以下とし、前記窒化作用を有する気体は、一酸化窒素又は一酸化二窒素とする技術が開示されている。酸化工程で成膜された酸化シリコン膜を一酸化窒素雰囲気又は一酸化二窒素雰囲気中で900℃以上の加熱処理をおこなうと、窒素によって不対結合手が埋められたり、酸化珪素膜中のSi-H結合やSi-OH結合が窒化あるいは酸化され、Si-N、あるいはSi<sub>2</sub>=N-O結合に変化し、酸化珪素膜中の水素は減少するとされている。

【0005】

非特許文献1では、ONO膜においてトップ酸化膜と窒化膜の間にSiON薄膜を有するものの、すなわち、SiO<sub>2</sub> / SiON / SiN / SiO<sub>2</sub>構造が開示されている。SiON薄膜は、窒化膜の熱酸化、又は、LPCVD (Low Pressure Chemical Vapor Deposition) によって成膜され、Si成分が過剰であるとされている。また、SiON薄膜は、SiNよりも電荷を効率よく捕捉するとされている。

【0006】

非特許文献2では、ONO膜においてトップ酸化膜と窒化物の界面にて窒素含有層が存在し、窒素含有層によってSi / SiO<sub>2</sub>界面での水素原子の含有量を減少させるものが開示されている。

【先行技術文献】

【特許文献】

10

20

30

40

50

## 【0007】

【特許文献1】特開2005-159266号公報

【特許文献2】特開平9-115904号公報

【非特許文献】

## 【0008】

【非特許文献1】Szu-Yu Wang、外8名、「Effect of fabrication process on the charge trapping behavior of SiON thin films」、Solid-State electronics、50号、2006年、p. 1171-1174

【非特許文献2】Igor Levin、外7名、「Structure, Chemistry, and Electrical Performance of Silicon Oxide-Nitride-Oxide Stacks on Silicon」、Journal of the Electrochemical Society、151巻、12号、2004年、p. G833-G838

10

【非特許文献3】Kazumasa Nomoto、外2名、「Data retention improvement of metal-oxide-nitride-oxide-semiconductor memories using silicon-tetrachloride-based silicon nitride with Ultralow Si-H bond density」、Japanese Journal of Applied Physics、Vol.43、No.4B、2004年、p. 2211-2216

【非特許文献4】Yen-Hao Shih、外11名、「Highly reliable 2-bit/cell nitride trapping flash memory using a novel array-nitride-sealing (ANS) ONO process」、0-7803-9269-8/05/\$20.00、米国、アメリカ電気・電子通信学会(IEEE)、2005年

【非特許文献5】G. Rosenman、外3名、「Deep traps in oxide-nitride-oxide stacks fabricated from hydrogen and deuterium containing precursors」、Journal of Applied Physics、99、023702、2006年

20

【非特許文献6】Yuji Yatsuda、外3名、「Effects of high temperature hydrogen annealing on n-channel Si-Gate MNOS devices」、Proc. 11th Conf. Solid State Devices、1979年、p. 219-224

【非特許文献7】Z. Liu、外6名、「Hydrogen Distribution in Oxide-Nitride-Oxide Stacks and Correlation with Data Retention of MONOS Memories」、IEEE proc. of IRPS, 2008, pp. 705-706.

【非特許文献8】Z. Liu、外5名、「A hydrogen storage layer on the surface of silicon nitride films」、Appl. Phys. Lett., 92, 192115(2008).

【発明の概要】

30

【発明が解決しようとする課題】

## 【0009】

ところで、ONO膜と水素原子の関係について、ONO膜における水素原子が電子トラップに悪影響を与えるのでONO膜中から水素原子を排除すべきとする「水素排除説」(非特許文献3、4参照)と、ONO膜における水素原子が電子トラップに寄与するのでONO膜中に水素原子が必要であるとする「水素必要説」(非特許文献5、6参照)がある。

## 【0010】

従来技術は、水素排除説に基づいて改良されたものであり、ONO膜中の水素濃度を減少させることで、ONO膜中の電子トラップ量を減少させて、電子トラップ量の変動を小さくしているが、トランジスタのしきい値電圧V<sub>t</sub>を所定の大きさに確保することができないおそれがある。一方、水素必要説によりONO膜中の水素濃度を確保することでトランジスタのしきい値電圧V<sub>t</sub>を所定の大きさに確保することができるが、ONO膜中の電子トラップ量が変動しやすく、トランジスタのしきい値電圧V<sub>t</sub>が変動するおそれがある。よって、両方の説を満たすようにONO膜を改善する余地がある。

40

## 【0011】

本発明の主な課題は、メモリセルにおけるゲート絶縁膜(トンネル絶縁膜)の改善によってデバイスの動作の信頼性を向上させることである。

【課題を解決するための手段】

## 【0012】

50

本発明の第1の視点においては、シリコン基板とゲート電極の間に、前記シリコン基板側から順に第1シリコン酸化膜、シリコン窒化膜、第2シリコン酸化膜が積層した絶縁膜が介在した半導体記憶装置であって、前記第1シリコン酸化膜と前記シリコン窒化膜の間の界面、前記シリコン窒化膜と前記第2シリコン酸化膜の間の界面、及び前記第2シリコン酸化膜と前記ゲート電極の間の界面の全て又は少なくとも1つの界面に水素吸蔵膜が介在することを特徴とする。

【0013】

本発明の第2の視点においては、シリコン基板とゲート電極の間に、前記シリコン基板側から順に第1シリコン酸化膜、シリコン窒化膜、第2シリコン酸化膜が積層した絶縁膜が介在した半導体記憶装置であって、前記シリコン窒化膜と前記第2シリコン酸化膜の間の界面、及び前記第2シリコン酸化膜と前記ゲート電極の間の界面のそれぞれに水素吸蔵膜が介在することを特徴とする。

10

【0014】

本発明の前記半導体記憶装置において、前記水素吸蔵膜は、 $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜であることが好ましい。

【0015】

本発明の前記半導体記憶装置において、前記水素吸蔵膜の水素濃度は、 $3 \times 10^{-9}$  atom/cm<sup>3</sup>より高いことが好ましい。

20

【0016】

本発明の第3の視点においては、半導体記憶装置の製造方法において、シリコン基板の表面にシリコン酸化膜を成膜する工程と、前記シリコン酸化膜を窒化して $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜を形成する工程と、を含むことを特徴とする。

【0017】

本発明の第4の視点においては、半導体記憶装置の製造方法において、シリコン酸化膜上にシリコン窒化膜を成膜する工程と、前記シリコン窒化膜の表面を酸化して $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜を形成する工程と、を含むことを特徴とする。

【0018】

本発明の第5の視点においては、半導体記憶装置の製造方法において、前記シリコン酸化膜の表面を窒化して $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜を形成する工程と、前記シリコン窒化酸化膜上にシリコン酸化膜を成膜する工程と、を含むことを特徴とする。

30

【0019】

本発明の第6の視点においては、半導体記憶装置の製造方法において、シリコン基板の表面に第1シリコン酸化膜を成膜する工程と、前記第1シリコン酸化膜上にシリコン窒化膜を成膜する工程と、前記シリコン窒化膜の表面を酸化して $\text{Si}_2\text{N}_2\text{O}$ を含む第1シリコン窒化酸化膜を形成する工程と、前記シリコン窒化膜と第1シリコン窒化酸化膜の間に、前記第1シリコン窒化酸化膜側から順に、第2シリコン酸化膜と、 $\text{Si}_2\text{N}_2\text{O}$ を含む第2シリコン窒化酸化膜とを形成する工程と、を含むことを特徴とする。

【0020】

本発明の前記半導体記憶装置の製造方法において、前記第1シリコン窒化酸化膜を形成する工程では、前記シリコン窒化膜の表面を大気に触れさせ、 $\text{N}_2$ 又はAr雰囲気中で900以上かつ1150以下の温度でアニールすることにより前記第1シリコン窒化酸化膜を形成することが好ましい。

40

【0021】

本発明の前記半導体記憶装置の製造方法において、前記第2シリコン酸化膜、前記第2シリコン窒化酸化膜を形成する工程では、 $\text{H}_2/\text{O}_2$ を含むガスによる湿式酸化を行うことによって前記第2シリコン酸化膜、前記第2シリコン窒化酸化膜を形成することが好ましい。

【0022】

本発明の前記半導体記憶装置の製造方法において、前記第1シリコン窒化酸化膜を形成する工程の後、前記第2シリコン酸化膜、前記第2シリコン窒化酸化膜を形成する工程を

50

行うまでの大気中での引き置き時間は、7時間以内であることが好ましい。

【発明の効果】

【0023】

本発明によれば、シリコン基板とゲート電極の間に介在するONO膜における界面に水素吸蔵膜が介在することで、シリコン基板の表面のシリコン酸化膜への水素拡散をブロックするとともに、電子トラップに寄与する水素を界面位置に安定に固定することができる。その結果、書換えによる電子トラップの劣化が改善され、読み出しへストレスによるしきい値電圧Vtシフトの変動を抑えることができる。ONOタイプの不揮発メモリの書換え後の保持劣化・RDT劣化(しきい値電圧の劣化)などが改善できる。SiON層は水素をブロックできるため、下層酸化膜への遊離水素の拡散を抑制できる。

10

【図面の簡単な説明】

【0024】

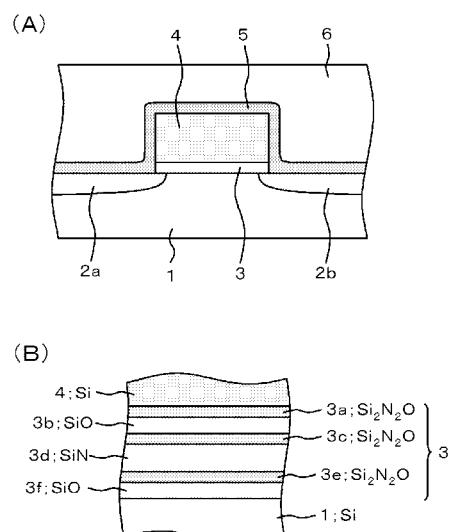

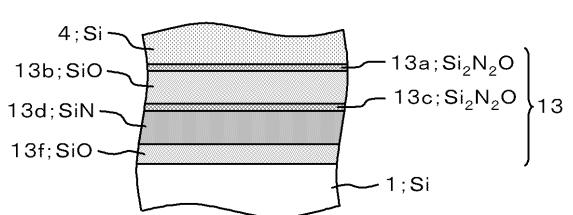

【図1】本発明の実施例1に係る半導体記憶装置におけるメモリセルの構成を模式的に示した(A)部分断面図、及び、(B)ゲート絶縁膜の拡大断面図である。

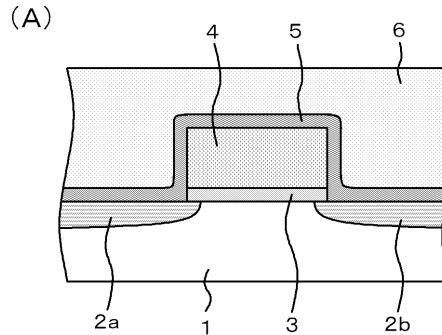

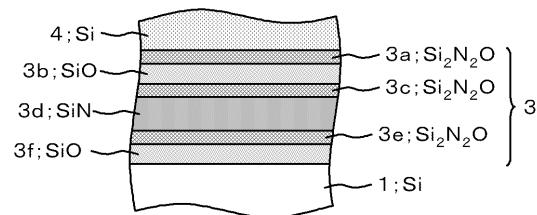

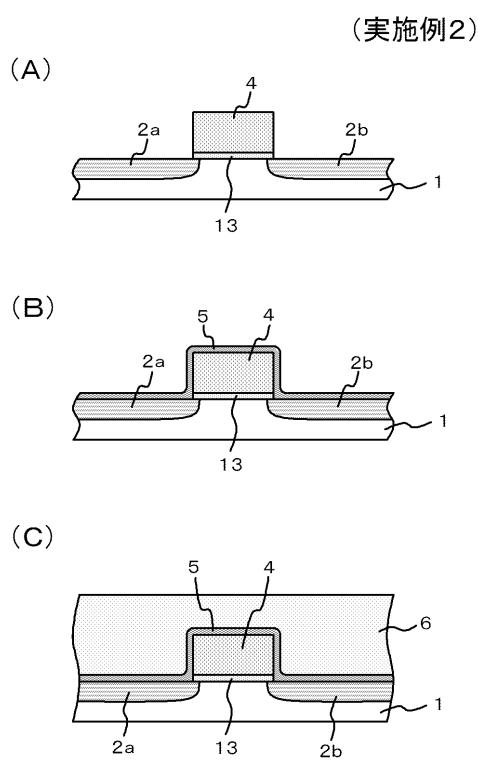

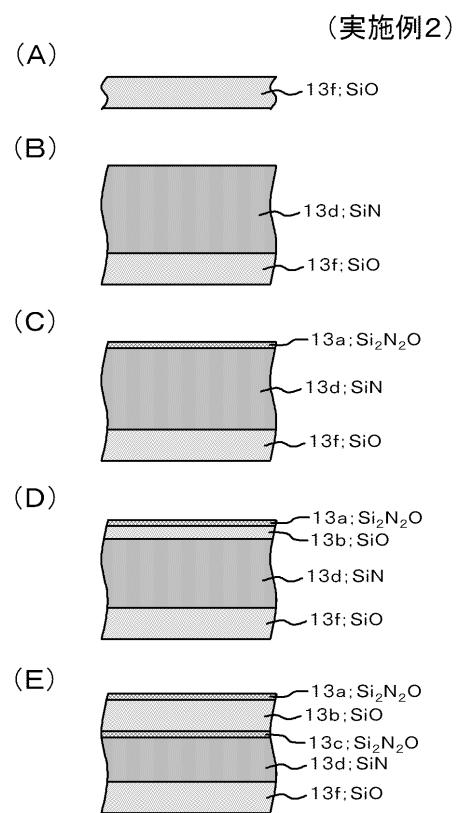

【図2】本発明の実施例2に係る半導体記憶装置におけるメモリセルの構成を模式的に示した(A)部分断面図、及び、(B)ゲート絶縁膜の拡大断面図である。

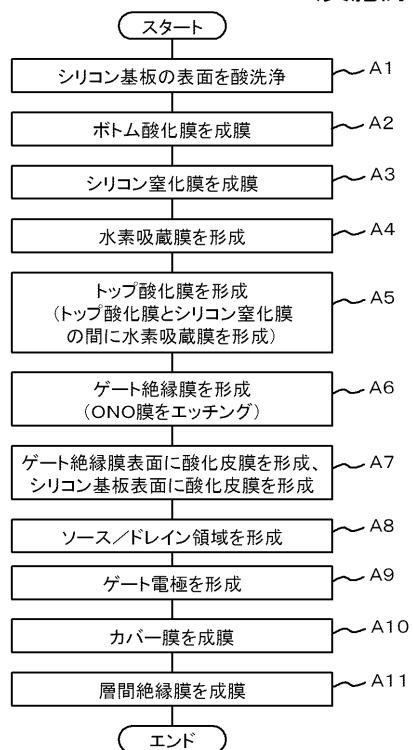

【図3】本発明の実施例2に係る半導体記憶装置の製造方法を模式的に示したフローチャートである。

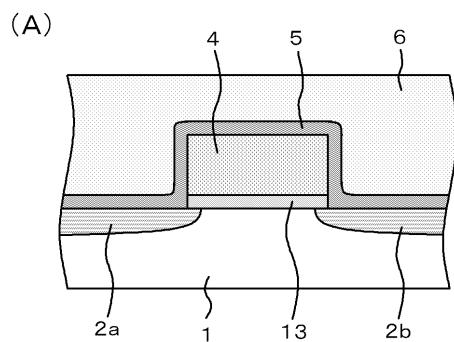

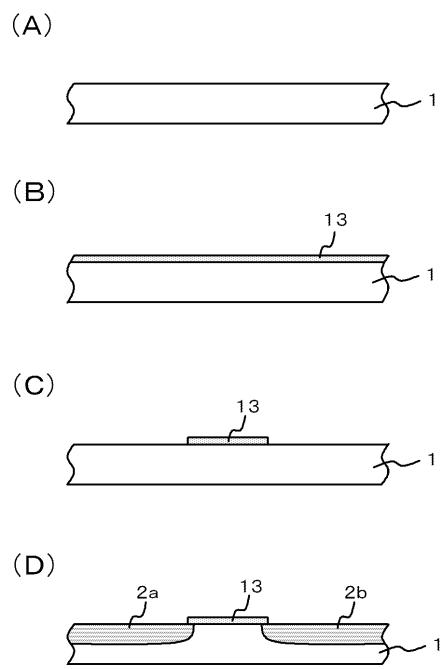

【図4】本発明の実施例2に係る半導体記憶装置の製造方法を模式的に示した第1の工程断面図である。

20

【図5】本発明の実施例2に係る半導体記憶装置の製造方法を模式的に示した第2の工程断面図である。

【図6】本発明の実施例2に係る半導体記憶装置におけるONO膜の製造工程を模式的に示した工程断面図である。

【発明を実施するための形態】

【0025】

本発明の実施形態では、シリコン基板(図1の1)とゲート電極(図1の4)の間に、前記シリコン基板(図1の1)側から順に第1シリコン酸化膜(図1の3f)、シリコン窒化膜(図1の3d)、第2シリコン酸化膜(図1の3b)が積層した絶縁膜(図1の3)が介在した半導体記憶装置であって、前記第1シリコン酸化膜(図1の3f)と前記シリコン窒化膜(図1の3d)の間の界面、前記シリコン窒化膜(図1の3d)と前記第2シリコン酸化膜(図1の3b)の間の界面、及び前記第2シリコン酸化膜(図1の3b)と前記ゲート電極(図1の4)の間の界面の全て又は少なくとも1つの界面に水素吸蔵膜(図1の3a、3c、3e)が介在する。

30

【実施例1】

【0026】

本発明の実施例1に係る半導体記憶装置について図面を用いて説明する。図1は、本発明の実施例1に係る半導体記憶装置におけるメモリセルの構成を模式的に示した(A)部分断面図、及び、(B)ゲート絶縁膜の拡大断面図である。

【0027】

図1(A)を参照すると、実施例1に係る半導体記憶装置におけるメモリセルでは、シリコン基板1(例えば、P型シリコン基板)におけるチャネルの両側に不純物(例えば、リン)が拡散したソース領域2a、ドレイン領域2bを有し、前記チャネル上にゲート絶縁膜3(トンネル絶縁膜)を介してゲート電極4(例えば、ポリシリコン)が形成されている。ゲート電極4及びソース・ドレイン領域2a、2bを含むメモリセル全体がカバー膜5(例えば、シリコン窒化膜)で覆われており、カバー膜5上に層間絶縁膜6(例えば、シリコン酸化膜)が形成されている。ゲート電極4は、ビア及び配線を通じてワード線(図示せず)と電気的に接続されている。ドレイン領域2bはビア及び配線を通じてビット線(図示せず)と電気的に接続されており、ソース領域2aはビア及び配線を通じてソース線と電気的に接続されている。なお、図1(A)に示したメモリセルのトランジスタ

40

50

の構成は一例であり、浮遊ゲート（フローティングゲート）を有する構成であってもよく、キャパシタであってもよい。

【0028】

図1(B)を参照すると、ゲート絶縁膜3(トンネル絶縁膜)は、シリコン基板1とゲート電極4の間に介在した絶縁膜である。ゲート絶縁膜3は、下層側から順に、シリコン酸化膜3f、水素吸蔵膜3e、シリコン窒化膜3d、水素吸蔵膜3c、シリコン酸化膜3b、水素吸蔵膜3aが積層したものである。ゲート絶縁膜3の水素濃度は、水素吸蔵膜3a、3c、3eから離れるにつれて、急激に低下するような急な濃度勾配を持つ。

【0029】

水素吸蔵膜3aは、水素原子を吸蔵する膜である。水素吸蔵膜3aは、シリコン酸化膜3bよりも多くの水素原子を含有する。水素吸蔵膜3aは、加熱により水素濃度を増加させることが可能である。水素吸蔵膜3aは、水素原子を吸蔵することで、シリコン酸化膜3bからの水素をブロックする機能を有し、ゲート電極4側に水素原子を通さないようにする。水素吸蔵膜3aの膜厚は、0nmより大きく、かつ、3nm未満である。水素吸蔵膜3aは、 $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜であり、その膜中の水素濃度が $3 \times 10^{19} \text{ atom/cm}^3$ (好ましくは $8 \times 10^{19} \text{ atom/cm}^3$ )を超える。なお、 $\text{Si}_2\text{N}_2\text{O}$ とは、SiとNとの組成比が2:2:1からなる化合物を表している。

【0030】

シリコン酸化膜3bは、 $\text{H}_2 + \text{O}_2$ 雰囲気で、ウェット酸化法により成膜した膜である。シリコン酸化膜3bの水素濃度は、水素原子が水素吸蔵膜3a及び水素吸蔵膜3cに吸引されて、水素吸蔵膜3a及び水素吸蔵膜3c中の水素濃度よりも低い。

【0031】

水素吸蔵膜3cは、水素原子を吸蔵する膜である。水素吸蔵膜3cは、シリコン酸化膜3b及びシリコン窒化膜3dよりも多くの水素原子を含有する。水素吸蔵膜3cは、加熱により水素濃度を増加させることができ。水素吸蔵膜3cは、水素原子を吸蔵することで、シリコン酸化膜3b - シリコン窒化膜3d間の水素原子の移動をブロックする機能を有する。水素吸蔵膜3cの膜厚は、0nmより大きく、かつ、3nm未満である。水素吸蔵膜3cは、 $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜であり、その膜中の水素濃度が $3 \times 10^{19} \text{ atom/cm}^3$ (好ましくは $8 \times 10^{19} \text{ atom/cm}^3$ )を超える。

【0032】

シリコン窒化膜3dは、シランヒアンモニアを原料ガスとしてCVD(Chemical Vapor Deposition)法により成膜した膜である。シリコン窒化膜3dの水素濃度は、水素原子が水素吸蔵膜3c及び水素吸蔵膜3eに吸引されて、水素吸蔵膜3c及び水素吸蔵膜3e中の水素濃度よりも低い。

【0033】

水素吸蔵膜3eは、水素原子を吸蔵する膜である。水素吸蔵膜3eは、シリコン酸化膜3f及びシリコン窒化膜3dよりも多くの水素原子を含有する。水素吸蔵膜3eは、加熱により水素濃度を増加させることができ。水素吸蔵膜3eは、水素原子を吸蔵することで、シリコン窒化膜3d中の水素原子をブロックする機能を有する。水素吸蔵膜3cの膜厚は、0nmより大きく、かつ、3nm以下である。水素吸蔵膜3eは、 $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜であり、その膜中の水素濃度が $3 \times 10^{19} \text{ atom/cm}^3$ (好ましくは $8 \times 10^{19} \text{ atom/cm}^3$ )を超える。

【0034】

シリコン酸化膜3fは、シリコン基板1の表面部分を熱酸化により成膜した膜である。シリコン酸化膜3fの水素濃度は、水素原子が水素吸蔵膜3eに吸引されて、水素吸蔵膜3e中の水素濃度よりも低い。

【0035】

なお、図1では、シリコン酸化膜3f - シリコン窒化膜3d間、シリコン窒化膜3d - シリコン酸化膜3b間、シリコン酸化膜3b - ゲート電極4間のそれぞれの界面に水素吸蔵膜3e、3c、3aが介在しているが、シリコン酸化膜3b、3f及びシリコン窒化膜

10

20

30

40

50

3 d 中の水素原子の引き付けることができれば、3つの界面のうち1又は2つの界面のみに水素吸蔵膜を介在させるようにしてもよい。

【0036】

水素吸蔵膜3a (Si<sub>2</sub>N<sub>2</sub>Oを含むシリコン窒化酸化膜)の製法については、シリコン窒化膜3dの表面部分をN<sub>2</sub>+O<sub>2</sub>アニール法により酸化したり、O<sub>3</sub>酸化法又はドライ酸化法による酸化後にISSG (In Situ Steam Generated)酸化法により酸化することで、水素吸蔵膜3aを得ることができる。酸化する際の温度は、900～1050 (O<sub>3</sub>酸化法の場合は400～1050)である。酸化する際の圧力は、数torr以上11気圧以下とする。

【0037】

水素吸蔵膜3c (Si<sub>2</sub>N<sub>2</sub>Oを含むシリコン窒化酸化膜)の製法については、シリコン窒化膜3dの表面部分をH<sub>2</sub>+O<sub>2</sub>雰囲気で、ウェット酸化法により酸化してシリコン酸化膜3bを形成する際に、シリコン酸化膜3bとシリコン窒化膜3dとの間に界面に水素吸蔵膜3cが形成される。ウェット酸化する際の温度は、800～1000である。酸化する際の圧力は、1torr以上500torr以下とする。また、H<sub>2</sub>/O<sub>2</sub>の流量比は、0.004以上0.4以下(特に好ましくは0.05以上0.33以下)である。

10

【0038】

水素吸蔵膜3e (Si<sub>2</sub>N<sub>2</sub>Oを含むシリコン窒化酸化膜)の製法については、シリコン酸化膜3fを形成した後、NH<sub>3</sub>ガスを用いて400～1050、数torr以上11気圧以下でアニールを行ったり、又は、窒素成分を含むプリカーサ(例えば、NH<sub>3</sub>、N<sub>2</sub>O、NO)を用いて400～1050、数torr以上11気圧以下で熱処理することにより、水素吸蔵膜3eを得ることができる。

20

【0039】

なお、水素吸蔵膜3a、3c、3eがSi<sub>2</sub>N<sub>2</sub>Oを含むシリコン窒化酸化膜であることは発明者の実験によって見出された。また、Si<sub>2</sub>N<sub>2</sub>Oが水素原子を吸蔵する機能を有し、かつ、水素原子・酸素原子の透過率が極めて低いことが発明者の実験によって見出された。その透過率は、酸素・窒素の比率に依存する。700以上で加熱する場合、SiO<sub>2</sub>、Si<sub>3</sub>N<sub>4</sub>から水素原子が追い出されるが、Si<sub>2</sub>N<sub>2</sub>Oは水素を吸い取る。

30

【0040】

ここで、特許文献1に記載のONO構造では、トップ酸化膜と窒化膜の間の界面で酸窒化物が存在するようであるが、ラジカル酸化剤を含む雰囲気中で急速熱酸化によって形成したものであるため、酸窒化物は酸素成分が多く水素濃度が低くなっている、酸窒化物は窒化膜中の水素原子を引きつける力がないと考えられる。

【0041】

なお、特許文献1では、基板上にボトム酸化物膜と窒化物膜を成膜した後、パターン化し、その後、900から1150の温度で加熱する加熱工程と、ラジカル酸化剤を含む雰囲気中で急速熱酸化するラジカル酸化工程と、によって、パターン化された表面及び側壁上に酸化皮膜を形成している。これにより、加工時間を短縮し、熱負荷を減少した信頼性を有するONO構造が得られるとされている。なお、特許文献1では、主にトップ酸化膜の成長についてラジカル酸化工程(H<sub>2</sub>/O<sub>2</sub>)の条件について記載されているが、加熱工程の雰囲気が記載されていない。また、特許文献1では、トラップユニットの最終構造はONO構造であるものの、電荷が主に窒化膜にトラップされるとしている。

40

【0042】

また、特許文献2に記載の酸化シリコン膜は、一酸化窒素雰囲気又は一酸化二窒素雰囲気中で900以上の加熱処理により窒化あるいは酸化されるため、膜中の水素が減少し、水素原子を引きつける力がないと考えられる。また、非特許文献1に記載のSiON薄膜は、その上層に高温酸化(HTO)されたトップ酸化膜が成膜されるため、膜中の水素が減少し、水素原子を引きつける力がないと考えられる。また、非特許文献2に記載のトップ酸化膜における窒素含有層は、トップ酸化膜が1000のスチーム酸化やTEOS

50

(テトラエトキシシラン)を670の加熱処理されるため、膜中の水素が減少し、水素原子を引きつける力がないと考えられる。

【0043】

一方、実施例1の水素吸蔵膜3a、3c、3eは、Si<sub>2</sub>N<sub>2</sub>Oを含むシリコン窒化酸化膜であり、水素原子を吸蔵する機能を有し、その膜中の水素濃度が3×10<sup>-9</sup>atom/cm<sup>3</sup>を超える。700以上で加熱する場合、SiO<sub>2</sub>、Si<sub>3</sub>N<sub>4</sub>中の水素原子が追い出されるが、Si<sub>2</sub>N<sub>2</sub>Oは水素を吸い取るため、シリコン酸化膜3b、3f及びシリコン窒化膜3dからの水素原子が水素吸蔵膜3a、3c、3eに吸蔵される。特許文献1に記載の酸窒化物や、特許文献2に記載の酸化シリコン膜における窒化酸化部分や、非特許文献1に記載のSiON薄膜や、非特許文献2に記載のトップ酸化膜における窒素含有層は、このような水素吸蔵性がなく、実施例1の水素吸蔵膜3a、3c、3e(Si<sub>2</sub>N<sub>2</sub>Oを含むシリコン窒化酸化膜)とは異なるものと解される。

10

【0044】

実施例1によれば、水素吸蔵膜3a、3c、3eが水素原子を吸い取る機能を有し、シリコン酸化膜3b、3f及びシリコン窒化膜3dにおける水素原子の拡散が抑制される。その結果、ゲート絶縁膜3中の水素濃度の変動が抑えられ、ゲート絶縁膜3中の電子トラップ量の変動が抑えられるので、デバイスの動作の信頼性を向上させることができる。つまり、ボトム側のシリコン酸化膜3fにおいて書換えによる自由水素の拡散が抑制されるとともに、シリコン窒化膜3dでの電子トラップに不可欠な安定な水素原子が水素吸蔵膜3c、3eで保持されるので、書き動作と消去動作のストレスに耐えることができ、安定した動作が実現される。

20

【実施例2】

【0045】

本発明の実施例2に係る半導体記憶装置について図面を用いて説明する。図2は、本発明の実施例2に係る半導体記憶装置におけるメモリセルの構成を模式的に示した(A)部分断面図、及び、(B)ゲート絶縁膜の拡大断面図である。

【0046】

実施例2は、ゲート絶縁膜13においてボトム酸化膜となるシリコン酸化膜13fとシリコン窒化膜13dとの間に水素吸蔵膜(図1の3eに相当するもの)が存在しない点で実施例1と異なる。また、実施例2は、ゲート絶縁膜13における水素吸蔵膜13c、シリコン酸化膜13b、及び水素吸蔵膜13aの成膜方法が実施例1と異なる。

30

【0047】

図2(A)を参照すると、実施例2に係る半導体記憶装置におけるメモリセルでは、シリコン基板1(例えば、P型シリコン基板)におけるチャネルの両側に不純物(例えば、リン)が拡散したソース領域2a、ドレイン領域2bを有し、前記チャネル上にゲート絶縁膜13(トンネル絶縁膜)を介してゲート電極4(例えば、ポリシリコン)が形成されている。ゲート電極4及びソース・ドレイン領域2a、2bを含むメモリセル全体がカバー膜5(例えば、シリコン窒化膜)で覆われており、カバー膜5上に層間絶縁膜6(例えば、シリコン酸化膜)が形成されている。ゲート電極4は、ビア及び配線を通じてワード線(図示せず)と電気的に接続されている。ドレイン領域2bはビア及び配線を通じてビット線(図示せず)と電気的に接続されており、ソース領域2aはビア及び配線を通じてソース線と電気的に接続されている。なお、図2(A)に示したメモリセルのトランジスタの構成は一例であり、浮遊ゲート(フローティングゲート)を有する構成であってもよく、キャパシタであってもよい。

40

【0048】

図2(B)を参照すると、ゲート絶縁膜13(トンネル絶縁膜)は、シリコン基板1とゲート電極4の間に介在した絶縁膜である。ゲート絶縁膜13は、下層側から順に、シリコン酸化膜13f、シリコン窒化膜13d、水素吸蔵膜13c、シリコン酸化膜13b、水素吸蔵膜13aが積層したものである。ゲート絶縁膜13の水素濃度は、水素吸蔵膜13a、13cから離れるにつれて、急激に低下するような急な濃度勾配を持つ。

50

## 【0049】

水素吸蔵膜13aは、水素原子を吸蔵する膜である。水素吸蔵膜13aは、シリコン酸化膜13bよりも多くの水素原子を含有する。水素吸蔵膜13aは、加熱により水素濃度を増加させることが可能である。水素吸蔵膜13aは、水素原子を吸蔵することで、シリコン酸化膜13bからの水素をブロックする機能を有し、ゲート電極4側に水素原子を通さないようにする。水素吸蔵膜3aの膜厚は、0nmより大きく、かつ、3nm未満である。水素吸蔵膜13aは、 $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜であり、その膜中の水素濃度が $3 \times 10^{19} \text{ atom/cm}^3$ （好ましくは $8 \times 10^{19} \text{ atom/cm}^3$ ）を超える。なお、 $\text{Si}_2\text{N}_2\text{O}$ とは、SiとNとの組成比が2:2:1からなる化合物を表している。

10

## 【0050】

シリコン酸化膜13bの水素濃度は、水素原子が水素吸蔵膜13a及び水素吸蔵膜13cに吸引されて、水素吸蔵膜13a及び水素吸蔵膜13c中の水素濃度よりも低い。

## 【0051】

水素吸蔵膜13cは、水素原子を吸蔵する膜である。水素吸蔵膜13cは、シリコン酸化膜13b及びシリコン窒化膜13dよりも多くの水素原子を含有する。水素吸蔵膜13cは、加熱により水素濃度を増加させることが可能である。水素吸蔵膜13cは、水素原子を吸蔵することで、シリコン酸化膜13b-シリコン窒化膜13d間の水素原子の移動をブロックする機能を有する。水素吸蔵膜13cの膜厚は、0nmより大きく、かつ、3nm未満である。水素吸蔵膜13cは、 $\text{Si}_2\text{N}_2\text{O}$ を含むシリコン窒化酸化膜であり、その膜中の水素濃度が $3 \times 10^{19} \text{ atom/cm}^3$ （好ましくは $8 \times 10^{19} \text{ atom/cm}^3$ ）を超える。

20

## 【0052】

その他の構成は、実施例1と同様である。

## 【0053】

次に、本発明の実施例2に係る半導体記憶装置について図面を用いて説明する。図3は、本発明の実施例2に係る半導体記憶装置の製造方法を模式的に示したフローチャートである。図4、図5は、本発明の実施例2に係る半導体記憶装置の製造方法を模式的に示した工程断面図である。図6は、本発明の実施例2に係る半導体記憶装置におけるONO膜の製造工程を模式的に示した工程断面図である。

30

## 【0054】

まず、シリコン基板1の表面を酸洗浄する（ステップA1；図3、図4（A）参照）。これにより、シリコン基板1の表面の自然酸化膜が除去される。

## 【0055】

次に、シリコン基板1上にボトム酸化膜となるシリコン酸化膜13fを形成する（ステップA2；図3、図6（A）参照）。なお、シリコン酸化膜13fは、例えば、シリコン基板1の熱酸化により形成することができる。

40

## 【0056】

次に、シリコン酸化膜13f上にシリコン窒化膜13dを成膜する（ステップA3；図3、図6（B）参照）。なお、シリコン窒化膜13dは、例えば、シランとアンモニアを原料ガスとしてCVD法により成膜することができる。

## 【0057】

次に、シリコン窒化膜13d上に水素吸蔵膜13aを形成する（ステップA4；図3、図6（C）参照）。

## 【0058】

ここで、水素吸蔵膜13aは、安定な水素を貯蔵できる膜であり、酸素の拡散を律速できる拡散バリア層となる。また、水素吸蔵膜13aは、シリコン窒化膜13dへ供給する酸素分圧を調整する役割を有する。

## 【0059】

水素吸蔵膜13aの形成は、以下のようにして行う。まず、一度、シリコン窒化膜13

50

d の表面を大気に触れさせ、N<sub>2</sub> 霧囲気中 (Ar 霧囲気中でも可) で 900 ~ 1150 の温度でアニール (加熱処理) することにより、シリコン窒化膜 13d 表面に水素吸蔵膜 13a (Si<sub>2</sub>N<sub>2</sub>O を含むシリコン窒化酸化膜) を形成する。N<sub>2</sub> 霧囲気中でアニールしているのは、シリコン窒化膜 13d への酸素の巻き込み量を 6 × 10<sup>-4</sup> atom/cm<sup>2</sup> 以下制限できるからである。なお、水素吸蔵膜 13a の膜厚は、3 nm 未満である。

#### 【0060】

次に、シリコン窒化膜 13d と水素吸蔵膜 13a の間に、シリコン窒化膜 13d 側から順に水素吸蔵膜 13c (Si<sub>2</sub>N<sub>2</sub>O を含むシリコン窒化酸化膜)、シリコン酸化膜 13b を形成する (ステップ A5; 図 3、図 6 (E) 参照)。これにより、図 4 (B) のようなゲート絶縁膜 13 用の ONO 膜ができる。

10

#### 【0061】

水素吸蔵膜 13c、シリコン酸化膜 13b の形成は、最適化された H<sub>2</sub> / O<sub>2</sub> ガス流量比の中でシリコン窒化膜 13d を湿式酸化させることで形成することができる。この際、シリコン窒化膜 13d の表面に形成された水素吸蔵膜 13a は、酸素の拡散を律速できる拡散バリア層として機能する。水素吸蔵膜 13a は、一定な酸素分圧においてしか形成されないため、酸素分圧を制御するために、ステップ A4 においてシリコン窒化膜 13d の表面に水素吸蔵膜 13a を形成し、ステップ A5 においてシリコン窒化膜 13d へ拡散する酸素の量を制御している。シリコン窒化膜 13d の湿式酸化では、初期の段階では、図 6 (D) のように、酸素原子が水素吸蔵膜 13a を通過してシリコン窒化膜 13d に供給され、酸素とシリコン窒化膜 13d が反応してトップ酸化膜となるシリコン酸化膜 13b が形成され、副生した窒素が水素吸蔵膜 13a を通過して外に出ゆく。シリコン酸化膜 13b が厚くなってくると、シリコン窒化膜 13d に供給される酸素濃度が低くなってくるので、図 6 (E) のように、シリコン酸化膜 13b とシリコン窒化膜 13d の間に水素吸蔵膜 13c が形成される。なお、シリコン窒化膜 13d の湿式酸化では、蓋となる水素吸蔵膜 13a が消失しないで残っている。また、ステップ A4 からステップ A5 の間の大気中での引き置き時間は、7 時間以内であることが望ましい。

20

#### 【0062】

次に、所定のゲート長のゲート絶縁膜 13 を形成 (パターニング) する (ステップ A6; 図 3、図 4 (C) 参照)。これにより、ゲート絶縁膜 13 以外の領域には、シリコン基板 1 が露出する。なお、ゲート絶縁膜 13 の形成は、フォトレジストを用いて余分な ONO 膜をエッチングすることにより形成することができる。

30

#### 【0063】

次に、ゲート絶縁膜 13 及びシリコン基板 1 の表面に酸化皮膜を形成する (ステップ A7; 図 3 参照)。なお、酸化皮膜は、熱酸化により形成することができる。

#### 【0064】

次に、ゲート絶縁膜 13 をマスクとしてシリコン基板 1 上にソース領域 2a 及びドレイン領域 2b を形成する (ステップ A8; 図 3、図 4 (D) 参照)。なお、ソース領域 2a 及びドレイン領域 2b は、イオン注入により行われる。

40

#### 【0065】

次に、ゲート絶縁膜 13 上にゲート電極 4 を形成する (ステップ A9; 図 3、図 5 (A) 参照)。なお、ゲート電極 4 の形成では、ゲート絶縁膜 13、ソース領域 2a、及びドレイン領域 2b を含むシリコン基板 1 上に、ゲート電極 4 となるポリシリコンを成膜し、その後、フォトレジストを用いて、余分なポリシリコンをエッチングすることにより形成することができる。

#### 【0066】

次に、ゲート電極 4、ソース領域 2a、及びドレイン領域 2b を含むシリコン基板 1 上に、カバー膜 5 (例えば、シリコン窒化膜) を成膜する (ステップ A10; 図 3、図 5 (B) 参照)。

#### 【0067】

50

その後、カバー膜 5 上に層間絶縁膜 6 ( 例えば、シリコン酸化膜 ) を成膜する ( ステップ A 11 ; 図 3 、図 5 ( C ) 参照 ) 。これにより、図 2 と同様な半導体記憶装置ができる。

#### 【 0 0 6 8 】

実施例 2 によれば、トップ酸化膜となるシリコン酸化膜 13 b とシリコン窒化膜 13 d の界面に安定な水素吸蔵膜 13 c が形成できるので、電子トラップ量が抑えられると同時に、シリコン窒化膜 13 d における水素原子の拡散を制限できるため、信頼性の高いメモリが得られる。

#### 【 0 0 6 9 】

なお、本発明は、先の特許出願：特願 2008-096373 号 ( 2008 年 4 月 2 日出願 ) の国内優先権主張に基づくものであり、出願の全記載内容は引用をもって本書に組み込み記載されているものとする。また、同出願の後に、同出願の発明者らによって、以下の事項が開示されている。非特許文献 7 では、書換え後のシリコン窒化膜での水素原子の保持劣化を改善するには、上層のシリコン酸化膜と中間のシリコン窒化膜との界面に安定な水素を貯蔵できる界面層の形成が有効であることが開示されている。また、非特許文献 8 では、安定な水素を貯蔵できる界面層はシリコン酸窒化膜であることが開示されている。ただし、非特許文献 7 、 8 では、本発明の実施例 2 に係る半導体記憶装置の製造方法が開示されていない。

#### 【 0 0 7 0 】

本発明は、上記実施例を基に説明したが、上記実施例に限定されることなく、本発明の範囲内において種々の変更、変形、改良等を含むことはいうまでもない。また、本発明の範囲内において、開示した要素の多様な組み合わせ、置換ないし選択が可能である。

#### 【 0 0 7 1 】

本発明のさらなる課題・目的及び展開形態は、請求の範囲を含む本発明の全開示事項からも明らかにされる。

#### 【 符号の説明 】

#### 【 0 0 7 2 】

- 1 シリコン基板

- 2 a ソース領域

- 2 b ドレイン領域

- 3 、 13 ゲート絶縁膜 ( トンネル絶縁膜 )

- 3 a 、 13 a 水素吸蔵膜 ( 第 1 シリコン窒化酸化膜 )

- 3 b 、 13 b シリコン酸化膜 ( トップ酸化膜、第 2 シリコン酸化膜 )

- 3 c 、 13 c 水素吸蔵膜 ( 第 2 シリコン窒化酸化膜 )

- 3 d 、 13 d シリコン窒化膜

- 3 e 水素吸蔵膜

- 3 f 、 13 f シリコン酸化膜 ( ボトム酸化膜、第 1 シリコン酸化膜 )

- 4 ゲート電極

- 5 カバー膜

- 6 層間絶縁膜

10

20

30

40

【図1】

(実施例1)

(B)

【図2】

(実施例2)

(B)

【図3】

(実施例2)

【図4】

(実施例2)

【図5】

【図6】

---

フロントページの続き

F ターム(参考) 5F101 BA23 BA26 BA35 BA36 BA45 BA48 BA53 BB02 BB05 BD02

BF03 BH02 BH03 BH04 BH16