(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-295629

(P2005-295629A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.C1.<sup>7</sup>

H02M 3/155

F 1

H02M 3/155

H02M 3/155

H02M 3/155

テーマコード(参考)

5 H 7 3 O

H

T

審査請求 未請求 請求項の数 5 O L (全 9 頁)

(21) 出願番号

特願2004-104470 (P2004-104470)

(22) 出願日

平成16年3月31日 (2004.3.31)

(71) 出願人 000006220

ミツミ電機株式会社

東京都多摩市鶴牧2丁目11番地2

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 鈴木 雅之

神奈川県厚木市酒井1601 ミツミ電機

株式会社厚木事業所内

(72) 発明者 竹下 順司

神奈川県厚木市酒井1601 ミツミ電機

株式会社厚木事業所内

(72) 発明者 大原 智光

神奈川県厚木市酒井1601 ミツミ電機

株式会社厚木事業所内

F ターム(参考) 5H730 AA14 AS01 BB14 DD04 EE59

FD01 FD11 FG01 XC19

(54) 【発明の名称】電源装置

(57) 【要約】 (修正有)

【課題】回路動作停止時のリーク電流を低減できる電源装置を提供する。

【解決手段】一端に電源電圧VDDが印加されるコイルLと、コイルLの他端と出力端子Toutとの間にドレイン-ソースが接続された第1のMOSトランジスタQ2と、出力端子Toutから出力される出力電圧Voutを検出し、出力端子Toutの電圧が所定の電圧となるようにコイルLの他端の接続を制御する制御回路112とを有する電源回路において、第1のMOSトランジスタQ2の基板とコイルLとの間に接続された第1の抵抗R11と、第1のMOSトランジスタQ2の基板と第2のMOSトランジスタQ12のゲートとの間に接続された第2の抵抗R12と、第2のMOSトランジスタQ12のゲートと第2の抵抗R12との接続点と基準電位GNDとの間に接続されたスイッチ手段Q11とを有する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

一端に入力端子が接続されたコイルと、該コイルの他端と出力端子との間にドレイン - ソースが接続された第 1 の M O S トランジスタと、該出力端子から出力される出力電圧を検出し、該出力端子の電圧が所定の電圧となるように該コイルの他端の接続を制御する制御回路部とを有する電源回路において、

前記第 1 の M O S トランジスタの基板と前記出力端子との間に接続された第 2 の M O S トランジスタと、

前記第 1 の M O S トランジスタの基板と前記コイルとの間に接続された第 1 の抵抗と、

前記第 1 の M O S トランジスタの基板と前記第 2 の M O S トランジスタのゲートとの間に接続された第 2 の抵抗と、10

前記第 2 の M O S トランジスタのゲートと前記第 2 の抵抗との接続点と基準電位との間に接続されたスイッチ手段とを有することを特徴とする電源装置。

**【請求項 2】**

前記第 2 の M O S トランジスタは、前記出力端子側から前記第 1 の M O S トランジスタの基板側に向かって順方向となるように寄生ダイオードが形成される構成とされたことを特徴とする請求項 1 記載の電源装置。

**【請求項 3】**

前記第 2 の M O S トランジスタは、P チャネル M O S トランジスタから構成され、基板が前記第 1 の M O S トランジスタの基板に接続されたことを特徴とする請求項 2 記載の電源装置。20

**【請求項 4】**

前記スイッチ手段は、前記出力端子から電源を出力するときにオンされ、前記出力端子から電源の出力を停止する時にオフされることを特徴とする請求項 1 乃至 3 のいずれか一項記載の電源装置。

**【請求項 5】**

前記スイッチ手段は、M O S トランジスタから構成されたことを特徴とする請求項 1 乃至 4 のいずれか一項記載の電源装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は電源装置に係り、特に、一端に電源電圧が印加されるコイルと、コイルの他端と出力端子との間にドレイン - ソースが接続された M O S トランジスタと、出力端子から出力される出力電圧を検出し、出力端子の電圧が所定の電圧となるように M O S トランジスタを制御する制御回路部とを有する電源装置に関する。

**【背景技術】****【0 0 0 2】**

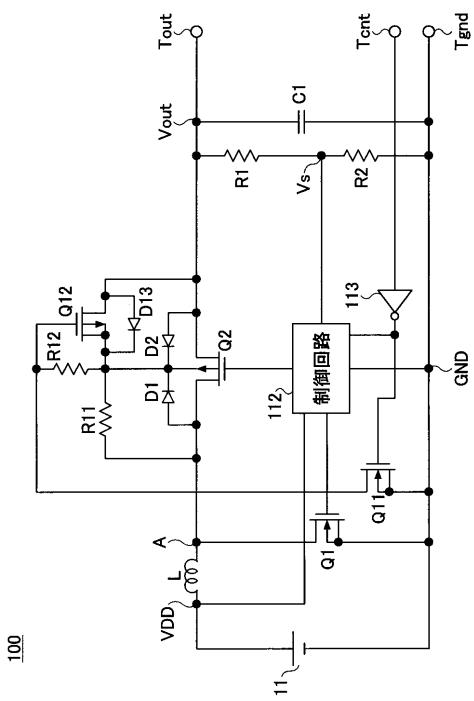

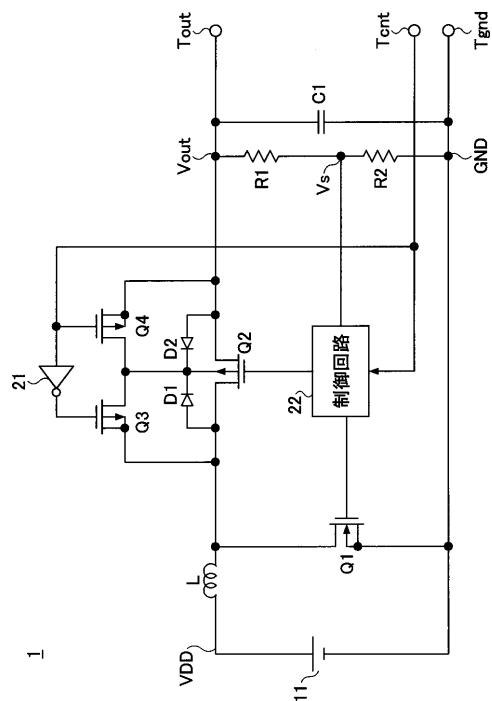

図 3 は従来の電源装置の一例の回路構成図を示す。

**【0 0 0 3】**

従来の電源装置 1 は、コイル L、M O S トランジスタ Q 1 ~ Q 4、抵抗 R 1、R 2、コンデンサ C 1、インバータ 2 1、制御回路 2 2 により、チョッパ方式の昇圧型スイッティングレギュレータを構成しており、電池などからなる直流電源 1 1 の出力電圧を昇圧して出力端子 T out より出力する（特許文献 1 参照）。40

**【0 0 0 4】**

直流電源 1 1 は、コイル L の一端に供給される。コイル L の他端は、N チャネル M O S トランジスタ Q 1 を介して接地端子 T gnd に接続されているとともに、P チャネル M O S トランジスタ Q 2 を介して出力端子 T out に接続されている。

**【0 0 0 5】**

出力端子 T out と接地端子 T gnd との間には、抵抗 R 1、R 2 が直列に接続されるとともに、コンデンサ C が接続されている。抵抗 R 1 と抵抗 R 2 との接続点には、出力端子 T ou50

$t$ から出力される出力電圧  $V_{out}$ を分割した電圧  $V_s$ が出現する。抵抗  $R_1$  と抵抗  $R_2$ との接続点に出現した電圧  $V_s$ は、制御回路 2 2 に供給される。

#### 【0006】

制御回路 2 2 は、電圧  $V_s$ に応じてMOSトランジスタ  $Q_1$  とMOSトランジスタ  $Q_2$  とを交互にオンさせる。このとき、出力端子  $T_{out}$  から出力される出力電圧  $V_{out}$  が一定となるように、その周期を制御している。

#### 【0007】

なお、MOSトランジスタ  $Q_3$ 、 $Q_4$  は、MOSトランジスタ  $Q_2$  の基板電圧を切り換えるためのスイッチ手段であり、MOSトランジスタ  $Q_2$  がオフ時に、出力端子  $T_{out}$  側にリーク電流が流れるの防止するための回路である。

10

#### 【0008】

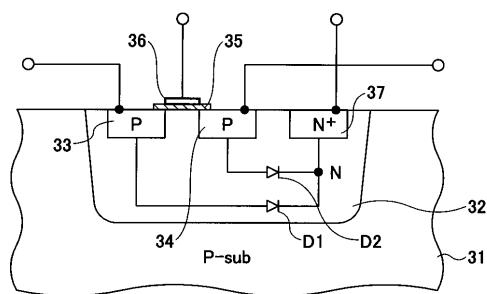

図4はpチャネルMOSトランジスタの断面図を示す。

#### 【0009】

pチャネルMOSトランジスタは、p形基板3 1にn形ウェル領域3 2を設け、さらに、ウェル領域3 2上に高濃度p形領域3 3、3 4を設け、ソース及びドレインとし、高濃度p形領域3 3と高濃度p形領域3 4との間の領域上に絶縁層3 5を挟んでゲート電極3 6を形成した構成とされている。このとき、高濃度p形領域3 3、3 4とウェル領域3 2及び高濃度n形領域3 7とで寄生ダイオード  $D_1$ 、 $D_2$  が形成される。

#### 【0010】

このとき、通常のMOSトランジスタのようにMOSトランジスタ  $Q_2$  のバックゲートである高濃度n形領域3 7をソース又はドレインに接続して、基板電位を決定すると、MOSトランジスタ  $Q_2$  がオフの時に寄生ダイオードを通してコイルL側から出力端子  $T_{out}$  側に電流が流れてしまう。

20

#### 【0011】

このため、MOSトランジスタ  $Q_3$ 、 $Q_4$  を設け、MOSトランジスタ  $Q_2$  の基板電位を切り換えて、MOSトランジスタ  $Q_2$  のオフ時にコイルL側から出力端子  $T_{out}$  側に電流が流れることを防止している。

#### 【0012】

端子  $T_{cnt}$ には、外部からコントロール信号が供給される。コントロール信号は、出力端子  $T_{out}$  から出力電圧  $V_{out}$  を出力又は停止させるための信号である。端子  $T_{cnt}$  に供給されたコントロール信号は、制御回路 2 2 に供給されるとともに、MOSトランジスタ  $Q_4$  のゲート、及び、インバータ2 1を介してMOSトランジスタ  $Q_3$  のゲートに供給される。

30

#### 【0013】

MOSトランジスタ  $Q_3$  は、ソース - ドレインがコイルLの他端とMOSトランジスタ  $Q_1$  の基板との間に接続されている。また、MOSトランジスタ  $Q_4$  は、ソース - ドレインが出力端子  $T_{out}$  とMOSトランジスタ  $Q_1$  のバックゲートである基板との間に接続されている。

#### 【0014】

MOSトランジスタ  $Q_3$  は、コントロール信号がロー・レベルのときには、そのゲート電位はハイ・レベルとなるので、オフされる。また、コントロール信号がハイ・レベルのときには、そのゲート電位はロー・レベルとなるので、オンされる。

40

#### 【0015】

MOSトランジスタ  $Q_4$  は、コントロール信号がロー・レベルのときには、そのゲート電位はロー・レベルとなるので、オンされる。また、コントロール信号がハイ・レベルのときには、そのゲート電位はハイ・レベルとなるので、オフされる。コントロール信号により、MOSトランジスタ  $Q_3$ 、 $Q_4$  を切り換えることにより、出力電圧  $V_{out}$  の出力停止時に、MOSトランジスタ  $Q_2$  の基板電位を切り換え、不要な電流が流れないようにしていた。

#### 【0016】

**【発明の開示】****【発明が解決しようとする課題】****【0017】**

しかるに、従来の電源装置1は、単に、MOSトランジスタQ3、Q4のスイッチングによって、基板電圧を切り換えていたため、MOSトランジスタQ2の基板電位などを自在に設定することはできなかった。

**【0018】**

本発明は上記の点に鑑みてされたもので、回路動作停止時のリーク電流を低減でき、回路設計を容易に行える電源装置を提供することを目的とする。

**【課題を解決するための手段】****【0019】**

本発明は、一端に電源電圧(VDD)が印加されるコイル(L)と、コイル(L)の他端と出力端子(Tout)との間にドレイン-ソースが接続された第1のMOSトランジスタ(Q2)と、出力端子(Tout)から出力される出力電圧(Vout)を検出し、出力端子(Tout)の電圧が所定の電圧となるようにコイル(L)の他端の接続を制御する制御回路(112)とを有する電源回路において、第1のMOSトランジスタ(Q2)の基板と出力端子(Tout)との間に接続された第2のMOSトランジスタ(Q12)と、第1のMOSトランジスタ(Q2)の基板とコイル(L)との間に接続された第1の抵抗(R11)と、第1のMOSトランジスタ(Q2)の基板と第2のMOSトランジスタ(Q12)のゲートとの間に接続された第2の抵抗(R12)と、第2のMOSトランジスタ(Q12)のゲートと第2の抵抗(R12)との接続点と基準電位(GND)との間に接続されたスイッチ手段(Q11)とを有することを特徴とする。

**【0020】**

また、本発明は、第2のMOSトランジスタ(Q12)は、出力端子(Tout)側から第1のMOSトランジスタ(Q2)の基板側に向かって順方向となるように寄生ダイオード(D13)が形成される構成とされたことを特徴とする。

**【0021】**

さらに、第2のMOSトランジスタ(Q12)は、PチャネルMOSトランジスタから構成され、基板が第1のMOSトランジスタ(Q2)の基板に接続されたことを特徴とする。

**【0022】**

また、スイッチ手段(Q11)は、出力端子(Tout)から電源(Vout)を出力するときにオンされ、出力端子(Tout)から電源の出力を停止する時にオフされることを特徴とする。

**【0023】**

スイッチ手段(Q11)は、MOSトランジスタから構成されたことを特徴とする。

**【0024】**

なお、上記参照符号はあくまでも参考であり、これによって、特許請求の範囲が限定されるものではない。

**【発明の効果】****【0025】**

本発明によれば、一端に入力端子が接続されたコイルと、コイルの他端と出力端子との間にドレイン-ソースが接続された第1のMOSトランジスタと、出力端子から出力される出力電圧を検出し、出力端子の電圧が所定の電圧となるようにコイルの他端の接続を制御する制御回路部とを有する電源回路において、第1のMOSトランジスタの基板と出力端子との間に接続された第2のMOSトランジスタと、第1のMOSトランジスタの基板とコイルとの間に接続された第1の抵抗と、第1のMOSトランジスタの基板と第2のMOSトランジスタのゲートとの間に接続された第2の抵抗と、第2のMOSトランジスタのゲートと第2の抵抗との接続点と基準電位との間に接続されたスイッチ手段とを設けることにより、出力端子からの電源の出力を停止したときに第1のMOSトランジスタ及び

10

20

30

40

50

第2のMOSトランジスタを確実にオフさせることができる。これによって、出力端子からの電源出力の停止時に出力端子から負荷にリーク電流が流れることを防止できる。

#### 【0026】

また、本発明によれば、第1の抵抗及び第2の抵抗により第1のMOSトランジスタの基板電位及び第2のMOSトランジスタのゲート電圧を調整できるため、設計を容易に行える。

#### 【発明を実施するための最良の形態】

##### 【0027】

###### 〔構成〕

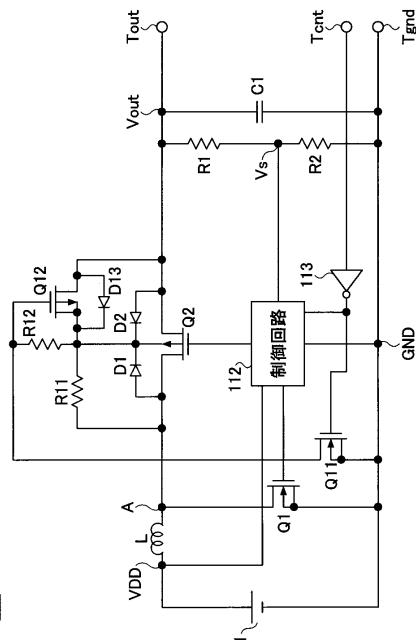

図1は本発明の一実施例の回路構成図を示す。同図中、図3と同一構成部分には同一符号を付し、その説明は省略する。

##### 【0028】

本実施例の電源装置100は、チョッパ方式の昇圧型スイッチングレギュレータであり、コイルL、MOSトランジスタQ1、Q2、Q11、Q12、抵抗R1、R2、R11、R12、コンデンサC1、制御回路112、インバータ113から構成されている。なお、ダイオードD1、D2は、MOSトランジスタQ2の基板とソース及びドレインとの間に形成される寄生ダイオードである。また、ダイオードD13はトランジスタQ12の基板とドレインとの間に形成される寄生ダイオードである。

##### 【0029】

コイルLは、一端に電池などから構成される直流電源11の正電位が印加されている。コイルLの他端は、NチャネルMOSトランジスタQ1のドレイン及びPチャネルMOSトランジスタQ2のドレインに接続されている。MOSトランジスタQ1のソースは、接地端子T<sub>gnd</sub>に接続されている。また、MOSトランジスタQ2のソースは、出力端子T<sub>out</sub>に接続されている。なお、ここで、このコイルLの他端とMOSトランジスタQ1、Q2のドレイン端との接続点をAとする。なお、MOSトランジスタQ2のソース及びドレインと基板との間には、図4に示すように寄生ダイオードD1、D2が寄生している。

##### 【0030】

MOSトランジスタQ1のゲート及びMOSトランジスタQ2のゲートは、制御回路112に接続されている。MOSトランジスタQ1及びMOSトランジスタQ2は、制御回路112からの駆動パルスにより交互にオンするようにスイッチングされる。このような動作によって、いわゆる、同期整流方式のレギュレータが構成されている。

##### 【0031】

nチャネルMOSトランジスタQ11は、ソース - ドレインが接地端子T<sub>gnd</sub>とMOSトランジスタQ12のゲートとの間に接続されている。MOSトランジスタQ11のゲートには、インバータ113を介してコントロール端子T<sub>cnt</sub>が接続されており、コントロール端子T<sub>cnt</sub>に供給されるコントロール信号を反転した反転コントロール信号が供給される。

##### 【0032】

さらに、pチャネルMOSトランジスタQ12は、ソース - ドレインがMOSトランジスタQ2の基板と出力端子T<sub>out</sub>との間に接続されている。MOSトランジスタQ12のゲートは、MOSトランジスタQ11を介して接地端子T<sub>gnd</sub>に接続されるとともに、抵抗R12を介してMOSトランジスタQ2の基板に接続されている。

##### 【0033】

抵抗R11は、MOSトランジスタQ2の基板と接続点Aとの間に接続されている。また、抵抗R12は、MOSトランジスタQ2の基板とMOSトランジスタQ11のゲートとの間に接続されている。

##### 【0034】

制御回路112には、抵抗R1と抵抗R2との接続点の電圧、すなわち、出力端子T<sub>out</sub>から出力される出力電圧V<sub>out</sub>に応じた電圧V<sub>s</sub>が供給されている。制御回路112は、抵抗R1と抵抗R2との接続点の電圧V<sub>s</sub>に応じたパルス幅のパルスを生成し、MOSトランジスタQ1、Q2のゲートに供給する。このとき、制御回路112は、MOSトラン

10

20

30

40

50

ジスタQ1、Q2のゲートに供給するパルスのパルス幅を出力端子Toutから出力される出力電圧Voutが一定の電圧となるように制御している。

#### 【0035】

また、制御回路112には、コントロール端子Tcntがインバータ113を介して接続されている。コントロール端子Tcntには、外部からコントロール信号が供給される。コントロール信号は、出力端子Toutからの出力電圧Voutを出力させる動作と停止させる動作とを制御するための信号である。

#### 【0036】

コントロール端子Tcntに供給されたコントロール信号は、出力端子Toutから出力電圧Voutを出力させるとときには、ローレベルとなり、出力端子Toutからの出力電圧Voutの出力を停止させるとときには、ハイレベルとなる。コントロール端子Tcntに供給されたコントロール信号は、インバータ113に供給される。インバータ113は、コントロール端子Tcntからのコントロール信号を反転させる。反転コントロール信号は、制御回路112及びMOSトランジスタQ11のゲートに供給される。

10

#### 【0037】

制御回路112は、コントロール端子Tcntに供給されるコントロール信号がローレベルであり、インバータ113の出力信号がハイレベルのときには、抵抗R1と抵抗R2との接続点の電圧Vsに応じたパルス幅のパルス信号を生成し、MOSトランジスタQ1、Q2のゲートに供給することによって、MOSトランジスタQ1とMOSトランジスタQ2とを交互にオンさせ、出力端子Toutから出力電圧Voutが出力されるように動作する。また、制御回路112は、コントロール端子Tcntに供給されるコントロール信号がハイレベルであり、インバータ113の出力信号がローレベルのときには、MOSトランジスタQ1のゲート電位をローレベルとし、MOSトランジスタQ2のゲート電位をハイレベルとすることにより、MOSトランジスタQ1、Q2を共にオフ状態とし、出力端子Toutからの出力電圧Voutの出力が停止されるように動作する。

20

#### 【0038】

このとき、MOSトランジスタQ11のゲートには、反転コントロール信号が供給されているので、インバータ113の出力信号がハイレベルのときには、ゲート電位がハイレベルとなり、MOSトランジスタQ11は、オン状態となる。MOSトランジスタQ11がオンすることにより、MOSトランジスタQ12のゲート電位がローレベルとなる。MOSトランジスタQ12は、ゲート電位がローレベルとなると、オンする。

30

#### 【0039】

MOSトランジスタQ11は、インバータ113の出力信号がローレベルのときには、ゲート電位がローレベルになるので、オフ状態となる。MOSトランジスタQ11がオフすると、MOSトランジスタQ12のゲート電位がハイレベルとなるので、MOSトランジスタQ12はオフ状態となる。

40

#### 【0040】

##### 〔動作〕

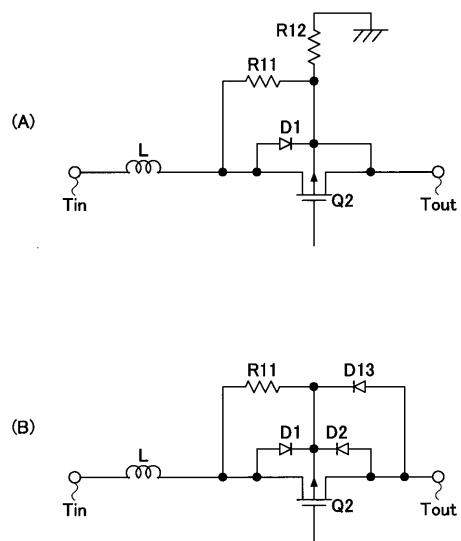

図2は本発明の一実施例の動作説明図を示す。図2(A)は昇圧動作時、図2(B)は昇圧停止時の要部の等価回路図を示す。

40

#### 【0041】

##### (A)昇圧動作時

昇圧動作時には、コントロール端子Tcntに供給されるコントロール信号がローレベルとされる。ローレベルのコントロール信号は、インバータ113により反転されてハイレベルとされ、制御回路112及びMOSトランジスタQ11のゲートに供給される。

#### 【0042】

制御回路112は、MOSトランジスタQ1とMOSトランジスタQ2とを交互にオンさせる。また、MOSトランジスタQ11は、ゲートがハイレベルとなるので、オン状態を維持する。MOSトランジスタQ11がオンすると、MOSトランジスタQ12のゲート電位がローレベルとなるので、MOSトランジスタQ12はオンする。

50

**【 0 0 4 3 】**

このため、MOSトランジスタQ2、Q11、Q12の周辺の回路は、図2(A)に示すような等価回路で表すことができる。

**【 0 0 4 4 】**

(a) MOSトランジスタQ1がオン状態、MOSトランジスタQ2がオフ状態のときには、電源11からの電流はコイルLとMOSトランジスタQ1を介してグランド電位に流れ、コイルLにエネルギー蓄積される。このとき、接続点Aはグランド電位となり、MOSトランジスタQ2の基板は、抵抗R12及びMOSトランジスタQ11を介して接地端子Tgndに接続されるので、グランド電位に維持される。

**【 0 0 4 5 】**

(b) MOSトランジスタQ1がオフ状態、MOSトランジスタQ2がオン状態のときには、コイルLに蓄積されたエネルギーは、MOSトランジスタQ2を介して出力端子Toutに出力される。

**【 0 0 4 6 】**

なお、このとき、接続点Aの電位が上昇するので、MOSトランジスタQ2の基板の電位は、接続点Aの電位を抵抗R11と抵抗R12で分割したものとなる。

**【 0 0 4 7 】****(B) 昇圧停止時**

昇圧停止時には、コントロール端子Tcntに供給されるコントロール信号は、ハイレベルとされる。コントロール端子Tcntに供給されるコントロール信号がハイレベルとなると、インバータ113の出力はローレベルとなる。

**【 0 0 4 8 】**

インバータ113の出力がローレベルとなることにより、制御回路112はMOSトランジスタQ1、Q2と共にオフ状態に維持する。また、インバータ113の出力がローレベルとなることにより、MOSトランジスタQ11がオフする。MOSトランジスタQ11がオフすると、トランジスタQ12には、抵抗R11、R12を介してハイレベルとされるので、トランジスタQ12はオン状態となる。このとき、MOSトランジスタQ2の基板は、電源電圧VDDに維持される。

**【 0 0 4 9 】**

このため、MOSトランジスタQ2、Q11、Q12の周辺の回路は、図2(B)に示すような等価回路で表すことができる。

**【 0 0 5 0 】**

このとき、MOSトランジスタQ1、Q2、Q11、Q12がすべてオフすることによって、図2(B)に示すように抵抗R11と寄生ダイオードD1、D2、D13が回路上に現れる。寄生ダイオードD2、D13は、共に出力端子ToutからトランジスタQ2の基板との間に逆方向に接続されることになる。これによって、接続点Aから出力端子Tout側に電流が流れることがなくなる。

**【 0 0 5 1 】**

本実施例によれば、出力端子からの電源の出力を停止したときに、MOSトランジスタQ2及びMOSトランジスタQ11を確実のオフさせることができ、また、このとき、寄生ダイオードD2、D13も逆方向とすることができるため、電源11から出力端子Toutにリーキ電流が流れることを防止することができる。

**【 0 0 5 2 】**

また、本実施例によれば、抵抗R11、R12によりMOSトランジスタQ2の基板電位及びMOSトランジスタQ12のゲート電圧を調整できるため、設計を容易に行える。

**【 図面の簡単な説明 】****【 0 0 5 3 】**

【図1】本発明の一実施例の回路構成図である。

【図2】本発明の一実施例の要部の等価回路図である。

【図3】従来の電源装置の一例の回路構成図である。

【図4】MOSトランジスタQ2の断面図である。

【符号の説明】

【0054】

11 直流電源

L コイル、R1、R2、R11、R12 抵抗、C1 コンデンサ

Q1、Q2、Q11、Q12 MOSトランジスタ、D1、D2、D13 寄生ダイオード

100 電源装置、112 制御回路、113 インバータ

【図1】

【図2】

【図3】

【図4】