[19] Patents Registry

The Hong Kong Special Administrative Region

香港特別行政區

專利註冊處

[11] 1004075 A EP 0474616 B1

[12]

# STANDARD PATENT SPECIFICATION 標準專利說明書

[21] Application No. 申請編號 98103077.3 [51] Int.Cl.<sup>6</sup> H03K

[22] Date of filing 提交日期 14.04.1998

[30] Priority 優先權 06.09.1990 US 578259

[45] Publication of the grant of the patent 批予專利的發表日期 13.11.1998

EP Application No. & Date 歐洲專利申請編號及日期

EP 91850217.0 05.09.1991

EP Publication No. 歐洲專利發表編號

EP 0474616

Publication date of EP grant of the patent 批予歐洲專利的發表日期 22.10.1997

[73] Proprietor 專利所有人

ERICSSON INC., 15 East Midland Avenue, Paramus New

Jersey 07652, United States of America 美利堅合眾國

[72] Inventor 發明人

DENT, PAUL WILKINSON

[74] Agent and / or address for service 代理人及/或送達地址

Hong Kong Patent Registrations Company, 2003, Tower Two,

Lippo Centre, 89 Queensway, Central, Hong Kong ,香港金鐘

道 89 號力寶中心第二座 2003 室

[54] APPARATUS AND METHOD FOR VARIABLE RATIO FREQUENCY DIVISION 可變比頻率除法的装置和方法

Europäisches Patentamt

European Patent Office

Office européen des brevets

(11) EP 0 474 616 B1

(12)

## **EUROPEAN PATENT SPECIFICATION**

(45) Date of publication and mention of the grant of the patent:22.10.1997 Bulletin 1997/43

(51) Int CL6: H03K 23/66

- (21) Application number: 91850217.0

- (22) Date of filing: 05.09.1991

- (54) Apparatus and method for variable ratio frequency division

Vorrichtung und Verfahren zur Frequenzteilung mit variablem Frequenzteilungverhältnis

Appareil et méthode de division de fréquence à rapport variable

- (84) Designated Contracting States: DE ES FR GB IT NL SE

- (30) Priority: **06.09.1990 US 578259**

- (43) Date of publication of application: 11.03.1992 Bulletin 1992/11

- (73) Proprietor: ERICSSON INC.

Paramus New Jersey 07652 (US)

- (72) Inventor: Dent, Paul Wilkinson Cary, North Carolina 27513 (US)

- (74) Representative: Lövgren, Tage Telefonaktiebolaget L M Ericsson Patent Department 126 25 Stockholm (SE)

- (56) References cited:

US-A- 4 084 082

US-A- 4 555 793

US-A- 4 856 032

- ELECTRONIC COMPONENTS AND APPLICATIONS vol. 1, no. 4, 1 August 1979, EINDHOVEN, HOLLAND pages 239 - 248; SCHILLHOF, U.: 'INTRODUCTION TO MICROCOMPUTER - CONTROLLED RADIO TUNING SYSTEM'

P 0 474 616 B1

Note: Within nine months from the publication of the mention of the grant of the European patent, any person may give notice to the European Patent Office of opposition to the European patent granted. Notice of opposition shall be filed in a written reasoned statement. It shall not be deemed to have been filed until the opposition fee has been paid. (Art 99(1) European Patent Convention).

## Description

## FIELD OF THE INVENTION

The present invention relates generally to a programmable divider for use in a digital frequency synthesizer. More particularly, the invention relates to a dual modulus counter suitable for controlling the programmable divider.

## BACKGROUND OF THE INVENTION

In digital frequency synthesizers, there is a need for a variable divider which counts the cycles of an input signal having a given frequency until a predetermined number of counts have been accumulated. The size of the count is usually referred to by the letter N. Once N counts have been accumulated, the variable divider is reset to begin the cycle again. It is desirable for the number of counts N to be variable in order that it can be programmed in advance of each count by means of a control input.

When N is large and the operating frequency of the counter is to be high, technical difficulties can arise in constructing a multistage high frequency variable divider. In the prior art, the problem is typically overcome by using a fixed high frequency divide by M stage prior to a variable divide by N stage. This solution is not always desirable because the total division factor can only be a multiple of M.

In a digital frequency synthesizer application, it is usually desirable to be able to program the total division factors in steps or increments of 1. The steps, therefore, relate to the frequency resolution or the frequency step size of the synthesizer. If the divider is only programmable in steps of M, the frequency steps available are relatively coarse and determined by the factor M.

Another approach to the problem is to begin with a high frequency divider stage or prescaler while retaining the ability to program the divider count cycle length in steps of 1. This arrangement allows the prescaler to be varied between dividing ratios of R and R+1.

It is possible, for example, for a dual ratio prescaler having the division ratios 10 and 11 to perform a division of 157. The number 157 can be expressed by the equation 7x11+(15-7)x10. The prescaler is first programmed to divide by 11, and the lower frequency divider stage is set to count 7 prescaler output pulses. After counting 7 prescaler output pulses, the prescaler is set to divide by 10. The low frequency divider stage is then set to count 8 prescaler output pulses. Upon completion of this count, a total of 7x11+8x10=157 input pulses have been applied to the prescaler input. The cycle is then begun again. It should be noted that in order to obtain numbers in steps of 1, the number of times the prescaler divides by 11 must be programmed from 0 to 9 and the number of 10's in the total number must not be less than 9. This relationship sets a lower bound of R(R-1) for the contiguous number range that can be achieved with a two ratio prescaler having ratios R and R+1.

The most common method employed to count two different numbers of prescaler output pulses, N1 and N2, while the prescaler is dividing respectively by ratios R1 and R2, is to use two separate low frequency down counters that are preset to the values N1 and N1 + N2. respectively. For example, the division of 157 with the aid of a 10/11 prescaler could be achieved by presetting one divider to N=7 and the other to N1+N2=15. The prescaler would then first be set to divide by R1(11) while both low frequency counters counted down on the prescaler output pulses. When the N1 counter reaches zero after 7 prescaler output pulses, the prescaler would switch and divide by 10, and the N2 counter would continue to count down a further 8 prescaler output pulses until it reaches zero, completing the cycle. This system has the advantage that a desired division number is simply expressed in values to which the N1 and N2 counters can be preset. This arrangement has the disadvantage that two variable dividers are required and power consumption is increased when both dividers are operating. Increased power consumption is a significant disadvantage for battery powered equipment

U.S. Patent No. 4,053,739 describes a single variable divider that is alternatively programmed with the value N1 when the prescaler divides by the value R1 and is programmed with the value N2 when the prescaler divides by the value R2. This device has the advantage that a single variable divider suffices. Unfortunately, the described arrangement includes additional circuit complexity in the form of a multi-line switch. The multi-line switch alternately selects the bits corresponding to the values N1 and N2 in order to preset the single variable divider. Although this additional circuitry operates at a lower power consumption than a circuit having two variable dividers, it still requires substantially the same amount of circuitry when implemented as an integrated circuit

Accordingly, there is a need for a counter for a programmable divider which can register both the counts N1 and N2 without them being presented alternately to the counter. This arrangement would eliminate the need for a complex multi-line switch.

U.S. Patent 4,856,032 (Klekotka et al. patent) teaches that one should program a high speed programmable frequency divider with the total count desired, and set a comparator to switch the prescaler to a second mode when a certain partial count has been reached. This arrangement works well when there is a relatively few number of divisions such as described in the Klekotka et al. patent. There is a distinct problem with the device disclosed in the Klekotka et al patent where the number of divisions with the prescaler in its first mode (R1), would greatly exceed the number in its second mode (R2). In other words, in the Klekotka et al. patent the values for N1 and N2 tend to be similar in magnitude, but the device does not work well when there is a great

disparity in the magnitudes of N1 and N2

## SUMMARY OF THE INVENTION

The present invention relates to a circuit and method for controlling a programmable divider for use in a digital frequency synthesizer. The programmable divider is responsive to a dual modulus counter. The dual modulus counter includes a preloadable binary counter, a comparator and logic gates which generate selection signals to control the programmable divider. The preloadable counter is loaded with a value N1. The counter counts to a predetermined intermediate value such as zero and generates an output signal. The counter then continues to count until it reaches a second value N2. The comparator compares the output of the counter to the value N2 which was loaded into the comparator. When the binary counter reaches the value N2, the comparator generates a second output with is applied to the logic gates. The logic gates generate the selection signals which cause the programmable divider to divide an input signal by the division ratios R1 or R2. In a first embodiment of the present invention, the binary counter is a down counter. In a second embodiment of the present invention, the binary counter is an up counter. The up counter is responsive to the predetermined value -N1, and the counter counts from this value -N1 to the predetermined intermediate output. The counter then counts from the predetermined intermediate output to the second predetermined value N2. The comparing means detects when the up counter has reached the second predetermined value N2. The dual modulus counter of the present invention may also be used to control more than one programmable divider. The present invention is particularly well suited for use in a digital frequency synthesizer of the type having a phase locked loop.

## BRIEF DESCRIPTION OF THE DRAWINGS

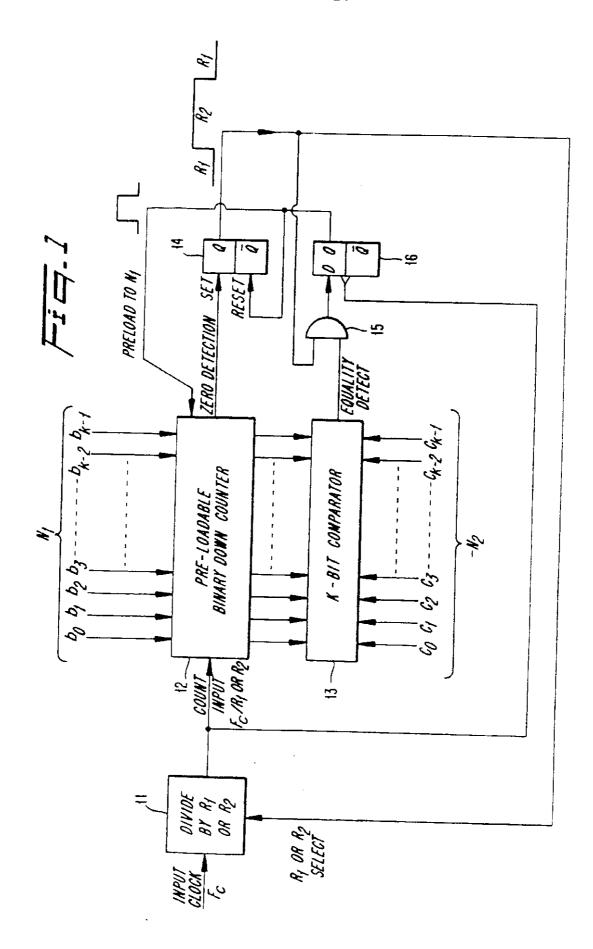

Fig. 1 is a schematic diagram of the first embodiment of the present invention having a binary down counter;

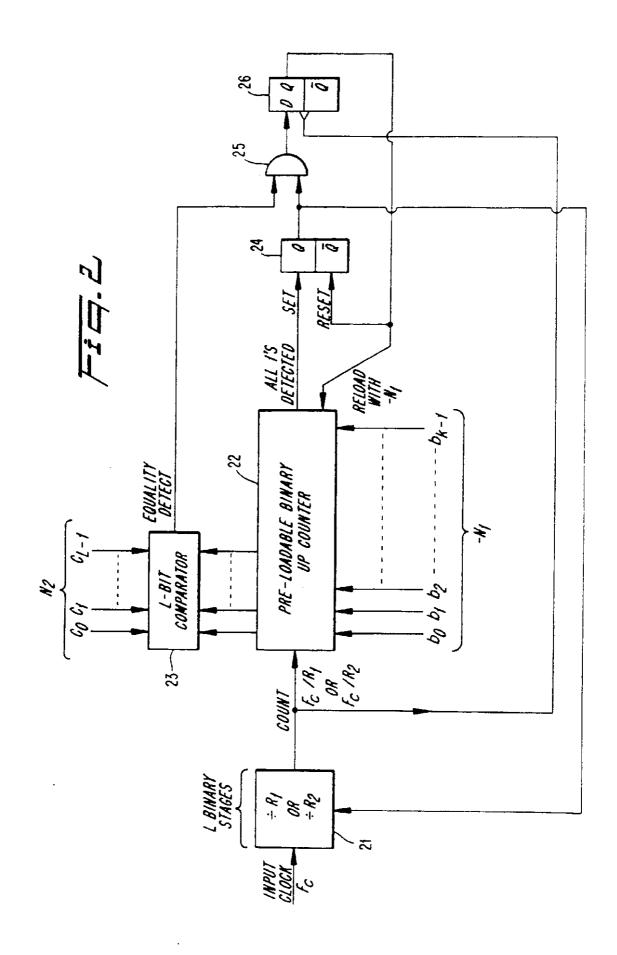

Fig. 2 is a schematic diagram of a second embodiment of the present invention having a binary up counter;

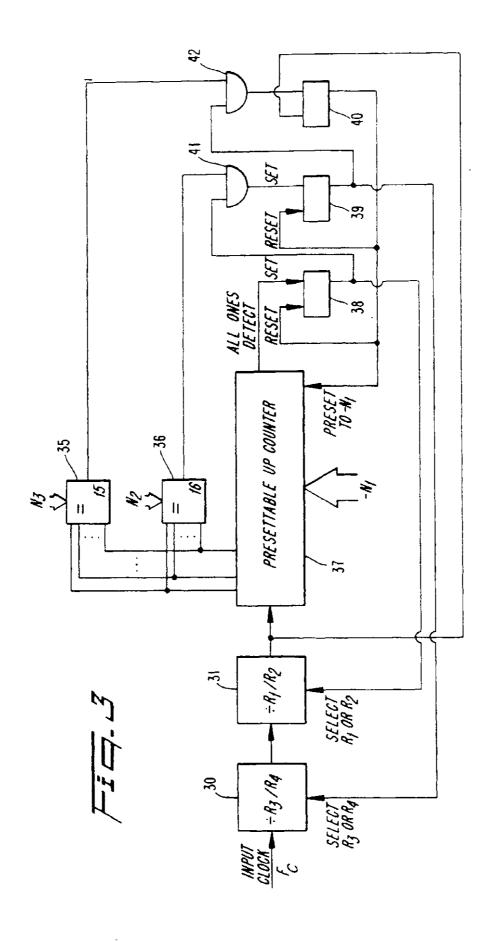

Fig. 3 is a schematic diagram of the dual modulus counter of the present invention controlling two programmable dividers; and

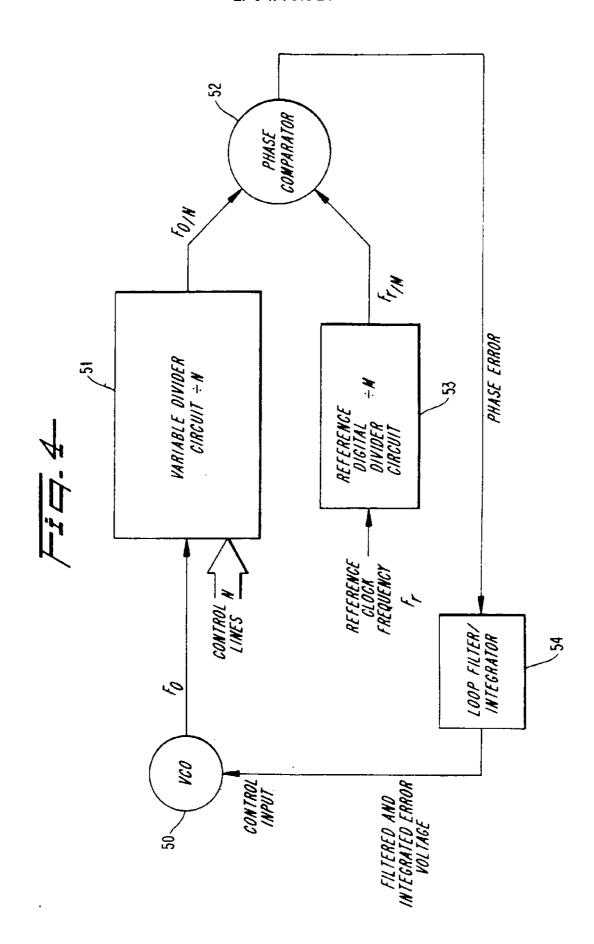

Fig. 4 is a schematic diagram of a phase tocked loop utilizing a variable divider.

## DETAILED DESCRIPTION OF THE INVENTION

Fig. 1 illustrates a schematic diagram of the first embodiment of the present invention. In the first embodiment, there is shown a dual modulus counter having a binary down counter 12 which is loaded at the beginning

of a count sequence with the value N1. There is a prescaler 11 which can divide by the ratios R1 or R2. The output pulses of the prescaler 11 decrement the down counter 12 until the down counter reaches the value zero. When the down counter 12 reaches zero, it generates an output pulse which sets a latch 14. The setting of the latch 14 causes the prescaler 11 to switch to its alternative division ratio R2. The output pulses of the prescaler 11 continue to decrement the down counter 12 until a comparator 13 detects that it has reached the state corresponding to a value -N2. When the comparator 13 detects the value -N2, the latch 14 is already set, and both inputs to an AND gate 15 are enabled. The AND gate 15 then generates an output signal which is clocked into a d-type flip flop 16 upon the next prescaler output pulse. The latch 14 is then reset, and the down counter 12 can be reloaded with the value N1, while the prescaler 11 resumes division by the ratio R1.

Since the inputs to the AND gate 15 are no longer enabled because the latch 14 has been reset, the output signal at the AND gate 15 will disappear and this state will be transferred into the d-type flip flop 16 upon the next output pulse of the prescaler 11. The preset control signal to the down counter 12 is removed leaving it loaded with the value N1 and ready for the next count sequence. The total number of prescaler input pulses in the count sequence, therefore is expressed by the equation  $N_{TOT}=(N1+1)R1+(N2+1)R2$ . In order to obtain a desired  $N_{TOT}$ , it is necessary to subtract the excess R1+R2 value from the desired number. For example, if R1=11 and R2=10, and a total division cycle length of 170 is desired, 10+11=21 is first subtracted from 170 resulting in the value 149. N1 must then be 9 and N2=14-9=5. In order to avoid impossible negative values of N2 arising. a desired count N must satisfy the following equations:

$INT \{(N-R1-R2)/R2\} \ge IN-R1-R2I_{R2}$

$INT \{ (N-R1-R2)/R1 \} \ge IN-R1-R2I_{R1}$

The expression INT (x) means the whole number part of x, i.e., if x = 5.3667, then INT(x) = 5. This is an expression of the above-described lower bound on the contiguous number range that can be spanned using the dual ratio prescalers associated with the present invention.

In the circuit illustrated in Fig. 1, there is no restriction placed on the relative magnitudes of N1 and N2. The word length of the comparator 13 was the same as the whole number in the counter 12. However, to cover a range of values of N in steps of 1 with no gaps only requires that N1+1 take on values between 1 and R1-3 i.e., the range of the least significant digit of N modulo R1. Since this range is often much shorter than the total length of the counter 12, the comparator 13 word length can be advantageously reduced. The reduction of the

word length of the comparator 13 can be achieved by using an up counter.

Referring now to Fig. 2, a second embodiment of the present invention using an up counter is illustrated. In the second embodiment of the present invention, there is a preloadable binary up counter 22 that is responsive to the output of a prescaler 21. The prescaler 21 is capable of dividing by division ratios R1 or R2. The up counter 22 is initially preset to a value -N1, while the prescaler 21 is initially set to divide by R1. The output pulses of the prescaler 21 increment the up counter 22 until the output of the up counter reaches all logical ones. When the output of the up counter 22 is all logical ones instead of all logical zeros, the output can be more rapidly detected.

Upon detecting all logical ones, a latch 24 is set causing the prescaler 21 to switch to division by the ratio R2. If N2 equals 111..1, an L-bit comparator 23 provides an output signal to an AND gate 25. The AND gate 25 generates an output signal. Otherwise the L-bit comparator 23 generates an output signal after one further output pulse from the prescaler 21 if N2=0, after two output pulses if N2=1, etc. On the immediately following prescaler output pulse, the output of AND gate 25 is clocked into a d-type flip flop 26 causing the latch 24 to be reset. The prescaler 21 returns to dividing by R1, and the up counter is reloaded with the value -N1. Since the resetting of the latch 24 removes one of the enabling inputs to the AND gate 25, the output of the AND gate becomes 0. This output is transferred to the d-type flip flop 26 on the next prescaler output pulse, thereby removing the reload control signal to the up counter 22 and leaving it in the state -N1 and leaving it ready to repeat the entire cycle.

The total number of prescaler input clock pulses in a complete division cycle for the circuit of Fig. 2 is defined by the equation N=N1xR1+(N2+2)xR2. It should be noted, however, that the value N2=-1 is correctly treated by the circuit, so that N2 is considered to range through the values -1, 0, +1 ... to 2\*\*L-2. The value N2' is defined by the equation N2'=N2+1 and ranges from the value 0 to 2<sup>L</sup>-1. The value N is defined by the equation N=N1xR1+N2'xR2+R2. The values for N1 and N2' may be calculated as follows: (1) Subtract the excess R2 from N to get N', (2) calculate N2' as the remainder upon division of N' by R1, (3) calculate N1 as the integer part of N'/R1-N2', and (4) apply N2=N2'-1 to the L-bit comparator 23 and N1 to the divider preload input of counter 22. These manipulations can be performed more simply if the value R1 is a power of 2

Referring now to Fig. 3, a schematic diagram illustrates a plurality of programmable dividers or prescalers 30, 31 being controlled by the dual modulus counter of the present invention. Two digital comparators 35, 36 are used to examine the state of the least significant Lbits of a main counter 37. After counting up from a value -N1 to an all logical ones condition, the comparators 35, 36 in turn detect when the least significant bits of the

main counter 37 becomes equal to N2 and then to the value N3. These events cause the prescalers 30 and 31 respectively to divide by their alternative ratios.

For example, suppose the prescaler 31 has the ratios 10 and 11 available, while the prescaler 30 has ratios of 9 and 10 available. Assuming that the flip flops 38, 39 and 40 are in the reset condition, both prescalers 30, 31 begin by dividing by 10. The counter 37 then counts up from -N1 until its output is all logical ones. The latch 38 then becomes set, causing the prescaler 31 to divide by 11. The counter 37 continues to count up until the comparator 36 detects a state corresponding to the value N2. If latch 38 is also set, both inputs to an AND gate 41 are enabled and the latch 39 is set. This causes the prescaler 30 to begin dividing by 9 while the prescaler 31 continues to divide by 11. The counter 37 continues to count until the comparator 35 detects a bit state corresponding to the value N3. At this point, if latch 39 is already set, both inputs to the AND gate 42 are enabled and upon the next output pulse from the prescaler 31 the output signal of the AND gate 42 is clocked into the flip flop 40, causing the latches 38, 39 to be reset and the reloading of the main counter 37 to the starting state N1. The prescalers 30, 31 are now back in their original divide by 10 condition, and the inputs to the AND gate 42 are no longer enabled. After one more pulse from the prescaler 31, the zero signal from the AND gate 42 is transferred into the flip flop 40 removing the reset condition and leaving the counter 37 in the state -N1 and ready to start a new cycle.

The total cycle length in terms of output pulses of the input clock signal  $F_{\rm c}$  can be expressed by the following equation:

N=100N1+110(N2+1)+99(N3-N2I+1)

where the absolute value of N3-N2 corresponds to modulo 2\*\*L, where L is the number of least significant bits of the counter 37 examined by the comparators 35, 36. The value N3' is defined by the equation N3'= IN3-N2I. The value of N, therefore, can be defined by the following equation:

N=100(N1+N2)+110(N2+1)+10N2-N3'+209

A desired count may be produced in the following fashion, (1) subtract the excess 209 from the desired count, getting N', (2) round up N' to the next multiple of 10, which is called N", (3) set N3' to (N"-N'), (4) set N2 to the 10's digit of N", and (5) set N1 to the 100's digit of N'-N2. For example, suppose N=1,568. Then N'=1,568-209=1,359. N"=1,360. N3'=N"-N'=1. N2=6 (10's digit of N"). N1=13-N2=7(100's digit N"-N2). Because of the subtraction of N2 from the number of 100's in N" and the value of N2 ranges up to 9, the number of 100's in N" can not be less than 9. Therefore, the lower

35

7

bound on the contiguous number range is of the order of 900/(209-9)=1,100. This is an order of magnitude lower than the lower bound of 9,900 that would apply for a two-ratio prescaler of ratios 100 and 101. In general, an advantageous way to obtain a total frequency reduction of the order of R\*\*2 from the input clock signal  $F_c$  to the input of the low frequency divider is to use two prescalers having the ratios (R, R+1) and (R, R-1) respectively.

The principles of the present inventions may be extended by adding additional comparators as necessary. The comparators are not constrained to be of the same word length and bits, nor are the prescalers they control constrained to exist separately. The two prescalers 30, 31 of Fig. 3 can also be regarded as a single circuit having three or more division ratios selectable by two or more control lines. Such an arrangement can be advantageous because the exact moment at which the highest frequency prescaler 30 is switched between its ratios can be more time critical than the lower frequency logic can define. It is, therefore, possible that a necessary precaution is to retime the control signal to the highest frequency prescaler with the logic having substantially the same speed as prescaler 31. The control signal from the low speed logic, therefore, should preferably pass through the medium speed prescaler 31 to be retimed more accurately. This will have a small penalty on the lower bound of the contiguous number range that the overall division ratios can span, but it will increase the maximum frequency of operation before timing problems are encountered.

The prescaler division ratios of the present invention are not constrained to any particular values. Common values that simplify the calculation of the values N1, N2, and N3 can be based on either a decimal number system or a binary number system. In cases where the ease of calculation is not an issue, such as when adequate microprocessor capability exists or number radix manipulations or when precomputed lookup tables can be used, it may be possible to find other advantageous combinations of prescaler ratios, e. g. noncommesurate primes.

Referring now to Fig. 4, a schematic diagram illustrates the use of the present invention in a phase locked loop. The phase locked loop includes a voltage controlled oscillator 50 which provides an output signal  $F_0$ . The output signal F<sub>0</sub> is applied to a variable divider circuit 51. The variable divider circuit 51 includes a programmable divider and the dual modulus counter of the present invention. The total division ratio N of the variable divider circuit 51 is a function of the values N1 and N2 associated with the dual modulus counter. The output of the variable divider circuit 51 is a divided output signal F<sub>0</sub>/N which is applied to a phase comparator 52. The phase comparator 52 compares the phase of the divided output signal Fn/N to a divided reference frequency signal F<sub>r</sub>/M. The divided reference frequency signal is produced from a reference clock signal that is divided by a digital divider 53. The output of the phase

comparator 52 is a signal representative of the phase error. The phase error signal is applied to a loop filter/integrator 54. The filtered and integrated output is then applied to the voltage controlled oscillator 50.

#### Claims

A variable ratio frequency divider circuit including a programmable dividing means [11, 21, 31] having division ratios R1 and R2, for dividing an input signal into a divided output signal, comprising:

> counting means [12, 22, 37] loaded with a predetermined value N1 or -N1 and responsive to the divided output signal of the programmable dividing means [11, 21, 31], for generating a plurality of outputs including a predetermined intermediate output of either zero or all ones: first comparing means [13, 23, 36] for comparing the output of said counting means [12, 22, 37] to a second predetermined value N2 or -N2 and for generating an equality detect output when the output of said counting means [12, 22, 37] corresponds to the value N2 or -N2; and logic means [14 -16, 24-26, 38-42], responsive to said counting means [12, 22, 37] and said comparing means [13, 23, 36], for generating selection signals for the programmable dividing means such that the programmable dividing means [11, 21, 31] divides the input signal by the ratio R1, N1 times and by the ratio R2, N2 times; said logic means including first latching means [14, 24 38] which is set upon the detection of the intermediate output, and a first AND gate [15, 25, 41] responsive to the equality detect output of said first comparing means [13, 23, 36] and said first latching means [14, 24, 38], in order that said counting means [12, 22, 37] can be reloaded with said predetermined value N1 or -N1 and the cycle restarted.

- A variable ratio frequency divider circuit according to claim 1, characterized in that said counting means [12] is a binary down counter and the intermediate output is zero.

- A variable ratio frequency divider circuit according to claim 1, characterized in that said counting means [22, 37] is a binary up counter and the intermediate output is all logical ones.

- 4. A variable ratio frequency divider circuit according to claim 1 which further includes second programmable dividing means [30] having division ratios R3 and R4, for dividing the input signal; and second comparing means [35] for comparing the output of said counting means to a third predetermined value

15

20

N3 and for generating an output when the output of said counting means [37] corresponds to the value N3.

- 5. A variable ratio frequency divider circuit according to claim 2 or 3, characterized by said logic means further including second latching means [16] responsive to said first AND gate [15] and said divided output signal.

- 6. A variable ratio frequency divider circuit according to claim 4, characterized by said logic means further including second latching means [39] responsive to said first latching means [38] and said first AND gate [41]; a second AND gate [42] responsive to said second latching means [39] and said second comparing means [35]; and third latching means [40] responsive to said second AND gate [42] and the divided output signal.

- 7. An apparatus according to claim 1 included in a phase locked loop having a voltage controlled oscillator [50] for generating an output; and phase comparison means [52] for comparing the divided output signal of said variable dividing means [51] to a reference signal to generate a phase error signal which is supplied to said voltage controlled oscillator [50].

- An apparatus according to claim 7 which further includes means for filtering [54] the phase error signal and means for integrating [54] the phase error signal.

- An apparatus according to claim 8 which further includes dividing means [53] for dividing the reference signal prior to its application to said phase comparison means.

- 10. A method of using a single digital counter [12, 22, 37] with a limited maximum operating frequency to control a preceding higher frequency stage [11,21, 31] having two available division ratios R1 and R2, comprising the steps of:

counting from a value N1 or -N1 which is determined by an initial state to which the digital counter [12, 22, 37] is set, while the preceding higher frequency stage [11, 21, 31] is set to divide by R1;

reaching a conveniently detectable state of either zero or all ones, such that the preceding higher frequency stage [11, 21, 31] has divided by R1, N1 times;

changing the division ratio to a value R2 after reaching the conveniently detectable state; continuing to divide by the ratio R2 until the digital counter [12, 22, 37] is detected by a com-

parator [13, 23, 36] to have reached a state corresponding to the value N2 or -N2 such that the preceding higher frequency stage [11, 21, 31] divides by the ratio R2, N2 times; and resetting the digital counter [12, 22, 37] with logic means, said logic means including a first latching means [14, 28, 38] which is set upon the detection of the conveniently detectable state, and a first AND gate [15, 25, 41] responsive to the output of said comparator [13, 23, 36] and said first latching means [14, 24, 38], in order that the digital counter [12, 22, 37] can be reloaded with said value N1 or -N1 and the cycle restarted.

11. A method according to claim 10 which further includes the step of varying the values of N1 or -N1 and N2 or -N2 such that the overall division ratio N varies in steps of one over a range of contiguous values.

## Patentansprüche

Frequenzteilerschaltung mit einem variablen Verhältnis, die eine programmierbare Teilungseinrichtung (11, 21, 31) mit Teilungsverhältnissen (R1 und R2) enthält, zum Teilen eines Eingangssignals in ein geteiltes Ausgangssignal, umfassend:

eine Zähleinrichtung (12, 22, 37), die mit einem vorgegebenen Wert N1 oder -N1 geladen ist und auf das geteilte Ausgangssignal der programmierbaren Teilungseinrichtung (11, 21, 31) anspricht, zum Erzeugen einer Vielzahl von Ausgängen einschließlich eines vorgegebenen Zwischenausgangs von entweder Null oder nur Einsen;

eine erste Vergleichseinrichtung (13, 23, 36) zum Vergleichen des Ausgangs der Zähleinrichtung (12, 22, 37) mit einem zweiten vorgegebenen Wert N2 oder -N2 und zum Erzeugen eines Gleichheitserfassungsausgangs, wenn der Ausgang der Zähleinrichtung (12, 22, 37) dem Wert N2 oder -N2 entspricht; und

eine Logikeinrichtung (14-16, 24-26, 38-42), die auf die Zähleinrichtung (12, 22, 37) und die Vergleichseinrichtuntg (13, 23, 36) anspricht, zum Erzeugen von Wählsignalen für die programmierbare Teilungseinrichtung, so daß die programmierbare Teilungseinrichtung (11, 21, 31) das Eingangssignal durch das Verhältnis R1 N1 mal und durch das Verhältnis R2 N2 mal teilt; wobei die Logikeinrichtung eine erste Halteeinrichtung (14, 24, 38), die bei der Erfassung des Zwischenausgangs gesetzt wird, und ein

15

20

erstes UND-Gatter (15, 25, 41), das auf den Gleichheitserfassungsausgang der ersten Vergleichseinrichtung (13, 23, 36) und die erste Halteeinrichtung (14, 24, 38) anspricht, damit die Zähleinrichtung (12, 22, 37) mit dem vorgegebenen Wert N1 oder -N1 neu geladen werden und der Zyklus neu gestartet werden kann, umfaßt.

2. Frequenzteilerschaltung mit variablem Verhältnis nach Anspruch 1,

dadurch gekennzeichnet, daß die Zähleinrichtung (12) ein binärer Abwärtszähler ist und der Zwischenausgang Null ist.

3. Frequenzteilerschaltung mit variablem Verhältnis nach Anspruch 1,

dadurch gekennzeichnet, daß die Zähleinrichtung (22, 37) ein binärer Aufwärts zähler und der Zwischenausgang nur logische Einsen ist.

- 4. Frequenzteilerschaltung mit variablem Verhältnis nach Anspruch 1, die ferner umfaßt: eine zweite programmierbare Teilungseinrichtung (30) mit Teilungsverhältnissen R3 und R4, zum Teilen des Eingangssignals; und eine zweite Vergleichseinrichtung (35) zum Vergleichen des Ausgangs der Zähleinrichtung mit einem dritten vorgegebenen Wert N3 und zum Erzeugen eines Ausgangs, wenn der Ausgang der Zähleinrichtung (37) einem Wert N3 antenspricht.

- 5. Frequenzteilerschaltung mit variablem Verhältnis nach Anspruch 2 oder 3, dadurch gekennzeichnet, daß die Logikeinrichtung ferner eine zweite Halteeinrichtung (16) umfaßt, die auf das erste UND-Gatter (15) und das geteilte Ausgangssignal anspricht.

- 6. Frequenzteilerschaltung mit variablem Verhältnis nach Anspruch 4, dadurch gekennzeichnet, daß die Logikeinrichtung ferner umfaßt: eine zweite Halteeinrichtung (39), die auf die erste Halteeinrichtung (38) und das erste UND-Gatter (41) anspricht; ein zweites UND-Gatter (42), welches auf die zweite Halteeinrichtung (39) und die zweite Vergleichseinrichtung (35) anspricht; und eine dritte Halteeinrichtung (40), die auf das zweite UND-Gatter (42) und das geteilte Ausgangssignal anspricht.

- 7. Vorrichtung nach Anspruch 1, enthalten in einer phasenstarren Regelschleife mit einem spannungsgesteuerten Oszillator (50) zum Erzeugen eines Ausgangs; und einer Phasenvergleichseinrichtung (52) zum Vergleichen des geteilten Ausgangssignals der variablen Teilungseinrichtung (31) mit einem Referenzsignal, um ein Phasenfehlersignal

zu erzeugen, welches an den spannungsgesteuerten Oszillator (50) angelegt wird.

- Vorrichtung nach Anspruch 7, die ferner eine Einrichtung zum Filtern (54) des Phasenfehlersignals und eine Einrichtung zum Integrieren (54) des Phasenfehlersignals umfaßt.

- Vorrichtung nach Anspruch 8, die ferner eine Teilungseinrichtung (53) zum Teilen des Referenzsignals vor dessen Anlegung an die Phasenvergleichseinrichtung umfaßt.

- 10. Verfahren zum Verwenden eines einzelnen digitalen Zählers (12, 22, 37) mit einer begrenzten maximalen Betriebsfrequenz, um eine vorangehende Stufe (11, 21, 31) höherer Frequenz mit zwei verfügbaren Teilungsverhältnissen R1 und R2 zu steuern, umfassend die folgenden Schritte:

Zählen von einem Wert N1 oder -N1, der durch einen Anfangszustand bestimmt wird, auf den der digitale Zähler (12, 22, 37) gesetzt wird, während die vorangehende Stufe (11, 21, 31) höherer Frequenz zum Teilen durch (R1) eingestellt wird;

Erreichen eines einfach erfaßbaren Zustands von entweder Null oder nur Einsen, so daß die vorangehende Stufe (11, 21, 31) höherer Frequenz durch R1 N1 mal geteilt hat;

Ändern des Teilungsverhältnisses auf einen Wert R2 nach Erreichen des einfach erfaßbaren Zustands;

Fortsetzen einer Teilung durch das Verhältnis R2, bis von einem Vergleicher (13, 23, 36) erfaßt wird, daß der digitale Zähler (12, 22, 37) einen Zustand erreicht hat, der dem Wert N2 oder -N2 entspricht, so daß die vorangehende Stufe (11, 21, 31) höherer Frequenz durch das Verhältnis R2 N2 mal geteilt hat; und

Zurücksetzen des digitalen Zählers (12, 22, 37) mit einer Logikeinrichtung, wobei die Logikeinrichtung eine Halteeinrichtung (14, 28, 38), die auf die Erfassung des einfach erfaßbaren Zustands hin gesetzt wird, und ein erstes UND-Gatter (15, 25, 41), das auf den Ausgang des Vergleichers (13, 23, 36) und die erste Halteeinrichtung (14, 24, 38) anspricht, damit der digitale Zähler (12, 22, 37) mit dem Wert N1 oder -N1 erneut geladen werden und der Zyklus erneut gestartet werden kann, umfaßt.

Verfahren nach Anspruch 10. ferner umfassend den Schritt einer Änderung der Werte von N1 oder -N1

15

und N2 oder -N2, so daß sich das Gesamtteilungsverhältnis N in Schritten von Eins über einem Bereich von zusammenhängenden Werten verändert.

#### Revendications

1. Circuit diviseur de fréquence à rapport variable, comprenant des moyens de division programmables [11, 21, 31] ayant des rapports de division R1 et R2, pour diviser un signal d'entrée de façon à donner un signal de sortie divisé, comprenant :

> des moyens de comptage [12, 22, 37] chargés avec une valeur prédéterminée N1 ou -N1, et réagissant au signal de sortie divisé des moyens de division programmables [11, 21, 31] pour générer un ensemble de signaux de sortie, comprenant un signal de sortie intermédiaire prédéterminé qui a soit une valeur zéro, soit 20 une valeur ne comprenant que des uns;

des premiers moyens de comparaison [13, 23, 36] pour comparer le signal de sortie des moyens de comptage [12, 22, 37] avec une seconde valeur prédéterminée N2 ou -N2, et pour générer un signal de sortie de détection d'égalité lorsque le signal de sortie des moyens de comptage [12, 22, 37] correspond à la valeur N2 ou -N2; et

des moyens logiques [14-16, 24-26, 38-42], réagissant aux moyens de comptage [12, 22, 37] et aux moyens de comparaison [13, 23, 36], en générant des signaux de sélection pour les moyens de division programmables, de façon que les moyens de division programmables [11, 21, 31] divisent le signal d'entrée N1 fois par le rapport R1 et N2 fois par le rapport R2; ces moyens logiques comprenant des premiers moyens à bascule [14, 24, 38] qui sont instaurés sous l'effet de la détection du signal de sortie intermédiaire, et une première porte ET [15, 25, 41] qui réagit au signal de sortie de détection d'égalité des premiers moyens de comparaison [13, 23, 36] et aux premiers moyens à bascule [14, 24, 38], de façon que les moyens de comptage [12, 22, 37] puissent être rechargés avec la valeur prédéterminée N1 ou -N1, et que le cycle puisse redémarrer.

- 2. Circuit diviseur de fréquence à rapport variable selon la revendication 1, caractérisé en ce que les moyens de comptage [12] consistent en un compteur binaire en sens décroissant, et le signal de sortie intermédiaire a la valeur zéro.

- 3. Circuit diviseur de fréquence à rapport variable selon la revendication 1, caractérisé en ce que les moyens de comptage [22, 37] consistent en un

compteur binaire en sens croissant, et le signal de sortie intermédiaire a une valeur ne comprenant que des uns logiques.

- Circuit diviseur de fréquence à rapport variable selon la revendication 1, comprenant en outre des seconds moyens de division programmables [30] ayant des rapports de division R3 et R4, pour diviser le signal d'entrée; et des seconds moyens de comparaison [35] pour comparer le signal de sortie des moyens de comptage avec une troisième valeur prédéterminée N3, et pour générer un signal de sortie lorsque le signal de sortie des moyens de comptage [37] correspond à la valeur N3.

- Circuit diviseur de fréquence à rapport variable selon la revendication 2 ou 3, caractérisé en ce que les moyens logiques comprennent en outre des seconds moyens à bascule [16] qui réagissent à la première porte ET [15] et au signal de sortie divisé.

- 6. Circuit diviseur de fréquence à rapport variable selon la revendication 4, caractérisé en ce que les moyens logiques comprennent en outre des seconds moyens à bascule [39] qui réagissent aux premiers moyens à bascule [38] et à la première porte ET [41]; une seconde porte ET [42] qui réagit aux seconds moyens à bascule [39] et aux seconds moyens de comparaison [35]; et des troisièmes moyens à bascule [40] qui réagissent à la seconde porte ET [42] et au signal de sortie divisé.

- Dispositif selon la revendication 1, incorporé dans une boucle d'asservissement de phase ayant un oscillateur commandé par tension [50] pour générer un signal de sortie; et des moyens de comparaison de phase [52] pour comparer le signal de sortie divisé des moyens de division variables [51] avec un signal de référence, de façon à générer un signal d'erreur de phase qui est appliqué à l'oscillateur commandé par tension [50].

- Dispositif selon la revendication 7, comprenant en outre des moyens [54] pour filtrer le signal d'erreur de phase et des moyens [54] pour intégrer le signal d'erreur de phase.

- Dispositif selon la revendication 8, comprenant en outre des moyens de division [53] pour diviser le signal de référence avant son application aux moyens de comparaison de phase.

- 10. Procédé d'utilisation d'un seul compteur numérique [12, 22, 37] avec une fréquence de fonctionnement maximale limitée, pour commander un étage de fréquence supérieure précédent [11, 21, 31] ayant deux rapports de division disponibles, R1 et R2. comprenant les étapes suivantes :

on compte à partir d'une valeur N1 ou -N1 qui est déterminée par un état initial auquel le compteur numérique [12, 22, 37] est positionné, pendant que l'étage de fréquence supérieure précédent [11, 21, 31] est réglé pour diviser par R1;

on atteint un état commodément détectable, qui est soit zéro soit un état ne comprenant que des uns, de façon que l'étage de fréquence supérieure précédent [11, 21, 31] ait divisé N1 fois

on change le rapport de division pour lui donner une valeur R2 après avoir atteint l'état commodément détectable;

on continue à diviser par le rapport R2 jusqu'à ce qu'un comparateur [13, 23, 36] détecte que le compteur numérique [12, 22, 37] a atteint un état correspondant à la valeur N2 ou -N2, de façon que l'étage de fréquence supérieure précédent [11, 21, 31] divise N2 fois par le rapport R2; et

on restaure le compteur numérique [12, 22, 37] avec des moyens logiques, ces moyens logiques comprenant des premiers moyens à bascule [14, 28, 38] qui sont instaurés sous l'effet 25 de la détection de l'état commodément détectable, et une première porte ET [15, 25, 41] qui réagit au signal de sortie du comparateur [13, 23, 36] et aux premiers moyens à bascule [14, 24, 38], de façon que le compteur numérique [12, 22, 37] puisse être rechargé avec la valeur N1 ou -N1 et que le cycle puisse redémarrer.

11. Procédé selon la revendication 10, comprenant en outre l'étape qui consiste à faire varier les valeurs de N1 ou -N1 et de N2 ou -N2, de façon que le rapport de division global N varie par pas de 1 sur une plage de valeurs contiguës.

40

45

50