(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7086562号

(P7086562)

(45)発行日 令和4年6月20日(2022.6.20)

(24)登録日 令和4年6月10日(2022.6.10)

(51)国際特許分類

|         |                |         |      |

|---------|----------------|---------|------|

| G 0 5 F | 3/02 (2006.01) | G 0 5 F | 3/02 |

| G 0 5 F | 1/56 (2006.01) | G 0 5 F | 1/56 |

F I

|  |  |         |

|--|--|---------|

|  |  | 3 1 0 E |

|--|--|---------|

請求項の数 20 (全29頁)

(21)出願番号 特願2017-211132(P2017-211132)

(22)出願日 平成29年10月31日(2017.10.31)

(65)公開番号 特開2019-82951(P2019-82951A)

(43)公開日 令和1年5月30日(2019.5.30)

審査請求日 令和2年10月23日(2020.10.23)

(73)特許権者 502161508

シナブティクス インコーポレイテッド

アメリカ合衆国, 95131 カリフォルニア州, サンノゼ, マッケイ ドライブ 1109

(74)代理人 100205350

弁理士 狩野 芳正

(74)代理人 100117617

弁理士 中尾 圭策

(72)発明者 曽根 康彦

東京都中野区中野4丁目10番2号 シナブティクス・ジャパン合同会社内

審査官 佐藤 匡

最終頁に続く

(54)【発明の名称】 バンドギャップリファレンス回路

## (57)【特許請求の範囲】

## 【請求項1】

電源線に接続され、第1ノードに第1電流を供給し、前記第1ノードと仮想ショートされた第2ノードに第2電流を供給するように構成された第1カレントミラーと、

前記第2ノードと接地線の間の、前記電源線に供給される電源電圧に抵抗が依存するよう<sup>に構成された</sup>第1可変抵抗素子と、

を備える

バンドギャップリファレンス回路。

## 【請求項2】

更に、

前記第1ノードと前記接地線の間の第1p n接合素子と、

前記第1可変抵抗素子と直列に接続された第2p n接合素子と、

を備える

請求項1に記載のバンドギャップリファレンス回路。

## 【請求項3】

更に、前記第2ノードと前記接地線の間に、前記第1可変抵抗素子及び前記第2p n接合素子と直列に接続された第1抵抗素子を備える

請求項2に記載のバンドギャップリファレンス回路。

## 【請求項4】

更に、前記第1カレントミラーの第1出力と、前記第2ノードの間に、前記電源電圧に抵

抗が依存するように構成された第2可変抵抗素子を備え、

前記第1カレントミラーが前記第1出力で前記第2電流を出力するように構成された請求項2又は3に記載のバンドギャップリファレンス回路。

【請求項5】

更に、前記第1カレントミラーと前記第2ノードの間に、前記第2可変抵抗素子と直列に接続された第2抵抗素子を備え、

前記第1カレントミラーは、前記第2可変抵抗素子及び前記第2抵抗素子を介して前記第2ノードに前記第2電流を供給するように構成された

請求項4に記載のバンドギャップリファレンス回路。

【請求項6】

更に、前記第1カレントミラーの前記第1電流を出力する第2出力端子と、前記第1ノードの間に、前記電源電圧に抵抗が依存する第3可変抵抗素子を備える

請求項4に記載のバンドギャップリファレンス回路。

【請求項7】

更に、

前記第1カレントミラーと前記第2ノードの間に、前記第2可変抵抗素子と直列に接続された第2抵抗素子と、

前記第1カレントミラーと前記第1ノードの間に、前記第3可変抵抗素子と直列に接続された第3抵抗素子

とを備え、

前記第1カレントミラーは、前記第2可変抵抗素子及び前記第2抵抗素子を介して前記第2ノードに前記第2電流を供給し、前記第3可変抵抗素子及び前記第3抵抗素子を介して前記第1ノードに前記第1電流を供給するように構成された

請求項6に記載のバンドギャップリファレンス回路。

【請求項8】

前記第1pn接合素子は、ダイオード接続された第1バイポーラトランジスタを含み、前記第2pn接合素子は、ダイオード接続された第2バイポーラトランジスタを含む

請求項2乃至7のいずれか1項に記載のバンドギャップリファレンス回路。

【請求項9】

更に、出力ノードと前記電源線の間に電流-電圧変換回路部を備え、

前記第1カレントミラーが、前記出力ノードに第3電流を供給するように構成され、

前記電流-電圧変換回路部が、前記出力ノードから出力される出力電圧を前記第3電流から生成するように構成された

請求項2又は4に記載のバンドギャップリファレンス回路。

【請求項10】

更に、

前記第1ノードと前記接地線の間に、前記第1pn接合素子と並列に接続された第2抵抗素子と、

前記第2ノードと前記接地線の間に、前記第2pn接合素子と並列に接続された第3抵抗素子

とを備える

請求項9に記載のバンドギャップリファレンス回路。

【請求項11】

前記電流-電圧変換回路部が、前記出力ノードと前記接地線の間に、前記電源電圧に依存する第4可変抵抗素子を備える

請求項9又は10に記載のバンドギャップリファレンス回路。

【請求項12】

前記電流-電圧変換回路部が、更に、

前記出力ノードと前記接地線の間の第3pn接合素子と、

前記第3pn接合素子と前記第4可変抵抗素子に並列に接続された第5抵抗素子

10

20

30

40

50

とを備える

請求項 1\_1 に記載のバンドギャップリファレンス回路。

【請求項 1\_3】

前記電流 - 電圧変換回路部が、更に、前記出力ノードと前記接地線の間に、前記第 3 p n 接合素子と前記第 4 可変抵抗素子に直列に接続された第 6 抵抗素子を備える

請求項 1\_2 に記載のバンドギャップリファレンス回路。

【請求項 1\_4】

前記第 1 p n 接合素子は、第 1 バイポーラトランジスタを含み、

前記第 2 p n 接合素子は、第 2 バイポーラトランジスタを含み、

当該バンドギャップリファレンス回路は、更に、第 3 ノードと前記接地線の間の第 3 バイポーラトランジスタを含み、

10

前記第 1 バイポーラトランジスタ、前記第 2 バイポーラトランジスタ及び前記第 3 バイポーラトランジスタのベースは、前記第 3 バイポーラトランジスタのコレクタに共通に接続され、

前記第 1 カレントミラーは、前記第 3 ノードに第 4 電流を出力するように構成され、

前記第 1 ノード、前記第 2 ノード及び前記第 3 ノードは、互いに仮想ショートされ、

前記第 1 電流が、前記第 1 バイポーラトランジスタのコレクタを流れ、

前記第 2 電流が、前記第 2 バイポーラトランジスタのコレクタを流れ、

前記第 4 電流が、前記第 3 バイポーラトランジスタのコレクタを流れ、

請求項 1\_2 又は 1\_3 に記載のバンドギャップリファレンス回路。

20

【請求項 1\_5】

更に、

第 5 電流を前記第 3 ノードに供給し、第 6 電流を前記電流 - 電圧変換回路部に供給するように構成された第 2 カレントミラーと、

前記第 1 ノードに第 1 入力が接続され、前記第 2 ノードに第 2 入力が接続され、前記第 1 電流、前記第 2 電流、前記第 3 電流及び前記第 4 電流を制御する第 1 制御電圧を前記第 1 カレントミラーに出力するように構成された第 1 演算増幅器と、

前記第 1 ノードに第 1 入力が接続され、前記第 3 ノードに第 2 入力が接続され、前記第 5 電流及び前記第 6 電流を制御する第 2 制御電圧を前記第 2 カレントミラーに出力するように構成された第 2 演算増幅器

30

とを備える

請求項 1\_4 に記載のバンドギャップリファレンス回路。

【請求項 1\_6】

前記第 1 可変抵抗素子が、前記電源電圧がゲートに供給された N M O S トランジスタを含む請求項 1 乃至 1\_3 のいずれか一項に記載のバンドギャップリファレンス回路。

【請求項 1\_7】

出力電圧の絶対温度に対する温度依存性を低減する方法であって、

電源線に接続された第 1 カレントミラーにより、第 1 ノードに第 1 電流を供給することと、前記第 1 カレントミラーにより、前記第 1 ノードと仮想ショートされた第 2 ノードに第 2 電流を供給することと、

前記電源線に供給される電源電圧に依存する抵抗を有する第 1 可変抵抗素子を介して、前記第 2 ノードから接地線に前記第 2 電流の少なくとも一部を流すことと、

前記第 1 カレントミラーに接続された出力ノードから前記出力電圧を得ることと、

を含む

方法。

【請求項 1\_8】

更に、

第 1 p n 接合素子を介して前記第 1 ノードから前記接地線に前記第 1 電流の少なくとも一部を流すこと

を含み、

40

50

前記第2ノードから前記接地線に前記第2電流の少なくとも一部を流すことは、前記第1可変抵抗素子と、前記第1可変抵抗素子と直列に接続された第2p-n接合素子とを介して前記第2ノードから前記接地線に前記第2電流の少なくとも一部を流すことを含む請求項17に記載の方法。

**【請求項19】**

前記第2ノードに前記第2電流を供給することは、前記第1カレントミラーにより、前記電源電圧に抵抗が依存する第2可変抵抗素子を介して前記第2電流を前記第2ノードに供給することを含む

請求項17に記載の方法。

**【請求項20】**

前記第1可変抵抗素子が、前記電源電圧がゲートに供給されたNMOStランジスタを含む

請求項17乃至19のいずれか1項に記載の方法。

10

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本開示は、バンドギャップリファレンス回路に関する。

**【背景技術】**

**【0002】**

バンドギャップリファレンス回路は、p-n接合の電流-電圧特性の温度依存性を利用して温度に対して安定した出力電圧を生成する電圧生成回路であり、半導体集積回路において広く用いられる。

20

**【0003】**

バンドギャップリファレンス回路の出力電圧は、一般に、外乱に対して相当に安定である。しかしながら、バンドギャップリファレンス回路の構成によっては、出力電圧が電源電圧に僅かに依存する場合がある。

**【先行技術文献】**

**【非特許文献】**

**【0004】**

**【文献】** H. Banba et al., "A CMOS Bandgap Reference Circuit with Sub-1-V Operation", IEEE Journal of Solid-state Circuits, vol. 34, pp. 670-674, May 1999.

Yuichi Okuda et al., "A Trimming-Free CMOS Bandgap-Reference Circuit with Sub-1-V-Supply Voltage Operation", 2007 Symposium on VLSI Circuits Digest of Technical Papers, PP 96-97

30

**【発明の概要】**

**【0005】**

一実施形態では、バンドギャップリファレンス回路が、電源線に接続され、第1ノードに第1電流を供給し、第1ノードと仮想ショートされた第2ノードに第2電流を供給するカレントミラーと、第1ノードと接地線の間の第1p-n接合素子と、第2ノードと接地線の間の、電源線に供給される電源電圧に抵抗が依存する可変抵抗素子と、可変抵抗素子と直列に接続された第2p-n接合素子とを備える。

40

**【0006】**

他の実施形態では、バンドギャップリファレンス回路が、電源線に供給される電源電圧に抵抗が依存する可変抵抗素子と、電源線に接続され、第1ノードに第1電流を供給し、第1ノードと仮想ショートされた第2ノードに可変抵抗素子を介して第2電流を供給するカレントミラーと、第1ノードと接地線の間の第1p-n接合素子と、第2ノードと接地線の間の第2p-n接合素子と、第2p-n接合素子に直列に接続された第1抵抗素子とを備える。

**【0007】**

更に他の実施形態では、バンドギャップリファレンス回路が、電源線に接続され、第1ノードに第1電流を供給し、第1ノードと仮想ショートされた第2ノードに第2電流を供給し、出力ノードに第3電流を供給するカレントミラーと、第1ノードと接地線の間の第1

50

p n 接合素子と、第 2 ノードと接地線の間の第 2 p n 接合素子と、第 2 p n 接合素子に直列に接続された第 1 抵抗素子と、出力ノードと接地線の間の、電源線に供給される電源電圧に抵抗が依存する可変抵抗素子とを備える。

【図面の簡単な説明】

【0 0 0 8】

【図 1】一実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 2】可変抵抗素子の構成の例を示す図である。

【図 3】他の実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 4】更に他の実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 5】他の実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

10

【図 6】他の実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 7】一実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 8】一実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 9】一実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 10】一実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 11】一実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 12】一実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 13】一実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【図 14】一実施形態のバンドギャップリファレンス回路の構成を示す回路図である。

【発明を実施するための形態】

【0 0 0 9】

以下では、添付図面を参照しながら、本開示の様々な実施形態を説明する。以下の説明において、同一又は類似する構成要素を、同一又は対応する参照符号で参照することがある。

【0 0 1 0】

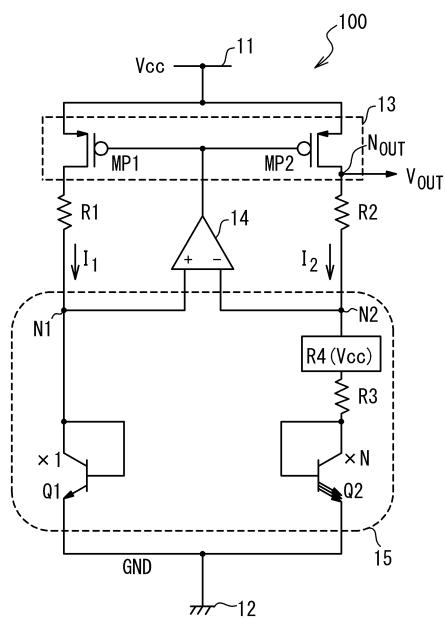

図 1 に示す一実施形態では、バンドギャップリファレンス回路 1 0 0 が、電源線 1 1 と、接地線 1 2 と、カレントミラー 1 3 と、演算増幅器 1 4 と、抵抗素子 R 1、R 2、R 3 と、可変抵抗素子 R 4 と、バイポーラトランジスタ Q 1、Q 2 とを備えている。電源線 1 1 には電源電圧 V c c が供給され、接地線 1 2 は、接地されている。

【0 0 1 1】

カレントミラー 1 3 は、電流 I 1、I 2 の電流レベルが同一であるように電流 I 1、I 2 を出力する。本実施形態では、カレントミラー 1 3 が、1 対の PMOS トランジスタ M P 1、M P 2 を備えている。PMOS トランジスタ M P 1、M P 2 は、ゲートが互いに接続され、更にソースが共通に電源線 1 1 に接続されている。PMOS トランジスタ M P 1 のドレインは、抵抗素子 R 1 を介してノード N 1 に接続され、PMOS トランジスタ M P 2 のドレインは、抵抗素子 R 2 を介してノード N 2 に接続されている。PMOS トランジスタ M P 1 のドレインは、電流 I 1 を出力する第 1 出力として用いられ、PMOS トランジスタ M P 2 のドレインは、電流 I 2 を出力する第 2 出力として用いられる。一実施形態では、抵抗素子 R 1、R 2 は、それらの抵抗が同一であるように設計される。

【0 0 1 2】

演算増幅器 1 4 は、非反転入力がノード N 1 に接続されており、反転入力がノード N 2 に接続されており、出力が PMOS トランジスタ M P 1、M P 2 のゲートに接続されている。演算増幅器 1 4 は、電流 I 1、I 2 を制御する制御電圧をカレントミラー 1 3 の PMOS トランジスタ M P 1、M P 2 のゲートに供給する。演算増幅器 1 4 は、ノード N 1、N 2 が同一の電位を有するように PMOS トランジスタ M P 1、M P 2 のゲートの電位を制御する。ノード N 1、N 2 は、このような演算増幅器 1 4 の動作によって仮想ショートされる (virtually shorted)。カレントミラー 1 3 及び演算増幅器 1 4 は、総合すると、ノード N 1、N 2 を同一の電位に制御すると共に、ノード N 1、N 2 に同一電流レベルの電流を供給する電流供給回路部として動作することになる。

【0 0 1 3】

バイポーラトランジスタ Q 1 は、ダイオード接続されており、p n 接合を有する第 1 の p

20

30

40

50

n接合素子として動作する。本実施形態では、バイポーラトランジスタQ1としてNPNトランジスタが用いられている。バイポーラトランジスタQ1は、コレクタ及びベースが、ノードN1に共通に接続され、エミッタが接地線12に接続されている。このような接続により、電流I1は、バイポーラトランジスタQ1のベース-エミッタ間のpn接合を順方向に流れることになる。

【0014】

バイポーラトランジスタQ2と抵抗素子R3と可変抵抗素子R4とが、ノードN2と接地線12との間に直列に接続されている。図1においては、可変抵抗素子R4の抵抗が電源電圧Vccに依存することを明確にするために、可変抵抗素子R4が記号“R4(Vcc)”で示されている。なお、バイポーラトランジスタQ2、抵抗素子R3及び可変抵抗素子R4が接続される順序は、適宜に変更可能である。

10

【0015】

バイポーラトランジスタQ2も、バイポーラトランジスタQ1と同様にダイオード接続されており、第2のpn接合素子として動作する。本実施形態では、バイポーラトランジスタQ2としてNPNトランジスタが用いられている。バイポーラトランジスタQ2のベース-エミッタ接合の面積は、バイポーラトランジスタQ1のベース-エミッタ接合の面積のN倍である。ここで、Nは、1より大きい数である。本実施形態では、バイポーラトランジスタQ2は、コレクタ及びベースが、抵抗素子R3及び可変抵抗素子R4を介してノードN2に共通に接続され、エミッタが接地線12に接続されている。このような接続により、電流I2は、バイポーラトランジスタQ2のベース-エミッタ間のpn接合を順方向に流れることになる。

20

【0016】

なお、バイポーラトランジスタQ1、Q2としては、ダイオード接続されたPNPトランジスタが用いられてもよい。

【0017】

一実施形態では、MOSトランジスタと共に形成される寄生バイポーラトランジスタが、バイポーラトランジスタQ1、Q2として用いられ得る。このような構成は、バンドギャップリファレンス回路100を、MOSトランジスタが集積化される集積回路に集積することを容易にする。

30

【0018】

ダイオード接続されたバイポーラトランジスタQ1、Q2の代わりに、pn接合を有する他の素子を用いてもよい。例えば、一実施形態では、半導体基板に形成されたウェルと該ウェルに形成された拡散層とを備えるダイオードがバイポーラトランジスタQ1、Q2の代わりに用いられてもよい。他の実施形態では、ダイオード接続されたバイポーラトランジスタQ1、Q2の代わりに、ダイオード接続されたMOSトランジスタが用いられてもよい。

【0019】

可変抵抗素子R4は、電源線11に供給される電源電圧Vccに依存する抵抗を有している。一実施形態では、図2に図示されているように、可変抵抗素子R4として、ゲートに電源電圧Vccが供給されたNMOSトランジスタMN1が用いられてもよい。ゲートに電源電圧Vccが供給されているNMOSトランジスタMN1のオン抵抗は、電源電圧Vccに依存するので、NMOSトランジスタMN1は、可変抵抗素子R4として用いられ得る。この場合、可変抵抗素子R4の抵抗は、電源電圧Vccが増大すると減少する。可変抵抗素子R4として用いられるNMOSトランジスタのゲートに、電源電圧Vccの代わりに、電源電圧Vccから例えば電圧分圧によって生成されたバイアス電圧が供給されてもよい。他の実施形態では、可変抵抗素子R4として、PMOSトランジスタが用いられてもよい。

40

【0020】

本実施形態では、バンドギャップリファレンス回路100の出力電圧Voutは、PMOSトランジスタMP2のドレインと抵抗素子R2とを接続する出力ノードNoutから出

50

力される。このような構成では、出力電圧  $V_{out}$  は、バイポーラトランジスタ Q 2 のベース - エミッタ電圧  $V_{BE2}$  と、抵抗素子 R 2、R 3、可変抵抗素子 R 4 における電圧降下の和として生成される。以下に議論するように、抵抗素子 R 2、R 3、可変抵抗素子 R 4 を流れる電流  $I_2$  が、正の温度依存性を有する一方で、バイポーラトランジスタ Q 2 のベース - エミッタ電圧  $V_{BE2}$  は、絶対温度  $T$  に対して負の温度依存性を有している。このため、バンドギャップリファレンス回路 100 の出力電圧  $V_{out}$  は、絶対温度  $T$  に対して温度依存性が小さい。詳細には、バンドギャップリファレンス回路 100 は、以下のように動作して出力電圧  $V_{out}$  を生成する。

【0021】

バイポーラトランジスタ Q 1、Q 2、抵抗素子 R 3 及び可変抵抗素子 R 4 の作用により、ノード N 1、N 2 に供給される電流  $I_1$ 、 $I_2$  は、絶対温度に比例する。この意味で、バイポーラトランジスタ Q 1、Q 2 と抵抗素子 R 3 と可変抵抗素子 R 4 とを、総称して、P-TAT (proportional to absolute temperature) 電流生成回路部 15 と呼ぶことがある。

10

【0022】

詳細には、カレントミラー 13 によって電流  $I_1$ 、 $I_2$  が同一の電流レベル  $I$  に制御される場合、バイポーラトランジスタ Q 2 のベース - エミッタ接合の面積がバイポーラトランジスタ Q 1 のベース - エミッタ接合の面積の N 倍であることから、バイポーラトランジスタ Q 1 のベース - エミッタ電圧  $V_{BE1}$  と、バイポーラトランジスタ Q 2 のベース - エミッタ電圧  $V_{BE2}$  とについて、例えば下記式 (1a) (1b) が成立する。

20

【数 1】

$$V_{BE1} = \frac{kT}{q} \ln\left(\frac{I}{I_S}\right) \quad \cdots(1a)$$

$$V_{BE2} = \frac{kT}{q} \ln\left(\frac{I}{I_S} \cdot \frac{1}{N}\right) \quad \cdots(1b)$$

30

ここで、 $I_S$  は、逆方向飽和電流であり、 $k$  は、ボルツマン定数であり、 $T$  は、絶対温度であり、 $q$  は、電気素量である。

【0023】

ノード N 1 とノード N 2 が仮想ショートされており、ノード N 2 の電圧が、バイポーラトランジスタ Q 1 のベース - エミッタ電圧  $V_{BE1}$  に一致することから、下記式 (2) が成立する：

40

【数 2】

50

$$I = \frac{V_{BE1} - V_{BE2}}{R3 + R4(Vcc)} \quad \cdots (2)$$

10

$R_4$  ( $V_{cc}$ ) は、可変抵抗素子  $R_4$  の抵抗であり、電源電圧  $V_{cc}$  に依存する。

【0024】

式 (1a)、(1b) を式 (2) に代入することにより、電流  $I_1$ 、 $I_2$  の電流レベル  $I$  が下記式 (3) として得られる：

【数3】

20

$$I = \frac{Vt \cdot \ln(N)}{R3 + R4(Vcc)} \quad \cdots (3)$$

30

ここで、 $V_t$  は、熱電圧であり、下記式 (4) で与えられる。

【数4】

$$Vt = \frac{kT}{q} \quad \cdots (4)$$

40

電流  $I_1$ 、 $I_2$  の電流レベル  $I$  は、絶対温度  $T$  に比例する。電流  $I_2$  が絶対温度  $T$  に比例して増加するので、抵抗素子  $R_2$ 、 $R_3$ 、可変抵抗素子  $R_4$  で発生する電圧降下も、絶対温度  $T$  に比例して増加する。

50

## 【0025】

出力電圧  $V_{out}$  は、抵抗素子  $R_2$ 、 $R_3$  及び可変抵抗素子  $R_4$  で発生する電圧降下とバイポーラトランジスタ  $Q_2$  のベース - エミッタ電圧  $V_{BE2}$  との和であり、例えば下記式(5)で表される：

## 【数5】

$$\begin{aligned}

V_{out} &= I \cdot (R_2 + R_3 + R_4(V_{cc})) + V_{BE2} \\

&= \frac{V_t \cdot \ln(N)}{R_3 + R_4(V_{cc})} \cdot (R_2 + R_3 + R_4(V_{cc})) + V_{BE2} \\

&= V_t \cdot \ln(N) \cdot \left( 1 + \frac{R_2}{R_3 + R_4(V_{cc})} \right) + V_{BE2} \quad \cdots(5)

\end{aligned}$$

10

熱電圧  $V_t$  が温度に比例して増加する正の温度依存性を有する一方で、ベース - エミッタ電圧  $V_{BE2}$  が負の温度依存性を有しているから、 $N$ 、 $R_2$ 、 $R_3$ 、 $R_4$  を適正に調節することにより、出力電圧  $V_{out}$  の温度依存性を低減することができる。

20

## 【0026】

加えて、式(5)からも理解されるように、可変抵抗素子  $R_4$  を設けない場合のバンドギャップリファレンス回路100の出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性に応じて可変抵抗素子  $R_4$  の特性を選択することで、出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性を低減できる。可変抵抗素子  $R_4$  を設けない場合、出力電圧  $V_{out}$  は、電源電圧  $V_{cc}$  の増加に伴って増加することが多い。この場合には、電源電圧  $V_{cc}$  が増加したときに抵抗が増大するような可変抵抗素子  $R_4$  を用いることで、出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性を低減することができる。逆に、可変抵抗素子  $R_4$  を設けない場合に出力電圧  $V_{out}$  が電源電圧  $V_{cc}$  の増加に伴って減少する場合には、電源電圧  $V_{cc}$  が増加したときに抵抗が減少するような可変抵抗素子  $R_4$  を用いることで、出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性を低減することができる。

30

## 【0027】

図3に示す実施形態では、バンドギャップリファレンス回路100が、図1に示された構成と類似した構成となっている。ただし、可変抵抗素子  $R_4$  を含んでいないPTAT電流生成回路部16が用いられると共に、出力ノード  $N_{out}$  とノード  $N_2$  の間に抵抗素子  $R_2$  と可変抵抗素子  $R_5$  が直列に接続されている。

## 【0028】

可変抵抗素子  $R_4$  と同様に、可変抵抗素子  $R_5$  としては、ゲートに電源電圧  $V_{cc}$  が供給されたN MOSトランジスタが用いられてもよい(図2参照)。この場合、可変抵抗素子  $R_5$  の抵抗は、電源電圧  $V_{cc}$  が増大すると減少する。可変抵抗素子  $R_5$  として用いられるN MOSトランジスタのゲートに、電源電圧  $V_{cc}$  の代わりに、電源電圧  $V_{cc}$  から例えば電圧分圧によって生成されたバイアス電圧が供給されてもよい。他の実施形態では、可変抵抗素子  $R_5$  として、PMOSトランジスタが用いられてもよい。なお、抵抗素子  $R_2$  と可変抵抗素子  $R_5$  の位置は、交換可能である。

40

## 【0029】

図2に示す構成では、ノード  $N_2$  の電圧が、バイポーラトランジスタ  $Q_1$  のベース - エミッタ電圧  $V_{BE1}$  に一致することから、下記式(6)：

## 【数6】

50

$$I = \frac{V_{BE1} - V_{BE2}}{R3} \quad \cdots (6)$$

10

が成立し、よって、電流  $I_1$ 、 $I_2$  の電流レベル  $I$  は、下記式(7)：

【数7】

20

$$I = \frac{Vt \cdot \ln(N)}{R3} \quad \cdots (7)$$

30

で得られる。

【0030】

出力電圧  $V_{out}$  は、例えば下記式(8)で表されるように、抵抗素子  $R_2$ 、可変抵抗素子  $R_5$  及び抵抗素子  $R_3$  で発生する電圧降下とバイポーラトランジスタ  $Q_2$  のベース - エミッタ電圧  $V_{BE2}$  との和であり、 $N$ 、 $R_2$ 、 $R_3$  及び  $R_5$  ( $V_{cc}$ ) を適正に調節することにより、温度依存性の少ない又は全くない出力電圧  $V_{out}$  を実現できる。

【数8】

$$\begin{aligned} V_{out} &= I \cdot (R2 + R3 + R5(V_{cc})) + V_{BE2} \\ &= \frac{Vt \cdot \ln(N)}{R3} \cdot (R2 + R3 + R5(V_{cc})) + V_{BE2} \\ &= Vt \cdot \ln(N) \cdot \left(1 + \frac{R2 + R5(V_{cc})}{R3}\right) + V_{BE2} \quad \cdots (8) \end{aligned}$$

40

【0031】

50

また、可変抵抗素子 R 5 を設けない場合のバンドギャップリファレンス回路 100 の出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性に応じて、出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性を低減するように、可変抵抗素子 R 5 の特性を選択してもよい。可変抵抗素子 R 5 を設けない場合、出力電圧  $V_{out}$  は、電源電圧  $V_{cc}$  の増加に伴って増加することが多い。この場合には、電源電圧  $V_{cc}$  が増加したときに抵抗が減少するような可変抵抗素子 R 5 を用いることで、出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性を低減することができる。逆に、可変抵抗素子 R 5 を設けない場合に出力電圧  $V_{out}$  が電源電圧  $V_{cc}$  の増加に伴って減少する場合には、電源電圧  $V_{cc}$  が増加したときに抵抗が減少するような可変抵抗素子 R 5 を用いることで、出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性を低減することができる。

10

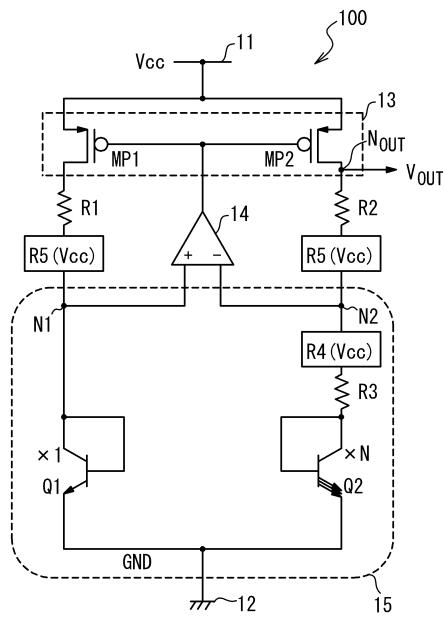

#### 【0032】

図 4 に示す一実施形態では、バンドギャップリファレンス回路 100 が、図 3 に示された構成と類似した構成となっているが、PMOS トランジスタ MP1 のドレインとノード N 1 の間に、抵抗素子 R 1 と可変抵抗素子 R 5 が直列に接続されている。図 3 の構成では、PMOS トランジスタ MP1、MP2 のドレインに接続される抵抗素子の抵抗が相違しているため、アーリ効果に起因して電流  $I_1$ 、 $I_2$  の電流レベルが相違し得る。一方で、図 4 の構成によれば、回路の対称性を高め、PMOS トランジスタ MP1、MP2 のアーリ効果に起因する電流  $I_1$ 、 $I_2$  の電流レベルの差を有効に低減することができる。なお、抵抗素子 R 1 と可変抵抗素子 R 5 の位置は交換可能である。

20

#### 【0033】

図 5 に示す一実施形態では、バンドギャップリファレンス回路 100 が、図 1 に示す構成と図 4 に示す構成の組み合わせとして構成される。図 5 の構成では、可変抵抗素子 R 4 を含んでいる P T A T 電流生成回路部 15 が用いられる。加えて、PMOS トランジスタ MP1 のドレインとノード N 1 の間に抵抗素子 R 1 と可変抵抗素子 R 5 が直列に接続され、PMOS トランジスタ MP2 のドレインとノード N 2 の間に抵抗素子 R 2 と可変抵抗素子 R 5 が直列に接続されている。

30

#### 【0034】

図 5 の構成では、出力電圧  $V_{out}$  は、抵抗素子 R 2、可変抵抗素子 R 5、可変抵抗素子 R 4 及び抵抗素子 R 3 で発生する電圧降下とバイポーラトランジスタ Q2 のベース - エミッタ電圧  $V_{BE2}$  との和であり、例えば下記式 (9) で表される：

#### 【数9】

$$\begin{aligned}

V_{out} &= I \cdot (R2 + R3 + R4(V_{cc}) + R5(V_{cc})) + V_{BE2} \\

&= \frac{Vt \cdot \ln(N)}{R3 + R4(V_{cc})} \cdot (R2 + R3 + R4(V_{cc}) + R5(V_{cc})) + V_{BE2} \\

&= Vt \cdot \ln(N) \cdot \left(1 + \frac{R2 + R5(V_{cc})}{R3 + R4(V_{cc})}\right) + V_{BE2} \quad \cdots(9)

\end{aligned}$$

40

ここで、式 (9) は、電流  $I_1$ 、 $I_2$  の電流レベル  $I$  が上記の式 (3) で与えられることを利用して得られている。

#### 【0035】

式 (9) に基づき、一実施形態では、N、R2、R3、R4 ( $V_{cc}$ ) 及び R5 ( $V_{cc}$ ) が、温度依存性が小さい又は全くない出力電圧  $V_{out}$  を生成するように調節される。

#### 【0036】

50

また、可変抵抗素子R4、R5の特性は、可変抵抗素子R4、R5を設けない場合のバンドギャップリファレンス回路100の出力電圧 $V_{out}$ の電源電圧 $V_{cc}$ に対する依存性に応じて、出力電圧 $V_{out}$ の電源電圧 $V_{cc}$ に対する依存性を低減するように選択される。

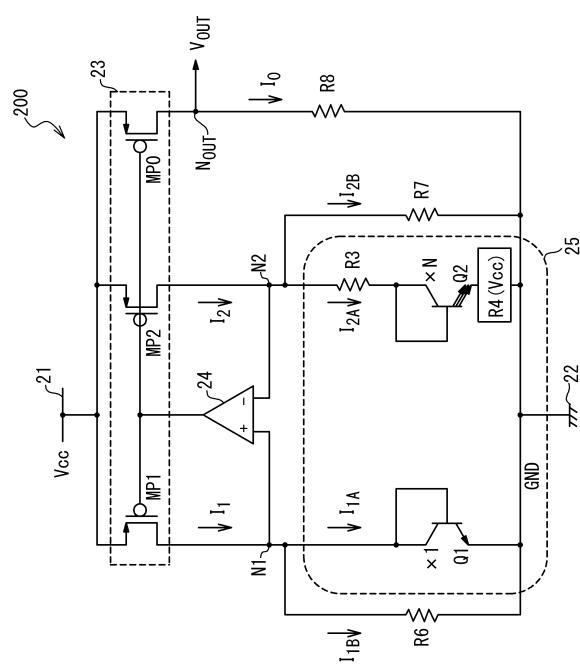

#### 【0037】

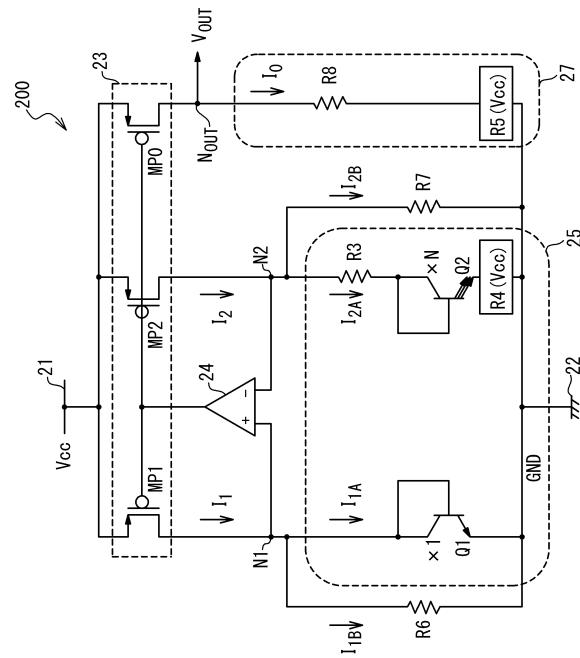

図6に示す一実施形態では、バンドギャップリファレンス回路200が、電源線21と、接地線22と、カレントミラー23と、演算増幅器24と、抵抗素子R3、R6、R7、R8と、可変抵抗素子R4と、バイポーラトランジスタQ1、Q2とを備えている。電源線21には電源電圧 $V_{cc}$ が供給され、接地線22は、接地されている。

#### 【0038】

カレントミラー23は、電流 $I_1$ 、 $I_2$ の電流レベルが同一であるように電流 $I_1$ 、 $I_2$ を出力する。加えて、カレントミラー23は、電流 $I_1$ 、 $I_2$ の電流レベルに比例する電流レベルを有する電流 $I_0$ を出力する。一実施形態では、カレントミラー23は、電流 $I_0$ の電流レベルが、電流 $I_1$ 、 $I_2$ の電流レベルと同じであるように電流 $I_0$ を出力してもよい。本実施形態では、カレントミラー23が、PMOSトランジスタMP0、MP1及びMP2を備えている。PMOSトランジスタMP0、MP1及びMP2は、ゲートが互いに接続され、更にソースが共通に電源線21に接続されている。PMOSトランジスタMP1のドレインは、ノードN1に接続され、PMOSトランジスタMP2のドレインは、ノードN2に接続されている。PMOSトランジスタMP0のドレインは、出力ノードNoutに接続されている。

#### 【0039】

演算増幅器24は、非反転入力がノードN1に接続されており、反転入力がノードN2に接続されており、出力がPMOSトランジスタMP1、MP2のゲートに接続されている。演算増幅器24は、電流 $I_1$ 、 $I_2$ 、 $I_0$ を制御する制御電圧をカレントミラー13のPMOSトランジスタMP1、MP2、MP0のゲートに出力する。演算増幅器14は、ノードN1、N2が同一の電位を有するようにPMOSトランジスタMP1、MP2のゲートの電位を制御する。ノードN1、N2は、このような演算増幅器24の動作により、仮想ショートされる。カレントミラー23及び演算増幅器24は、総合すると、ノードN1、N2を同一の電位に制御すると共に、ノードN1、N2に同一電流レベルの電流を供給する電流供給回路部として動作することになる。

#### 【0040】

図1に示したバンドギャップリファレンス回路100と同様に、本実施形態でも、バイポーラトランジスタQ1、Q2、抵抗素子R3及び可変抵抗素子R4が、PTAT電流生成回路部25として動作する。バイポーラトランジスタQ1は、ノードN1と接地線22の間に接続されている。抵抗素子R3、バイポーラトランジスタQ2及び可変抵抗素子R4は、ノードN1と接地線22の間に直列に接続されている。バイポーラトランジスタQ2のベース-エミッタ接合の面積は、バイポーラトランジスタQ1のベース-エミッタ接合の面積のN倍である。なお、抵抗素子R3、バイポーラトランジスタQ2及び可変抵抗素子R4が接続される順序は、順不同である。

#### 【0041】

抵抗素子R6は、ノードN1と接地線22の間に、バイポーラトランジスタQ1と並列に接続されており、抵抗素子R7は、ノードN2と接地線22の間に、抵抗素子R3、バイポーラトランジスタQ2及び可変抵抗素子R4と並列に接続されている。一実施形態では、抵抗素子R6、R7は、同一の抵抗を有するように設計される。

#### 【0042】

抵抗素子R8は、出力ノードNoutと接地線22の間に接続されている。抵抗素子R8は、出力ノードNoutに供給される電流 $I_0$ から出力電圧 $V_{out}$ を生成する電流-電圧変換回路部として機能する。

#### 【0043】

本実施形態のバンドギャップリファレンス回路200は、概略的には、下記の動作によつ

10

20

30

40

50

て温度依存性が小さい出力電圧  $V_{out}$  を生成する。バイポーラトランジスタ Q1 を流れる電流  $I_{1A}$  及び抵抗素子 R3、バイポーラトランジスタ Q2 及び可変抵抗素子 R4 を流れる電流  $I_{2A}$  は、いずれも、正の温度依存性を有する P T A T 電流である。一方、抵抗素子 R6 を流れる電流  $I_{1B}$  及び抵抗素子 R7 を流れる電流  $I_{2B}$  は、負の温度依存性を有する C T A T (complementary to absolute temperature) 電流である。電流  $I_1$  は、電流  $I_{1A}$  と電流  $I_{1B}$  の和電流であり、電流  $I_2$  は、電流  $I_{2A}$  と電流  $I_{2B}$  の和電流であるから、電流  $I_1$ 、 $I_2$  の温度依存性を小さくすることができる。よって、電流  $I_1$ 、 $I_2$  のミラーリングにより生成される電流  $I_0$  も温度依存性を小さくすることができる。出力電圧  $V_{out}$  は、電流  $I_0$  が抵抗素子 R8 を流れることで発生する電位差として生成されるので、出力電圧  $V_{out}$  の温度依存性も低減される。詳細には、バンドギャッププリファレンス回路 100 の出力電圧  $V_{out}$  は、以下のように得られる。

【0044】

ノード N2 に流れ込む電流  $I_2$  は、電流  $I_{2A}$  と電流  $I_{2B}$  の和電流であるから、下記式 (10) が成立する。

【数10】

10

$$I_2 = I_{2A} + I_{2B} \quad \cdots (10)$$

20

【0045】

ノード N1、N2 が仮想ショートされることから、ノード N2 の電位は、バイポーラトランジスタ Q1 のベース - エミッタ電圧  $V_{BE1}$  になり、よって、電流  $I_{2A}$ 、 $I_{2B}$  は、下記式 (11a)、(11b) で表される。

【数11】

30

$$I_{2A} = \frac{V_{BE1} - V_{BE2}}{R3 + R4(V_{CC})} \quad \cdots (11a)$$

$$I_{2B} = \frac{V_{BE1}}{R7} \quad \cdots (11b)$$

40

【0046】

ベース - エミッタ電圧  $V_{BE1}$ 、 $V_{BE2}$  を表す式 (1a)、(1b) と、式 (10)、(11a)、(11b) から、電流  $I_2$  は、下記式 (12) として表される：

【数12】

50

$$I_2 = \frac{Vt \cdot \ln(N)}{R3 + R4(Vcc)} + \frac{V_{BE1}}{R7} \quad \cdots(12)$$

【0047】

10

カレントミラー 23 が、電流  $I_2$  と同一の電流レベルを有するように電流  $I_3$  を出力する場合、出力電圧  $V_{out}$  は、例えば下記式(13)で表される：

【数13】

$$V_{out} = \left( \frac{Vt \cdot \ln(N)}{R3 + R4(Vcc)} + \frac{V_{BE1}}{R7} \right) \cdot R8 \quad \cdots(13)$$

20

【0048】

熱電圧  $V_t$  が温度に比例して増加する正の温度依存性を有する一方で、ベース - エミッタ電圧  $V_{BE1}$  が負の温度依存性を有しているから、式(13)からも理解されるように、 $N$ 、 $R2$ 、 $R3$ 、 $R4$  ( $Vcc$ ) 及び  $R7$  を調節することにより、出力電圧  $V_{out}$  の温度依存性を低減することができる。

【0049】

30

また、可変抵抗素子  $R4$  を設けない場合のバンドギャップリファレンス回路 200 の出力電圧  $V_{out}$  の電源電圧  $Vcc$  に対する依存性に応じて可変抵抗素子  $R4$  の特性を選択することで、出力電圧  $V_{out}$  の電源電圧  $Vcc$  に対する依存性を低減できる。

【0050】

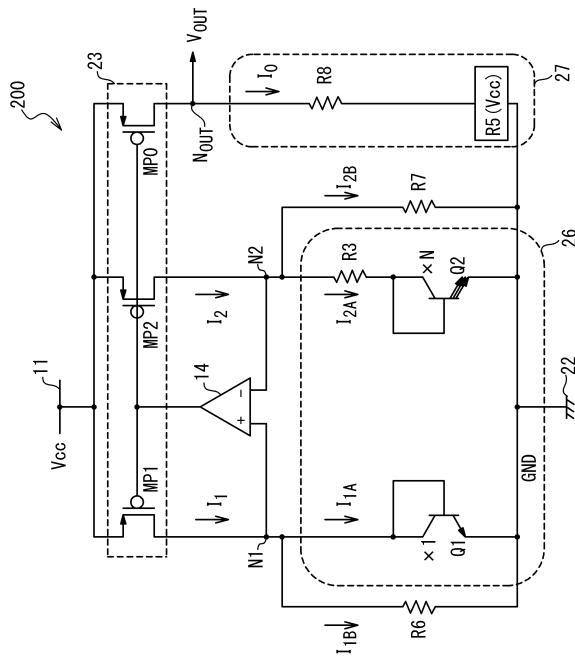

図 7 に示す実施形態では、バンドギャップリファレンス回路 200 が、図 6 に示された構成と類似した構成となっている。ただし、可変抵抗素子  $R4$  を含んでいない P T A T 電流生成回路部 26 が用いられると共に、出力ノード  $N_{out}$  と接地線 22 の間に抵抗素子  $R8$  と可変抵抗素子  $R5$  とが直列に接続された電流 - 電圧変換回路部 27 が接続される。

【0051】

図 7 に図示されているバンドギャップリファレンス回路 200 では、電流  $I_2$  は、例えば下記式(14)で表される。

【数14】

40

50

$$I_2 = \frac{Vt \cdot \ln(N)}{R3} + \frac{V_{BE1}}{R7} \quad \cdots (14)$$

10

## 【0052】

よって、出力電圧  $V_{out}$  は、例えば下記式(15)で表される。

## 【数15】

$$V_{out} = \left( \frac{Vt \cdot \ln(N)}{R3} + \frac{V_{BE1}}{R7} \right) \cdot (R8 + R5(Vcc)) \quad \cdots (15)$$

20

## 【0053】

式(15)からも理解されるように、N、R2、R3及びR7を適正に調節することにより、出力電圧  $V_{out}$  の温度依存性を低減することができる。

## 【0054】

また、可変抵抗素子R5を設けない場合のバンドギャップリファレンス回路200の出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性に応じて可変抵抗素子R5の特性を適切に選択することで、出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性を低減できる。

30

## 【0055】

図8に示す実施形態では、バンドギャップリファレンス回路200が、図6に示す構成と図7に示す構成の組み合わせとして構成される。図8の構成では、可変抵抗素子R4を含んでいるPTAT電流生成回路部25が用いられる。加えて、出力ノード  $N_{out}$  と接地線22の間に抵抗素子R8と可変抵抗素子R5とが直列に接続された電流-電圧変換回路部27が接続される。

## 【0056】

図8の構成では、出力電圧  $V_{out}$  は、例えば、下記式(16)で表される：

40

## 【数16】

$$V_{out} = \left( \frac{Vt \cdot \ln(N)}{R3 + R4(Vcc)} + \frac{V_{BE1}}{R7} \right) \cdot (R8 + R5(Vcc)) \quad \cdots (16)$$

50

**【 0 0 5 7 】**

式(16)に基づき、一実施形態では、N、R3、R4( $V_{ccc}$ )及びR7が、温度依存性が小さい又は全くない出力電圧 $V_{out}$ を生成するように調節される。

**【 0 0 5 8 】**

また、可変抵抗素子R4、R5の特性は、可変抵抗素子R4、R5を設けない場合のバンドギャップリファレンス回路200の出力電圧 $V_{out}$ の電源電圧 $V_{ccc}$ に対する依存性に応じて、出力電圧 $V_{out}$ の電源電圧 $V_{ccc}$ に対する依存性を低減するように調節される。

**【 0 0 5 9 】**

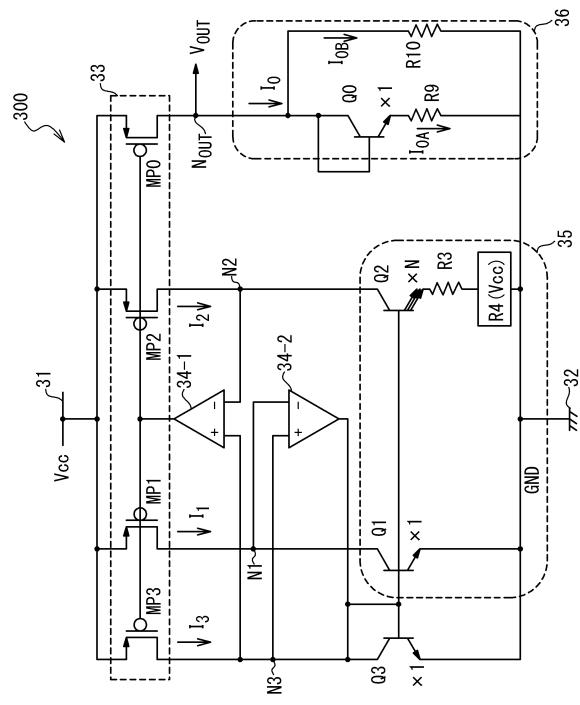

図9に示す一実施形態では、バンドギャップリファレンス回路300が、電源線31と、接地線32と、カレントミラー33と、演算増幅器34-1、34-2と、抵抗素子R3と、可変抵抗素子R4と、バイポーラトランジスタQ1、Q2、Q3と、電流-電圧変換回路部36とを備えている。電源線31には電源電圧 $V_{ccc}$ が供給され、接地線32は、接地されている。

10

**【 0 0 6 0 】**

カレントミラー33は、電流 $I_0$ 、 $I_1$ 、 $I_2$ 、 $I_3$ の電流レベルが同一であるように電流 $I_0$ 、 $I_1$ 、 $I_2$ 、 $I_3$ を出力する。本実施形態では、カレントミラー33が、PMOSトランジスタMP0、MP1、MP2及びMP3を備えている。PMOSトランジスタMP0、MP1、MP2及びMP3は、ゲートが互いに接続され、更にソースが共通に電源線31に接続されている。PMOSトランジスタMP1、MP2、MP3のドレインは、それぞれ、ノードN1、N2、N3に接続されている。PMOSトランジスタMP0のドレインは、出力ノード $N_{out}$ に接続されている。

20

**【 0 0 6 1 】**

バイポーラトランジスタQ1、Q2、Q3は、それぞれ、pn接合を有する第1、第2及び第3のpn接合素子として動作する。本実施形態では、バイポーラトランジスタQ1、Q2、Q3としてNPNトランジスタが用いられる。バイポーラトランジスタQ1、Q2、Q3のベースは、バイポーラトランジスタQ3のコレクタに共通に接続されている。バイポーラトランジスタQ1、Q2、Q3のコレクタは、それぞれ、ノードN1、N2、N3に接続されている。バイポーラトランジスタQ1、Q3のエミッタは、接地線32に接続されており、バイポーラトランジスタQ2のエミッタは、抵抗素子R3及び可変抵抗素子R4を介して接地線32に接続されている。このような接続により、電流 $I_1$ 、 $I_2$ 、 $I_3$ は、それぞれ、バイポーラトランジスタQ1、Q2、Q3のベース-エミッタ間のpn接合の順方向に流れることになる。

30

**【 0 0 6 2 】**

本実施形態では、バイポーラトランジスタQ1、Q3のベース-エミッタ接合の面積が同一であり、バイポーラトランジスタQ2のベース-エミッタ接合の面積は、バイポーラトランジスタQ1、Q3のベース-エミッタ接合の面積のN倍である。ここで、Nは、1より大きい数である。

**【 0 0 6 3 】**

演算増幅器34-1は、反転入力がノードN1に接続されており、非反転入力がノードN2に接続されており、出力がPMOSトランジスタMP0、MP1、MP2、MP3のゲートに接続されている。演算増幅器34-1は、電流 $I_1$ 、 $I_2$ を制御する制御電圧をカレントミラー33のPMOSトランジスタMP1、MP2のゲートに出力する。

40

**【 0 0 6 4 】**

演算増幅器34-2は、反転入力がノードN3に接続されており、非反転入力がノードN1に接続されており、出力がバイポーラトランジスタQ1、Q2、Q3のベースに接続されている。演算増幅器34-2は、電流 $I_1$ 、 $I_3$ を制御する制御電圧をバイポーラトランジスタQ1、Q2、Q3のベースに出力する。

**【 0 0 6 5 】**

演算増幅器34-1、34-2は、全体としては、ノードN1、N2、N3が同一の電位

50

を有するようにPMOSトランジスタMP1、MP2、MP3のゲートの電位及びバイポーラトランジスタQ1、Q2、Q3のベースの電位を制御することになる。ノードN1、N2、N3は、このような演算増幅器34-1、34-2の動作によって仮想ショートされる。カレントミラー33、演算増幅器34-1及び34-2は、総合すると、ノードN1、N2、N3を同一の電位に制御すると共に、ノードN1、N2、N3に同一電流レベルの電流を供給する電流供給回路部として動作することになる。

【0066】

電流・電圧変換回路部36は、カレントミラー33から受け取った電流 $I_0$ から出力電圧 $V_{out}$ を生成する。本実施形態では、電流・電圧変換回路部36は、ダイオード接続されたバイポーラトランジスタQ0と、抵抗素子R9、R10とを備えている。バイポーラトランジスタQ0のベース-エミッタ接合の面積は、バイポーラトランジスタQ1、Q3のベース-エミッタ接合の面積と同じである。バイポーラトランジスタQ0と抵抗素子R9とは、出力ノードNoutと接地線32の間に直列に接続されている。なお、バイポーラトランジスタQ0と抵抗素子R9の位置は、交換可能である。抵抗素子R10は、出力ノードNoutと接地線32の間に、バイポーラトランジスタQ0及び抵抗素子R9と並列に接続されている。

10

【0067】

本実施形態のバンドギャップリファレンス回路300は、概略的には、下記の原理により、温度依存性が小さい出力電圧 $V_{out}$ を生成可能である。バイポーラトランジスタQ1を流れる電流 $I_1$ 、バイポーラトランジスタQ2、抵抗素子R3及び可変抵抗素子R4を流れる電流 $I_2$ を流れる電流は、正の温度依存性を有するPTAT電流である。この意味で、バイポーラトランジスタQ1、Q2と抵抗素子R3と可変抵抗素子R4とを、総称して、PTAT電流生成回路部35と呼ぶことがある。

20

【0068】

電流・電圧変換回路部36に供給される電流 $I_0$ は、電流 $I_1$ 、 $I_2$ と同一の電流レベル $I$ を有しているから、電流 $I_0$ もPTAT電流である。電流・電圧変換回路部36は、電流 $I_0$ を、正の温度依存性を有する電流 $I_{0A}$ と温度依存性が小さい電流 $I_{0B}$ に分流し、電流 $I_{0B}$ が抵抗素子R10に流れることで発生する電圧を、出力電圧 $V_{out}$ として出力する。よって、バンドギャップリファレンス回路300は、出力電圧 $V_{out}$ の温度依存性を小さくすることができる。詳細には、バンドギャップリファレンス回路300は、以下のように動作して出力電圧 $V_{out}$ を生成する。

30

【0069】

本実施形態においては、電流 $I_1$ 、 $I_2$ 、 $I_0$ の電流レベル $I$ は、同一であり、下記式(17)で表される。

【数17】

$$I = \frac{Vt \cdot \ln(N)}{R3 + R4(Vcc)} \quad \dots (17)$$

40

【0070】

また、電流 $I_0$ は、電流 $I_1$ 、 $I_2$ と同一の電流レベル $I$ を有し、且つ、バイポーラトランジスタQ0及び抵抗素子R9を流れる電流 $I_{0A}$ と抵抗素子R10を流れる電流 $I_{0B}$ の和電流であるから、下記式(18)が成立する：

【数18】

50

$$I_0 = I = I_{0A} + I_{0B} \quad \cdots (18)$$

10

【0071】

また、バイポーラトランジスタ Q 0 のベース - エミッタ電圧  $V_{BE0}$ 、抵抗素子 R 9 及び R 10 の電圧降下について、下記式 (19) が成立する：

【数19】

$$V_{BE0} + I_{0A} \cdot R9 = I_{0B} \cdot R10 \quad \cdots (19)$$

20

【0072】

式 (17) ~ (19) から、電流  $I_{0B}$  は、下記式 (20) により表される：

【数20】

$$\begin{aligned} I_{0B} &= \frac{I \cdot R9 + V_{BE0}}{R9 + R10} \\ &= \frac{1}{R9 + R10} \cdot \left( \frac{R9 \cdot Vt \cdot \ln(N)}{R3 + R4(Vcc)} + V_{BE0} \right) \quad \cdots (20) \end{aligned}$$

30

【0073】

出力電圧  $V_{out}$  は、例えば下記式 (21) により表される：

【数21】

40

50

$$\begin{aligned}

V_{out} &= I_{0B} \cdot R10 \\

&= \frac{R10}{R9 + R10} \cdot \left( \frac{R9 \cdot Vt \cdot \ln(N)}{R3 + R4(Vcc)} + V_{BE0} \right) \quad \cdots(21)

\end{aligned}$$

10

## 【0074】

熱電圧  $V_t$  が温度に比例して増加する正の温度依存性を有する一方で、ベース - エミッタ電圧  $V_{BE0}$  が負の温度依存性を有しているから、R3、R4 (Vcc) 及び R9 を適正に調節することにより、出力電圧  $V_{out}$  の温度依存性を低減することができる。

## 【0075】

加えて、式(21)からも理解されるように、可変抵抗素子 R4 を設けない場合のバンドギャップリファレンス回路 300 の出力電圧  $V_{out}$  の電源電圧  $Vcc$  に対する依存性に応じて可変抵抗素子 R4 の特性を適切に選択することで、出力電圧  $V_{out}$  の電源電圧  $Vcc$  に対する依存性を低減できる。

20

## 【0076】

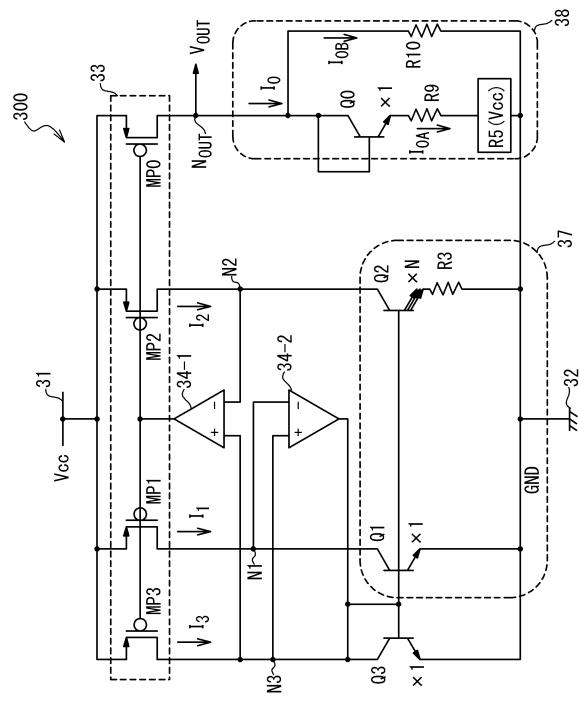

図 10 に示す実施形態では、バンドギャップリファレンス回路 300 が、図 9 に示された構成と類似した構成となっている。ただし、可変抵抗素子 R4 を含んでいない P T A T 電流生成回路部 37 が用いられると共に、バイポーラトランジスタ Q0 と抵抗素子 R9 とに可変抵抗素子 R5 が直列に接続された電流 - 電圧変換回路 38 が用いられる。なお、バイポーラトランジスタ Q0 と抵抗素子 R9 と可変抵抗素子 R5 が接続される順序は、順不同である。

## 【0077】

本実施形態においては、電流  $I_1$ 、 $I_2$ 、 $I_0$  の電流レベル  $I$  は、同一であり、下記式(22)で表される。

30

## 【数22】

$$I = \frac{Vt \cdot \ln(N)}{R3} \quad \cdots(22)$$

40

## 【0078】

また、バイポーラトランジスタ Q0 のベース - エミッタ電圧  $V_{BE0}$ 、抵抗素子 R9 及び R10 の電圧降下について、下記式(23)が成立する：

## 【数23】

$$V_{BE0} + I_{0A} \cdot (R9 + R5(Vcc)) = I_{0B} \cdot R10 \quad \cdots(23)$$

50

## 【0079】

式(18)、(22)、(23)から、電流  $I_{0B}$  は、下記式(24)により表される：

## 【数24】

$$I_{0B} = \frac{I \cdot (R9 + R5(Vcc)) + V_{BE0}}{R9 + R5(Vcc) + R10}$$

$$= \frac{1}{R9 + R10 + R5(Vcc)} \cdot \left( \frac{(R9 + R5(Vcc)) \cdot Vt \cdot \ln(N)}{R3} + V_{BE0} \right) \quad \cdots(24)$$

10

## 【0080】

出力電圧  $V_{out}$  は、例えば下記式(25)により表される：

## 【数25】

$$V_{out} = I_{0B} \cdot R10$$

$$= \frac{R10}{R9 + R10 + R5(Vcc)} \cdot \left( \frac{(R9 + R5(Vcc)) \cdot Vt \cdot \ln(N)}{R3} + V_{BE0} \right) \quad \cdots(25)$$

20

## 【0081】

熱電圧  $V_t$  が温度に比例して増加する正の温度依存性を有する一方で、ベース - エミッタ電圧  $V_{BE1}$  が負の温度依存性を有しているから、式(25)からも理解されるように、 $N$ 、 $R3$ 、 $R9$  及び  $R5$  ( $Vcc$ ) を適正に調節することにより、出力電圧  $V_{out}$  の温度依存性を低減することができる。

## 【0082】

また、可変抵抗素子  $R5$  を設けない場合のバンドギャップリファレンス回路300の出力電圧  $V_{out}$  の電源電圧  $Vcc$  に対する依存性に応じて可変抵抗素子  $R5$  の特性を適切に選択することで、出力電圧  $V_{out}$  の電源電圧  $Vcc$  に対する依存性を低減できる。

30

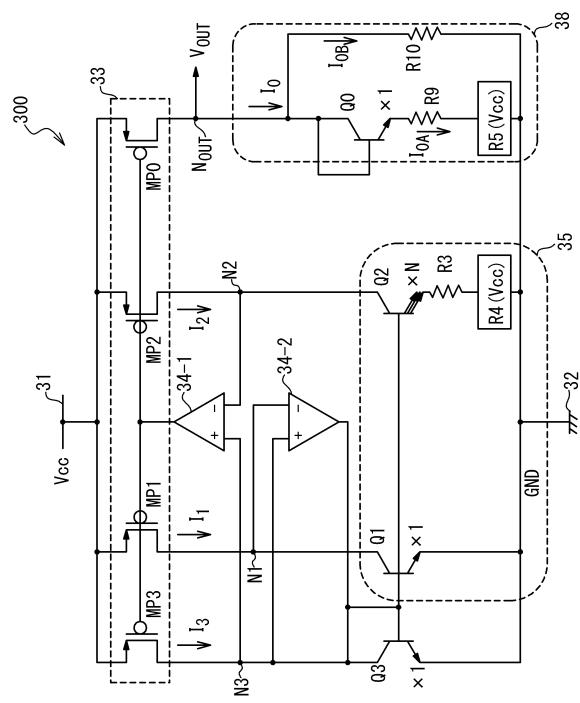

## 【0083】

図11に示す実施形態では、バンドギャップリファレンス回路300が、図9に示す構成と図10に示す構成の組み合わせとして構成される。図11の構成では、可変抵抗素子  $R4$  を含んでいるPTAT電流生成回路部35が用いられる。加えて、バイポーラトランジスタ  $Q0$  と抵抗素子  $R9$  とに可変抵抗素子  $R5$  が直列に接続された電流 - 電圧変換回路38が用いられる。

## 【0084】

図11の構成では、出力電圧  $V_{out}$  は、例えば下記式(26)により表される：

## 【数26】

$$V_{out} = \frac{R10}{R9 + R10 + R5(Vcc)} \cdot \left( \frac{(R9 + R5(Vcc)) \cdot Vt \cdot \ln(N)}{R3 + R4(Vcc)} + V_{BE0} \right) \quad \cdots(26)$$

40

50

## 【0085】

式(26)に基づき、一実施形態では、N、R3、R4(Vcc)、R5(Vcc)及びR9が、温度依存性が小さい又は全くない出力電圧Voutを生成するように調節される。

## 【0086】

また、可変抵抗素子R4、R5の特性は、可変抵抗素子R4、R5を設けない場合のバンドギャップリファレンス回路300の出力電圧Voutの電源電圧Vccに対する依存性に応じて、出力電圧Voutの電源電圧Vccに対する依存性を低減するように選択される。

## 【0087】

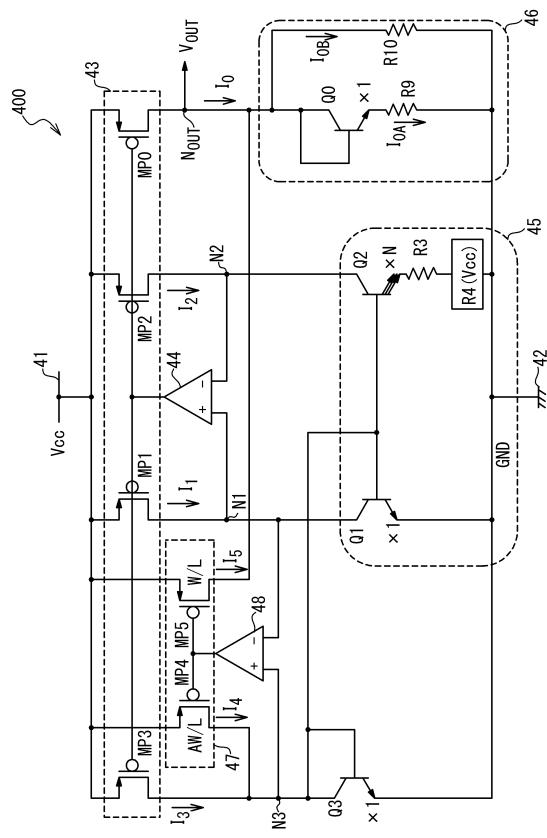

図12に示す一実施形態では、バンドギャップリファレンス回路400が、電源線41と、接地線42と、カレントミラー43と、演算増幅器44と、抵抗素子R3と、可変抵抗素子R4と、バイポーラトランジスタQ1、Q2、Q3と、電流-電圧変換回路部46と、カレントミラー47と、演算増幅器48とを備えている。電源線41には電源電圧Vccが供給され、接地線42は、接地されている。

10

## 【0088】

カレントミラー43は、電流I0、I1、I2、I3の電流レベルが同一であるように電流I0、I1、I2、I3を出力する。本実施形態では、カレントミラー43が、PMOSトランジスタMP0、MP1、MP2、MP3を備えている。PMOSトランジスタMP0、MP1、MP2、MP3は、ゲートが互いに接続され、更にソースが共通に電源線41に接続されている。PMOSトランジスタMP1、MP2、MP3のドレインは、それぞれ、ノードN1、N2、N3に接続されている。PMOSトランジスタMP0のドレインは、出力ノードNoutに接続されている。

20

## 【0089】

バイポーラトランジスタQ1、Q2、Q3は、それぞれ、pn接合を有する第1、第2及び第3のpn接合素子として動作する。本実施形態では、バイポーラトランジスタQ1、Q2、Q3としてNPNトランジスタが用いられる。バイポーラトランジスタQ1、Q2、Q3のベースは、バイポーラトランジスタQ3のコレクタに共通に接続されている。バイポーラトランジスタQ1、Q2、Q3のコレクタは、それぞれ、ノードN1、N2、N3に接続されている。バイポーラトランジスタQ1、Q3のエミッタは、接地線42に接続されており、バイポーラトランジスタQ2のエミッタは、抵抗素子R3及び可変抵抗素子R4を介して接地線42に接続されている。このような接続により、電流I1、I2、I3は、それぞれ、バイポーラトランジスタQ1、Q2、Q3のベース-エミッタ間のpn接合の順方向に流れることになる。

30

## 【0090】

本実施形態では、バイポーラトランジスタQ1、Q3のベース-エミッタ接合の面積が同一であり、バイポーラトランジスタQ2のベース-エミッタ接合の面積は、バイポーラトランジスタQ1、Q3のベース-エミッタ接合の面積のN倍である。ここで、Nは、1より大きい数である。

## 【0091】

演算増幅器44は、非反転入力がノードN1に接続されており、反転入力がノードN2に接続されており、出力がPMOSトランジスタMP0、MP1、MP2、MP3のゲートに接続されている。演算増幅器44は、電流I0、I1、I2、I3を制御する制御電圧をカレントミラー13のPMOSトランジスタMP0、MP1、MP2、MP3のゲートに出力する。演算増幅器44は、ノードN1、N2が同一の電位を有するようにPMOSトランジスタMP0、MP1、MP2及びMP3のゲートの電位を制御する。ノードN1、N2は、このような演算増幅器44の動作によって仮想ショートされる。カレントミラー43及び演算増幅器44は、総合すると、ノードN1、N2を同一の電位に制御すると共に、ノードN1、N2に同一電流レベルの電流を供給する電流供給回路部として動作することになる。

40

## 【0092】

50

電流 - 電圧変換回路部 4 6 は、カレントミラー 4 3 から受け取った電流  $I_0$  に応じて出力電圧  $V_{out}$  を生成する。本実施形態では、電流 - 電圧変換回路部 4 6 は、ダイオード接続されたバイポーラトランジスタ  $Q_0$  と、抵抗素子  $R_9$ 、 $R_{10}$  とを備えている。バイポーラトランジスタ  $Q_0$  のベース - エミッタ接合の面積は、バイポーラトランジスタ  $Q_1$ 、 $Q_3$  のベース - エミッタ接合の面積と同じである。バイポーラトランジスタ  $Q_0$  と抵抗素子  $R_9$  とは、出力ノード  $N_{out}$  と接地線 4 2 の間に直列に接続されている。なお、バイポーラトランジスタ  $Q_0$  と抵抗素子  $R_9$  の位置は、交換可能である。抵抗素子  $R_{10}$  は、出力ノード  $N_{out}$  と接地線 4 2 の間に、バイポーラトランジスタ  $Q_0$  及び抵抗素子  $R_9$  と並列に接続されている。

【 0 0 9 3 】

カレントミラー 4 7 は、電流  $I_4$  をノード  $N_3$  に出力すると共に、電流  $I_5$  を電流 - 電圧変換回路部 4 6 に出力する。電流 - 電圧変換回路部 4 6 には、カレントミラー 4 3 からの電流  $I_0$  とカレントミラー 4 7 からの電流  $I_5$  の和電流が供給されることになる。カレントミラー 4 7 のミラー比は、 $A : 1$  であり、電流  $I_5$  は、電流  $I_4$  の  $1 / A$  倍である。本実施形態では、カレントミラー 4 7 が、PMOSトランジスタ  $M_P 4$ 、 $M_P 5$  を備えている。 $PMOS$ トランジスタ  $M_P 4$ 、 $M_P 5$  は、ゲートが互いに接続され、更にソースが共通に電源線 4 1 に接続されている。 $PMOS$ トランジスタ  $M_P 4$  のドレインは、ノード  $N_3$  に接続されており、 $PMOS$ トランジスタ  $M_P 5$  のドレインは、電流 - 電圧変換回路部 4 6 に接続されている。一実施形態では、 $PMOS$ トランジスタ  $M_P 4$ 、 $M_P 5$  は、同一のゲート長  $L$  を有しており、 $PMOS$ トランジスタ  $M_P 4$  のゲート幅  $W_{MP 4}$  が  $PMOS$ トランジスタ  $M_P 5$  のゲート幅  $W_{MP 5}$  の  $A$  倍であるように設計される。

【 0 0 9 4 】

演算増幅器 4 8 は、電流  $I_4$ 、 $I_5$  を制御する制御電圧をカレントミラー 4 7 の  $PMOS$ トランジスタ  $M_P 4$ 、 $M_P 5$  のゲートに出力する。演算増幅器 4 8 は、ノード  $N_2$ 、 $N_3$  が同一の電位を有するように  $PMOS$ トランジスタ  $M_P 4$  及び  $M_P 5$  のゲートの電位を制御する。ノード  $N_2$ 、 $N_3$  は、演算増幅器 4 8 により仮想ショートされる。

【 0 0 9 5 】

本実施形態のバンドギャップリファレンス回路 4 0 0 は、下記のような動作により出力電圧  $V_{out}$  を出力する。

【 0 0 9 6 】

電流  $I_1$ 、 $I_2$ 、 $I_3$  は、コレクタ電流としてバイポーラトランジスタ  $Q_1$ 、 $Q_2$ 、 $Q_3$  に供給される一方で、カレントミラー 4 3 により電流  $I_1$ 、 $I_2$ 、 $I_3$  が、同一の電流レベルに制御されるから、カレントミラー 4 7 からノード  $N_3$  に供給される電流  $I_4$  は、バイポーラトランジスタ  $Q_1$ 、 $Q_2$ 、 $Q_3$  のベース電流の和電流である。よって、カレントミラー 4 7 から電流 - 電圧変換回路部 4 6 に供給される電流  $I_5$  は、バイポーラトランジスタ  $Q_1$ 、 $Q_2$ 、 $Q_3$  のベース電流に依存する。

【 0 0 9 7 】

一般に、エミッタ接地のバイポーラトランジスタでは、ベース電流がコレクタ電流と比較すると非常に小さいから、バイポーラトランジスタ  $Q_1$ 、 $Q_2$ 、 $Q_3$  のベース電流の和電流である電流  $I_4$  は、バイポーラトランジスタ  $Q_1$ 、 $Q_2$ 、 $Q_3$  のコレクタ電流である電流  $I_1$ 、 $I_2$ 、 $I_3$  に対して非常に小さいと考えてよい。ここで、電流  $I_0$  の電流レベルは、電流  $I_1$ 、 $I_2$ 、 $I_3$  と同一であり、電流  $I_5$  は電流  $I_4$  の  $1 / A$  倍の電流レベルを有するから、電流  $I_5$  は、電流  $I_0$  に対して非常に小さいと考えてよい。

【 0 0 9 8 】

この場合、バンドギャップリファレンス回路 4 0 0 の出力電圧  $V_{out}$  は、第 1 近似としては、図 9 に示したバンドギャップリファレンス回路 3 0 0 と同様に、例えば上記の式 (21) で表される。よって、 $N$ 、 $R_3$ 、 $R_4$  ( $V_{cc}$ ) 及び  $R_9$  を適正に調節することによって出力電圧  $V_{out}$  の温度依存性を低減することができる。加えて、可変抵抗素子  $R_4$  を設けない場合のバンドギャップリファレンス回路 4 0 0 の出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性に応じて可変抵抗素子  $R_4$  の特性を選択することによって出力電

10

20

30

40

50

圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性を低減できる。

【 0 0 9 9 】

カレントミラー 4 7 から電流 - 電圧変換回路部 4 6 に供給される電流  $I_5$  は、出力電圧  $V_{out}$  の非線形的な温度依存性を補償するために用いられる。式 (21) からも理解されるように、出力電圧  $V_{out}$  はベース - エミッタ電圧  $V_{BE0}$  に依存する。バイポーラトランジスタのベース - エミッタ電圧は、一般に、負の非線形的な温度依存性を有していることが知られている。一方で、熱電圧  $V_t$  は、絶対温度  $T$  に比例し、線形的な温度依存性を有している。よって、電流  $I_0$  のみを電流 - 電圧変換回路部 4 6 に供給する場合には、出力電圧  $V_{out}$  の非線形的な温度依存性は、完全には解消されない。一方で、電流  $I_5$  は、バイポーラトランジスタ  $Q_1$ 、 $Q_2$ 、 $Q_3$  のベース電流に比例する電流レベルを有しており、よって、非線形的な温度依存性を有している。本実施形態では、電流  $I_0$  に加えて電流  $I_5$  を電流 - 電圧変換回路部 4 6 に供給することで、ベース - エミッタ電圧  $V_{BE0}$  の非線形的な温度依存性を補償し、出力電圧  $V_{out}$  の温度依存性をより低減することができる。

10

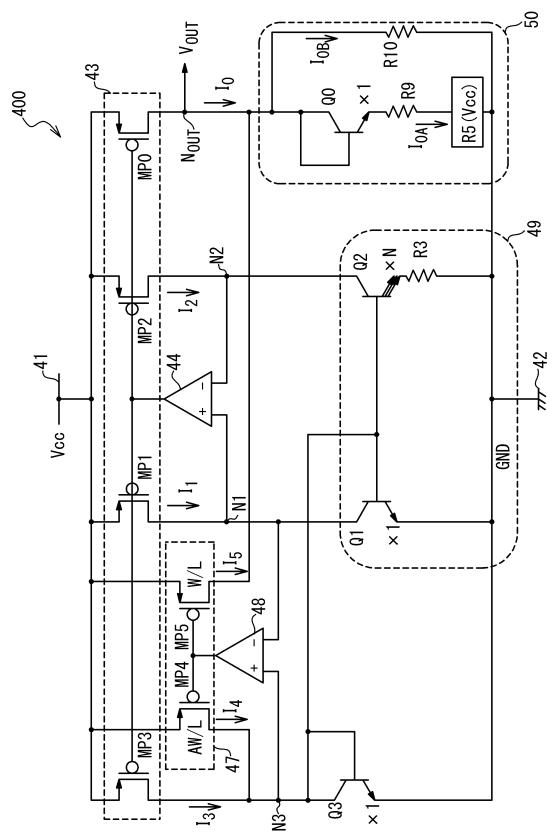

【 0 1 0 0 】

図 13 に示す一実施形態では、バンドギャップリファレンス回路 400 が、図 12 に示された構成と類似した構成となっている。ただし、可変抵抗素子  $R_4$  を含んでいない PTA T 電流生成回路部 49 が用いられると共に、バイポーラトランジスタ  $Q_0$  と抵抗素子  $R_9$  とに可変抵抗素子  $R_5$  が直列に接続された電流 - 電圧変換回路 50 が用いられる。なお、バイポーラトランジスタ  $Q_0$  と抵抗素子  $R_9$  と可変抵抗素子  $R_5$  が接続される順序は、順不同である。

20

【 0 1 0 1 】

図 13 に示すバンドギャップリファレンス回路 400 についても、図 12 に示すバンドギャップリファレンス回路 400 と同様の議論が成立する。図 13 に示すバンドギャップリファレンス回路 400 の出力電圧  $V_{out}$  は、第 1 近似としては、図 10 に示したバンドギャップリファレンス回路 300 と同様に、例えば上記の式 (25) で表される。よって、 $N$ 、 $R_3$ 、 $R_9$  及び  $R_5$  ( $V_{cc}$ ) を適正に調節することによって出力電圧  $V_{out}$  の温度依存性を低減することができる。また、可変抵抗素子  $R_5$  を設けない場合のバンドギャップリファレンス回路 400 の出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性に応じて可変抵抗素子  $R_5$  の特性を選択することで、出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性を低減できる。

30

【 0 1 0 2 】

図 14 に示す一実施形態では、バンドギャップリファレンス回路 400 が、図 12 に示す構成と図 13 に示す構成の組み合わせとして構成される。図 14 の構成では、可変抵抗素子  $R_4$  を含んでいる PTA T 電流生成回路部 45 が用いられる。加えて、バイポーラトランジスタ  $Q_0$  と抵抗素子  $R_9$  とに可変抵抗素子  $R_5$  が直列に接続された電流 - 電圧変換回路 50 が用いられる。

【 0 1 0 3 】

図 14 に示すバンドギャップリファレンス回路 400 についても、図 12 及び図 13 に示すバンドギャップリファレンス回路 400 と同様の議論が成立する。図 14 に示すバンドギャップリファレンス回路 400 の出力電圧  $V_{out}$  は、第 1 近似としては、図 11 に示したバンドギャップリファレンス回路 300 と同様に、例えば上記の式 (26) で表される。式 (26) に基づき、一実施形態では、 $N$ 、 $R_3$ 、 $R_4$  ( $V_{cc}$ )、 $R_5$  ( $V_{cc}$ ) 及び  $R_9$  が、温度依存性が小さい又は全くない出力電圧  $V_{out}$  を生成するように調節される。また、可変抵抗素子  $R_4$ 、 $R_5$  の特性は、可変抵抗素子  $R_4$ 、 $R_5$  を設けない場合のバンドギャップリファレンス回路 300 の出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性に応じて、出力電圧  $V_{out}$  の電源電圧  $V_{cc}$  に対する依存性を低減するように選択される。

40

【 0 1 0 4 】

以上には、本開示の様々な実施形態が具体的に記載されているが、本開示に記載された技

50

術は、様々な変更と共に実施され得る。

【符号の説明】

【0105】

100、200、300、400：バンドギャップリファレンス回路

11：電源線

12：接地線

13：カレントミラー

14：演算増幅器

15、16：P T A T 電流生成回路部

21：電源線

22：接地線

23：カレントミラー

24：演算増幅器

25、26：P T A T 電流生成回路部

27：電流 - 電圧変換回路部

31：電源線

32：接地線

33：カレントミラー

34-1、34-2：演算増幅器

35、37：P T A T 電流生成回路部

36、38：電流 - 電圧変換回路部

41：電源線

42：接地線

43：カレントミラー

44：演算増幅器

45、49：P T A T 電流生成回路部

46、50：電流 - 電圧変換回路部

47：カレントミラー

48：演算増幅器

M N 1：N M O S トランジスタ

M P 0 ~ M P 5：P M O S トランジスタ

N 1 ~ N 3：ノード

N o u t：出力ノード

Q 0 ~ Q 3：バイポーラトランジスタ

R 1 ~ R 3、R 6 ~ R 1 0：抵抗素子

R 4、R 5：可変抵抗素子

10

20

30

40

50

【図面】

【図 1】

【図 5】

【図 6】

10

20

【図 7】

【図 8】

30

40

50

【図 9】

【図 10】

10

20

【図 11】

【図 12】

30

40

50

【図 1 3】

【図 1 4】

10

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開2014-086000 (JP, A)

特開2013-054471 (JP, A)

特開2009-217809 (JP, A)

特開2013-058155 (JP, A)

特開2012-243054 (JP, A)

米国特許出願公開第2005/0110476 (US, A1)

特開2007-192718 (JP, A)

特開2000-267749 (JP, A)

特開2010-073133 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

- G 05 F 3 / 02

G 05 F 1 / 56