(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4178225号

(P4178225)

(45) 発行日 平成20年11月12日(2008.11.12)

(24) 登録日 平成20年9月5日(2008.9.5)

(51) Int.Cl.

F 1

G 11 C 11/407 (2006.01)

G 11 C 11/34 362 S

G 11 C 11/4076 (2006.01)

G 11 C 11/34 354 C

請求項の数 6 (全 14 頁)

(21) 出願番号 特願平10-184483

(22) 出願日 平成10年6月30日(1998.6.30)

(65) 公開番号 特開2000-21165(P2000-21165A)

(43) 公開日 平成12年1月21日(2000.1.21)

審査請求日 平成16年1月16日(2004.1.16)

(73) 特許権者 308014341

富士通マイクロエレクトロニクス株式会社

東京都新宿区西新宿二丁目7番1号

(74) 代理人 100094525

弁理士 土井 健二

(74) 代理人 100094514

弁理士 林 恒徳

(72) 発明者 矢田 雅大

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 富田 浩由

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 園田 康弘

最終頁に続く

(54) 【発明の名称】集積回路装置

## (57) 【特許請求の範囲】

## 【請求項 1】

外部クロック信号とクロックイネーブル信号とが供給され、前記外部クロック信号と所定の位相関係を有する内部クロック信号を内部回路に供給する集積回路装置において、

前記外部クロックを入力して入力クロック信号を出力する入力バッファと、

前記入力クロック信号と所定の位相関係を有する遅延クロック信号を生成する D L L 回路と、

前記遅延クロック信号に応答して前記クロックイネーブル信号を取り込んで、クロック出力制御信号を生成するクロックイネーブルタイミング制御回路と、

前記クロック出力制御信号に応答して、前記遅延クロック信号を前記内部クロック信号として前記内部回路に供給又は停止するゲート回路と、

前記クロックイネーブル信号とアクティブコマンドとに基づいて活性化信号を生成するパワーダウン制御回路とを有し、

前記アクティブコマンドが供給され且つ前記クロックイネーブル信号が非活性状態になる第1の低消費電力モード時には、前記活性化信号に基づいて前記入力バッファの活性化状態を維持して前記D L L回路の活性化状態を維持し、前記アクティブコマンドが供給されず且つ前記クロックイネーブル信号が非活性状態になる第2の低消費電力モード時には、前記活性化信号に基づいて前記入力バッファを非活性状態にし、

前記第1の低消費電力モードから通常モードに移行する時には前記ゲート回路は前記クロック出力制御信号に応答して前記内部回路への前記遅延クロック信号の供給を開始し、

10

20

通常モードから前記第1の低消費電力モードに移行する時には、前記ゲート回路は前記クロック出力制御信号に応答して前記内部回路への前記遅延クロック信号の供給を停止することを特徴とする集積回路装置。

#### 【請求項2】

外部クロック信号とクロックイネーブル信号とが供給され、前記外部クロック信号と所定の位相関係を有する内部クロック信号を内部回路に供給する集積回路装置において、

前記外部クロックを入力して入力クロック信号を出力する入力バッファと、

前記外部クロック信号と所定の位相関係を有する遅延クロック信号を生成するD L L回路と、

前記クロックイネーブル信号を、前記遅延クロック信号に応答して取り込んで、クロック出力制御信号を生成する第1の制御回路と、

前記クロックイネーブル信号とアクティブコマンドとに基づいて前記入力バッファの活性化信号を生成する第2の制御回路と、

前記クロック出力制御信号に応答して、前記遅延クロック信号を前記内部クロック信号として前記内部回路に供給開始又は供給停止するゲート回路とを有し、

通常モード時には前記ゲート回路は前記内部回路へ前記遅延クロック信号を供給し、アクティブパワーダウンモード時には前記活性化信号に基づいて前記入力バッファの活性化状態を保つことで前記D L L回路を活性状態に保つと共に、前記ゲート回路が前記クロック出力制御信号に基づいて前記内部回路への前記遅延クロック信号の供給を停止することを特徴とする集積回路装置。

10

20

#### 【請求項3】

請求項2において、前記第1の制御回路は、前記クロックイネーブル信号を、前記遅延クロック信号の第1のエッジのタイミングで取り込み、前記遅延クロック信号の第1とは異なる第2のエッジのタイミングで前記クロック出力制御信号を出力することを特徴とする集積回路装置。

#### 【請求項4】

請求項2において、前記第1の制御回路は、前記クロックイネーブル信号を、前記遅延クロック信号の第1のエッジのタイミングで取り込む第1のラッチ回路と、前記第1のラッチ回路の出力信号を、前記遅延クロック信号の第1とは異なる第2のエッジのタイミングで取り込み、前記クロック出力制御信号を生成する第2のラッチ回路とを有することを特徴とする集積回路装置。

30

#### 【請求項5】

外部クロック信号とクロックイネーブル信号とが供給され、前記外部クロック信号と所定の位相関係を有する内部クロック信号を内部回路に供給する集積回路装置において、

前記外部クロック信号を入力するクロック用入力バッファと、

前記クロック用入力バッファからのクロック信号を供給され、前記外部クロック信号と所定の位相関係を有する遅延クロック信号を生成するD L L回路と、

前記遅延クロック信号に応答して前記クロックイネーブル信号を取り込んで、クロック出力制御信号を生成するクロックイネーブルタイミング制御回路と、

前記クロックイネーブル信号とアクティブコマンドとに基づいて活性化信号を生成するパワーダウン制御回路と、

前記アクティブコマンドが供給され且つ前記クロックイネーブル信号が非活性状態になる第1のパワーダウンモードに移行する時に、前記クロック出力制御信号に応答して、前記遅延クロック信号を前記内部クロック信号として前記内部回路に供給することを停止し、前記第1のパワーダウンモードから復帰する時に前記クロック出力制御信号に応答して前記供給することを開始するゲート回路とを有し、

前記第1のパワーダウンモード時に、前記クロック入力バッファを活性状態にして前記D L L回路を活性状態に維持し、

前記アクティブコマンドが供給されず且つ前記クロックイネーブル信号が非活性状態になる第2のパワーダウンモード時に、前記活性化信号に応答して、前記クロック用入力バ

40

50

ツファを非活性状態にして前記 D L L 回路を停止することを特徴とする集積回路装置。

**【請求項 6】**

外部クロック信号とクロックイネーブル信号とが供給され、前記外部クロック信号と所定の位相関係を有する内部クロック信号を内部回路に供給する集積回路装置において、

前記外部クロック信号を入力するクロック用入力バッファと、

前記クロック用入力バッファからのクロック信号を供給され、前記外部クロック信号と所定の位相関係を有する遅延クロック信号を生成する D L L 回路と、

前記アクティブコマンドが供給され且つ前記クロックイネーブル信号が非活性状態になる第 1 のパワーダウンモードに移行する時に、前記クロックイネーブル信号の前記非活性状態に従い且つ前記遅延クロック信号に応答して、前記遅延クロック信号を前記内部クロック信号として前記内部回路に供給することを停止し、前記第 1 のパワーダウンモードから復帰する時に前記クロックイネーブル信号の前記活性化状態に従い且つ前記遅延クロック信号に応答して前記供給することを開始するゲート回路と、

前記アクティブコマンドが供給されず且つ前記クロックイネーブル信号が非活性状態になる第 2 のパワーダウンモード時に、前記クロックイネーブル信号の前記非活性状態に応答して、前記クロック用入力バッファを非活性状態にするパワーダウン制御回路とを有することを特徴とする集積回路装置。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、供給されるクロック信号と所定の位相関係を有する内部クロック信号を出力する回路を有する集積回路装置に関し、低消費電力モードから通常モードへの復帰動作を高速化することができる内部クロック出力回路を有する集積回路装置に関する。

**【0002】**

**【従来の技術】**

クロック同期型のダイナミック・ランダム・アクセス・メモリ (D R A M) としてシンクロナス D R A M ( S D R A M ) が注目されている。 S D R A M は、システム側から与えられる外部クロック信号に同期してアドレス、データ、コマンド等の信号が供給され、その外部クロック信号に同期して読み出しデータ信号を出力するもので高速動作が可能である。

**【0003】**

S D R A M の高速化に伴い、外部クロック信号を内部で取り込み生成させた内部クロック信号は、外部クロック信号の位相との間にずれを生じるため、入力アドレス、データ、コマンド等の信号や出力データ信号のストローブ信号として使用できない場合がある。

**【0004】**

この位相ずれを補償するため、ディレー・ロックド・ループ ( D e l a y   L o c k e d   L o o p , 以下単に D L L ) 回路等により、外部クロック信号に位相同期した或いは外部クロック信号の位相から所定の位相差を有する内部クロック信号を生成し、その内部クロック信号のタイミングで入力アドレス信号等を取り込み、出力データ信号を出力されることが行われる。

**【0005】**

一方、クロック信号の高速化は S D R A M の書き込みや読み出し等の頻度を高くし、 S D R A M の消費電力の増大を招いている。そこで、アクセスが行われない場合に S D R A M の内部動作を停止させる低消費電力モードを設け、低消費電力モード時は、クロックイネーブル信号を非活性レベル ( L レベル ) にすることにより、入力バッファが外部クロック信号を取り込むことを停止させ、不要な内部動作を停止させている。

**【0006】**

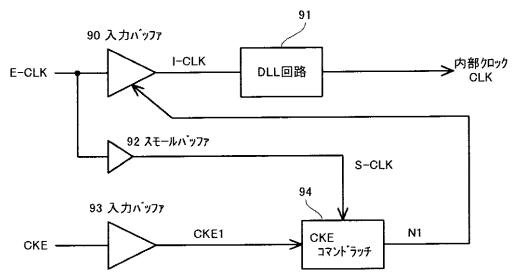

図 7 は、 S D R A M 等に設けられた従来の内部クロック出力回路の構成図である。外部クロック信号 E - C L K は入力バッファ 90 に入力され、波形整形されてクロック信号 I - C L K となる。クロック信号 I - C L K と外部クロック信号 E - C L K との間には、入力

10

20

30

40

50

バッファ90の遅延時間に相当する位相ずれが生じる。

**【0007】**

クロック信号I-CLKはDLL回路91に入力される。 DLL回路91は、外部クロック信号E-CLKと位相同期した内部クロック信号CLKを、ストローブ信号として図示しないアドレスバッファ等に供給する。また、外部クロック信号E-CLKは、スマートバッファ92にも入力される。スマートバッファ92は、CKEコマンドラッチ回路94のデータ取り込み信号となるクロック信号S-CLKを出力する。

**【0008】**

一方、クロックイネーブル信号CKEは、外部クロック信号E-CLKを取り込むか否かを制御する信号であり、入力バッファ93に入力されてクロックイネーブル信号CKE1となりCKEコマンドラッチ回路94に出力される。CKEコマンドラッチ回路94は、クロックイネーブル信号CKE1をクロック信号S-CLKの立ち上がりのタイミングで取り込んで、クロック出力制御信号N1を生成し入力バッファ90に出力する。

10

**【0009】**

入力バッファ90は、クロック出力制御信号N1がLレベルとなることにより非活性化され、クロック信号I-CLKの出力を停止する。 DLL回路91は、入力であるクロック信号I-CLKが停止されると、内部クロック信号CLKの出力を停止する。これにより内部の動作が停止し、SDRAMを低消費電力モードに移行させていた。

**【0010】**

**【発明が解決しようとする課題】**

20

しかしながら、低消費電力モード時に入力バッファ90を非活性化し外部クロック信号E-CLKの取り込みを停止すると、 DLL回路91のフィードバック動作が停止してしまう。このように低消費電力モードで DLL回路91を停止させると、通常モードに復帰する時、 DLL回路91がアンロック状態からロック状態まで移行するのに長時間を要し、その間はSDRAMの書き込みや読み出し等の動作を行うことができなくなる。

**【0011】**

また、SDRAMの高速化に伴い、 DLL回路91を低消費電力モード時にも継続して動作させ、 SDRAM内部の一部の動作を停止するアクティブパワーダウンモードが要求されている。このアクティブパワーダウンモードでは、 DLL回路のロック状態が維持され、パワーダウンモードから復帰した時、短時間で通常動作を開始することができる。この場合は、単純に入力バッファ90で外部クロック信号E-CLKの取り込みを停止させると DLL回路が停止し好ましくない。

30

**【0012】**

一方、低消費電力モードに移行させるためのクロックイネーブル信号CKEは、外部クロック信号E-CLKとは非同期に生成されて内部クロック出力回路に入力される。このため、CKEコマンドラッチ回路94で生成されるクロック出力制御信号N1の立ち下がり及び立ち上がりのタイミングは、 DLL回路91の出力である内部クロック信号CLKに対して非同期となる。

**【0013】**

このため、通常モードから低消費電力モードに移行するパワーダウンエントリー時、及び低消費電力モードから通常モードに復帰するパワーダウンイグジット時において、クロックイネーブル信号CKEの入力タイミングによっては、予め設定されているパルス幅より狭いパルス幅の内部クロック信号CLKが出力されてしまう可能性がある。

40

**【0014】**

このような予め設定されているパルス幅を確保できない内部クロック信号CLKをSDRAM等に供給すると、所定のパルス幅の内部クロック信号CLKを基準として動作するSDRAM等の誤動作を招き、信頼性の低下につながる。

**【0015】**

そこで本発明は、低消費電力モードから通常モードに復帰する場合の動作を高速化できる内部クロック出力回路を有する集積回路装置を提供することを目的とする。

50

**【0016】**

また本発明は、通常モードから低消費電力モードに移行するパワーダウンエントリー時、及び低消費電力モードから通常モードに復帰するパワーダウンイグジット時において、内部クロック信号のパルス欠けを生じない内部クロック出力回路を有する集積回路装置を提供することを目的とする。

**【0017】****【課題を解決するための手段】**

上記の目的は、外部クロック信号とクロックイネーブル信号とが供給され、外部クロック信号と所定の位相関係を有する内部クロック信号を内部回路に供給する集積回路装置において、外部クロック信号と位相同期した遅延クロック信号を生成するD L L回路を、低消費電力モードにおいても継続して動作させ、内部回路への遅延クロックの供給を停止する。そして、低消費電力モードから通常モードに復帰する時に、継続して動作しているD L L回路の遅延クロック信号を内部クロック信号として内部回路に供給することにより達成される。

10

**【0018】**

本発明によれば、D L L回路は、低消費電力モードにおいても遅延クロック信号を継続して生成している。このため、低消費電力モードから通常モードに復帰する時に、D L L回路はすでにロックオン状態にあり、外部クロック信号に位相同期した内部クロック信号を内部回路に直ちに供給することができ、集積回路装置を書き込みや読み出し等ができる状態に高速に移行させることができる。

20

**【0019】**

また、上記の目的は、外部クロック信号とクロックイネーブル信号とが供給され、外部クロック信号と所定の位相関係を有する内部クロック信号を内部回路に供給する集積回路装置において、内部クロック信号を内部回路に供給するか否かを制御するクロック出力制御信号を、遅延クロック信号と所定の位相関係のタイミングで生成し、ゲート回路に出力することにより達成される。

**【0020】**

本発明によれば、クロック出力制御信号は、遅延クロック信号と所定の位相関係、例えば立ち下がりのタイミングに同期してゲート回路に入力されるので、低消費電力モードに移行する時及び通常モードに復帰する時に、内部クロック信号のパルス欠けを生じることがなく、集積回路装置の誤動作を未然に防止し、信頼性を向上させることができる。

30

**【0021】****【発明の実施の形態】**

以下、本発明の実施の形態の例について図面に従って説明する。しかしながら、かかる実施の形態例が本発明の技術的範囲を限定するものではない。

**【0022】**

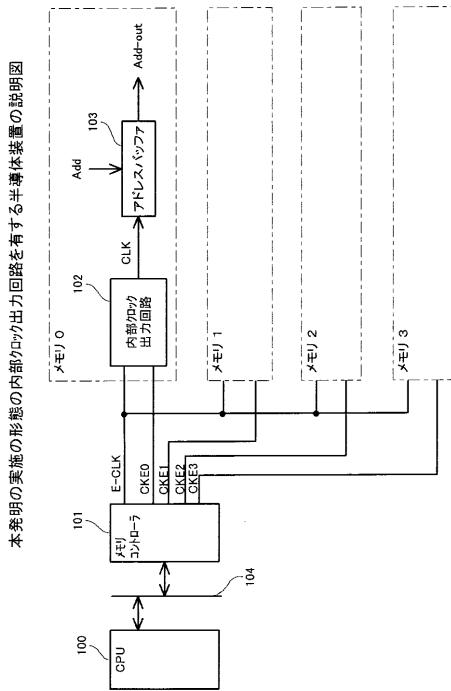

図1は、本発明の実施の形態の内部クロック出力回路を有する集積回路装置の使用状態を示す図である。C P U 1 0 0は、バス1 0 4を介してメモリコントローラ1 0 1に接続されたメモリ0～3にアクセスする。メモリコントローラ1 0 1は、各メモリ0～3に外部クロック信号E - C L Kを供給すると共に、各メモリ0～3を低消費電力モードに移行させるためのクロックイネーブル信号C K E 0～3を出力する。メモリ0～3は、クロックイネーブル信号C K E 0～3がHレベルの時通常モードとなり、クロックイネーブル信号C K E 0～3がLレベルの時低消費電力モードとなる。

40

**【0023】**

メモリ0～3は、例えばS D R A M等の集積回路装置でそれぞれ同様の構成を有する。メモリ0内の内部クロック出力回路1 0 2は、外部クロック信号E - C L Kを取り込んで、外部クロック信号E - C L Kと位相同期した内部クロック信号C L Kを生成し、通常モードでは内部クロック信号C L Kをアドレスバッファ1 0 3に出力する。アドレスバッファ1 0 3は、供給された内部クロック信号C L Kに同期してアドレスA d dを取り込み、アドレス出力A d d - o u tを外部に出力する。

50

**【 0 0 2 4 】**

一方、クロックイネーブル信号 CKE0 も内部クロック出力回路 102 に入力される。内部クロック出力回路 102 は、クロックイネーブル信号 CKE0 が L レベルとなると内部クロック信号 CLK の出力を停止し、アドレスバッファ 102 の動作を停止させてメモリ 0 を低消費電力モードに移行させる。

**【 0 0 2 5 】**

クロックイネーブル信号 CKE0 が H レベルとなると、内部クロック信号 CLK の出力が開始され通常モードとなるが、本実施の形態では、内部クロック出力回路 102 は、通常モードに復帰する時に、外部クロック信号 E-CLK に位相同期した内部クロック信号 CLK を直ちに出力することができ、メモリ 0 の通常モードへの復帰動作を高速化することができる。

10

**【 0 0 2 6 】**

また、本実施の形態では、内部クロック信号 CLK は、低消費電力モードに移行する時及び通常モードに復帰する時に、パルス欠けのないクロック信号を出力するので、アドレスバッファ 103 等の誤動作を未然に防止し信頼性を向上させることができる。

**【 0 0 2 7 】**

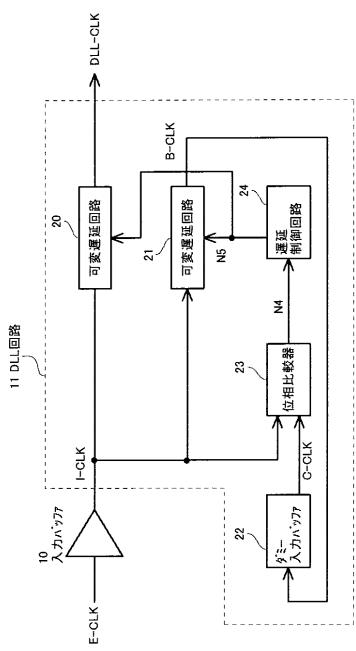

図 2 は、本発明の実施の形態の内部クロック出力回路 102 の構成図である。まず、クロックイネーブル信号 CKE に応答して、内部クロック CLK の供給を停止するアクティブパワーダウンモードについて説明する。

**【 0 0 2 8 】**

アクティブパワーダウンモードでは、上位のメモリコントローラからアクティブコマンド AC が供給されると共にクロックイネーブル信号 CKE が L レベルになる。その結果、パワーダウン制御回路 18 は、クロックイネーブル信号 CKE が L レベルになっていても活性化信号 PD を活性状態にし、入力バッファ 10、14 の活性状態を維持する。

20

**【 0 0 2 9 】**

外部クロック信号 E-CLK は入力バッファ 10 に入力され、波形成形が行われてクロック信号 I-CLK となる。クロック信号 I-CLK と外部クロック信号 E-CLK との間には、入力バッファ 10 の遅延時間に相当する遅れが生じる。

**【 0 0 3 0 】**

クロック信号 I-CLK は DLL 回路 11 に入力される。DLL 回路 11 は、外部クロック信号 E-CLK と位相同期した遅延クロック信号 DLL-CLK を生成する。遅延クロック信号 DLL-CLK は、NAND 回路 12 に出力されると共に、CKE コマンドラッチ回路 15 及び CKE タイミング制御回路 16 に出力される。

30

**【 0 0 3 1 】**

一方、クロックイネーブル信号 CKE は入力バッファ 14 に入力され、波形成形が行われてクロックイネーブル信号 CKE1 となる。クロックイネーブル信号 CKE1 とクロックイネーブル信号 CKE との間にも、入力バッファ 14 の遅延時間に相当する遅れが生じる。

。

**【 0 0 3 2 】**

クロックイネーブル信号 CKE1 は CKE コマンドラッチ回路 15 に入力される。CKE コマンドラッチ回路 15 は、クロックイネーブル信号 CKE1 を遅延クロック信号 DLL-CLK の立ち上がりのタイミングで取り込み、ラッチ信号 N1 を出力する。

40

**【 0 0 3 3 】**

ラッチ信号 N1 は CKE タイミング制御回路 16 に入力される。CKE タイミング制御回路 16 は、遅延クロック信号 DLL-CLK が H レベルの時のラッチ信号 N1 をラッチし、遅延クロック信号 DLL-CLK が L レベルと時に保持してクロック出力制御信号 N2 を出力する。クロック出力制御信号 N2 は NAND 回路 12 に入力される。

**【 0 0 3 4 】**

クロック出力制御信号 N2 は、NAND 回路 12 により、遅延クロック信号 DLL-CLK を内部クロック信号 CLK として出力するか否かを制御する。クロック出力制御信号 N

50

2がHレベルの時にNAND回路12を通過した遅延クロック信号DLL-CLKは、インバータ13で反転されて内部クロック信号CLKとなり、前述したSDRAMのアドレスバッファ等に供給される。また、クロック出力制御信号N2がLレベルの時は、遅延クロック信号DLL-CLKはNAND回路12を通過できず、内部クロック信号CLKはSDRAMのアドレスバッファ等に供給されない。

#### 【0035】

このように本実施の形態の内部クロック出力回路102では、アクティブコマンドACが供給されると共にクロックイネーブル信号CKEがLレベルとなるアクティブパワーダウンモードにおいて、DLL回路11は、外部クロック信号E-CLKに位相同期した遅延クロック信号DLL-CLKを継続して生成している。このためアクティブパワーダウンモードから通常モードに復帰する時に、外部クロック信号E-CLKに位相同期した内部クロック信号CLKをアドレスバッファ等に直ちに供給することができ、SDRAMを書き込みや読み出し等のできる状態に高速に移行させることができる。10

#### 【0036】

また、クロック出力制御信号N2は、遅延クロック信号DLL-CLKの立ち下がりのタイミングに同期してNAND回路12に入力される。従って、アクティブパワーダウンモードに移行する時及び通常モードに復帰する時に、遅延クロック信号DLL-CLKの次の立上がり時から内部クロック信号CLKが停止又は再開されるので、内部クロック信号CLKのパルス欠けを生じることがなく、SDRAMの誤動作を未然に防止し信頼性向上させることができる。20

#### 【0037】

このようにアクティブパワーダウンモードでは、入力バッファ10、14及びDLL回路11等を動作させ、クロックイネーブル信号CKEに対応して内部クロックCLKの供給を停止する。一方、消費電力を更に低減するためには、入力バッファ10、14及びDLL回路11等の動作を停止させるスタンバイパワーダウンモードが設けられる。

#### 【0038】

スタンバイパワーダウンモードでは、上位のメモリコントローラからのアクティブコマンドACがない状態で、クロックイネーブル信号CKEがLレベルとなる。その結果、パワーダウン制御回路18は活性化信号PDを非活性状態にする。このため入力バッファ10、14は非活性化され、更に、クロック信号I-CLKが供給されないことからDLL回路11の動作も停止する。従って、スタンバイパワーダウンモードでは、アクティブパワーダウンモードより更に消費電力を低減することが可能である。30

#### 【0039】

また、スタンバイパワーダウンモードでは、入力バッファ14が非活性状態にあるので、スマートバッファ17によりクロックイネーブル信号CKEのHレベルへの変化が検出される。その結果、パワーダウン制御回路18は、活性化信号PDを活性状態にもどして、入力バッファ10、14を活性化する。そして、DLL回路11の動作再開と共にNAND回路12が開かれ、内部クロック信号CLKが他の入力バッファや内部回路に供給される。

#### 【0040】

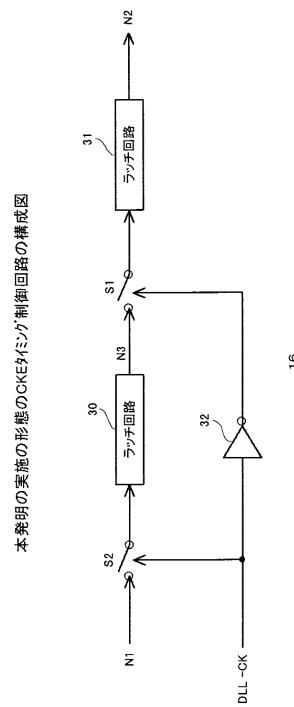

図3は、本発明の実施の形態の内部クロック出力回路102に内蔵されるDLL回路11の構成図である。DLL回路11は同じ遅延特性を有する可変遅延回路20、21を備え、可変遅延回路20の遅延量を最適値に設定することにより、外部から供給される外部クロック信号E-CLKの位相に同期した遅延クロック信号DLL-CLKを生成する。40

#### 【0041】

外部から供給される外部クロック信号E-CLKは、入力バッファ10を介してクロック信号I-CLKとなりDLL回路11に入力される。クロック信号I-CLKは、可変遅延回路20、21に供給されると共に、位相比較器23にも供給される。

#### 【0042】

可変遅延回路21から出力されたクロック信号B-CLKは、ダミー入力バッファ22を50

介して、位相比較器 23 にクロック信号 C - C L K として供給される。位相比較器 23 は、クロック信号 I - C L K とクロック信号 C - C L K の位相を比較し、位相比較信号 N4 を遅延制御回路 24 に出力する。遅延制御回路 24 は、可変遅延回路 21 と可変遅延回路 20 とにそれぞれ遅延制御信号 N5 を出力し、クロック信号 I - C L K とクロック信号 C - C L K の位相が一致するように、可変遅延回路 20、21 の遅延量を制御する。即ち、その遅延量は、外部クロック信号 E - C L K の 1 周期の時間から入力バッファ 10 の遅延時間を差し引いた時間である。

#### 【 0 0 4 3 】

可変遅延回路 20、21 は、多数の遅延素子を直列に接続した構造になっており、遅延制御信号 N5 により信号が通過する遅延素子の数が制御される。可変遅延回路 20、21 は、遅延制御信号 N5 により同じ遅延量を与えるように制御されるため、可変遅延回路 20 に入力されるクロック信号 I - C L K は、可変遅延回路 20 により遅延クロック信号 D L L - C L K が外部クロック信号 E - C L K の位相と同期する遅延量を与えられて D L L 回路 11 から出力される。従って、D L L 回路 11 は、クロック信号 I - C L K が供給されていれば、その位相比較と遅延制御動作を継続する。

#### 【 0 0 4 4 】

図 4 は、本発明の実施の形態の内部クロック出力回路 102 に内蔵される CKE タイミング制御回路 16 の構成図である。図 2 に示したように、クロックイネーブル信号 CKE は、入力バッファ 14 を介してクロックイネーブル信号 CKE1 となり CKE コマンドラッチ回路 15 に入力される。クロックイネーブル信号 CKE1 は、CKE コマンドラッチ回路 15 により遅延クロック信号 D L L - C L K の立ち上がりエッジで取り込まれ、ラッチ信号 N1 となって図 4 に示すスイッチ S2 に入力される。

#### 【 0 0 4 5 】

スイッチ S2 は、遅延クロック信号 D L L - C L K が H レベルの期間オンとなり、ラッチ信号 N1 をラッチ回路 30 に出力する。従って、ラッチ回路 30 は、遅延クロック信号 D L L - C L K が L レベルから H レベルに変化した時にラッチ信号 N1 を受け取り、遅延クロック信号 D L L - C L K が H レベルから L レベルに変化した時のラッチ信号 N1 を保持する。

#### 【 0 0 4 6 】

ラッチ回路 30 の出力信号 N3 はスイッチ S1 に入力される。スイッチ S1 は、遅延クロック信号 D L L - C L K をインバータ 32 で反転した信号で制御され、遅延クロック信号 D L L - C L K が L レベルの期間オンとなる。従って、ラッチ回路 31 は、遅延クロック信号 D L L - C L K が H レベルから L レベルに変化した時に信号 N3 を受け取り、遅延クロック信号 D L L - C L K が L レベルから H レベルに変化した時の信号 N3 を保持する。ラッチ回路 31 の出力が内部クロック出力制御信号 N2 となり、図 2 に示した NAND 回路 12 に出力される。

#### 【 0 0 4 7 】

なお図 4 では、遅延クロック信号 D L L - C L K の立ち上がりのタイミングで信号 N1 を受け取り信号 N3 を生成しているが、図 2 に示した CKE コマンドラッチ回路 15 の遅延時間が大きい場合は、スイッチ S2 及びラッチ回路 30 を省略し信号 N1 を直接スイッチ S1 に入力してもよい。

#### 【 0 0 4 8 】

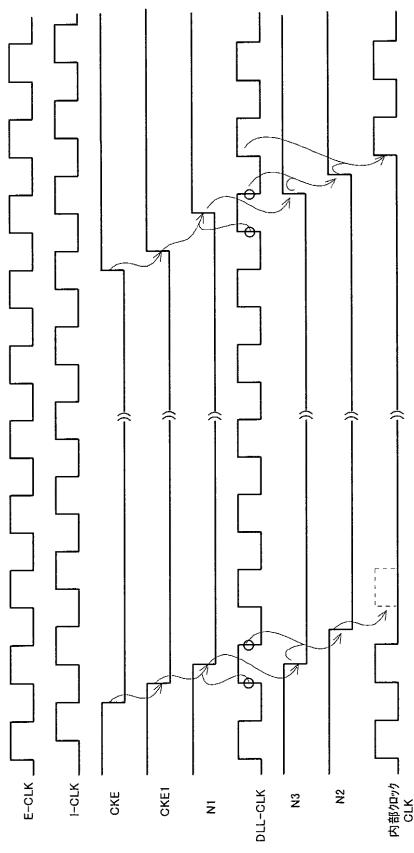

図 5 は、本発明の実施の形態の内部クロック出力回路 102 のタイムチャートである。内部クロック出力回路 102 の動作を図 2 及び図 4 を参照しつつ図 5 のタイムチャートにより説明する。

#### 【 0 0 4 9 】

外部クロック信号 E - C L K は、入力バッファ 10 の遅延時間に相当する遅れを生じてクロック信号 I - C L K となる。一方、クロックイネーブル信号 CKE は外部クロック信号 E - C L K とは非同期で入力され、入力バッファ 14 の遅延時間に相当する遅れを生じてクロックイネーブル信号 CKE1 となる。なお、クロックイネーブル信号 CKE が H レベ

10

20

30

40

50

ルの期間が通常モードであり、クロックイネーブル信号 CKE が L レベルの期間が低消費電力モードである。

#### 【 0 0 5 0 】

クロック信号 I - CLK は DLL 回路 11 に入力され、外部クロック信号 E - CLK に位相同期した遅延クロック信号 DLL - CLK となる。また、クロックイネーブル信号 CKE 1 は CKE コマンドラッチ回路 15 に入力され、遅延クロック信号 DLL - CLK の立ち上がりのタイミングで取り込まれてラッチ信号 N1 となる。

#### 【 0 0 5 1 】

ラッチ信号 N1 は、CKE タイミング制御回路 16 のスイッチ S2 (図 4 参照) に入力される。スイッチ S2 は遅延クロック信号 DLL - CLK が H レベルの期間オンとなるので、ラッチ回路 30 は遅延クロック信号 DLL - CLK が H レベルから L レベルに変化する時の信号 N1 をラッチする。ラッチ回路 30 の出力が信号 N3 である。

10

#### 【 0 0 5 2 】

信号 N3 はスイッチ S1 に入力される。スイッチ S1 は遅延クロック信号 DLL - CLK が L レベルの期間オンとなるので、ラッチ回路 31 は遅延クロック信号 DLL - CLK が L レベルから H レベルに変化する時の信号 N3 をラッチする。ラッチ回路 31 の出力がクロック出力制御信号 N2 である。このクロック出力制御信号 N2 が L レベルとなると、NAND 回路 12 により内部クロック信号 CLK の出力が停止される。

20

#### 【 0 0 5 3 】

このように本実施の形態の内部クロック出力回路 102 は、低消費電力モードにおいても外部クロック信号 E - CLK に位相同期した遅延クロック信号 DLL - CLK が生成されている。このため低消費電力モードから通常モードに復帰する時に、外部クロック信号 E - CLK に位相同期した内部クロック信号 CLK を直ちに出力することができる。従って、通常モードに復帰する時の SDRAM の書き込みや読み出し等の動作を高速化することができる。

#### 【 0 0 5 4 】

また、クロック出力制御信号 N2 は、遅延クロック信号 DLL - CLK の立ち下がりのタイミングに同期して出力されるため、低消費電力モードに移行する時及び通常モードに復帰する時に、内部クロック信号 CLK のパルス欠けを生じない。このため、内部クロック信号 CLK が供給されるアドレスバッファ等の誤動作を未然に防止し、SDRAM の信頼性を向上させることができる。

30

#### 【 0 0 5 5 】

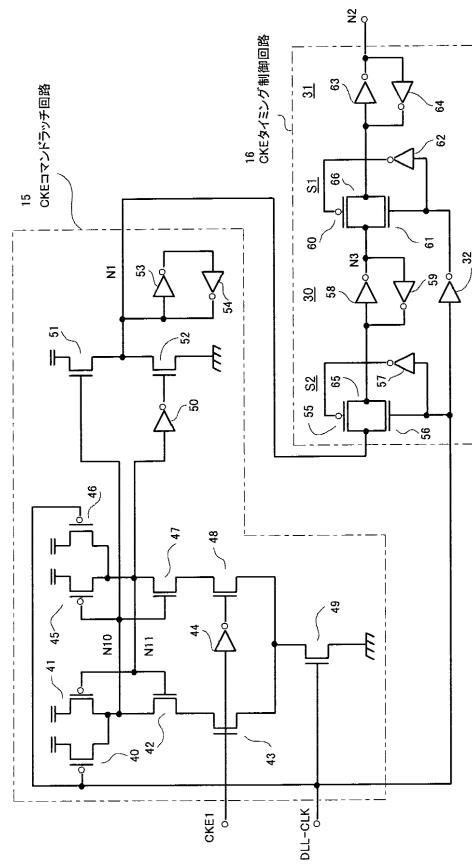

図 6 は、本発明の実施の形態の CKE コマンドラッチ回路 15 と CKE タイミング制御回路 16 の回路例を示す。CKE コマンドラッチ回路 15 は、P 型トランジスタ 40、41、45、46、51、N 型トランジスタ 42、43、47、48、49、52、インバータ 44、50、53、54 を有し、遅延クロック信号 DLL - CLK の立ち上がりタイミングのクロックイネーブル信号 CKE 1 をラッチし、ラッチ信号 N1 を出力する。

#### 【 0 0 5 6 】

遅延クロック信号 DLL - CLK が L レベルの時は、N 型トランジスタ 49 はオフし、P 型トランジスタ 40、46 はオンとなるため、ノード N10、N11 は共に H レベルである。このため P 型トランジスタ 51 と N 型トランジスタ 52 は共にオフとなり、ノード N1 はハイインピーダンス状態となる。なお、ノード N10、N11 は共に H レベルであるため、N 型トランジスタ 42、47 は共にオンとなっている。

40

#### 【 0 0 5 7 】

遅延クロック信号 DLL - CLK が H レベルになると N 型トランジスタ 49 はオンとなる。この時クロックイネーブル信号 CKE 1 が L レベルの場合は、インバータ 44 により N 型トランジスタ 48 のゲートが H レベルとなるため、N 型トランジスタ 48 がオンしノード N11 を L レベルとする。一方、クロックイネーブル信号 CKE 1 が H レベルの場合は、N 型トランジスタ 43 がオンしノード N10 を L レベルとする。ノード N10 又は N11 が L レベルとなると、P 型トランジスタ 45 又は 41 がオンし、反対側のノード N11 又は

50

N10をHレベルに確定する。

**【0058】**

ノードN10がLレベルでノードN11がHレベルの場合は、P型トランジスタ51はオン、N型トランジスタ52はオフとなり、ノードN1はHレベルとなってインバータ53、54によりラッチされる。一方、ノードN10がHレベルでノードN11がLレベルの場合は、P型トランジスタ51はオフ、N型トランジスタ52はオンとなり、ノードN1はLレベルとなってインバータ53、54によりラッチされる。

**【0059】**

CKEタイミング制御回路16は、P型トランジスタ55とN型トランジスタ56によるトランスマルチゲート65、インバータ32等を有する。なお、トランスマルチゲート65とインバータ57とが図4に示したスイッチS2に相当し、トランスマルチゲート66とインバータ62とがスイッチS1に相当する。また、インバータ58と59とが図4に示したラッチ回路30に相当し、インバータ63と64とがラッチ回路31に相当する。

10

**【0060】**

CKEコマンドラッチ回路15から出力されたラッチ信号N1はトランスマルチゲート65に入力され、遅延クロック信号DLL-CLKのHレベルの期間にトランスマルチゲート65を通過し、ラッチ回路30でラッチされて信号N3となる。

**【0061】**

信号N3はトランスマルチゲート66に入力され、遅延クロック信号DLL-CLKのLレベルの期間にトランスマルチゲート66を通過し、ラッチ回路31でラッチされてクロック出力制御信号N2となる。このクロック出力制御信号N2が、図2に示したNAND回路12により内部クロック信号CLKを出力するか否かを制御する。

20

**【0062】**

このように本発明の実施の形態では、低消費電力モードに移行する時、入力バッファ10を非活性化して外部クロック信号E-CLKの取り込みを停止させるのではなく、NAND回路12で内部クロック信号CLKの出力を停止させている。

**【0063】**

従って、入力バッファ10及びDLL回路11は、外部クロック信号E-CLKが入力される限り活性状態であり、NAND回路12に遅延クロック信号DLL-CLKを供給し続ける。このため、低消費電力モードから通常モードに復帰した際の内部クロック信号CLKの位相ズレを防止でき、SDRAM等を通常動作に高速に復帰させることができる。

30

**【0064】**

**【発明の効果】**

以上説明した通り、本発明によれば、低消費電力モードにおいても外部クロック信号に位相同期した内部クロック信号を継続して生成しているため、低消費電力モードから通常モードに復帰する場合に、外部クロック信号に位相同期した内部クロック信号を直ちに供給することができ、SDRAM等の動作を高速化することができる。

**【0065】**

また本発明によれば、通常モードから低消費電力モードに移行するパワーダウンエントリー時、及び低消費電力モードから通常モードに復帰するパワーダウンイグジット時において、内部クロック信号のパルス欠けによるSDRAM等の誤動作を未然に防止し、信頼性向上させることができる。

40

**【図面の簡単な説明】**

**【図1】**本発明の実施の形態の内部クロック出力回路を有する集積回路装置の説明図である。

**【図2】**本発明の実施の形態の内部クロック出力回路の構成図である。

**【図3】**本発明の実施の形態のDLL回路の構成図である。

**【図4】**本発明の実施の形態のCKEタイミング制御回路の構成図である。

**【図5】**本発明の実施の形態の内部クロック出力回路のタイムチャートである。

**【図6】**本発明の実施の形態のCKEコマンドラッチ回路とCKEタイミング制御回路の

50

回路図である。

【図7】従来の内部クロック出力回路の構成図である。

【符号の説明】

- 10、14 入力バッファ

- 11 DLL回路

- 12 NAND回路

- 13 インバータ

- 15 CKEコマンドラッチ回路

- 16 CKEタイミング制御回路

- 30、31 ラッチ回路

- 102 内部クロック出力回路

- 103 アドレスバッファ

10

【図1】

【図2】

【図3】

本発明の実施の形態のDLL回路の構成図

【図4】

【図5】

本発明の実施の形態の内部クロック出力回路のタイムチャート

【図6】

本発明の実施の形態のCKEコマンドラッチ回路とCKEタイミング制御回路の回路図

【図7】

従来の内部クロック出力回路の構成図

---

フロントページの続き

(56)参考文献 特開平08-315572(JP,A)

特開平06-290583(JP,A)

特開平09-198875(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/407

G11C 11/4076