(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5498376号

(P5498376)

(45) 発行日 平成26年5月21日(2014.5.21)

(24) 登録日 平成26年3月14日(2014.3.14)

(51) Int.Cl.

F 1

H01L 27/105 (2006.01)

H01L 27/10 447

H01L 21/8246 (2006.01)

H01L 43/08 Z

H01L 43/08 (2006.01)

請求項の数 8 (全 26 頁)

(21) 出願番号 特願2010-508587 (P2010-508587)

(86) (22) 出願日 平成20年5月15日 (2008.5.15)

(65) 公表番号 特表2010-527516 (P2010-527516A)

(43) 公表日 平成22年8月12日 (2010.8.12)

(86) 國際出願番号 PCT/US2008/063781

(87) 國際公開番号 WO2008/144438

(87) 國際公開日 平成20年11月27日 (2008.11.27)

審査請求日 平成23年3月29日 (2011.3.29)

(31) 優先権主張番号 60/938,678

(32) 優先日 平成19年5月17日 (2007.5.17)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/943,513

(32) 優先日 平成19年6月12日 (2007.6.12)

(33) 優先権主張国 米国(US)

(73) 特許権者 503020345

インテグレイテッド・マグネットエレクトロニクス

INTEGRATED MAGNETOELECTRONICS

アメリカ合衆国 カリフォルニア州94709 バークレー, オックスフォード・ストリート, 1214

(74) 代理人 1100000028

特許業務法人明成国際特許事務所

(72) 発明者 トロク・イー・・ジェームズ

アメリカ合衆国 ミネソタ州55126-1317 ショアビュー, カントリー・コード アイ・ダブリュ, 860

最終頁に続く

(54) 【発明の名称】スケーラブル不揮発性記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

1 または複数のメモリセルから成る記憶装置であって、各メモリセルは、磁気抵抗性を示す第1の多層薄膜記憶素子と、前記第1の多層薄膜記憶素子の上側に配置され、前記第1の多層薄膜記憶素子と電気的に絶縁されている第1の信号線と、前記第1の信号線の上側に配置され、前記第1の薄膜記憶素子および第1の信号線の両方と電気的に絶縁されている第2の信号線と、

前記第2の信号線の上側に配置され、前記第1の薄膜記憶素子、前記第1の信号線、および前記第2の信号線と電気的に絶縁され、磁気抵抗性を示す第2の多層薄膜記憶素子と、前記第1の薄膜記憶素子および前記第2の薄膜記憶素子と直接接触する2つの非導電性保持素子とを備え、

前記第1の薄膜記憶素子、前記第2の薄膜記憶素子、および前記保持素子とが前記第1および第2の信号線の周りに完全磁束閉鎖構造を形成する、記憶装置。

## 【請求項 2】

前記1または複数のメモリセルは複数の列と複数の行に配列されている複数のメモリセルを備え、前記メモリセルの各列内の第1の薄膜記憶素子は第1の連続薄膜構造の一部であり、各メモリセルの第1の信号線はメモリセルの対応する列の第1の連続駆動線の一部

10

20

であり、各メモリセルの第2の信号線はメモリセルの対応する行の第2の連続駆動線の一部であり、前記第1の信号線の1つと前記第2の信号線の1つは各メモリセルにて交差し、それぞれの信号線の電流の方向が各メモリセルにおいて平行となるように構成されている、請求項1に記載の記憶装置。

【請求項3】

第1の駆動線の各々が蛇行パターンに構成され、隣接するメモリセルの列に対応する第1の駆動線は、各メモリセルに関連するセル面積が、 $f$ をリソグラフィ印刷の特徴サイズとした場合に $4f^2$ となるように重なり合う、請求項2に記載の記憶装置。

【請求項4】

1ビット以上の情報を記憶するように第1の薄膜記憶素子が構成されている、請求項1に記載の記憶装置。 10

【請求項5】

前記1または複数のメモリセルは、少なくとも一個の処理装置と関連するキャッシュ記憶装置と長期記憶とを含む記憶階層状に配置されているメモリセルの複数のアレイを備える、請求項1に記載の記憶装置。

【請求項6】

請求項1に記載の記憶装置であって、各メモリセルが磁気抵抗性を示す多層薄膜記憶素子を備え、前記記憶素子は水平幅と鉛直厚さで特徴付けられ、前記記憶素子の鉛直厚さが記憶素子の水平幅に対して前記記憶素子の体積が所定期間記憶素子の磁化状態の熱的安定を確保するのに十分であるように制御される、記憶装置。 20

【請求項7】

請求項6に記載の記憶装置であって、各記憶素子が少なくとも1周期の層から成り、各周期の層が高保磁力層、低保磁力層、及び高保磁力層と低保磁力層の間の非磁気層を含み、前記記憶素子の鉛直厚さは高保磁力層、低保磁力層、或は非磁気層の一枚以上の層の厚さを調整することで制御される、記憶装置。

【請求項8】

請求項6に記載の記憶装置であって、各記憶素子が複数の周期の層から成り、各周期の層が高保磁力層、低保磁力層、及び高保磁力層と低保磁力層の間の非磁気層を含み、記憶素子の鉛直厚さは層の周期の数で制御される、記憶装置。

【発明の詳細な説明】 30

【技術分野】

【0001】

【関連特許出願】

本出願は、「INHERENTLY RADHARD NONVOLATILE MEMORY」の名称で2007年5月17日に提出された米国仮出願60/938678号、「INHERENTLY RADHARD NONVOLATILE MEMORY」の名称で2007年12月7日に提出された米国仮出願61/012106号、及び、「MAGNETORESISTIVE MEMORIES」の名称で2007年6月12日に提出された米国仮特許出願60/943513号を基に米国特許法35U.S.C.119(e)によって優先権を主張するものである。本出願は、更に「SCALABLE NONVOLATILE MEMORY」の名称で2008年5月14日に提出された米国特許出願12/120549号を基に米国特許法35U.S.C.120によって優先権を主張するものである。 40

【0002】

本発明は不揮発性記憶装置に関し、殊に、磁気抵抗性に基づく記憶装置に関する。

【背景技術】

【0003】

半導体及び磁気RAM(MRAM)を含む従来の不揮発性記憶装置は、放射線から保護するための遮蔽を必要とする。従来のMRAM構成は磁気的記憶素子を使用することで不揮発性を提供するが、個々のメモリセルにアドレスするためにCMOSトランジスタを使用 50

されるので、システムに対して放射障害に対する脆弱性が取り込まれる。

#### 【0004】

近年に於いて、M R A M 産業では磁気トンネル接合型（M T J）構造に基づく不揮発性記憶装置の開発と商業化に主として焦点をあてている。従来のM T J 記憶装置および最近開発されたるトグル型M T J 記憶装置は共に製品化に際して求められる程度の密度を達成するためには障害となる欠点を有している。先ず、M T J 記憶装置のセルは、セルデザインの複雑さ及び密接したセルの干渉の理由により、C M O S のプロセシングの線幅よりかなり大きい。

#### 【0005】

次に、セル間の距離の縮小に従って、完全選択（f u l l - s e l e c t e d）と半選択（h a l f - s e l e c t e d）セルの切り替えフィールド分布間の重なりの結果、恐らく近隣セルからの消磁場に起因して、許容不可能な高い書き込みエラー率をもたらす。最後に、殆どのM T J デザインには通称「磁化クリープ」なる現象であって、セルが時間と共に消磁されて情報内容が喪失されるという問題を有している。

10

#### 【発明の概要】

#### 【0006】

本発明の種々の実施例において、メモリセル及び磁気抵抗性に基づく構成、及び同製造方法が提供される。具体的な種類の実施例に於いては、一個以上のメモリセルを含む記憶装置（及びかのような記憶装置を内蔵する電子システム）で各メモリセルが磁気抵抗性を示す第1の多層薄膜記憶素子を含むものが許容される。第1の信号線は前記第1の多層薄膜記憶素子の上側に配置され、第1の多層薄膜記憶素子と電気的に絶縁されている。第2の信号線は第1の信号線の上側に配置され、前記第1の薄膜記憶素子と第1の信号線の両方と電気的に絶縁されている。少なくとも一個の非導電性保持（k e e p e r）素子が前記第1の薄膜記憶素子と直接接触している。前記第1の薄膜記憶素子と前記保存素子とは完全閉鎖フラクス構造の少なくとも一部を形成する。実施例の種々のサブセットに於いて、第1の薄膜記憶素子の各々は一個以上のG M R 素子、M T J 素子、C I P 素子、またはC P P 素子を含むものであつてよい。種々の別のサブセットに於いて、各メモリセルの第1の信号線と第2の信号線とは、その各々に関連する電流方向が平行するように構成される。

20

#### 【0007】

更に他の実施例の記憶装置（及びかのような記憶装置を内蔵する電子システム）は、絶縁体によって隔離された第1と第2の磁気層を有する磁気トンネル接合型（M T J）記憶素子が配列の中の各メモリセルに含まれることが許容される。各列のメモリセルの第1の磁気層は直列に接続されて第1のセンス線を形成し、各列のメモリセルの第2の磁気層は直列に接続されて第2のセンス線を形成する。

30

#### 【0008】

更に他の実施例に於いては、各メモリセルが磁気抵抗性を示す多層薄膜記憶素子を含む記憶装置、そのような記憶装置を内蔵する電子システム、及びそのような記憶装置の製造の方法が可能とされる。記憶素子は水平幅と鉛直厚さで特徴付けられる。記憶素子の鉛直厚さは記憶素子の水平幅に対し、記憶素子の体積が所定期間、記憶素子の磁化状態の熱的安定を確保するのに十分であるように制御される。

40

#### 【0009】

本発明の特徴及び利点は、明細書の残りと図面を参照することによって更に明確になることであろう。

#### 【図面の簡単な説明】

#### 【0010】

【図1】本発明の実施例と共に使用されるメモリセルの簡素化された断面である。

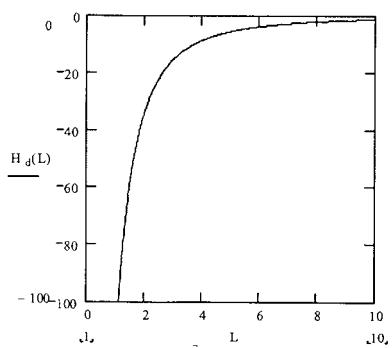

【図2】セルの長さの関数としての消磁場の図面の一例である。

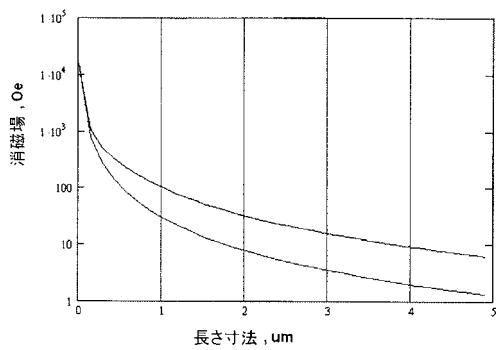

【図3】セルの長さの関数としての消磁場の図面の異なる二つの間隙サイズの場合の一例である。

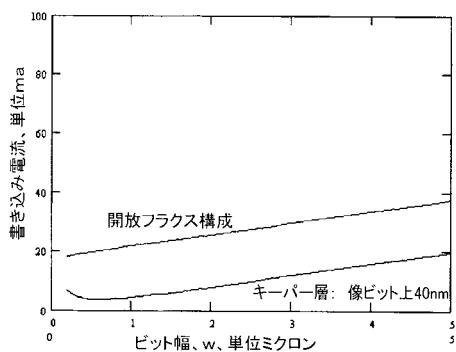

【図4】開放フラクス構造と保存装置付きの構造との理論的書き込み電流の図面の一例で

50

ある。

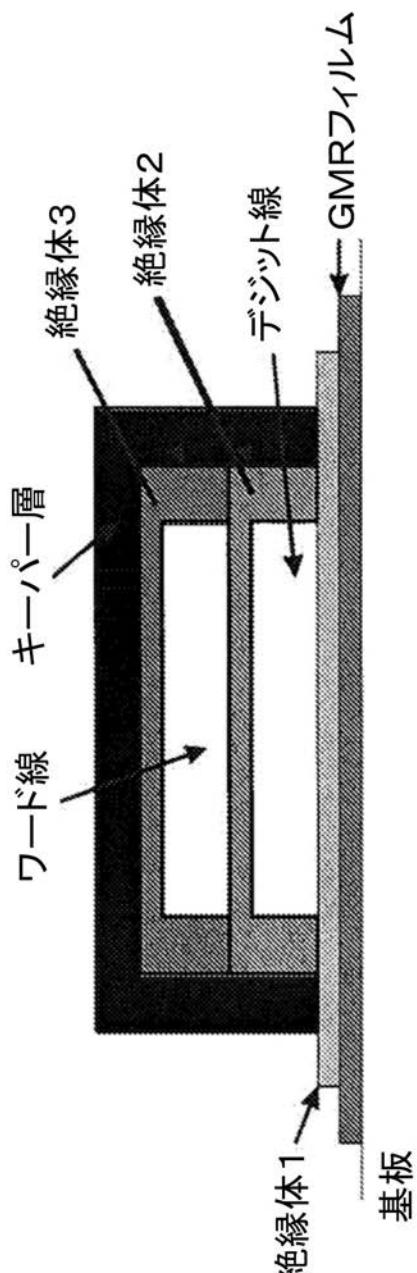

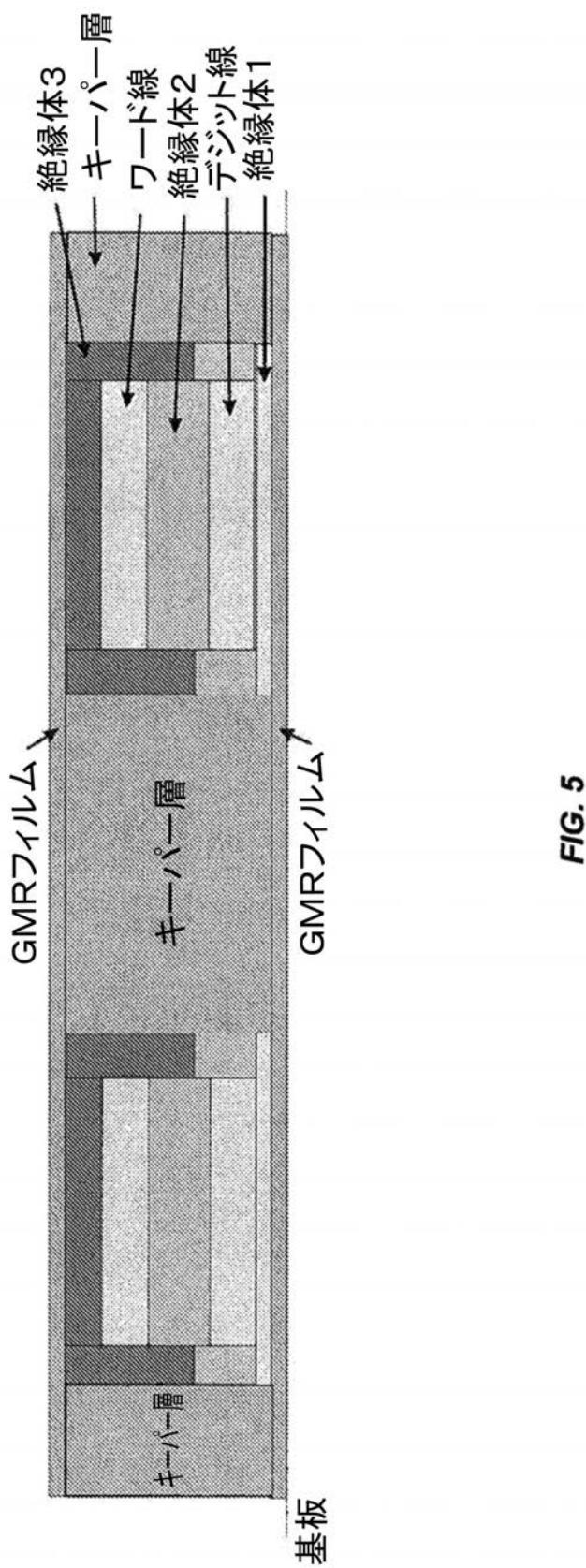

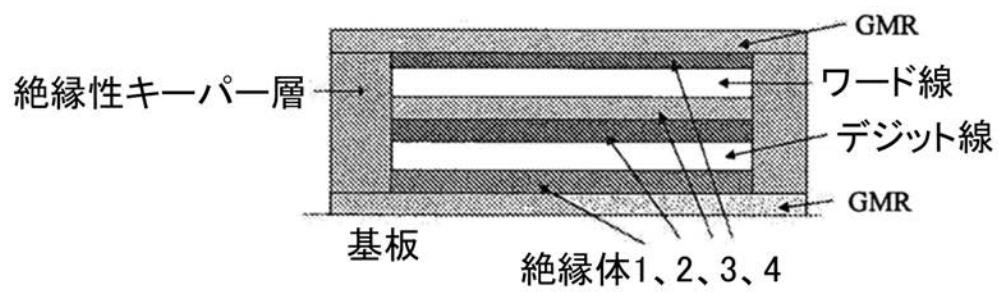

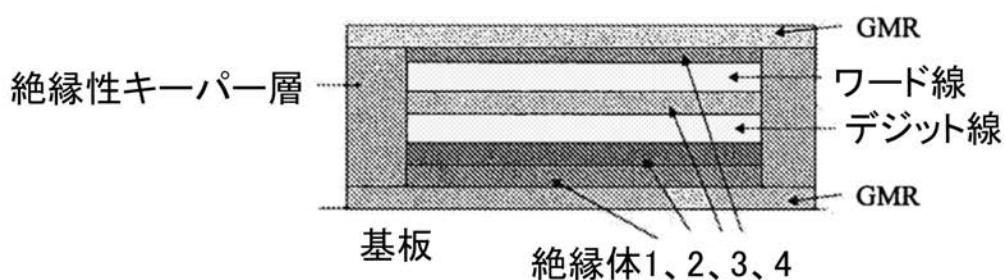

【図5】本発明の種々の実施例で使用可能な完全閉鎖フラクス構造を有するメモリセルの簡素化断面である。

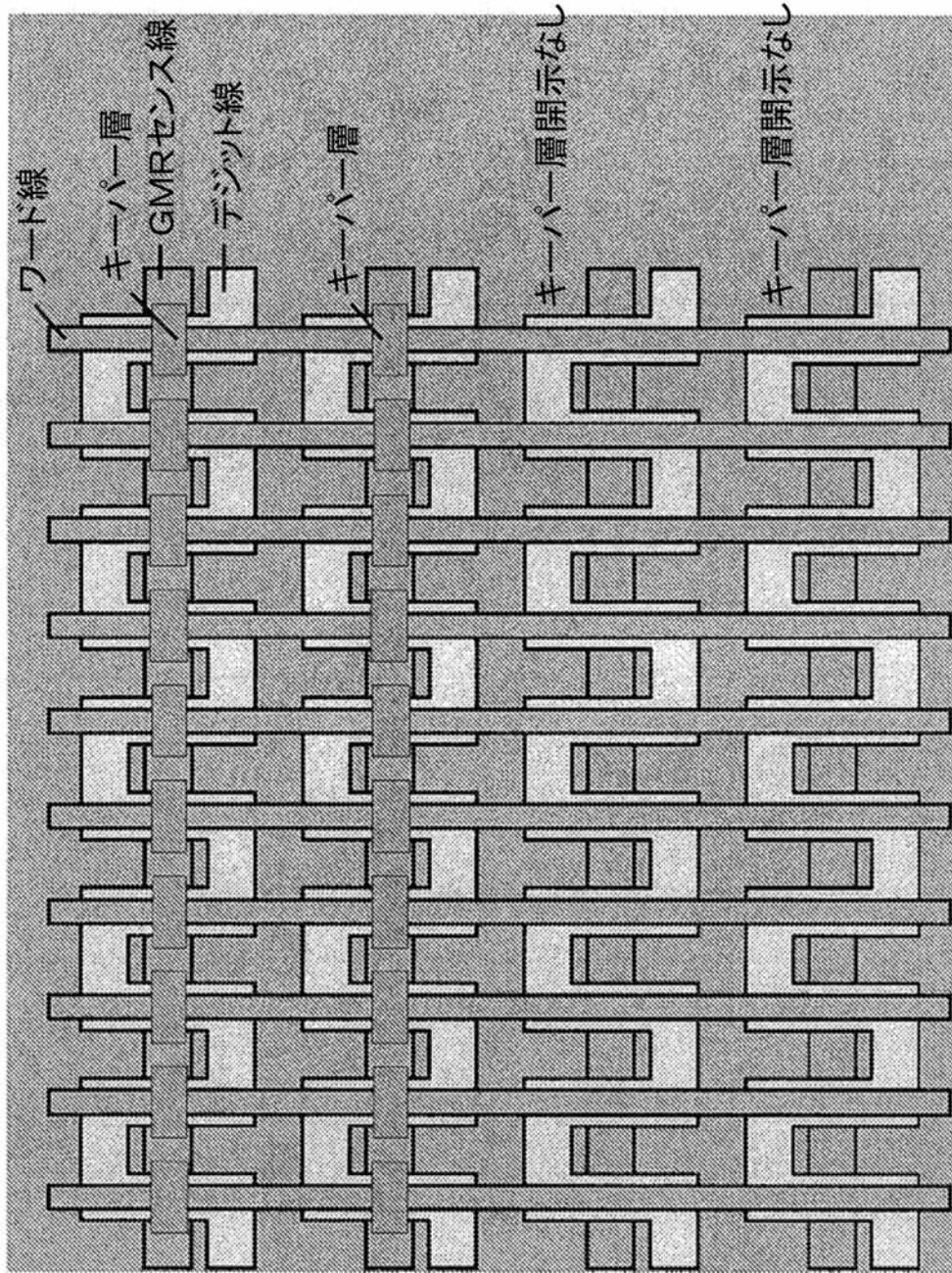

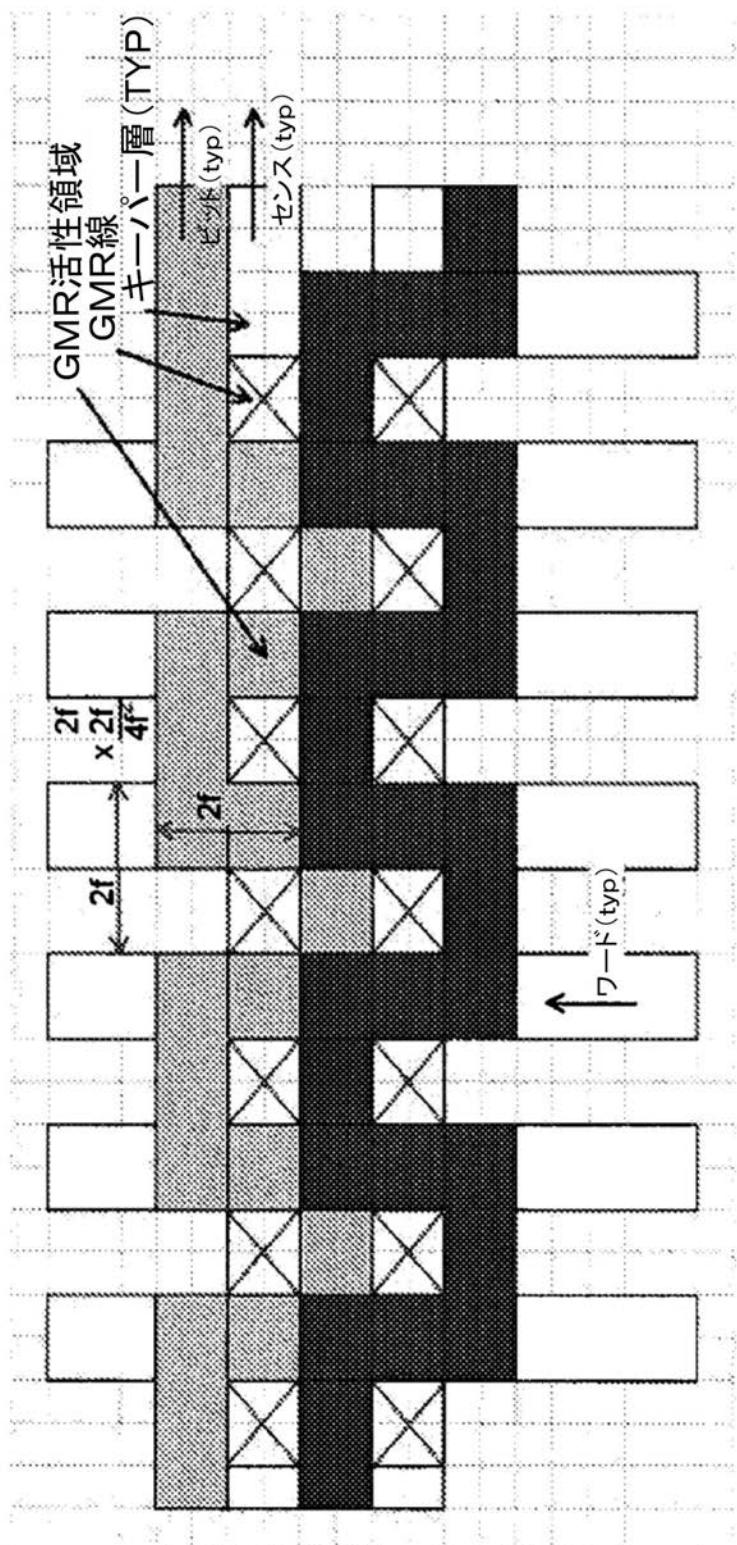

【図6】本発明の特種実施例による記憶装置配列の簡素化上面図である。

【図7】本発明の特種実施例による記憶装置配列の簡素化上面図である。

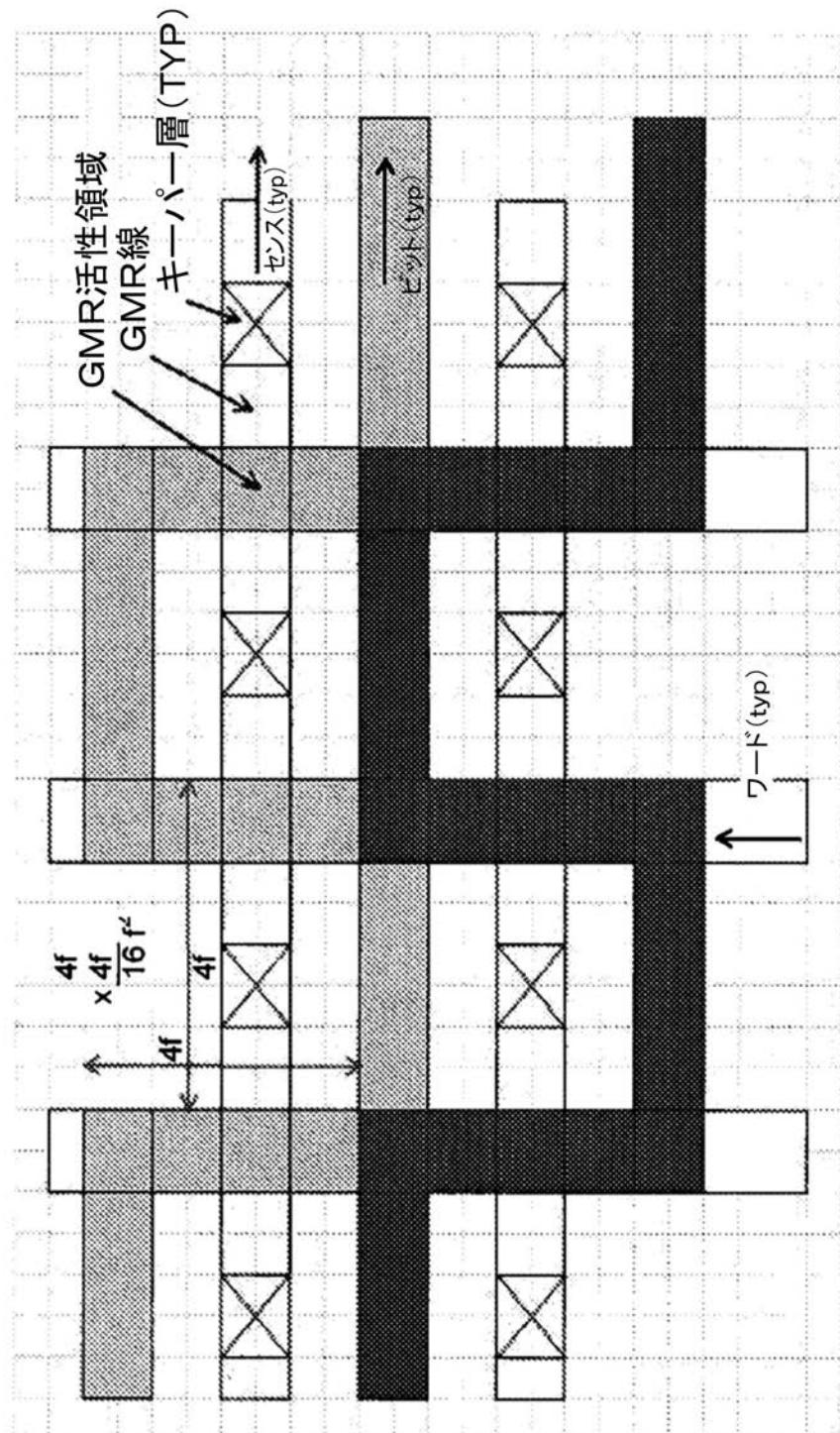

【図8】本発明の特種実施例による記憶装置配列の簡素化上面図である。

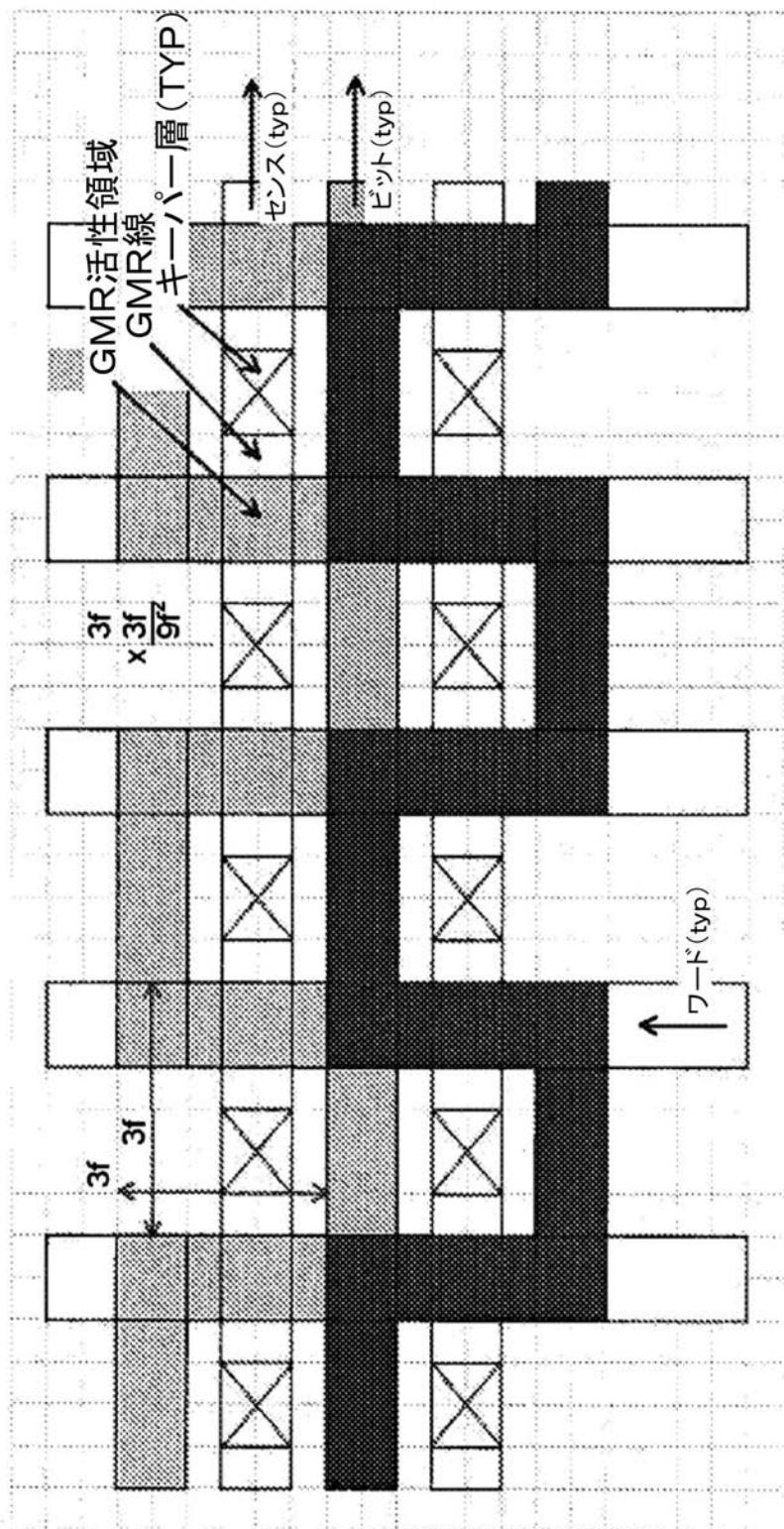

【図9】本発明の特種実施例による記憶装置配列の簡素化上面図である。

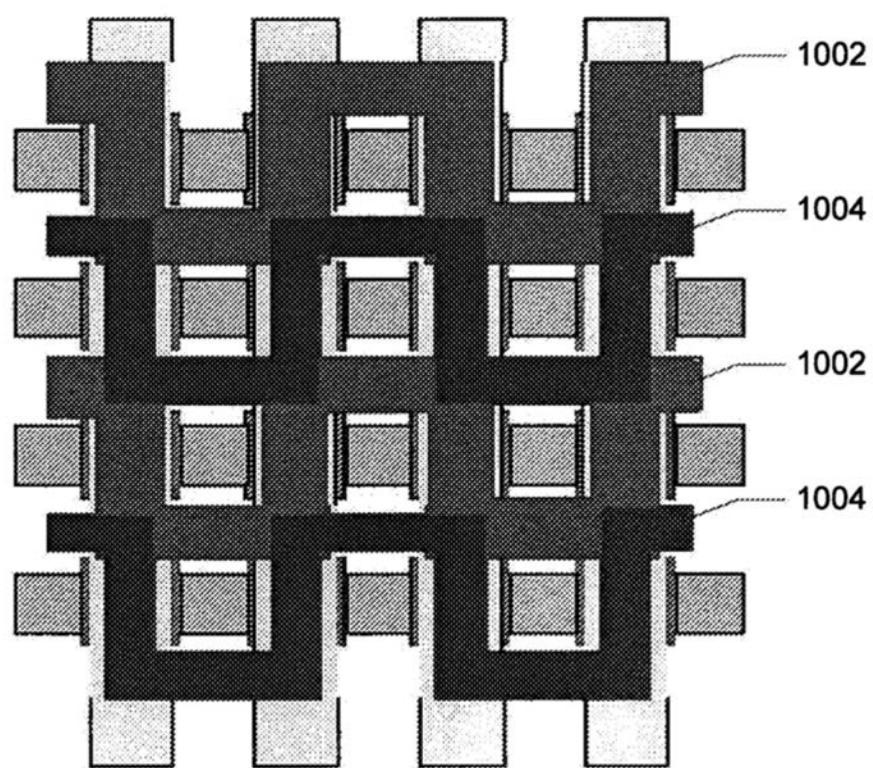

【図10】本発明の特種実施例による記憶装置配列の簡素化上面図である。

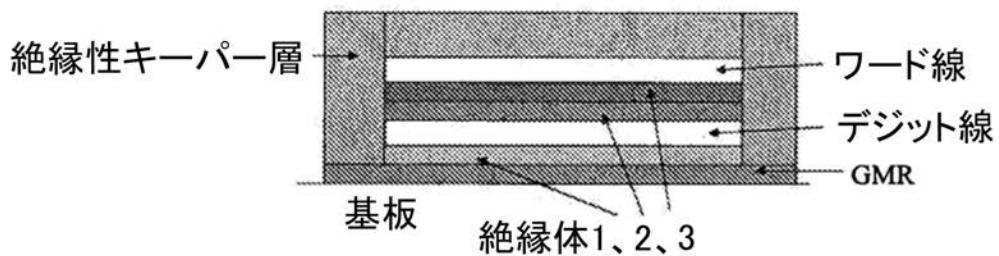

【図11】本発明の種々の実施例に使用可能な完全閉鎖フラクス構造を有するメモリセルの簡素化断面である。 10

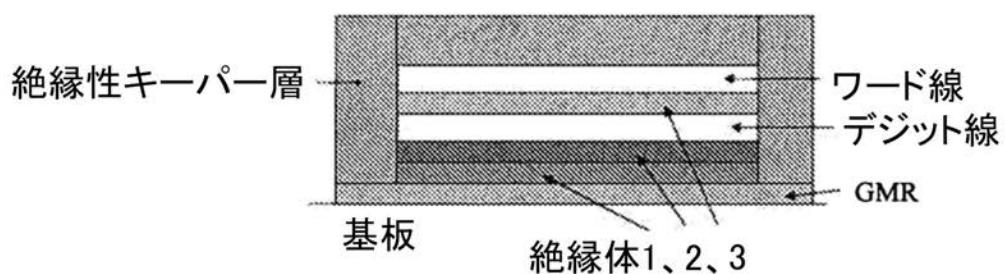

【図12】本発明の種々の実施例に使用可能な完全閉鎖フラクス構造を有するメモリセルの簡素化断面である。

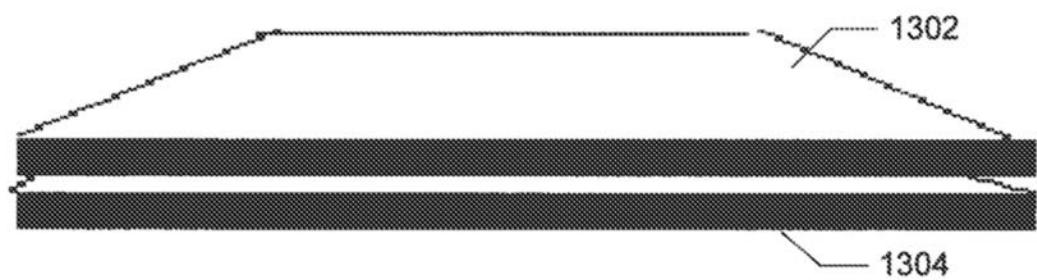

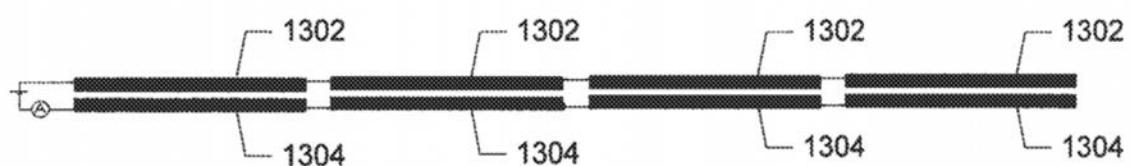

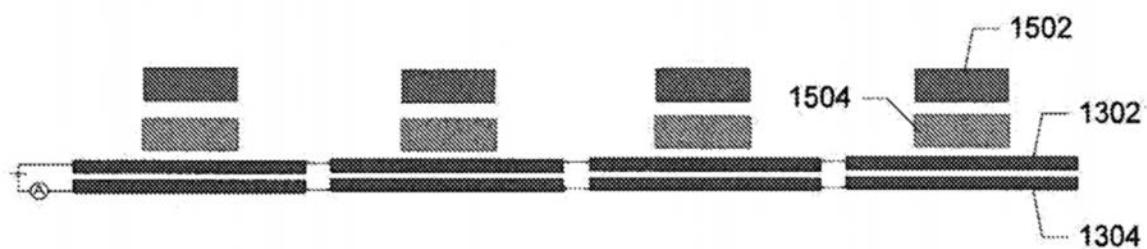

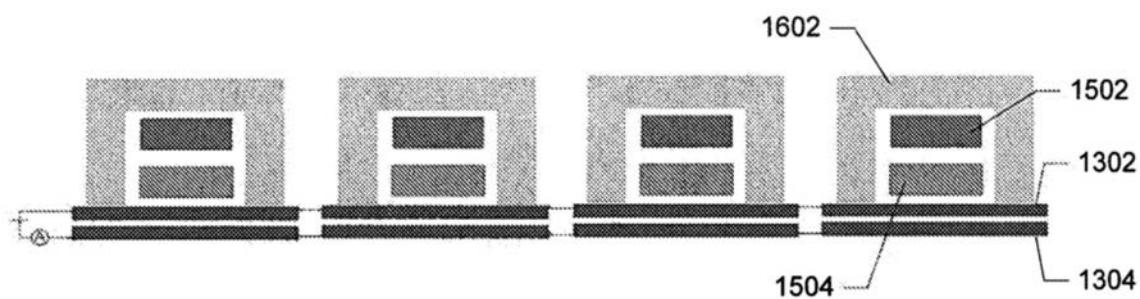

【図13】本発明の種々の実施例に使用可能な完全閉鎖フラクス構造を有するメモリセルの種々の観点の簡素化した図である。

【図14】本発明の種々の実施例に使用可能な完全閉鎖フラクス構造を有するメモリセルの種々の観点の簡素化した図である。

【図15】本発明の種々の実施例に使用可能な完全閉鎖フラクス構造を有するメモリセルの種々の観点の簡素化した図である。

【図16】本発明の種々の実施例に使用可能な完全閉鎖フラクス構造を有するメモリセルの種々の観点の簡素化した図である。 20

#### 【発明を実施するための形態】

##### 【0011】

発明を実施するに当たり、発明者が最良とみなす形体を含めた実施例を、以降、詳細に参照することにする。これらの具体的な実施例は添付された図に示されている。本発明はこれらの実施例によって記述されるものではあるが、本発明はこれらの実施例によって限定されるものではなく、後述の請求項で定義されるように、本発明の趣旨を逸脱しない範囲で代替物、改良物、均等物などを含むものとする。以後の記述に於いて、本発明の完璧な理解のために具体的に詳述される。本発明はこれら具体的な詳細例の一部または全部を備えることなく実施可能である。別の例として、本発明の実際の内容を不明確にしない目的のため、周知の機能・構成についての説明は省略する。 30

##### 【0012】

本発明の種々の実施例に於いて、種々の磁気抵抗機構に基づく不揮発性記憶装置が可能とされる。本明細書に記述されるいくつかの実施例は、細小化に関する問題を解消し、従来の技術で不可能であった大きさの磁気抵抗性記憶装置を可能とした。具体的な種類の実施例に於いて、メモリセルや構成は、書き込み電流密度がリソグラフィ印刷における線幅に対してほぼ不变、即ち書き込み電流が線幅に比例して縮小する完全閉鎖フラクス構造を有するメモリセルデザインを使用して実施される。本明細書に図示されるメモリセルや配列の構成は簡素化されており、種々の関係ある特徴を明確に示すために、必ずしもスケール通りには示されていない。

##### 【0013】

本明細書において、磁気的媒体に関して「消磁場」の用語が使用される場合、これは、媒体自身が磁化されたソースからなる磁気媒体内部の場を意味する。この場は磁気媒体の外側に延び、通常「フリンジ場」と呼ばれている。しかし、これは同じ現象に関する二つの異なる名称であると理解されるべきである。磁気媒体の内部では、消磁場は駆動電流に向き合っており、素子サイズの減少と共に大幅に増大する。これが従来のMTJ MRAMデザインにおいて大きな書き込み電流が必要とされる理由である。フリンジ場は、磁気ディスクへの書き込みに使用されるディスクヘッドに於いて必須である。しかしながら、MRAMの場合には、一個のセルからのフリンジ場が近隣のセルのビット値を変えるので、重大な問題となる。

##### 【0014】

10

20

30

40

50

飽和矩形セルは磁化方向に垂直なセルの各端部にシート状の極を有する。その近接場  $H_d$  は 2 M で不变であり、これは NiFe の場合 5000 ガウスでフィルム保磁力の 20e より遙かに大きい。従って端部は消磁され、極はセルの端部に広げられる。事実、M はメモリセル上の位置と共に変化する可能性がある。

#### 【0015】

開放フラックス構造においては、書き込み電流が  $H_d$  に打ち勝つ場を供給しなくてはならないので、消磁場  $H_d$  及びそれに対応する駆動電流が極めて大きくなる。本願発明の種々の実施例に於いて、消磁場はキーパー層（保持部：keeper）の使用によって減少され、閉鎖の促進及び／または閉鎖構造の形成をすることになる。キーパー層とは低保磁力のフィルムであって、その磁化の結果の境界条件として、フィルム面での磁界が消去され、消磁場が弱められる。具体的な実施例に於いて、キーパー層は消磁場を弱化することと、必要とする駆動電流を弱化すること（これは消磁場とは別問題である）と、二つの機能を持つ。例えば、駆動電流を半分にすることで、消費電力は 4 分の 1 に減少され、選択に必要とされる面積が縮小される。

#### 【0016】

消磁場  $H_d$  の例えは図 1 に示されるようなメモリ素子の関連するパラメタへの依存度を調べるために、M をセルの位置の関数とし、その結果セル中央に於ける  $H_d$  を以下のようにした。

#### 【0017】

#### 【数1】

$$H_d = M_0 T \int_{-\frac{a}{2}}^{\frac{a}{2}} \int_{-\frac{L}{2}}^{\frac{L}{2}} -\frac{8}{L^2} \left[ \frac{x^2}{\left(x^2 + y^2\right)^{\frac{3}{2}}} - \frac{x^2}{\left[x^2 + y^2 + (2g)^2\right]^{\frac{3}{2}}} \right] dx dy$$

#### 【0018】

ここで、L は易軸（easy axis）に沿ったセルの長さ、a は難軸（hard axis）に沿ったセルの幅、T は磁気層全体（介在する導体層や非磁気層を除く）の厚さ、g はセルとキーパー層間の隙間の厚さ（即ち、絶縁体 1 の厚さ）、及び  $M_0$  は中央の最大磁化である。

#### 【0019】

この積分値は Mathcad を使用して数値的に得られた。セルの長さの関数とし、他のパラメタの値を一定とした場合の消磁場の図面を図 2 に示す。この例において、消磁場  $H_d$  は o e の単位で与えられており、L の単位は  $\mu m$  である。更に  $M_0 = 800$  ガウス、T = 20 nm、g = 0.1  $\mu m$ 、a = 1  $\mu m$  である。一定の方向比（a / L）の場合、隙間の大きさが一定ならば  $H_d$  はセルのスケールが縮小するにつれて増大する。従って、セルの大きさがナノ規模に縮小されると、消磁場は許容不可能な程に大きくなる。図 3 は、隙間の二つの大きさの場合について、消磁場を L（L = 3a）の関数として示すものである。即ち隙間が 20 nm（下側の曲線）と、隙間が 10 nm（上側の曲線）との場合であり、 $M_0 = 800$  ガウス、T = 10 nm である。

#### 【0020】

開放フラックス構造とキーパー層を有する構造についての、 $H_d = 250$  e の薄膜セルへの理論的書き込み電流が図 4 に於いて比較されている。図示されているように、少なくとも部分的フラックス閉鎖を供するキーパー層は、ビット或はセル幅が隙間（ギャップ）の大きさに近づくまで書き込み電流を減少するために有効である。

#### 【0021】

シミュレーションの結果でも、消磁場に急激な増加がある場合、最小サイズが約 1  $\mu m$  以下に縮小すると、図 1 に示されるセルのようなセルのための駆動場が非常に大きくなるこ

10

20

30

40

50

とを示唆している。従って、ミクロン以下のレベルに於いては、このようなセルデザインは受け入れがたい。従って、発明の具体的な実施例に於いて、記憶素子とキーパー層との間の隙を無くし、その結果、駆動電流がセルの幅と事実上リニアに縮小し続けるようなセルデザインが提供される。

#### 【0022】

GMR (giant magnetoresistance: 巨大磁気抵抗) 薄膜素子に基づく具体的な実施例群について記述する。これらの実施例で使用される薄膜構造とはGMRを示すものであり、その中の高い保磁力を有する（即ち比較的高い場で転換する）磁性層が記憶に使用され、低い保磁力を有する（即ち比較的低い場で転換する）磁性層が読み出しに使用されるものである。ビット値は磁化方向として記憶される。素子の抵抗値は、硬層と軟層の相対的磁化方向に依存する。そのような実施例と共に使用するのに適したGMR素子が非磁性的導体層を介在させた各々のタイプの磁気層をもつもの、あるいは数周期のそのような層をもつものであってよいと理解されよう。

10

#### 【0023】

完全閉鎖フラクス構造を持つ「無隙：ギャップレス（gapless）」セルデザインの例であって、本発明の具体的な実施例によって設計された例が図5に示されている。このようなメモリセルの配列は図6に示されるように構成されてもよい。この構成に於いて、個々のセルは交差する駆動（アドレス）線の配列によってアクセスされる。書き込みは交差する駆動線の各々に与えられる二本の半選択電流の一致による。半選択電流の各々は硬（記憶）層を転換するのに必要な場の半分を供給するものである。このような構成は典型的にクロスポイント（cross point）メモリ配置と呼ばれている。図6のセルはGMRセンス線の中にあり、その一部をなす。従って、セルは、GMR素子の中には物理的に別個の物体ではないが直列なのであり、即ちそこには連続的な線が存在することになる。GMR線の活性部分（メモリセル）は、直線や蛇行線のオーバーレイのもと、これらの線が平行であるGMR線の部分によって物理的に決定される。例として、直線の駆動線をワード線、蛇行線の駆動線をデジット線と呼ぶことにする。しかし、これらの名称は任意の名称であり、発明の範囲を限定するものではない。読み出しには、硬層のいずれも転換せず（非破壊的読み出し）その行のすべてのセルの軟層を転換するために十分の力を有し、しかし硬層を転換する半選択電流より弱い全選択電流パルスが関係する。センス線バイアス電流はGMR線に信号を生成する。例えば、コバルト（記憶）層を転換する全選択場は100eVであり、パマロイ（読み出し）層を転換する全選択場は20eVであってよい。

20

#### 【0024】

描かれたデザインが、メモリセルに於いて平行なワードとデジット線を使用する理由は2つある。第一の理由は、これによってキーパー層の端部がGMR素子に近く位置され、H<sub>d</sub>を小さくすることが出来るからである。第2の理由は、パルス的硬軸場と硬軸場の変化中にオンする易軸場との結合によって生じる累積的妨害機構（磁化クリープとも呼ばれる）が存在するからである。セル自身が消磁されて情報内容が失われることになるこの障害の形態は、易軸場のみを使用するこのデザインによって回避される。この易軸（easy-axis）構成を利用するメモリセルの配列は、図5で示された構成に限られるものではない。例えば、図1及び図11～16に示されるメモリセルは同様な構成に変更されてもよい。

30

#### 【0025】

図5のメモリセルは完全閉鎖フラクス構造であり、その結果、ビット転換に要する場はセルサイズが減少しても一定である。即ち、阻害問題の緩和に関する実験的証拠は、二つの問題に共通する物理的要因、即ち消磁場を持つが故に、駆動電流はフィーチャー（特徴）サイズの減少に対応することを強く示唆している。ナノ規模の特徴的サイズに於けるミクロアンプ程度の駆動電流は予期されており、クロスポイントメモリ配列の理論的限界に近いセルサイズ即ちアドレス線の交差する配列によりアクセスされる記憶装置は実現可能である。これは、典型的なMTJ-MRAMセルのそれより一桁小さいものである。

40

50

## 【0026】

マクスウェルの方式  $\times H = J_{free}$  ( S I 単位 ) によれば、電線内の電流による磁場は  $H = 1 / 2 I ( a + T )$  であることを示している。ここで線の幅と層の厚さはメートル単位であり、Iはアンペア単位の電流である。即ち、ストリップ線内部に生じる場は、駆動電流に比例し、(  $T = a$  であるから ) 特徴サイズに反比例する。必要とされる転換場は、消磁場が存在しない限り、特徴サイズに依存しない。従って、書き込み電流は消磁場が存在しない限り線の幅に比例した規模となる。

## 【0027】

本願発明の具体的な実施例として、様々な手法によって、外部磁場に対する保護が提供される。上記の如く、キーパー層は、キーパー層がその上に置かれた構造に外部磁場が入り込まないようにするために使用することが出来る。外部磁場が存在する場合、それが迷走磁場であっても印加磁場であっても、キーパー層内の磁化が、その極が外部場に対して等しくて反対の磁場を生成する構成へと変化し、キーパー層で保護された構造内への進入を中和するように機能する。10

## 【0028】

更に、具体的な実施例の場合、チップ全体を保護するコネティク ( connectic ) 磁気遮蔽が供給される。このような遮蔽は長期間に亘って軍関係に於いて潜水艦、航空機、ミサイル内での磁気薄膜メモリの保護に使用されていた。

## 【0029】

図 1、5 および 11 ~ 16 に示されたようなメモリセルを配置するための幾何学形が次に図 7 - 9 を参照して記述される。最初の 2 例はパーマロイのキーパー層を使用することに基づいたものである。パーマロイは導電性金属合金であり、短絡のないようにキーパー層と磁気抵抗素子との間の絶縁が必要とされる(例えば図 1 のセル)。より密度の高い第三の幾何学形が、非導電性保存装置と無間隙デザインの使用によって可能とされる(例えば図 5 のセル)。20

## 【0030】

図 7 に示される第 1 の幾何学形では、間隔仕様要求を控え目に最低特徴サイズの  $f$  と仮定し、その結果セル面積を約  $16 f^2$  とする。ビット線は濃淡の灰色のシェイディングで示す如く重なった(しかし絶縁された)蛇行形導電体である。ワード線は白色で示されたストリップ線であり、図では一部ビット線に隠されている。GMR 線(センス線としても使用される)は示される如く水平のストリップ線である。キーパー層は X<sub>s</sub> で示されて居る。30

## 【0031】

図 8 に示される第 2 の幾何学形は、従来の半導体処理過程で周知であったように、異なる層で製造される特徴は間隔をより密に出来ると仮定したものである。この例に於いては、異なる層に形成された特徴間の距離を  $f / 2$  としてある。導電性キーパー層の絶縁をより薄くする結果として、セル面積は約  $9 f^2$  となる。

## 【0032】

図 9 に示される第三の幾何学形は不導電性磁性体のキーパー層材料を使用して居る。これによって別個の絶縁層が不要となり、その結果セル面積が単ビットセルの理論的限界である  $4 f^2$  となる。40

## 【0033】

フェライトは絶縁性磁性体である。数年前、記録用ディスク産業界では、ハードドライブ用のフェライトで覆われたディスクがかなり成功しており、ここでは高磁力の材料に焦点が置かれていた。図 9 での  $4 f^2$  のセルのキーパー層は低保磁性で高透磁率の材料から成る。非結晶フェライト膜はそのような実施例のキーパー層のための使用に好適な例である。前記の配列幾何学的形の例のように、ビット線は濃淡の灰色のシェイディングで示す如く重なった(しかし絶縁された)蛇行形導電体である。ワード線は白色で示されたストリップ線であり、一部ビット線で隠されて居る。GMR 線(センス線としても使用される)はキーパー層の下の(同様に白色の)水平なストリップ線であり、同様に一部隠されてい50

る。キーパー層はやはり X s で示されている。

【 0 0 3 4 】

一般的に、本発明の種々な実施例による保存装置の実施には広範囲の材料が使用可能なものであり、好適な新しい材料は続々と開発されて居る。使用に好適な例を網羅することは非現実的なことであり、若干の例を此処に掲げることにする。

【 0 0 3 5 】

好適な材料の一例は、 $M O - F e_2 O_3$  のようなスピネル構造のフェライトであり、此処で M とは  $M n$ ,  $F e$ ,  $C o$ ,  $N i$ ,  $C u$ ,  $M g$ ,  $L i$  のような二価の金属である。このようなフェライトの混合物も使用可能である。好適な材料の別例は、ヘマタイト（アルファ  $F e_2 O_3$ ）、イルメナイト ( $F e T i O_3$ ) のようなコランダム系の酸化物である。又、M を  $C o$ ,  $N i$ , 或いは  $M n$  としての  $M T i O - F e_2 O_3$ 、及び M を  $B a$ ,  $S r$ , 或いは  $P b$  のような大きい二価のイオンとする  $M O - 6 F e_2 O_3$  のようなマグネットプランバイト酸化物も使用可能である。更に使用可能な別例は、M が  $L a$ ,  $C a$ ,  $B a$ , 或いは  $S t$  の一つである  $M F e O_3$  のようなパーゴスカイト酸化物である。その他、 $N M n O_3$  や  $M C o O_3$  も好適である。M が  $S m$ ,  $E u$ ,  $G d$ ,  $T b$ ,  $D y$ ,  $H o$ ,  $E r$ ,  $T m$ ,  $Y b$ ,  $L u$  或いは Y のような三価の金属の一つである  $3 M_2 O_3 - 5 F e_2 O_3$  のようなフェリマグネティクガーネットも使用出来る。以上に加え、上記及びその他の適切な材料の混合物も使用可能である。

【 0 0 3 6 】

本発明の実施例のキーパー層の実施に好適な材料に関する更なる情報については、*S o s h i n Chikazumi* による題名 "Ferrimagnetic Oxides and Compounds" なる John Wiley & Sons (1964) 発行の教科書 Physics of Magnetism の 5.3 節に記載されて居り、同書の全体はあらゆる目的のために此処に取り込まれたものとする。更に、M をアルカリ土類金属イオン、Me を二価金属とする  $M_3 M e_2 F e_{24} O_{41}$  のような新しい材料も使用出来る。

【 0 0 3 7 】

具体的な実施例によれば、別個の堆積とパタニングの二工程で交互のデジット線を製造し、絶縁性のキーパー層材料を使用することで、セル面積は  $4 f^2$  にまで縮小可能である。このような配置で重なったデジット線の平面図が図 10 に示されて居る。別個に堆積された二組の蛇行デジット線 1002 と 1004 は二つの暗い灰色で示され、これらは互いに絶縁されて居る。蛇行線の下には GMR 線は無く、重なりによって妨害が生じることはない。明示の目的のため、キーパー層は開示されていない。更に、図は正確なスケールを示すものではなく、例えばデジット線は実際より狭く示されて居る。

【 0 0 3 8 】

別個に堆積された二組の蛇行的デジット線は相互に、更にはワード線及び GMR 素子から絶縁されている。従って、三枚の絶縁層があることになる。図 10 に示される配置の断面に於けるこれらの層の順番は、その断面図が配置の何処に於いてとられたものかに依存する。図 11 は、本発明の種々の実施例で使用される、夫々一個の GMR 素子を含む二種類の無間隙の  $4 f^2$  セルの中央を通る二つの断面を示すものである。図 11 (a) ではデジット線は GMR 素子に近く、絶縁体 2 と 3 が隣接して居る。図 11 (b) ではデジット線はワード線に近く、絶縁体 1 と 2 が隣接して居る。具体的な実施例に於いては、或るデジット線に沿ったビットは総て同一のタイプであり、隣接したデジット線に沿ったものは異なるタイプである。絶縁体であるキーパー層は二本の駆動線のみならず GMR 層に接触し、その結果各セルが完全閉鎖フラクス構造となる。

【 0 0 3 9 】

本発明の種々の実施例に於いて使用可能なその他の  $4 f^2$  デザインの例として、重なるデジット線、絶縁性キーパー層、及び二個の GMR 素子を含むもの（例えば図 5 に示されたデザインと同様なもの）が図 12 に示されて居る。図 12 (a) ではデジット線は GMR 素子に近く、絶縁体 2 と 3 が隣接して居る。図 12 (b) ではデジット線はワード線に近

く、絶縁体1と2が隣接している。

#### 【0040】

これらの実施例に於いて、上方と下方のGMR素子に貯蔵されるデータは同一である。即ち、各ビット値は与えられたセルの異なる2個の位置に貯蔵される。これら2個の薄膜構造は抵抗を2倍にして、図11のセルデザインの場合に比して2倍の信号が実施されるよう直列に接続されてもよい。ノイズはRの平方根に依存するので、図12のセルは比較的少ない追加的処理の複雑さに拘らず、図11のものよりこの面で機能的に優秀である。従って、GMR素子はノイズが2.5倍に増えるのみで、センス信号を倍加すべく直列に接続することが出来る。

#### 【0041】

10

上記に於いて、完全閉鎖フラクス構造を持つメモリセル用の基礎としてGMR薄膜素子を使用する具体的な実施例を記述したが、本発明はこれに限定されるものでない。具体的な実施例に於いて、閉鎖フラクス構成を有するMTJ素子を使用するメモリセルや配置が考査されている。

#### 【0042】

具体的な実施例に於いて、上記のメモリセルや配置構成と同様であって、GMR薄膜素子がMTJ素子（「トンネル対」とも呼ばれる）で置き換えられたものが提供されている。一実施例によれば、各センス線が一対のセンス線として実施され、センシングはトンネル接合の抵抗により（直列でなく）並列に行われる。

#### 【0043】

20

トンネル対は図13に示されるように、絶縁間隙によって隔離された一対の磁気フィルム1302と1304によって実施されてもよい。この二枚の磁気フィルムは介在する絶縁体を通る電子のトンネル効果によって電気的に接続されて居る。絶縁体の抵抗の大小は、二枚のフィルムの磁化の方向が平行なのか反平行なのかに依存する。図14に示される如く、MTJ素子は平行に、即ち上方のフィルムを上方のフィルムに、下方のフィルムを下方のフィルムに接続して、一対のセンス線を形成することが出来る。

#### 【0044】

特定のMTJ素子のセンシングは素子のフィルムの中の一枚の磁化を前後に動かしてビットの対の間の抵抗を転換することで行ってもよい。これは図15に示される如く、MTJ素子の上のワード及びデジット線1502及び1504によって行うことが出来る。上記の如く、ワード及びデジット線は、同様な利点を得るために図6に示された如く各MTJ素子の領域に於いて平行であってもよい。更に、図16に示される如く、キーパー層構造1602が各MTJ素子の上で直接接触するようにされてあり、そのようにして、消磁場を除去する完全閉鎖フラクス構造が与えられる。

30

#### 【0045】

完全閉鎖フラクスデザインはMTJ素子を使用して実施してもよいが、GMRに基づいた実施で達成出来る様な小規模の場合、そのような規模では熱効果による不安定性が障礙となるので、かようなメモリセルの配列は不適当たり得る。

#### 【0046】

40

これらのセル、配列、及び構成を実現するのに本発明の種々の実施例と共に使用可能である量子磁気抵抗（QMR）に基づくメモリセル及び配列構造（GMR及びMTJ構造を含む）及び関連技術に関する更なる詳細については、米国特許5237529, 5592413及び5587943を参照されたい。更に、例えばプロセッサキャッシュメモリ、システムメモリ、長期貯蔵、その他のようなメモリ階層レベルの一部或は全部に於いて実施可能な計算システムは、本明細書に記述した技術を使用して実現可能なものである。

#### 【0047】

メモリセル自身のみならず、関連電子部品をすべて金属とする実施例も考慮されている。このような全金属メモリチップは元来、放射線に対して耐性を有している。このようなメモリ、当該メモリを部品として含むシステムを実現するために使用可能な全金属汎用電子部品を実施するための情報については、米国特許5929636, 6031273, 64

50

69927 及び 6484740 を参照のこと。これら特許引例の各々のすべての開示内容はすべての目的に於いて、本願内に組み込まれるものとする。

#### 【0048】

上記のごとく、又本発明の実施例に従い、理論上最低値に近いメモリセルサイズが実現可能な技術が提供されている。これにより、高程度の情報密度を持つメモリ構成が可能となる。更に大きな密度を実現するため、此処に開示された技術はその他の技術と併用されてもよいことに留意されるべきである。例えば、開示内容をすべての目的に於いて本願内に組み込まれるものとする米国特許 6594175 に記載のテクニクを使用して個々のメモリセルが複数ビットの情報を貯蔵することが考慮されている。他の例として、開示内容をすべての目的に於いて本願内に組み込まれるものとする米国特許 6992919 に記載の如く、密度を更に増大すべく、三次元的に構成された複数レベルノメモリセルと関連した電子部品とが製造されてもよい。

10

#### 【0049】

更に、リソグラフィ印刷技術の将来の発展により、水平方向及び面内の大きさをより縮小したメモリ素子の製造が可能となるであろう。面積の縮小化により、種々の次世代の磁気 RAM デザインが期待される。

#### 【0050】

その一例として、巨大磁気抵抗 (GMR) に基づく CPP (Current Perpendicular to the Plane) メモリ素子がある。これらの素子内では、CIP (current in plane) 素子の場合水平に流れるのと異なり、センス電流は素子内を鉛直に流れる。これにより、好適な条件のもとでは GMR のより高い値が得られることが知られている。CPP 素子に関連する問題の一つは、水平方向の次元より厚さの極めて小さい GMR フィルムの結果として、鉛直方向の電流に対して素子の抵抗が低すぎることになり、センシングが難しくなると言うことである。従って、ある実施例の場合、この問題に対応する CPP メモリ素子が与えられ、より大きな情報密度を可能とする機構を供給する。そのような実施例に於いて、幅の広さより厚みのある CPP 素子とし、それによって抵抗値を適当なものとする。

20

#### 【0051】

増加する微小化に関する別の問題は、メモリ素子の総体積が小さくなり過ぎて、その熱的安定性が許容不可能な程度になると言うことである。即ち、かなり小さい粒子の場合、室温における熱エネルギー (kT) はかなり大きいものとなり、粒子の磁化は熱変動に対して不安定（逆行自発性）になる可能性がある。これは緩和現象である。初期に於いて磁化されたサンプルの磁化は以下のように自発的に変化する：

$$M(t) = M_0 e^{-p(-t/\tau)}$$

ここで緩和時間は

$$= \tau_0 e^{-p(KV/(kT))}$$

で与えられ、ここで K は材料の本質的異方性であり、V はサンプルの体積、そして典型的に  $\tau_0$  は  $10^{-9}$  秒である。情報が少なくとも 10 年間安定であるため、 $KV > 40 kT$  であることが望ましい。典型的な材料の場合 K は約  $2.2 \times 10^5 J/m^3$  であり、それは最小サンプル体積が約  $10^3 nm^3$  であることを意味する。

30

40

#### 【0052】

本発明の種々の実施例の場合、CPP メモリ素子の鉛直方向の厚さは、その質量或は体積を所定の時間の間熱的安定性が確保されるだけのレベルに保たれるようにその厚さが縮小されるに従って十分增加される。厚さの増加は層の枚数（基本的薄膜構成の複数周期）を増加することで達成可能であり、これが GMR 値と信号を更に増加させるものであると言うことが追加的利点となる。実験的複数周期或は格子フィルムの GMR 値は、室温に於いて 100% 前後の範囲と知られて居る。

#### 【0053】

これらの厚さが増加されると、それに従って、磁気層間の非磁気的金属層の厚さも低保磁力層が独立に転換出来る点まで二層間に交換される力が増加しないように増加されなくて

50

はいけないかも知れないことに留意することが必要である。そうであれば、この解決法はトンネル層の効果がトンネリングを可能にする為に非常に狭い範囲になくてはならないその厚さに鋭敏であるM T Jに基づくメモリとてそれ程効果的でないかも知れない。しかし、トンネル層への制限条件が満たされて居る限り、此処に記述された技術はこのようなメモリ素子の実施に使用可能であろう。

#### 【0054】

具体的な実施例によれば、質量と体積を事実上一定に保つため、メモリ素子の鉛直方向の厚さは水平方向の特徴サイズの二乗に比例して増加される。従って、例えば最小特徴サイズが約6nmであって方向比が約1である場合、ミクロン程度の最小特徴サイズで各々が約8nmの二層G M R フィルムの個々の層の厚さは各々約15nm増加される。別例として、厚さの総合的増加は、個々の層の厚さを約8nmに保持し、単一のG M R フィルムを3周期の複周期構造で置き換えることで実施することが出来る。これら二つの方法は結合して行うことも出来る。具体的な実施例に於いて、これは記憶層および読み出し層は共に別個に熱的不安定に対する脆弱性を有し得るので、これは記憶層と読み出し層の両方に行われる。上記の如く、これは両者間の非磁気層に対して行われてもよい。

10

#### 【0055】

この新しい手法は、更に高密度のシステムの達成の為に、ここに記述されたその他の新たな手法と共に実施されてよいものと留意されるべきものである。別例として、本明細書に記述されたC P P メモリ素子は、本明細書に記述されたその他の技術を使用せずに実施されてもよいものである。

20

#### 【0056】

本発明は明確に理解されるべく詳細に亘って記述されたものであるが、当業者には本発明の意図や範囲から脱却することなく本明細書に記述された実施例の形態とか詳細とかに変更が加えられることが自明であろう。更に、種々の実施例によって本発明の種々なる利点、観点、目的などが記述されてあるが、本発明の範囲とはこれらの利点、観点、目的などによって限定されるものではないと理解されるであろう。むしろ、発明の範囲とは添付された請求項によって決定されるものである。

適用例1：メモリセルの配列から成る記憶装置であって、各メモリセルは、磁気抵抗性を示す第1の多層薄膜記憶素子と、前記第1の多層薄膜記憶素子の上側に配置され、前記第1の多層薄膜記憶素子と電気的に絶縁されている第1の信号線と、前記第1の信号線の上側に配置され、前記第1の薄膜記憶素子および第1の信号線の両方と電気的に絶縁されている第2の信号線と、前記第1の薄膜記憶素子と直接接触する少なくとも一つの非導電性保持素子とを備え、前記第1の薄膜記憶素子と前記保持素子とが完全閉鎖フラクス構造の少なくとも一部を形成する、記憶装置。

30

適用例2：第1の薄膜記憶素子の各々が一つ以上のG M R 素子、M T J 素子、C I P 素子、またはC P P 素子を含む、適用例1に記載の記憶装置。

適用例3：前記配列中の前記メモリセルは複数の列と複数の行に配列され、前記メモリセルの各列内の第1の薄膜記憶素子は第1の連続薄膜構造の一部であり、各メモリセルの第1の信号線はメモリセルの対応する列の第1の連続駆動線の一部であり、各メモリセルの第2の信号線はメモリセルの対応する行の第2の連続駆動線の一部であり、第1の駆動線の一本と第2の駆動線の一本とが各メモリセルで交差し、各々に関連する電流方向が各メモリセルにおいて平行であるように構成されている、適用例1に記載の記憶装置。

40

適用例4：第1の駆動線の各々が蛇行パターンに構成され、隣接するメモリセルの列に対応する第1の駆動線が重なり合う、適用例3に記載の記憶装置。

適用例5：隣接するメモリセルの列に対応する第1の駆動線は、各メモリセルに関連するセル面積が、 $f$  をリソグラフィ印刷の特徴サイズとした場合に  $4f^2$  となるように重なり合う、適用例4に記載の記憶装置。

適用例6：1ビット以上の情報を記憶するように第1の薄膜記憶素子が構成されている、適用例1に記載の記憶装置。

適用例7：各メモリセルは更に、第1の及び第2の信号線の上部に配置され、第1およ

50

び第2の信号線と電気的に絶縁されている第2の多層薄膜記憶素子を備え、前記第2の薄膜記憶素子は完全閉鎖フラクス構造の一部を形成する、適用例1に記載の記憶装置。

適用例8：各列のメモリセル内の第2の薄膜記憶素子が第2の連続薄膜構造の一部であり、メモリセルの各列に関連する第1の及び第2の連続薄膜構造が電気的に並列に接続されている、適用例7に記載の記憶装置。

適用例9：システム記憶装置を含む電子システムであって、前記システム記憶装置が複数の記憶セルを備え、各記憶セルは、磁気抵抗性を示す多層薄膜記憶素子と、前記第1の多層薄膜記憶素子の上側に配置され、前記第1の多層薄膜記憶素子と電気的に絶縁されている第1の信号線と、第1の信号線の上側に配置され、前記第1の薄膜記憶素子と第1の信号線の両方と電気的に絶縁されている第2の信号線と、前記第1の薄膜記憶素子と直接接觸する少なくとも1つの非導電性保持素子とを備え、前記第1の薄膜記憶素子と前記保存素子とが完全閉鎖フラクス構造の少なくとも一部を形成する、電子システム。10

適用例10：システム記憶装置が少なくとも1個の処理装置と関連するキャッシュ記憶装置と長期記憶とを含む記憶階層の一部であり、記憶階層の少なくとも他の一部分が完全閉鎖フラクス構造を持つメモリセルの追加的配列を含むも、適用例9に記載の電子システム。

適用例11：複数の列と複数の行に配列されたメモリセルの配列を備える記憶装置であって、各メモリセルは、磁気トンネル接合型（MTJ）記憶素子と、前記MTJ記憶素子の上部に配置され、前記MTJ記憶素子と電気的に絶縁されている第1の信号線と、前記第1の信号線の上部に配置され、前記MTJ記憶素子と第1の信号線の両方と電気的に絶縁されている第2の信号線とを備え、各メモリセルの前記第1の信号線はメモリセルの対応する列の第1の連続駆動線の一部であり、各メモリセルの前記第2の信号線はメモリセルの対応する行の第2の連続駆動線の一部であり、前記第1の駆動線の一本と第2の駆動線の一本とが各メモリセルで交差し、各々に関連する電流方向が各メモリセルにおいて平行であるように構成されている、記憶装置。20

適用例12：前記第1の駆動線の各々が蛇行パターンに構成され、隣接するメモリセルの列に対応する第1の駆動線が重なり合う、適用例11に記載の記憶装置。

適用例13：複数の列と複数の行に配列されたメモリセルの配列を備える記憶装置であって、各メモリセルは、絶縁体によって隔離された第1と第2の磁気層を有し、各列のメモリセルの第1の磁気層は直列に接続されて第1のセンス線を形成し、各列のメモリセルの第2の磁気層は直列に接続されて第2のセンス線を形成する、磁気トンネル接合型（MTJ）記憶素子と、前記MTJ記憶素子の上部に配置され、前記MTJ記憶素子と電気的に絶縁されている第1の信号線と、前記第1の信号線の上部に配置され、前記MTJ記憶素子と第1の信号線の両方と電気的に絶縁されている第2の信号線と、前記MTJ記憶素子と直接接觸する少なくとも1個の非導電性保持素子とを備え、前記MTJ記憶素子と前記保存素子とが完全閉鎖フラクス構造の少なくとも一部を形成する、記憶装置。30

適用例14：複数のメモリセルから成る記憶装置であって、各メモリセルが磁気抵抗性を示す多層薄膜記憶素子を備え、前記記憶素子は水平幅と鉛直厚さで特徴付けられ、前記記憶素子の鉛直厚さが記憶素子の水平幅に対して前記記憶素子の体積が所定期間記憶素子の磁化状態の熱的安定を確保するのに十分であるように制御される、記憶装置。40

適用例15：各記憶素子が少なくとも1周期の層から成り、各周期の層が高保磁力層、低保磁力層、及び高保磁力層と低保磁力層の間の非磁気層を含み、前記記憶素子の鉛直厚さは高保磁力層、低保磁力層、或は非磁気層の一枚以上の層の厚さを調整することで制御される、適用例14に記載の記憶装置。

適用例16：各記憶素子が複数の周期の層から成り、各周期の層が高保磁力層、低保磁力層、及び高保磁力層と低保磁力層の間の非磁気層を含み、記憶素子の鉛直厚さは層の周期の数で制御される、適用例14に記載の記憶装置。

適用例17：各記憶素子が更に前記薄膜記憶素子と直接接觸する少なくとも1つの非導電性保持素子を備え、前記薄膜記憶素子と前記保存素子とが完全閉鎖フラクス構造の少な50

くとも一部を形成する、適用例 1 4 に記載の記憶装置。

適用例 1 8 : 複数のメモリが複数の列と複数の行から成る配列に整列され、各メモリセルは更に薄膜記憶素子の上側に配置され前記薄膜記憶素子と電気的に絶縁されたている第 1 の信号線と第 1 の信号線の上側に配置され、前記薄膜記憶素子と第 1 の信号線の両方と電気的に絶縁されている第 2 の信号線とを備え、各メモリセルの第 1 の信号線はメモリセルの対応する列の第 1 の連続駆動線の一部であり、各メモリセルの第 2 の信号線はメモリセルの対応する行の第 2 の連続駆動線の一部であり、第 1 の駆動線の一本と第 2 の駆動線の一本とが各メモリセルで交差し、各々に関連する電流方向が各メモリセルにおいて平行であるように構成されている、適用例 1 4 に記載の記憶装置。

適用例 1 9 : 第 1 の駆動線の各々が蛇行パターンに構成され、隣接するメモリセルの列に対応する第 1 の駆動線が重なり合う、適用例 1 4 に記載の記憶装置。 10

適用例 2 0 : 複数のメモリセルを形成する工程を備える記憶装置の製造方法であって、各メモリセルは磁気抵抗性を示す多層薄膜記憶素子を備え、前記記憶素子は水平幅と鉛直厚さで特徴付けられ、前記複数のメモリセルを形成する工程は、記憶素子の鉛直厚さが記憶素子の水平幅に対し、記憶素子の体積が所定期間、記憶素子の磁化状態の熱的安定を確保するのに十分であるように制御する工程を備える、方法。

適用例 2 1 : 磁気抵抗性を示す第 1 の多層薄膜記憶素子と、前記第 1 の多層薄膜記憶素子の上側に配置され、前記第 1 の多層薄膜記憶素子と電気的に絶縁されている第 1 の信号線と、第 1 の信号線の上側に配置され、前記第 1 の薄膜記憶素子と第 1 の信号線の両方と電気的に絶縁されている第 2 の信号線と、前記第 1 の薄膜記憶素子と直接接触する少なくとも 1 つの非導電性保持素子とを備え、前記第 1 の薄膜記憶素子と前記保存素子とが完全閉鎖 フラクス構造の少なくとも一部を形成する、メモリセル。 20

適用例 2 2 : 前記第 1 の薄膜記憶素子の各々が一個以上の G M R 素子、M T J 素子、C I P 素子、または C P P 素子を含む、適用例 2 1 に記載のメモリセル。

適用例 2 3 : 前記第 1 の信号線と第 2 の信号線は、各々に関連する電流方向が平行するように構成されている、適用例 2 1 に記載のメモリセル。

適用例 2 4 : 1 ビット以上の情報を記憶するように前記第 1 の薄膜記憶素子が構成されている、適用例 2 1 に記載のメモリセル。

適用例 2 5 : 前記第 1 の及び第 2 の信号線の上部に配置され、前記第 1 および第 2 の信号線と電気的に絶縁されている第 2 の多層薄膜記憶素子を更に備え、前記第 2 の薄膜記憶素子が完全閉鎖 フラクス構造の一部を形成する、適用例 2 1 に記載のメモリセル。 30

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図1】

FIG. 1

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図 10】

*FIG. 10*

【図 11】

(a)

(b)

FIG. 11

【図12】

(a)

(b)

FIG. 12

【図13】

**FIG. 13**

【図14】

**FIG. 14**

【図15】

**FIG. 15**

【図16】

FIG. 16

---

フロントページの続き

(31)優先権主張番号 61/012,106

(32)優先日 平成19年12月7日(2007.12.7)

(33)優先権主張国 米国(US)

(31)優先権主張番号 12/120,549

(32)優先日 平成20年5月14日(2008.5.14)

(33)優先権主張国 米国(US)

(72)発明者 フレミング・デビッド・レスリー

アメリカ合衆国 ミネソタ州 55345 ミネトンカ, ウィリストン・ロード, 5325

(72)発明者 ワーリ・エドワード

アメリカ合衆国 ミネソタ州 55112 セント・ポール, セント・スティーブン・ストリート,

5613

(72)発明者 スピッツァー・リチャード

アメリカ合衆国 カリフォルニア州 94709 パークレー, オックスフォード・ストリート, 1

214

審査官 境 周一

(56)参考文献 特開2001-273759(JP,A)

特開2003-289135(JP,A)

特開2003-258209(JP,A)

特開平11-176149(JP,A)

特開2005-044847(JP,A)

特開平10-302456(JP,A)

特開2002-289807(JP,A)

特開2003-283001(JP,A)

特開2004-200459(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/10 - 27/118

H01L 29/82

G11C 11/00 - 11/16

H01L 43/00 - 43/14