(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4646917号

(P4646917)

(45) 発行日 平成23年3月9日(2011.3.9)

(24) 登録日 平成22年12月17日(2010.12.17)

(51) Int.Cl.

H02M 3/28 (2006.01)

F 1

H02M 3/28

B

請求項の数 5 (全 10 頁)

(21) 出願番号 特願2006-535521 (P2006-535521)

(86) (22) 出願日 平成16年9月30日 (2004.9.30)

(65) 公表番号 特表2007-508800 (P2007-508800A)

(43) 公表日 平成19年4月5日 (2007.4.5)

(86) 國際出願番号 PCT/US2004/031994

(87) 國際公開番号 WO2005/038548

(87) 國際公開日 平成17年4月28日 (2005.4.28)

審査請求日 平成19年8月27日 (2007.8.27)

(31) 優先権主張番号 10/685,094

(32) 優先日 平成15年10月14日 (2003.10.14)

(33) 優先権主張国 米国(US)

(73) 特許権者 300057230

セミコンダクター・コンポーネンツ・イン

ダストリーズ・リミテッド・ライアビリテ

ィ・カンパニー

アメリカ合衆国 アリゾナ州 85008

フェニックス イースト・マクドウェル

・ロード50005

(74) 代理人 100091915

弁理士 本城 雅則

(74) 代理人 100099106

弁理士 本城 吉子

(72) 発明者 サカッブ、フランティセク

チェコ共和国 75661 ロズノフ ピ

ー・アール ザソバ715

最終頁に続く

(54) 【発明の名称】電源制御システムのスタートアップ方法および回路

## (57) 【特許請求の範囲】

## 【請求項 1】

スタートアップ回路(10)の出力(36)に出力電圧を生成するための電源制御システムのスタートアップ方法において、

入力電圧(22)を受け取り、これに応答してバイアス電流(14)を生成し、かつ、前記バイアス電流を高電圧装置(16)の出力トランジスタ(12)に結合するために、前記高電圧装置(16)を結合する段階と、

前記出力電圧(36)が第1値よりも小さいときに、前記バイアス電流を前記出力トランジスタ(12)から前記高電圧装置の出力に切り換えるためにスイッチ要素(17)を結合する段階であって、前記バイアス電流は、前記高電圧装置の前記出力において前記出力電圧を形成するために用いられる、段階と、

前記出力電圧が前記第1値よりも大きいときに、前記バイアス電流を前記出力トランジスタの制御電極に結合するために前記高電圧装置を結合し、前記バイアス電流よりも大きい出力電流を生成する段階と、

から構成されることを特徴とする電源制御システムのスタートアップ方法。

## 【請求項 2】

入力電圧を受け取り、これに応答してバイアス電流を生成し、かつ、前記バイアス電流を高電圧装置の出力トランジスタに結合するために、前記高電圧装置を結合する前記段階は、前記入力電圧を受け取るためにJ-FETトランジスタ(14)の第1電流輸送電極を結合する段階、前記J-FETトランジスタの第2電流輸送電極を前記出力トランジス

タ(12)の第1電流輸送電極に結合する段階、および、前記J-FETトランジスタの前記第2電流輸送電極から電流を受け取るために抵抗(13)を結合し、かつ、前記バイアス電流を前記出力トランジスタの制御電極に結合する段階を含むことを特徴とする請求項1記載の方法。

**【請求項3】**

入力電圧(22)を受け取る段階と、

前記入力電圧から第1電流(14)を生成する段階と、

前記第1電流をスタートアップ回路(10)の出力(36)へ切り換える段階と、

前記スタートアップ回路の出力で出力電圧を生成するために前記第1電流を使用する段階と、

前記出力電圧が第1値より大きくなった後に、前記出力電圧を生成するために前記第1電流よりも大きい第2電流(12)を出力トランジスタの出力から前記スタートアップ回路の出力に結合する段階と、

から構成されることを特徴とする電源制御システムのスタートアップ方法。

**【請求項4】**

前記第1電流をスタートアップ回路の出力へ切り換える前記段階は、ピンチ抵抗(17)をイネーブルにして前記第1電流を前記出力に結合する段階を含むことを特徴とする請求項3記載の方法。

**【請求項5】**

電圧入力(22)と電圧リターン(38)との間で入力電圧を受けるためのスタートアップ回路(10)を構成する段階と、

前記スタートアップ回路(10)の出力(36)における第1値の出力電圧に応答して前記スタートアップ回路(10)の出力(36)で第1出力電流を生成する段階であって、前記第1出力電流は、前記スタートアップ回路の前記出力において前記出力電圧を形成するために用いられる、段階と、

前記スタートアップ回路の出力(36)を前記電圧リターン(38)に結合して前記第1出力電流を前記電圧リターンに切り換え、前記出力電圧を前記第1値未満に減じ、それにより前記スタートアップ回路の動作を抑止し、かつ前記第1出力電流の値を減じる段階と、

から構成されることを特徴とする電源制御システム方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、一般に、電子装置に関し、より詳しくは、半導体装置および構造を形成する方法に関する。

**【背景技術】**

**【0002】**

過去において、電子産業は、制御された出力電圧および電流の提供を目的として、高値または大きな入力電圧を制御するための多様な方法および装置を用いた。かかる装置の一例が、オンライン・ブートストラップ・スタートアップ回路と称されるもので、1995年12月19日にTisinger他に対して特許された米国特許番号5,477,175に開示されており、それは、参照としてここに組込まれる。ブートストラップ・スタートアップ回路は、大きな入力電圧を受け取り、キャパシタを充電する出力電流を生成し、そして出力電圧を生成する。多くのアプリケーションは、キャパシタの充電および出力電圧の生成を制御することができるような電流のシーケンスを要求する。しかしながら、複数のブートストラップ・スタートアップ回路を使用すると、その結果生じた半導体製品、さらにその半導体製品を使用したアプリケーションが複雑になり、製造コストも増大する。

**【0003】**

従って、高電圧値を有する入力電圧を受け取り、入力電圧から電流のシーケンスを生成

10

20

30

40

50

することができるようなスタートアップ回路が望まれる。

**【0004】**

説明を単純かつ明瞭にするために、図中の要素は必ずしも同じ寸法ではなく、また、異なる図中の同一の参照番号は同一の要素を示す。さらに、周知のステップおよび要素についての記述および詳細は、記述を単純化するために省略される。ここで用いられる電流輸送電極は、MOSトランジスタのソースまたはドレイン、またはバイポーラ・トランジスタのエミッタまたはコレクタのような装置を通って電流を輸送する装置の要素を意味し、また、制御電極は、MOSトランジスタのゲートまたはバイポーラ・トランジスタのベースのような装置を通って電流を制御する装置の要素を意味する。

**【発明の開示】**

10

**【0005】**

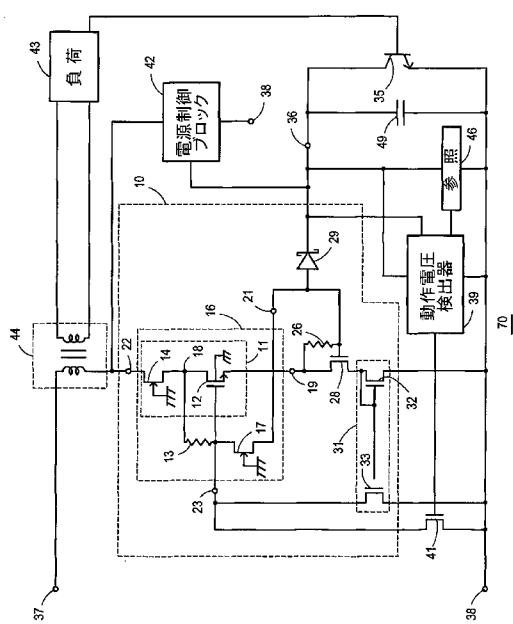

図1は、デュアル動作モードを有し、かつ、単一の高電圧入力から複数の出力電流を生成することができる、高電圧スタートアップ回路10の一部分の実施例を概略的に示した図である。回路10は一般に電源制御システム70の一部であり、システム70のスタートアップ・シーケンスを制御するために使用される。回路10は、高電圧電流制御装置16を含み、それは高電圧電流制御要素11を含み、それはさらに高電圧J-FETトランジスタ14およびMOSトランジスタ12を含んで形成される。回路10、装置16、および要素11は、点線の枠によって一般的に示される。装置16は、さらにピンチ抵抗17、およびトランジスタ12のゲートにバイアス電流を提供するために形成されるバイアス抵抗13を含む。装置16は、高電圧入力22で高電圧を受け取り、かつ制御入力23に与えられた制御信号に応答して出力19で出力電流を生成するために形成される。装置16は、さらに、以下で述べられように抵抗17を通して、バイアス電流として、別の出力電流を生成する。

20

**【0006】**

かかる機能性を提供するために、トランジスタ14のドレインは入力22に接続され、また、ソースは共通ノード18に接続される。トランジスタ12のドレインは、トランジスタ14のソースおよびノード18に接続される。トランジスタ12のゲートは、入力23および抵抗13の第1端子に接続され、また、ソースは出力19に接続される。抵抗13の第2端子は、トランジスタ14のソースおよびトランジスタ12のドレインに接続される。トランジスタ14は、トランジスタのゲートとして使用される基板を有するJ-FETトランジスタとして形成され、したがって、トランジスタ14のゲート接続はボディに接続されて示される。典型的には、基板とボディはシステム内の最も負の電位に接続される。抵抗17は、基板に接続されたゲートを有する低いピンチオフ電圧のJ-FETとして形成される。抵抗17の第1端子はトランジスタ12のゲートに接続され、および、第2端子は装置16の出力21に接続される。抵抗17の第1端子はJ-FETの等価ドレインであり、また、第2端子は等価ソースである。出力21は、ダイオード29を経由して回路10の出力36に接続される。好適な実施例では、トランジスタ12はNチャネルMOSトランジスタであり、トランジスタ14はNチャネルJ-FETトランジスタであり、また、ピンチ抵抗17は、基板によって形成されたゲートおよび被覆されたP形領域を有し、その両方が基板に接続されたNチャネルJ-FETとして形成される。他の実施例では、トランジスタ12は、J-FETまたはバイポーラ・トランジスタのような他のトランジスタ構造であってもよい。

30

**【0007】**

抵抗17およびトランジスタ12, 14の降伏電圧は、アプリケーションおよび多様な他の要因に依存する。世界的な線間電圧アプリケーションのある実施例において、基板に関するトランジスタ14のドレインの降伏電圧は400ボルト(400V)を超えることがある、また、トランジスタ12のソースにおける持続可能な電圧は50ボルト(50V)を超えることがある。

40

**【0008】**

入力22に印加された電圧がトランジスタ14のピンチオフ電圧よりも小さいとき、出

50

力 19 はノード 18 に印加された電圧に従う。入力 22 で印加された電圧がトランジスタ 14 のピンチオフ電圧よりも大きいとき、トランジスタ 14 はドレイン電流の飽和モードでオンになり、また、装置 16 の出力は、入力 23 を制御するために印加された電圧によって制御される。外部電圧が入力 23 に印加されない場合、例えば入力 23 が浮遊している場合、抵抗 13 はトランジスタ 14 からゲートのバイアス電流を供給し、装置 16 およびトランジスタ 12 の両方をイネーブルにし、出力 19 で出力電流を生成する。動作回路において、外部制御電圧は、典型的には入力 23 に印加され、出力電流値を制御する。入力 23 に印加された電圧がトランジスタ 12 のスレショルド電圧よりも小さいゲート対ソース電圧を生成するとき、トランジスタ 12 は典型的にはディセーブルになる。

## 【 0 0 0 9 】

10

スタートアップ回路 10 は、回路 10 の高電圧スタートアップ・シーケンス、および電源制御システム 70 のスタートアップ・シーケンスを制御するために装置 16 を使用する。回路 10 は、電圧入力 37 と電圧リターン 38 との間で入力電圧を受け取る。フィルタ・キャパシタ 49、動作電圧検出器 39、参照 46、ディセーブル・トランジスタ 41、トランスフォーマ 44、電源制御ブロック 42、抑止トランジスタ 35、および負荷 43 のような電源制御システムの他の要素は、所望の電源制御機能を提供するために、典型的には回路 10 と外部的に接続される。キャパシタ 49、検出器 39、トランジスタ 41、参照 46、トランスフォーマ 44、電源制御ブロック 42、および負荷 43 は、装置 16 および回路 10 の動作についての記述をわかりやすくするために示される。当業者は、完全な電源制御システムを形成するためには、図 1 に典型例として示されない他の周知の要素および機能が含まれることを理解するであろう。ほとんどの実施例では、キャパシタ 49、トランスフォーマ 44、電源制御ブロック 42、および負荷 43 は、装置 16 および回路 10 が形成される半導体ダイの外部にある。いくつかの実施例においては、ブロック 42 の一部または全部が、装置 16 および回路 10 が形成される半導体ダイの他の部分にある。

20

## 【 0 0 1 0 】

参照 46 は、参照 46 の出力に参照電圧を提供する。参照電圧は、動作電圧値を検出するための検出レベルを設定するために検出器 39 によって使用される。検出器 39 は、出力 36 で参照電圧および出力電圧を受け取り、かつ、出力電圧が所望の動作電圧値と同等または大きいときに、これに応答して装置 16 をディセーブルにするために形成される。好適な実施例では、検出器 39 はヒステリシスを有し、出力電圧が所望の動作電圧値付近でわずかに変化するときに、検出器 39 がオンまたはオフに切り替わることを防止する。

30

## 【 0 0 1 1 】

装置 16 および回路 10 は初期電流を提供するために用いられるが、この初期電流は小さく、かつ、電源制御システムに電力が供給されたときにキャパシタ 49 を充電するために使用される。出力 36 の電圧が初期電圧に達した後、装置 16 は大きな出力電流を供給し、動作電圧までキャパシタ 49 を充電する。回路 10 は、大きな出力電流の値を制御し、制御電流を生成する。初期電圧の値は、典型的には動作電圧の値よりも非常に小さい。初期電圧値は、通常できるだけ低く選択されるので、キャパシタ 49 をできるだけ早く初期値まで充電し、スタートアップ・システム 70 に要求される時間を最小限にすることができる。動作電圧値は、典型的には、負荷 43 のような回路 10 の外部にある他の回路に通常動作を提供するような値になるように選択される。

40

## 【 0 0 1 2 】

入力 37 に電力が供給される前は、キャパシタ 49 は放電され、また、出力 36 は 0 ボルトである。従って、回路 10 は動作しておらず、また、装置 16 からの出力電流は無い。入力電圧が入力 37 に印加されたとき、電流は、トランスフォーマ 44 を通って装置 16 の入力 22 へ流れ始める。入力 22 の電圧が増加するにつれて、トランジスタ 14 がオンになり、抵抗 13 を通ってトランジスタ 12 のゲートにバイアス電流を供給する。抵抗 17 は、ダイオード 29 を経由して出力 36 に接続され、かつ、抵抗 13 のサイズに対して適切に設計されており、また、キャパシタ 49 が放電されるので、抵抗 17 は入力 23

50

を低に引き下げる、トランジスタ 12 をディセーブルにする。抵抗 13 からのバイアス電流は、初期電流として抵抗 17 を通って出力 36 へ流れ、キャパシタ 49 の充電を開始し、したがって、抵抗 17 はトランジスタ 12 をディセーブルにし続け、また、装置 16 の出力 19 からの電流の流れは無い。出力 36 の出力電圧は動作電圧よりも小さいので、検出器 39 の出力は低く、また、トランジスタ 41 はディセーブルになる。抵抗 17 はピンチ抵抗であり、ゲートが最低の電位に接続されるので、抵抗 17 を通る電流の流れはソースまたは出力 36 に接続された端子の電位に依存する。抵抗 13 からのバイアス電流が初期電流として抵抗 17 を通って流れ、キャパシタ 49 を充電するにつれて、出力 36 の電圧は増加し、これに対応するような減少が抵抗 17 を通って流れる電流に生じる。出力 36 の電圧が抵抗 17 のピンチオフ電圧に達したとき、抵抗 17 を通る電流経路が遮断され、10 抵抗 17 は導通を止める。抵抗 13 からのバイアス電流は、ここでトランジスタ 12 をイネーブルにし、それが出力 19 で出力電流を生成する。従って、トランジスタ 12 は、回路 10 の出力トランジスタとみなすことができる。トランジスタ 12 は、キャパシタ 49 を動作電圧値まで素早く充電するために、抵抗 17 によって供給することができる初期電流よりも大きい電流を提供するように形成される。典型的には、トランジスタ 12 は、抵抗 17 の電流の約 30 倍から 2000 倍の間の電流を供給するように形成される。抵抗 17 のピンチオフ電圧からトランジスタ 12 のスレショルド電圧を引いた電圧によって、初期電圧値が設定されると理解することができる。ある実施例において、ピンチオフ電圧は、約 3 ボルト (3.0 V) に設計され、対応する初期電圧値は約 1.2 ボルトであった。

## 【0013】

20

一旦トランジスタ 12 がイネーブルになると、回路 10 はトランジスタ 12 からの出力電流を制御して、出力 36 に制御電流を供給する。制御された出力電流はキャパシタ 49 の充電を開始する。装置 16 の出力電流を制御するために、回路 10 は電流制御ループを有し、それには、センス抵抗 26、センス・トランジスタ 28、および参照トランジスタ 32 およびミラー・トランジスタ 33 を含む電流ミラー 31 が含まれる。出力 19 で生成された出力電流は、電流制御ループによって制御される。出力 19 の電流は抵抗 26 を通って流れ、抵抗 26 の両端で対応する電圧降下を生成する。抵抗 26 はトランジスタ 28 のゲートおよびソース間に接続され、トランジスタ 28 のゲート対ソース電圧を形成し、したがって、抵抗 26 の両端の電圧降下によって、トランジスタ 28 を介してセンス電流の流れが確立される。電流ミラー 31 は、トランジスタ 28 からセンス電流を受け取り、これに応答して制御入力 23 に印加される電圧を制御し、これによってトランジスタ 12 のゲート電圧、ならびに要素 11 および装置 16 の出力電流値を制御する。出力 19 の出力電流が増加するにつれて、センス電流はこれに対応して増加し、これに応答してトランジスタ 28 のゲート電圧、およびこれに応答して入力 23 の制御電圧を低下させ、出力電流値を減少させる。当業者は、トランジスタ 28, 32, 33 もまたバイポーラ・トランジスタであってもよいことを理解するであろう。2つの電流制御ループは、いくつかの実施例では省略されてもよい。30

## 【0014】

30

制御出力電流によってキャパシタ 49 が動作電圧値まで充電されたとき、検出器 39 の出力は高値に切り替わり、これによって、トランジスタ 41 がイネーブルになり、装置 16 のトランジスタ 12 がディセーブルになる。トランジスタ 41 は、抵抗 13 からバイアス電流を引き込む。抵抗 13 の値は、トランジスタ 41 がバイアス電流を引き込むときに電力消散が最小限になり、かつ、抵抗 17 が所望の時間内にキャパシタ 49 を充電するのに十分な電流を供給できることを保障するように設計される。ダイオード 29 は、トランジスタ 41 がイネーブルである間、電流が出力 36 からリターン 38 へ逆流するのを妨げる。好適な実施例では、検出器 39 はヒステリシスを有し、動作電圧値付近での出力電圧のわずかな変化に伴って、検出器 39 がオンまたはオフに切り替わるのを防止する。ヒステリシス入力により、出力電圧が、動作電圧値から検出器 39 のヒステリシス・オフセット電圧を引いた電圧とほぼ等しい値まで減少したとき、検出器 39 はトランジスタ 12 および装置 16 を再度イネーブルにする。40

50

## 【0015】

回路10の動作中に、回路10を抑止することが適切な場合がある。例えば、負荷43が、回路10をディセーブルにすることを要求する条件を検出することがある。かかる場合には、負荷43または他の回路(図示せず)がトランジスタ35をイネーブルにし、出力36を低に引き下げて回路10の動作を抑止することができる。出力36を低に引き下げるこによって、キャパシタ49が放電される。キャパシタ49が、検出器39のヒステリシス・オフセットよりも小さい値まで放電されたとき、検出器39の出力は低になってトランジスタ41をディセーブルにし、これによって、抵抗13がトランジスタ12へ電流を供給することを許容し、トランジスタ12をイネーブルにして出力電流を生成する。トランジスタ35は、制御出力電流を引き込み、キャパシタ49を放電し続ける。キャパシタ49が初期電圧値よりも小さい値まで放電されたとき、抵抗17は、初期電流として抵抗13からのバイアス電流をトランジスタ35へ流す。トランジスタ35は初期電流を引き込み、トランジスタ12をディセーブルにして回路10を抑止する。抑止機能が適切に動作することを保証するために、初期電圧はトランジスタ35の飽和電圧よりも大きくなければならない。トランジスタ12は最早出力電流を供給しないので、トランジスタ35のみが、出力電流ではなくバイアス電流を引き込まなければならない。回路10を抑止することによって、通常は電源制御ブロック42内の電源供給制御装置の動作もまた抑止される。通常は、かかる動作を促進するために、出力36と電源供給制御装置との間に接続が設けられる。バイアス電流は出力電流と比較して小さく、一般的には約30倍から2000倍、好ましくは約50倍小さいので、電力放散は最小限になり、スタートアップ回路は抑止され、また、装置16はバイアス電流とほぼ等しいスタンバイ電流を供給する。したがって、この方法は、スタンバイ電流を維持する一方で回路10の動作を抑止するための容易な方法を提供し、また、負荷43がトランジスタ35をディセーブルにするときにキャパシタ49を容易に再充電することができる方法を提供する。システム70が抑止される間、電力放散量を最小限にすることは重要である。バイアス電流、したがって初期電流が低い電流であるために、システム70を抑止する当該方法は、入力37に印加された電圧から放散される電力量を最小限にする。典型的には、バイアス電流の値は、商標「ENERGY STAR(登録商標)として知られる基準のような認可基準で指定されたスタンバイ電流よりも小さくなるように選択される。装置16およびトランジスタ35は、システム70の抑止回路を形成すると理解することができる。さらに、検出器39は、装置16のような他の制御シーケンスを使用して、初期電圧値を検出した後に出力電流だけを供給することも可能であり、あるいは、シーケンスを逆にして、初期電圧値を検出する前に出力電流を供給すること、また、初期電圧値を検出した後にバイアス電流を供給すること等も可能である。

## 【0016】

トランジスタ35は、動作シーケンスにおいて何時でもイネーブルになり、また、抑止機能は、その時に存在する出力電圧および電流の値で開始できることを、当業者は理解するであろう。

## 【0017】

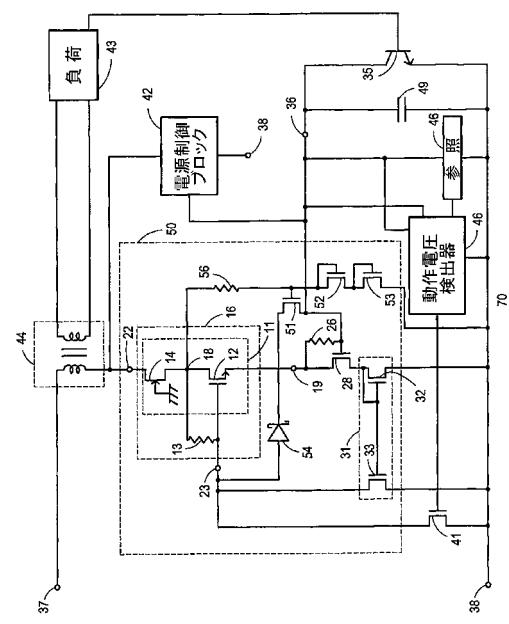

図2は、図1に関して記述された回路10の他の実施例である高電圧スタートアップ回路50の一部の実施例を概略的に図示する。回路50は、点線の枠によって一般的な方法で示される。回路50は、初期電流を供給するために使用されるトランジスタ51に結合された比較器を含み、出力電圧が初期電圧よりも小さいときにトランジスタ12をディセーブルにし、出力電圧が初期電圧値に達する前に装置16をイネーブルにする。トランジスタ51のドレインは、ダイオード54を通じて装置16の入力23に接続される。トランジスタ51のソースは出力36に接続されて出力電圧を受け取り、また、ゲートはトランジスタ52のドレインおよびゲートの両方に接続されてトランジスタ52,53から参照電圧を受け取る。ゲート・バイアス抵抗56の第1端子はトランジスタ51のゲートに接続され、また、第2端子はノード18に接続される。トランジスタ52のソースは、トランジスタ53のゲートおよびドレインの両方に接続される。トランジスタ53のソース

10

20

30

40

50

は、リターン38に接続される。

**【0018】**

トランジスタ52,53は直列に接続され、トランジスタ52のドレインで固定参照電圧を提供するために調整されたスレショルド電圧を有するように形成される。抵抗56は、所望の参照電圧でトランジスタ52,53にバイアスを与るためにバイアス電流を提供する。好適な実施例では、トランジスタ52,53の各スレショルドは、それぞれ約2.3ボルトに調整され、また、その結果生じる参照電圧は約4.6ボルトである。回路10の動作と同様に、電力が入力37に与えられたとき、キャパシタ49が放電され、出力36は0ボルトになる。トランジスタ14がオンになり、抵抗13がバイアス電流をトランジスタ12に供給するとき、トランジスタ51のソースは低になり、また、ゲートは参考電圧まで充電され、したがって、トランジスタ51はイネーブルになる。トランジスタ51は、トランジスタ12のゲートを放電されたキャパシタ49の低電圧まで引き下げ、それによってトランジスタ12をディセーブルにする。トランジスタ51は、さらに、初期電流としてバイアス電流を出力36へ流し、それによって、トランジスタ12がディセーブルのままで維持され、かつキャパシタ49の充電の開始が保証される。出力36の出力電圧は動作電圧よりも小さいので、検出器39の出力は低く、また、トランジスタ41はディセーブルになる。トランジスタ51からの初期電流がキャパシタ49を充電するにつれて、トランジスタ51のソース電圧は増加し、これに対応してゲート対ソース電圧が減少し、それによってトランジスタ51を通る電流が減少する。出力36の電圧が、トランジスタ51のゲートに印加された参考電圧からトランジスタ51のスレショルド電圧を引いた電圧とほぼ等しい値に達したとき、トランジスタ51を通る電流経路は遮断され、そしてトランジスタ51は導通を止める。抵抗13からのバイアス電流はトランジスタ12をイネーブルにし、それによって出力19で第2出力電流が生成される。ダイオード54は、トランジスタ51のドレインがソースよりも低電圧にある場合、例えばトランジスタ41がトランジスタ12をディセーブルするような場合に、電流がトランジスタ51の真性ボディ・ダイオードを通って入力23へ逆流するのを防止する。参考電圧からトランジスタ51のスレショルド電圧を引いた電圧で初期電圧値が設定されると理解することができる。一旦トランジスタ12がイネーブルになれば、回路10は、トランジスタ12からの出力電流を制御し、制御電流を出力36に供給する。

**【0019】**

トランジスタ35がイネーブルになって出力36が低に引き下げられることにより、キャパシタ49が放電する。キャパシタ49が、検出器39のヒステリシス・オフセットよりも小さい値まで放電されたとき、検出器39の出力はトランジスタ12をイネーブルにし、出力電流を生成する。トランジスタ35は出力電流を引き込み、キャパシタ49を放電し続ける。キャパシタ49が初期電圧値よりも小さい値まで放電されたとき、トランジスタ51は、初期電流として抵抗13からトランジスタ35へバイアス電流を流す。トランジスタ35は初期電流を引き込み、それによってトランジスタ12がディセーブルになる。

**【0020】**

図3は、図1の装置16および回路10を含む半導体デバイス60の拡大平面図を示す。装置60は半導体ダイ61上に形成される。

**【0021】**

上記の全てより、新規な装置、その装置を形成する方法、およびその装置を使用する方法が示されたことは明白である。他の機能のうち、スタートアップ装置の出力を低電圧に引き下げるこことによって電源制御システムの動作を抑止する機能も含まれる。出力の低電圧によって、スタートアップ装置は電流の充電をディセーブルにし、電源制御システムの動作を抑止する。

**【図面の簡単な説明】**

**【0022】**

【図1】本発明に従って高電圧スタートアップ回路を含む電源制御システムの一部の実施

10

20

30

40

50

例を概略的に図示する。

【図2】本発明に従って図1の電源制御システムおよび高電圧スタートアップ回路の他の実施例を概略的に図示する。

【図3】本発明に従って図1の高電圧スタートアップ回路を含む半導体デバイスの拡大平面図を示す。

【図1】

【図2】

【図3】

---

フロントページの続き

(72)発明者 ハラミク , ヨセフ

チェコ共和国 75661 ロズノフ ピー・アール ハゾピーク2806

(72)発明者 ホール , ジェファーソン , ダブリュー

アメリカ合衆国 アリゾナ州 85249 チャンドラー サウス・モンテ・ビスタ・ストリート

5110

審査官 今井 貞雄

(56)参考文献 特開平10-243555(JP,A)

特開2000-023461(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/28