(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2015-0009592

(43) 공개일자 2015년01월26일

(51) 국제특허분류(Int. Cl.)

*H01Q 1/38* (2015.01) *H01Q 1/52* (2006.01)

*H01Q 13/08* (2006.01)

(21) 출원번호 10-2014-7035044

(22) 출원일자(국제) 2013년05월06일

심사청구일자 없음

(85) 번역문제출일자 2014년12월12일

(86) 국제출원번호 PCT/EP2013/059394

(87) 국제공개번호 WO 2013/171087

국제공개일자 2013년11월21일

(30) 우선권주장

1254368 2012년05월14일 프랑스(FR)

(71) 출원인

톰슨 라이센싱

프랑스 92130 이씨레물리노 잔 다르크 뤼 1-5

(72) 발명자

로인 똥, 도미니끄

프랑스 에프-35576 쎄송 쎄비네 쎄에스 176 16

자크 데 양 블랑 아브뉘 데 양 블랑 975 때끄니꼴

로르 에르 에 데 프랑스

미나르, 필립쁘

프랑스 에프-35576 쎄송 쎄비네 쎄에스 176 16

자크 데 양 블랑 아브뉘 데 양 블랑 975 때끄니꼴

로르 에르 에 데 프랑스

로베르, 장-뤽

프랑스 35830 베똥 뤼 뿔 고갱 2

(74) 대리인

양영준, 전경석, 백만기

전체 청구항 수 : 총 11 항

(54) 발명의 명칭 다층 기판 상에 슬롯 라인을 생성하는 방법 및 상기 방법에 따라 구현되고 분리 슬롯 또는 안테나로서 이용되는 적어도 하나의 슬롯 라인을 포함하는 다층 인쇄 회로

### (57) 요 약

본 발명은 적어도 제1 도전층, 유전체층 및 제2 도전층을 포함하는 다층 기판 상에 단락 슬롯 라인(short-circuited slot-line)을 구현하기 위한 방법에 관한 것으로, 본 발명은 다음 단계들, 제1 도전층에 전기적 길이(L)를 갖는 슬롯 라인(2)을 에칭(etching)하는 단계, 제1 도전층에 슬롯 라인 주위에 전기적 길이(L1)(여기서,  $L1 \leq L$ )를 갖는 제1 벤드의 제1 부분(5a)을 에칭하는 단계, 제1 도전층에 슬롯 라인 주위에 전기적 길이(L2)(여기서,  $L2 \leq L$ )를 갖는 상기 제1 벤드의 제2 부분(5b)을 에칭하는 단계, 제2 도전층에 전기적 길이(L3)를 갖는 루프의 형태로 제2 벤드(7)를 에칭하는 단계를 포함하고, 제2 벤드의 한 단부(8a)는 제1 벤드의 제1 부분에 연결되고 제2 벤드의 다른 단부(8b)는 제1 벤드의 제2 부분에 연결되어 도전 루프를 형성한다. 본 방법은 특히 분리 슬롯 라인들 및 슬롯-안테나를 구현하는 데 이용된다.

### 대 표 도 - 도4

## 특허청구의 범위

### 청구항 1

적어도 제1 도전층, 유전체층 및 제2 도전층을 포함하는 인쇄 회로의 다층 기판에 단락 슬롯 라인(short-circuited slot-line)을 구현하기 위한 방법으로서,

상기 제1 도전층에, 전기적 길이(L)를 갖는 슬롯 라인(2, 101)을 에칭(etching)하는 단계;

상기 제1 도전층에, 슬롯 라인의 한 측면을 따라, 전기적 길이(L1)(여기서,  $L1 \leq L$ )를 갖는 제1 도전 밴드의 제1 부분(5a, 103a)을 에칭하는 단계;

상기 제1 도전층에, 상기 슬롯 라인의 또 다른 측면을 따라 전기적 길이(L2)(여기서,  $L2 \leq L$ )를 갖는 상기 제1 도전 밴드의 제2 부분(5b, 103b)을 에칭하는 단계; 및

상기 제2 도전층에, 전기적 길이(L3)를 갖는 루프의 형태로 제2 도전 밴드(7, 106)를 에칭하는 단계를 포함하고,

상기 제2 도전 밴드의 한 단부(8a, 108a)는 상기 제1 도전 밴드의 제1 부분에 연결되고, 상기 제2 도전 밴드의 다른 단부(8b, 108b)는 상기 제1 도전 밴드의 상기 제2 부분에 연결되어 도전 루프를 형성하는 슬롯 라인 구현 방법.

### 청구항 2

제1항에 있어서,

상기 슬롯 라인은 전기적 길이( $L < 90^\circ$ )의 라인인 것을 특징으로 하는 슬롯 라인 구현 방법.

### 청구항 3

제2항에 있어서,

상기 슬롯 라인은 전기적 길이( $L=45^\circ$ )를 갖는 것을 특징으로 하는 슬롯 라인 구현 방법.

### 청구항 4

제1항 내지 제3항 중 어느 한 항에 있어서,

상기 제1 도전 밴드의 상기 제1 및 제2 부분들의 전기적 길이들(L1, L2)은 동일한 것을 특징으로 하는 슬롯 라인 구현 방법.

### 청구항 5

제4항에 있어서,

상기 제1 도전 밴드의 상기 제1 및 제2 부분들의 전기적 길이들은  $45^\circ$  와 동일한 것을 특징으로 하는 슬롯 라인 구현 방법.

### 청구항 6

제1항 내지 제5항 중 어느 한 항에 있어서,

상기 제2 도전 밴드의 전기적 길이(L3)가 상기 제1 도전 밴드의 제1 및 제2 부분들의 전기적 길이들(L1, L2)의 합과 실질적으로 동일한 것을 특징으로 하는 슬롯 라인 구현 방법.

### 청구항 7

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 전기적 길이들의 합( $L3 + L1 + L2$ )은 실질적으로  $180^\circ$  와 동일한 것을 특징으로 하는 슬롯 라인 구현

방법.

### 청구항 8

제1항 내지 제7항 중 어느 한 항에 따라 구현된 적어도 하나의 슬롯 라인을 포함하는 것을 특징으로 하는 다층 인쇄 회로.

### 청구항 9

제8항에 있어서,

상기 슬롯 라인은 분리 슬롯(20)인 것을 특징으로 하는 인쇄 회로.

### 청구항 10

제8항에 있어서,

상기 슬롯 라인은 슬롯-안테나(101)를 형성하고, 상기 슬롯 라인은 개방 회로에서 종단되는 슬롯 라인(105)까지 피드 측면(feed side)에 대향하는 측면으로 연장되는 것을 특징으로 하는 인쇄 회로.

### 청구항 11

적어도 제8항 내지 제10항 중 어느 한 항에 따른 다층 인쇄 회로를 포함하는 단말기.

## 명세서

### 기술 분야

[0001] 본 발명은 일반적으로 무선 시스템에서 이용되는 인쇄 회로 기판에 관한 것이다. 더 구체적으로, 다층 기판 상에 슬롯 라인을 구현하기 위한 방법에 관한 것이고, 또한 상기 방법에 따라 구현된 적어도 하나의 슬롯 라인을 포함하는 다층 인쇄 회로에 관한 것이며, 이 슬롯 라인은 특히 분리 슬롯 또는 슬롯 안테나로서 이용될 수 있다.

### 배경 기술

[0002] 무선 통신 분야에서, 전송 채널의 용량을 증가시키고 전체 시스템의 동작을 향상시키기 위해 MIMO(Multiple Input Multiple Output) 회로의 이용이 증가되고 있다. MIMO 회로의 사용은 일반적으로 동일한 보드에 구현될 안테나의 수의 증가를 초래하게 된다. 반면에, 회로의 접적을 용이하게 하기 위해 안테나는 요즘 PCB(printed circuit board)에 직접 프린팅된다. 그러나, 물리 법칙에 따라 안테나의 길이 및 분리 엘리먼트의 길이는 파장에 의존한다. 그에 따라, 2개의 PIFA 타입 안테나 간의 상호 결합을 감소시키기 위해 단락 슬롯이 이용되는 경우에, 실질적으로  $\lambda g/4 - \lambda g$ 는 동작 주파수에서의 관내 파장(guided wavelength)임 - 와 같아야 하는 슬롯의 파장은 2.4GHz 주파수 대역에서의 WiFi 동작을 위해 약 23mm의 물리적 길이를 갖게 된다. 이 길이는 대량 생산에서 이용되는 인쇄 회로 기판에 대한 비용 및 사이즈 제한에 있어서 무시할 정도가 아니다. 그러나, 인쇄 회로 기판은 다층 구조를 갖는 기판으로 가장 흔히 형성된다.

### 발명의 내용

#### 과제의 해결 수단

[0003] 따라서 본 발명은 인쇄 회로 기판의 사이즈를 제한하면서 분리 라인들 또는 슬롯 안테나로서 이용될 수 있는 단락 슬롯 라인(short-circuited slot-line)을 구현하기 위한 인쇄 회로 기판들의 다층 구조를 이용하는 것을 제안한다.

[0004] 그에 따라, 본 발명은 적어도 하나의 제1 도전층, 유전체층 및 제2 도전층을 포함하는 인쇄 회로의 다층 기판에 서의 단락 슬롯 라인을 구현하기 위한 방법에 관한 것으로, 이 방법은 다음 단계들,

[0005] 제1 도전층에 전기적 길이(L)를 갖는 슬롯 라인을 에칭(etching)하는 단계,

[0006] 제1 도전층에 슬롯 라인의 제1 측면을 따라 전기적 길이(L1)(여기서,  $L1 \leq L$ )를 갖는 제1 도전 밴드의 제1 부분을 에칭하는 단계,

- [0007] 제1 도전층에 슬롯 라인의 제2 측면을 따라 전기적 길이(L2)(여기서,  $L_2 \leq L$ )를 갖는 상기 제1 도전 밴드의 제2 부분을 에칭하는 단계,

- [0008] 제2 도전층에 전기적 길이(L3)를 갖는 루프의 형태로 제2 도전 밴드를 에칭하는 단계를 포함하고,

- [0009] 제2 도전 밴드의 한 단부는 제1 도전 밴드의 제1 부분에 연결되고, 제2 도전 밴드의 다른 단부는 제1 도전 밴드의 제2 부분에 연결되어 도전 루프를 형성한다.

- [0010] 본 발명의 또 다른 특징에 따른, 제1 도전 밴드의 제1 및 제2 부분의 전기적 길이들(L1, L2)은 동일하다.

- [0011] 본 발명의 또 다른 특징에 따른, 전기적 길이(L3)는 전기적 길이들(L1, L2)의 합과 실질적으로 동일하다.

- [0012] 특정 실시예에 따른, 슬롯 라인은 전기적 길이( $L < 90^\circ$ )의 라인이고, 바람직하게 슬롯 라인의 전기적 길이( $L = 45^\circ$ )이다.

- [0013] 또 다른 실시예에 따라, 제1 도전 밴드의 제1 및 제2 부분의 전기적 길이들(L1, L2)은  $45^\circ$  와 동일하다.

- [0014] 바람직하게, 제1 및 제2 도전 밴드들의 총 전기적 길이는 실질적으로  $180^\circ$  와 동일하다.

- [0015] 본 발명은 또한 상기 설명된 바와 같이 구현된 적어도 하나의 슬롯 라인을 포함하는 것을 특징으로 하는 다중 인쇄 회로에 관한 것이다.

- [0016] 한 실시예에 따른 슬롯 라인은 분리 슬롯이다.

- [0017] 또 다른 실시예에 따른 슬롯 라인은 슬롯 안테나이다. 이 경우에, 슬롯 안테나의 동작을 향상시키기 위해 제1 밴드의 제1 및 제2 부분들을 결정하는 슬롯들은 개방 회로 슬롯까지 연장된다.

- [0018] 본 발명은 또한 상기 설명된 바와 같은 적어도 인쇄 회로를 포함하는 단말기에 관한 것이다.

### 도면의 간단한 설명

- [0019] 본 발명의 다른 특징들 및 장점들은 첨부 도면을 참조하여 구현되는 상이한 실시예들의 설명을 읽을 때 나타날 것이다.

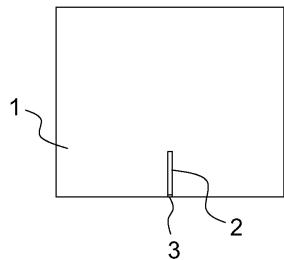

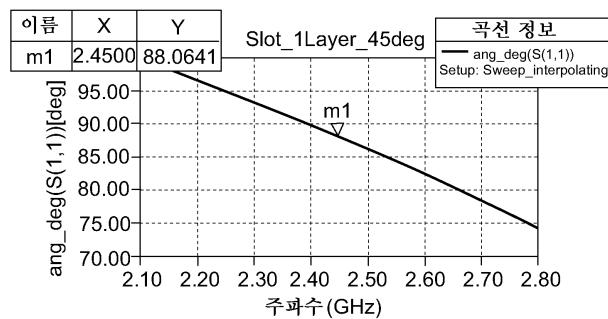

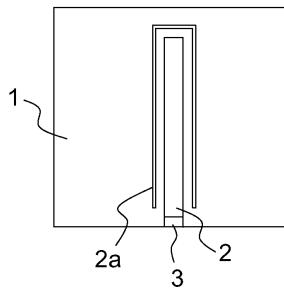

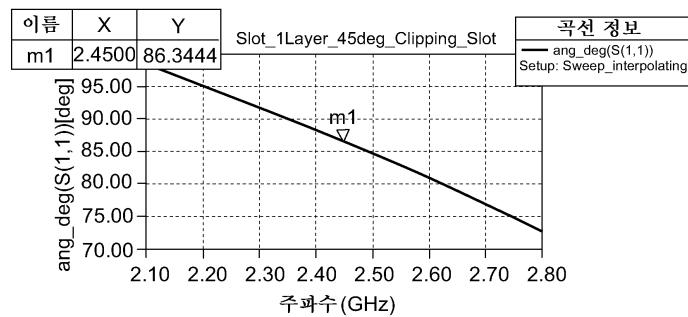

- 도 1a 및 도 1b는 본 발명의 구현 방법에 따른 분리 슬롯을 구현하는 제1 단계뿐만 아니라 상기 슬롯의 주파수의 함수로서 입력에서의 리턴된 반사 위상을 제공하는 곡선을 각각 도시한다.

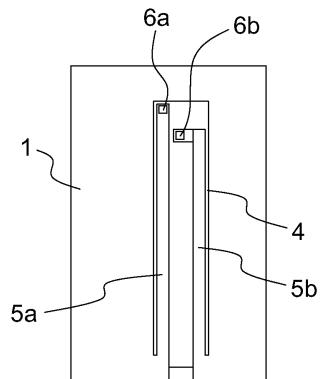

- 도 2a는 본 발명의 방법에 따른 분리 슬롯을 구현하는 제2 단계를 도시하고, 도 2b는 도 2a의 분리 슬롯의 주파수의 함수로서 입력에서의 리턴된 반사 위상을 제공하는 곡선을 도시한다.

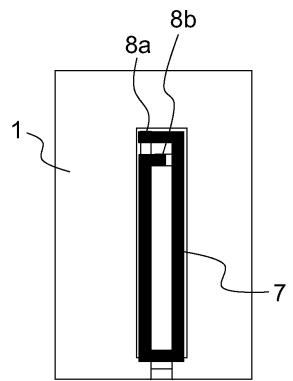

- 도 3a 및 도 3b는 분리 슬롯과 제1 도전 밴드의 평면도 및 본 발명의 방법에 따라 구현된 분리 슬롯의 평면도를 각각 도시한다.

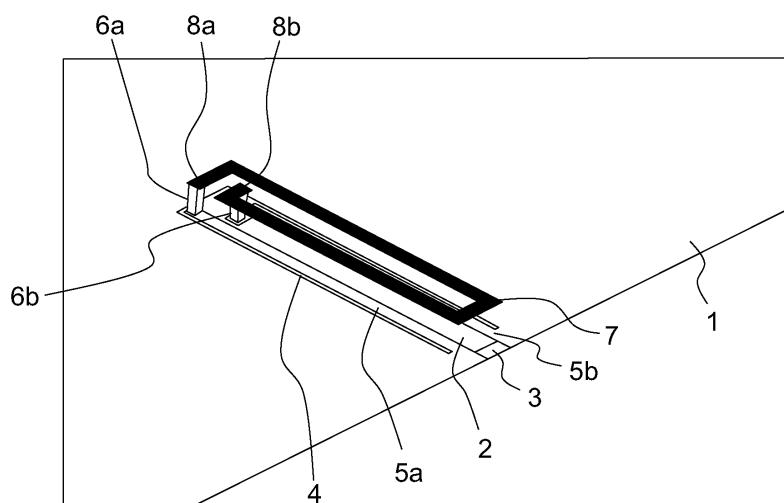

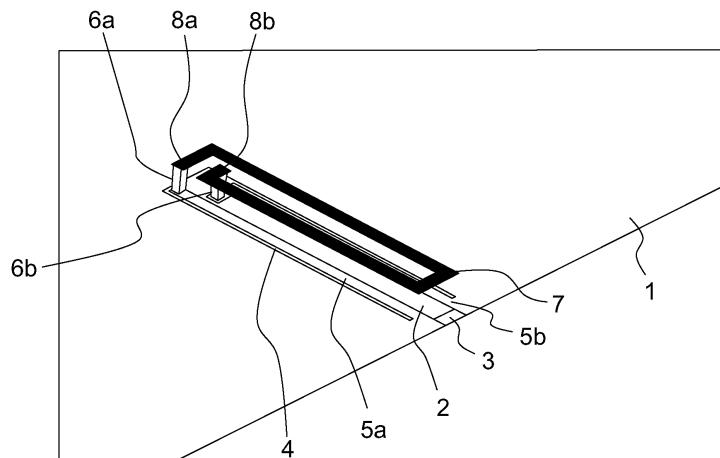

- 도 4는 본 발명의 방법에 따라 구현된 분리 슬롯의 투시도를 도시한다.

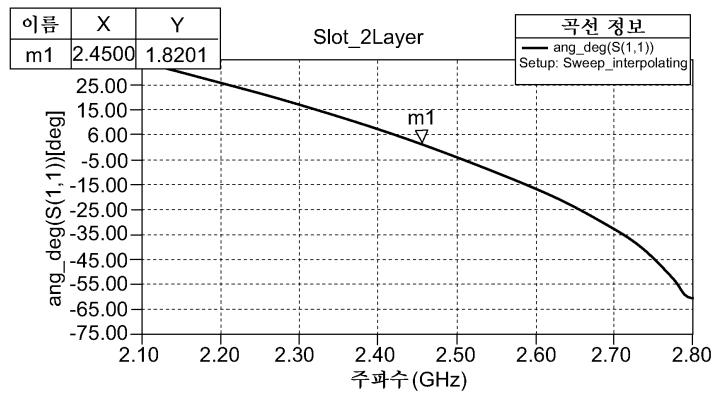

- 도 5는 도 4에서 도시된 바와 같은 분리 슬롯을 시뮬레이팅하여 획득된, 주파수의 함수로서 입력에서의 리턴된 반사 위상을 제공하는 곡선이다.

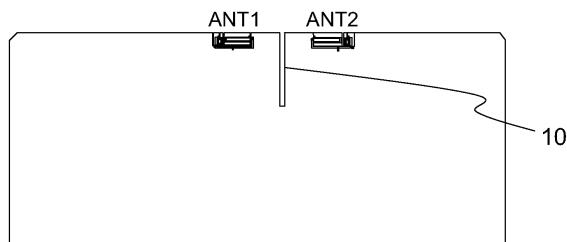

- 도 6은 종래 기술에 따른 분리 슬롯을 특징으로 하는 인쇄 회로 기판의 도시적인 평면 개략도이다.

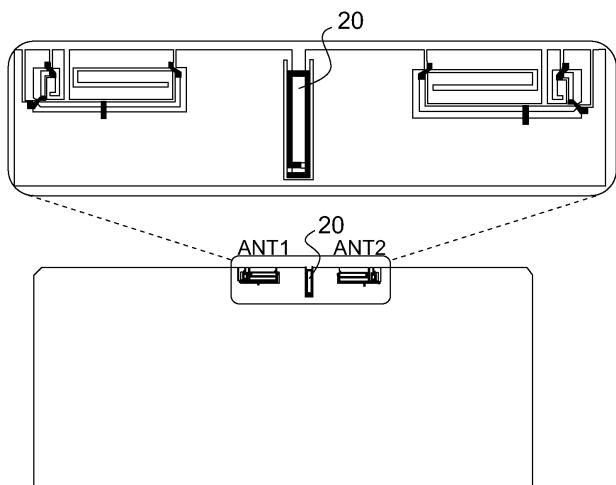

- 도 7은 인쇄 회로 기판 및 본 발명의 방법에 따라 구현된 분리 슬롯을 갖는 안테나 부분을 확대한 평면 개략도이다.

- 도 8a 및 도 8b는 도 6의 종래 기술에 따른 분리 슬롯 또는 도 7의 본 발명에 따른 분리 슬롯을 시뮬레이팅하여 획득된, 주파수의 함수로서 분리 및 적용에 대한 곡선을 각각 도시한다.

- 도 9는 도 6의 분리 슬롯 및 도 7의 분리 슬롯의 경우에서의 2개의 안테나 간의 분리 곡선을 제공한다.

- 도 10은 본 발명의 방법에 따라 구현된 슬롯 안테나의 개략적인 투시도이다.

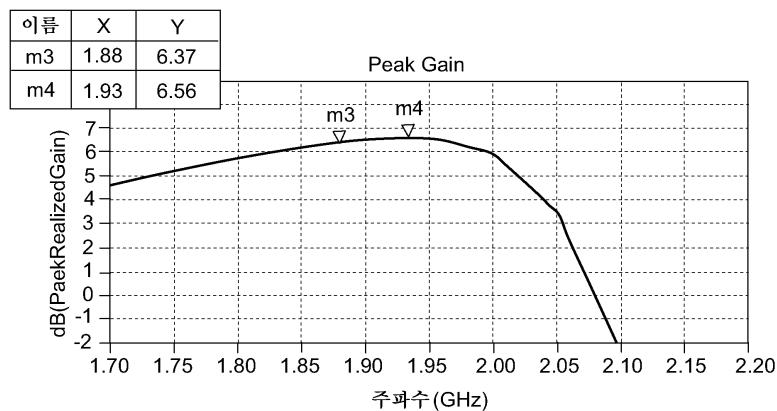

- 도 11, 도 12 및 도 13은 도 10에서 도시된 안테나에 대한 dB에서의 주파수의 함수로서 적용, 효율(yield) 및 이득(gain)을 각각 제공하는 곡선이다.

### 발명을 실시하기 위한 구체적인 내용

- [0020] 도 1 내지 도 5를 참조하여, 본 발명의 방법에 따라 다층 인쇄 회로 기판 상에 분리 슬롯을 구현하는 것에 대한 설명이 먼저 제공될 것이다.

- [0021] 이 경우에, 인쇄 회로는 1mm의 두께를 갖는 FR4로서 알려진 기판을 이용하여 구현된다.

- [0022] 도 1a에서 도시된 바와 같이, 가진점(excitation point; 3)을 포함한 기판(1)의 가장자리에 단락 슬롯 라인(2)이 에칭되었다.

- [0023] 본 발명에 따라, 슬롯 라인(2)은 90° 보다 작은 전기적 길이를 갖고, 바람직하게 전기적 길이는 45° 와 같도록 선택된다. 이 특정 실시예에서, 이하에 더 상세하게 설명된 바와 같이 슬롯 라인의 길이는 슬릿을 포개어 접음으로써 2개로 분리된다. 그러나, 얻고자 하는 결과 또는 기판을 구현하는 데의 제약에 따라 다른 전기적 길이들이 선택될 수 있다.

- [0024] 도 1a에서 도시된 바와 같은 슬롯 라인은 HFSS 3D EM 시뮬레이터를 이용하여 시뮬레이팅되었다. 시뮬레이션에 서, 그리고 상기 언급된 바와 같이, 기판은 FR4 기판이고 슬롯 라인(2)은 1mm의 폭 및 10mm의 길이를 갖는다.

- [0025] 상기 언급된 파라미터들을 이용하여, 도 1b에 도시된 바와 같이, 주파수의 함수로서 입력(3)에서의 리턴 반사 위상(각도)을 제공하는 곡선이 얻어졌다. 이 경우에, 약 45° 의 전기적 길이의 슬롯에 있어서, 획득된 위상은 포인트(m1)로 나타낸 바와 같이 2.45GHz의 주파수에서 90° 에 가깝다는 것을 알 수 있다.

- [0026] 더 구체적으로 도 2a에 도시된 제2 단계에서, 슬롯 라인 주위의 제1 도전 밴드의 제1 및 제2 부분들을 구현하기 위해, 슬롯 라인(2) 주위에 그 슬롯 라인(2)을 둘러싸는 얇은 슬롯(4)이 에칭되어 있다. 시뮬레이팅된 실시예에서, 이 슬롯(4)은 0.15mm의 폭을 갖고 슬롯 라인(2)의 가장자리들로부터 0.5mm의 거리에 위치된다. 슬롯(4)은 도전층에 또는 기판(1)의 접지 평면 위에 에칭되어 있다. 이 경우에, 그리고 도 2b에 도시된 바와 같이, 곡선 상의 포인트(m1)에 대한 위상의 값은 도 1b에 도시된 것과 유사하고, 이것은 슬롯 라인(2) 주위에 에칭되어 있는 슬롯(4)이 메인 슬롯의 거동을 변화시키지 않는다는 것을 의미한다.

- [0027] 다음 단계에서, 도 3a에 도시된 바와 같이 도 2a에 도시된 단락 부분(2a)은 전기적 길이(L1)를 갖는 제1 도전 밴드의 제1 부분 및 전기적 길이(L2)를 갖는 제1 도전 밴드의 제2 부분을 각각 형성하는 2개의 도전 부분들(5a, 5b)을 구현하도록 개방되어 있다.

- [0028] 후속 단계에서, 그리고 도 3b에서 도시된 바와 같이, 인쇄 회로의 도전층(1)에 대향하는 제2 도전층에 루프의 형태로 제2 도전 밴드(7)가 구현되어 있다. 도전층(7)의 2개의 단부(8a, 8b)는 금속화된 홀(hole)에 의해 연결되거나 또는 제1 도전층 상에 구현된 제1 밴드의 제1 및 제2 부분들(5a, 5b)의 2개의 단부(6a, 6b)와 유사하게 연결된다.

- [0029] 상기 설명된 방법에 따라 구현된 분리 슬롯 라인의 완성된 투시도는 도시되고, 도 4에서, 도 3a 및 도 3b를 참조하여 설명된 엘리먼트와 동일한 엘리먼트들은 동일한 참조부호들로 나타낸다.

- [0030] 대략 2개로 분리된 전기적 라인 길이를 갖는 도 4에 도시된 분리 슬롯은 단락된 1/4 파장 라인의 경우에서와 같이 입력 포트(3)에서의 0° 에 근접한 리턴된 위상을 얻을 수 있다. 이 결과는 도 4에서 도시된 바와 같이 분리 슬롯 라인에 대한 도 5의 적용 곡선(S11)에 도시되어 있다. 이 경우에, 포인트(m1)는 시뮬레이션으로 획득된 리턴 위상이 2.4GHz에서의 WiFi 대역의 중앙 주파수에서 0° 에 가깝다는 것을 도시한다. 이것은 부분들(5a, 7, 5b)로 형성된 루프에서, 슬롯 라인 주위의 표면 전류가 입력 포트로 되돌아오기 전에 2-s 회로(two-s circuit)를 수행하고, 그에 따라 실질적으로 180° 와 동일한 전기적 길이를 따라 움직인다는 사실로써 설명된다.

- [0031] 이 실시예에서, 45° 와 동일한 전기적 길이를 갖는 슬롯 라인이 구현되었다. 한편, 제1 밴드의 제1 부분(5a) 및 제2 부분(5b)의 전기적 길이들(L1, L2)은 실질적으로 동일하고 45° 와 같으며, 제2 밴드(7)의 전기적 길이(L3)는 실질적으로 전기적 길이들의 합(L1 + L2)과 같다. 그러나, 90° 보다 작은 다른 전기적 길이들이 고려될 수 있다.

- [0032] 도 6 내지 도 9에 도시된 바와 같이, 우리는 MIMO 회로를 위해 구현된 2개의 안테나(ANT1, ANT2)의 분리에서 획득된 결과와, 표준 분리 슬롯 라인 또는 본 발명의 방법에 따라 구현된 분리 슬롯 라인으로 각각 분리된 결과들을 비교했다.

- [0033] 도 6에서, 2개의 안테나들(ANT1, ANT2)은 2개의 안테나들 간의 단층 기판의 상층에 에칭된 단락 슬롯 라인(10)에 의해 분리된다. 이 경우에, 슬롯 라인(10)의 길이는  $\lambda/4$ 와 같고,  $\lambda$ 는 동작 주파수에서의 파장이다.

- [0034] 도 7에서, 도 7의 확대된 부분에서 도시된 바와 같이 본 발명의 방법에 따라 구현된 분리 슬롯 라인(20)이 도시

되어 있다. 이 슬롯(20)은 도 6에 도시된 슬롯 라인(10)과 비교하여 감소된 사이즈를 갖는다.

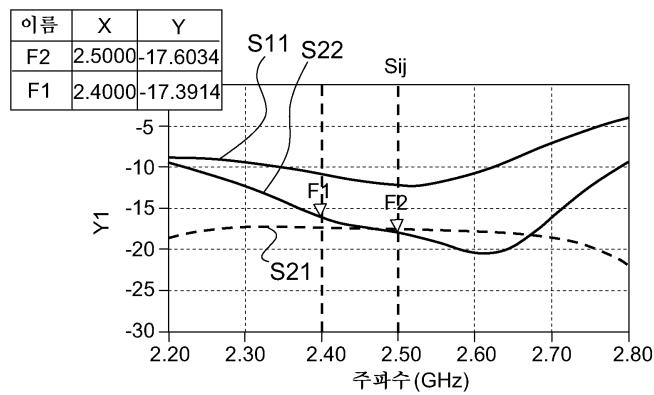

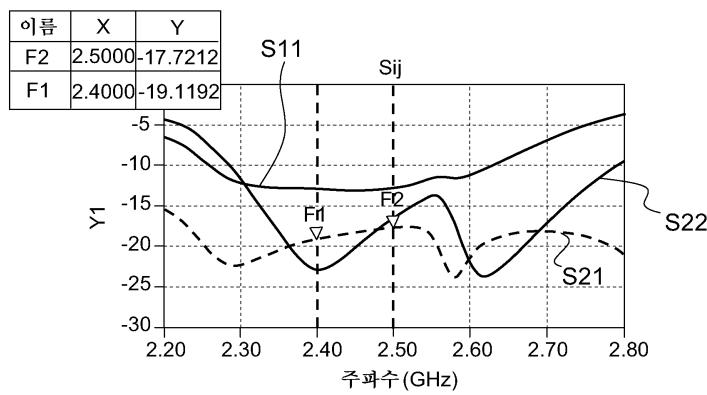

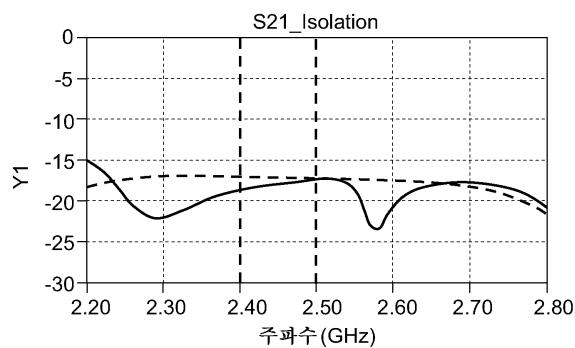

[0035] 도 8a, 도 8b 및 도 9에서의 곡선들을 보면, 도 6에서의 회로의 성능과 도 7에서의 안테나의 성능을 비교할 수 있다. 도 8a는 도 6에서 도시된 회로의 전송 곡선(S21)뿐만 아니라 적용 곡선들(S11, S22)을 도시하고, 반면 도 8b는 도 7에서 도시된 회로의 응답들(S11, S22, S21)을 제공한다. 이러한 곡선들은 이용되는 분리 슬롯 라인의 타입이 어느 것이든 안테나의 응답들(S11, S22)이 동일한 레벨에 있고, 획득된 분리 레벨이 2개의 타입의 슬롯 라인들에 대하여 약 17dB이라는 것을 도시한다. 한편, 도 9에 도시된 곡선들은 2개의 타입의 슬롯 라인들에 대하여 유사한 분리 레벨을 유효하게 하는 도 6에서의 회로 및 도 7에서의 회로 각각에 대한 주파수의 함수로서 전송 응답(S21)을 제공한다.

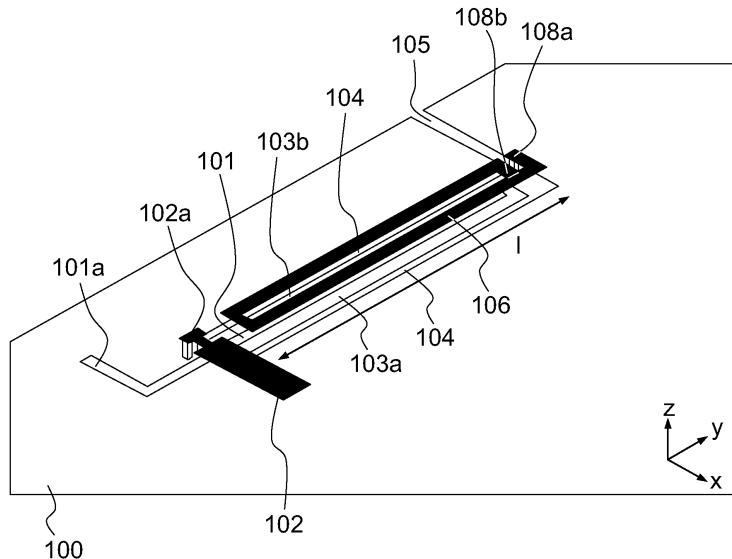

[0036] 우리는 이제 도 10 내지 도 13을 참조하여, 본 발명에 따른 방법을 이용하는 슬롯 안테나의 구현을 설명할 것이다.

[0037] 도 10에서 상기 설명된 본 발명의 방법에 따라 획득된 슬롯 안테나가 투시도로 도시된다. 다층 기판 상에 인쇄 회로 기판의 한 부분을 형성하는 슬롯 안테나가 구현된다. 기판(100)의 제1 도전층 상에, 전자기 결합에 의한 안테나의 퍼딩(feeding)을 획득하기 위해 부분(101a)으로 연장되는 슬롯 라인(101)이 구현되었다. 이 경우에, 도 10에서 도시된 바와 같이, 마이크로스트립 라인(102)의 일부는 기판의 대향측 상에 구현되고 금속화된 홀(102a)을 통해 도전층에 연결된다. 부분(102) 및 부분(101a)의 길이들은 슬롯 안테나(101)의 퍼딩을 획득하기 위해 알려진 방식으로 결정된다.

[0038] 도 10에 도시된 바와 같이 그리고 본 발명의 방법에 따라, 슬롯 라인(101) 주위와 좁은 폭의 슬롯(104)을 예칭하고, 퍼드 라인(102)에 대향하는 슬롯 라인(101)의 단부에서 슬롯(104)과 슬롯 라인(101) 사이의 단락 회로를 제거하여, 슬롯 라인(101)의 각각의 측면 상에 제1 도전 밴드의 2개의 부분들(103a, 103b)이 구현되었다. 한편, 층(100)에 대향하는 도전층에, 도 10에 도시된 바와 같이, 루프를 형성하는 제2 도전 밴드(106)가 구현되었다. 결과적으로, 도전 밴드(106)의 2개의 단부는 도전 비아들(108a, 108b)을 통해 도전 밴드들의 단부들(103a, 103b)에 각각 연결되어, 층 전기적 길이(L')의 전류 도전 루프를 형성한다. 한편, 도 10에 도시된 안테나의 동작을 향상시키기 위해, 슬롯(104)의 단부와 층(100)의 가장자리 사이의 제1 층(100)에 개방-회로 슬롯(105)이 구현된다. 이 슬롯(105)은 슬롯-안테나의 동작 밴드를 넓히고 방사 효율을 증가시키는 데 기여한다.

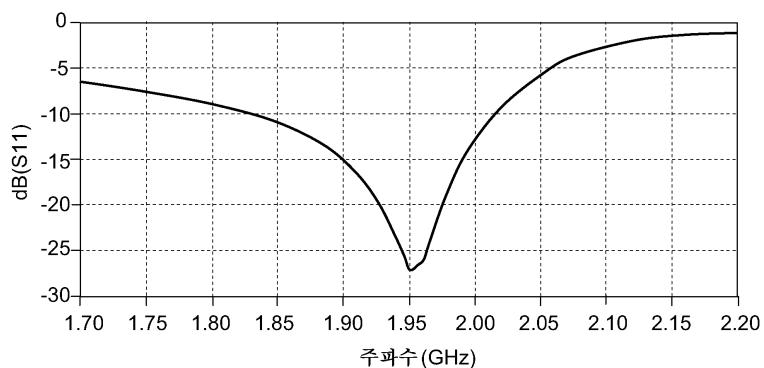

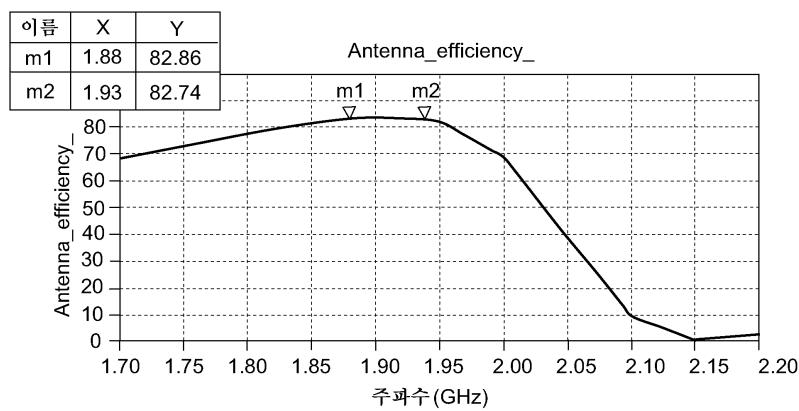

[0039] 도 6에서 도시된 바와 같은, 안테나는 DECT 대역, 즉, 1880MHz 내지 1930MHz 사이에 포함된 주파수 대역에서 동작하도록 시뮬레이팅되었다. 시뮬레이션에 있어서, 1.2mm의 두께를 갖는 FR4로서 알려진 유전체 재료에 구현된  $230 \times 306\text{mm}^2$ <sup>2</sup> 사이즈의 기판이 이용되었다. 안테나는 기판의 가장자리를 중 하나에 위치되었다. 시뮬레이션에 있어서, 슬롯의 물리적 길이는 약 21mm가 되도록 선택되었다.

[0040] 얻어진 결과가 도 11 내지 도 13에 곡선들로 주어져 있고, 도 11에서는 적용 응답(S11)이 주파수의 함수로서 dB로 도시되어 있으며, DECT 대역에서는 -12dB 미만의 손실을 보여준다.

[0041] 도 12는 안테나의 효율을 주파수의 함수로서 도시하고, DECT 대역에서 80%보다 큰 효율을 보여준다.

[0042] 도 13은 피크 이득을 주파수의 함수로서 dB로 도시하고, DECT 대역에서 6dBi보다 큰 이득을 보여준다.

[0043] 슬롯-안테나에 비교하여, 그러한 구조는 접지 평면 상에 점유된 표면이 2배로 감소되는 것을 가능하게 한다. 풀딩된 슬롯의 결과로서 빈 공간은 전자 컴포넌트들을 위치시키도록 활용될 수 있다. 소형화됨으로써 전자 기판에 기계적 및 구현 제한들을 고려하면서 더 용이하게 위치될 수 있도록 할 수 있는 한편, MIMO 시스템에 의해 요구되는 방사 패턴들에서의 다양성을 제공할 수 있다.

[0044] 당업자에게 전술된 실시예들이 예로서 제공되었다는 것은 명백하다.

## 도면

## 도면1a

## 도면1b

## 도면2a

## 도면2b

도면3a

도면3b

도면4

## 도면5

## 도면6

## 도면7

도면8a

도면8b

도면9

도면10

도면11

도면12

## 도면13