(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0041461

(43) 공개일자 2014년04월04일

- (51) 국제특허분류(Int. Cl.)

*H02M 1/44* (2007.01) *H02M 7/48* (2007.01)

*H02J 17/00* (2006.01)

- (21) 출원번호 10-2013-7026924

- (22) 출원일자(국제) 2012년03월12일

심사청구일자 없음

- (85) 번역문제출일자 2013년10월11일

- (86) 국제출원번호 PCT/US2012/028829

- (87) 국제공개번호 WO 2012/125590

국제공개일자 2012년09월20일

- (30) 우선권주장

61/451,823 2011년03월11일 미국(US)

- (71) 출원인

유타 스테이트 유니버시티

미국 유타 84341 스위트 108 놀스 로간, 놀스 리

서치 파크웨이 1780

- (72) 발명자

설리, 퀸리 테브로

미국 유타 84321, 리버 하이츠, 646 사우스 600

이스트

샤프, 브라이언 토마스

미국 유타 84321, 리버 하이츠, 646 사우스 600

이스트

(뒷면에 계속)

- (74) 대리인

윤동열

전체 청구항 수 : 총 20 항

(54) 발명의 명칭 비대칭 전압 상쇄 기술들을 사용하여 LCL 컨버터들을 제어하기 위한 방법 및 장치

### (57) 요 약

비대칭 전압 상쇄를 이용하는 LCL 공진 컨버터 제어를 위한 방법 및 장치가 기술된다. 제어 변수들의 최적 궤적을 결정하는 방법들이 논의된다. 부하 파라미터들을 감지하는 실제 구현 예들이 포함된다. 출력 전류 조절에 의해 양호한 천이 응답 특성을 달성하기 위한 AVC를 갖는 간단한 PI, PID 및 퍼지 로직 제어기들이 포함된다.

**대 표 도** - 도37

(72) 발명자

우, 헌터

미국 유에스 84322, 로간, 룸 209, 블렌 홀, 700

노스 1200 이스트

길크리스트, 아론

미국 유타 84321, 로간, 1174 이스트 1900 노스

## 특허청구의 범위

### 청구항 1

비대칭 전압 상쇄 기술들을 사용하여 회로를 제어하는 컴퓨터 구현 방법으로서, 로딩 조건 및 적어도 하나의 회로 파라미터에 기초하여 다이오드 역회복 손실(diode reverse recovery loss)을 피하는 복수의 지점들 - 각각의 지점은 제어 변수들의 조합을 포함함 - 을 결정하는 단계; 복수의 지점들의 각각에 대해 고조파 왜곡(harmonic distortion)을 결정하는 단계; 결정된 고조파 왜곡에 기초하여, 최소화된 고조파 왜곡을 갖는 지점들의 궤적을 결정하는 단계; 지점들의 궤적 상의 적어도 하나의 지점에 대해 제어 변수들의 조합을 사용하여 회로를 제어하는 단계; 및 로딩 조건에 기초하여 회로 내의 전력 레벨을 제어하는 단계를 포함하는 것을 특징으로 하는 컴퓨터 구현 방법.

### 청구항 2

제1항에 있어서, 제어 변수들의 조합은, 알파 플러스 제어 변수; 알파 마이너스 제어 변수; 및 베타 제어 변수를 포함하며, 알파 플러스 제어 변수, 알파 마이너스 제어 변수, 및 베타 제어 변수는 비대칭 전압 상쇄를 가능하게 하는 것을 특징으로 하는 컴퓨터 구현 방법.

### 청구항 3

제1항에 있어서, 회로는, 제1 인덕터; 커패시터; 및 제2 인덕터를 포함하며, 제1 인덕터, 커패시터, 및 제2 인덕터는 인덕터 커패시터 인덕터(LCL) 컨버터를 형성하도록 구성되는 것을 특징으로 하는 컴퓨터 구현 방법.

### 청구항 4

제3항에 있어서, 적어도 하나의 회로 파라미터는, 제1 인덕턴스에 기초하는 제1 인덕턴스 대 제2 인덕터에 기초하는 제2 인덕턴스의 비; 임피던스; 및 반사 임피던스; 및 구성요소 공차 중 적어도 하나를 포함하는 것을 특징으로 하는 컴퓨터 구현 방법.

### 청구항 5

제1항에 있어서, 회로의 로딩 조건을 모니터링하는 단계; 및 로딩 조건에 기초하여 제어 변수들의 조합을 조절하는 단계를 추가로 포함하는 것을 특징으로 하는 컴퓨터 구현 방법.

**청구항 6**

제1항에 있어서,

회로의 적어도 하나의 회로 파라미터를 모니터링하는 단계; 및

감지된 회로 파라미터에 기초하여 지점들의 궤적을 따라 제어 변수들의 조합을 조절하는 단계를 추가로 포함하는 것을 특징으로 하는 컴퓨터 구현 방법.

**청구항 7**

제1항에 있어서, 지점들의 궤적 상의 적어도 하나의 지점에 대한 제어 변수들의 조합은 일정한 스위칭 주파수에서 소프트 스위칭(soft switching)을 가능하게 하는 것을 특징으로 하는 컴퓨터 구현 방법.

**청구항 8**

회로의 다이오드 역회복 손실들을 감소시키도록 구성된 제어기로서,

프로세서;

프로세서와 전자 통신하는 메모리를 포함하며,

메모리는, 프로세서에 의해 실행될 때, 프로세서가

로딩 조건 및 적어도 하나의 회로 파라미터에 기초하여 다이오드 역회복 손실을 피하는 복수의 지점들 - 각각의 지점은 제어 변수들의 조합을 포함함 - 을 결정하는 단계;

복수의 지점들의 각각에 대해 고조파 왜곡을 결정하는 단계;

결정된 고조파 왜곡에 기초하여, 최소화된 고조파 왜곡을 갖는 지점들의 궤적을 결정하는 단계;

지점들의 궤적 상의 적어도 하나의 지점에 대해 제어 변수들의 조합을 사용하여 회로를 제어하는 단계; 및

로딩 조건에 기초하여 회로에서의 전력 레벨을 제어하는 단계

를 수행하게 하는 실행가능 명령들을 저장하는 것을 특징으로 하는 제어기.

**청구항 9**

제8항에 있어서, 제어 변수들의 조합은,

알파 플러스 제어 변수;

알파 마이너스 제어 변수; 및

베타 제어 변수를 포함하며,

알파 플러스 제어 변수, 알파 마이너스 제어 변수, 및 베타 제어 변수는 비대칭 전압 상쇄를 가능하게 하는 것을 특징으로 하는 제어기.

**청구항 10**

제8항에 있어서, 회로는,

제1 인덕터;

커패시터; 및

제2 인덕터를 포함하며,

제1 인덕터, 커패시터, 및 제2 인덕터는 인덕터 커패시터 인덕터(LCL) 컨버터를 형성하도록 구성되는 것을 특징으로 하는 제어기.

**청구항 11**

제10항에 있어서, 적어도 하나의 회로 파라미터는,

제1 인덕터에 기초하는 제1 인덕턴스 대 제2 인덕터에 기초하는 제2 인덕턴스의 비;

임피던스;

반사 임피던스; 및

구성요소 공차 중 적어도 하나를 포함하는 것을 특징으로 하는 제어기.

### 청구항 12

제8항에 있어서,

회로의 로딩 조건을 모니터링하는 단계; 및

로딩 조건에 기초하여 제어 변수들의 조합을 조절하는 단계를 추가로 포함하는 것을 특징으로 하는 제어기.

### 청구항 13

제8항에 있어서,

회로의 적어도 하나의 회로 파라미터를 모니터링하는 단계; 및

감지된 회로 파라미터에 기초하여 지점들의 궤적을 따라 제어 변수들의 조합을 조절하는 단계를 추가로 포함하는 것을 특징으로 하는 제어기.

### 청구항 14

제8항에 있어서, 지점들의 궤적 상의 적어도 하나의 지점에 대한 제어 변수들의 조합은 일정한 스위칭 주파수에서 소프트 스위칭을 가능하게 하는 것을 특징으로 하는 제어기.

### 청구항 15

유도 전력 전송 시스템으로서,

송신기 코일을 갖는 공진 컨버터 회로;

송신기 코일로부터 전력을 수신하도록 구성된 수신기 코일; 및

제어기를 포함하며,

제어기는,

공진 컨버터 회로의 적어도 하나의 회로 파라미터 및 로딩 조건에 기초하여 공진 컨버터에 대해 다이오드 역회복 손실을 피하는 복수의 지점들 - 각각의 지점은 제어 변수들의 조합을 포함함 - 을 결정하는 단계;

복수의 지점들의 각각에 대해 고조파 왜곡을 결정하는 단계;

결정된 고조파 왜곡에 기초하여, 최소화된 고조파 왜곡을 갖는 지점들의 궤적을 결정하는 단계;

지점들의 궤적 상의 적어도 하나의 지점에 대해 제어 변수들의 조합을 사용하여 공진 컨버터 회로를 제어하는 단계; 및

로딩 조건에 기초하여 공진 컨버터 회로에서의 전력 레벨을 제어하는 단계

를 수행하는 프로세서를 포함하는 것을 특징으로 하는 유도 전력 전송 시스템.

### 청구항 16

제15항에 있어서, 제어 변수들의 조합은,

알파 플러스 제어 변수;

알파 마이너스 제어 변수; 및

베타 제어 변수를 포함하며,

알파 플러스 제어 변수, 알파 마이너스 제어 변수, 및 베타 제어 변수는 비대칭 전압 상쇄를 가능하게 하는 것

을 특징으로 하는 유도 전력 전송 시스템.

### 청구항 17

제15항에 있어서, 공진 컨버터 회로는,

다이오드;

제1 인덕터;

커패시터; 및

제2 인덕터를 포함하며,

제1 인덕터, 커패시터, 및 제2 인덕터는 인덕터 커패시터 인덕터(LCL) 컨버터를 형성하도록 구성되는 것을 특징으로 하는 유도 전력 전송 시스템.

### 청구항 18

제17항에 있어서, 회로 파라미터는,

제1 인덕터에 기초하는 제1 인덕턴스 대 제2 인덕터에 기초하는 제2 인덕턴스의 비;

반사 임피던스; 및

구성요소 공차 중 적어도 하나를 포함하는 것을 특징으로 하는 유도 전력 전송 시스템.

### 청구항 19

제15항에 있어서, 프로세서는,

회로의 로딩 조건을 모니터링하는 단계;

로딩 조건에 기초하여 제어 변수들의 조합을 조절하는 단계;

회로의 적어도 하나의 회로 파라미터를 모니터링하는 단계; 및

회로 파라미터에 기초하여 지점들의 궤적을 따라 제어 변수들의 조합을 조절하는 단계를 추가로 수행하는 것을 특징으로 하는 유도 전력 전송 시스템.

### 청구항 20

제15항에 있어서, 지점들의 궤적 상의 지점에 대한 제어 변수들의 조합은 공진 컨버터 회로의 일정한 스위칭 주파수에서 소프트 스위칭을 가능하게 하는 것을 특징으로 하는 유도 전력 전송 시스템.

## 명세서

### 기술 분야

관련 출원들에 대한 상호 참조

[0001] 본 출원은 2011년 3월 11일자로 출원된 미국 가특허 출원 제61/451,823호에 대한 우선권을 주장한다.

정부 후원 연구

[0004] 본 발명은 미국 에너지국에 의해 보상되는 계약 DE-EE0003114 하의 정부 지원으로 이루어졌다. 정부는 본 발명에서 소정의 권리를 갖는다.

[0005] 본 발명은 유도 전력 전송 시스템(inductive power transfer system)들의 효율을 개선하기 위한 방법에 관한 것이며, 특히, 비대칭 전압 상쇄 기술들을 사용하여 LCL 공진 컨버터들을 제어하는 것에 관한 것이다.

### 배경 기술

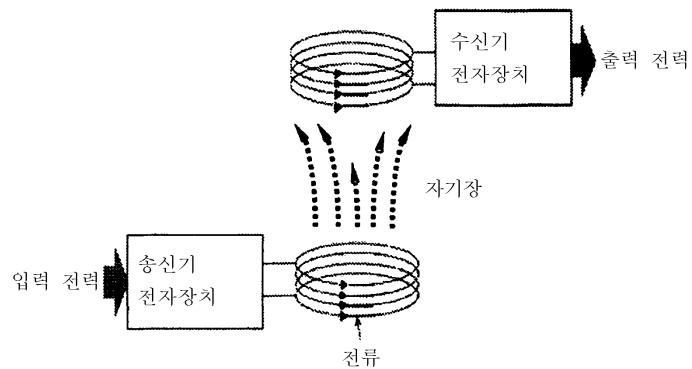

[0006] 무선 전력 전송을 실현하는 하나의 방법은, 일정한 고주파 교류로부터의 전기 에너지 형태인 입력 전력이 암페어의 법칙에 따라 시변(time varying) 자기장들로 변환되는 유도 전송(Inductive Power Transfer, IPT)으

로서 알려진 프로세스를 통한다(도 1). 수신단에서, 자기장은 패러데이의 법칙에 따라 유도 전압으로 변환되어서, 부하에 대한 출력 전력을 생성한다. 무선 전력 전송은 차량과 차도 사이에 어떠한 물리적 접속도 없이 움직이는 동안에 또는 정지 동안에 전기 차량이 연속으로 충전되게 할 수 있다. IPT 시스템들은, 폭 넓게는, 전원, 자기 커플러(magnetic coupler) 및 핏업 수신기(pickup receiver)를 포함하는, 3개의 카테고리들로 분리될 수 있다.

### 발명의 내용

[0007]

무선 전원들의 설계에서의 요점은 비용 및 크기를 또한 낮게 유지하면서 손실 및 기생 효과가 없거나 또는 거의 없이 DC 전력을 고주파 AC 전력으로 변환하는 것이다. 실제로, 0의 손실은 결코 달성되지 않는다. 그러므로, 전력 컨버터들을 설계하는 목적은 비용, 크기, 및 전자기 간섭(EMI)과 같은 기생 효과들을 최소로 유지하면서, 최고의 가능한 변환 효율을 얻는 것이었다. 고전력 인덕터 커패시터 인덕터(LCL) 공진 컨버터들의 효율 개선 및 EMI 감소는 무선 전력 전송 분야에서 중요한 과제가 되고 있다. 전기 효율 문제는 송신기 전자장치에서의 변환 손실과 관련된다.

[0008]

재생 에너지 부문의 급격한 성장으로, 고효율 시스템들의 개념은 더욱 더 필수적이 되고 있다. 이러한 경향에 따라, 초고효율을 달성할 수 있는 것은 잘 확립된 개념인 것으로 판명되고 있다. 이와 같이, 현대의 전력 전자장치는 고도로 효율적인 소프트 스위칭식 컨버터(soft switched converter)들에 주요 중점을 두고 있다.

[0009]

MOSFET 기술은 그들의 성능 면에서 과거 10년에 걸쳐 급속히 성장하고 있다. 이를 소자들은 오늘날 많은 전력 전자장치 시스템들에 대한 기본 구축 블록으로서 사용된다. 그러나, 그러한 소자들에서의 바디 다이오드(body diode)는 통상 특히 LCL 컨버터들에서 보고되는 거대한 다이오드 역회복 손실(reverse recovery loss)들을 야기하는 매우 불량한 턴-오프(turn off) 특성들을 갖는다. 필요한 것은 효율을 개선하기 위한 LCL 컨버터들에 대한 제어 전략이다. 이는 LCL 컨버터들에서 다이오드 역회복 손실들을 제거하기 위한 최적의 스위칭 조건들을 포함한다. MOSFET의 고속 스위칭 속도 및 매우 낮은 온 상태(on state) 저항은 절연 게이트 양극성 트랜지스터(insulated gate bipolar transistor, IGBT) 성능을 개선하는 데 필요하다.

[0010]

유도 전력 전송(IPT) 시스템들에서 사용되는 고전력 LCL 공진 컨버터들의 효율적 제어를 제공하기 위한 비대칭 전압 상쇄(Asymmetric Voltage Cancellation, AVC)를 사용하는 새로운 변조 기술이 개시된다. AVC 제어는 허용 가능한 총 고조파 왜곡(Total Harmonic Distortion, THD) 및 관련 손실을 달성하면서 다이오드 역회복 손실들을 피하는 방식을 제공한다. H-브리지에서 스위치들에 걸리는 여분의 기생 또는 외부의 커패시턴스와 커플링되면, 완전 소프트 스위칭식 제로 전압 스위칭(Zero Voltage Switching, ZVS) 고정 주파수 공진 전력 컨버터가 실현된다.

### 도면의 간단한 설명

[0011]

<도 1>

도 1은 유도 전력 전송을 예시하는 도면.

<도 2>

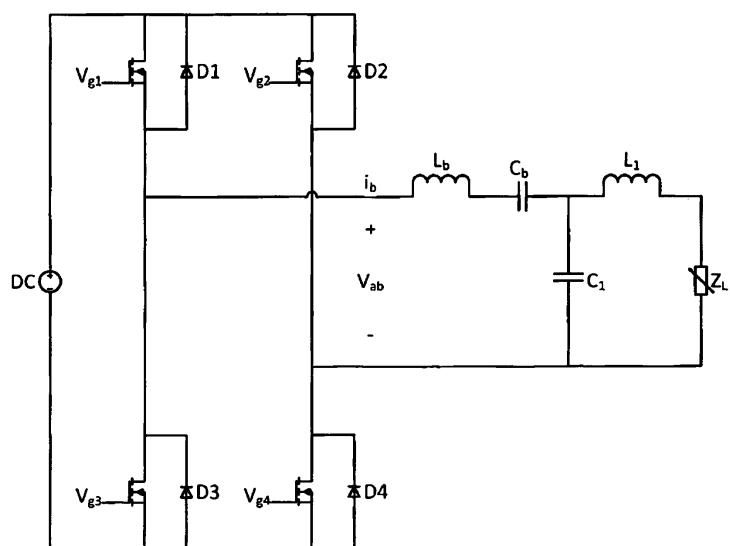

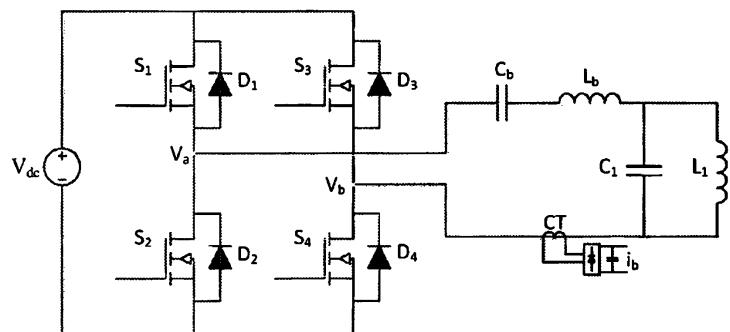

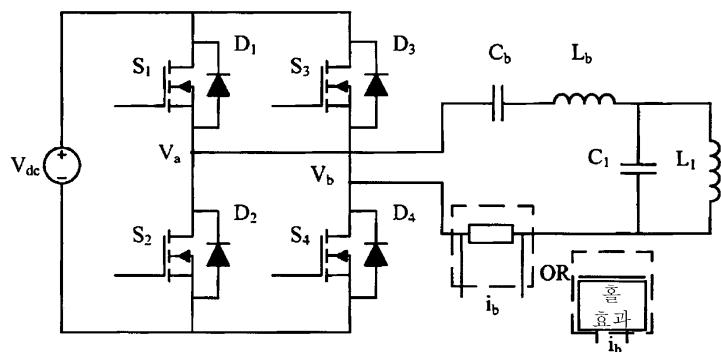

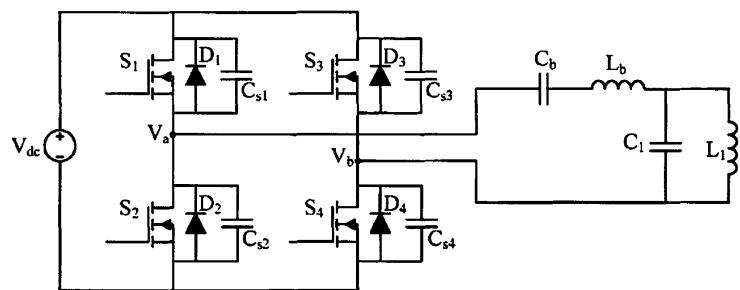

도 2는 풀 브리지(full bridge) 제어를 갖는 LCL 공진 컨버터를 예시하는 도면.

<도 3>

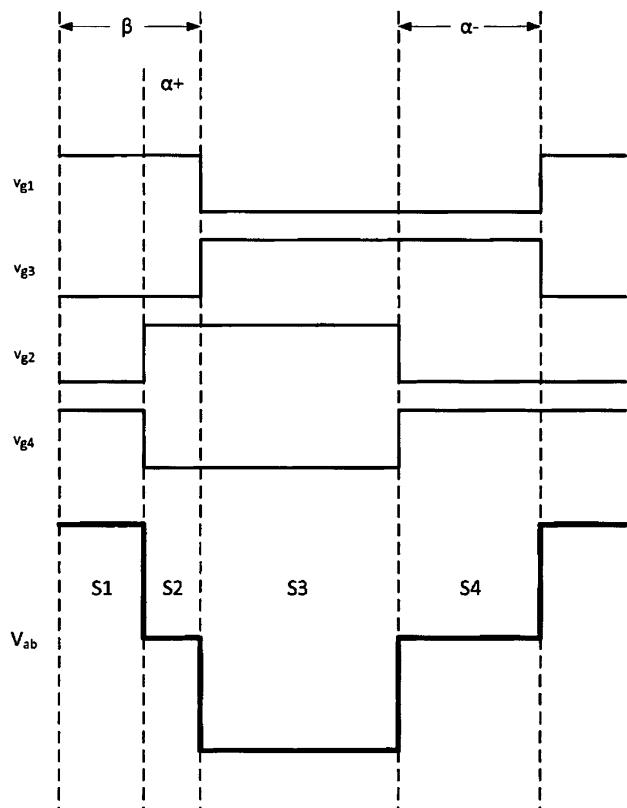

도 3은 H-브리지 출력 전압에 대한 예시적인 스위치 게이트 파형의 맵을 예시하는 도면.

<도 4>

도 4는 H-브리지에 대한 다양하고 예시적인 스위칭 천이 상태들을 갖는 표를 예시하는 도면.

<도 5>

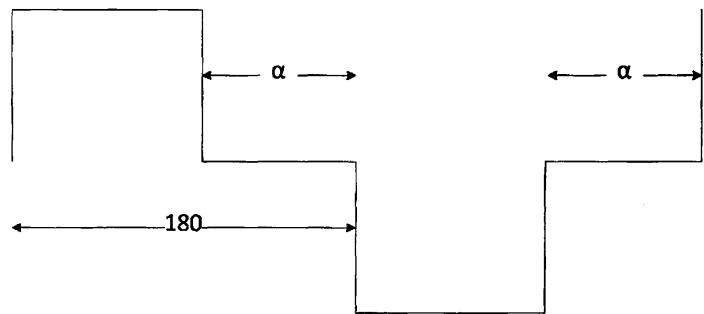

도 5는 예시적인 대칭 전압 상쇄 제어  $V_{ab}$  파형을 예시하는 도면.

<도 6>

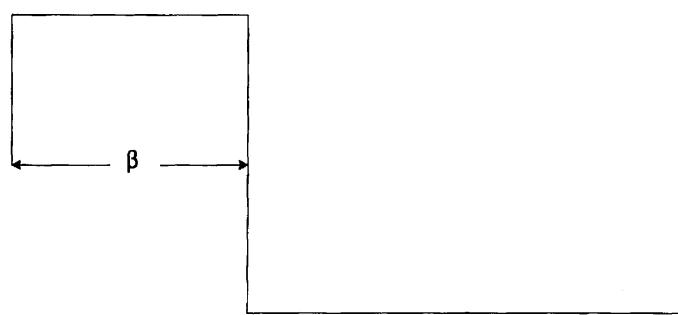

도 6은 예시적인 비대칭 듀티 사이클 제어  $V_{ab}$  파형을 예시하는 도면.

&lt;도 7&gt;

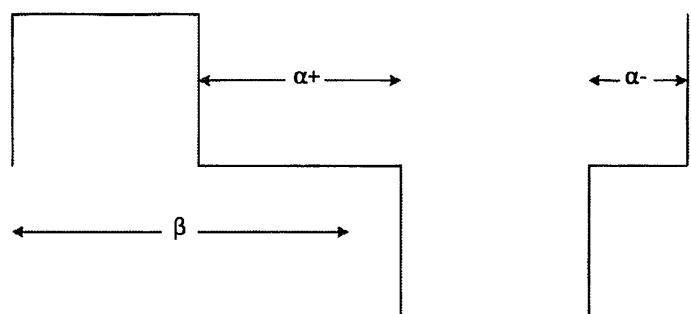

도 7은 예시적인 비대칭 전압 상쇄 제어  $V_{ab}$  과형을 예시하는 도면.

&lt;도 8&gt;

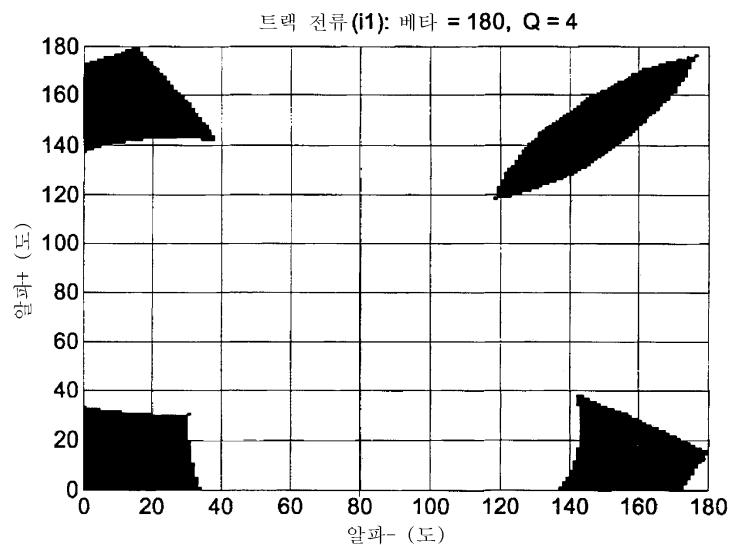

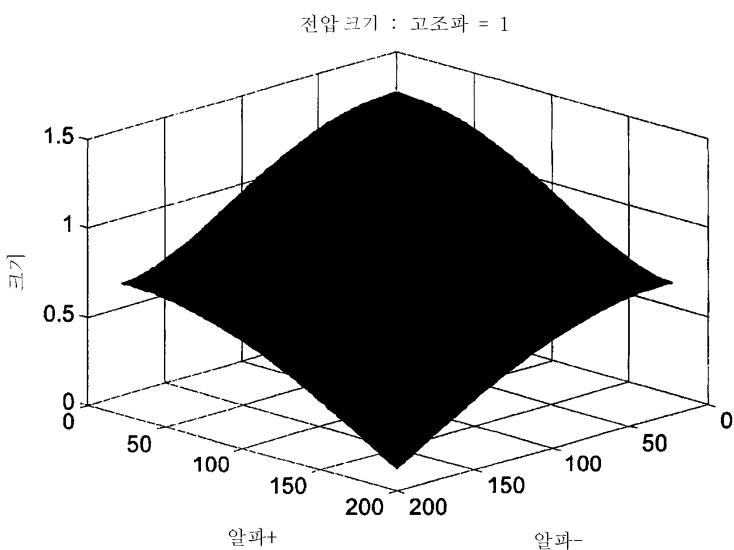

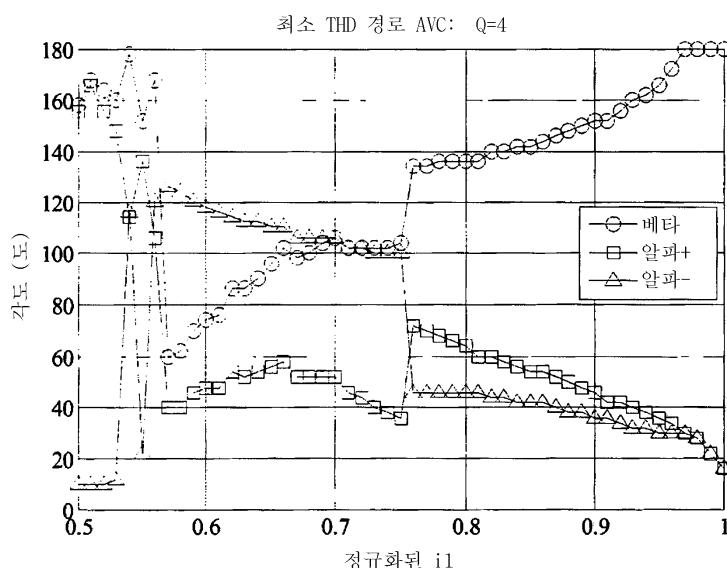

도 8은 상이한 제어 각도들, 베타 = 180 및  $Q_1 = 4.0$ 에 대한 THD를 예시하는 도면.

&lt;도 9&gt;

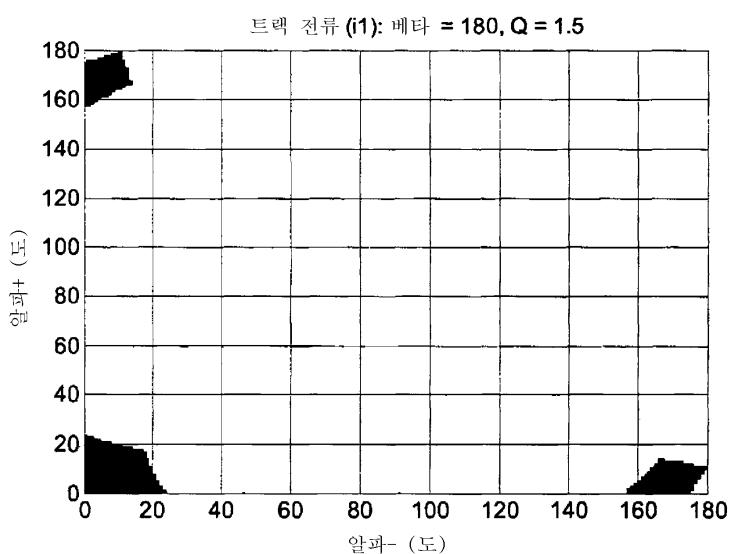

도 9는 상이한 제어 각도들, 베타 = 180 및  $Q_1 = 1.5$ 에 대한 THD를 예시하는 도면.

&lt;도 10&gt;

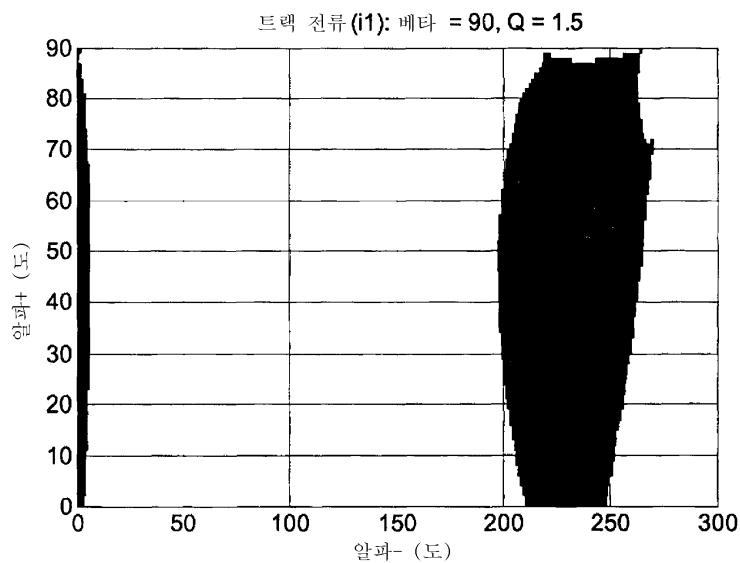

도 10은 상이한 제어 각도들, 베타 = 90 및  $Q_1 = 1.5$ 에 대한 THD를 예시하는 도면.

&lt;도 11&gt;

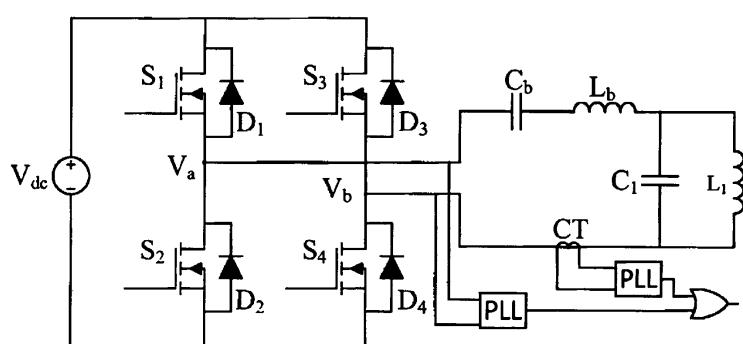

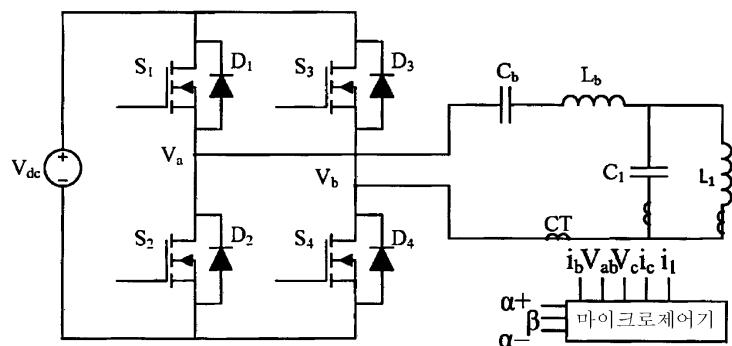

도 11은 브리지 전류를 검출하는 전류 변환기(Current Transformer, CT)를 사용하는 예시적인 LCL 컨버터를 예시하는 도면.

&lt;도 12&gt;

도 12는 베타=180에 대한  $V_{ab}$ 의 예시적인 진폭 성분 플롯을 예시하는 도면.

&lt;도 13&gt;

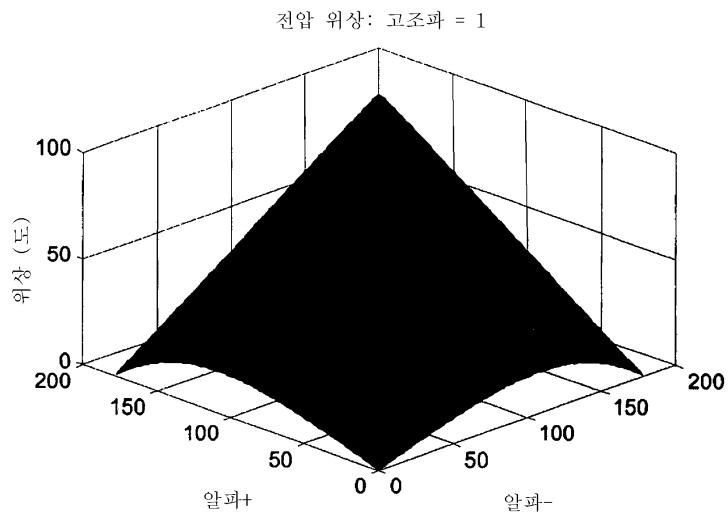

도 13은 베타=180에 대한  $V_{ab}$ 의 예시적인 위상 성분 플롯을 예시하는 도면.

&lt;도 14&gt;

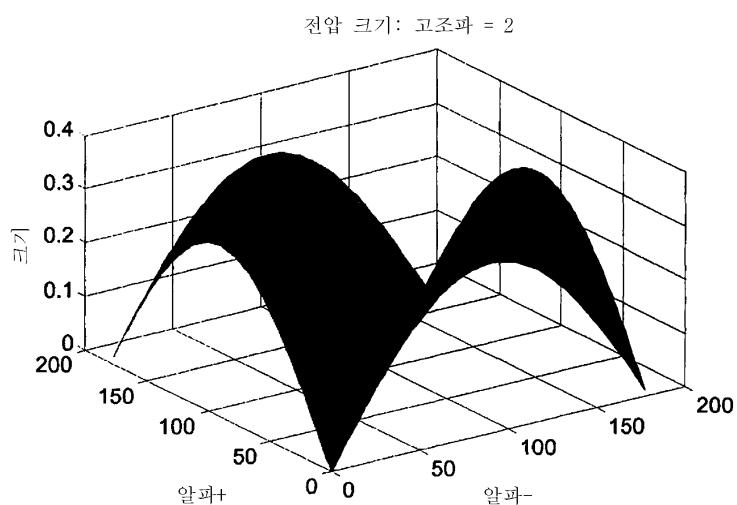

도 14는 베타=180에 대한  $V_{ab}$ 의 제2 고조파의 예시적인 진폭 성분 플롯을 예시하는 도면.

&lt;도 15&gt;

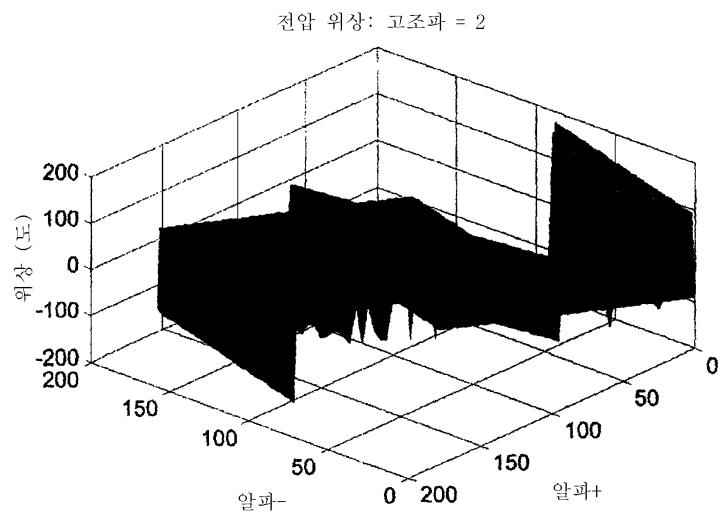

도 15는 베타=180에 대한  $V_{ab}$ 의 제2 고조파의 예시적인 위상 성분 플롯을 예시하는 도면.

&lt;도 16&gt;

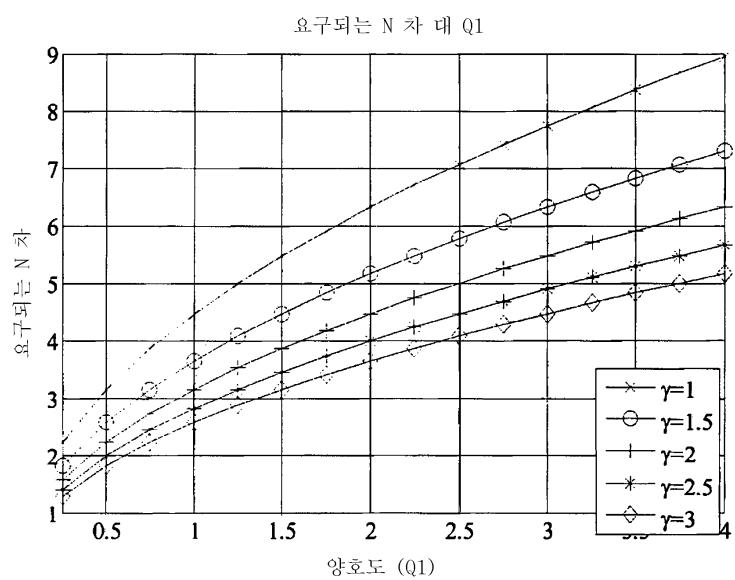

도 16은 양호도(quality factor)의 함수로서 N차의 관계를 예시하는 도면.

&lt;도 17&gt;

도 17은 다이오드 역회복 손실을 결정하기 위한 예시적인 플로우차트를 예시하는 도면.

&lt;도 18&gt;

도 18은 그리디 세일즈퍼슨 알고리즘(Greedy salesperson algorithm)의 예시적인 개략도.

&lt;도 19&gt;

도 19는  $Q_1=2$ 에 대한 그리디 세일즈퍼슨 알고리즘의 예시적인 솔루션을 예시하는 도면.

&lt;도 20&gt;

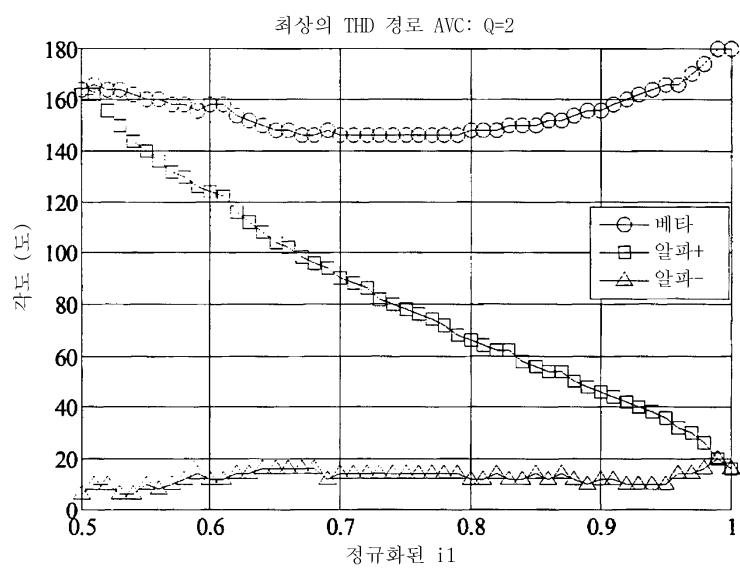

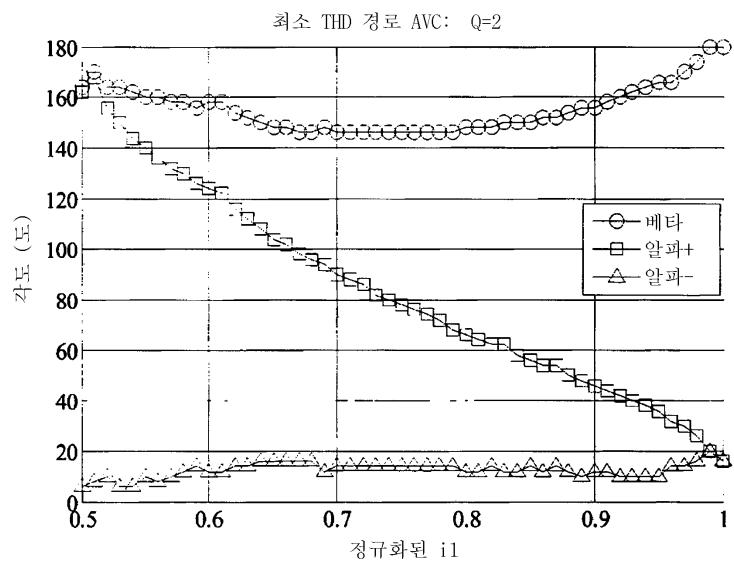

도 20은  $Q_1=2$ 에 대한 THD의 제어 각도들에 대한 그리디 세일즈퍼슨 알고리즘의 예시적인 솔루션을 예시하는 도면.

&lt;도 21&gt;

도 21은  $Q_1=2$ 에 대한 최적의 THD의 그리디 세일즈퍼슨 알고리즘의 예시적인 솔루션을 예시하는 도면.

&lt;도 22&gt;

도 22는  $Q_1=4$ 에 대한 그리디 세일즈퍼슨 알고리즘의 예시적인 솔루션을 예시하는 도면.

&lt;도 23&gt;

도 23은  $Q_1=4$ 에 대한 THD의 제어 각도들에 대한 그리디 세일즈퍼슨 알고리즘의 예시적인 솔루션을 예시하는 도면.

&lt;도 24&gt;

도 24는 최소 THD 경로를 갖는 그리디 세일즈퍼슨 알고리즘의 예시적인 솔루션을 예시하는 도면.

&lt;도 25&gt;

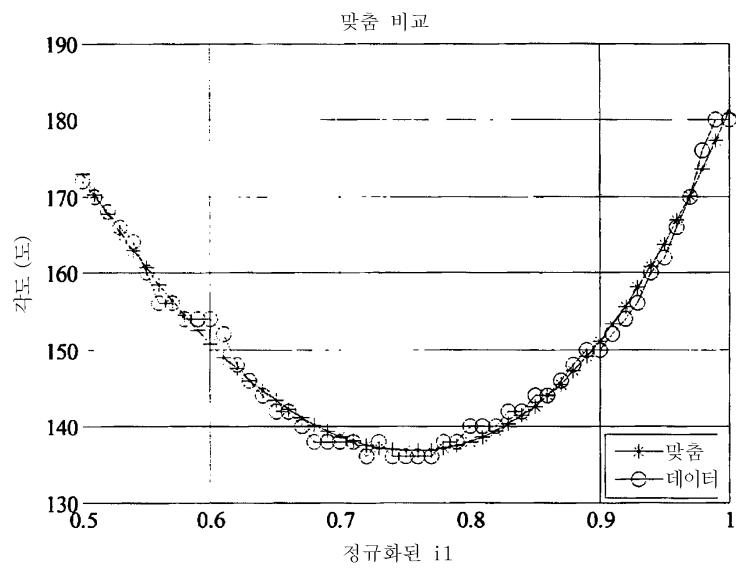

도 25는 베타 각도에 대한 4차 다항식 맞춤을 예시하는 도면.

&lt;도 26&gt;

도 26은 저항기 또는 홀 효과 센서(Hall Effect sensor)를 사용한 브리지 인덕터 전류 측정 감지를 예시하는 도면.

&lt;도 27&gt;

도 27은 PLL을 사용하는 예시적인 위상 검출 회로를 예시하는 도면.

&lt;도 28&gt;

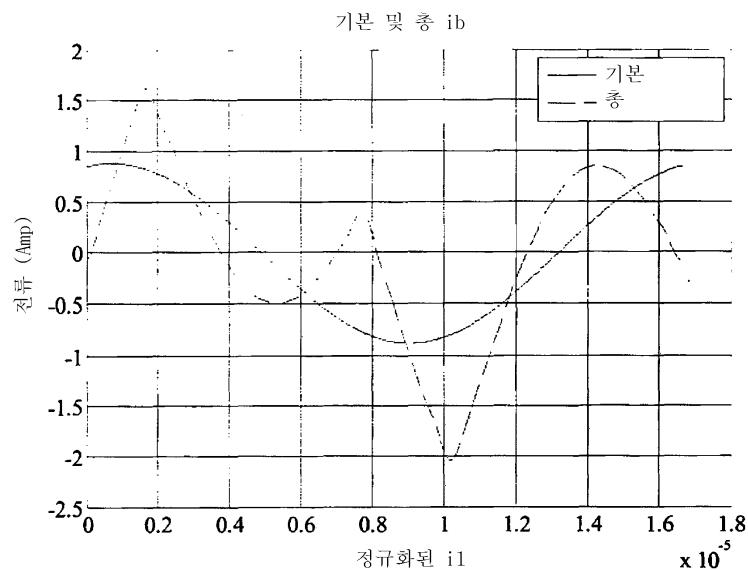

도 28은 예시적인 필터링된 브리지 전류 파형을 예시하는 도면.

&lt;도 29&gt;

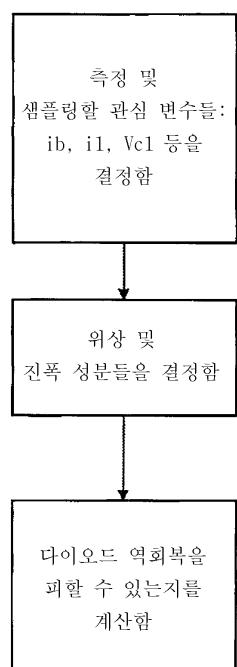

도 29는 예시적인 측정 회로의 블록도를 예시하는 도면.

&lt;도 30&gt;

도 30은 제어기의 예시적인 마이크로제어기 입력 출력 신호도 구현을 예시하는 도면.

&lt;도 31&gt;

도 31은 AVC의 마이크로제어기 구현에 대한 예시적인 내부 블록도를 예시하는 도면.

&lt;도 32&gt;

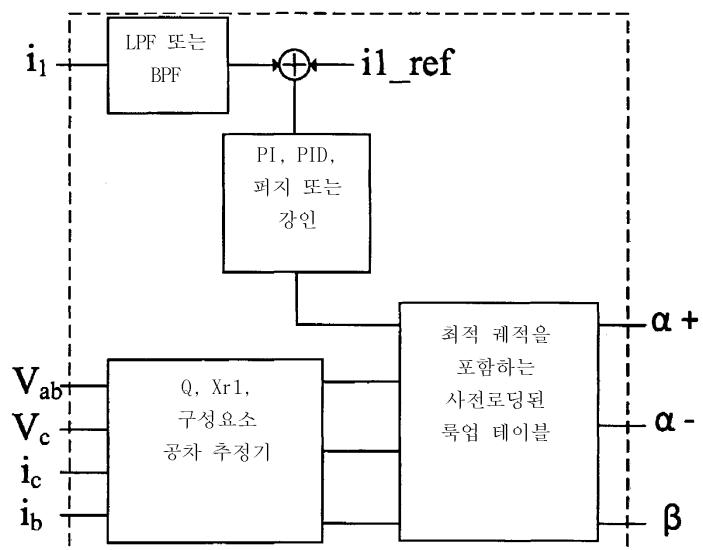

도 32는 AVC 제어기를 설계하기 위한 예시적인 블록도를 예시하는 도면.

&lt;도 33&gt;

도 33은 여분의 스위치 출력 커패시턴스를 갖는 예시적인 소프트 스위칭식 고정 주파수 LCL 컨버터를 예시하는 도면.

&lt;도 34&gt;

도 34는 스위칭 커패시턴스 값들을 결정하기 위한 예시적인 플로우차트를 예시하는 도면.

&lt;도 35&gt;

도 35는 스위칭의 경우에서의 다양하고 예시적인 브리지 전류들을 예시하는 도면.

&lt;도 36&gt;

도 36은 LCL 공진 네트워크에 대한 예시적인 구성요소 값들의 표를 예시하는 도면.

&lt;도 37&gt;

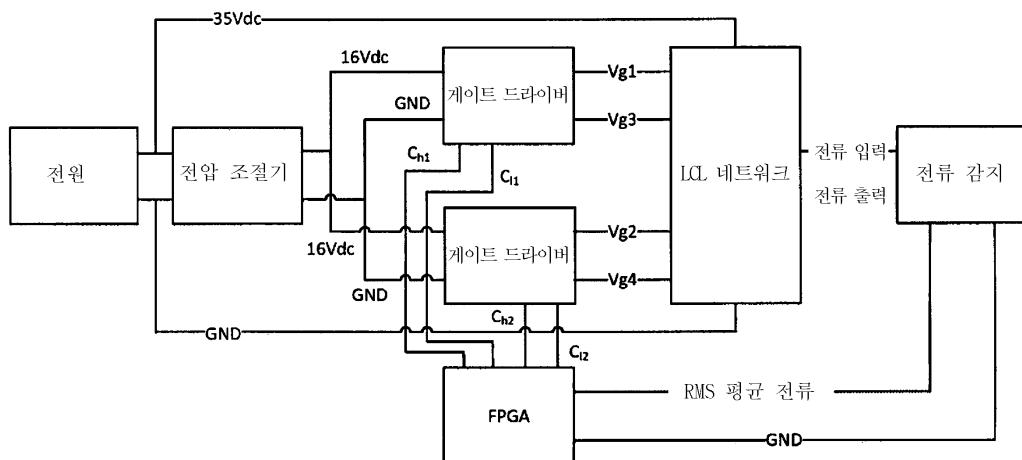

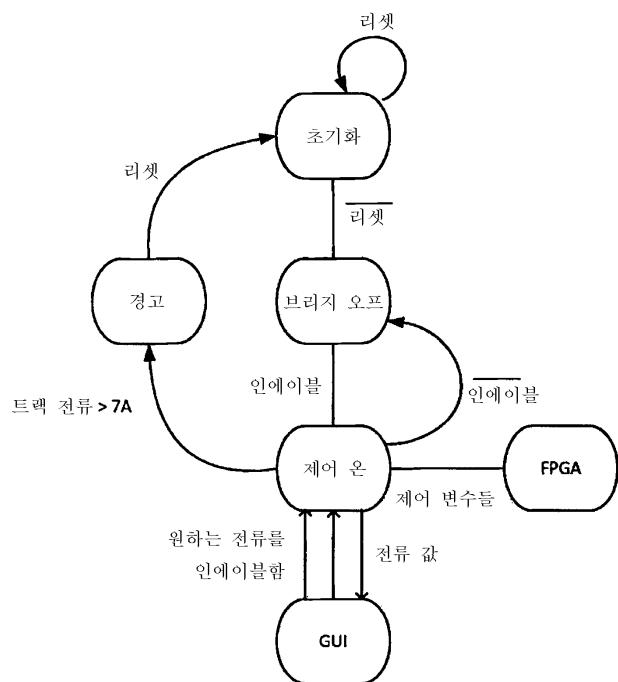

도 37은 예시적인 고 레벨 제어 블록도를 예시하는 도면.

&lt;도 38&gt;

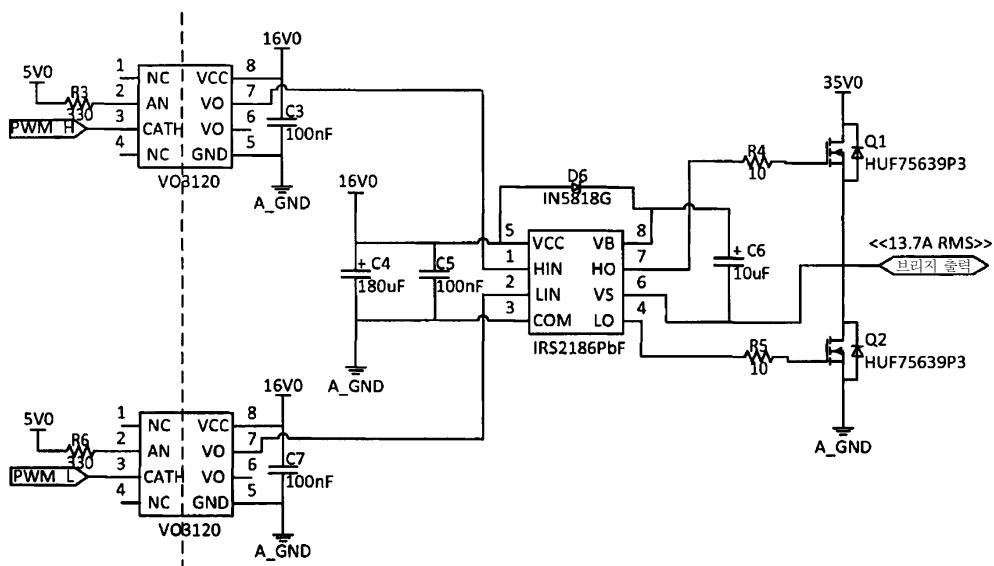

도 38은 예시적인 H-브리지 하프 드라이버(half driver)의 저 레벨 개략도.

&lt;도 39&gt;

도 39는 개시된 시스템을 통한 예시적인 전류 경로를 예시하는 도면.

<도 40>

도 40은 예시적인 LCL 컨버터 시스템의 고 레벨 개략도를 예시하는 도면.

<도 41>

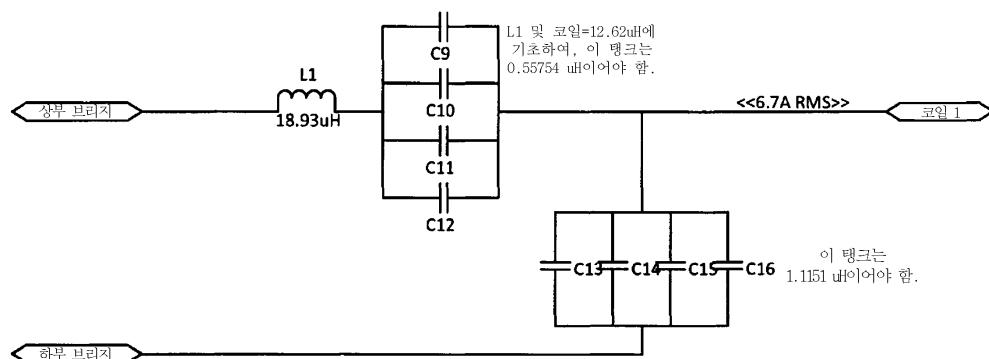

도 41은 예시적인 LCL 공진 네트워크의 개략도.

<도 42>

도 42는 예시적인 소프트웨어 흐름도를 예시하는 도면.

<도 43>

도 43은 예시적인 그래픽 사용자 인터페이스(Graphical User Interface, GUI)의 일례를 예시하는 도면.

<도 44>

도 44는 예시적인 하드웨어 기술 언어(Hardware Description Language, HDL) 설계 로직의 흐름도를 예시하는 도면.

<도 45>

도 45는 예시적인 비대칭 전압 상쇄 시에 총 고조파 왜곡 개선을 열거한 표를 예시하는 도면.

<도 46>

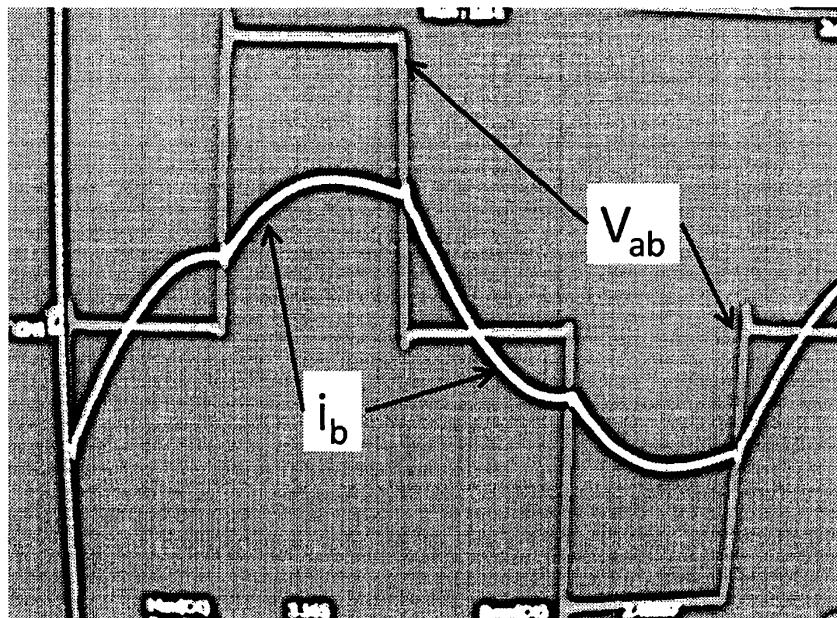

도 46은 다이오드 역회복을 피할 수 없음을 나타내는 예시적인 실험 결과들을 예시하는 도면.

<도 47>

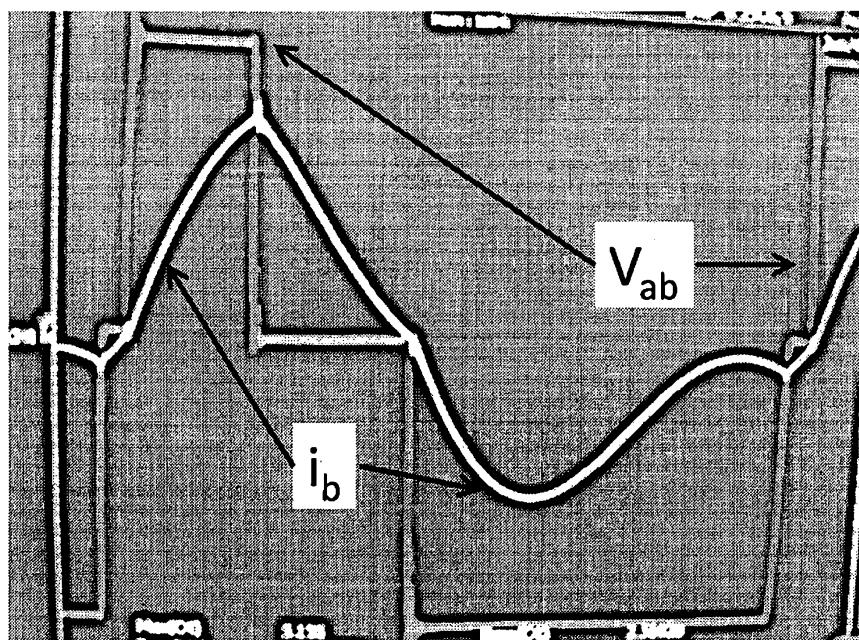

도 47은 다이오드 역회복을 피할 수 있음을 나타내는 예시적인 실험 결과들을 예시하는 도면.

<도 48>

도 48은 비대칭 전압 상쇄 대 대칭 전압 상쇄의 예시적인 효율 비교를 예시하는 도면.

### 발명을 실시하기 위한 구체적인 내용

[0012] 본 발명은 개선된 인덕터 커패시터 인덕터(LCL) 공진 컨버터를 위한 장치 및 관련 방법을 포함한다. 하기의 설명에서, 구체적인 바람직한 실시예들의 철저한 이해를 위해 많은 구체적인 상세사항들이 제공된다. 그러나, 당업자는 실시예들이 구체적인 상세사항들 중 하나 이상 없이 또는 다른 방법들, 구성요소들, 재료 등에 의해 실시될 수 있다는 것을 인식할 것이다. 몇몇 경우들에서, 바람직한 실시예들의 태양들을 모호하게 하는 것을 피하여 위하여 잘 알려진 구조물, 재료들 또는 동작들이 상세히 도시되거나 설명되지 않는다. 또한, 설명된 특징부들, 구조물들 또는 특성들은 다양할 대안 실시예들에서 임의의 적합한 방식으로 조합될 수 있다. 따라서, 도면의 몇몇 태양들에서 예시된 바와 같은 본 발명의 실시예들의 하기의 보다 상세한 설명은 본 발명의 범주를 제한하고자 하는 것이 아니라 단지 본 발명의 다양한 실시예들을 대표한다.

[0013] 본 명세서 및 뒤따르는 특허청구범위에서, 단수 형태("a", "an", "the")는 내용이 명백하게 달리 지시하지 않는다면 복수 형태를 포함한다. 본 명세서에 개시된 모든 범위들은 구체적으로 표시되지 않는다면 모든 종점들 및 중간 값들을 포함한다. 게다가, "선택적인" 또는 "선택적으로"는 예를 들어 후속으로 설명되는 상황들이 일어날 수 있거나 일어날 수 없는 경우들을 말하고, 그 상황들이 일어나는 경우들 및 그 상황들이 일어나지 않는 경우들을 포함한다. 용어 "하나 이상" 및 "적어도 하나"는 예를 들어 후속으로 설명되는 상황들 중 하나의 상황이 일어나는 경우들 및 후속으로 설명되는 상황들 중 하나 초과의 상황들이 일어나는 경우들을 말한다.

[0014] 본 개시 내용은 개선된 인덕터 커패시터 인덕터(LCL) 공진 컨버터를 위한 방법 및 장치를 설명한다. LCL 네트워크는 원하는 주파수에서의 공진을 위해 튜닝된다. 공진 시에 동작되는 LCL 네트워크는 일정한 AC 전원으로서 작동한다. LCL 컨버터는 도전 상태에 있는 동안 바디 다이오드의 역 바이어스와 관련되는 다이오드 역회복 손실로 인해 통상적으로는 비효율적이다. 이는 높은 스위칭 손실들을 초래한다. 컨버터 효율은 또한, 정상 동작 양호도(Q1) 값들이 다이오드 역회복 손실을 피하는 것을 불가능하게 만드는 로딩 범위와 관련된다. Q1은 아래의 수학식에 의해 정의될 수 있다:

## 수학식 1

$$Q_1 = \frac{\omega L_1}{R_{r1}}$$

[0015]

[0016] 여기서,  $R_{r1}$ 은 반사 트랙 저항이고,  $\omega$ 는 라디안(radian) 단위의 주파수이고,  $L_1$ 은 트랙 인덕턴스이다. LCL 공진 컨버터들에 대한 기존의 제어 방법들은 대칭 전압 상쇄(Symmetric Voltage Cancellation, SVC) 및 비대칭 듀티 사이클(Asymmetric Duty Cycle, ADC) 기술들을 포함한다. 이들 방법들 둘 모두는 단일 제어 변수를 이용한다. 본 발명은 SVC 및 ADC에 비해 더 큰 융통성을 위하여 3개의 제어 변수들을 이용하는 비대칭 전압 상쇄(ACV)를 도입한다. 이는 SVC 및 ADC + 추가적 융통성과 동등한 제어를 허용하는데, 따라서, 본래, ACV는 LCL 공진 컨버터 제어를 위한 SVC 및 ADC보다 덜 효율적이어서는 안된다. 풀 브리지 직렬 공진 컨버터와 같은 다른 컨버터들이 ACV를 사용하여 왔지만, 발명자들은 LCL 컨버터들 내로의 ACV 적용을 인지하고 있지 않다.

[0017] 유도 전력 전송에서의 하나의 문제점은 전자기 간섭(EMI)이다. 이 경우에, EMI는 원치 않는 주파수로 방사되는 전력으로 간주된다. 이는, 신호가 완전한 정현파는 아니고 고조파들이 그의 기본 주파수와 함께 도입되는 때에 발생한다. 고조파들은 기본 주파수의 정수 배의 정현파 신호들이다. 이는 총 고조파 왜곡(THD)이라 불리는 잘 알려진 변수에 의해, 또는 고조파들이 기여하는 전력의 백분율에 의해 정량화될 수 있다. 예를 들어, 9차 고조파(540kHz)를 갖는 60 kHz 동작 주파수 신호는 AM 무선과 간섭할 수 있다.

[0018] 패러데이의 법칙은 기전력(electromotive force)을 유도하기 위해 변화하는 자기장을 요구한다. 유사하게, 암페어의 법칙에 의하면, 변화하는 자기장을 생성하기 위하여 변화하는 전류가 요구된다. 따라서, 고주파 교류(AC)가 생성되어야 한다. 이는, 직류(DC) 입력을 원하는 AC 입력으로 변환하기 위해 일부 컨버터 또는 인버터가 사용되어야 한다는 것을 의미한다. DC-AC 변환을 위한 하나의 방법은 풀 브리지 제어를 갖는 LCL 공진 컨버터이다.

[0019] 도 2에 도시된 바와 같은 LCL 공진 컨버터는, DC 입력을 취하고 고주파 AC 출력을 생성하는 잘 알려진 회로이다. LCL 공진 컨버터에 대한 바람직한 특질은, 그의 공진 주파수에서 튜닝되고 동작될 때, 그에 놓이는 부하와는 상관없이 출력 전류가 일정하게 유지되는 것이다. 이는 AC 출력 전류가 부하, 예컨대 일정 전류원 특성을 알지 않고서 제어될 수 있다는 것을 의미한다. 게다가, LCL 컨버터들은 경부하(light load)(1의 역률(power factor)) 및 고조파 필터링 능력들에서 고효율이라는 이점을 갖는다.

[0020] 그러나, LCL 공진 컨버터들은 그들의 풀 브리지 제어에서 문제점을 갖는다. 풀 브리지 제어기 내의 다이오드들은 다이오드 역회복 손실이라고 알려져 있는 높은 스위칭 손실을 입기 쉽다.

### 1. 다이오드 역회복 손실들을 감소시키도록 LCL 컨버터들에 사용되는 ACV

[0022] 다이오드 역회복 손실은, 순방향 바이어싱되는 다이오드가, 전류가 그를 통해 여전히 흐르고 있는 동안에, 음(negative)의 방향으로 순간 전압 천이를 가질 때 발생한다. 예를 들어, 상태  $S_1$ 로부터 상태  $S_2$ 로의 천이는 도 2 내지 도 4를 참조하여 설명될 수 있다. 전류  $i_b$ 가  $S_1$ 에서 음이면, 그 상태는  $S_{1b}$ 로 알려진다. 전류가  $D_1$  및  $D_4$ 를 통해 흐르고,  $V_{ab}$ 는 양(positive)이다.  $V_{g1}$ 이 높고  $V_{g2}$ 가 낮으므로, 역방향으로는  $D_4$ 에 걸쳐 어떠한 전압도 없다. 일단 회로가  $S_{2b}$ 로 천이하면,  $V_{g1}$ 이 높고  $V_{g2}$ 가 높아서, 역방향으로  $D_4$ 에 걸쳐 높은 전압이 있다. 이제,  $D_4$ 는 전류가  $V_{g2}$ 와 관련된 MOSFET의 채널을 통하여 흐르기 시작함에 따라 비도전 상태로 천이할 것이지만, 잠시 동안,  $D_4$ 는 높은 역바이어스 전압에 의해 도전 상태이다. 이러한 현상은 다이오드 역회복 손실이라고 불리며, 관련 스위칭 손실은, 전형적으로 특히 불량한 성능의 바디 다이오드들을 갖는 전력 MOSFET의 구성요소들과 같은 일부 구성요소들에 대한 도전 손실에서의 것의 수십 내지 수백 배일 수 있다. 이는 제조 동안에 MOSFET 내의 바디 다이오드의 고유의 불량한 특성들로 인한 것이다. 이 문제점을 피하는 현재의 방법들은 수동(passive) 다이오드 구성요소들(탁월한 역회복 응답을 가짐)을 바디 다이오드와 병렬로 배치하거나, ADC 제어를 사용하는 것이다. 그러나, 전자는 회로의 비용 및 크기 둘 모두를 증가시키고, 후자는 증가된 고조파를 과정에 도입하여서 THD를 증가시킨다.

[0023] 현재는 LCL 공진 컨버터들에 통상적으로 사용되는 2개의 제어 방법들이 있다. 전류를 제어하는 데 이용되는 제 1 방법은 SVC 제어이다(도 5 참조). 이 방법은 구현하기 용이하다는 이점들을 가지며,  $120^\circ$ 의 도전각이 사용

될 때 매우 우수한 고조파 필터링 능력을 갖는다. SVC 제어는 구현하기가 매우 용이한데, 이는 SVC 제어가 단지 하나의 제어 변수, 즉 도전각  $\sigma$ ( $180^\circ$  -알파)만을 사용하기 때문이다. SVC 제어는 또한 낮은 THD를 제공하는데, 이는  $120^\circ$  의 도전각이 모든 3차 고조파 성분들을 제거하고, 대칭성이 모든 짹수 고조파들을 제거하기 때문이다. 그러나, SVC에는 단점들이 존재하는데, 이는 바디 다이오드들에 의한 전술된 스위칭 손실들이 상대적으로 높은 Q1 ( $Q_1 > 5$ ) 조건들에 대해서도  $\sigma = 120^\circ$  에서 특히 높기 때문이다. 다이오드 역회복 손실들은 회로의 동작 양호도( $Q_1$ )에 직접적으로 반비례한다.

[0024] LCL 공진 컨버터들을 제어하는 데 사용되는 제2 방법은 ADC 제어이다(도 6 참조). 이 방법은 구현하기가 쉽다는 이점들을 가지며, 소정의 양호도보다 큰 다이오드 역회복 손실을 피한다. SVC처럼, ADC는 하나의 제어 변수인 베타만을 갖는다. 그러나, 이는 비대칭 파형 때문에 훨씬 더 높은 THD를 갖는다.

[0025] SVC 및 ADC 제어와는 대조적으로, AVC 제어는 다이오드 역회복 손실을 감소시키면서 LCL 공진 컨버터에 입력되는 AC를 제어할 수 있는 솔루션(도 7 참조)을 제공한다. AVC 제어는 3개의 제어 변수들, 즉 알파+, 베타 및 알파-를 사용한다. THD를 감소시키고 다이오드 역회복 손실을 포함으로써 SVC 및 ADC의 조합된 이득들을 가질 가능성을 갖는다.

## 2. LCL 컨버터들의 성능을 최적화하는 AVC

[0027] AVC 제어는 수반되는 3개의 제어 변수들 때문에 구현하기가 훨씬 더 어렵다. 부가적으로, 최상의 결과들을 달성하기 위해, LCL 공진 컨버터의 부하 조건( $Q_1$ ) 및 감마( $L_b/L_1$ )가 고려되어야 한다(섹션 3 및 섹션 4에서 추가로 논의됨). 게다가, 부 핵업(secondry pickup)으로부터의 반사 반응 임피던스가 또한 고려되어야 하는데, 이후에 보여지는 바와 같이, 특히 가변 상호 커플링 조건들을 나타내는 시스템들에서, 모든 반응 부하가 수동적으로 보상될 수 있는 것은 아니기 때문이다. 유도 전력 전송 시스템들 내의 가변 상호 커플링 시스템들은 송신기와 수신기 코일들 사이에 가변 높이 및 정렬을 갖는다. 이들 시스템들의 예들은 드라이버들이 완전 패킹 정렬 위치들 및 이동 중인 차량으로의 전력 전송을 착수할 수 있는 정지 EV 충전 시스템들을 포함한다. 또한, LCL 컨버터들을 비용 효과적으로 유지하기 위해, 네트워크 내의 구성요소들을 튜닝하는 정확도는, 제조 비용이 이들 튜닝 구성요소들의 제조 공차와 직접적으로 연결되기 때문에, 너무 높을 수는 없다. 컨버터들의 비용을 합리적으로 유지하기 위해, 튜닝 시에 얼마간의 공차가 허용되어야 하고, AVC 알고리즘은 센서들을 통한 측정에 의해 또는 개인 설계(robust design)를 통해 이러한 변동을 보상하여, 광범위한 잘못 튜닝된 조건들에 걸쳐 동작하여야 한다.

[0028] 요약하면, 최적의 AVC 제어 알고리즘은, 상이한  $Q_1$ , 감마( $L_b/L_1$ ), 반사 임피던스, 및 구성요소 감도 문제들 하에, 다이오드 역회복 손실의 회피를 충족시킬 3개의 변수들인 알파+, 베타, 알파-에 대한 궤적을 찾을 수 있다. 불행하게도, 문제는 극히 복잡한데, 이는 이러한 조건을 충족시킬 수 있는 알파+, 베타 및 알파-의 많은 조합들이 존재하고, 최적의 솔루션을 결정하는 것이 간단하지 않기 때문이다. 최적의 솔루션을 관리하는 몇몇 기본 지침들은 THD, 스위칭 손실들(다이오드 역회복 손실들이 아님), 및 도전 손실이다.

[0029] 복잡한 문제점을 해결할 몇 가지 접근법들이 여기에 있다:

[0030] 정상 상태 시간 도메인 분석 접근법(steady-state time domain analysis approach)이 AVC의 솔루션들을 해석하는 데 사용될 수 있다. 이 실시에는 각각의 스위칭 상태에서의 상태-공간 표현을 사용하여  $V_{ab}$ ,  $i_b$ , 및  $i_1$ 의 단일 주기 파형을 해석한다. 이 접근법을 사용한 파형 솔루션은 또한 SPICE 모델링을 사용하여 검증되었다. 예를 들어, 도 2에서의 LCL 컨버터는 한 세트의 구분적(piecewise) 선형 상태 방정식들에 의해 모델링될 수 있다:

## 수학식 2

$$\dot{x}(t) = A \cdot x(t) + B \cdot V_d(t)$$

[0032] 여기서  $x$ 는 상태 벡터이고,  $A$ 는 시스템 행렬이고,  $B$ 는 입력 행렬이고,  $V_d$ 는 입력 컨버터 전압이다.

### 수학식 3

$$x(t) = \begin{bmatrix} i_b(t) \\ V_b(t) \\ V_c(t) \\ i_1(t) \end{bmatrix}, A = \begin{bmatrix} 0 & -1/L_b & -1/L_b & 0 \\ 1/C_b & 0 & 0 & 0 \\ 1/C_1 & 0 & 0 & -1/C_1 \\ 0 & 0 & 1/L_1 & -R_L/L_1 \end{bmatrix}, B = \begin{bmatrix} 1/L_b \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

[0033]

[0034] 다음과 같이 4개의 시간 구간들을 정의하는 것이 가능하고,

### 수학식 4

$$\Delta_0 = t_1 - t_0$$

$$\Delta_1 = t_2 - t_1$$

$$\Delta_2 = t_3 - t_2$$

[0035]

$$\Delta_3 = t_4 - t_3$$

[0036]

[0037] 4개의 구간들을 고려하면 다음과 같다:

### 수학식 5

[0038]

$$V_d(\Delta_0) = V_{dc}, \quad V_d(\Delta_1) = 0, \quad V_d(\Delta_2) = -V_{dc}, \quad V_d(\Delta_3) = 0$$

[0039] 구성  $k$ 에서 상태 방정식들의 시간 도메인 솔루션은 다음과 같다:

### 수학식 6

[0040]

$$x(t_{k+1}) = e^{A\Delta_k} \cdot x(t_k) + A^{-1}(e^{A\Delta_k} - I)B \cdot V_d(\Delta_k)$$

[0041]

4개의 상태들에 대한 시간 도메인 솔루션들을 나타내는 수학식 6으로부터 4개의 수학식들이 유도될 수 있으며, 4개의 수학식들을 동시적 형태로 조합하는 것은 하기의 행렬을 제공한다:

### 수학식 7

[0042]

$$\begin{bmatrix} -e^{A\Delta_0} & I & 0 & 0 \\ 0 & -e^{A\Delta_1} & I & 0 \\ 0 & 0 & -e^{A\Delta_2} & I \\ I & 0 & 0 & -e^{A\Delta_3} \end{bmatrix} \begin{bmatrix} x(t_0) \\ x(t_1) \\ x(t_2) \\ x(t_3) \end{bmatrix} = \begin{bmatrix} A^{-1}(e^{A\Delta_0} - I)B \cdot V_{dc} \\ 0 \\ -A^{-1}(e^{A\Delta_2} - I)B \cdot V_{dc} \\ 0 \end{bmatrix}$$

[0043]

수학식 7을 풀면 각각의 시간 구간에서 상태 벡터 조건이 주어질 것이다. 초기 조건으로서의 상태 벡터를 수학식 6에 대입하면, 전체 시간 도메인 솔루션이 제공된다.

[0044]

제어 변수들인 베타, 알파+, 및 알파-, 그리고 도 2에 나타낸 바와 같은 회로 특성들인  $L_b$ ,  $C_b$ ,  $L_1$ ,  $C_1$  및  $Z_r$ 이 알고리즘에서 사용된다. 알고리즘은 많은  $Q_1$  값들(로딩 조건들)과 함께 베타, 알파+, 및 알파-의 가능한 조합들을 통해 반복하도록 이루어지며,  $i_1$ ,  $i_b$ ,  $i_1$ 의 총 고조파 왜곡, 및  $i_b$ 의 총 고조파 왜곡에 대한 4개의 행렬들을 채운다. 조합이 다이오드 역회복 손실을 피한다면, 행렬들 내의 대응하는 지점들은 제곱평균 제곱근  $i_1$ , 및

$i_b$  값들, 및 총 고조파 왜곡 값들로 채워진다. 또한, 모든 스위칭 천이들에서의 스위칭 전류 및 각각의 상태에 대한 도전 전류가 절감된다.

[0045] 누적된 THD 데이터는 도 8에 도시된 바와 같이 허용가능성 행렬로 표시될 수 있다. 다이오드 역회복 손실을 피할 수 없는 백색 영역들은 무시된다. 이 예가  $180^\circ$ 의 베타 값에 대해 행하여졌으므로, 대각선(이때, 알파+ = 알파-)은 SVC 제어와 상관된다. 부가적으로, 알파+ = 알파- = 0인 지점은 ADC 제어와 상관된다.

[0046] 전류가 대략 6.2A와 3.7A 사이에서 제어된다면 또는 0.95와 0.57 사이의 정규화된 전류라면, 다이오드 역회복 손실을 SVC 제어에 의해 피하는 것이 불가능하다. 보다 낮은  $Q_1$  값들에 대해서 다이오드 역회복 손실을 피하기가 더 어려워진다. 도 9는 도 8과 비교되어  $Q_1$  값을 감소시키는 효과를 예시할 수 있는 허용가능성 행렬이다. 허용가능성 행렬들은 SVC 제어가 다이오드 역회복 손실을 피하지 못한다는 것을 명백히 나타낸다. 별도의 허용가능성 행렬이 각각의 상이한 베타 값에 대해 구성되지만, 허용가능성 행렬들의 평가는 ADC 제어가 다이오드 역회복 손실을 피한다는 것을 나타낸다. 도 10은 도 8 및 도 9와 비교되어 변화하는 베타의 효과를 예시할 수 있는 다른 허용가능성 행렬이다.

[0047] 도 10에서, 원점에서의 지점은 대략 4.6A에 대응하며, 이때 도 9에서 원점에서의 지점은 약 6.5A에 대응한다. 둘 모두의 경우들에서, 다이오드 역회복 손실을 피한다. 그러므로, ADC 제어를 사용하면, 전류는 다이오드 역회복 손실을 피하면서 그의 최대 값의 72%로 하향 제어되었다. 이는 48.2%의 시스템 내 전력 전송 감소에 대응하는데, 이는 전류와 전력 사이에 제곱 관계가 있기 때문이다. 그러나,  $I_1$ 에 대한 THD와 관련하여 가혹한 가격이 지불되었고, 그 값은 10%만큼 높다. 이는, 다이오드 역회복 손실을 피하면서 합리적인 THD를 제공하도록 AVC가 제안된 경우이다.

[0048] 일 실시예에서, 도 36에 도시된 바와 같이, 6.57A RMS의 최대 주 트랙 전류(primary track current)( $i_1$ ) 및 1.5의 비  $L_b/L_1$ 에 대해 하드웨어가 설계되었다. LCL 컨버터를 설계하기 위해, 요구되는  $X_1$ 이 다음과 같이 먼저 결정되며,

## 수학식 8

$$X_1 = \frac{2\sqrt{2}V_{dc}}{\pi(i_1)_{max}}$$

[0049] 여기서,  $V_{dc}$ 는 H-브리지에 대한 입력 DC 전압이다.

[0051]  $X_1$ 을 사용하면, 인더턴스 및 커패시턴스 값들이 다음을 사용하여 결정될 수 있다:

## 수학식 9

$$X_1 = \frac{1}{\omega C_1} = \omega L_1 = \frac{\omega L_b}{\gamma} = \frac{1}{\omega C_b(\gamma - 1)}$$

[0053] 이 수학식에서, 감마는 비이며, 이에 의해  $\gamma = (L_b/L_1)$ 는 다이오드 역회복 손실을 피하는 영역들에 대해 상당한 영향을 미치는  $C_b$ 의 크기를 결정한다. 따라서, 감마는 다이오드 역회복 손실을 피하는 시스템의 설계에서 중요한 파라미터이다. 비  $L_b/L_1$ 이 작을수록, 다이오드 역회복 손실을 피할 수 있는 영역들은 더 크다. 그러나, 얻어질 수 있는 최소 비는,  $C_b$ 가 무한대보다 클 수 없기 때문에 1이다. 1.5의 비는 ( $C_b$ 의 허용가능한 값으로) 회로를 구현가능하게 유지하기에 충분히 크고, 다이오드 역회복 회피를 위한 사용가능한 영역들을 제공하기에는 충분히 작다. 도 11은 사용될 수 있는 값들의 목록을 나타낸다. 인더터들은 원하는 값들을 얻도록 맞춤 튜닝되며, 커패시터들은 뱅크(bank)들로 있어서 미세 튜닝에 용통성을 제공한다.

[0054] 일단 모든 이러한 파형들 및 데이터가 계산되었다면, 특정  $Q$ 에서의 다이오드 역회복 손실을 피하는 최적의 궤적, 감마, 반사 임피던스 및 구성요소 공차가 THD로부터 계산된 최저 가중 지수, 스위칭 손실 및 도전 손실에

기초하여 결정될 수 있다. 최적의 궤적은 출력 전류를 최대 설계 값으로부터 소정의 사전결정된 양으로 하향 조절할 제어 각도들이어야 한다. 그러나, 이 조건을 여전히 충족시킬 수 있는 지점들의 수는 매우 크고, 최적의 궤적을 맵핑하는 것은 어렵다.

## 수학식 10

$$P_{\text{가중}} = a_0 \cdot THD + a_1 \cdot P_{\text{스위칭 손실}} + a_2 \cdot P_{\text{도전 손실}}$$

[0055]

[0056]

### 3. 분석 솔루션을 통한 최적의 궤적

[0057]

최적의 궤적을 결정하는 하나의 접근법은 분석 함수 공식화를 통한다. 이 접근법은 주파수 도메인 스펙트럼 분석에 대한 확장이다. 여기서, 그래픽, 계산 및 최적화 방법들을 포함하는 분석 기술들 중 일부는 최적의 궤적을 해석하는 데 사용된다. 주파수 분석을 실행하기 위해, 전체 주파수 분해가 사용된다. 주파수 분해는 2개의 단계들로 이루어지는데, 입력 전압은 AVC 제어 알고리즘 및 LCL 공진 네트워크의 주파수 응답에 의해 생성된다. 주 트랙 전류에 대한 주파수 성분들의 진폭은,

## 수학식 11

$$I_1(n) = V_{ab}(n) \cdot Y_{V1}(n\omega_0)$$

[0058]

[0059]

이고, 여기서  $n$ 은  $n$ 차 고조파 성분,  $Y_{V1}$ 은 네트워크의 입력 전압에 대한 주 트랙 전류의 어드미턴스이고,  $\omega_0$ 은 기본 공진 각주파수이다.

[0060]

유사하게, 브리지 전류는,

## 수학식 12

$$I_b(n) = V_{ab}(n) \cdot Y_{Vb}(n\omega_0)$$

[0061]

[0062]

이고,  $Y_{Vb}$ 는 네트워크의 입력 전압에 대한 브리지 전류의 어드미턴스이다. 둘 모두의 변수들의 계산은 매우 복잡하고, 각각은 고려되어야 하는 진폭 및 위상 성분들 모두를 갖는다.

[0063]

$V_{ab}$ 에 대해, 진폭 및 위상 성분들은 다음과 같다:

## 수학식 13

[0064]

$$= \frac{|V_{ab}(n)|}{\sqrt{\frac{V_{dc}}{n\pi} \cdot \left(4 + 2\cos(n\alpha_+) - 2\cos(n\beta) + 2\cos(n\alpha_-) - 2\cos(n(\beta + \alpha_-)) - 2\cos(n(\beta - \alpha_+)) - 2\cos(n(\beta - \alpha_+ + \alpha_-))\right)}}$$

## 수학식 14

[0065]

$$\arg(V_{ab}(n)) = \tan^{-1} \frac{\sin(n(\beta - \alpha_+)) + \sin(n\beta) + \sin(n\alpha_-)}{1 - \cos(n(\beta - \alpha_-)) - \cos(n\beta) + \cos(n\alpha_+)}$$

[0066]

둘 모두의 진폭 및 위상에 대한 수학식들은 미분 및 적분의 직접적인 계산 방법들을 사용하여 분석적으로 예측하기 어렵다. 그러므로, 분석 단순화 방법들이 직접적인 계산 방법들을 사용하기 전에 사용된다. 여기서, 분

석 계산 기술들 이전에 함수의 특성을 결정하기 위해 그래픽 기반 접근법이 먼저 사용될 수 있다. 도 12 및 도 13은  $V_{ab}$ 의 기본 진폭 및 위상 성분을 각각 나타낸다. 게다가, 제2 고조파 성분 진폭 및 위상 성분이 도 14 및 도 15에 각각 도시되어 있다. 다른 고조파 성분들이 또한 분석될 수 있지만, 여기에는 도시되지 않는다. 다른  $\beta$  각도들에 대한 플롯들이 또한 분석될 필요가 있지만, 여기에는 도시되지 않는다.

[0067] 회로의 어드미턴스는 LCL 네트워크에 대해 결정될 수 있다. 주 트랙 및 브리지를 포함하는 2개의 어드미턴스들이 고려된다. 브리지 어드미턴스는 다이오드 역회복 손실들이 제거되는지를 결정하며, 주 트랙 어드미턴스는 기본 전류 및 트랙 전류 내의 THD를 결정한다. 첫째로, 브리지 어드미턴스가 분석된다. 소정의 감마 비를 갖는 LCL 네트워크에 대해, 그 네트워크의 임피던스는,

### 수학식 15

$$Z_{in}(\omega) = R_{in}(\omega) + jX_{in}(\omega)$$

### 수학식 16

$$[0069] R_{in}(\omega) = R_1 \left( \frac{1}{(1 - \omega_n^2)^2 + (\omega_n/Q_1)^2} \right)$$

### 수학식 17

$$[0070] X_{in}(\omega) = j\omega_0 L_1 \left( \omega_n \gamma - \frac{\gamma - 1}{\omega_n} + \frac{\omega_n - \omega_n^3 + (\omega_n/Q_1)^2}{(1 - \omega_n^2)^2 + (\omega_n/Q_1)^2} \right)$$

[0071]이고, 여기서  $\omega_n$ 은 정규화된 주파수이고,  $\omega_0$ 은 기본 주파수이다.

[0072] 기본 저항에 대해, 이는 다음과 같이 단순화될 수 있다:

### 수학식 18

$$[0073] R_{in}(\omega_0) = Q_1 X_1$$

[0074] 보다 높은 고조파 저항들은 기본 및 반응 임피던스들보다는 실질적으로 더 낮으며, 그들은 선형 분석에서 무시될 것이다.

[0075] 입력 리액턴스  $X_{in}$ 에 대해, 뒤의 2개 항들은 첫번째 항과 비교하여 이보다 더 높은 고조파에서 0에 비교적 가깝고, 수학식의 진폭은 첫번째 항에 의해 좌우된다. 2차 고조파는 다음에 의해 근사화될 수 있다:

### 수학식 19

$$[0076] Z_{in}(2\omega_0) = j\omega_0 L_1(2\gamma - 0.5)$$

[0077] 2차 고조파를 넘는 고조파들에 대해, 이는 다음에 의해 근사화될 수 있다:

## 수학식 20

$$Z_{in}(n\omega_0) = j\omega_0 L_1 n\gamma$$

[0078]

[0079] 다이오드 역회복을 피하기 위한 중요한 방법이, 기본 동위상 성분이 통상적으로 다이오드 역회복을 피할 수 없기 때문에, 더 높은 차수의 고조파들을 브리지 전류 파형에 도입시키는 것이라는 것에 주목하여야 한다. 그러므로, 이러한 고조파 분석은 정상적으로 무시되어서는 안되는 중요한 단계이다.

[0080]

[0080] 발생하는 하나의 의문은, 브리지 전류를 정확하게 결정하기 위해 얼마나 많은 고조파들이 유지될 필요가 있느냐는 것이다. 임피던스 정확도는, 브리지 내로의 반응 전류가  $90^\circ$  벗어난 위상의 것이기 때문에, 실제 전류와 반응 전류의 비에 비례하는 것으로 밝혀졌다. 그러므로,

## 수학식 21

[0081]

$$e_Z \propto \frac{X_{in}(n\omega_0)}{R_{in}(\omega_0)} = \frac{n\gamma}{Q_1}$$

[0082]

전류 정확도는 다음과 같다:

## 수학식 22

[0083]

$$\text{정확도}_{lb} \propto \frac{1/V_{ab}(n\omega)}{1/e_Z} \propto \frac{\gamma n^2}{Q_1} > \text{계수}$$

[0084]

[0084] 이 수학식을 사용하여, 정확도 계수(accuracy factor)=10에 대한 회로를 분석하는 데 요구되는 n차 고조파가 도 16에 도시되어 있다. 이는,  $\gamma=1.5$  및  $Q_1=4$ , 대략 7의 N차가 요구될 때 일 실시예에 대한 전형적인 동작 조건들에 대해 발명자들에 의해 밝혀졌지만, 이는 상이한 동작 조건들에 대해 변한다. 4의  $Q_1$ 이 사용되는데, 그 이유는  $Q_1=4$ 를 넘어서는 다이오드 역회복 손실들을 피할 수 있고 이들이 분석될 필요가 없기 때문이다.

[0085]

[0085] 차수가 결정된 후, LCL 컨버터에 대한 임피던스 및 전압 입력이 함께 결정될 수 있다. 이는 네트워크의 임피던스를 근사화하도록 인덕턴스를 사용함으로써 달성될 수 있으며, 이때 복소 부분은 입력 전압 진폭 및 위상 성분들이다. 입력 전압의 진폭 및 위상의 소정의 비를 결정함으로써, 다이오드 역회복 손실들을 피할 수 있다. 이들을 이용하여, 주 트랙 전류의 THD는 주 트랙의 어드미턴스에 의해 결정될 수 있다.

[0086]

[0086] 여기서 해결되는 2개의 문제점들이 있다는 것이 요약될 수 있다. 첫번째는 다이오드 역회복 손실을 피하는지의 여부이다. 제2 계산은 역회복 손실을 피하는 지점을 측하고, 동작을 위한 최적의 THD를 갖는 경향을 계산한다.

[0087]

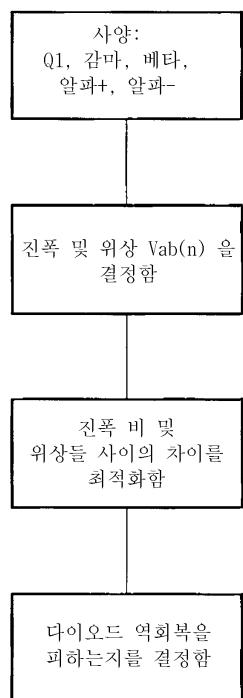

[0087] 역회복 손실 회피의 계산을 위한 예시적인 플로우차트가 도 17에 도시되어 있다. 루틴은 주파수 성분들을 결정하도록 시스템 파라미터들을 사용함으로써 시작된다. 이어서, 광범위한 베타, 알파+, 알파- 각도 조건들에 걸쳐 다이오드 역회복 조건을 예측하도록, 진폭 성분에 대한 최적 비를 결정하는 루틴이 사용된다. 최적의 경향이 결정된 후, 한 세트의 제어 각도들의 결과들은 계산 루틴의 출력이다.

[0088]

[0088] 다이오드 역회복 손실들을 피하는 경향이 결정된 후, 솔루션들은 이어서 THD 값들과 관련하여 최적의 제어 경향을 결정하는 제2 계산 루틴에 대한 입력이 된다. 이를 루틴들은 반드시 2단계의 연대적 순서 계산을 취할 필요가 있는 것은 아니다. 2단계들 사이에서 뒤로 그리고 앞으로 계산하는 반복 프로세스는 보다 최적인 결과들을 생성하는 것으로 나타났다.

[0089]

4. TSP를 해석하는 알고리즘들을 통한 최적의 궤적

[0090]

제어 한계들의 본질로 인해, 제어 각도들인 알파+, 알파-, 및 베타의 최대 점프 크기는 인접한 정규화된 트랙

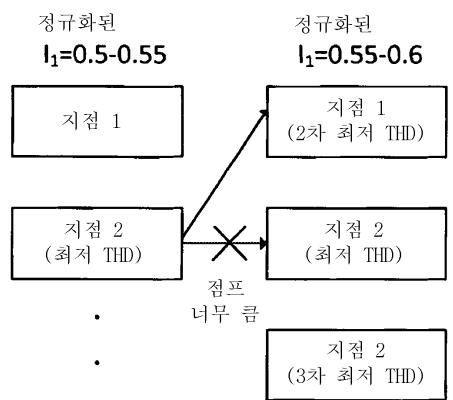

전류들에 대한 경계로 구속되어야 한다. 이 경계를 도입함으로써, 최적의 THD 경로는 결정하기가 어려워지는데, 그 이유는 국부 지점에서의 최저 THD가 궤적을 통한 보다 높은 전체 THD를 상쇄시킬 수 있기 때문이다. 이러한 특정 유형의 문제점은 TSP(Travelling Salesperson Problem)로서 정량화될 수 있다. TSP는 수학 및 컴퓨터 과학에서 잘 알려진 극히 복잡한 문제이다. 대략 100 단계를 또는 이동 노드들에 의해, 억지 방식(brute force manner)으로 이 문제를 계산할 가능성은 실제로 실행불가능하여  $6 \times 10^{169}$  개의 비교를 요구한다. 그러므로, 계산 시간을 현저히 감소시켜 근최적 AVC 솔루션을 결정하는 알고리즘들은 절대적인 최적 솔루션을 보장함이 없이 구현된다. 계산된 솔루션은 통상적으로 AVC에 대해 최적에 매우 가깝다. 여기서, 그리디 세일즈퍼슨 알고리즘은 계산 자원들을 최소화하면서 근최적 궤적을 결정하는 데 이용될 수 있다. TSP를 해석하는 많은 다른 알고리즘 옵션들이 또한 사용될 수 있다. LCL 컨버터들의 AVC 제어를 위한 최적 궤적을 해석하는 데 사용될 수 있는 TSP 알고리즘들의 가능한 변형들 중 일부가 이하에서 설명된다.

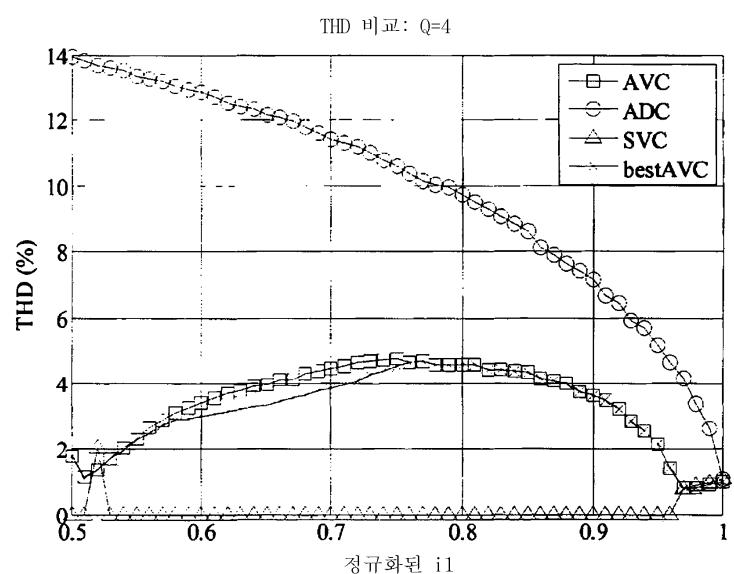

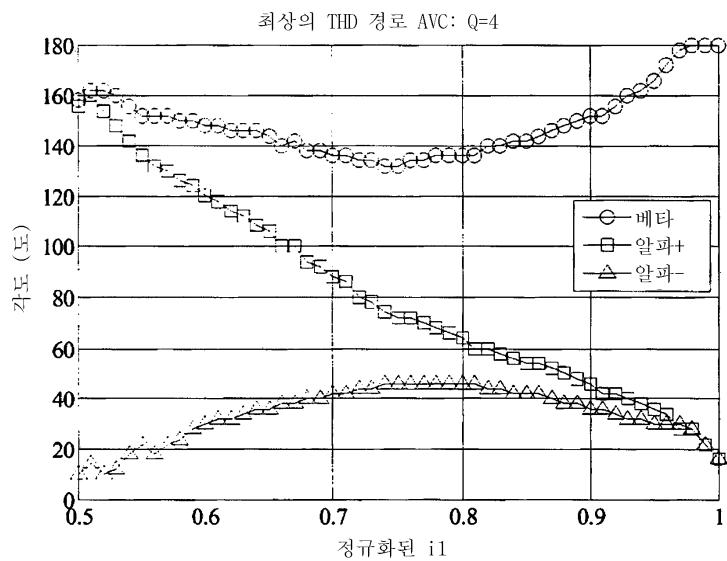

[0091] 그리디 세일즈맨 알고리즘 예가 도 18에 도시되어 있다. 알고리즘은  $I_1=0.5-0.55$ 의 정규화된 전류 범위에서 시작되고, 최저 THD 지점은 데이터 세트로부터 결정된다. 알고리즘은 이어서 가장 가까운 이웃들( $I_1=0.55-0.6$ ) 내의 지점들을 살펴보기 시작하고, 소정의 최대 점프 각도(특정 경우에는 6도)의 제약을 충족시키는 최저 THD 지점을 결정한다. 이 경우에, 데이터 세트의 최저 THD 지점은 선택되지 않는데, 그 이유는 점프 각도가 너무 크기 때문이다. 이 프로세스는,  $I_1=0.5-1$ 로부터의 완전한 궤적이 맵핑될 때까지 반복된다. 알고리즘은, 시작에서의 제2의 최상의 THD 지점을 사용하여 프로세스를 다시 개시하여, 발견될 수도 있는 다른 최적 궤적이 존재하는지를 결정할 것이다. 이는, N회 동안 반복될 수 있으며,  $Q_1=2$ 의 예의 경우, 단 하나의 반복만이 요구된다. 도 19는 그리디 세일즈퍼슨 알고리즘을 사용하여 AVC에 대해 결정된 궤적을 도시한다. 도 19에서, "bestAVC"가 AVC의 상부에 중첩된다. 절대 최적치의 여분의 플롯이 또한 비교 목적으로 추가된다. 이것이 TSP를 해석하는 것 및 최상의 가능한 솔루션을 찾는 것과 동등하다는 것에 주목한다. 몇몇 시뮬레이션들에서 최상의 가능한 솔루션들은, 모든 가능한 옵션들이 억지 방법들을 사용하여 계산될지라도 점프 각도 제약들로 인해 결코 달성되지 못할 수 있다. 어떠한 점프 각도 제약도 없는 최적치는 간단한 그리디 세일즈퍼슨 알고리즘 솔루션과 거의 동일하다는 것을 알 수 있다. 점프 각도 제약이 없는 절대 최적 솔루션 및 그리디 세일즈퍼슨 솔루션에 대한 요구되는 알파+, 알파-, 및 베타 각도들이 도 20 및 도 21에 플로팅되어 있다. 계산된 각도들은 거의 동일하며, 이 경우에 그리디 세일즈퍼슨 알고리즘이 가장 최적인 솔루션을 얻기에 충분한 것 이상임을 알 수 있다. 유사한 계산이  $Q_1=4$ 에 대해 실행되었고, 그 결과들이 도 22에 도시되어 있다. 이 경우에, 최상의 솔루션은 그리디 세일즈퍼슨 솔루션과는 약간 상이하였다. 이는, 그리디 세일즈퍼슨 알고리즘이 최적인 것이 아니라, 점프 각도들이 제약되지 않는 경우에 최상의 것만큼 양호하지 않을 수 있다는 것을 반드시 의미하지는 않는다. 이러한 두 가지 경우들에 대한 점프 각도를 사이의 차이가 도 23 및 도 24에 도시되어 있다.

[0092] 바람직한 궤적이 결정된 후, 이것의 물리적 실현은 마이크로제어기에 저장된 루업 테이블을 사용하여 완성될 수 있다. 그러나, 이는  $Q_1$ 의 상이한 동작 조건들에 대해 많은 지점들을 요구할 수 있다. 지점들의 개수를 감소시키는 하나의 방법은 최소 제곱 맞춤(least squares fitting)에 의한 다항식 근사화를 사용하는 것이다. 곡선 맞춤 예가 도 25에 도시되어 있다. 여기서, 베타 각도를 추정하는 데 4차 다항식이 이용되며, 근사화가 매우 정확하다는 것을 알 수 있다.

[0093] 최적의 궤적을 결정하는 방법이 후술된다. 여기서, 4차 최소 제곱 다항식이 일례로서 사용된다. 변수  $I_1$ 만이 근사화에 포함되며, 모든 다른 변수들은 상수들로서 간주되어 근사화에 고유하게 포함된다. 전술되어진 정규화된 특성들을 근사화하기 위해, 근사화 함수는 다음의 형태이다:

### 수학식 23

$$f(\alpha_+, \alpha_-, \beta) = a_4 I_1^4 + a_3 I_1^3 + a_2 I_1^2 + a_1 I_1 + a_0$$

[0094] 그리고, 다항식에 대한 값들은,

## 수학식 24

$$A = \begin{bmatrix} a_4 \\ a_3 \\ a_2 \\ a_1 \\ a_0 \end{bmatrix} = (X^T X)^{-1} X^T Y$$

[0096]

[0097]로부터 얻어질 수 있으며, 이때  $X$ 는 알파+, 알파-, 및 베타에 대한 데이터 행렬이다.  $Y$ 는 이 경우에 있어서 정규화된 주 트랙 전류와 같은 정규화된 관심 출력 데이터에 대한 데이터 행렬이다.  $X$  행렬은 정사각형이 아닐 가능성이 매우 크기 때문에, 직접 행렬 역변환은 가능하지 않다. 따라서, 의사 역 프로세스(pseudo-inverse process)가 통상적으로 요구되며, 이때 행렬 역변환이 발생할 수 있도록 행렬  $X$ 의 전치(transpose)가 추가되어 이를 정사각형 행렬로 변환시켜야 한다.

[0098]

2개 이상의 동작 파라미터들을 포함하는 하나의 다항식을 이용하는 다변수 회귀 방법(multi-variable regression method)들이 또한 옵션이다. 일례로서, 다변수 회귀를 사용하는, 상기 문제에 대한 최소 제곱 맞춤 다항식은 아래와 같다:

## 수학식 25

$$\begin{aligned} f(\alpha_+, \alpha_-, \beta) = & a_3 I_1^3 + a_2 I_1^2 + a_1 I_1 + a_0 + b_3 Q_1^3 + b_2 Q_1^2 + b_1 Q_1 + c_2 Q_1^2 I_1 \\ & + c_1 I_1^2 Q_1 + d_1 I_1 Q_1 \end{aligned}$$

[0099]

[0100] 이 예에서, 3차 표면 근사화가 주어진다. 다항식들의 계수들은 수학식 24의 의사 행렬 역변환 프로세스의 유사한 프로세스를 사용하여 계산된다. 다항식에서의 계수들의 개수가, 다항식에 대한 차수의 조합들이 또한 포함되어야 하기 때문에, 표면 근사화를 위해 현저히 증가한다는 것에 주목한다.

[0101]

### 5. AVC용 감지 회로들

[0102]

감지 회로는 로딩 조건( $Q_1$ ) 및 반사 반응 임피던스 및 구성요소 공차들을 측정하는 데 사용될 수 있다. 회로의  $Q_1$ 을 측정하기 위해, 도 11에 도시한 바와 같이, 브리지 전류를 측정하는 전류 변환기를 갖는 간단한 정류기가 사용된다. rms 브리지 전류는 대략적으로,

## 수학식 26

$$i_b = \frac{V_{ab} R_{r1}}{X_1^2}$$

[0103]

[0104]

과 관련되며, 여기서  $V_{ab}$ 는 LCL 네트워크로의 AC 입력 전압이고,  $R_{r1}$ 은 부 핵심의 반사 저항이고,  $X_1 (= \omega L_1)$ 은 LCL 네트워크의 리액턴스이다. 이 수학식은 어떠한 반사 리액턴스도 없음을 가정한다.  $X_1$ 이 설계 값이고  $V_{ab}$ 가 제어기 입력이므로, 둘 모두의 변수들은 공지되고  $R_{r1}$ 은  $i_b$ 를 측정함으로써 직접적으로 추정된다.  $Q_1$ 에 대한  $R_{r1}$ 의 관계는 수학식 1에서  $Q_1 = \omega L_1 / R_{r1}$ 로서 정의된다.

[0105]

브리지 인덕터 전류를 측정하는 다른 대안은 도 26에 도시한 바와 같은 전력 저항기들 및 홀 효과 센서들을 사용하는 것이다. 이들 감지 회로 토폴로지(topology)들의 조합의 임의의 사용이 또한 가능하다.

[0106]

주 트랙 코일에 대한 반사 저항을 결정하기 위해, 보다 개선된 감지 회로가 사용될 수 있다. 감지 회로는 브리지 인덕터 전류를,

## 수학식 27

$$i_b = \frac{V_{ab}Z_1}{X_1^2} = \frac{V_{ab}}{X_1^2}(R_{r1} + jX_{r1})$$

[0107]

[0108]

로서 여전히 측정함으로써 쉽게 얻어질 수 있으며, 이때  $X_{r1}$ 은 부 핵업의 반사 저항이다. 그러므로,  $V_{ab}$ 에 대한  $i_b$ 의 기본 성분의 위상을 측정함으로써, 실제 및 반응 반사 임피던스들이 결정된다. 앞에서 개발된  $i_b$ 의 진폭 측정에 더하여, 위상 측정 회로가 도 27에서 도입된다.  $i_b$  및  $V_{ab}$  둘 모두의 위상을 획득하기 위해 위상 고정 루프(Phase Lock Loop, PLL) 회로가 사용될 수 있고, 그 위상들 사이의 차이는 OR 게이트를 통과하게 된다.  $I_b$  및  $V_{ab}$ 는 50% 듀티 사이클 파형을 가질 것이며, 이들이 반사 저항만을 나타내는 완전 동위상이라면, OR 게이트는 50% 듀티 사이클을 출력할 것이다. 반응 부하들에 대해,  $i_b$  및  $V_{ab}$ 는 완전히 동위상이지는 않을 것이며, 그러므로 OR 출력은 50% 출력보다 클 것이다.  $V_{ab}$ 가  $i_b$ 를 선행하면,  $X_{r1}$ 은 용량성이어야 하고, 유사하게  $X_{r2}$ 는  $i_b$ 가  $V_{ab}$ 를 선행할 때 유도성일 것이다. LCL 네트워크가 브리지 전류측에서 측정될 때 유도 반사 임피던스를 반전시킨다는 것에 주목해야 한다. 저역 통과 필터들 및 대역 통과 필터들과 같은 다른 회로들이 PLL 이전에 추가되어, 고조파 성분들을 제거함으로써 위상 검출의 정확도를 개선할 수 있다. 파형의 필터링된 버전이 도 28에 도시되어 있다. 위상 진폭은 필터링 후의 브리지 전류에 대해 결정되며,  $V_{ab}$ 의 기본 진폭 및 위상 성분은 수학식 13 및 수학식 14를 사용하여 결정된다. 게다가, 다른 게이트 레벨 구현예들이 위상을 측정하는 데 사용될 수 있다. 또한, 아날로그-디지털 변환(Analog to Digital Conversion, ADC)은 고주파 파형을 샘플링하는 데 사용되며, 디지털 신호 프로세서(Digital Signal Processor, DSP)들은 아날로그 회로 상대물에 의해 개발된 유사한 방식으로 진폭 및 위상 성분들을 둘 모두를 측정하는 데 사용된다. 또한, 이들 회로들 중 임의의 것의 합리적인 방식으로의 조합은 또한 위상 및 진폭  $i_b$  둘 모두를 검출하고 측정하여서, 회로의 반사 저항 및 리랜턴스를 추정 할 수 있다.

[0109]

도 29에 예시된 요약 블록도는 센서 블록의 동작을 개괄한다. 먼저, 주요한 관심 변수들이 측정되거나 샘플링 된다. 이어서, 전술된 방법들 - 이로 한정되지 않음 - 을 사용하여 측정치들의 진폭 및 위상 성분들이 얻어진다. 이어서, 진폭 및 위상 성분들은 다이오드 역회복이 달성될 수 있는지의 계산에 사용된다.

[0110]

제조 동안 공진 전력 컨버터들에서 저비용을 유지하기 위해, 보다 낮은 공차들을 갖는 튜닝 구성요소들이 사용되어야 한다. 이는 LCL 컨버터에 여분의 반응성 부하를 추가하며, 그의 성능 특성을 변경한다. 이를 보상하기 위해, 위에서 개발된 전압 및 전류 센서들이 공진 커패시터 전압 및 주 트랙 전류를 측정하는 데 사용될 수 있다. 그러나, 이는 대량 제조되는 시스템들에서는 너무 고가일 수 있다. 다른 대안은 최악의 경우의 튜닝 부정합에 대한 다이오드 역회복 손실들을 피하도록 그리고 정상 동작 동안에 덜 최적인 THD, 스위칭 손실, 및 도전 손실 특성에서 동작하도록 제어 궤적을 선택하는 것이다. 설계 절차들은 몬테-카를로(Monte-Carlo) 분석 및 강인 시스템 설계 기술들을 모두를 사용한다. 이러한 분석 뒤의 아이디어는, 광범위한 구성요소 공차들(예컨대, ±10%)에 대해 LCL 공진 네트워크를 시뮬레이팅하는 것이다. 광범위한 계산 또는 시뮬레이션들은 튜닝 구성요소들의 모든 조합들에 대해 수행되어, 다이오드 역회복을 피하는 것과 관련된 최악의 경우의 조건이 충분한 여유를 가지고 충족됨을 보장하는 것을 도와야 한다.

[0111]

### 6. AVC용 제어기들

[0112]

동작 동안 최적의 궤적을 달성하기 위해, 제어 시스템이 실제로 구현되어야 한다. 주 제어 변수는 LCL 컨버터의 출력 전류의 조절이다. 시스템 식별 또는 천이 분석 기술들을 사용하여 컨버터 특성을 모델링한 후에, 감소된 차수의 전달 함수가 추론된다. 이 전달 함수를 사용하여, 단순 비례 적분(PID) 제어기를 갖는 페루프 시스템이 도 30에 도시된 바와 같이 구현될 수 있다. 제어기는, 도 31에 도시된 바와 같이,  $i_b$ ,  $V_{ab}$ ,  $V_c$ ,  $i_c$ 와 같은 요구되는 입력들과 함께, 출력 전류 측정치로부터의 입력을 획득하며, 마이크로제어기 내의 사전로딩된 톱업 테이블을 통해 H-브리지를 위한 최적의 제어 각도들을 결정한다. 비례 적분 미분(PID), 퍼지 로직, 강인 제어기들, 상태 공간 제어기들, 또는 기타의 것들과 같은 다른 제어기들이 또한 사용될 수 있다. 게다가, 이 제어 함수의 디지털 및 아날로그 구현들 둘 모두가 가능하다.

[0113]

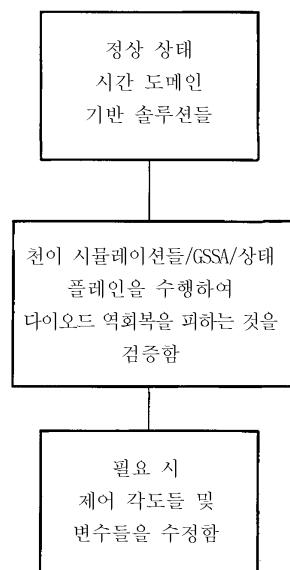

다른 방법들 대신에 AVC를 사용하여 LCL 컨버터를 제어하는 차이점들 중 하나는 천이 조건들 하에서 다이오드

역회복을 피하는 능력이다. 이는 시간 도메인에서 계산된 정상 상태 솔루션들로부터 보장하기가 매우 어렵다. 그러므로, 추가의 결정적 동작 조건들이 제어기 설계에 포함되어 다이오드 역회복을 피하게 한다. 이는, 제어 각도에서의 시스템 이득이 상이한  $Q_1$  및 다른 파라미터들 하에서 변화할 필요가 있을 수 있기 때문이다. 이와 같이, 비선형성은 전통적인 제어기들 내에 도입되어 요구되는 응답 시간들을 달성하게 할 수 있다. 이 문제를 분석적으로 풀기 위해, 상태 플레인(state-plane) 분석 및 일반화된 상태 공간 평균화(generalized state space averaging, GSSA)가 제어기 설계에 포함될 수 있다. 대표적인 설계 프로세스의 플로우차트가 도 32에 도시되어 있다. 다이오드 역을 시간 도메인 정상 상태 솔루션들을 기초로 하여 피할 수 있는지를 검증하는 데 분석이 이용될 수 있다. 이것이 충족되지 않는다면, 2개의 옵션들이 이용가능하다. 제1 옵션은 천이 응답 및 정상 상태가 매우 유사하도록 매우 느린 속도로 트랙 전류를 상승시키기 위해 제어기에서 보다 낮은 이득을 사용한다. 그러나, 이는 일부 응용들에서는 항상 실용적인 것은 아니다. 다른 옵션은, 천이 동안, 역회복 손실들을 피하기에 충분한 여유가 여전히 이용가능하도록, 천이 순간의 브리지 전류를 더 크게 가중함으로써 최적의 궤적을 수정하는 것이다. 이는 수학식 10에서 가중치를 변화시키는 것을 수반한다.

[0114]

## 7. 소프트 스위칭식 고정 주파수 LCL 컨버터

[0115]

AVC의 구현으로, 다이오드 역회복 손실들을 완전히 피할 수 있다. 이와 같이, LCL 컨버터에서의 H-브리지는 전력 MOSFET들 또는 IGBT들의 턴-오프 손실들만을 가질 수 있다. 이러한 스위칭 특성에 의해, 전력 스위칭 소자들의 여분의 소형 커패시터들 또는 기생 출력 커패시턴스들은 제로 전압 스위칭(ZVS) 조건들을 달성하는 완전 소프트 스위칭식 컨버터의 설계를 도울 수 있다. 전형적인 회로 구조가 도 33에 도시되어 있다. ZVS 조건은 스위치 전압을 일시적으로 유지하는 데 커패시터들을 사용함으로써 달성될 수 있는 반면, 그를 통한 전류는 스위치 턴-오프 조건들 동안에 0으로 감소한다. 이는, 전압 천이가 턴-오프 조건 동안에 최소가 되게 하여서, 소프트 스위칭 조건들을 달성할 수 있게 한다. 그러나, 소프트 스위칭을 보장하기 위해 일부 설계 제약들이 존재하는데, 그 이유는 스위치들을 가로지른 커패시터들이 주의깊게 제어되어야 하거나, 여분의 커패시터들의 치명적인 단락 조건들이 발생하여 극한 조건들에서 심지어 더 높은 스위칭 손실들 또는 전력 소자 결함을 야기할 수 있기 때문이다. 스위치들이 턴-온되기 전에 커패시터가 완전히 방전되는 것을 보장하기 위해, 하기의 수학식이 충족되어야 한다:

## 수학식 28

$$C_{sn} = \frac{i_b(0)t_{dead}}{V_{dc}}$$

[0116]

여기서,  $t_{dead}$ 는 H-브리지의 불감 시간(dead time)(즉, H-브리지의 분로에서 슛-스루(shoot-through) 전류를 피하도록 스위칭 상태들을 변화시키기 전에 요구되는 시간)이고,  $i_b(0)$ 는 스위칭 순간의 브리지 인덕터 전류이고,  $V_{dc}$ 는 H-브리지에 대한 DC 입력 전압이다.

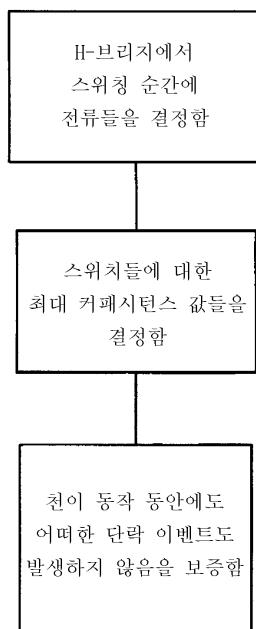

[0117]

스위치들을 가로지른 병렬 커패시터는 H-브리지에서 4개의 스위치들에 대해 반드시 동일한 것은 아닐 수 있다. 이는, 스위치들을 통한 전류가 4개의 스위칭 조건들( $S_1, S_2, S_3, S_4$ ) 하에서 상이하여서, 수학식 27에 따라 상이한 커패시턴스 값이 요구되기 때문이다. 도 34에 도시된 플로우차트는 최적의 커패시터 값들을 결정하는 데 사용될 수 있다. 플로우차트에서의 제1 단계는 스위칭 순간에 전류 값들의 범위를 결정하는 것이다. 스위칭 천이들 각각에서의 전류들의 예가 도 35에 도시되어 있다. 이를 전류 값들은 앞서 개발된 시간 도메인 분석 기술로부터 계산된다. 플로우차트에서의 계산 루틴은 스위치에서의 단락 이벤트가 나타나기 전에 허용되는 최대 커패시턴스를 결정해야 한다. 각각의 H-브리지 다리부(leg)에서의 커패시턴스 값들이 2개의 스위칭 순간들에 대해 공유된다는 것에 주목한다.  $S_1$  및  $S_3$ 은 함께 그룹화되어 한 세트의 커패시터 값들을 공유하고,  $S_2$  및  $S_4$ 는 함께 그룹화되어 다른 세트를 공유한다.

[0118]

스위칭 주파수를 일정하게 유지하면서 소프트 스위칭을 달성하도록 IPT 전원들을 위한 신규한 컨버터가 설계되었다(LCL 컨버터 및 AVC). 이 컨버터는 고정 주파수 및 소프트 스위칭이 쉽게 동시에 실현될 수 없는 IPT에서 전통적인 컨버터들보다 상당한 이득을 갖는다. 이러한 신규한 제어 기술은 컨버터가 한번에 둘 모두의 이점들을 포함하게 하였다.

[0119]

몇몇 구성들에서, 본 명세서에서 설명되는 시스템들 및 방법들은 (예를 들어, 전술된 바와 같이) 제어기에 의해

수행될 수 있다. 예를 들어, 제어기는 프로세서, 및 프로세서와 전자 통신하는 메모리를 포함할 수 있다. 몇몇 구성들에서, 메모리는 프로세서가 본 명세서에 설명된 시스템들 및 방법들을 가능하게 하는 프로세서-실행 가능한 명령들을 저장할 수 있다. 예를 들어, 프로세서는 프로세서가 알파 플러스(예컨대, 알파+), 알파 마이너스(예컨대, 알파-), 및 THD를 감소시키고 다이오드 역회복 손실을 피하게 하는 베타를 선택하게 하는 실행 가능한 명령들을 실행할 수 있다.

[0121] 하기의 예들은 단지 예시적인 것이며, 어떠한 방식으로든 본 발명을 제한하고자 하는 것은 아니다.

[0122] 예

[0123] 다양한 위에 개시된 그리고 다른 특징들 및 기능들, 또는 이들의 대안들이 많은 다른 상이한 시스템들 또는 응용들 내로 바람직하게 조합될 수 있다는 것을 알 것이다. 또한, 본 발명에서의 다양한 현재 예측되지 않거나 기대되지 않는 대안들, 변경들, 변형들 또는 개선들은 당업자에 의해 이후에 이루어질 수 있고, 또한 하기의 특허청구범위에 의해 포함되고자 의도된다.

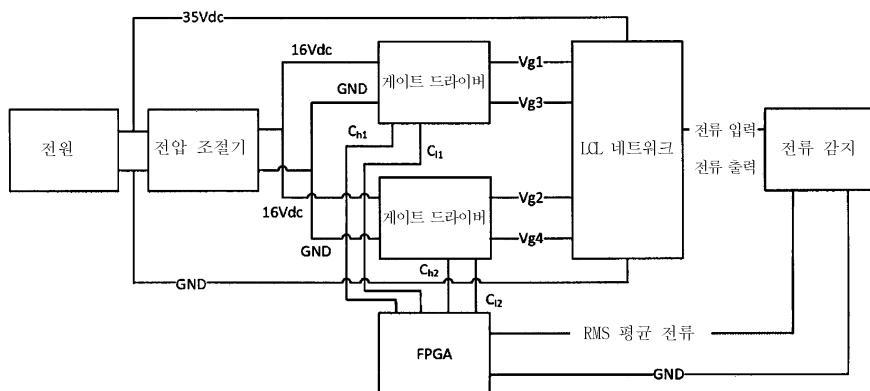

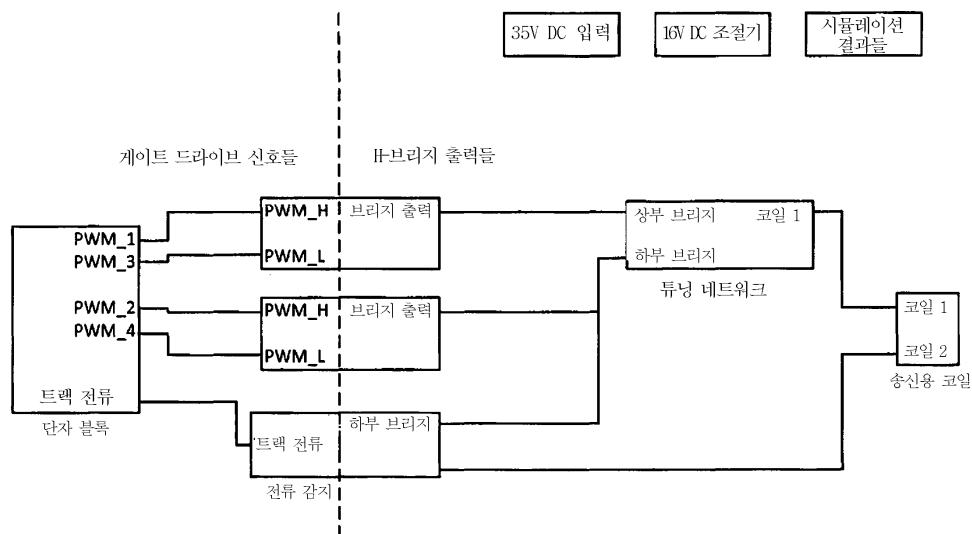

[0124] 도 36에 도시한 파라미터 값들을 갖는 장치의 일 실시예의 전체 설계 구성이 도 37에 예시되어 있다. 도 38은 게이트 드라이버들의 개략도이다. 도 39는 개시된 시스템을 통한 전류 경로를 예시한다.

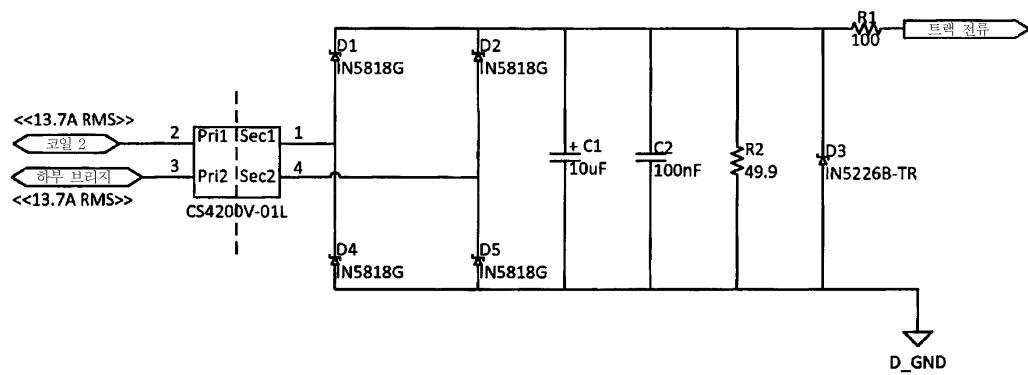

[0125] 도 40은 시스템의 일 실시예의 고 레벨 블록도를 도시한다. 나노보드(NanoBoard) 3000 제어기가 광 아이솔레이터(opto-isolator)들을 통해 회로의 나머지와 통신하기 때문에, 점선으로 된 청색 선은 절연을 나타낸다. 도 41은 LCL 컨버터의 공진 탱크를 도시한다.

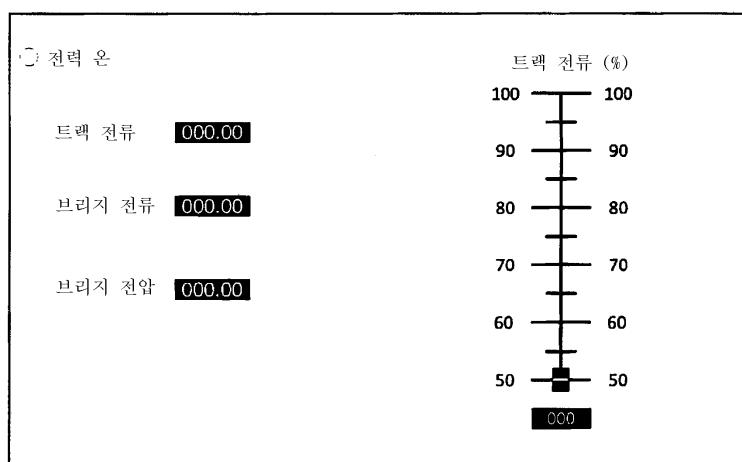

[0126] 이 실시예에서, 소프트웨어는 원하는 전류 값, 과전류 보호, 및 제어 시스템을 설정하기 위한 사용자 인터페이스를 제공한다. 이어서, 이러한 제어들은 타이밍 임계 게이트 레벨 제어들을 위한 필드 프로그래밍가능 게이트 어레이(Field Programmable Gate Array, FPGA)에서의 하드웨어 기술 언어(HDL) 설계를 제어하는 펌웨어로 전송된다. 도 42는 소프트웨어의 일반적인 개요를 도시하고, 도 43은 그래픽 사용자 인터페이스(GUI)의 스크린샷을 도시한다.

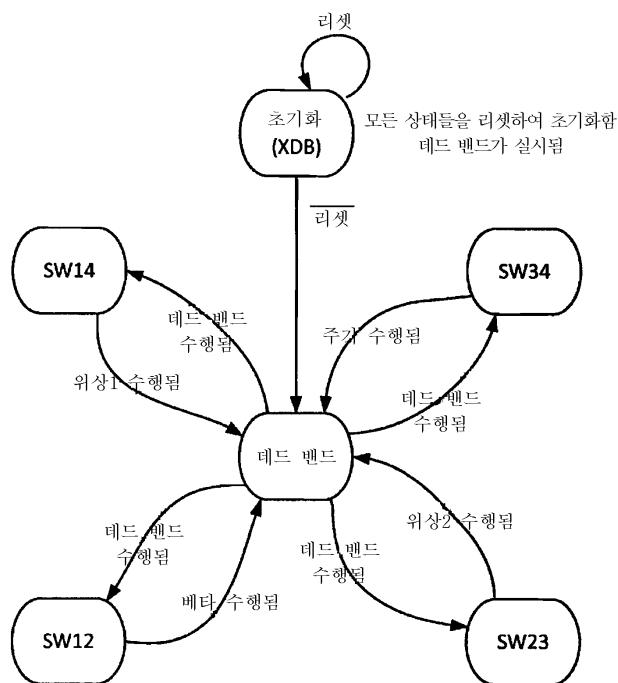

[0127] 이 실시예에서, 펌웨어는 HDL 설계 인터페이스를 통한 풀 브리지의 임계 타이밍 제어를 설정한다. 제어 변수들은 소프트웨어로부터 전달되고 유효성에 대해 검사되며, HDL 설계 인터페이스는 타이밍을 수정하는 데 사용된다. 펌웨어 및 HDL 설계는 또한 풀 브리지에 대한 보호를 제공하는데, 그 이유는 그들이 모든 스위칭 천이들에 대해 데드 밴드(dead band)를 시행하여, 동시에 턴-온되는 하이(high) 측 MOSFET 및 로우(low)측 MOSFET로부터 보호하기 때문이다. 펌웨어의 예시적인 흐름도가 도 44에 제공되어 있다.

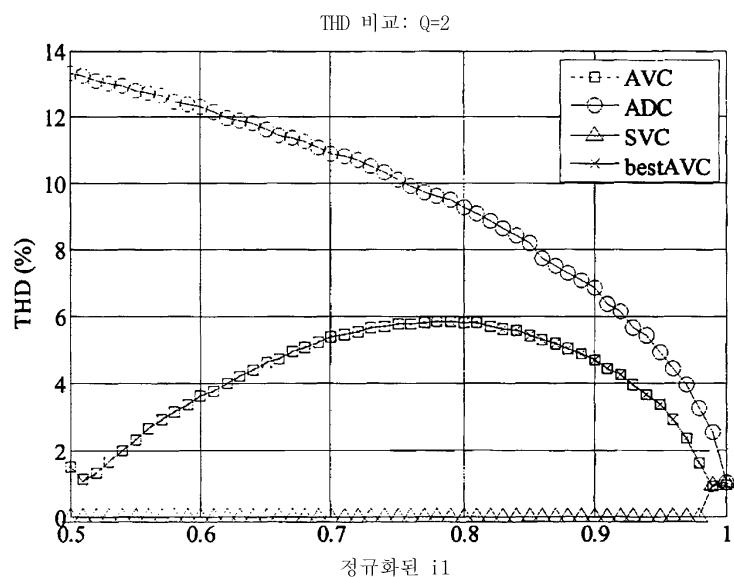

[0128] 개시된 AVC 방법 및 장치는, 도 8 내지 도 10에 도시된 바와 같은 다이오드 역회복 손실을, ADC 제어가 다이오드 역회복 손실을 피할 수 있는 동일한 범위에 걸쳐서, 피할 수 있도록 구현될 수 있다. 개시된 AVC 방법 및 장치는 또한 SVC 제어와 유사한 THD 결과들을 제공한다.

[0129] THD와 관련하여 AVC 이득들이 도 45에 요약되어 있는데, 여기서 ADC 및 SVC 제어 방법들에 비한 THD의 최대 개선 및 평균 개선이 나타나 있다.

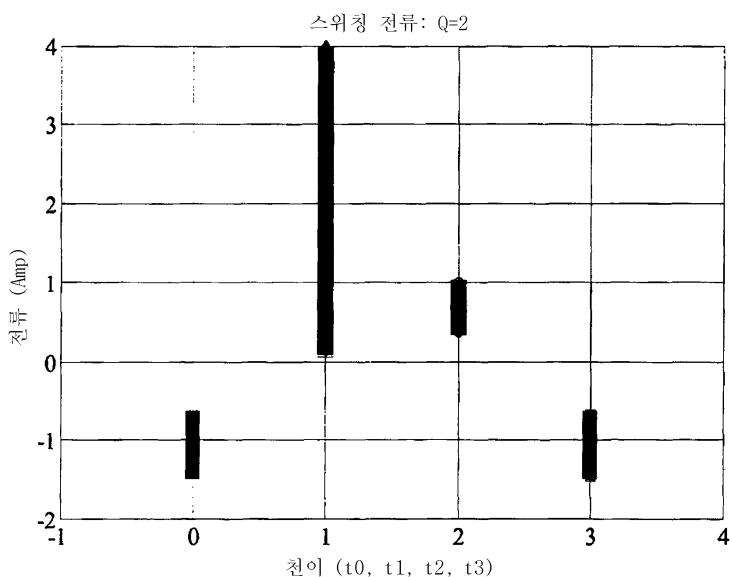

[0130] 개시된 AVC 방법 및 장치에 대한 시험 결과들이 도 46 및 도 47에 나타나 있으며, 이 도면들은 동일한 부하( $Q=2$ ) 및 동일한  $i_1$  (4.8A RMS)를 사용한 SVC 제어와 AVC 제어 사이의 비교를 도시한다. 이들 과형들에서, 전압( $V_{ab}$ ) 및 전류( $i_b$ )가 표기되어 있다. 이는, SVC 제어가 다이오드 역회복 손실을 피하지 못하고, 본 발명의 일 실시예에 따라 구현될 때의 AVC 제어가 다이오드 역회복 손실을 피한다는 것을 보여준다. SVC 과형 예(도 46)에서, 제1 및 제3 스위칭 천이들에서의 전류는 전압의 변화와 동일한 부호이다(즉, 전류가 양이고 전압이 상승 중이다). 이는, 다이오드 역회복 손실이 발생하고 있음을 나타낸다. 비교에서, AVC 과형 예(도 47)는, 모든 스위칭 천이들에서 전류가 전압의 변화와 반대의 부호를 갖는다는 것을 나타낸다. 그러므로, 다이오드 역회복 손실을 피한다.

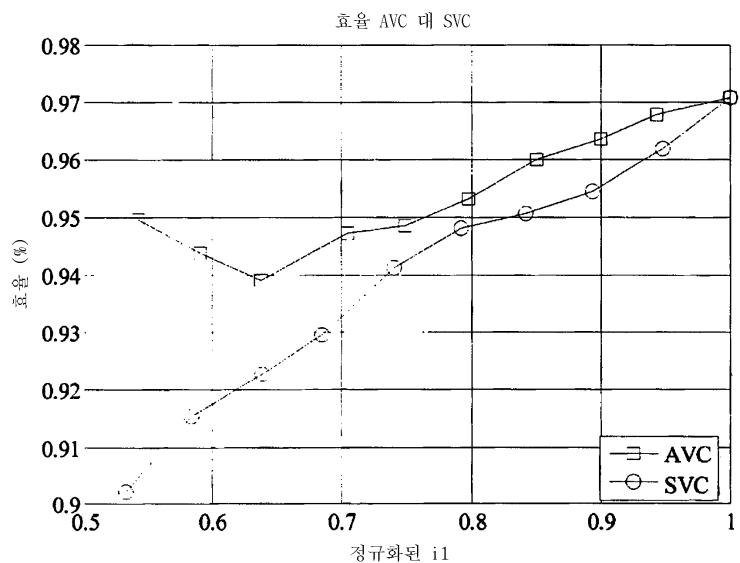

[0131] 도 48은 AVC 제어가 더 효율적임을 나타낸다. 그 효율은 또한 넓은 전력 범위에 걸쳐 더욱 일관성이 있다.

[0132] 컨디셔닝 회로에서의 개시된 AVC 제어의 실시예들은 고효율 비간섭 무선 충전 시스템을 달성하는 것을 돋는다. 이러한 제어 장치 및 방법은 현재의 최신 SVC 제어 및 ADC 제어 방식들보다 훨씬 더 복잡하며, SVC 제어 및 ADC 제어 시스템들이 단독으로 할 수 없는 것을 하는 능력을 제공한다. 더 구체적으로, AVC 제어는 광범위한 로딩 조건들 및 전류 값들에 걸쳐 다이오드 역회복 손실을 피하고 허용가능한 THD를 달성하는 능력을 제공한다.

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

| 시작 상태                 | 종료 상태                 | 스위칭 조건        |

|-----------------------|-----------------------|---------------|

| $S1a(V_{ab} +, ib +)$ | $S1b(V_{ab} +, ib -)$ | 제로 전압 스위칭     |

|                       | $S2a(V_{ab} 0, ib +)$ | 어려움(허용가능함)    |

| $S1b(V_{ab} +, ib -)$ | $S1a(V_{ab} +, ib +)$ | 제로 전압 스위칭     |

|                       | $S2b(V_{ab} 0, ib -)$ | 어려움(다이오드 역회복) |

| $S2a(V_{ab} 0, ib +)$ | $S2b(V_{ab} 0, ib -)$ | 제로 전압 스위칭     |

|                       | $S3a(V_{ab} -, ib +)$ | 어려움(허용가능함)    |

| $S2b(V_{ab} 0, ib -)$ | $S2a(V_{ab} 0, ib +)$ | 제로 전압 스위칭     |

|                       | $S3b(V_{ab} -, ib -)$ | 어려움(다이오드 역회복) |

| $S3a(V_{ab} -, ib +)$ | $S3b(V_{ab} -, ib -)$ | 제로 전압 스위칭     |

|                       | $S4a(V_{ab} 0, ib +)$ | 어려움(다이오드 역회복) |

| $S3b(V_{ab} -, ib -)$ | $S3a(V_{ab} -, ib +)$ | 제로 전압 스위칭     |

|                       | $S4b(V_{ab} 0, ib -)$ | 어려움(허용가능함)    |

| $S4a(V_{ab} 0, ib +)$ | $S4b(V_{ab} 0, ib -)$ | 제로 전압 스위칭     |

|                       | $S1a(V_{ab} +, ib +)$ | 어려움(다이오드 역회복) |

| $S4b(V_{ab} 0, ib -)$ | $S4a(V_{ab} 0, ib +)$ | 제로 전압 스위칭     |

|                       | $S1b(V_{ab} +, ib -)$ | 어려움(허용가능함)    |

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

**도면15****도면16**

### 도면17

### 도면18

## 도면19

## 도면20

도면21

도면22

도면23

도면24

도면25

도면26

도면27

## 도면28

## 도면29

도면30

도면31

도면32

## 도면33

## 도면34

## 도면35

## 도면36

|      |           |

|------|-----------|

| 구성요소 | 값         |

| Lb   | 18.93 uH  |

| Cb   | 1.1151 uF |

| L1   | 12.62 uH  |

| C1   | 0.5575 uF |

도면37

도면38

도면49

도면40

도면41

## 도면42

## 도면43

## 도면44

## 도면45

| Q-값 | % THD<br>최대<br>ADC/AVC | % THD<br>평균<br>ADC/AVC | ADC<br>적용가능성 | % TDH<br>최대<br>SCV/AVC | % TDH<br>평균<br>SCV/AVC | SVC<br>적용가능성 |

|-----|------------------------|------------------------|--------------|------------------------|------------------------|--------------|

| 4   | 12.684                 | 3.342                  | 예            | 1.515                  | 1.124                  | 아니오          |

| 2   | 12.363                 | 2.584                  | 예            | 1.000                  | 1.000                  | 아니오          |

| 1.5 | 12.077                 | 2.498                  | 예            | 1.000                  | 1.000                  | 아니오          |

도면46

도면47

## 도면48