(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4136452号

(P4136452)

(45) 発行日 平成20年8月20日(2008.8.20)

(24) 登録日 平成20年6月13日(2008.6.13)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/8234 | (2006.01) | HO1L 27/06 | 102A |

| HO1L 27/06   | (2006.01) | HO1L 29/78 | 613A |

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 613Z |

| HO1L 21/822  | (2006.01) | HO1L 27/04 | C    |

| HO1L 27/04   | (2006.01) | HO1L 27/04 | G    |

請求項の数 14 (全 33 頁) 最終頁に続く

(21) 出願番号

特願2002-148648 (P2002-148648)

(22) 出願日

平成14年5月23日 (2002.5.23)

(65) 公開番号

特開2003-347419 (P2003-347419A)

(43) 公開日

平成15年12月5日 (2003.12.5)

審査請求日

平成17年5月17日 (2005.5.17)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 一法師 隆志

東京都千代田区丸の内二丁目2番3号 三

菱電機株式会社内

(72) 発明者 岩松 俊明

東京都千代田区丸の内二丁目2番3号 三

菱電機株式会社内

審査官 宇多川 勉

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

支持基板と、絶縁層と、所定導電型で第1濃度の半導体層とがこの順に積層されたSOI基板と、

前記SOI基板の第1の素子形成領域内に形成され、前記半導体層の主表面上に形成された第1のゲート絶縁膜を有する第1のMOSFETと、

前記第1のゲート絶縁膜の下方において、前記主表面から所定距離だけ隔てた深さよりも深い部分の前記半導体層内に形成された、前記所定導電型の第1のウェル領域と、

前記SOI基板の第2の素子形成領域内に形成され、前記主表面上に形成された第1のキャパシタ誘電体膜を有する第1のMOSキャパシタと

10

を備え、

前記第1のウェル領域は、不純物濃度が前記第1濃度よりも高い第2濃度の、第1の不純物濃度分布を有しており、

前記第1のキャパシタ誘電体膜の下方において、前記半導体層は、不純物濃度が、少なくとも、前記主表面から所定距離を隔てた深さから、前記半導体層と前記絶縁層との界面に至るまでの部分に渡って、深さ方向に均一かつ前記第1濃度の、第2の不純物濃度分布を有している、半導体装置。

## 【請求項 2】

支持基板と、絶縁層と、所定導電型で第1濃度の半導体層とがこの順に積層されたSOI基板と、

20

前記 S O I 基板の第 1 の素子形成領域内に形成され、前記半導体層の主表面上に形成された第 1 のゲート絶縁膜を有する第 1 の M O S F E T と、

前記第 1 のゲート絶縁膜の下方において、前記主表面から所定距離だけ隔てた深さよりも深い部分の前記半導体層内で、前記半導体層と前記絶縁層の界面に至る領域に形成された、前記所定導電型の第 1 の不純物導入領域と、

前記 S O I 基板の第 2 の素子形成領域内に形成され、前記主表面上に形成された第 1 のキャパシタ誘電体膜を有する第 1 の M O S キャパシタと

を備え、

前記第 1 の不純物導入領域は、不純物濃度が前記第 1 濃度よりも高い第 2 濃度の、第 1 の不純物濃度分布を有しており、

10

前記第 1 のキャパシタ誘電体膜の下方において、前記半導体層は、不純物濃度が、少なくとも、前記主表面から所定距離を隔てた深さから、前記半導体層と前記絶縁層との界面に至るまでの部分に渡って、深さ方向に均一かつ前記第 1 濃度の、第 2 の不純物濃度分布を有している、半導体装置。

#### 【請求項 3】

支持基板と、絶縁層と、所定導電型で第 1 濃度の半導体層とがこの順に積層された S O I 基板と、

前記 S O I 基板の第 1 の素子形成領域内に形成され、前記半導体層の主表面上に形成された第 1 のゲート絶縁膜を有する第 1 の M O S F E T と、

20

前記第 1 のゲート絶縁膜の下方において、前記ゲート絶縁膜と前記半導体層の界面から前記主表面から所定距離だけ隔てた深さまでの前記半導体層内に形成された、前記所定導電型の第 1 の不純物導入領域と、

前記 S O I 基板の第 2 の素子形成領域内に形成され、前記主表面上に形成された第 1 のキャパシタ誘電体膜を有する第 1 の M O S キャパシタと

を備え、

前記第 1 の不純物導入領域は、不純物濃度が前記第 1 濃度よりも高い第 2 濃度の、第 1 の不純物濃度分布を有しており、

前記第 1 のキャパシタ誘電体膜の下方において、前記半導体層は、不純物濃度が、少なくとも、前記主表面から所定距離を隔てた深さから、前記半導体層と前記絶縁層との界面に至るまでの部分に渡って、深さ方向に均一かつ前記第 1 濃度の、第 2 の不純物濃度分布を有している、半導体装置。

30

#### 【請求項 4】

前記第 2 の不純物濃度分布において、不純物濃度が、前記主表面から前記界面に至るまでの全体に渡って、深さ方向に均一かつ前記第 1 濃度である、請求項 1 乃至請求項 3 のいずれか一つに記載の半導体装置。

#### 【請求項 5】

前記第 1 のゲート絶縁膜の下方において、前記第 1 のウェル領域よりも浅く前記主表面内に形成された、前記所定導電型の第 1 のチャネルドープ領域と、

前記第 1 のキャパシタ誘電体膜の下方において、前記第 1 のウェル領域よりも浅く前記主表面内に形成された、前記所定導電型の第 2 のチャネルドープ領域とをさらに備える、

請求項 1 及び請求項 2 のいずれか一つに記載の半導体装置。

40

#### 【請求項 6】

前記 S O I 基板の第 3 の素子形成領域内に形成され、前記主表面上に形成された第 2 のゲート絶縁膜を有する第 2 の M O S F E T と、

前記第 2 のゲート絶縁膜の下方において、前記主表面から所定距離だけ隔てた深さよりも深い部分の前記半導体層内に形成された、前記所定導電型の第 2 のウェル領域と、

前記 S O I 基板の第 4 の素子形成領域内に形成され、前記主表面上に形成された第 2 のキャパシタ誘電体膜を有する第 2 の M O S キャパシタと

をさらに備え、

前記第 1 の M O S F E T は、第 1 の電圧で駆動される第 1 の半導体回路に含まれる M O

50

S F E Tであり、

前記第1のM O S キャパシタは、前記第1の半導体回路に接続されたM O S キャパシタであり、

前記第2のM O S F E Tは、前記第1の電圧よりも高い第2の電圧で駆動される第2の半導体回路に含まれるM O S F E Tであり、

前記第2のM O S キャパシタは、前記第2の半導体回路に接続されたM O S キャパシタであり、

前記第2のウェル領域は、不純物濃度が前記第1濃度よりも高い第2濃度の、第3の不純物濃度分布を有しており、

前記第2のキャパシタ誘電体膜の下方において、前記半導体層は、不純物濃度が、少な

くとも、前記主表面から所定距離を隔てた深さから、前記半導体層と前記絶縁層との界面

に至るまでの部分に渡って、深さ方向に均一かつ前記第1濃度の、第2の不純物濃度分布

を有している、請求項1乃至請求項3のいずれか一つに記載の半導体装置。

#### 【請求項7】

前記S O I 基板の第3の素子形成領域内に形成され、前記主表面上に形成された第2の

ゲート絶縁膜を有する第2のM O S F E Tと、

前記第2のゲート絶縁膜の下方において、前記主表面から所定距離だけ隔てた深さより

も深い部分の前記半導体層内で、前記半導体層と前記絶縁層の界面に至る領域に形成され

た、前記所定導電型の第2の不純物導入領域と、

前記S O I 基板の第4の素子形成領域内に形成され、前記主表面上に形成された第2の

キャパシタ誘電体膜を有する第2のM O S キャパシタと

をさらに備え、

前記第1のM O S F E Tは、第1の電圧で駆動される第1の半導体回路に含まれるM O

S F E Tであり、

前記第1のM O S キャパシタは、前記第1の半導体回路に接続されたM O S キャパシタ

であり、

前記第2のM O S F E Tは、前記第1の電圧よりも高い第2の電圧で駆動される第2の

半導体回路に含まれるM O S F E Tであり、

前記第2のM O S キャパシタは、前記第2の半導体回路に接続されたM O S キャパシタ

であり、

前記第2の不純物導入領域は、不純物濃度が前記第1濃度よりも高い第2濃度の、第3

の不純物濃度分布を有しております、

前記第2のキャパシタ誘電体膜の下方において、前記半導体層は、不純物濃度が、少な

くとも、前記主表面から所定距離を隔てた深さから、前記半導体層と前記絶縁層との界面

に至るまでの部分に渡って、深さ方向に均一かつ前記第1濃度の、第2の不純物濃度分布

を有している、請求項2及び請求項3のいずれか一つに記載の半導体装置。

#### 【請求項8】

前記第1の半導体回路に前記第1の電圧を供給する第1の電源と、

前記第2の半導体回路に前記第2の電圧を供給する第2の電源と、

前記第1及び第2の半導体回路に共通に接続された共通配線と

をさらに備え、

前記第1のM O S キャパシタは、前記第1の電源と前記共通配線との間に接続されてお

り、

前記第2のM O S キャパシタは、前記第2の電源と前記共通配線との間に接続されてい

る、請求項6及び請求項7のいずれか一つに記載の半導体装置。

#### 【請求項9】

所定導電型で第1濃度の半導体基板と、

前記半導体基板の第1の素子形成領域内に形成され、前記半導体基板の第1主表面上に

形成されたゲート絶縁膜を有するM O S F E Tと、

前記ゲート絶縁膜の下方における前記第1主表面内に形成された、前記所定導電型のウ

10

20

30

40

50

エル領域と、

前記半導体基板の第2の素子形成領域内に形成され、前記第1主表面上に形成されたキャパシタ誘電体膜を有するMOSキャパシタと

を備え、

前記ウェル領域は、不純物濃度が前記第1濃度よりも高い第2濃度の、第1の不純物濃度分布を有しており、

前記キャパシタ誘電体膜の下方において、前記半導体基板は、不純物濃度が、前記第1主表面から、前記第1主表面の反対側の第2主表面に至るまでの全体に渡って、深さ方向に均一かつ前記第1濃度の、第2の不純物濃度分布を有している、半導体装置。

## 【請求項10】

10

(a) ゲート絶縁膜を有するMOSFETが形成される予定の第1の素子形成領域と、キャパシタ誘電体膜を有するMOSキャパシタが形成される予定の第2の素子形成領域とを有し、支持基板と、絶縁層と、所定導電型の半導体層とがこの順に積層されたSOI基板を準備する工程と、

(b) 前記第2の素子形成領域を第1のマスク材で覆って第1の不純物を注入することにより、前記主表面から所定距離だけ隔てた深さよりも深い部分の、前記第1の素子形成領域における前記半導体層内に、前記所定導電型のウェル領域を形成する工程と、

(c) 前記工程(b)よりも後に実行され、前記第1の素子形成領域における前記主表面上に、前記ゲート絶縁膜を形成する工程と、

(d) 前記工程(b)よりも後に実行され、前記第2の素子形成領域における前記主表面上に、前記キャパシタ誘電体膜を形成する工程と

を備える、半導体装置の製造方法。

20

## 【請求項11】

(a) ゲート絶縁膜を有するMOSFETが形成される予定の第1の素子形成領域と、キャパシタ誘電体膜を有するMOSキャパシタが形成される予定の第2の素子形成領域とを有し、支持基板と、絶縁層と、所定導電型の半導体層とがこの順に積層されたSOI基板を準備する工程と、

(b) 前記第2の素子形成領域を第1のマスク材で覆って第1の不純物を注入することにより、前記主表面から所定距離だけ隔てた深さよりも深い部分の、前記第1の素子形成領域における前記半導体層内で、前記半導体層と前記絶縁層の界面に至る領域に、前記所定導電型の第1の不純物導入領域を形成する工程と、

30

(c) 前記工程(b)よりも後に実行され、前記第1の素子形成領域における前記主表面上に、前記ゲート絶縁膜を形成する工程と、

(d) 前記工程(b)よりも後に実行され、前記第2の素子形成領域における前記主表面上に、前記キャパシタ誘電体膜を形成する工程と

を備える、半導体装置の製造方法。

## 【請求項12】

40

(e) 前記工程(d)よりも前に実行され、前記第2の素子形成領域を第2のマスク材で覆って前記第1の素子形成領域内に第2の不純物を注入することにより、前記所定導電型のチャネルドープ領域を、前記ウェル領域よりも浅く前記主表面内に形成する工程をさらに備える、請求項10に記載の半導体装置の製造方法。

## 【請求項13】

(e) 前記工程(d)よりも前に実行され、前記第2の素子形成領域を第2のマスク材で覆って前記第1の素子形成領域内に第2の不純物を注入することにより、前記所定導電型のチャネルドープ領域を、前記第1の不純物導入領域よりも浅く前記主表面内に形成する工程をさらに備える、請求項11に記載の半導体装置の製造方法。

## 【請求項14】

(a) ゲート絶縁膜を有するMOSFETが形成される予定の第1の素子形成領域と、キャパシタ誘電体膜を有するMOSキャパシタが形成される予定の第2の素子形成領域とを有する、所定導電型の半導体基板を準備する工程と、

50

(b) 前記第2の素子形成領域を第1のマスク材で覆って第1の不純物を注入することにより、前記第1の素子形成領域における前記半導体基板内に、前記所定導電型のウェル領域を形成する工程と、

(c) 前記第2の素子形成領域を第2のマスク材で覆って第2の不純物を注入することにより、前記第1の素子形成領域における前記半導体基板の主表面上に、前記所定導電型のチャネルドープ領域を形成する工程と、

(d) 前記工程(b)及び(c)よりも後に実行され、前記第1の素子形成領域における前記主表面上に、前記ゲート絶縁膜を形成する工程と、

(e) 前記工程(b)及び(c)よりも後に実行され、前記第2の素子形成領域における前記主表面上に、前記キャパシタ誘電体膜を形成する工程と

を備える、半導体装置の製造方法。

10

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は、半導体装置及びその製造方法に関するものであり、特に、基板上に形成された絶縁膜（具体的には、MOSキャパシタのキャパシタ誘電体膜又はMOSFETのゲート絶縁膜）の信頼性が向上された、半導体装置及びその製造方法に関する。

##### 【0002】

##### 【従来の技術】

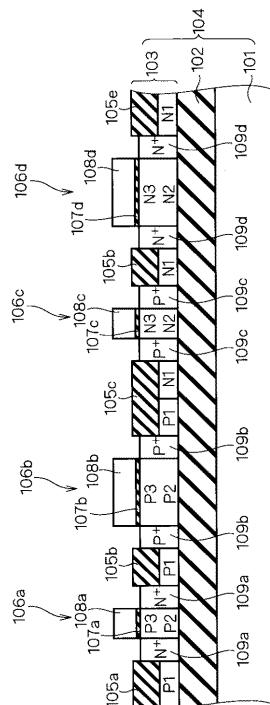

図42は、従来の第1の半導体装置の構造を示す断面図である。従来の第1の半導体装置は、SOI基板104と、素子分離絶縁膜105a～105eと、NMOSFET106aと、PMOSFET106cと、MOSキャパシタ106b, 106dとを備えている。MOSキャパシタ106b, 106dは、例えばデカップリングキャパシタとして使用されている。SOI基板104は、シリコン基板101と、BOX(buried oxide)層102と、P型のシリコン層103とがこの順に積層された構造を有している。素子分離絶縁膜105a～105eは、シリコン層103の上面内に部分的に形成されている。素子分離絶縁膜105a～105eの底面は、BOX層102の上面に接触していない。このような構造の素子分離絶縁膜は、「部分分離型の素子分離絶縁膜」と称されている。

20

##### 【0003】

NMOSFET106aは、シリコン層103の上面に形成されたゲート酸化膜107aと、ゲート電極108aと、N<sup>+</sup>型の対を成すソース・ドレイン領域109aとを有している。MOSキャパシタ106bは、シリコン層103の上面に形成されたキャパシタ誘電体膜107bと、キャパシタ上部電極108bと、P<sup>+</sup>型の対を成すコンタクト領域109bとを有している。PMOSFET106cは、シリコン層103の上面に形成されたゲート酸化膜107cと、ゲート電極108cと、P<sup>+</sup>型の対を成すソース・ドレイン領域109cとを有している。MOSキャパシタ106dは、シリコン層103の上面に形成されたキャパシタ誘電体膜107dと、キャパシタ上部電極108dと、N<sup>+</sup>型の対を成すコンタクト領域109dとを有している。

30

##### 【0004】

素子分離絶縁膜105a～105eの底面とBOX層102の上面とによって挟まれている部分のシリコン層103内には、素子分離のためのP型不純物又はN型不純物が、イオン注入によって、不純物濃度P1又は不純物濃度N1で注入されている。また、このイオン注入に起因して、ゲート酸化膜107a, 107c及びキャパシタ誘電体膜107b, 107dの下方において、BOX層102との界面付近におけるシリコン層103内には、P型不純物又はN型不純物が、不純物濃度P2又は不純物濃度N2で注入されている。

40

##### 【0005】

さらに、ゲート酸化膜107a, 107cの下方において、シリコン層103の上面内には、NMOSFET106a又はPMOSFET106cのしきい値電圧を設定するためのP型不純物又はN型不純物が、イオン注入によって、不純物濃度P3又は不純物濃度N3で注入されている。また、このイオン注入に起因して、キャパシタ誘電体膜107b,

50

107dの下方において、シリコン層103の上面内には、P型不純物又はN型不純物が、不純物濃度P3又は不純物濃度N3で注入されている。

#### 【0006】

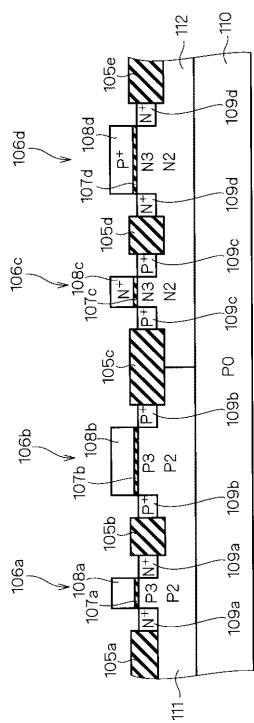

図43は、従来の第2の半導体装置の構造を示す断面図である。従来の第2の半導体装置は、不純物濃度P0のP型のシリコン基板110と、不純物濃度P2のP型ウェル111と、不純物濃度N2のN型ウェル112と、素子分離絶縁膜105a～105eと、NMOSFET106aと、PMOSFET106cと、MOSキャパシタ106b, 106dとを備えている。P型ウェル111及びN型ウェル112は、シリコン基板110の上面内に形成されている。MOSキャパシタ106bはP型ウェル111上に形成されており、MOSキャパシタ106dはN型ウェル112上に形成されている。

10

#### 【0007】

このように従来の第1及び第2の半導体装置では、ゲート酸化膜107aの下方におけるシリコン層103又はシリコン基板110の不純物プロファイルと、キャパシタ誘電体膜107bの下方におけるシリコン層103又はシリコン基板110の不純物プロファイルとが、互いに等しい。また、ゲート酸化膜107cの下方におけるシリコン層103又はシリコン基板110の不純物プロファイルと、キャパシタ誘電体膜107dの下方におけるシリコン層103又はシリコン基板110の不純物プロファイルとが、互いに等しい。

#### 【0008】

##### 【発明が解決しようとする課題】

半導体集積回路の規模が増大すると、キャパシタ上部電極108b, 108dに電圧が印加される実効的な時間が、ゲート電極108a, 108cのそれよりも長くかかることがある。これに伴い、キャパシタ誘電体膜107b, 107dには、ゲート酸化膜107a, 107cよりも高い信頼性が要求される。特に、MOSキャパシタ106b, 106dがデカップリングキャパシタとして使用されている場合には、キャパシタ上部電極108b, 108dに直流電圧が継続的に印加されるため、キャパシタ誘電体膜107b, 107dには、より高い信頼性が要求される。

20

#### 【0009】

また、MOSキャパシタに限らず、ゲート電極に高い電圧が印加されるMOSFETにおいては、ゲート絶縁膜に高い信頼性が要求される。従って、ゲート電圧が高いMOSFETにおいては、ゲート電圧が低いMOSFETよりも、ゲート絶縁膜の信頼性を高める改良が必要となる。

30

#### 【0010】

しかしながら従来の第1及び第2の半導体装置によると、信頼性を高めるための改良がなされておらず、キャパシタ誘電体膜107b, 107dの信頼性が不十分であるという問題がある。

#### 【0011】

本発明はかかる問題を解決するために成されたものであり、基板の主面上に形成された絶縁膜（MOSキャパシタのキャパシタ誘電体膜又はMOSFETのゲート絶縁膜）の信頼性が向上された、半導体装置及びその製造方法を得ることを目的とするものである。

#### 【0012】

40

##### 【課題を解決するための手段】

この発明のうち請求項1に記載の半導体装置は、支持基板と、絶縁層と、所定導電型で第1濃度の半導体層とがこの順に積層されたSOI基板と、SOI基板の第1の素子形成領域内に形成され、半導体層の主表面上に形成された第1のゲート絶縁膜を有する第1のMOSFETと、第1のゲート絶縁膜の下方において、主表面から所定距離だけ隔てた深さよりも深い部分の半導体層内に形成された、所定導電型の第1のウェル領域と、SOI基板の第2の素子形成領域内に形成され、主表面上に形成された第1のキャパシタ誘電体膜を有する第1のMOSキャパシタとを備え、第1のウェル領域は、不純物濃度が第1濃度よりも高い第2濃度の、第1の不純物濃度分布を有しており、第1のキャパシタ誘電体膜の下方において、半導体層は、不純物濃度が、少なくとも、主表面から所定距離を隔て

50

た深さから、半導体層と絶縁層との界面に至るまでの部分に渡って、深さ方向に均一かつ第1濃度の、第2の不純物濃度分布を有しているものである。

また、この発明のうち請求項2に記載の半導体装置は、支持基板と、絶縁層と、所定導電型で第1濃度の半導体層とがこの順に積層されたSOI基板と、SOI基板の第1の素子形成領域内に形成され、半導体層の主表面上に形成された第1のゲート絶縁膜を有する第1のMOSFETと、第1のゲート絶縁膜の下方において、主表面から所定距離だけ隔てた深さよりも深い部分の半導体層内で、半導体層と絶縁層の界面に至る領域に形成された、所定導電型の第1の不純物導入領域と、SOI基板の第2の素子形成領域内に形成され、主表面上に形成された第1のキャパシタ誘電体膜を有する第1のMOSキャパシタとを備え、第1の不純物導入領域は、不純物濃度が第1濃度よりも高い第2濃度の、第1の不純物濃度分布を有しており、第1のキャパシタ誘電体膜の下方において、半導体層は、不純物濃度が、少なくとも、主表面から所定距離を隔てた深さから、半導体層と絶縁層との界面に至るまでの部分に渡って、深さ方向に均一かつ前記第1濃度の、第2の不純物濃度分布を有しているものである。10

また、この発明のうち請求項3に記載の半導体装置は、支持基板と、絶縁層と、所定導電型で第1濃度の半導体層とがこの順に積層されたSOI基板と、SOI基板の第1の素子形成領域内に形成され、半導体層の主表面上に形成された第1のゲート絶縁膜を有する第1のMOSFETと、第1のゲート絶縁膜の下方において、ゲート絶縁膜と半導体層の界面から主表面から所定距離だけ隔てた深さまでの半導体層内に形成された、所定導電型の第1の不純物導入領域と、SOI基板の第2の素子形成領域内に形成され、主表面上に形成された第1のキャパシタ誘電体膜を有する第1のMOSキャパシタとを備え、第1の不純物導入領域は、不純物濃度が第1濃度よりも高い第2濃度の、第1の不純物濃度分布を有しており、第1のキャパシタ誘電体膜の下方において、半導体層は、不純物濃度が、少なくとも、主表面から所定距離を隔てた深さから、半導体層と絶縁層との界面に至るまでの部分に渡って、深さ方向に均一かつ第1濃度の、第2の不純物濃度分布を有しているものである。20

#### 【0013】

また、この発明のうち請求項4に記載の半導体装置は、請求項1乃至請求項3のいずれか一つに記載の半導体装置であって、第2の不純物濃度分布において、不純物濃度が、主表面から接觸面に至るまでの全体に渡って、深さ方向に均一かつ第1濃度であることを特徴とするものである。30

#### 【0014】

また、この発明のうち請求項5に記載の半導体装置は、請求項1及び請求項2のいずれか一つに記載の半導体装置であって、第1のゲート絶縁膜の下方において、第1のウェル領域よりも浅く主表面内に形成された、所定導電型の第1のチャネルドープ領域と、第1のキャパシタ誘電体膜の下方において、第1のウェル領域よりも浅く主表面内に形成された、所定導電型の第2のチャネルドープ領域とをさらに備えることを特徴とするものである。

#### 【0015】

また、この発明のうち請求項6に記載の半導体装置は、請求項1乃至請求項3のいずれか一つに記載の半導体装置であって、SOI基板の第3の素子形成領域内に形成され、主表面上に形成された第2のゲート絶縁膜を有する第2のMOSFETと、第2のゲート絶縁膜の下方において、主表面から所定距離だけ隔てた深さよりも深い部分の半導体層内に形成された、所定導電型の第2のウェル領域と、SOI基板の第4の素子形成領域内に形成され、主表面上に形成された第2のキャパシタ誘電体膜を有する第2のMOSキャパシタとをさらに備え、第1のMOSFETは、第1の電圧で駆動される第1の半導体回路に含まれるMOSFETであり、第1のMOSキャパシタは、第1の半導体回路に接続されたMOSキャパシタであり、第2のMOSFETは、第1の電圧よりも高い第2の電圧で駆動される第2の半導体回路に含まれるMOSFETであり、第2のMOSキャパシタは、第2の半導体回路に接続されたMOSキャパシタであり、第2のウェル領域は、不純物4050

濃度が第1濃度よりも高い第2濃度の、第3の不純物濃度分布を有しており、第2のキャパシタ誘電体膜の下方において、半導体層は、不純物濃度が、少なくとも、主表面から所定距離を隔てた深さから、半導体層と絶縁層との界面に至るまでの部分に渡って、深さ方向に均一かつ第1濃度の、第2の不純物濃度分布を有していることを特徴とするものである。

また、この発明のうち請求項7に記載の半導体装置は、請求項2及び請求項3のいずれか一つに記載の半導体装置であって、SOI基板の第3の素子形成領域内に形成され、主表面上に形成された第2のゲート絶縁膜を有する第2のMOSFETと、第2のゲート絶縁膜の下方において、主表面から所定距離だけ隔てた深さよりも深い部分の半導体層内で、半導体層と絶縁層の界面に至る領域に形成された、所定導電型の第2の不純物導入領域と、SOI基板の第4の素子形成領域内に形成され、主表面上に形成された第2のキャパシタ誘電体膜を有する第2のMOSキャパシタとをさらに備え、第1のMOSFETは、第1の電圧で駆動される第1の半導体回路に含まれるMOSFETであり、第1のMOSキャパシタは、第1の半導体回路に接続されたMOSキャパシタであり、第2のMOSFETは、第1の電圧よりも高い第2の電圧で駆動される第2の半導体回路に含まれるMOSFETであり、第2のMOSキャパシタは、第2の半導体回路に接続されたMOSキャパシタであり、第2の不純物導入領域は、不純物濃度が第1濃度よりも高い第2濃度の、第3の不純物濃度分布を有しており、第2のキャパシタ誘電体膜の下方において、半導体層は、不純物濃度が、少なくとも、主表面から所定距離を隔てた深さから、半導体層と絶縁層との界面に至るまでの部分に渡って、深さ方向に均一かつ第1濃度の、第2の不純物濃度分布を有していることを特徴とするものである。

10

20

#### 【0016】

また、この発明のうち請求項8に記載の半導体装置は、請求項6及び請求項7のいずれか一つに記載の半導体装置であって、第1の半導体回路に第1の電圧を供給する第1の電源と、第2の半導体回路に第2の電圧を供給する第2の電源と、第1及び第2の半導体回路に共通に接続された共通配線とをさらに備え、第1のMOSキャパシタは、第1の電源と共に接続されており、第2のMOSキャパシタは、第2の電源と共に接続されていることを特徴とするものである。

#### 【0017】

また、この発明のうち請求項9に記載の半導体装置は、所定導電型で第1濃度の半導体基板と、半導体基板の第1の素子形成領域内に形成され、半導体基板の第1主表面上に形成されたゲート絶縁膜を有するMOSFETと、ゲート絶縁膜の下方における第1主表面内に形成された、所定導電型のウェル領域と、半導体基板の第2の素子形成領域内に形成され、第1主表面上に形成されたキャパシタ誘電体膜を有するMOSキャパシタとを備え、ウェル領域は、不純物濃度が第1濃度よりも高い第2濃度の、第1の不純物濃度分布を有しており、キャパシタ誘電体膜の下方において、半導体基板は、不純物濃度が、第1主表面から、第1主表面の反対側の第2主表面に至るまでの全体に渡って、深さ方向に均一かつ第1濃度の、第2の不純物濃度分布を有しているものである。

30

#### 【0018】

また、この発明のうち請求項10に記載の半導体装置の製造方法は、(a)ゲート絶縁膜を有するMOSFETが形成される予定の第1の素子形成領域と、キャパシタ誘電体膜を有するMOSキャパシタが形成される予定の第2の素子形成領域とを有し、支持基板と、絶縁層と、所定導電型の半導体層とがこの順に積層されたSOI基板を準備する工程と、(b)第2の素子形成領域を第1のマスク材で覆って第1の不純物を注入することにより、主表面から所定距離だけ隔てた深さよりも深い部分の、第1の素子形成領域における半導体層内に、所定導電型のウェル領域を形成する工程と、(c)工程(b)よりも後に実行され、第1の素子形成領域における主表面上に、ゲート絶縁膜を形成する工程と、(d)工程(b)よりも後に実行され、第2の素子形成領域における主表面上に、キャパシタ誘電体膜を形成する工程とを備えるものである。

40

また、この発明のうち請求項11に記載の半導体装置の製造方法は、(a)ゲート絶縁

膜を有するMOSFETが形成される予定の第1の素子形成領域と、キャパシタ誘電体膜を有するMOSキャパシタが形成される予定の第2の素子形成領域とを有し、支持基板と、絶縁層と、所定導電型の半導体層とがこの順に積層されたSOI基板を準備する工程と、(b)第2の素子形成領域を第1のマスク材で覆って第1の不純物を注入することにより、主表面から所定距離だけ隔てた深さよりも深い部分の、第1の素子形成領域における半導体層内で、半導体層と絶縁層の界面に至る領域に、所定導電型の第1の不純物導入領域を形成する工程と、(c)前記工程(b)よりも後に実行され、第1の素子形成領域における主表面上に、ゲート絶縁膜を形成する工程と、(d)工程(b)よりも後に実行され、第2の素子形成領域における主表面上に、キャパシタ誘電体膜を形成する工程とを備えるものである。

10

## 【0019】

また、この発明のうち請求項12に記載の半導体装置の製造方法は、請求項10に記載の半導体装置の製造方法であって、(e)工程(d)よりも前に実行され、第2の素子形成領域を第2のマスク材で覆って第1の素子形成領域内に第2の不純物を注入することにより、所定導電型のチャネルドープ領域を、ウェル領域よりも浅く主表面内に形成する工程をさらに備えることを特徴とするものである。

また、この発明のうち請求項13に記載の半導体装置の製造方法は、請求項11に記載の半導体装置の製造方法であって、(e)工程(d)よりも前に実行され、第2の素子形成領域を第2のマスク材で覆って第1の素子形成領域内に第2の不純物を注入することにより、所定導電型のチャネルドープ領域を、第1の不純物導入領域よりも浅く主表面内に形成する工程をさらに備えることを特徴とするものである。

20

## 【0020】

また、この発明のうち請求項14に記載の半導体装置の製造方法は、(a)ゲート絶縁膜を有するMOSFETが形成される予定の第1の素子形成領域と、キャパシタ誘電体膜を有するMOSキャパシタが形成される予定の第2の素子形成領域とを有する、所定導電型の半導体基板を準備する工程と、(b)第2の素子形成領域を第1のマスク材で覆って第1の不純物を注入することにより、第1の素子形成領域における半導体基板内に、所定導電型のウェル領域を形成する工程と、(c)第2の素子形成領域を第2のマスク材で覆って第2の不純物を注入することにより、第1の素子形成領域における半導体基板の主表面内に、所定導電型のチャネルドープ領域を形成する工程と、(d)工程(b)及び(c)よりも後に実行され、第1の素子形成領域における主表面上に、ゲート絶縁膜を形成する工程と、(e)工程(b)及び(c)よりも後に実行され、第2の素子形成領域における主表面上に、キャパシタ誘電体膜を形成する工程とを備えるものである。

30

## 【0021】

## 【発明の実施の形態】

実施の形態1.

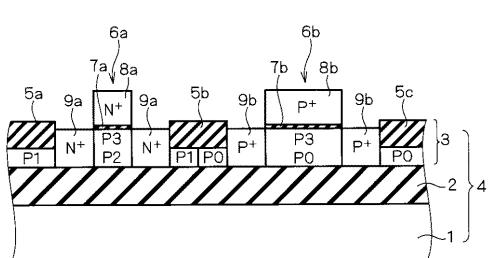

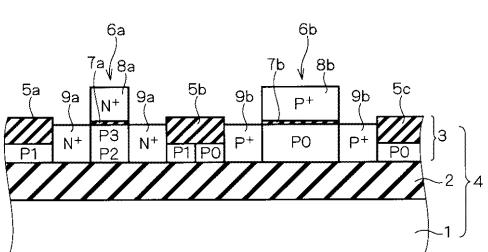

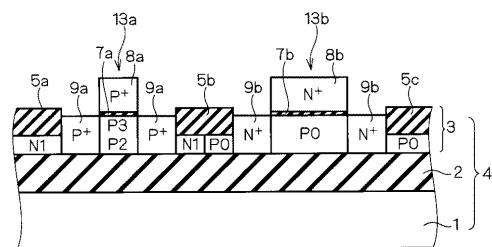

図1は、本発明の実施の形態1に係る半導体装置の構造を示す断面図である。本実施の形態1に係る半導体装置は、SOI基板4と、部分分離型の素子分離絶縁膜5a～5cと、NMOSFET6aと、MOSキャパシタ6bとを備えている。MOSキャパシタ6bは、例えはデカッピングキャパシタとして使用されている。SOI基板4は、シリコン基板1と、BOX層2と、P型のシリコン層3とがこの順に積層された構造を有している。シリコン層3の不純物濃度P0は、 $1E15 \text{ cm}^{-3}$ 程度である。素子分離絶縁膜5a～5cは、シリコン層3の上面内に部分的に形成されている。素子分離絶縁膜5a～5cは、トレンチ型又はLOCOS型の素子分離絶縁膜である。

40

## 【0022】

NMOSFET6aは、素子分離絶縁膜5a, 5bによって規定される第1の素子形成領域内に形成されている。NMOSFET6aは、ゲート酸化膜7aと、ゲート電極8aと、N<sup>+</sup>型の対を成すソース・ドレイン領域9aとを有している。ゲート酸化膜7aは、シリコン層3の上面上に形成されている。ゲート電極8aは、ゲート酸化膜7a上に形成されている。ソース・ドレイン領域9aは、ゲート酸化膜7aの下方のチャネル形成領域を

50

挟んで、シリコン層 3 内に形成されている。

【 0 0 2 3 】

MOS キャパシタ 6 b は、素子分離絶縁膜 5 b , 5 c によって規定される第 2 の素子形成領域内に形成されている。MOS キャパシタ 6 b は、シリコン層 3 の上面に形成されたキャパシタ誘電体膜 7 b と、キャパシタ誘電体膜 7 b 上に形成されたキャパシタ上部電極 8 b とを有している。キャパシタ誘電体膜 7 b は、ゲート酸化膜 7 a よりも高い信頼性が要求される膜である。ここで、絶縁膜にとって「信頼性」とは、絶縁膜に印加されるストレス又はその蓄積によっても、その絶縁膜の絶縁性が破壊することのない性質を意味する。信頼性を表す尺度としては、MTBF (平均故障間隔) やMTTF (平均故障時間) 等がある。

10

【 0 0 2 4 】

キャパシタ誘電体膜 7 b を挟んでキャパシタ上部電極 8 b に対向する部分のシリコン層 3 は、MOS キャパシタ 6 b のキャパシタ下部電極として機能する。また、MOS キャパシタ 6 b は、P<sup>+</sup>型の対を成すコンタクト領域 9 b を有している。コンタクト領域 9 b は、キャパシタ下部電極として機能する部分のシリコン層 3 を挟んで、シリコン層 3 内に形成されている。

【 0 0 2 5 】

素子分離絶縁膜 5 a の底面とBOX 層 2 の上面とによって挟まれている部分のシリコン層 3 内には、イオン注入によって、素子分離のためのP型不純物が注入されている。このP型不純物が注入されている部分のシリコン層 3 の不純物濃度 P 1 は、1E17 ~ 2E18 cm<sup>-3</sup>程度である。同様に、図 1において素子分離絶縁膜 5 b の左半分の底面 (NMOSFET 6 a に接する側の半分の底面) と、BOX 层 2 の上面とによって挟まれている部分のシリコン層 3 内には、P型不純物が不純物濃度 P 1 で注入されている。

20

【 0 0 2 6 】

また、このときのイオン注入に起因して、ゲート酸化膜 7 a の下方において、BOX 层 2 との界面付近におけるシリコン層 3 内には、P型不純物が注入されている。一方、キャパシタ誘電体膜 7 b の下方において、BOX 层 2 との界面付近におけるシリコン層 3 の不純物濃度は、シリコン層 3 のそもそもの不純物濃度 P 0 である。

【 0 0 2 7 】

ゲート酸化膜 7 a の下方において、シリコン層 3 の上面内には、イオン注入によって、NMOSFET 6 a のしきい値電圧を設定するためのP型不純物が注入されている。即ち、P型のチャネルドープ領域が形成されている。このP型不純物が注入されている部分のシリコン層 3 の不純物濃度 P 3 は、1E16 ~ 1E18 cm<sup>-3</sup>程度である。また、このときのイオン注入に起因して、キャパシタ誘電体膜 7 b の下方において、シリコン層 3 の上面内には、P型不純物が不純物濃度 P 3 で注入されている。

30

【 0 0 2 8 】

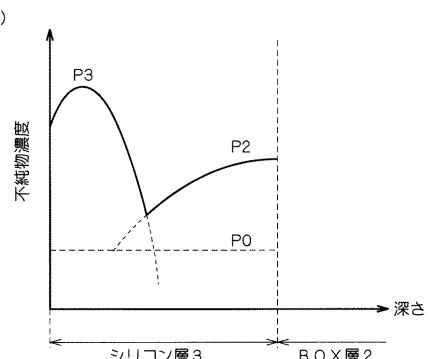

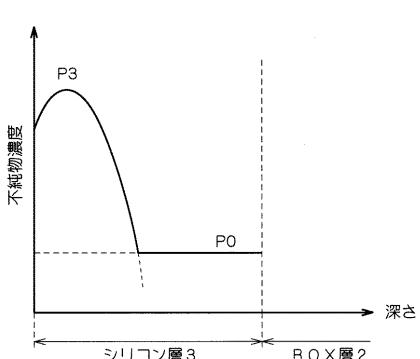

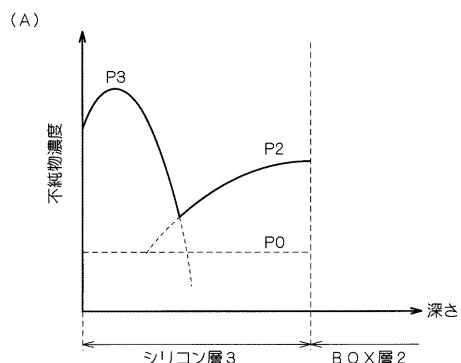

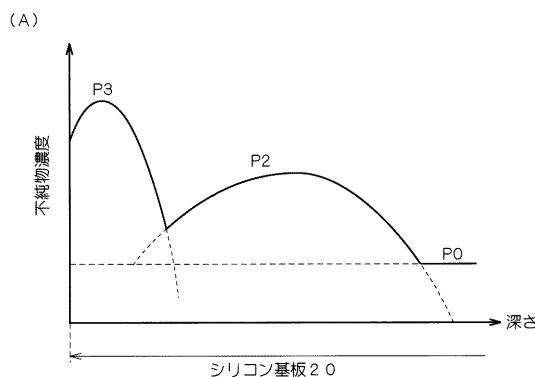

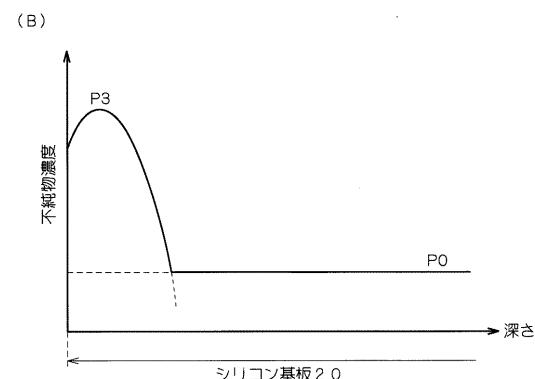

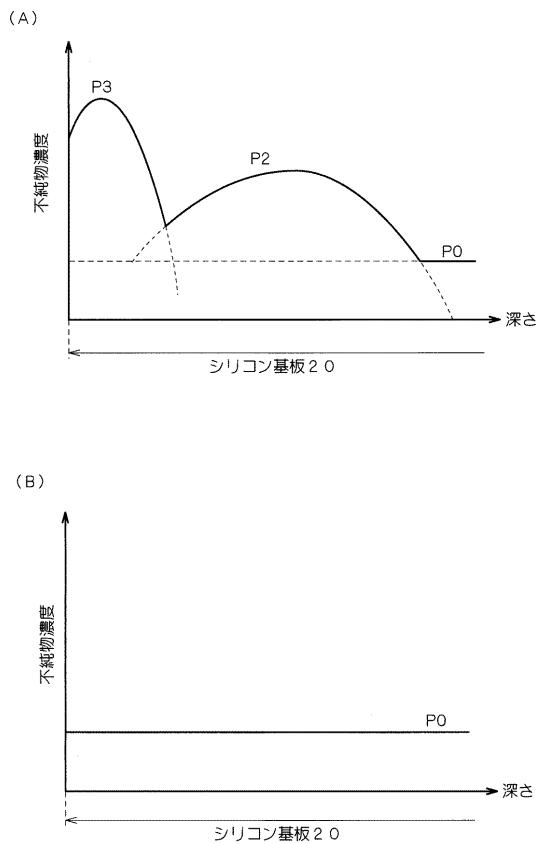

図 2 (図 2 (A) , 図 2 (B)) は、ゲート酸化膜 7 a の下方におけるシリコン層 3 の不純物プロファイル (図 2 (A)) と、キャパシタ誘電体膜 7 b の下方におけるシリコン層 3 の不純物プロファイル (図 2 (B)) とを示す図である。図 2 に示すように、本実施の形態 1 に係る半導体装置では、ゲート酸化膜 7 a の下方におけるシリコン層 3 の不純物プロファイルと、キャパシタ誘電体膜 7 b の下方におけるシリコン層 3 の不純物プロファイルとが、互いに異なっている。図 2 (A) に示すように、ゲート酸化膜 7 a の下方において、シリコン層 3 は、不純物濃度 P 0 よりも高い不純物濃度 P 2 , P 3 の不純物プロファイルを有している。また、図 2 (B) に示すように、キャパシタ誘電体膜 7 b の下方において、シリコン層 3 は、シリコン層 3 の上面 (横軸ゼロ) から所定距離を隔てた深さから、シリコン層 3 と BOX 层 2 との接触面に至るまでの部分に渡って、不純物濃度が P 0 で均一の不純物プロファイルを有している。

40

【 0 0 2 9 】

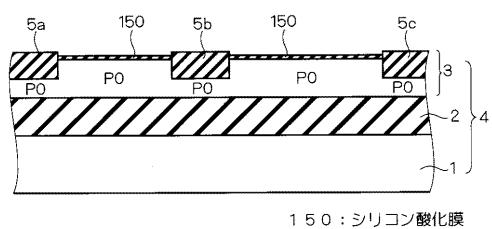

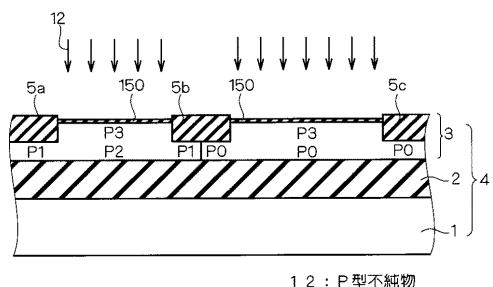

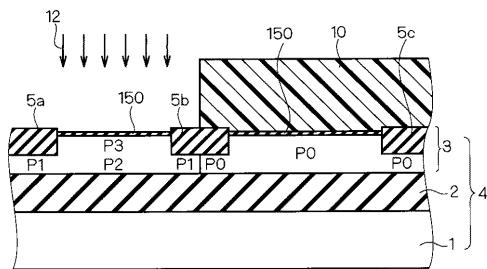

図 3 ~ 図 6 は、本発明の実施の形態 1 に係る半導体装置の製造方法を工程順に示す断面図である。図 3 を参照して、まず、SOI 基板 4 を準備する。次に、周知のトレンチ分離技

50

術又はLOCOS分離技術によって、シリコン層3の上面内に素子分離絶縁膜5a～5cを形成する。図3に示すように、シリコン層3の上面上には、素子分離絶縁膜5a～5cを形成する際にシリコン窒化膜の下敷き膜として機能する、シリコン酸化膜150を残す。

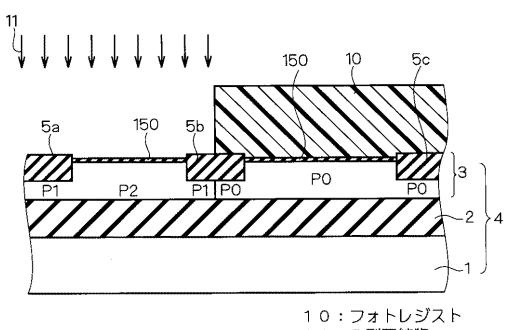

#### 【0030】

図4を参照して、次に、写真製版法によって、第2の素子形成領域を覆ってフォトレジスト10を形成する。図4において素子分離絶縁膜5bの右半分の上面、及び素子分離絶縁膜5cの上面は、フォトレジスト10によって覆われている。次に、フォトレジスト10を注入マスクに用いて、イオン注入法によって、BOX層2との界面付近におけるシリコン層3内に到達し得る比較的高いエネルギーで、P型不純物11をシリコン層3内に深く注入する。P型不純物11は、素子分離絶縁膜5a, 5b及び第1の素子形成領域におけるシリコン酸化膜150を通して、シリコン層3内に注入される。これにより、シリコン層3内に、不純物濃度P1, P2の不純物注入領域が形成される。その後、フォトレジスト10を除去する。

#### 【0031】

図5を参照して、次に、イオン注入法によって、比較的低いエネルギーで、P型不純物12をシリコン層3の上面内に浅く注入する。P型不純物12は、第1及び第2の素子形成領域におけるシリコン酸化膜150を通して、シリコン層3内に注入される。これにより、素子分離絶縁膜5a～5cが形成されていない部分のシリコン層3の上面内に、不純物濃度P3の不純物注入領域が形成される。その後、フッ酸を用いたウェットエッチング法によって、シリコン酸化膜150が除去される。

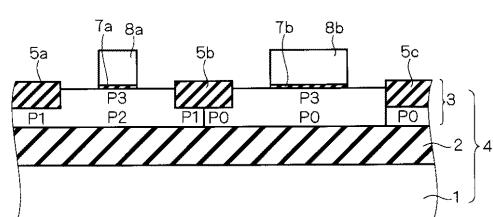

#### 【0032】

図6を参照して、次に、熱酸化法によって、第1及び第2の素子形成領域におけるシリコン層3の上面上に、3.5nm程度の膜厚のシリコン酸化膜を形成する。次に、CVD法によって、全面にポリシリコン膜を形成する。次に、写真製版法及び異方性ドライエッチング法によってこのポリシリコン膜をパターニングすることにより、ゲート電極8a及びキャパシタ上部電極8bを形成する。ゲート電極8aの下にはゲート酸化膜7aが形成されており、キャパシタ上部電極8bの下にはキャパシタ誘電体膜7bが形成されている。ゲート酸化膜7aは、第1の素子形成領域におけるシリコン層3の上面上に形成されており、キャパシタ誘電体膜7bは、第2の素子形成領域におけるシリコン層3の上面上に形成されている。

#### 【0033】

その後、写真製版法及びイオン注入法によってシリコン層3内に部分的にN型不純物を注入することにより、ソース・ドレイン領域9aを形成する。このときのイオン注入によって、ゲート電極8a内にもN型不純物が注入される。また、写真製版法及びイオン注入法によってシリコン層3内に部分的にP型不純物を注入することにより、コンタクト領域9bを形成する。このときのイオン注入によって、キャパシタ上部電極8b内にもP型不純物が注入される。以上の工程により、図1に示した構造が得られる。

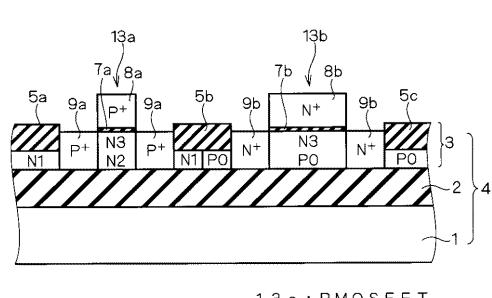

#### 【0034】

図7は、本実施の形態1に係る半導体装置の変形例を示す断面図である。以上の説明では、NMOSFET6aが形成されている場合の例について述べたが、図7に示すように、NMOSFET6aの代わりにPMOSFET13aが形成されていてもよい。PMOSFET13aは、P<sup>+</sup>型のソース・ドレイン領域9aと、P<sup>+</sup>型のゲート電極8aとを有している。

#### 【0035】

また、以上の説明では、P<sup>+</sup>型のコンタクト領域9bを有するMOSキャパシタ6bが形成されている場合の例について述べたが、MOSキャパシタ6bの代わりに、N<sup>+</sup>型のコンタクト領域9bを有するMOSキャパシタ13bが形成されていてもよい。MOSキャパシタ13bは、N<sup>+</sup>型の上部電極8bを有している。

#### 【0036】

10

20

30

40

50

図7に示した半導体装置では、図1に示した半導体装置における不純物濃度P1, P2, P3の不純物注入領域の代わりに、不純物濃度N1, N2, N3の不純物注入領域がそれぞれ形成されている。

#### 【0037】

このように本実施の形態1に係る半導体装置及びその製造方法によれば、図4に示したように、第2の素子形成領域を覆ってフォトレジスト10を形成した後、このフォトレジスト10を注入マスクに用いて、シリコン層3内にP型不純物11がイオン注入される。上記の通りP型不純物11は比較的高いエネルギーでイオン注入されるため、P型不純物11のイオン注入によってシリコン層3は大きなダメージを受ける。そして、このダメージは、その後にシリコン層3の上面に形成される絶縁膜の信頼性を低下させる原因となる。しかしながら、本実施の形態1に係る半導体装置の製造方法によれば、P型不純物11をイオン注入する際には、第2の素子形成領域を覆ってフォトレジスト10が予め形成されている。従って、P型不純物11のイオン注入によって第2の素子形成領域におけるシリコン層3がダメージを受けることはない。その結果、その後に第2の素子形成領域におけるシリコン層3の上面に形成されるキャパシタ誘電体膜7bの信頼性を高めることができる。10

#### 【0038】

実施の形態2.

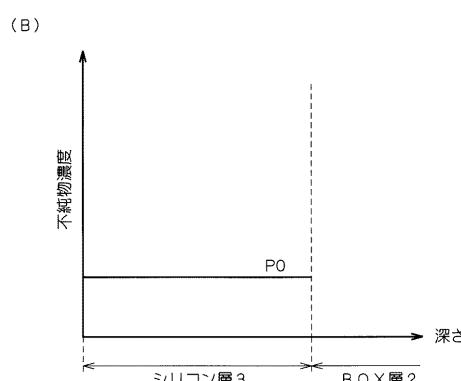

図8は、本発明の実施の形態2に係る半導体装置の構造を示す断面図である。また、図9(図9(A), 図9(B))は、ゲート酸化膜7aの下方におけるシリコン層3の不純物プロファイル(図9(A))と、キャパシタ誘電体膜7bの下方におけるシリコン層3の不純物プロファイル(図9(B))とを示す図である。図8に示すように、キャパシタ誘電体膜7bの下方において、シリコン層3の上面内には、不純物濃度P3の不純物注入領域が形成されていない。その結果、図9(B)に示すように、キャパシタ誘電体膜7bの下方におけるシリコン層3の不純物濃度は、シリコン層3の上面から底面に渡る全ての深さに関して、シリコン層3のそもそもの不純物濃度P0である。本実施の形態2に係る半導体装置のその他の構造は、図1に示した上記実施の形態1に係る半導体装置の構造と同様である。20

#### 【0039】

図10は、本発明の実施の形態2に係る半導体装置の製造方法の一工程を示す断面図である。上記実施の形態1に係る半導体装置の製造方法では、図4に示したフォトレジスト10が除去された後に、図5に示した工程でP型不純物12がイオン注入された。これに対して、本実施の形態2に係る半導体装置の製造方法では、図10に示すように、フォトレジスト10を除去する前に、P型不純物12のイオン注入を行う。即ち、フォトレジスト10を注入マスクに用いて、シリコン層3の上面内にP型不純物12をイオン注入する。30

#### 【0040】

図11は、本実施の形態2に係る半導体装置の変形例を示す断面図である。図11に示すように、NMOSFET6aの代わりにPMOSFET13aが形成されていてもよく、また、MOSキャパシタ6bの代わりにMOSキャパシタ13bが形成されていてもよい。図1, 8に示したMOSキャパシタ6bでは、上部電極(キャパシタ上部電極8b)の導電型と、下部電極(シリコン層3)の導電型とが同一(いずれもP型)であった。これに対し、図11に示したMOSキャパシタ13bでは、上部電極の導電型(N型)と下部電極の導電型(P型)とが互いに異なっている。40

#### 【0041】

このように本実施の形態2に係る半導体装置及びその製造方法によれば、P型不純物11のイオン注入に起因して第2の素子形成領域におけるシリコン層3がダメージを受けることのみならず、P型不純物12のイオン注入に起因して第2の素子形成領域におけるシリコン層3がダメージを受けることをも回避できる。そのため、上記実施の形態1と比較して、キャパシタ誘電体膜7bの信頼性をさらに高めることができる。

#### 【0042】

50

### 実施の形態 3 .

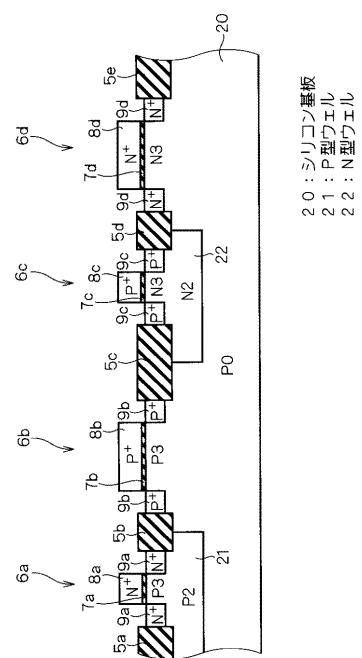

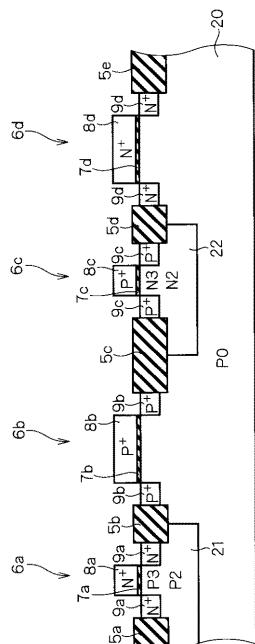

図12は、本発明の実施の形態3に係る半導体装置の構造を示す断面図である。本実施の形態3に係る半導体装置は、不純物濃度P0のP型のシリコン基板20と、素子分離絶縁膜5a～5eと、NMOSFET6aと、PMOSFET6cと、MOSキャパシタ6b, 6dとを備えている。シリコン基板20は、SOI基板ではない通常の基板（「バルク基板」とも称されている）である。NMOSFET6aは、素子分離絶縁膜5a, 5bによって規定される第1の素子形成領域内に形成されている。MOSキャパシタ6bは、素子分離絶縁膜5b, 5cによって規定される第2の素子形成領域内に形成されている。PMOSFET6cは、素子分離絶縁膜5c, 5dによって規定される第3の素子形成領域内に形成されている。MOSキャパシタ6dは、素子分離絶縁膜5d, 5eによって規定される第4の素子形成領域内に形成されている。

#### 【0043】

第1の素子形成領域におけるシリコン基板20の上面内には、不純物濃度P2のP型ウェル21が形成されている。NMOSFET6aのソース・ドレイン領域9aは、P型ウェル21内に形成されている。第3の素子形成領域におけるシリコン基板20の上面内には、不純物濃度N2のN型ウェル22が形成されている。PMOSFET6cのソース・ドレイン領域9cは、N型ウェル22内に形成されている。第2及び第4の素子形成領域におけるシリコン基板20内には、P型ウェル21及びN型ウェル22は形成されていない。

#### 【0044】

図13(図13(A), 図13(B))は、ゲート酸化膜7aの下方におけるシリコン基板20の不純物プロファイル(図13(A))と、キャパシタ誘電体膜7bの下方におけるシリコン基板20の不純物プロファイル(図13(B))とを示す図である。図13に示すように、本実施の形態3に係る半導体装置では、ゲート酸化膜7aの下方におけるシリコン基板20の不純物プロファイルと、キャパシタ誘電体膜7bの下方におけるシリコン基板20の不純物プロファイルとが、互いに異なっている。図13(A)に示すように、ゲート酸化膜7aの下方において、シリコン基板20は、不純物濃度P0よりも高い不純物濃度P2, P3の不純物プロファイルを有している。また、図13(B)に示すように、キャパシタ誘電体膜7bの下方において、シリコン基板20は、シリコン基板20の上面(横軸ゼロ)から所定距離を隔てた深さから、シリコン基板20の底面に至るまでの部分に渡って、不純物濃度がP0で均一の不純物プロファイルを有している。

#### 【0045】

図14～図18は、本発明の実施の形態3に係る半導体装置の製造方法を工程順に示す断面図である。図14を参照して、まず、シリコン基板20を準備する。次に、シリコン基板20の上面内に、素子分離絶縁膜5a～5eを形成する。図14に示すように、シリコン基板20の上面上には、素子分離絶縁膜5a～5eを形成する際にシリコン窒化膜の下敷き膜として機能する、シリコン酸化膜150が残されている。

#### 【0046】

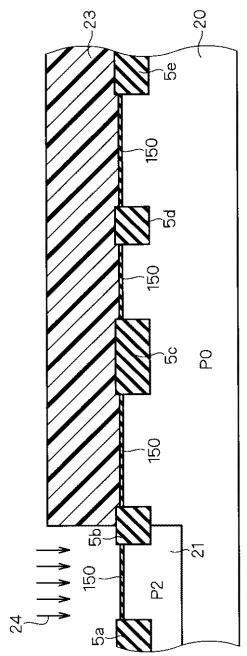

図15を参照して、次に、写真製版法によって、第2～第4の素子形成領域を覆ってフォトレジスト23を形成する。次に、フォトレジスト23を注入マスクに用いて、イオン注入法によって、P型不純物24を比較的高いエネルギーでシリコン基板20内に注入する。これにより、第1の素子形成領域におけるシリコン基板20の上面内に、不純物濃度P2のP型ウェル21が比較的深く形成される。その後、フォトレジスト23を除去する。

#### 【0047】

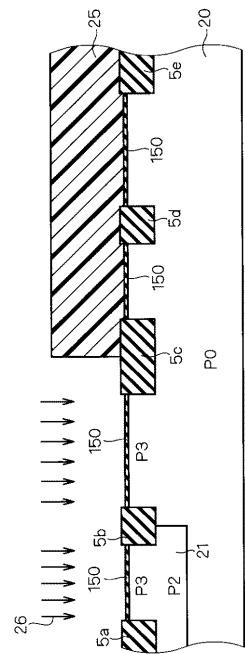

図16を参照して、次に、写真製版法によって、第3及び第4の素子形成領域を覆ってフォトレジスト25を形成する。次に、フォトレジスト25を注入マスクに用いて、イオン注入法によって、NMOSFET6aのしきい値電圧を設定するためのP型不純物26を、比較的低いエネルギーでシリコン基板20内に注入する。これにより、第1及び第2の素子形成領域におけるシリコン基板20の上面内に、不純物濃度P3の不純物注入領域が比較的浅く形成される。その後、フォトレジスト25を除去する。

10

20

30

40

50

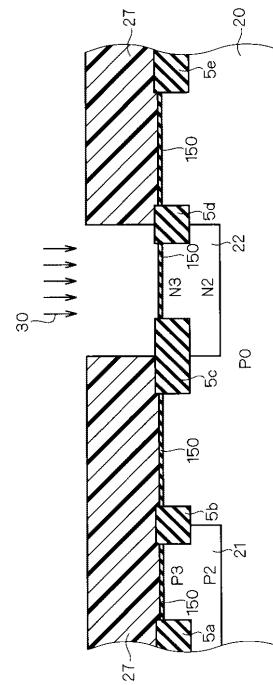

**【0048】**

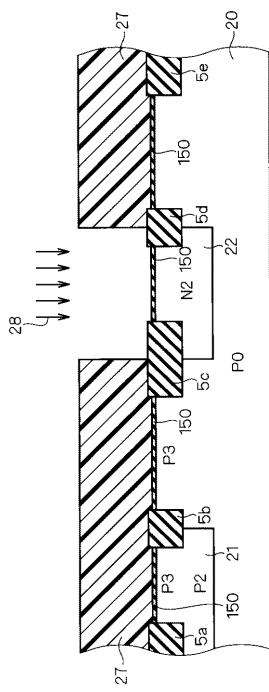

図17を参照して、次に、写真製版法によって、第1、第2、及び第4の素子形成領域を覆ってフォトレジスト27を形成する。次に、フォトレジスト27を注入マスクに用いて、イオン注入法によって、N型不純物28を比較的高いエネルギーでシリコン基板20内に注入する。これにより、第3の素子形成領域におけるシリコン基板20の上面内に、不純物濃度N2のN型ウェル22が比較的深く形成される。その後、フォトレジスト27を除去する。

**【0049】**

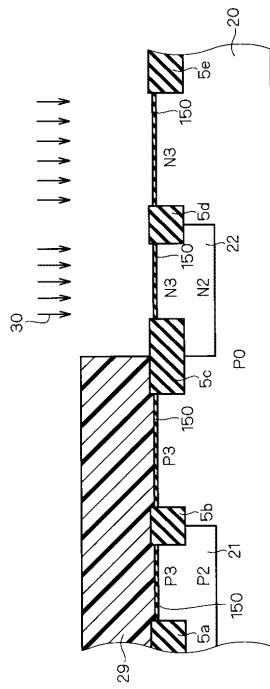

図18を参照して、次に、写真製版法によって、第1及び第2の素子形成領域を覆ってフォトレジスト29を形成する。次に、フォトレジスト29を注入マスクに用いて、イオン注入法によって、PMOSFET6cのしきい値電圧を設定するためのN型不純物30を、比較的低いエネルギーでシリコン基板20内に注入する。これにより、第3及び第4の素子形成領域におけるシリコン基板20の上面内に、不純物濃度N3の不純物注入領域が比較的浅く形成される。その後、フォトレジスト29を除去する。

10

**【0050】**

その後、上記実施の形態1に係る半導体装置の製造方法と同様に、シリコン酸化膜150の除去工程と、ゲート酸化膜7a, 7c、キャパシタ誘電体膜7b, 7d、ゲート電極8a, 8c、及びキャパシタ上部電極8b, 8dの形成工程と、ソース・ドレイン領域9a, 9c及びコンタクト領域9b, 9dの形成工程とがこの順に実行されることにより、図12に示した構造が得られる。

20

**【0051】**

このように本実施の形態3に係る半導体装置及びその製造方法によれば、図15に示したように、少なくとも第2及び第4の素子形成領域を覆ってフォトレジスト23を形成した後、このフォトレジスト23を注入マスクに用いて、シリコン基板20内にP型不純物24がイオン注入される。また、図17に示したように、少なくとも第2及び第4の素子形成領域を覆ってフォトレジスト27を形成した後、このフォトレジスト27を注入マスクに用いて、シリコン基板20内にN型不純物28がイオン注入される。従って、P型不純物24及びN型不純物28のイオン注入によって第2及び第4の素子形成領域におけるシリコン基板20がダメージを受けることはないため、キャパシタ誘電体膜7b, 7dの信頼性を高めることができる。

30

**【0052】**

実施の形態4。

図19は、本発明の実施の形態4に係る半導体装置の構造を示す断面図である。また、図20(図20(A), 図20(B))は、ゲート酸化膜7aの下方におけるシリコン基板20の不純物プロファイル(図20(A))と、キャパシタ誘電体膜7bの下方におけるシリコン基板20の不純物プロファイル(図20(B))とを示す図である。図19に示すように、キャパシタ誘電体膜7bの下方において、シリコン基板20の上面内には、不純物濃度P3の不純物注入領域が形成されていない。また、キャパシタ誘電体膜7dの下方において、シリコン基板20の上面内には、不純物濃度N3の不純物注入領域が形成されていない。その結果、図20(B)に示すように、キャパシタ誘電体膜7b, 7dの下方におけるシリコン基板20の不純物濃度は、シリコン基板20の上面から底面に渡る全ての深さに関して、シリコン基板20のそもそもの不純物濃度P0である。本実施の形態4に係る半導体装置のその他の構造は、図12に示した上記実施の形態3に係る半導体装置の構造と同様である。

40

**【0053】**

図21, 22は、本発明の実施の形態4に係る半導体装置の製造方法を工程順に示す断面図である。上記実施の形態3に係る半導体装置の製造方法では、図15に示したフォトレジスト23が除去された後に、図16に示した工程でフォトレジスト25が形成され、その後にP型不純物26がイオン注入された。これに対して、本実施の形態4に係る半導体装置の製造方法では、図21に示すように、フォトレジスト23を除去する前に、P型不

50

純物 2 6 のイオン注入を行う。即ち、フォトレジスト 2 5 を形成することなく、フォトレジスト 2 3 を注入マスクに用いて、シリコン基板 2 0 の上面内に P 型不純物 2 6 をイオン注入する。

#### 【 0 0 5 4 】

また、上記実施の形態 3 に係る半導体装置の製造方法では、図 1 7 に示したフォトレジスト 2 7 が除去された後に、図 1 8 に示した工程でフォトレジスト 2 9 が形成され、その後に N 型不純物 3 0 がイオン注入された。これに対して、本実施の形態 4 に係る半導体装置の製造方法では、図 2 2 に示すように、フォトレジスト 2 7 を除去する前に、N 型不純物 3 0 のイオン注入を行う。即ち、フォトレジスト 2 9 を形成することなく、フォトレジスト 2 7 を注入マスクに用いて、シリコン基板 2 0 の上面内に N 型不純物 3 0 をイオン注入する。10

#### 【 0 0 5 5 】

このように本実施の形態 4 に係る半導体装置及びその製造方法によれば、P 型不純物 2 4 及び N 型不純物 2 8 のイオン注入に起因して第 2 及び第 4 の素子形成領域におけるシリコン基板 2 0 がダメージを受けることのみならず、P 型不純物 2 6 及び N 型不純物 3 0 のイオン注入に起因して第 2 及び第 4 の素子形成領域におけるシリコン基板 2 0 がダメージを受けることをも回避できる。そのため、上記実施の形態 3 と比較して、キャパシタ誘電体膜 7 b , 7 d の信頼性をさらに高めることができる。

#### 【 0 0 5 6 】

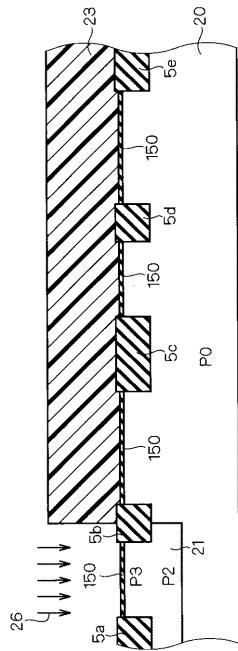

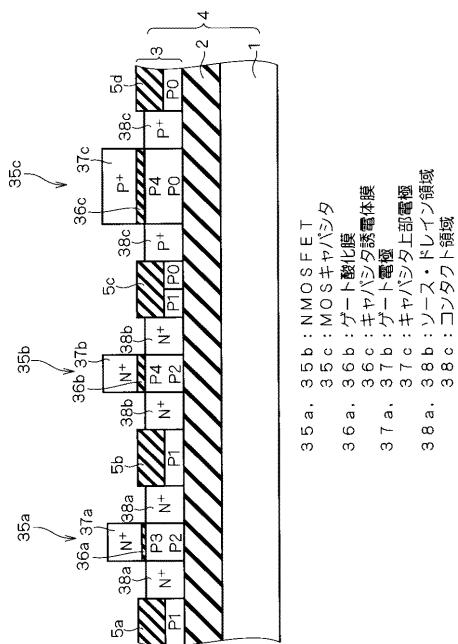

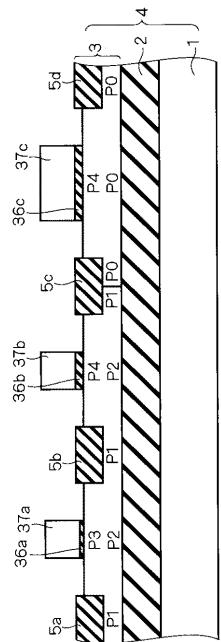

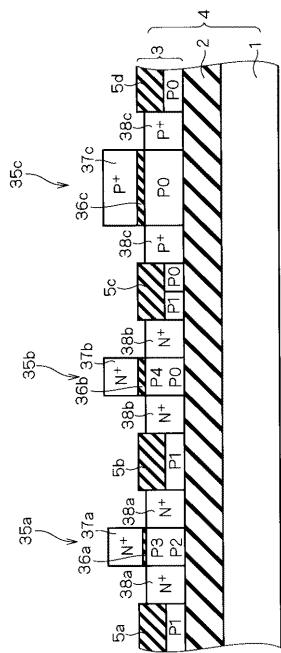

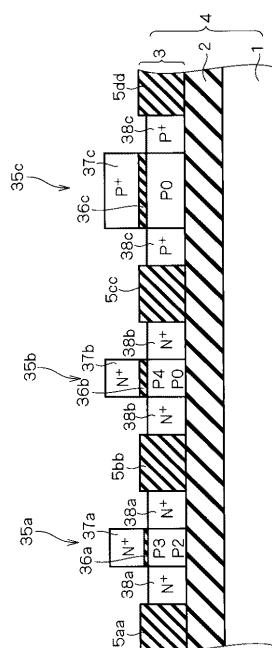

実施の形態 5 .20

図 2 3 は、本発明の実施の形態 5 に係る半導体装置の構造を示す断面図である。本実施の形態 5 に係る半導体装置は、SOI 基板 4 と、部分分離型の素子分離絶縁膜 5 a ~ 5 d と、NMOSFET 3 5 a , 3 5 b と、MOS キャパシタ 3 5 c とを備えている。NMOSFET 3 5 a は、素子分離絶縁膜 5 a , 5 b によって規定される第 1 の素子形成領域内に形成されている。NMOSFET 3 5 a は、比較的低い電圧で駆動される低電圧回路を構成する MOSFET であり、3 . 5 nm 程度の膜厚のゲート酸化膜 3 6 a を有している。NMOSFET 3 5 a のゲート電極 3 7 a には、1 . 8 V 程度のゲート電圧が印加される。また、NMOSFET 3 5 a は、対を成すソース・ドレイン領域 3 8 a を有している。

#### 【 0 0 5 7 】

NMOSFET 3 5 b は、素子分離絶縁膜 5 b , 5 c によって規定される第 2 の素子形成領域内に形成されている。NMOSFET 3 5 b は、比較的高い電圧で駆動される高電圧回路を構成する MOSFET であり、ゲート酸化膜 3 6 a よりも高い信頼性が要求されるゲート酸化膜 3 6 b を有している。ゲート酸化膜 3 6 b の膜厚は、ゲート酸化膜 3 6 a の膜厚よりも大きく、7 . 5 nm 程度である。NMOSFET 3 5 b のゲート電極 3 7 b には、ゲート電極 3 7 a に印加されるゲート電圧よりも高い、3 . 3 V 程度のゲート電圧が印加される。また、NMOSFET 3 5 b は、対を成すソース・ドレイン領域 3 8 b を有している。30

#### 【 0 0 5 8 】

MOS キャパシタ 3 5 c は、素子分離絶縁膜 5 c , 5 d によって規定される第 3 の素子形成領域内に形成されている。MOS キャパシタ 3 5 c は、キャパシタ誘電体膜 3 6 c とキャパシタ上部電極 3 7 c とを有している。キャパシタ誘電体膜 3 6 c はゲート酸化膜 3 6 a よりも高い信頼性が要求される膜であり、キャパシタ誘電体膜 3 6 c の膜厚はゲート酸化膜 3 6 b の膜厚と同一である。但し、キャパシタ誘電体膜 3 6 c の膜厚を、ゲート酸化膜 3 6 b の膜厚よりも大きくしてもよい。この場合、シリコン層 3 の上面上には、互いに膜厚が異なる 3 種類の絶縁膜が形成されることになる。また、MOS キャパシタ 3 5 c は、対を成すコンタクト領域 3 8 c を有している。40

#### 【 0 0 5 9 】

素子分離絶縁膜 5 a , 5 b の底面と BOX 層 2 の上面とによって挟まれている部分のシリコン層 3 内には、イオン注入によって、P 型不純物が不純物濃度 P 1 で注入されている。同様に、図 2 3 において素子分離絶縁膜 5 c の左半分の底面 ( NMOSFET 3 5 b に接50

する側の半分の底面)と、BOX層2の上面とによって挟まれている部分のシリコン層3内には、P型不純物が不純物濃度P1で注入されている。また、このときのイオン注入に起因して、ゲート酸化膜36a, 36bの下方において、BOX層2との界面付近におけるシリコン層3内には、P型不純物が不純物濃度P2で注入されている。一方、キャパシタ誘電体膜36cの下方において、BOX層2との界面付近におけるシリコン層3の不純物濃度は、シリコン層3のそもそもの不純物濃度P0である。

#### 【0060】

ゲート酸化膜36aの下方において、シリコン層3の上面内には、イオン注入によって、NMOSFET35aのしきい値電圧を設定するためのP型不純物が不純物濃度P3で注入されている。

10

#### 【0061】

ゲート酸化膜36bの下方において、シリコン層3の上面内には、イオン注入によって、NMOSFET35bのしきい値電圧を設定するためのP型不純物が不純物濃度P4で注入されている。不純物濃度P4は、不純物濃度P3よりも低い。また、このときのイオン注入に起因して、キャパシタ誘電体膜36cの下方において、シリコン層3の上面内には、P型不純物が不純物濃度P4で注入されている。

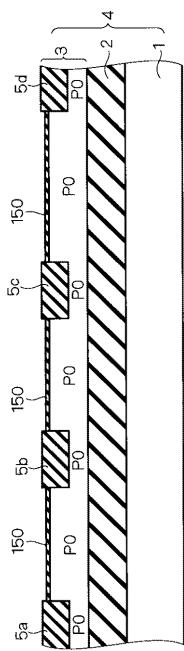

#### 【0062】

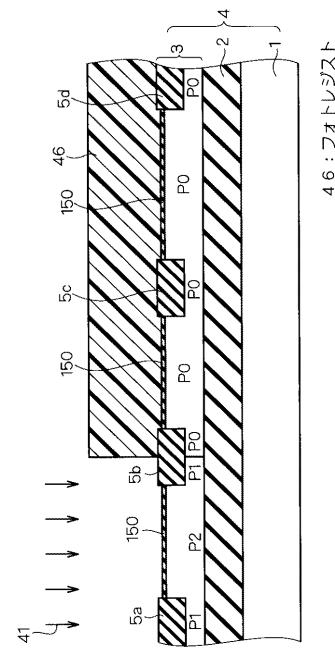

図24～図30は、本発明の実施の形態5に係る半導体装置の製造方法を工程順に示す断面図である。図24を参照して、まず、SOI基板4を準備した後、素子分離絶縁膜5a～5dを形成する。上記実施の形態1と同様に、シリコン層3の上面内にはシリコン酸化膜150が残されている。

20

#### 【0063】

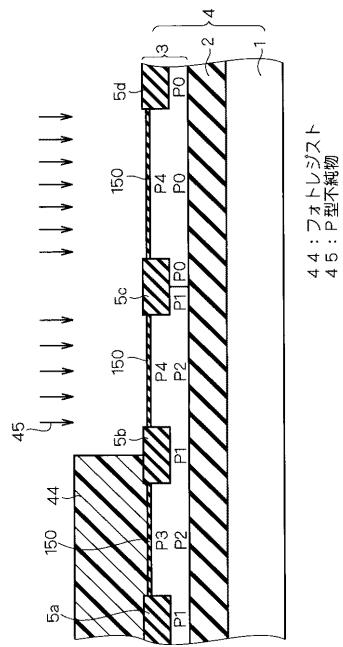

図25を参照して、次に、写真製版法によって、第3の素子形成領域を覆ってフォトレジスト40を形成する。次に、フォトレジスト40を注入マスクに用いて、イオン注入法によって、BOX層2との界面付近におけるシリコン層3内に到達し得る比較的高いエネルギーで、P型不純物41をシリコン層3内に深く注入する。これにより、第1及び第2の素子形成領域におけるシリコン層3内に、不純物濃度P1, P2の不純物注入領域が形成される。その後、フォトレジスト40を除去する。

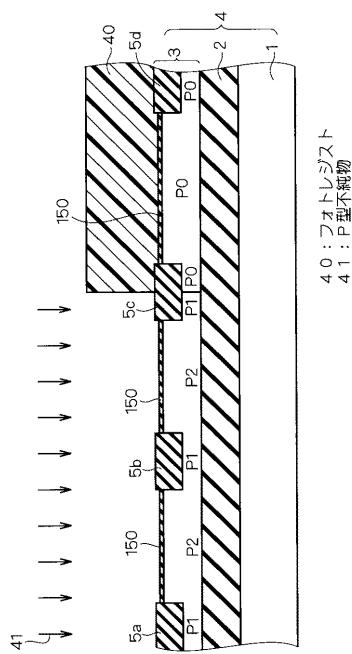

#### 【0064】

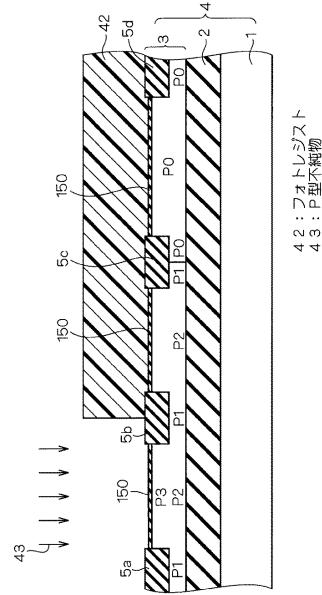

図26を参照して、次に、写真製版法によって、第2及び第3の素子形成領域を覆ってフォトレジスト42を形成する。次に、フォトレジスト42を注入マスクに用いて、イオン注入法によって、比較的低いエネルギーで、P型不純物43をシリコン層3の上面内に浅く注入する。これにより、第1の素子形成領域におけるシリコン層3の上面内に、不純物濃度P3の不純物注入領域が形成される。その後、フォトレジスト42を除去する。

30

#### 【0065】

図27を参照して、次に、写真製版法によって、第1の素子形成領域を覆ってフォトレジスト44を形成する。次に、フォトレジスト44を注入マスクに用いて、イオン注入法によって、比較的低いエネルギーで、P型不純物45をシリコン層3の上面内に浅く注入する。これにより、第2及び第3の素子形成領域におけるシリコン層3の上面内に、不純物濃度P4の不純物注入領域が形成される。その後、フォトレジスト44及びシリコン酸化膜150を除去する。

40

#### 【0066】

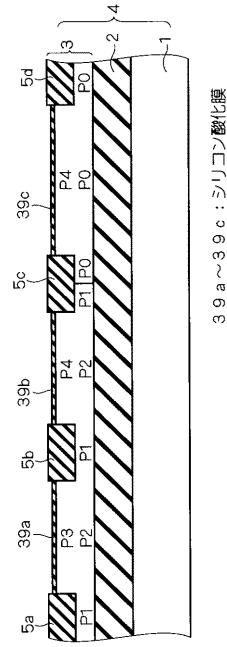

図28を参照して、次に、熱酸化法によって、第1～第3の素子形成領域におけるシリコン層3の上面内に、シリコン酸化膜39a～39cを形成する。

#### 【0067】

図29を参照して、次に、写真製版法及びエッチング法によってシリコン酸化膜39aを除去することにより、第1の素子形成領域におけるシリコン層3の上面を露出する。次に、熱酸化法によって、第1の素子形成領域におけるシリコン層3の上面内に、シリコン酸化膜36aを形成する。この熱酸化によってシリコン酸化膜39b, 39cの膜厚が増大し、シリコン酸化膜36b, 36cが形成される。

50

**【0068】**

図30を参照して、次に、全面に形成したポリシリコン膜をパターニングすることにより、ゲート電極37a, 37b及びキャパシタ上部電極37cを形成する。その後、写真製版法及びイオン注入法によって、N型不純物及びP型不純物をシリコン層3内に部分的に注入することにより、ソース・ドレイン領域38a, 38b及びコンタクト領域38cを形成する。以上の工程により、図23に示した構造が得られる。

**【0069】**

このように本実施の形態5に係る半導体装置及びその製造方法によれば、図25に示したように、第3の素子形成領域を覆ってフォトレジスト40を形成した後、このフォトレジスト40を注入マスクに用いて、シリコン層3内にP型不純物41がイオン注入される。従って、P型不純物41のイオン注入によって第3の素子形成領域におけるシリコン層3がダメージを受けることはないため、キャパシタ誘電体膜36cの信頼性を高めることができる。10

**【0070】**

また、ゲート酸化膜36b及びキャパシタ誘電体膜36cの膜厚が、ゲート酸化膜36aの膜厚よりも大きいため、ゲート酸化膜36aと比較して、ゲート酸化膜36b及びキャパシタ誘電体膜36cの信頼性を高めることができる。

**【0071】**

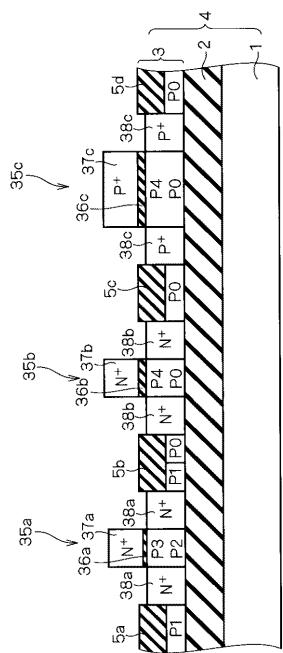

実施の形態6.

図31は、本発明の実施の形態6に係る半導体装置の構造を示す断面図である。ゲート酸化膜36bの下方において、シリコン層3内には、不純物濃度P2の不純物注入領域が形成されていない。その結果、ゲート酸化膜36bの下方において、BOX層2との界面付近におけるシリコン層3の不純物濃度は、シリコン層3のそもそもその不純物濃度P0である。また、図31において素子分離絶縁膜5bの右半分の底面(NMOSFET35bに接する側の半分の底面)と、BOX層2の上面とによって挟まれている部分のシリコン層3の不純物濃度は、シリコン層3のそもそもその不純物濃度P0である。さらに、素子分離絶縁膜5cの底面とBOX層2の上面とによって挟まれている部分のシリコン層3の不純物濃度は、シリコン層3のそもそもその不純物濃度P0である。本実施の形態6に係る半導体装置のその他の構造は、図23に示した上記実施の形態5に係る半導体装置の構造と同様である。2030

**【0072】**

図32は、本発明の実施の形態6に係る半導体装置の製造方法の一工程を示す断面図である。上記実施の形態5に係る半導体装置の製造方法では、図25に示した工程において、第3の素子形成領域を覆うフォトレジスト40が形成された。本実施の形態6に係る半導体装置の製造方法では、フォトレジスト40の代わりに、図32に示すように、第2及び第3の素子形成領域を覆うフォトレジスト46を形成する。P型不純物41は、フォトレジスト46を注入マスクに用いてイオン注入される。

**【0073】**

このように本実施の形態6に係る半導体装置及びその製造方法によれば、P型不純物41のイオン注入によって第2の素子形成領域におけるシリコン層3がダメージを受けることはない。そのため、上記実施の形態5と比較すると、ゲート酸化膜36bの信頼性を高めることができる。

**【0074】**

実施の形態7.

図33は、本発明の実施の形態7に係る半導体装置の構造を示す断面図である。キャパシタ誘電体膜36cの下方において、シリコン層3の上面内には、不純物濃度P4の不純物注入領域が形成されていない。その結果、キャパシタ誘電体膜36cの下方において、シリコン層3の上面付近における不純物濃度は、シリコン層3のそもそもその不純物濃度P0である。本実施の形態7に係る半導体装置のその他の構造は、図23に示した上記実施の形態5に係る半導体装置の構造と同様である。4050

## 【0075】

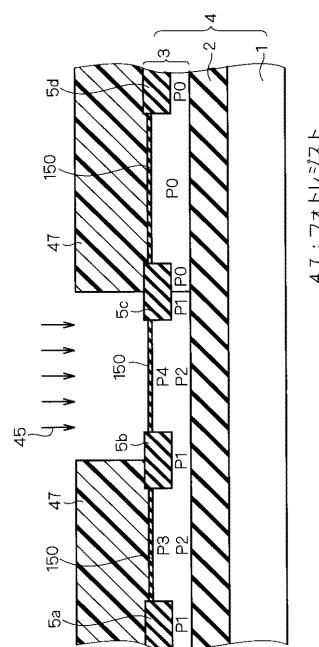

図34は、本発明の実施の形態7に係る半導体装置の製造方法の一工程を示す断面図である。上記実施の形態5に係る半導体装置の製造方法では、図27に示した工程において、第1の素子形成領域を覆うフォトレジスト44が形成された。本実施の形態7に係る半導体装置の製造方法では、フォトレジスト44の代わりに、図34に示すように、第1及び第3の素子形成領域を覆うフォトレジスト47を形成する。P型不純物45は、フォトレジスト47を注入マスクに用いてイオン注入される。

## 【0076】

このように本実施の形態7に係る半導体装置及びその製造方法によれば、P型不純物41のイオン注入に起因して第3の素子形成領域におけるシリコン層3がダメージを受けることのみならず、P型不純物45のイオン注入に起因して第3の素子形成領域におけるシリコン層3がダメージを受けることをも回避できる。そのため、上記実施の形態5と比較して、キャパシタ誘電体膜36cの信頼性をさらに高めることができる。

10

## 【0077】

図35は、本実施の形態7に係る半導体装置の変形例を示す断面図である。この変形例は、上記実施の形態6と本実施の形態7とを組み合わせることによって実現されている。上記実施の形態5に係る半導体装置とは異なり、ゲート酸化膜36bの下方には、不純物濃度P2の不純物注入領域が形成されていない。また、キャパシタ誘電体膜36cの下方には、不純物濃度P4の不純物注入領域が形成されていない。これにより、上記実施の形態6による効果と、本実施の形態7による効果とをともに得ることができる。

20

## 【0078】

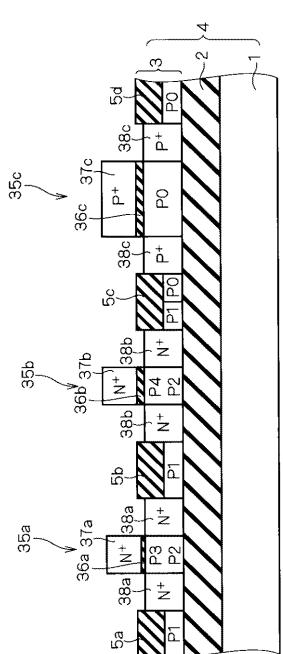

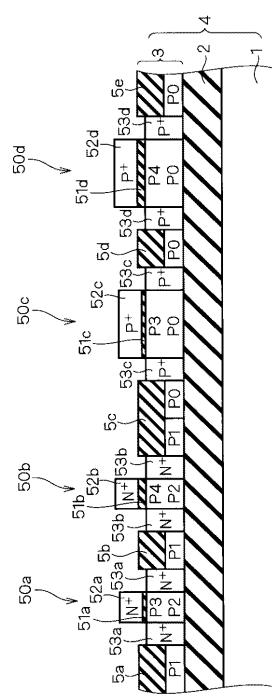

実施の形態8。

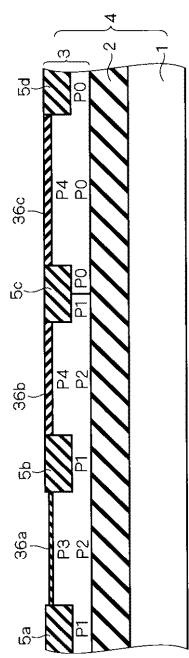

図36は、本発明の実施の形態8に係る半導体装置の構造を示す断面図である。本実施の形態8に係る半導体装置は、SOI基板4と、部分分離型の素子分離絶縁膜5a～5eと、NMOSFET50a, 50bと、MOSキャパシタ50c, 50dとを備えている。NMOSFET50aは第1の素子形成領域内に形成されており、NMOSFET50bは第2の素子形成領域内に形成されており、MOSキャパシタ50cは第3の素子形成領域内に形成されており、MOSキャパシタ50dは第4の素子形成領域内に形成されている。

30

## 【0079】

NMOSFET50aは低電圧回路を構成するMOSFETであり、NMOSFET50bは高電圧回路を構成するMOSFETである。本実施の形態8に係る半導体装置では、デバイスの動作の安定化を図るために、低電圧回路に対応するMOSキャパシタ50cと、高電圧回路に対応するMOSキャパシタ50dとが個別に形成されている。MOSキャパシタ50cは低電圧回路に接続されており、MOSキャパシタ50dは高電圧回路に接続されている。

30

## 【0080】

ゲート酸化膜51b及びキャパシタ誘電体膜51c, 51dは、ゲート酸化膜51aよりも高い信頼性が要求される膜である。ゲート酸化膜51b及びキャパシタ誘電体膜51dの膜厚は、ゲート酸化膜51aの膜厚よりも大きい。

40

## 【0081】

第1及び第2の素子形成領域におけるシリコン層3の底部にP型不純物をイオン注入する際に、第3及び第4の素子形成領域がフォトレジストで覆われる。その結果、キャパシタ誘電体膜51c, 51dの下方において、BOX層2との界面付近におけるシリコン層3の不純物濃度は、シリコン層3のそもそもの不純物濃度P0となっている。

## 【0082】

変形例として、第1の素子形成領域におけるシリコン層3の上部にP型不純物をイオン注入する際に、少なくとも第3の素子形成領域をフォトレジストによって覆ってよい。これにより、キャパシタ誘電体膜51cの下方に不純物濃度P3の不純物注入領域が形成されることを、回避することができる。

50

**【 0 0 8 3 】**

また、第2の素子形成領域におけるシリコン層3の上部にP型不純物をイオン注入する際に、少なくとも第4の素子形成領域をフォトレジストによって覆ってもよい。これにより、キャパシタ誘電体膜51dの下方に不純物濃度P4の不純物注入領域が形成されることを、回避することができる。

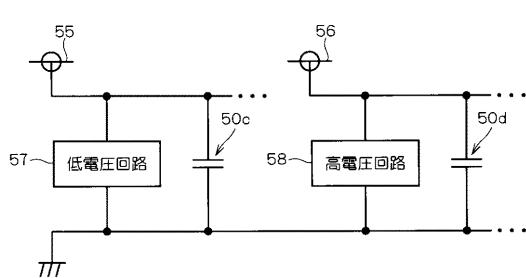

**【 0 0 8 4 】**

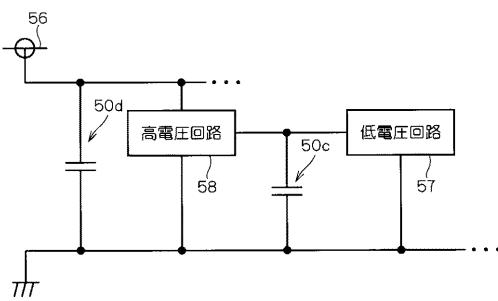

図37は、本実施の形態8に係る半導体装置が適用された回路の第1の例を示す回路図である。低電圧回路57及び高電圧回路58には、図36に示したNMOSFET50a及びNMOSFET50bがそれぞれ含まれている。低電圧回路57には、比較的低い電源電位を供給する電源55が接続されている。高電圧回路58には、比較的高い電源電位を供給する電源56が接続されている。低電圧回路57及び高電圧回路58には、GND電位を与える共通配線が接続されている。MOSキャパシタ50cは、電源55と共に接続され、低電圧回路57用のデカップリングキャパシタとして機能する。MOSキャパシタ50dは、電源56と共に接続され、高電圧回路58用のデカップリングキャパシタとして機能する。

10

**【 0 0 8 5 】**

図38は、本実施の形態8に係る半導体装置が適用された回路の第2の例を示す回路図である。図38に示した回路には、2つの電源55, 56が設けられているのではなく、1つの電源56のみが設けられている。低電圧回路57には、電源56の電源電位を高電圧回路58によってダウンコンバートした電位が、供給されている。即ち、図38に示した回路では、高電圧回路58が低電圧回路57用の電源として機能している。

20

**【 0 0 8 6 】**

このように本実施の形態8に係る半導体装置及びその製造方法によれば、低電圧回路57用のMOSキャパシタ50cと、高電圧回路58用のMOSキャパシタ50dとが個別に形成された半導体集積回路において、イオン注入に起因するシリコン層3のダメージを抑制又は回避することにより、キャパシタ誘電体膜51c, 51dの信頼性を高めることができる。その結果、半導体集積回路のキャパシタ部の信頼性、ひいては半導体集積回路全体の信頼性を向上することができる。

**【 0 0 8 7 】**

実施の形態9。

30

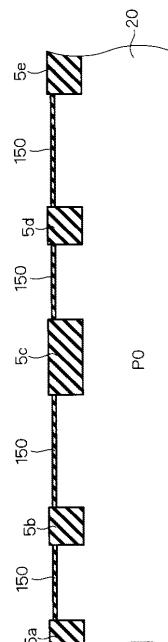

図39は、本発明の実施の形態9に係る半導体装置の構造を示す断面図である。上記実施の形態1, 2, 5~8では、SOI基板4のシリコン層3の上面内に、部分分離型の素子分離絶縁膜5a~5eが形成されていた。これに対して本実施の形態9に係る半導体装置では、図39に示すように、部分分離型の素子分離絶縁膜5a~5eに代えて、素子分離絶縁膜5aa~5ddが形成されている。素子分離絶縁膜5aa~5ddの底面は、BOX層2の上面に接触している。このような構造の素子分離絶縁膜は、「完全分離型の素子分離絶縁膜」と称されている。

**【 0 0 8 8 】**

このように本実施の形態9に係る半導体装置によれば、完全分離型の素子分離絶縁膜5aa~5ddを形成することにより、上記実施の形態1, 2, 5~8に係る半導体装置と比較して、素子間の分離効果を高めることができる。

40

**【 0 0 8 9 】**

実施の形態10。

上記実施の形態1, 2, 5~8では、キャパシタ部では素子分離のための不純物注入を行わないことで、キャパシタ誘電体膜の信頼性の向上が図られていた。しかしながら、上記実施の形態1, 2, 5~8では部分分離型の素子分離絶縁膜5a~5eが採用されていたため、半導体素子のレイアウトによっては、回路の不具合が生じる可能性があった。例えば図11に示したように、PMOSFET13aと、N型のコンタクト領域9bを有するMOSキャパシタ13bとが互いに隣接して形成されている場合には、P<sup>+</sup>-N1-P0-N<sup>+</sup>型の寄生サイリスタ構造がシリコン層3内に形成されるため、ラッチアップが発生

50

する可能性があった。そこで本実施の形態 10 では、かかる不具合の発生を回避し得る半導体装置を提案する。

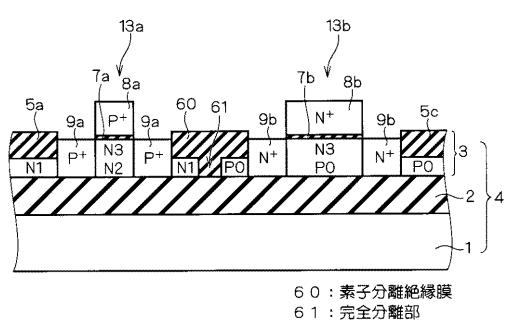

#### 【 0 0 9 0 】

図 4 0 は、例えば図 1 1 を基礎として、本発明の実施の形態 10 に係る半導体装置の構造を示す断面図である。PMOSFET 13a と MOS キャパシタ 13bとの間には、部分分離型の素子分離絶縁膜 5b の代わりに、素子分離絶縁膜 60 が形成されている。素子分離絶縁膜 60 の底面の一部には BOX 層 2 の上面に接触する完全分離部 61 が形成されており、素子分離絶縁膜 60 は、完全分離型の素子分離絶縁膜として機能する。

#### 【 0 0 9 1 】

このように本実施の形態 10 に係る半導体装置によれば、互いに隣接する MOSFET 10 と MOS キャパシタとの間には、完全分離型の素子分離絶縁膜 60 が形成されている。従って、たとえ PMOSFET と N 型のコンタクト領域を有する MOS キャパシタとが互いに隣接して形成されている場合であっても、寄生サイリスタ構造が形成されることはないと 10 め、ラッチャップの発生を回避することができる。

#### 【 0 0 9 2 】

なお、上記実施の形態 1 ~ 10 の説明では、MOSFET 及び MOS キャパシタの構造を簡略化して図示した。しかしながら、本願発明の目的は、基板の主面上に形成された絶縁膜の信頼性を向上するために、絶縁膜が形成される予定の領域の下方に位置する部分の基板内において、イオン注入に起因する基板のダメージを抑制又は回避することである。そのため、LDD 構造（又はエクステンション構造）やシリサイド構造が採用された半導体装置及びその製造方法に関しても、本願発明を適用することは可能である。 20

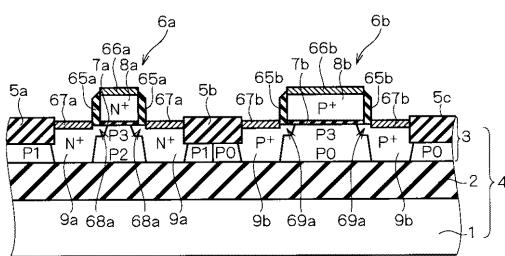

#### 【 0 0 9 3 】

図 4 1 は、本発明の実施の形態 1 ~ 10 に係る半導体装置の変形例を示す断面図である。ゲート電極 8a 及びキャパシタ上部電極 8b の各側面には、サイドウォール 65a, 65b がそれぞれ形成されている。ゲート電極 8a 及びキャパシタ上部電極 8b の各上面には、シリサイド層 66a, 66b がそれぞれ形成されている。ソース・ドレイン領域 9a 及びコンタクト領域 9b は、エクステンション領域 68a, 69a をそれぞれ有している。ソース・ドレイン領域 9a 及びコンタクト領域 9b の各上面には、シリサイド層 67a, 67b がそれぞれ形成されている。

#### 【 0 0 9 4 】

##### 【発明の効果】

この発明のうち請求項 1 ~ 3, 5 に係るものによれば、第 1 濃度が半導体層のそもそもの不純物濃度である場合、半導体装置の製造方法は以下の工程を備える。即ち、第 2 の素子形成領域を覆ってフォトレジストを形成し、このフォトレジストを注入マスクに用いて半導体層の底部内に不純物をイオン注入することによって、第 1 の素子形成領域における半導体層内にウェル領域あるいは第 1 の不純物導入領域を形成する工程を備える。従って、このイオン注入によって第 2 の素子形成領域における半導体層がダメージを受けることはないため、その後に第 2 の素子形成領域における半導体層の主表面上に形成される第 1 のキャパシタ誘電体膜の信頼性を高めることができる。 30

#### 【 0 0 9 5 】

また、この発明のうち請求項 4 に係るものによれば、第 1 濃度が半導体層のそもそもの不純物濃度である場合、半導体装置の製造工程において、第 2 の素子形成領域内には不純物がイオン注入されない。従って、イオン注入によって第 2 の素子形成領域における半導体層がダメージを受けることはないため、第 1 のキャパシタ誘電体膜の信頼性をさらに高めることができる。 40

#### 【 0 0 9 6 】

また、この発明のうち請求項 6, 7 に係るものによれば、第 1 濃度が半導体層のそもそもの不純物濃度である場合、半導体装置の製造方法は以下の工程を備える。即ち、第 2 及び第 4 の素子形成領域を覆ってフォトレジストを形成し、このフォトレジストを注入マスクに用いて半導体層の底部内に不純物をイオン注入することによって、第 1 及び第 3 の素 50

子形成領域における半導体層内に第1及び第2の不純物導入領域あるいは第1及び第2のウェル領域をそれぞれ形成する工程を備える。従って、このイオン注入によって第2及び第4の素子形成領域における半導体層がダメージを受けることはないため、その後に第2及び第4の素子形成領域における半導体層の主表面上にそれぞれ形成される第1及び第3のキャパシタ誘電体膜の信頼性を高めることができる。

【0097】

また、この発明のうち請求項8に係るものによれば、デカップリングキャパシタとして機能する第1及び第2のMOSキャパシタの第1及び第2のキャパシタ誘電体膜の信頼性を高めることができる。

【0098】

また、この発明のうち請求項9に係るものによれば、第1濃度が半導体基板のそもそもの不純物濃度である場合、半導体装置の製造方法は以下の工程を備える。即ち、第2の素子形成領域を覆ってフォトレジストを形成し、このフォトレジストを注入マスク用いて半導体基板の第1主表面内に不純物をイオン注入することによって、第1の素子形成領域における半導体基板内にウェル領域を形成する工程を備える。従って、このイオン注入によって第2の素子形成領域における半導体基板がダメージを受けることはないため、その後に第2の素子形成領域における半導体基板の第1主表面上に形成されるキャパシタ誘電体膜の信頼性を高めることができる。

【0099】

また、この発明のうち請求項10, 11に係るものによれば、第1の不純物の注入工程によって第2の素子形成領域における半導体層がダメージを受けることはない。その結果、その後に第2の素子形成領域における半導体層の主表面上に形成されるキャパシタ誘電体膜の信頼性を高めることができる。

【0100】

また、この発明のうち請求項12, 13に係るものによれば、第2の不純物の注入工程によって第2の素子形成領域における半導体層がダメージを受けることはない。その結果、その後に第2の素子形成領域における半導体層の主表面上に形成されるキャパシタ誘電体膜の信頼性をさらに高めることができる。

【0101】

また、この発明のうち請求項14に係るものによれば、第1及び第2の不純物の注入工程によって第2の素子形成領域における半導体基板がダメージを受けることはない。その結果、その後に第2の素子形成領域における半導体基板の主表面上に形成されるキャパシタ誘電体膜の信頼性を高めることができる。

【図面の簡単な説明】

【図1】 本発明の実施の形態1に係る半導体装置の構造を示す断面図である。

【図2】 本発明の実施の形態1に関して、シリコン層の不純物プロファイルを示す図である。

【図3】 本発明の実施の形態1に係る半導体装置の製造方法を工程順に示す断面図である。

【図4】 本発明の実施の形態1に係る半導体装置の製造方法を工程順に示す断面図である。

【図5】 本発明の実施の形態1に係る半導体装置の製造方法を工程順に示す断面図である。

【図6】 本発明の実施の形態1に係る半導体装置の製造方法を工程順に示す断面図である。

【図7】 本発明の実施の形態1に係る半導体装置の変形例を示す断面図である。

【図8】 本発明の実施の形態2に係る半導体装置の構造を示す断面図である。

【図9】 本発明の実施の形態2に関して、シリコン層の不純物プロファイルを示す図である。

【図10】 本発明の実施の形態2に係る半導体装置の製造方法の一工程を示す断面図で

10

20

30

40

50

ある。

- 【図11】 本発明の実施の形態2に係る半導体装置の変形例を示す断面図である。

- 【図12】 本発明の実施の形態3に係る半導体装置の構造を示す断面図である。

- 【図13】 本発明の実施の形態3に関して、シリコン基板の不純物プロファイルを示す図である。

- 【図14】 本発明の実施の形態3に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図15】 本発明の実施の形態3に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図16】 本発明の実施の形態3に係る半導体装置の製造方法を工程順に示す断面図である。 10

- 【図17】 本発明の実施の形態3に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図18】 本発明の実施の形態3に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図19】 本発明の実施の形態4に係る半導体装置の構造を示す断面図である。

- 【図20】 本発明の実施の形態4に関して、シリコン基板の不純物プロファイルを示す図である。

- 【図21】 本発明の実施の形態4に係る半導体装置の製造方法を工程順に示す断面図である。 20

- 【図22】 本発明の実施の形態4に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図23】 本発明の実施の形態5に係る半導体装置の構造を示す断面図である。

- 【図24】 本発明の実施の形態5に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図25】 本発明の実施の形態5に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図26】 本発明の実施の形態5に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図27】 本発明の実施の形態5に係る半導体装置の製造方法を工程順に示す断面図である。 30

- 【図28】 本発明の実施の形態5に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図29】 本発明の実施の形態5に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図30】 本発明の実施の形態5に係る半導体装置の製造方法を工程順に示す断面図である。

- 【図31】 本発明の実施の形態6に係る半導体装置の構造を示す断面図である。

- 【図32】 本発明の実施の形態6に係る半導体装置の製造方法の一工程を示す断面図である。 40

- 【図33】 本発明の実施の形態7に係る半導体装置の構造を示す断面図である。

- 【図34】 本発明の実施の形態7に係る半導体装置の製造方法の一工程を示す断面図である。

- 【図35】 本発明の実施の形態7に係る半導体装置の変形例を示す断面図である。

- 【図36】 本発明の実施の形態8に係る半導体装置の構造を示す断面図である。

- 【図37】 本発明の実施の形態8に係る半導体装置が適用された回路の第1の例を示す回路図である。

- 【図38】 本発明の実施の形態8に係る半導体装置が適用された回路の第2の例を示す回路図である。

- 【図39】 本発明の実施の形態9に係る半導体装置の構造を示す断面図である。 50

【図40】 本発明の実施の形態10に係る半導体装置の構造を示す断面図である。

【図41】 本発明の実施の形態1~10に係る半導体装置の変形例を示す断面図である。

【図42】 従来の第1の半導体装置の構造を示す断面図である。

【図43】 従来の第2の半導体装置の構造を示す断面図である。

【符号の説明】

1 シリコン基板、2 BOX層、3 シリコン層、4 SOI基板、5a~5d 素子分離絶縁膜、6a, 35a, 35b, 50a, 50b NMOSFET、6b, 13b, 35c, 50c, 50d MOSキャバシタ、7a, 36a, 36b, 51a, 51b ゲート酸化膜、7b, 36c, 51c, 51d キャバシタ誘電体膜、8a, 37a, 37b, 52a, 52b ゲート電極、8b, 37c, 52c, 52d キャバシタ上部電極、10, 23, 25, 27, 29, 40, 42, 44, 46, 47 フォトレジスト、11, 12, 24, 26, 41, 43, 45 P型不純物、13a PMOSFET、20 シリコン基板、21 P型ウェル、22 N型ウェル、28, 30 N型不純物、57 低電圧回路、58 高電圧回路、60 素子分離絶縁膜、61 完全分離部。 10

【図1】

- 1 : シリコン基板

- 2 : BOX層

- 3 : シリコン層

- 4 : SOI基板

- 5 a ~ 5 c : 素子分離絶縁膜

- 6 a : NMOSFET

- 6 b : MOSキャバシタ

- 7 a : ゲート酸化膜

- 7 b : キャバシタ誘電体膜

- 8 a : ゲート電極

- 8 b : キャバシタ上部電極

- 9 a : ソース・ドレイン領域

- 9 b : コンタクト領域

【図2】

(B)

【図3】

【図5】

【図4】

【図6】

【図7】

【図9】

【図8】

【図 1 0】

【図 1 2】

【図 1 1】

【図 1 3】

【図 1 4】

【図15】

2 4 : P型不純物

【図16】

2 5 : P型不純物

2 6 : フオトレジスト

【図17】

2 7 : フオトレジスト

2 8 : N型不純物

【図18】

2 9 : フオトレジスト

3 0 : N型不純物

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

5 a a ~ 5 d d : 素子分離絶縁膜

【図40】

【図42】

【図41】

【図43】

---

フロントページの続き

|                          |                      |

|--------------------------|----------------------|

| (51)Int.Cl.              | F I                  |

| H 01 L 21/8238 (2006.01) | H 01 L 27/08 3 2 1 A |

| H 01 L 27/092 (2006.01)  | H 01 L 27/08 1 0 2 A |

| H 01 L 27/088 (2006.01)  | H 01 L 27/08 3 3 1 E |

| H 01 L 27/08 (2006.01)   |                      |

(56)参考文献 特開平06-163818(JP,A)

特開平11-204655(JP,A)

特開2000-340674(JP,A)

特開2000-299388(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8234

H01L 21/822

H01L 21/8238

H01L 27/04

H01L 27/06

H01L 27/08

H01L 27/088

H01L 27/092

H01L 29/786