(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5222628号

(P5222628)

(45) 発行日 平成25年6月26日(2013.6.26)

(24) 登録日 平成25年3月15日(2013.3.15)

(51) Int.Cl.

G06K 19/07 (2006.01)

F 1

G06K 19/00

G06K 19/00J

H

請求項の数 3 (全 32 頁)

(21) 出願番号 特願2008-141002 (P2008-141002)

(22) 出願日 平成20年5月29日 (2008.5.29)

(65) 公開番号 特開2009-9558 (P2009-9558A)

(43) 公開日 平成21年1月15日 (2009.1.15)

審査請求日 平成23年5月5日 (2011.5.5)

(31) 優先権主張番号 特願2007-144372 (P2007-144372)

(32) 優先日 平成19年5月31日 (2007.5.31)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 河江 大輔

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 池田 隆之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 上妻 宗広

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 村田 充裕

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

【請求項 1】

アンテナと、第1の端子と第2の端子とを有する第1の回路と、第3の端子と第4の端子とを有する第2の回路と、第3の回路と、第1の容量素子と、第2の容量素子と、トランジスタと、第5の端子と第6の端子とを有するダイオードと、を有し、前記アンテナは、前記第1の端子と電気的に接続されており、前記第1の容量素子は、前記第2の端子と電気的に接続されており、前記第1の容量素子は、前記第3の端子と電気的に接続されており、前記第1の容量素子は、前記トランジスタのソース又はドレインの一方と電気的に接続されており、前記第1の容量素子は、第5の端子と電気的に接続されており、前記第2の容量素子は、前記トランジスタのソース又はドレインの他方と電気的に接続されており、前記第2の容量素子は、第6の端子と電気的に接続されており、前記第1の回路は、前記第1の端子に入力される信号を整流して前記第2の端子から出

10

20

力することができる機能を有し、

前記第2の回路は、前記第3の端子に入力される第1の電圧を第2の電圧に変換して前記第4の端子から出力することができる機能を有し、

前記第3の回路は、前記トランジスタのオン、オフを制御することができる機能を有し、

前記ダイオードは、前記第6の端子から前記第5の端子へ電流を流すことができる機能を有することを特徴とする半導体装置。

【請求項2】

アンテナと、

前記アンテナに電気的に接続され、前記アンテナからの交流信号を直流信号に変換する整流回路と、

前記整流回路に電気的に接続され、前記整流回路を介して前記アンテナと電気的に接続された電荷蓄積回路と、

前記電荷蓄積回路に電気的に接続された定電圧回路と、を有し、

前記電荷蓄積回路は、複数のスイッチと、複数の容量素子と、電荷蓄積制御回路と、を有し、

前記複数の容量素子は、前記スイッチを介して、電気的に並列に接続されており、

前記電荷蓄積制御回路は、前記定電圧回路に供給する電圧に応じて前記スイッチのオン又はオフを制御するものであり、

前記スイッチは、トランジスタ、及びダイオードを有し、

前記複数の容量素子への電荷の蓄積は、トランジスタにより制御され、

前記複数の容量素子からの電荷の放出は、ダイオードにより制御されることを特徴とする半導体装置。

【請求項3】

アンテナと、

前記アンテナに電気的に接続され、前記アンテナからの交流信号を直流信号に変換する整流回路と、

前記整流回路に電気的に接続され、前記整流回路を介して前記アンテナと電気的に接続された電荷蓄積回路と、

前記電荷蓄積回路に電気的に接続された定電圧回路と、を有し、

前記電荷蓄積回路は、複数のスイッチと、複数の容量素子と、電荷蓄積制御回路と、を有し、

前記複数の容量素子の一方の電極は、それぞれ、前記スイッチを介して、電気的に接続されており、

前記電荷蓄積制御回路は、前記定電圧回路に供給する電圧に応じて前記スイッチのオン又はオフを制御するものであり、

前記スイッチは、トランジスタ、及びダイオードを有し、

前記複数の容量素子への電荷の蓄積は、トランジスタにより制御され、

前記複数の容量素子からの電荷の放出は、ダイオードにより制御されることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関する。特に無線通信によりデータの交信が可能な半導体装置、所謂RFID (Radio Frequency Identification) 用ICチップ (IDチップ、トランスポンダともいう) に関する。

【0002】

なお、ここでいう半導体装置とは、半導体特性を利用して機能しうる装置全般を指すものとする。

【背景技術】

10

20

30

40

50

## 【0003】

近年、ユビキタス情報社会と言われるように、いつ、どのような状態でも情報ネットワークにアクセスできる環境整備がなされている。このような環境の中、個々の対象物にID（個体識別番号）を与えることで、その対象物の履歴を明確にし、生産、管理に役立てるといった個体認識技術が実用化に向けて研究が行われている。その中でも、無線通信により、外部通信装置（以下、通信装置という。またリーダライタ、リーダ／ライタ、コントローラ、インテロゲータ、質問器ともいわれる）とデータの交信をおこなう、RFID（Radio Frequency Identification）技術を利用した半導体装置（以下、半導体装置という。IDチップ、ICチップ、トランスポンダともいわれる）が普及し始めている。

10

## 【0004】

半導体装置は、アンテナより、通信装置より送信された無線信号を受信する。無線信号は交流電圧の信号（以下、交流信号という）であるため、整流化が行われる整流回路により直流電圧の信号（以下、直流信号という）に変換される。直流信号は、定電圧回路（レギュレータ、または電源回路ともいう）に入力され、電源電圧Vddが生成される。定電圧回路で生成された電源電圧Vddは、半導体装置を構成する複数の回路に供給される。

## 【0005】

半導体装置において、定電圧回路への安定した電圧の供給は半導体装置の安定した動作に影響を与えるため、重要である。一例として、非特許文献1には、定電圧回路に安定した電圧を供給するため容量素子を設ける構成について開示されている。

20

【非特許文献1】Ray Barnett, Ganesh Balachandran, Steve Lazar, Brad Kramer, George Konnai, Suribhotla Rajasekhar, Vladimir Drobny, "A Passive UHF RFID Transponder for EPC Gen 2 with -14dBm Sensitivity in 0.13 μm CMOS" ISSCC, 32 8, PP582-583, pp623, 2007

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0006】

30

非特許文献1にも図示されている定電圧回路に安定した電圧を供給するための容量素子は、静電容量を大きくすることにより、後段の定電圧回路に供給する電圧を安定化することができる。しかしながら、容量素子の静電容量を大きくすると、所望の電圧を得るまでに、容量素子に電荷を蓄積させる分の時間だけ、時間がかかるという問題がある。また、容量素子の静電容量を小さくすると、所望の電圧を得ることができるものの、入力される電荷を蓄積することが難しくなり、且つ安定した電圧を後段の定電圧回路に供給することが難しくなるといった問題がある。

## 【0007】

上記の実情を鑑み、所望の電圧を短期間に生成し、且つ安定した電圧を定電圧回路に供給することのできる半導体装置を提供することを課題とする。

40

## 【課題を解決するための手段】

## 【0008】

本発明の半導体装置は、前述した課題を解決するために、容量素子を複数に分割し、分割した各容量素子を、スイッチを介して並列に接続する構成を有する電荷蓄積回路を設けることを特徴とする。そして本発明の半導体装置における電荷蓄積回路は、容量素子間に設けたスイッチを制御することにより、動的に定電圧回路に電圧を供給する電荷蓄積回路の静電容量を可変にすることができる。

## 【0009】

本発明の一は、アンテナと、アンテナに電気的に接続された整流回路と、整流回路に電気的に接続された電荷蓄積回路と、電荷蓄積回路に電気的に接続された定電圧回路と、を有

50

し、電荷蓄積回路は、複数のスイッチと、複数の容量素子を有し、複数の容量素子は、スイッチを介して、電気的に並列に接続されている半導体装置である。

#### 【0010】

また本発明の一は、アンテナと、アンテナに電気的に接続された整流回路と、整流回路に電気的に接続された電荷蓄積回路と、電荷蓄積回路に電気的に接続された定電圧回路と、を有し、電荷蓄積回路は、複数のスイッチと、複数の容量素子を有し、複数の容量素子の一方の電極は、それぞれ、スイッチを介して、電気的に接続されている半導体装置である。

#### 【0011】

また本発明の一は、アンテナと、アンテナに電気的に接続された整流回路と、整流回路に電気的に接続された電荷蓄積回路と、電荷蓄積回路に電気的に接続された定電圧回路と、を有し、電荷蓄積回路は、複数のスイッチと、複数の容量素子と、電荷蓄積制御回路と、を有し、複数の容量素子は、スイッチを介して、電気的に並列に接続されており、電荷蓄積制御回路は、定電圧回路に供給する電圧に応じてスイッチのオン又はオフを制御する半導体装置である。

#### 【0012】

また本発明の一は、アンテナと、アンテナに電気的に接続された整流回路と、整流回路に電気的に接続された電荷蓄積回路と、電荷蓄積回路に電気的に接続された定電圧回路と、を有し、電荷蓄積回路は、複数のスイッチと、複数の容量素子を有し、複数の容量素子の一方の電極は、それぞれ、スイッチを介して、電気的に接続されており、電荷蓄積制御回路は、定電圧回路に供給する電圧に応じてスイッチのオン又はオフを制御する半導体装置である。

#### 【発明の効果】

#### 【0013】

本発明の半導体装置は、分割して設けた容量素子間のスイッチを制御する電荷蓄積回路を有する。そのため本発明の半導体装置は、エネルギーを蓄積していない初期状態において、電荷蓄積回路の静電容量が小さくなるようにスイッチを制御することができるため、短期間に所望の電圧を生成することができる。そして本発明の半導体装置は、所望の電源電圧が得られた後、電荷蓄積回路の静電容量を大きくなるようにスイッチを制御することができるため、入力される電荷を蓄積することができ、且つ安定した電圧を定電圧回路に供給することができる。

#### 【発明を実施するための最良の形態】

#### 【0014】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更しうることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

#### 【0015】

##### (実施の形態1)

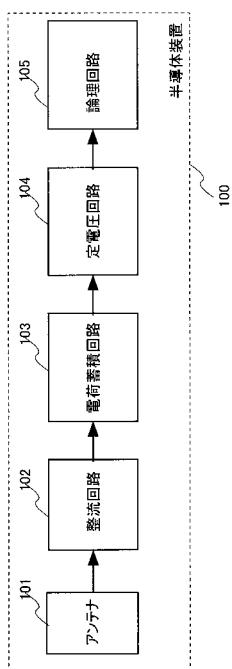

本発明の半導体装置の構成について、図1に示すブロック図を用いて説明する。なお本実施の形態においては、無線通信によりデータの交信が可能な半導体装置、所謂R F I D (Radio Frequency Identification)用ICチップ (IDチップ、ICチップ、トランスポンダともいう)として利用する場合について説明する。

#### 【0016】

図1の半導体装置100は、アンテナ101、整流回路102、電荷蓄積回路103、定電圧回路104、及び論理回路105によって構成される。

#### 【0017】

なお、ここでは図示しないが、図1においてアンテナ101は、外部通信装置(以下、通信装置という。またリーダライタ、リーダ/ライタ、コントローラ、インテロゲータ、

10

20

30

40

50

質問器ともいわれる)からの信号の受信、及び通信装置への信号の送信を行う。

【0018】

なお、図1において、アンテナ101の形状は、特に限定されない。つまり、半導体装置100におけるアンテナ101に適用する信号の伝送方式は、電磁結合方式、電磁誘導方式又はマイクロ波方式等を用いることができる。伝送方式は、実施者が適宜使用用途を考慮して選択すればよく、伝送方式に伴って最適な長さや形状のアンテナを設ければよい。

【0019】

例えば、伝送方式として、電磁結合方式又は電磁誘導方式(例えば、13.56MHz帯)を適用する場合には、電界密度の変化による電磁誘導を利用するため、アンテナとして機能する導電膜を輪状(例えば、ループアンテナ)、らせん状(例えば、スパイラルアンテナ)に形成する。

【0020】

また、伝送方式としてマイクロ波方式(例えば、UHF帯(860~960MHz帯)、2.45GHz帯等)を適用する場合には、信号の伝送に用いる電波の波長を考慮してアンテナとして機能する導電膜の長さや形状を適宜設定すればよく、アンテナとして機能する導電膜を、線状(例えば、ダイポールアンテナ)、平坦な形状(例えば、パッチアンテナ)等に形成することができる。また、アンテナとして機能する導電膜の形状は線状に限られず、電磁波の波長を考慮して曲線状や蛇行形状またはこれらを組み合わせた形状で設けてよい。

【0021】

なお、半導体装置と通信装置との通信方式は、単方向通信または双方向通信であって、空間分割多重化方式、偏波面分割多重化方式、周波数分割多重化方式、時分割多重化方式、符号分割多重化方式、直交周波数分割多重化方式のいずれも用いることができる。

【0022】

なお、半導体装置と通信装置との搬送波の周波数は、サブミリ波である300GHz以上3THz未満、ミリ波である30GHz以上300GHz未満、マイクロ波である3GHz以上30GHz未満、極超短波である300MHz以上3GHz未満、超短波である30MHz以上300MHz未満、短波である3MHz以上30MHz未満、中波である300kHz以上3MHz未満、長波である30kHz以上300kHz未満、及び超長波である3kHz以上30kHz未満のいずれの周波数も用いることができる。また、半導体装置と通信装置との搬送波の変調方式は、アナログ変調であってもデジタル変調であってもよく、振幅変調、位相変調、周波数変調、及びスペクトラム拡散のいずれであってもよい。望ましくは、振幅変調、または、周波数変調にするとよい。

【0023】

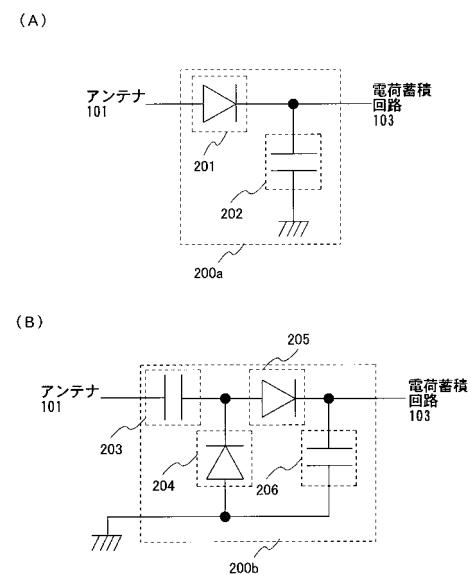

次に、図1に示した整流回路102の構成例について図2(A)、図2(B)に示す。整流回路102は、アンテナ101が受信する電波により生成される交流信号を直流信号に変換する回路であればよい。例えば、図2(A)に示すように整流回路200aは、ダイオード201、容量素子202によって整流回路102を構成すればよい。

【0024】

なお、図1に示した整流回路102は、半波2倍圧整流回路と呼ばれる回路構成を採用してもよい。例えば、図2(B)に示すように整流回路200bは、容量素子203、ダイオード204、ダイオード205、容量素子206によって、半波2倍圧整流回路を構成すればよい。これに限らず半波4倍圧整流回路や半波6倍圧整流回路や全波整流回路などを用いてもよい。

【0025】

なお、図2(A)及び図2(B)に示す容量素子は2つの端子を用いて電気的な接続が行われている。その場合、容量素子の一方の電極を第1の電極と呼び、他方の電極を第2の電極と呼ぶ。また、図2(A)及び図2(B)に示すダイオードは2つの端子を用いて電気的な接続が行われている。その場合、ダイオードの陽極を第1の電極と呼び、ダイオード

10

20

30

40

50

ドの陰極を第2の電極と呼ぶ。

【0026】

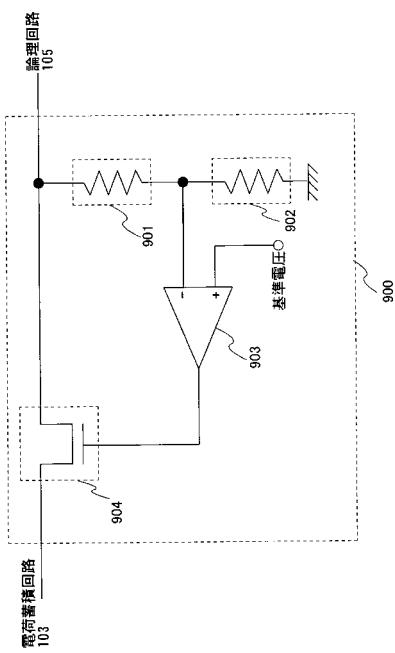

次に図1に示した定電圧回路104の構成例について図19に示す。図19に示す定電圧回路104は第1の抵抗素子901、第2の抵抗素子902、コンパレータ903、トランジスタ904を有する構成である。コンパレータ903は、基準電圧が非反転入力端子に入力され、論理回路105に接続される側のノードの電圧を第1の抵抗素子901と第2の抵抗素子902とで抵抗分割した電圧が反転入力端子に入力され、これらの電圧値を比較する機能を有する。コンパレータ903の出力端子は、トランジスタ904のゲート端子に接続される。そしてコンパレータ903は、トランジスタ904を介して一定の電圧を出力する機能を奏するものである。

10

【0027】

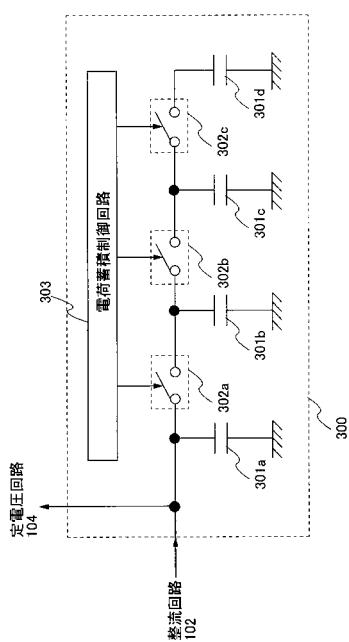

次に、本発明の特徴点である図1に示す半導体装置が具備する電荷蓄積回路103の構成について詳述する。電荷蓄積回路103は複数の容量素子、及び複数のスイッチを有し、並列に設けられた容量素子が、それぞれスイッチを介して電気的に接続されている。電荷蓄積回路103は、整流回路102より出力される直流信号の電荷をスイッチのオン又はオフを切り替えることにより複数の容量素子に順次蓄積していくことで所望の電圧に短期間に昇圧し、定電圧回路104に安定した電圧を出力する電圧をする回路である。

【0028】

図3に電荷蓄積回路103の具体的な回路構成について示し、説明する。図3に示す電荷蓄積回路300は、第1の容量素子301a、第2の容量素子301b、第3の容量素子301c、第4の容量素子301d、スイッチ302a、スイッチ302b、スイッチ302c、及び電荷蓄積制御回路303を有する。図3において、整流回路102は、第1の容量素子301aの第1の電極及びスイッチ302aの一方の端子に電気的に接続される。また、第1の容量素子301aの第1の電極、第2の容量素子301bの第1の電極、第3の容量素子301cの第1の電極、及び第4の容量素子301dの第1の電極は、スイッチ302a、スイッチ302b、及びスイッチ302cを介して、並列に接続されている。また第1の容量素子301aの第2の電極、第2の容量素子301bの第2の電極、第3の容量素子301cの第2の電極、及び第4の容量素子301dの第2の電極は、それぞれグラウンド線に接続されている。また、スイッチ302a、スイッチ302b、及びスイッチ302cは、電荷蓄積制御回路303によって、オンまたはオフが制御される。

20

【0029】

なお、図3において、電荷蓄積回路300を構成する容量素子の数が4つ、スイッチの数が3つである場合の例について示した。本発明は、容量素子の数及びスイッチの数が限定されないものであることを付記する。本実施の形態で説明する構成においては、並列に接続された容量素子の一方の電極間に、スイッチを設ける構成であればよい。なお図3において、スイッチ間のノードに接続される容量素子は1つである例について示したが、複数設ける構成でもよい。

30

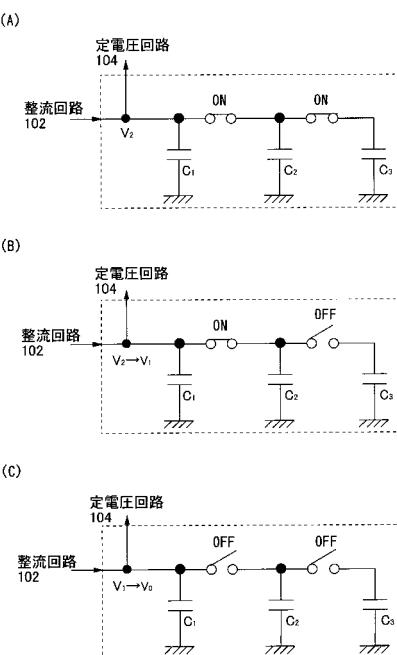

【0030】

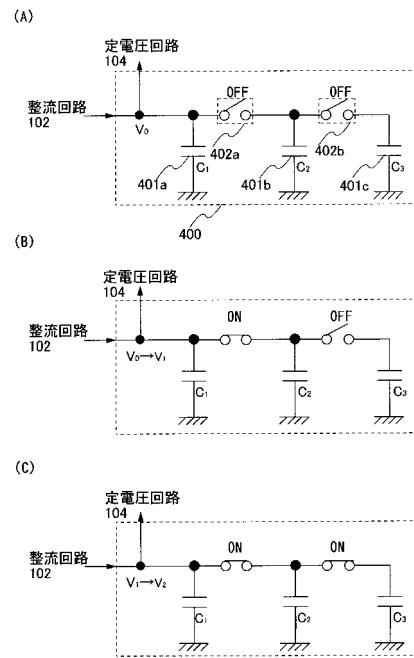

次に電荷蓄積回路103の具体的な動作について図4(A)乃至(C)及び図5(A)乃至(C)を用いて説明する。なお、図4(A)乃至(C)及び図5(A)乃至(C)に示す電荷蓄積回路400は、第1の容量素子401a、第2の容量素子401b、第3の容量素子401c、スイッチ402a、及びスイッチ402bを有する。なお、図4(A)乃至(C)及び図5(A)乃至(C)では、各スイッチのオン又はオフの動作について説明するものであるため、電荷蓄積制御回路については図示しない。また、図4(A)乃至(C)及び図5(A)乃至(C)において、整流回路102から入力される直流信号の電荷をQ、定電圧回路104に出力される電圧がV0, V1, V2と段階的に変化する例について説明する。なお、前述の定電圧回路104に出力される電圧はV0 < V1 < V2の関係を有するものとする。そして直流信号は、第1の容量素子401aの第1の電極及びスイッチ402aの一方の端子に入力される。また、第1の容量素子401aの第1の電極

40

50

電極、第2の容量素子401bの第1の電極、及び第3の容量素子401cの第1の電極は、スイッチ402a及びスイッチ402bを介して、並列に接続されている。また第1の容量素子401aの第2の電極、第2の容量素子401bの第2の電極、及び第3の容量素子401cの第2の電極は、それぞれグラウンド線に接続されている。また、スイッチ402a、及びスイッチ402bは、電荷蓄積制御回路(図示せず)によって、オンまたはオフが制御される。なお、図4(A)に符号を付し、図4(B)乃至(C)及び図5(A)乃至(C)については、省略している。また図4(A)乃至(C)及び図5(A)乃至(C)で説明する第1の容量素子401aの静電容量をC1、第2の容量素子401bの静電容量をC2、第3の容量素子401cの静電容量をC3とする。なお、静電容量C1、静電容量C2、及び静電容量C3は、同じ静電容量でも良いし、異なっていてよい。

10

### 【0031】

なお本明細書で説明する定電圧回路104に出力される電圧とは、グラウンド電位を基準電位とした場合の、電位差に相当する。そのため、電圧V0乃至V2のことを電位V0乃至V2と呼ぶこともある。

### 【0032】

図4(A)の状態について説明する。電荷蓄積回路400には、整流回路102から出力される直流信号の電荷Qが蓄積される。電荷蓄積回路400は、初期状態ではスイッチはオフ、すなわちスイッチ402a及びスイッチ402bはオフになっており、電荷Qは静電容量C1である第1の容量素子401aに蓄積されていく。このとき、静電容量C1である第1の容量素子401aに電荷Qが蓄積されることにより、静電容量C、電荷Q、及び電圧Vの関係式:  $Q = CV$  より、  $Q / C_1 = V_0$  ( $V_0$  は定電圧回路104に出力する所望の電圧)を得ることができる。なお、第1の容量素子401aの静電容量C1は、蓄積される電荷Qによって短期間に電圧V1が得られるよう予め小さく設計することが望ましい。

20

### 【0033】

なお、本明細書でいう電荷Qとは、整流回路102で得られる直流信号の電圧によって、電荷蓄積回路400に供給される電荷のことをいう。そして、電荷蓄積回路400では、電荷を蓄積するための静電容量の値が小さいほど、短期間に所望の電圧を得ることができる。なお、説明のため本実施の形態において、電荷蓄積回路400に供給される電荷Qは、図4(B)乃至(C)の状態となる期間ごとに供給される電荷の総数であるものとする。

30

### 【0034】

次に図4(B)の状態について説明する。電荷蓄積回路400には、整流回路102から出力される直流信号の電荷Qが図4(A)の状態に引き続き供給されている。このとき、定電圧回路104に出力するための所望の電圧V0が既に得られているものの、電荷を蓄積するための第1の容量素子401aでは、整流回路102から出力される直流信号の電圧に依存して、蓄積できる電荷が飽和してしまう。この状態のとき、スイッチ402aをオンにすることにより、電荷を蓄積することのできる容量素子を第1の容量素子401a及び第2の容量素子401bと増やすことで、アンテナ101で受信した電力を、電荷として容量素子に蓄積することができる。図4(B)の状態のとき、電荷を蓄積するための静電容量は第1の容量素子401a及び第2の容量素子401bが有する静電容量を併せた静電容量( $C_1 + C_2$ )となる。電荷Qは図4(A)の状態で蓄積された分の電荷Qと、順次電荷蓄積回路400に入力される電荷Qと併せて2Qとなる。そして、静電容量、電荷、及び電圧の関係式により、  $2Q / (C_1 + C_2) = V_1$  を得ることができる。なお静電容量C2は、静電容量C1に比べて小さいものであることが望ましい、静電容量C2を静電容量C1に比べて小さく設けることにより、スイッチ402aがオンになる際の電圧V0から電圧V1に変化する際の電圧の変動幅を小さくすることができ、安定した電圧を定電圧回路104に供給することができる。

40

### 【0035】

50

次に図4(C)の状態について説明する。電荷蓄積回路400には、整流回路102から出力される直流信号の電荷Qが、図4(A)、図4(B)の状態に引き続き供給されている。このとき、定電圧回路104に出力するためのV0が既に得られているものの、電荷を蓄積するための第1の容量素子401a及び第2の容量素子401bでは、整流回路102から出力される直流信号の電圧に依存して、蓄積できる電荷が飽和してしまう。この状態のとき、スイッチ402aと併せてスイッチ402bをオンにすることにより、電荷を蓄積することのできる容量素子を第1の容量素子401a、第2の容量素子401b、第3の容量素子401cと増やすことにより、アンテナ101で受信した電力を、電荷として容量素子に蓄積することができる。図4(C)の状態のとき、電荷を蓄積するための静電容量は第1の容量素子401a、第2の容量素子401b、及び第3の容量素子401cが有する静電容量を併せた静電容量( $C_1 + C_2 + C_3$ )となる。電荷Qは図4(B)の状態で蓄積された分の電荷2Qと、順次電荷蓄積回路400に入力される電荷Qと併せて3Qとなる。そして、静電容量、電荷、及び電圧の関係式により、 $3Q / (C_1 + C_2 + C_3) = V_2$ を得ることができる。なお静電容量 $C_3$ は、静電容量( $C_1 + C_2$ )に比べて小さいものであることが望ましい、静電容量 $C_3$ を静電容量( $C_1 + C_2$ )に比べて小さく設けることにより、スイッチ402bがオンになる際の電圧 $V_1$ から電圧 $V_2$ に変化する際の電圧の変動幅を小さくすることができ、安定した電圧を定電圧回路104に供給することができる。10

#### 【0036】

以上図4(A)乃至図4(C)では、電荷蓄積回路400の電荷の蓄積方法について示した。図4(A)乃至図4(C)に示す構成は一例であり、容量素子及びスイッチの数を増やして電荷を蓄積することができる静電容量を増やす構成としてもよい。また、スイッチのオンまたはオフについては、図4(A)乃至図4(C)で示した順に限定されるものではなく、例えばスイッチ402aとスイッチ402bを同時にオンして電荷を蓄積するための静電容量を可変する構成としてもよい。20

#### 【0037】

次に、電荷蓄積回路400に蓄積された電荷の放出に関する動作について図5(A)乃至図5(C)を用いて説明する。

#### 【0038】

図5(A)の状態について説明する。電荷蓄積回路400は、整流回路102から出力される直流信号の電圧による電荷の供給が行われない期間、定電圧回路104への安定した電圧の出力を行うため、複数の容量素子に保持された電荷を放出して、安定した電圧を定電圧回路104に出力する。複数の容量素子に蓄積された電荷の放出は、図5(A)に示すように、スイッチ402a及びスイッチ402bが共にオンの状態から、図5(B)に示すように、スイッチ402aをオン及びスイッチ402bをオフの状態を経て、図5(C)に示すように、スイッチ402a及びスイッチ402bが共にオフの状態とする。そして、図5(A)乃至図5(C)に説明したように電荷蓄積回路400は、複数の容量素子である第1の容量素子、第2の容量素子、及び第3の容量素子からの電荷の放出を行うことができる。30

#### 【0039】

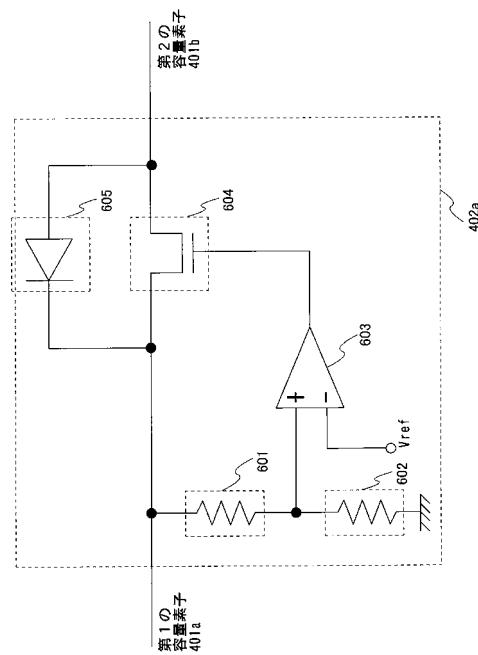

ここで、図3で示したスイッチ302a乃至スイッチ302c、及び図4(B)乃至(C)及び図5(A)乃至(C)で説明したスイッチ402a及びスイッチ402bの具体的な構成について図6を用いて説明する。電荷の蓄積時及び放出時の電荷蓄積回路の動作を加えて説明するため、図6では、図4(B)乃至(C)及び図5(A)乃至(C)で説明したスイッチ402aの構成を具体的に説明するものとする。40

#### 【0040】

図6に示すスイッチ402aは第1の抵抗素子601、第2の抵抗素子602、コンパレータ603、トランジスタ604、ダイオード605を有する構成である。コンパレータ603は、図3で説明した電荷蓄積制御回路303からの参照電圧(図6中の $V_{ref}$ )が反転入力端子に入力され、第1の容量素子401aの第1の電極の電圧を第1の抵抗素50

子 6 0 1 と第 2 の抵抗素子 6 0 2 とで抵抗分割した電圧が非反転入力端子に入力され、これらの電圧値を比較する機能を有する。コンパレータ 6 0 3 の出力端子は、トランジスタ 6 0 4 のゲート端子に接続される。そしてコンパレータ 6 0 3 は、第 1 の容量素子 4 0 1 a の第 1 の電極の電圧が V 0 より大きい場合にトランジスタ 6 0 4 をオンにし、第 1 の容量素子 4 0 1 a の第 1 の電極と第 2 の容量素子 4 0 1 b の第 1 の電極を電気的に接続させるスイッチとしての機能を奏するものである。そのため図 3 で説明した電荷蓄積制御回路 3 0 3 により、参照電圧を制御することで、複数の容量素子に順次電荷を蓄積するためのスイッチのオン又はオフの制御を行うことができる。ダイオード 6 0 5 は第 1 の電極が第 2 の容量素子 4 0 1 b の第 1 の電極に接続され、ダイオード 6 0 5 の第 2 の電極が第 1 の容量素子 4 0 1 a の第 1 の電極に接続されるように設けられる。

10

#### 【 0 0 4 1 】

なお、電荷蓄積時において、第 1 の容量素子 4 0 1 a と第 2 の容量素子 4 0 1 b への電荷の蓄積は、第 1 の容量素子 4 0 1 a の方が一定の電圧に達するまでは第 2 の容量素子 4 0 1 b の第 1 の電極に電荷の蓄積を行われないようにすることで所望の電圧を短期間に得ることができる。また電荷放出時において、第 1 の容量素子 4 0 1 a と第 2 の容量素子 4 0 1 b からの電荷の放出は、第 1 の容量素子 4 0 1 a の電圧が降下した場合に、第 2 の容量素子 4 0 1 b に蓄積されている電荷を第 1 の容量素子 4 0 1 a 側に供給して第 1 の容量素子 4 0 1 a の第 1 の電極に電荷を補給するように行われるようになると、電荷の放出を効率よく行い、且つ所望の電圧を効率よく得ることができる。本実施の形態で説明する図 6 の構成において、ダイオード 6 0 5 は、電荷蓄積時には、第 1 の容量素子 4 0 1 a から第 2 の容量素子 4 0 1 b へ電荷の漏電を防ぐものであり、電荷放出時には、第 1 の容量素子 4 0 1 a が電荷の放出により電圧降下した際に、第 2 の容量素子 4 0 1 b 側より電荷の補給を行うようにするものである。

20

#### 【 0 0 4 2 】

なお、本実施の形態においては、スイッチ 4 0 2 a の構成について詳細に説明したが、他のスイッチにおいても参照電圧を異ならせることで同様の機能を奏するものであり、ここでは説明を省略する。

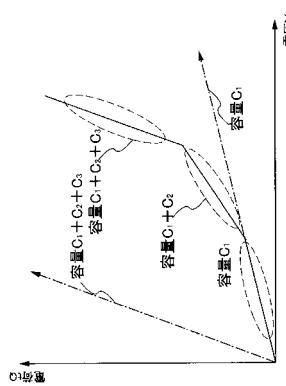

#### 【 0 0 4 3 】

次に、電荷蓄積回路における本発明の特徴である、分割して設けた容量素子間をスイッチで切り替えて静電容量を可変にし、電荷の蓄積を行う利点について図 7 を用いて説明する。図 7 では、具体的な説明をするため、上記図 4 ( A ) 乃至 ( C ) 及び図 5 ( A ) 乃至 ( C ) で説明した電荷蓄積回路が具備する第 1 の容量素子乃至第 3 の容量素子の静電容量 C 1 乃至 C 3 を用いた電荷蓄積時の電圧の変化について述べる。

30

#### 【 0 0 4 4 】

図 7 に示す図は、電荷蓄積回路を構成する容量素子の静電容量 ( 図中では単に容量と呼ぶ ) が ( C 1 + C 2 + C 3 ) である場合、電荷蓄積回路を構成する容量素子の静電容量が ( C 1 ) 、及び電荷蓄積回路を構成する容量素子の静電容量が ( C 1 ) から ( C 1 + C 2 ) 、 ( C 1 + C 2 ) から ( C 1 + C 2 + C 3 ) と可変させた場合の電荷の蓄積量と定電圧回路に出力される電圧の相関について示したものである。なお、容量素子の静電容量の大きさは、 ( C 1 ) < ( C 1 + C 2 ) < ( C 1 + C 2 + C 3 ) となる。

40

#### 【 0 0 4 5 】

まず図 7 に示すグラフにおいて、静電容量が ( C 1 ) である場合、及び静電容量が ( C 1 + C 2 + C 3 ) である場合の電荷の蓄積量と定電圧回路に出力される電圧の相関について説明する。なお、電荷蓄積回路に蓄積される電荷の量は、前段の整流回路から出力される直流信号の電圧に依存するものであるため、図 7 の説明では、整流回路から出力される直流信号の電圧が一定である場合について説明を行う。

#### 【 0 0 4 6 】

図 7 に示すグラフにおいて、静電容量が ( C 1 ) である場合、電荷の蓄積に対する電圧の変化量は、静電容量 C 、電荷 Q 、及び電圧 V の関係式 :  $V = Q / C$  により電荷の蓄積に対する電圧の変化量は大きいものの、蓄積することのできる電荷量は少ない。一方、静電

50

容量が(  $C_1 + C_2 + C_3$  )である場合、静電容量C、電荷Q、及び電圧Vの関係式:  $V = Q / C$  により、電荷の蓄積に対する電圧の変化量は小さいものの、蓄積することのできる電荷量が多い。

【0047】

次に、静電容量が(  $C_1$  )から(  $C_1 + C_2$  )、(  $C_1 + C_2$  )から(  $C_1 + C_2 + C_3$  )と可変させた場合の電荷の蓄積量と定電圧回路に出力される電圧の相関について説明する。静電容量が電荷の蓄積開始時に(  $C_1$  )である場合、静電容量C、電荷Q、及び電圧Vの関係式:  $V = Q / C$  により、電荷の蓄積に対する電圧の変化量は大きいものの、蓄積することのできる電荷量は少ない。しかし本実施の形態の構成では、電荷の蓄積により、所望の電圧まで短期間に達した後に静電容量が(  $C_1$  )から(  $C_1 + C_2$  )、(  $C_1 + C_2$  )から(  $C_1 + C_2 + C_3$  )と可変することができる。そのため、電荷の蓄積により、所望の電圧に達した後は、蓄積することのできる電荷を増やすことができる。そのため、本実施の形態で説明した電荷蓄積回路を具備する半導体装置では、エネルギーを蓄積していない初期状態において、電荷蓄積回路の静電容量が小さくなるようにスイッチを制御することで、短期間に所望の電圧を生成することができる。そして、所望の電源電圧が得られた後、電荷蓄積回路の静電容量を大きくなるようにスイッチを制御することで、入力される電荷を効率よく蓄積することができ、且つ安定した電圧を定電圧回路に供給することができる。

10

【0048】

なお、本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。

20

【0049】

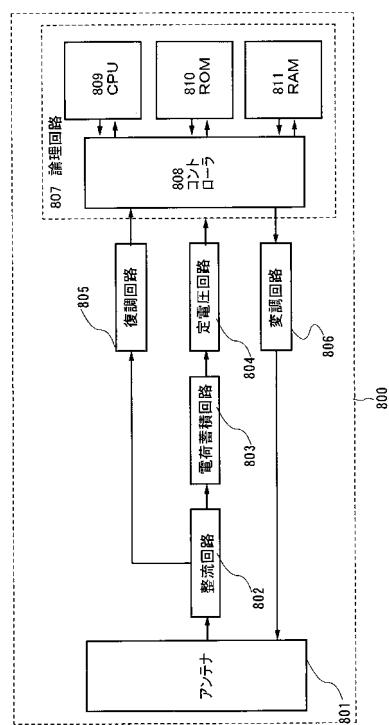

(実施の形態2)

本実施の形態では、上記実施の形態で説明した電荷蓄積回路を具備する半導体装置( R F I D タグ、 I D チップ、 I C タグ、 I D タグ、 R F タグ、 無線タグ、 電子タグ、 トランスポンダともいわれる )の構成について説明する。

【0050】

図8における半導体装置800は、一例として、アンテナ801、整流回路802、電荷蓄積回路803、定電圧回路804、復調回路805、変調回路806、論理回路807によって構成されている。また、論理回路807はコントローラ808、CPU809( Central Processing Unit )、ROM810( Read Only Memory )、RAM811( Random Access Memory )によって構成されている。論理回路807は、CPU809などの論理回路、ワーク領域としてのRAM811として揮発性メモリ( 代表的にはSRAM )、CPU809のプログラムを格納する書き込み可能なROM810として不揮発性メモリ( 代表的にはEEPROM )によって構成され、コントローラ808により各ブロック間のデータの読み出しままたは書き込みを制御するものであればよい。

30

【0051】

なお、半導体装置800における電荷蓄積回路803は、上記実施の形態で説明した構成を取り得る。すなわち、エネルギーを蓄積していない初期状態において、電荷蓄積回路の静電容量が小さくなるようにスイッチを制御することで、短期間に所望の電圧を生成することができる。そして、所望の電源電圧が得られた後、電荷蓄積回路の静電容量を大きくなるようにスイッチを制御することで、入力される電荷を効率よく蓄積することができ、且つ安定した電圧を定電圧回路に供給することができるものである。

40

【0052】

図8において、アンテナ801で外部の通信装置より受信した信号が整流回路802に入力される。整流回路802からの出力信号は復調回路805、及び電荷蓄積回路803に入力される。復調回路805からの信号は論理回路807に入力され、半導体装置の固有情報に関する情報が変調回路806に出力される。そして変調回路806からの出力信号はアンテナ801に出力され、半導体装置外部の通信装置に信号が出力される。また電荷

50

蓄積回路 803 からは定電圧回路 804 で一定の電圧を出力するための電圧が定電圧回路 804 に供給される。そして定電圧回路 804 からは、半導体装置の各回路を動作するための電源電圧が供給される。

【0053】

なお、通信装置と半導体装置の間の信号の伝送方式は、搬送波の波長によって電磁結合方式、電磁誘導方式、マイクロ波方式など様々な種類に分類することができる。なお、半導体装置と通信装置との無線信号の送受信を長距離間で行う場合には、マイクロ波方式を選択することが望ましい。

【0054】

なお、本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。

10

【0055】

(実施の形態 3)

本実施の形態では、上記実施の形態で述べた半導体装置を構成するトランジスタの作製例について説明する。本実施の形態では特に、絶縁基板上に形成された半導体膜により作成したトランジスタを具備する半導体装置とする形態について説明する。

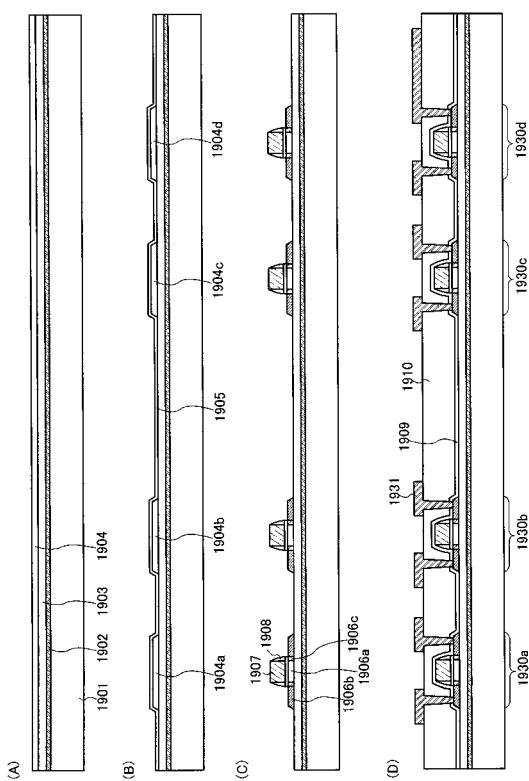

【0056】

基板 1901 の一表面に剥離層 1902 を形成し、続けて下地となる絶縁膜 1903 および非晶質半導体膜 1904 ( 例えは非晶質珪素を含む膜 ) を形成する ( 図 9 ( A ) ) 。剥離層 1902 、絶縁膜 1903 および非晶質半導体膜 1904 は、連続して形成することができる。連続して形成することにより、大気に曝されないため不純物の混入を防ぐことができる。

20

【0057】

基板 1901 は、ガラス基板、石英基板、金属基板やステンレス基板、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いるとよい。このような基板であれば、その面積や形状に大きな制限はないため、例えは、1 辺が 1 メートル以上あって、矩形状のものを用いれば、生産性を格段に向上させることができる。このような利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。従って、シリコン基板と比較して集積回路部やアンテナを大きく形成した場合であっても、低コスト化を実現することができる。

30

【0058】

なお、本工程では、剥離層 1902 を基板 1901 の全面に設けているが、必要に応じて、基板 1901 の全面に剥離層を設けた後に、フォトリソグラフィ法及びエッチングにより剥離層 1902 を選択的に設けてもよい。また、基板 1901 に接するように剥離層 1902 を形成しているが、必要に応じて、基板 1901 に接するように酸化珪素 ( SiO<sub>x</sub> ) 膜、酸化窒化珪素 ( SiO<sub>x</sub>N<sub>y</sub> ) ( x > y ) 膜、窒化珪素 ( SiN<sub>x</sub> ) 膜、窒化酸化珪素 ( SiN<sub>x</sub>O<sub>y</sub> ) ( x > y ) 膜等の絶縁膜を形成し、当該絶縁膜に接するように剥離層 1902 を形成してもよい。

【0059】

剥離層 1902 は、金属膜や金属膜と金属酸化膜の積層構造等を用いることができる。金属膜としては、タンゲステン ( W ) 、モリブデン ( Mo ) 、チタン ( Ti ) 、タンタル ( Ta ) 、ニオブ ( Nb ) 、ニッケル ( Ni ) 、コバルト ( Co ) 、ジルコニウム ( Zr ) 、亜鉛 ( Zn ) 、ルテニウム ( Ru ) 、ロジウム ( Rh ) 、パラジウム ( Pd ) 、オスミウム ( Os ) 、イリジウム ( Ir ) から選択された元素または前記元素を主成分とする合金材料若しくは化合物材料からなる膜を単層又は積層して形成する。また、これらの材料は、スパッタリング法やプラズマ CVD 法等の各種 CVD 法等を用いて形成することができる。金属膜と金属酸化膜の積層構造としては、上述した金属膜を形成した後に、酸素雰囲気下または N<sub>2</sub>O 雰囲気下におけるプラズマ処理、酸素雰囲気下または N<sub>2</sub>O 雰囲気下における加熱処理を行うことによって、金属膜表面に当該金属膜の酸化物または酸化窒化物を設けることができる。また、金属膜を形成した後に、オゾン水等の酸化力の強い溶

40

50

液で表面を処理することにより、金属膜表面に当該金属膜の酸化物又は酸化窒化物を設けることができる。

【0060】

絶縁膜1903は、スパッタリング法やプラズマCVD法等により、珪素の酸化物または珪素の窒化物を含む膜を、単層又は積層で形成する。下地となる絶縁膜が2層構造の場合、例えば、1層目として窒化酸化珪素膜を形成し、2層目として酸化窒化珪素膜を形成するとよい。下地となる絶縁膜が3層構造の場合、1層目の絶縁膜として酸化珪素膜を形成し、2層目の絶縁膜として窒化酸化珪素膜を形成し、3層目の絶縁膜として酸化窒化珪素膜を形成するとよい。または、1層目の絶縁膜として酸化窒化珪素膜を形成し、2層目の絶縁膜として窒化酸化珪素膜を形成し、3層目の絶縁膜として酸化窒化珪素膜を形成するとよい。下地となる絶縁膜は、基板1901からの不純物の侵入を防止するブロッキング膜として機能する。

10

【0061】

半導体膜1904は、スパッタリング法、LPCVD法、プラズマCVD法等により、25~200nm(好ましくは30~150nm)の厚さで形成する。半導体膜1904としては、例えば、非晶質珪素膜を形成すればよい。

【0062】

次に、非晶質の半導体膜1904にレーザー光を照射して結晶化を行う。なお、レーザー光の照射と、RTA又はファーネスアーナー炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とを組み合わせた方法等により非晶質の半導体膜1904の結晶化を行ってもよい。その後、得られた結晶質半導体膜を所望の形状にエッチングして、半導体膜1904a~1904dを形成し、当該半導体膜1904a~1904dを覆うようにゲート絶縁膜1905を形成する(図9(B))。

20

【0063】

半導体膜1904a~1904dの作製工程の一例を以下に簡単に説明すると、まず、プラズマCVD法を用いて、膜厚50~60nmの非晶質半導体膜(例えば、非晶質珪素膜)を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体膜上に保持させた後、非晶質半導体膜に脱水素化の処理(500、1時間)と、熱結晶化の処理(550、4時間)を行って結晶質半導体膜を形成する。その後、レーザー発振器からレーザー光を照射し、フォトリソグラフィ法及びエッチングを用いることよって半導体膜1904a~1904dを形成する。なお、結晶化を助長する金属元素を用いる熱結晶化を行わずに、レーザー光の照射だけで非晶質半導体膜の結晶化を行ってもよい。

30

【0064】

レーザー発振器としては、連続発振型のレーザー(CWレーザー)やパルス発振型のレーザー(パルスレーザー)を用いることができる。ここで用いることができるレーザービームは、Arレーザー、Krレーザー、エキシマレーザーなどの気体レーザー、単結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザー、ガラスレーザー、ルビーレーザー、アレキサンドライトレーザー、Ti:サファイアレーザー、銅蒸気レーザーまたは金蒸気レーザーのうち一種または複数種から発振されるものを用いることができる。このようなレーザービームの基本波、及びこれらの基本波の第2高調波から第4高調波のレーザービームを照射することで、大粒径の結晶を得ることができる。例えば、Nd:YVO<sub>4</sub>レーザー(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いることができる。このときレーザーのパワー密度は0.01~100MW/cm<sup>2</sup>程度(好ましくは0.1~10MW/cm<sup>2</sup>)が必要である。そして、走査速度を10~2000cm/sec程度として照射する。なお、単結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶(セラミック)のY

40

50

AG、 $Y_2O_3$ 、 $YVO_4$ 、 $YAlO_3$ 、 $GdVO_4$ に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザー、Arイオンレーザー、またはTi:サファイアレーザーは、連続発振をさせることができ、Qスイッチ動作やモード同期などを行うことによって10MHz以上の発振周波数でパルス発振をさせることも可能である。10MHz以上の発振周波数でレーザービームを発振させると、半導体膜がレーザーによって溶融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波数が低いパルスレーザーを用いる場合と異なり、半導体膜中において固液界面を連続的に移動させることができたため、走査方向に向かって連続的に成長した結晶粒を得ることができる。

## 【0065】

10

次に、半導体膜1904a～半導体膜1904dを覆うゲート絶縁膜1905を形成する。ゲート絶縁膜1905は、CVD法やスパッタリング法等により、珪素の酸化物又は珪素の窒化物を含む膜を、単層又は積層して形成する。具体的には、酸化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜を、単層又は積層して形成する。

## 【0066】

また、ゲート絶縁膜1905は、半導体膜1904a～半導体膜1904dに対し高密度プラズマ処理を行い、表面を酸化又は窒化することで形成しても良い。例えば、He、Ar、Kr、Xeなどの希ガスと、酸素、酸化窒素( $NO_2$ )、アンモニア、窒素、水素などの混合ガスを導入したプラズマ処理で形成する。この場合のプラズマの励起は、マイクロ波の導入により行うと、低電子温度で高密度のプラズマを生成することができる。この高密度プラズマで生成された酸素ラジカル( $OH$ ラジカルを含む場合もある)や窒素ラジカル( $NH$ ラジカルを含む場合もある)によって、半導体膜の表面を酸化又は窒化することができる。

20

## 【0067】

このような高密度プラズマを用いた処理により、1～20nm、代表的には5～10nmの絶縁膜が半導体膜に形成される。この場合の反応は、固相反応であるため、当該絶縁膜と半導体膜との界面準位密度はきわめて低くすることができる。このような、高密度プラズマ処理は、半導体膜(結晶性シリコン、或いは多結晶シリコン)を直接酸化(若しくは窒化)するため、形成される絶縁膜の厚さは理想的には、ばらつきをきわめて小さくすることができる。加えて、結晶性シリコンの結晶粒界でも酸化が強くされたことがないため、非常に好ましい状態となる。すなわち、ここで示す高密度プラズマ処理で半導体膜の表面を固相反応することにより、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶縁膜を形成することができる。

30

## 【0068】

ゲート絶縁膜1905は、高密度プラズマ処理によって形成される絶縁膜のみを用いても良いし、それに加えてプラズマや熱反応を利用したCVD法で酸化シリコン、酸窒化シリコン、窒化シリコンなどの絶縁膜を堆積し、積層させても良い。いずれにしても、高密度プラズマで形成した絶縁膜をゲート絶縁膜の一部又は全部に含んで形成されるトランジスタは、特性のばらつきを小さくすることができる。

## 【0069】

40

また、半導体膜に対し、連続発振レーザー光若しくは10MHz以上の周波数で発振するレーザー光を照射しながら一方向に走査して結晶化させて得られた半導体膜1904a～1904dは、そのレーザー光の走査方向に結晶が成長する特性がある。その走査方向をチャネル長方向(チャネル形成領域が形成されたときにキャリアが流れる方向)に合わせてトランジスタを配置し、上記ゲート絶縁層を組み合わせることで、特性ばらつきが小さく、しかも電界効果移動度が高い薄膜トランジスタ(TFT)を得ることができる。

## 【0070】

次に、ゲート絶縁膜1905上に、第1の導電膜と第2の導電膜とを積層して形成する。ここでは、第1の導電膜は、プラズマCVD法やスパッタ法等により、20～100nmの厚さで形成する。第2の導電膜は、100～400nmの厚さで形成する。第1の導

50

電膜と第2の導電膜は、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素又はこれらの元素を主成分とする合金材料若しくは化合物材料で形成する。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成する。第1の導電膜と第2の導電膜の組み合わせの例を挙げると、窒化タンタル膜とタングステン膜、窒化タングステン膜とタングステン膜、窒化モリブデン膜とモリブデン膜等が挙げられる。タングステンや窒化タンタルは、耐熱性が高いため、第1の導電膜と第2の導電膜を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2層構造ではなく、3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

10

## 【0071】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極とゲート配線を形成するためのエッチング処理を行って、半導体膜1904a～1904dの上方にゲート電極1907を形成する。

## 【0072】

次に、フォトリソグラフィ法により、レジストからなるマスクを形成して、半導体膜1904a～1904dに、イオンドープ法またはイオン注入法により、n型を付与する不純物元素を低濃度に添加する。n型を付与する不純物元素は、15族に属する元素を用いれば良く、例えばリン(P)、砒素(As)を用いる。

## 【0073】

次に、ゲート絶縁膜1905とゲート電極1907を覆うように、絶縁膜を形成する。絶縁膜は、プラズマCVD法やスパッタ法等により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む膜や、有機樹脂などの有機材料を含む膜を、単層又は積層して形成する。次に、絶縁膜を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、ゲート電極1907の側面に接する絶縁膜1908(サイドウォールともよばれる)を形成する。絶縁膜1908は、後にLDD(Lightly Doped drain)領域を形成する際のドーピング用のマスクとして用いる。

20

## 【0074】

次に、フォトリソグラフィ法により形成したレジストからなるマスクと、ゲート電極1907および絶縁膜1908をマスクとして用いて、半導体膜1904a～1904dにn型を付与する不純物元素を添加して、チャネル形成領域1906aと、第1の不純物領域1906bと、第2の不純物領域1906cを形成する(図9(C))。第1の不純物領域1906bは薄膜トランジスタのソース領域又はドレイン領域として機能し、第2の不純物領域1906cはLDD領域として機能する。第2の不純物領域1906cが含む不純物元素の濃度は、第1の不純物領域1906bが含む不純物元素の濃度よりも低い。

30

## 【0075】

続いて、ゲート電極1907、絶縁膜1908等を覆うように、絶縁膜を単層または積層して形成し、当該絶縁膜上に薄膜トランジスタのソース電極又はドレイン電極として機能する導電膜1931を形成する。その結果、薄膜トランジスタ1930a～1930dが得られる(図9(D))。

40

## 【0076】

絶縁膜は、CVD法、スパッタリング法、SOG法、液滴吐出法、スクリーン印刷法等により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ等の有機材料やシリコサン材料等により、単層または積層で形成する。ここでは、絶縁膜を2層で設けた例を示しており、1層目の絶縁膜1909として窒化酸化珪素膜で形成し、2層目の絶縁膜1910として酸化窒化珪素膜で形成することができる。

## 【0077】

なお、絶縁膜1909、1910を形成する前、または絶縁膜1909、1910のうちの一方又は両方を形成した後に、半導体膜1904a～1904dの結晶性の回復や半

50

導体膜に添加された不純物元素の活性化、半導体膜の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザーアニール法またはRTA法などを適用するとい。

#### 【0078】

導電膜1931は、フォトリソグラフィ法によりレジストパターンを形成し、これをマスクとして用いて絶縁膜1909、1910等をエッチングして、第1の不純物領域1906bを露出させるコンタクトホールを形成した後、コンタクトホールを充填するように導電膜を形成し、当該導電膜を選択的にエッチングして形成する。なお、導電膜を形成する前に、コンタクトホールにおいて露出した半導体膜1904a～1904dの表面にシリサイドを形成してもよい。

10

#### 【0079】

また、導電膜1931は、CVD法やスパッタリング法等により、アルミニウム(A1)、タンステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。導電膜1931は、例えば、バリア膜とアルミニウムシリコン(A1-Si)膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン(A1-Si)膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜1931を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができること。

20

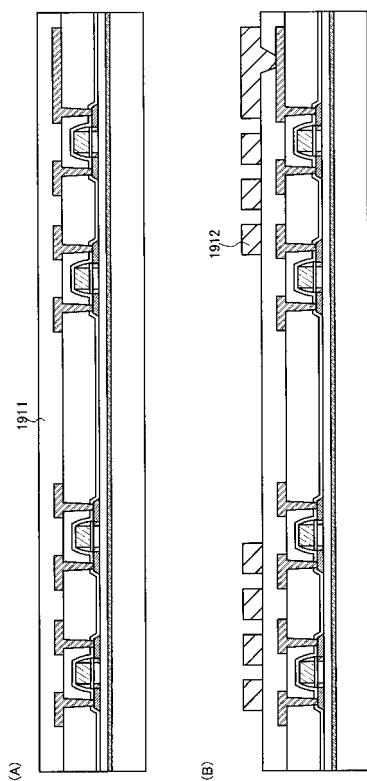

#### 【0080】

次に、導電膜1931を覆うように、絶縁膜1911を形成する(図10(A))。絶縁膜1911は、CVD法、スパッタリング法、SOG法、液滴吐出法またはスクリーン印刷法等を用いて、無機材料又は有機材料により、単層又は積層で形成する。また、絶縁膜1911は、好適には、0.75μm～3μmの厚さで形成する。

30

#### 【0081】

次に、絶縁膜1911の表面にアンテナとして機能する導電膜1912を選択的に形成する(図10(B))。

#### 【0082】

導電膜1912は、フォトリソグラフィ法及びエッチングにより絶縁膜1911を選択的にエッチングして、導電膜1931を露出させるコンタクトホールを形成した後、コンタクトホールを充填するように導電膜を形成し、当該導電膜を選択的にエッチングして形成する。

40

#### 【0083】

また導電膜1912は、CVD法、スパッタリング法、スクリーン印刷やグラビア印刷等の印刷法、メッキ処理等を用いて、導電性材料により形成すればよい。導電性材料は、アルミニウム(A1)、チタン(Ti)、銀(Ag)、銅(Cu)、金(Au)、白金(Pt)ニッケル(Ni)、パラジウム(Pd)、タンタル(Ta)、モリブデン(Mo)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層構造又は積層構造で形成する。

#### 【0084】

例えば、スクリーン印刷法を用いてアンテナとして機能する導電膜1912を形成する

50

場合には、粒径が数 nm から数十  $\mu$ m の導電体粒子を有機樹脂に溶解または分散させた導電性のペーストを選択的に印刷することによって設けることができる。導電体粒子としては、銀 (Ag)、金 (Au)、銅 (Cu)、ニッケル (Ni)、白金 (Pt)、パラジウム (Pd)、タンタル (Ta)、モリブデン (Mo) およびチタン (Ti) 等のいずれか一つ以上の金属粒子やハロゲン化銀の微粒子、または分散性ナノ粒子を用いることができる。スクリーン印刷法を用いて形成することにより、工程の簡略化が可能となり低コスト化を図ることができる。

【0085】

次に、アンテナとして機能する導電膜 1912 を覆うように絶縁膜 1913 を形成する (図 11 (A))。 10

【0086】

絶縁膜 1913 は、CVD 法、スパッタリング法、SOG 法、液滴吐出法、スクリーン印刷法等により、シリコンの酸化物やシリコンの窒化物等の無機材料 (例えば、酸化珪素膜、酸化窒化珪素膜、窒化珪素膜、窒化酸化珪素膜等)、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ等の有機材料やシリコサン材料等により、単層または積層で形成する。

【0087】

次に、薄膜トランジスタ 1930a ~ 1930d やアンテナとして機能する導電膜 1912 を含む素子形成層を基板 1901 から剥離する。

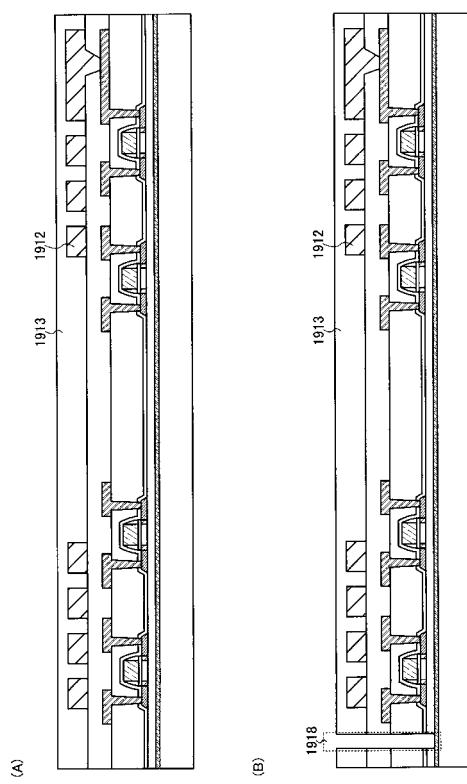

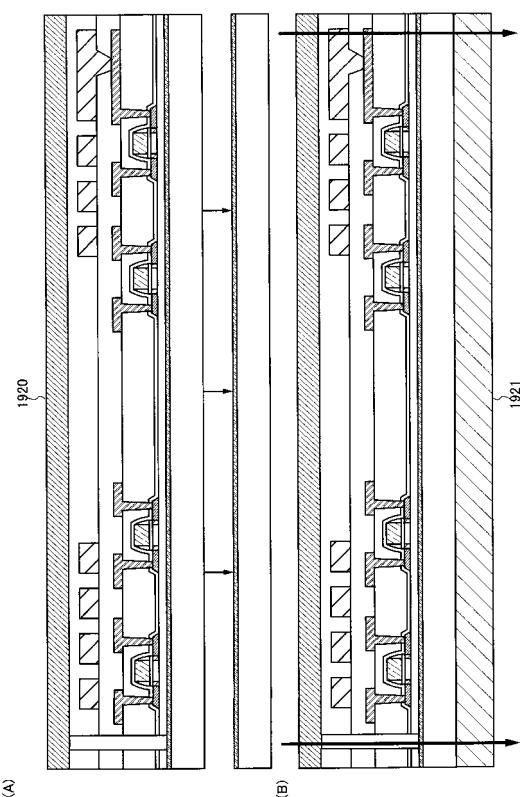

【0088】

まず、レーザー光を照射することにより開口部 1918 を形成する (図 11 (B))。 続いて、素子形成層の一方の面 (ここでは、絶縁膜 1917 の表面) を第 1 のシート材料 1920 に貼り合わせた後、物理的な力を用いて基板 1901 から素子形成層を剥離する (図 12 (A))。 第 1 のシート材料 1920 としては、ホットメルトフィルム等を用いることができる。また、後に第 1 のシート材料 1920 を剥離する場合には、熱を加えることにより粘着力が弱まる熱剥離テープを用いることができる。

【0089】

なお、剥離する際に水やオゾン水等の水溶液で剥離する面を濡らしながら行うことによって、薄膜トランジスタ 1930a ~ 1930d 等の素子が静電気等によって破壊されることを防止できる。また、素子形成層が剥離された基板 1901 を再利用することによって、低コスト化を実現することができる。 30

【0090】

次に、素子形成層の他方の面 (基板 1901 から剥離により露出した面) に、第 2 のシート材料 1921 を設ける (図 12 (B))。 第 2 のシート材料 1921 は、ホットメルトフィルム等を用い、加熱処理と加圧処理の一方又は両方を行うことにより素子形成層の他方の面に貼り合わせることができる。また、第 1 のシート材料 1920 として熱剥離テープを用いた場合には、第 2 のシート材料 1921 を貼り合わせる際に加えた熱を利用して剥離することができる。

【0091】

次に、第 2 のシート材料 1921 上に設けられた素子形成層をダイシング、スクライビング又はレーザーカット法等により選択的に分断することによって、複数の半導体装置を得ることができる。 第 2 のシート材料 1921 として、プラスチック等の可撓性を有する基板を用いることによって可撓性を有する半導体装置を作製することができる。 40

【0092】

なお、本実施の形態では、基板 1901 上に薄膜トランジスタやアンテナ等の素子を形成した後、当該基板 1901 から剥離することによって可撓性を有する半導体装置を作製する場合について示したが、これに限られない。 例えば、基板 1901 上に剥離層 1902 を設けずに図 12 (A)、図 9 (A) の工程を適用することにより、基板 1901 上に薄膜トランジスタやアンテナ等の素子が設けられた半導体装置を作製することができる。

【0093】

なお本実施の形態では、アンテナを半導体素子と同じ基板上に形成する例について説明したが、この構成に限定されない。半導体素子を形成した後、別途形成したアンテナを、集積回路と電気的に接続するようにしても良い。この場合、アンテナと集積回路との電気的な接続は、異方導電性フィルム ( A C F ( A n i s o t r o p i c C o n d u c t i v e F i l m ) ) や異方導電性ペースト ( A C P ( A n i s o t r o p i c C o n d u c t i v e P a s t e ) ) 等で圧着させることにより電気的に接続することができる。また、他にも、銀ペースト、銅ペーストまたはカーボンペースト等の導電性接着剤や半田接合等を用いて接続を行うことも可能である。

#### 【 0 0 9 4 】

なお、本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。

10

#### 【 0 0 9 5 】

##### ( 実施の形態 4 )

本実施の形態では、上記実施の形態 3 において、半導体装置のトランジスタの作製に用いられる絶縁基板上の半導体膜として単結晶半導体を用いた形態について説明する。

#### 【 0 0 9 6 】

以下本実施の形態では、単結晶半導体が形成される絶縁基板 ( 以下、S O I ( S i l i c o n o n I n s u l a t o r ) 基板という ) の製造方法について説明する。

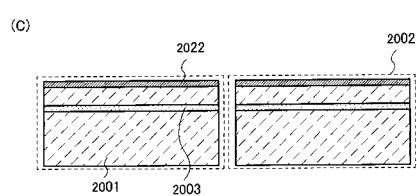

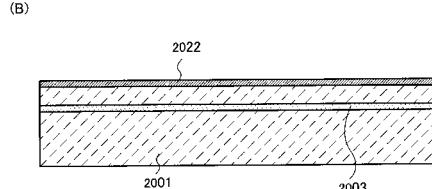

#### 【 0 0 9 7 】

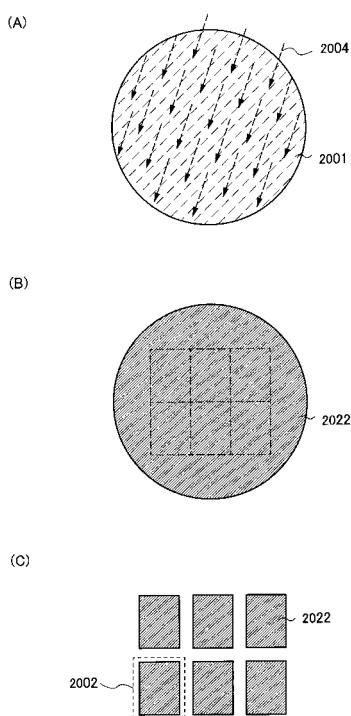

まず、半導体基板 2 0 0 1 を準備する ( 図 1 3 ( A ) 、図 1 5 ( A ) 参照 )。半導体基板 2 0 0 1 としては、市販の半導体基板を用いればよく、例えばシリコン基板やゲルマニウム基板、ガリウムヒ素やインジウムリンなどの化合物半導体基板が挙げられる。市販のシリコン基板としては、直径 5 インチ ( 1 2 5 m m ) 、直径 6 インチ ( 1 5 0 m m ) 、直径 8 インチ ( 2 0 0 m m ) 、直径 1 2 インチ ( 3 0 0 m m ) サイズのものが代表的であり、その形状は円形のものがほとんどである。また、膜厚は 1 . 5 m m 程度まで適宜選択できる。

20

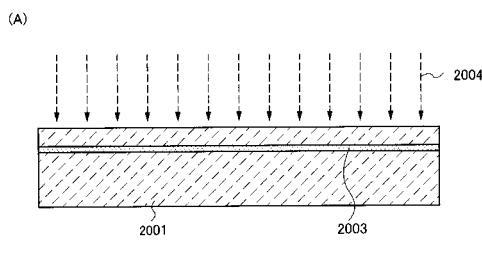

#### 【 0 0 9 8 】

次に、半導体基板 2 0 0 1 の表面から電界で加速されたイオン 2 0 0 4 を所定の深さに打ち込み、イオンドーピング層 2 0 0 3 を形成する ( 図 1 3 ( A ) 、図 1 5 ( A ) 参照 )。イオン 2 0 0 4 の打ち込みは、後にベース基板に転置する S O I 層の膜厚を考慮して行われる。好ましくは、S O I 層の膜厚が 5 n m 乃至 5 0 0 n m 、より好ましくは 1 0 n m 乃至 2 0 0 n m の厚さとなるようとする。イオンを打ち込む際の加速電圧及びイオンのドーズ量は、転置する S O I 層の膜厚を考慮して適宜選択する。イオン 2 0 0 4 は、水素、ヘリウム、又はフッ素等のハロゲンのイオンを用いることができる。なお、イオン 2 0 0 4 としては、水素、ヘリウム、又はハロゲン元素から選ばれたソースガスをプラズマ励起して生成された一の原子又は複数の同一の原子からなるイオン種を用いることが好ましい。水素イオンを注入する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup> イオンを含ませると共に、H<sub>3</sub><sup>+</sup> イオンの割合を高めておくとイオンの打ち込み効率を高めることができ、打ち込み時間を短縮することができるため好ましい。また、このような構成とすることで、半導体基板から S O I 層の分離を容易に行うことができる。

30

#### 【 0 0 9 9 】

なお、所定の深さにイオンドーピング層 2 0 0 3 を形成するために、イオン 2 0 0 4 を高ドーズ条件で打ち込むことが必要となる場合がある。このとき、条件によっては半導体基板 2 0 0 1 の表面が粗くなってしまう。そのため、半導体基板のイオンが打ち込まれる表面に、保護層として窒化シリコン層又は窒化酸化シリコン層などを膜厚 5 0 n m 乃至 2 0 0 n m の範囲で設けておいてもよい。

40

#### 【 0 1 0 0 】

次に、半導体基板 2 0 0 1 に接合層 2 0 2 2 を形成する ( 図 1 3 ( B ) 、図 1 5 ( B ) 参照 )。接合層 2 0 2 2 は、半導体基板 2 0 0 1 がベース基板と接合を形成する面に形成する。ここで形成する接合層 2 0 2 2 としては、上述のように有機シランを原料ガスに用

50

いた化学気相成長法により成膜される酸化シリコン層が好ましい。その他に、シランを原料ガスに用いた化学気相成長法により成膜される酸化シリコン層を適用することもできる。化学気相成長法による成膜では、半導体基板 2001 に形成したイオンドーピング層 2003 から脱ガスが起こらない程度の温度が適用される。例えば、350 以下の成膜温度が適用される。なお、単結晶半導体基板または多結晶半導体基板などの半導体基板から SOI 層を分離する加熱処理は、化学気相成長法による成膜温度よりも高い加熱処理温度が適用される。

#### 【0101】

次に、半導体基板 2001 を所望の大きさ、形状に加工する（図 13 (C)、図 15 (C) 参照）。具体的には、所望のサイズとなるように加工する。図 15 (C) では、円形の半導体基板 2001 を分断して、矩形の半導体基板 2002 を形成する例を示している。この際、接合層 2022 及びイオンドーピング層 2003 も分断される。つまり、所望のサイズであり、所定の深さにイオンドーピング層 2003 が形成され、表面（ベース基板との接合面）に接合層 2022 が形成された半導体基板 2002 が得られる。

#### 【0102】

半導体基板 2002 は、予め分断し、所望の半導体装置のサイズとすることが好ましい。半導体基板 2001 の分断は、ダイサー或いはワイヤソー等の切断装置、レーザー切断、プラズマ切断、電子ビーム切断、その他任意の切断手段を用いることができる。

#### 【0103】

なお、半導体基板表面に接合層を形成するまでの工程順序は、適宜入れ替えることが可能である。図 13 及び図 15 では半導体基板にイオンドーピング層を形成し、半導体基板の表面に接合層を形成した後、半導体基板を所望のサイズに加工する例を示している。これに対し、例えば、半導体基板を所望のサイズに加工した後、所望のサイズの半導体基板にイオンドーピング層を形成し、所望のサイズの半導体基板の表面に接合層を形成することもできる。

#### 【0104】

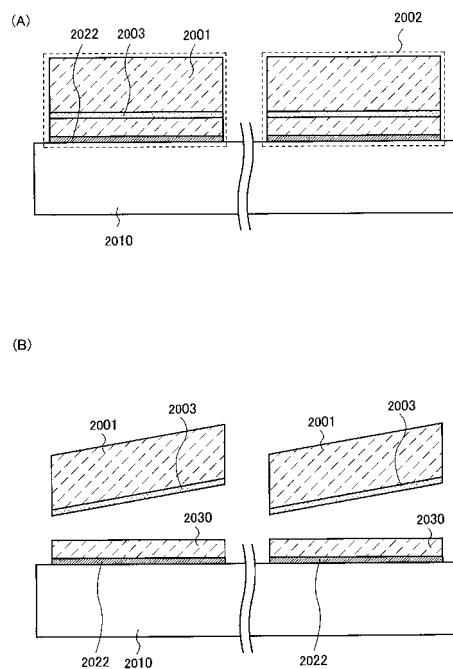

次に、ベース基板 2010 と半導体基板 2002 を貼り合わせる。図 14 (A) には、ベース基板 2010 と半導体基板 2002 の接合層 2022 が形成された面とを密着させ、ベース基板 2010 と接合層 2022 を接合させて、ベース基板 2010 と半導体基板 2002 を貼り合わせる例を示す。なお、接合を形成する面（接合面）は十分に清浄化しておくことが好ましい。ベース基板 2010 と接合層 2022 を密着させることにより接合が形成される。この接合はファンデルワールス力が作用しており、ベース基板 2010 と半導体基板 2002 とを圧接することで、水素結合による強固な接合を形成することが可能である。

#### 【0105】

また、ベース基板 2010 と接合層 2022 との良好な接合を形成するために、接合面を活性化しておいてもよい。例えば、接合を形成する面の一方又は双方に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行うことで接合面を活性化することもできる。このような表面処理により、400 以下の温度であっても異種材料間の接合を形成することが容易となる。

#### 【0106】

また、接合層 2022 を介してベース基板 2010 と半導体基板 2002 を貼り合わせた後は、加熱処理又は加圧処理を行うことが好ましい。加熱処理又は加圧処理を行うことで接合強度を向上させることが可能となる。加熱処理の温度は、ベース基板 2010 の耐熱温度以下であることが好ましい。加圧処理においては、接合面に垂直な方向に圧力が加わるように行い、ベース基板 2010 及び半導体基板 2002 の耐圧性を考慮して行う。

#### 【0107】

次に、加熱処理を行い、イオンドーピング層 2003 を劈開面として半導体基板 200

10

20

30

40

50

2の一部をベース基板2010から分離する(図14(B)参照)。加熱処理の温度は接合層2022の成膜温度以上、ベース基板2010の耐熱温度以下で行うことが好ましい。例えば、400乃至600の加熱処理を行うことにより、イオンドーピング層2003に形成された微小な空洞の体積変化が起こり、イオンドーピング層2003に沿って分離することが可能となる。接合層2022はベース基板2010と接合しているので、ベース基板2010上には半導体基板2002と同じ結晶性のSOI層2030が残存することとなる。

#### 【0108】

以上で、ベース基板2010上に接合層2022を介してSOI層2030が設けられたSOI構造が形成される。なお、SOI基板は、1枚のベース基板上に接合層を介して複数のSOI層が設けられた構造である。

10

#### 【0109】

なお、分離により得られるSOI層は、その表面を平坦化するため、化学的機械的研磨(Chemical Mechanical Polishing: CMP)を行うことが好ましい。また、CMP等の物理的研磨手段を用いず、SOI層の表面にレーザービームを照射して平坦化を行ってもよい。なお、レーザービームを照射する際は、酸素濃度が10ppm以下の窒素雰囲気下で行うことが好ましい。これは、酸素雰囲気下でレーザービームの照射を行うとSOI層表面が荒れる恐れがあるからである。また、得られたSOI層の薄膜化を目的として、CMP等を行ってもよい。

#### 【0110】

本実施の形態で述べたSOI基板の製造方法は、ガラス基板等の耐熱温度が600以下のベース基板2010であっても接合部の接着力が強固なSOI層2030を得ることができる。また、600以下の温度プロセスを適用すればよいため、ベース基板2010として、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスの如き無アルカリガラスと呼ばれる電子工業用に使われる各種ガラス基板を適用することができる。もちろん、セラミック基板、サファイヤ基板、石英基板等を適用することも可能である。

20

#### 【0111】

本実施の形態で説明したSOI基板は、単結晶半導体膜をガラス基板等の絶縁基板上に直接作製することができるため、半導体特性を高めるための半導体膜のレーザー結晶化等の結晶化工程の必要がない。そのため、SOI基板を作製し、上記実施の形態3で述べた方法を用いてトランジスタ等を作製することで、トランジスタ特性のばらつきの少ない素子を用いて半導体装置を構成することができるため、信頼性の高い半導体装置を作製することができる。

30

#### 【0112】

なお、本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。

#### 【0113】

##### (実施の形態5)

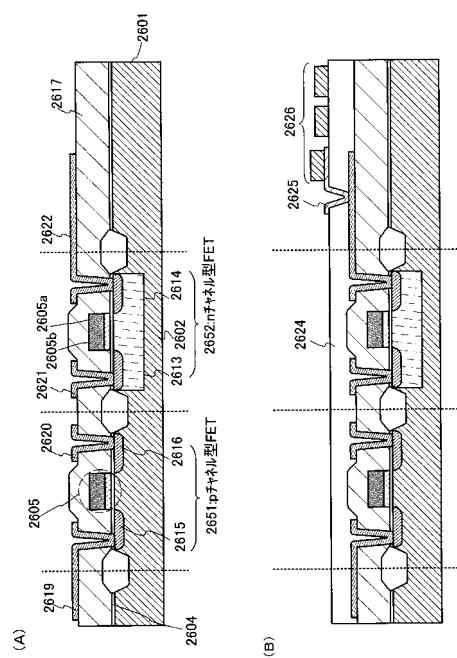

本実施の形態では、上記実施の形態で述べた半導体装置を構成するトランジスタの作製例について説明する。本実施の形態では特に、単結晶シリコンにより半導体装置を構成するトランジスタを作製する形態について図16、図17を用いて説明する。

40

#### 【0114】

まず、図16(A)を用いて、トランジスタの作製工程について説明する。単結晶シリコンからなるシリコン基板2601を用意する。そして、n型の導電性が付与されたシリコン基板の正面(素子形成面または回路形成面)の素子形成領域にp型ウェル2602を選択的に形成する。また、シリコン基板の裏面を研磨する等の手法によって薄くすることも可能である。予め、シリコン基板を薄膜化することによって、半導体装置を軽量で薄型な半導体装置を作製することができる。

#### 【0115】

50

次いで、第1の素子形成領域と第2の素子形成領域とを区画するための素子分離領域となるフィールド酸化膜2603を形成する。フィールド酸化膜2603は厚い熱酸化膜であり、公知のLOCOS法を用いて形成すればよい。なお、素子分離法は、LOCOS法に限定されず、例えば素子分離領域はトレンチ分離法を用いてトレンチ構造を有していてもよいし、LOCOS構造とトレンチ構造の組み合わせであってもよい。

【0116】

次いで、シリコン基板の表面を、例えば熱酸化させることによってゲート絶縁膜2604を形成する。ゲート絶縁膜2604は、CVD法を用いて形成してもよく、酸化窒化珪素膜や酸化珪素膜や窒化珪素膜やそれらの積層膜を用いることができる。

【0117】

次いで、ポリシリコン層2605aとシリサイド層2605bとの積層膜を全面に形成し、リソグラフィ技術およびドライエッチング技術に基づき積層膜を形成することによってゲート絶縁膜上にポリサイド構造を有するゲート電極2605を形成する。ポリシリコン層2605aは低抵抗化するために予め、 $10^{21} / \text{cm}^3$ 程度の濃度でリン(P)をドープしておいても良いし、ポリシリコン層を形成した後で濃いn型不純物を拡散させても良い。また、シリサイド層2605bを形成する材料はモリブデンシリサイド(MoSix)、タングステンシリサイド(WSix)、タンタルシリサイド(TaSix)、チタンシリサイド(TiSix)などを適用することが可能であり、公知の方法に従い形成すれば良い。

【0118】

なおゲート電極の側壁にサイドウォールを形成してもよい。例えば、酸化珪素からなる絶縁材料層を全面にCVD法にて堆積させ、かかる絶縁材料層をエッチバックすることによってサイドウォールを形成すればよい。エッチバックの際に自己整合的にゲート絶縁膜を選択的に除去してもよい。

【0119】

次いで、ソース領域およびドレイン領域を形成するために、露出したシリコン基板にイオン注入を行う。pチャネル型FETを形成すべき第1の素子形成領域をレジスト材料で被覆し、n型不純物であるヒ素(As)やリン(P)をシリコン基板に注入してソース領域2613及びドレイン領域2614を形成する。また、nチャネル型FETを形成すべき第2の素子形成領域をレジスト材料で被覆し、p型不純物であるボロン(B)をシリコン基板に注入してソース領域2615及びドレイン領域2616を形成する。

【0120】

次いで、イオン注入された不純物の活性化および、イオン注入によって発生したシリコン基板における結晶欠陥を回復するために、活性化処理を行う。

【0121】

そして、活性化後に層間絶縁膜や、ソース電極またはドレイン電極となるメタル配線等を形成する。層間絶縁膜2617は、プラズマCVD法や減圧CVD法を用いて酸化シリコン膜や酸化窒化シリコン膜などを形成する。なお、さらにその上にリンガラス(PSG)、あるいはボロンガラス(BSG)、もしくはリンボロンガラス(PBSG)の層間絶縁膜を形成してもよい。

【0122】

メタル電極2619、メタル電極2621、メタル電極2620、メタル電極2622は、層間絶縁膜2617およびゲート絶縁膜2604にそれぞれのFETのソース領域及びドレイン領域に達するコンタクトホールを形成した後に形成するもので、低抵抗材料として通常良く用いられるアルミニウム(A1)を用いると良い。また、A1とチタン(Ti)の積層構造としても良い。

【0123】

なお、コンタクトホールは、電子線直接描画技術によって形成してもよい。電子線直接描画は、ポジ型の電子線描画用レジストを層間絶縁膜2617上の全面に形成し、電子線が照射された部分を現像液によって溶解させる。そして、コンタクトホールが形成される

10

20

30

40

50

箇所のレジストに穴が空き、レジストをマスクとしてドライエッティングを行なうことにより、所定の位置の層間絶縁膜 2617 およびゲート絶縁膜 2604 がエッティングされてコンタクトホールを形成することができる。以上のようにして、p チャネル型トランジスタ 2651、n チャネル型トランジスタ 2652 を単結晶基板を用いて作製することができる（図 16（A））。

#### 【0124】

次に図 16（B）に示すように層間膜 2624 を形成する。そして層間膜 2624 をエッティングしコンタクトホールを形成し、メタル電極 2622 の一部を露出させる。層間膜 2624 は樹脂には限定せず、CVD 酸化膜など他の膜であっても良いが、平坦性の観点から樹脂であることが望ましい。また、感光性樹脂を用いて、エッティングを用いずにコンタクトホールを形成しても良い。次に層間膜 2624 上に、コンタクトホールを介してメタル電極 2622 と接する配線 2625 を形成する。

10

#### 【0125】

次にアンテナとして機能する導電膜 2626 を、配線 2625 と接するように形成する。導電膜 2626 は、銀（Ag）、金（Au）、銅（Cu）、パラジウム（Pd）、クロム（Cr）、白金（Pt）、モリブデン（Mo）、チタン（Ti）、タンタル（Ta）、タンゲステン（W）、アルミニウム（Al）、鉄（Fe）、コバルト（Co）、亜鉛（Zn）、錫（Sn）、ニッケル（Ni）などの金属を用いて形成することができる。導電膜 2626 は、上記金属で形成された膜の他に、上記金属を主成分とする合金で形成された膜、或いは上記金属を含む化合物を用いて形成された膜を用いても良い。導電膜 2626 は、上述した膜を単層で用いても良いし、上述した複数の膜を積層して用いても良い。

20

#### 【0126】

導電膜 2626 は、CVD 法、スパッタリング法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、めっき法、フォトリソグラフィ法、蒸着法等を用いて形成することができる。

#### 【0127】

なお本実施の形態では、アンテナを半導体素子と同じ基板上に形成する例について説明したが、この構成に限定されない。半導体素子を形成した後、別途形成したアンテナを、集積回路と電気的に接続するようにしても良い。この場合、アンテナと集積回路との電気的な接続は、異方導電性フィルム（ACF（Anisotropic Conductive Film））や異方導電性ペースト（ACP（Anisotropic Conductive Paste））等で圧着させることにより電気的に接続することができる。また、他にも、銀ペースト、銅ペーストまたはカーボンペースト等の導電性接着剤や半田接合等を用いて接続を行うことも可能である。

30

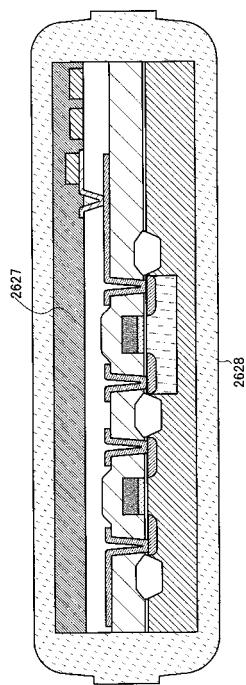

#### 【0128】

次に図 17 に示すように、アンテナとして機能する導電膜 2626 を覆うように保護膜 2627 を形成する。保護膜 2627 は、窒化シリコン膜、または酸化シリコン膜、あるいは窒化酸化シリコン膜で形成されている。また、窒化シリコン膜等の代わりに有機樹脂膜、若しくは保護膜の上有機樹脂膜を積層してもよい。有機樹脂材料として、ポリイミド、ポリアミド、アクリル、ベンゾシクロブテン（BCB）などを用いることができる。有機樹脂膜を用いる利点は、膜の形成方法が簡単である点や、比誘電率が低いので寄生容量を低減できる点、平坦化するのに適している点などがある。勿論、上述した以外の有機樹脂膜を用いても良い。

40

#### 【0129】

そして、図 17 に示すように、フィルム 2628 によって覆い、半導体装置を完成させることができる。フィルム 2628 の表面には、水分や酸素等の侵入を防ぐために、保護膜を形成しても良い。保護膜は、珪素を有する酸化物、又は珪素を有する窒化物によって形成することができる。また、フィルムには半導体装置のブースターアンテナとなるパターンが形成されていてもよい。

#### 【0130】

50

このように単結晶基板上に形成された半導体装置は、軽量でより小型化された製品を提供することができる。またこのような半導体装置は小型化された半導体装置を作成することができ、トランジスタ特性のばらつきも小さいため、好適である。

#### 【0131】

なお、本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。

#### 【0132】

##### (実施の形態6)

本実施の形態では、本発明の無線通信によりデータの交信を行う半導体装置の用途について説明する。本発明の半導体装置は、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類（運転免許証や住民票等）、包装用容器類（包装紙やボトル等）、記録媒体（DVDソフトやビデオテープ等）、乗物類（自転車等）、身の回り品（鞄や眼鏡等）、食品類、植物類、動物類、人体、衣類、生活用品類、電子機器等の商品や荷物の荷札等の物品に設ける、いわゆるICラベル、ICタグ、ICカードとして使用することができる。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置（単にテレビ、テレビ受像機、テレビジョン受像機とも呼ぶ）及び携帯電話等を指す。

10

#### 【0133】

なお、本明細書において、ICカードとは、プラスチック製カードに薄片化した半導体集積回路（ICチップ）を埋設して情報を記録できるようにしたカードである。データを読み書きする方式の違いによって「接触式」と「非接触式」に分けられる。非接触式カードにはアンテナが内蔵されており、微弱な電波を利用して端末と交信することができるものである。また、ICタグとは、物体の識別に利用される微小なICチップ（特にこの用途のICチップを「ICチップ」ともいう。）に自身の識別コードなどの情報が記録されており、電波を使って管理システムと情報を送受信する能力をもつものをいう。数十ミリメートルの大きさで、電波や電磁波で読み取り器と交信することができる。本発明の無線通信によりデータの交信を行う半導体装置に使うICタグの態様はさまざまであり、カード形式のものや、ラベル類（ICラベルという）、証書類などがある。

20

#### 【0134】

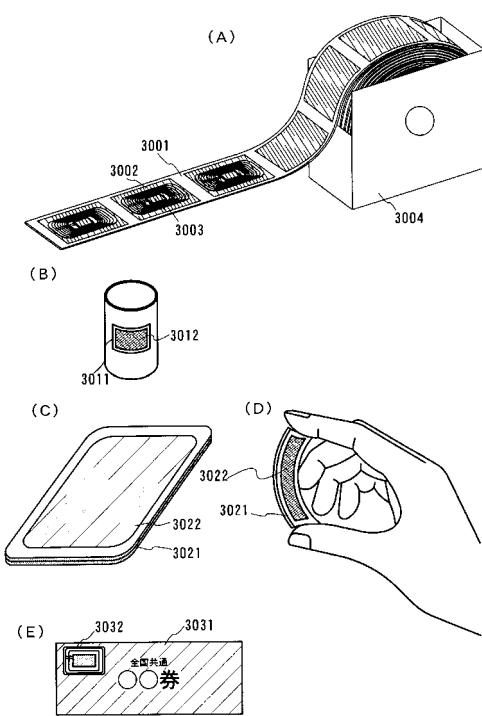

本実施の形態では、図18を参照して、本発明の応用例、及びそれらを付した商品の一例について説明する。

30

#### 【0135】

図18（A）は、本発明に係る半導体装置の完成品の状態の一例である。ラベル台紙3001（セパレート紙）上に、半導体装置3002を内蔵した複数のICラベル3003が形成されている。ICラベル3003は、ボックス3004内に収納されている。また、ICラベル3003上には、その商品や役務に関する情報（商品名、ブランド、商標、商標権者、販売者、製造者等）が記されており、一方、内蔵されている半導体装置には、その商品（又は商品の種類）固有のIDナンバーが付されており、偽造や、商標権、特許権等の知的財産権侵害、不正競争等の不法行為を容易に把握することができる。また、半導体装置内には、商品の容器やラベルに明記しきれない多大な情報、例えば、商品の产地、販売地、品質、原材料、効能、用途、数量、形状、価格、生産方法、使用方法、生産時期、使用時期、賞味期限、取扱説明、商品に関する知的財産情報等を入力しておくことができ、取引者や消費者は、簡易な読み取り装置によって、それらの情報にアクセスすることができる。また、生産者側からは容易に書換え、消去等も可能であるが、取引者、消費者側からは書換え、消去等ができない仕組みになっている。

40

#### 【0136】

図18（B）は、半導体装置3012を内蔵したラベル状のICタグ3011を示している。ICタグ3011を商品に備え付けることにより、商品管理が容易になる。例えば、商品が盗難された場合に、商品の経路を辿ることによって、その犯人を迅速に把握することができる。このように、ICタグを備えることにより、所謂トレーサビリティに優れた商品を流通させることができる。

50

## 【0137】

図18(C)は、本発明に係る半導体装置3022を内包したICカード3021の完成品の状態の一例である。上記ICカード3021としては、キャッシュカード、クレジットカード、プリペイドカード、電子乗車券、電子マネー、テレフォンカード、会員カード等のあらゆるカード類が含まれる。

## 【0138】

なお図18(C)に示したICカードにおいては、半導体装置を構成するトランジスタとして薄膜トランジスタを用いることにより、図18(D)に示すように折り曲げた形状に変形させたとしても使用することができる。

## 【0139】

図18(E)は、無記名債券3031の完成品の状態を示している。無記名債券3031には、半導体装置3032が埋め込まれており、その周囲は樹脂によって成形され、半導体装置を保護している。ここで、該樹脂中にはフィラーが充填された構成となっている。無記名債券3031は、本発明に係るICラベル、ICタグ、ICカードと同じ要領で作成することができる。なお、上記無記名債券類には、切手、切符、チケット、入場券、商品券、図書券、文具券、ビール券、おこめ券、各種ギフト券、各種サービス券等が含まれるが、勿論これらに限定されるものではない。また、紙幣、硬貨、有価証券類、無記名債券類、証書類等に本発明の半導体装置3032を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。

## 【0140】

また、ここでは図示しないが、書籍、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に本発明の半導体装置を設けることにより、検品システム等のシステムの効率化を図ることができる。また乗物類に半導体装置を設けることにより、偽造や盗難を防止することができる。また、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物に無線タグを埋め込むことによって、生まれた年や性別または種類等を容易に識別することが可能となる。

## 【0141】

以上、本発明の半導体装置は物品(生き物を含む)であればどのようなものにでも設けて使用することができる。

## 【0142】

なお、本実施の形態は、本明細書の実施の形態の技術的要素と組み合わせて行うことができる。

## 【図面の簡単な説明】

## 【0143】

【図1】実施の形態1を説明するための図。

【図2】実施の形態1を説明するための図。

【図3】実施の形態1を説明するための図。

【図4】実施の形態1を説明するための図。

【図5】実施の形態1を説明するための図。

【図6】実施の形態1を説明するための図。

【図7】実施の形態1を説明するための図。

【図8】実施の形態2を説明するための図。

【図9】実施の形態3を説明するための図。

【図10】実施の形態3を説明するための図。

【図11】実施の形態3を説明するための図。

【図12】実施の形態3を説明するための図。

【図13】実施の形態4を説明するための図。

【図14】実施の形態4を説明するための図。

【図15】実施の形態4を説明するための図。

【図16】実施の形態5を説明するための図。

10

20

30

40

50

【図17】実施の形態5を説明するための図。

【図18】実施の形態6を説明するための図。

【図19】実施の形態1を説明するための図。

【符号の説明】

【0144】

|         |          |    |

|---------|----------|----|

| 1 0 0   | 半導体装置    | 10 |

| 1 0 1   | アンテナ     |    |

| 1 0 2   | 整流回路     |    |

| 1 0 3   | 電荷蓄積回路   |    |

| 1 0 4   | 定電圧回路    |    |

| 1 0 5   | 論理回路     |    |

| 2 0 0 a | 整流回路     | 20 |

| 2 0 0 b | 整流回路     |    |

| 2 0 1   | ダイオード    |    |

| 2 0 2   | 容量素子     |    |

| 2 0 3   | 容量素子     |    |

| 2 0 4   | ダイオード    |    |

| 2 0 5   | ダイオード    |    |

| 2 0 6   | 容量素子     |    |

| 3 0 0   | 電荷蓄積回路   |    |

| 3 0 1 a | 容量素子     |    |

| 3 0 1 b | 容量素子     |    |

| 3 0 1 c | 容量素子     |    |

| 3 0 1 d | 容量素子     |    |

| 3 0 2 a | スイッチ     |    |

| 3 0 2 b | スイッチ     |    |

| 3 0 2 c | スイッチ     |    |

| 3 0 3   | 電荷蓄積制御回路 |    |

| 4 0 0   | 電荷蓄積回路   | 30 |

| 4 0 1 a | 容量素子     |    |

| 4 0 1 b | 容量素子     |    |

| 4 0 1 c | 容量素子     |    |

| 4 0 2 a | スイッチ     |    |

| 4 0 2 b | スイッチ     |    |

| 6 0 1   | 抵抗素子     |    |

| 6 0 2   | 抵抗素子     |    |

| 6 0 3   | コンパレータ   |    |

| 6 0 4   | トランジスタ   |    |

| 6 0 5   | ダイオード    |    |

| 8 0 0   | 半導体装置    | 40 |

| 8 0 1   | アンテナ     |    |

| 8 0 2   | 整流回路     |    |

| 8 0 3   | 電荷蓄積回路   |    |

| 8 0 4   | 定電圧回路    |    |

| 8 0 5   | 復調回路     |    |

| 8 0 6   | 変調回路     |    |

| 8 0 7   | 論理回路     |    |

| 8 0 8   | コントローラ   |    |

| 8 0 9   | CPU      |    |

| 8 1 0   | ROM      | 50 |

|           |           |    |

|-----------|-----------|----|

| 8 1 1     | R A M     |    |

| 9 0 1     | 抵抗素子      |    |

| 9 0 2     | 抵抗素子      |    |

| 9 0 3     | コンパレータ    |    |

| 9 0 4     | トランジスタ    |    |

| 1 9 0 1   | 基板        |    |

| 1 9 0 2   | 剥離層       |    |

| 1 9 0 3   | 絶縁膜       |    |

| 1 9 0 4   | 半導体膜      | 10 |

| 1 9 0 4 a | 半導体膜      |    |

| 1 9 0 4 b | 半導体膜      |    |

| 1 9 0 4 c | 半導体膜      |    |

| 1 9 0 4 d | 半導体膜      |    |

| 1 9 0 5   | ゲート絶縁膜    |    |

| 1 9 0 6 a | チャネル形成領域  |    |

| 1 9 0 6 b | 不純物領域     |    |

| 1 9 0 6 c | 不純物領域     |    |

| 1 9 0 7   | ゲート電極     |    |

| 1 9 0 8   | 絶縁膜       |    |

| 1 9 0 9   | 絶縁膜       | 20 |

| 1 9 1 0   | 絶縁膜       |    |

| 1 9 1 1   | 絶縁膜       |    |

| 1 9 1 2   | 導電膜       |    |

| 1 9 1 3   | 絶縁膜       |    |

| 1 9 1 7   | 絶縁膜       |    |

| 1 9 1 8   | 開口部       |    |

| 1 9 2 0   | シート材料     |    |

| 1 9 2 1   | シート材料     |    |

| 1 9 3 1   | 導電膜       |    |

| 1 9 5 0   | 領域        | 30 |

| 1 9 5 1   | 素子層       |    |

| 2 0 0 1   | 半導体基板     |    |

| 2 0 0 2   | 半導体基板     |    |

| 2 0 0 3   | イオンドーピング層 |    |

| 2 0 0 4   | イオン       |    |

| 2 0 1 0   | ベース基板     |    |

| 2 0 2 2   | 接合層       |    |

| 2 0 3 0   | S O I 層   |    |

| 2 6 0 1   | シリコン基板    |    |

| 2 6 0 2   | p型ウェル     | 40 |

| 2 6 0 3   | フィールド酸化膜  |    |

| 2 6 0 4   | ゲート絶縁膜    |    |

| 2 6 0 5   | ゲート電極     |    |

| 2 6 0 5 a | ポリシリコン層   |    |

| 2 6 0 5 b | シリサイド層    |    |

| 2 6 1 3   | ソース領域     |    |

| 2 6 1 4   | ドレイン領域    |    |

| 2 6 1 5   | ソース領域     |    |

| 2 6 1 6   | ドレイン領域    |    |

| 2 6 1 7   | 層間絶縁膜     | 50 |

|           |               |    |

|-----------|---------------|----|

| 2 6 1 8   | 導電膜           |    |

| 2 6 1 9   | メタル電極         |    |

| 2 6 2 0   | メタル電極         |    |

| 2 6 2 1   | メタル電極         |    |

| 2 6 2 2   | メタル電極         |    |

| 2 6 2 4   | 層間膜           |    |

| 2 6 2 5   | 配線            |    |

| 2 6 2 6   | 導電膜           |    |

| 2 6 2 7   | 保護膜           |    |

| 2 6 2 8   | フィルム          | 10 |

| 2 6 5 1   | p チャネル型トランジスタ |    |

| 2 6 5 2   | n チャネル型トランジスタ |    |

| 3 0 0 1   | ラベル台紙         |    |

| 3 0 0 2   | 半導体装置         |    |

| 3 0 0 3   | I C ラベル       |    |

| 3 0 0 4   | ボックス          |    |

| 3 0 1 1   | I C タグ        |    |

| 3 0 1 2   | 半導体装置         |    |

| 3 0 2 1   | I C カード       |    |

| 3 0 2 2   | 半導体装置         | 20 |

| 3 0 3 1   | 無記名債券         |    |

| 3 0 3 2   | 半導体装置         |    |

| 1 9 3 0 a | 薄膜トランジスタ      |    |

| 1 9 3 0 d | 薄膜トランジスタ      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(56)参考文献 特開平07-321696(JP,A)

特開2000-090221(JP,A)

特開2006-119811(JP,A)

(58)調査した分野(Int.Cl., DB名)

|         |           |

|---------|-----------|

| G 0 6 K | 1 9 / 0 7 |

| H 0 4 B | 1 / 5 9   |

| H 0 4 B | 5 / 0 2   |

| B 4 2 D | 1 5 / 1 0 |