(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3987159号

(P3987159)

(45) 発行日 平成19年10月3日(2007.10.3)

(24) 登録日 平成19年7月20日(2007.7.20)

(51) Int.C1.

F 1

G06F 1/26 (2006.01)

G06F 3/00 (2006.01)G06F 1/00 330F

G06F 3/00 Q

請求項の数 25 (全 15 頁)

(21) 出願番号 特願平9-157158

(22) 出願日 平成9年6月13日(1997.6.13)

(65) 公開番号 特開平10-63379

(43) 公開日 平成10年3月6日(1998.3.6)

審査請求日 平成16年6月14日(2004.6.14)

(31) 優先権主張番号 663754

(32) 優先日 平成8年6月14日(1996.6.14)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 590000879

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国テキサス州ダラス、ノース

セントラルエクスプレスウェイ 135

OO

(74) 代理人 100066692

弁理士 浅村 晃

(74) 代理人 100072040

弁理士 浅村 肇

(74) 代理人 100094673

弁理士 林 銀三

(74) 代理人 100091339

弁理士 清水 邦明

最終頁に続く

(54) 【発明の名称】外部データ・ドライブのインテリジェント駆動回路

## (57) 【特許請求の範囲】

## 【請求項1】

コンピュータ装置であって、

処理回路と、

信号を転送するための複数の入力/出力ピンを含み、前記処理回路に結合される入力/出力ポート・コネクタと、

前記入力/出力ポート・コネクタへのデータ・ドライブの接続を検出するデータ・ドライブ検出回路と、

を含み、

前記データ・ドライブ検出回路は、

10

第1のピン上の所定の信号を検出する回路と、

前記第1のピン上の前記所定の信号の検出に応じて第2のピンに電流を供給する回路と

、

前記第2のピン上の電圧に応じて所定の出力を生成する回路と、

を含み、

前記コンピュータ装置は、さらに

前記検出回路の出力に応じて、検出されたデータ・ドライブを駆動するため前記ピンの

一つに選択的に電力を供給するための電力・イネーブル回路、

を含むコンピュータ装置。

## 【請求項2】

20

請求項 1 に記載のコンピュータ装置であって、前記所定の信号は接地電圧信号であるコンピュータ装置。

【請求項 3】

請求項 1 に記載のコンピュータ装置であって、前記第 2 のピンは、プリンタが前記入力 / 出力ポートに接続される場合は接地に、前記入力 / 出力ポートがデータ・ドライブに結合される場合はロードに接続されるコンピュータ装置。

【請求項 4】

請求項 1 に記載のコンピュータ装置であって、前記入力 / 出力ポート・コネクタがパラレル・ポート・コネクタであるコンピュータ装置。

【請求項 5】

請求項 1 ~ 4 のいずれか 1 項に記載のコンピュータ装置であって、前記データ・ドライブ検出回路は、更に前記第 2 のピンへの電流をディスエーブルする回路を含むコンピュータ装置。

【請求項 6】

請求項 5 に記載のコンピュータ装置であって、電流をディスエーブルする前記回路は、所定時間後に前記第 2 のピンへの電流をディスエーブルする回路を含むコンピュータ装置。

【請求項 7】

請求項 1 ~ 4 のいずれか 1 項に記載のコンピュータ装置であって、オーバーヒートィングに応じて前記データ・ドライブへの電力をディスエーブルする熱保護回路を更に含むコンピュータ装置。

【請求項 8】

コンピュータであって、

処理回路と、

接続されたデータ・ドライブ又はプリンタのいずれか一方に信号を転送するための複数の入力 / 出力ピンを有する、前記処理回路に結合されるパラレル・ポート・コネクタと、

データ・ドライブ又はプリンタのいずれが前記パラレル・ポート・コネクタに接続されているかを検出するためのデータ・ドライブ検出回路と、

を含み、

前記データ検出回路は、前記第 1 のピン及び基準電圧に結合される第 1 の演算増幅器と、第 2 のピン及び前記基準電圧に結合される第 2 の演算増幅器とを含み、前記第 1 の演算増幅器の出力は前記第 1 のピンが所定の電圧に結合されているかどうかに応じ、前記第 2 の演算増幅器の出力は前記第 2 のピンが電圧レールに結合されているかどうかに応答するコンピュータを含み、

前記コンピュータは、さらに

前記検出回路の出力に応じて、検出されたデータ・ドライブを駆動するため前記ピンの一つに選択的に電力を供給し、検出されたプリンタへの電力をディスエーブルする電力・イネーブル回路を含むコンピュータ。

【請求項 9】

請求項 8 に記載のコンピュータであって、前記データ・ドライブ検出回路は、前記第 2 のピンに電流を供給するための回路を更に含むコンピュータ。

【請求項 10】

請求項 9 に記載のコンピュータであって、前記第 2 のピンに電流を供給するための回路は、所定時間の期間、前記第 2 のピンに電流を供給するための回路を含むコンピュータ。

【請求項 11】

請求項 8 ~ 10 のいずれか 1 項に記載のコンピュータであって、前記電力・イネーブル回路はトランジスタを含むコンピュータ。

【請求項 12】

請求項 8 ~ 10 のいずれか 1 項に記載のコンピュータであって、前記データ・ドライブ検出回路の出力に応じて、データ・ドライブが前記パラレル・ポート・コネクタに結合さ

10

20

30

40

50

れるかどうかを表す信号を生成するロジックを更に含むコンピュータ。

【請求項 1 3】

複数のピンを有する入力／出力ポート・コネクタに結合されるデバイスに選択的に電力を供給する回路であって、

前記入力／出力ポート・コネクタへの前記デバイスの接続を検出するためのデバイス検出回路と、

前記入力／出力ポート・コネクタの第 1 のピンに結合されるパワー・レールを前記デバイスが有するかどうかを判定するためのデバイス識別回路と、

前記検出回路の出力に応じて、前記デバイス識別回路に応じてデバイスを駆動するため前記第 1 のピンに選択的に電力を供給するための電力・イネーブル回路と、

10

を含む電力供給回路。

【請求項 1 4】

請求項 1 3 に記載の電力供給回路であって、前記デバイス検出回路は、第 2 のピン上の接地信号に応答する回路を含む電力供給回路。

【請求項 1 5】

請求項 1 3 または 1 4 に記載の電力供給回路であって、前記識別回路は、前記第 1 のピンがパワー・レールに結合されるかどうかに応じて識別信号を生成するための回路を含む電力供給回路。

【請求項 1 6】

請求項 1 5 に記載の電力供給回路であって、識別信号を生成するため前記回路は、前記第 1 のピンに電流を供給するための回路を含む電力供給回路。

20

【請求項 1 7】

請求項 1 5 に記載の電力供給回路であって、識別信号を生成するため前記回路は、所定の期間、前記第 1 のピンに電流を供給する回路を含む電力供給回路。

【請求項 1 8】

請求項 1 3 または 1 4 に記載の電力供給回路であって、前記電力・イネーブル回路は、前記識別信号に応じて前記第 1 のピンに電流を流すための回路を含む電力供給回路。

【請求項 1 9】

請求項 1 6 に記載の電力供給回路であって、前記電力・イネーブル回路は、前記識別信号によって駆動される制御ゲートを有するトランジスタを含む電力供給回路。

30

【請求項 2 0】

複数のピンを有する入力／出力ポート・コネクタに結合されるデバイスに電力を供給する方法であって、

入力／出力ポート・コネクタへのデバイスの接続を検出し、

前記入力／出力ポート・コネクタの第 1 のピンに結合されるパワー・レールをデバイスが有するかどうかを判定し、

前記判定工程に応じて、デバイスを駆動するため前記第 1 のピンに電源を結合する工程を含む方法。

【請求項 2 1】

請求項 2 0 に記載の方法であって、前記検出工程は、第 2 のピンが接地に接続されるかどうかを検出する工程を含む方法。

40

【請求項 2 2】

請求項 2 0 に記載の方法であって、前記判定工程は、第 1 のピンがパワー・レール結合されるかどうかに応じて識別信号を生成する工程を含む方法。

【請求項 2 3】

請求項 2 2 項に記載の方法であって、前記生成工程は、前記第 1 のピンに電流を供給する工程を含む方法。

【請求項 2 4】

請求項 2 2 に記載の方法であって、前記生成工程は、所定の時間の期間、前記第 1 のピンに電流を供給する工程を含む方法。

50

## 【請求項 25】

請求項 20 に記載の方法であって、前記結合工程は、前記識別信号に応じて第 1 のピンに電源を結合する工程を含む方法。

## 【発明の詳細な説明】

## 【0001】

## 【産業上の利用分野】

本発明は一般的にコンピュータに関し、更に詳細には外部データ・ドライブ用のインテリジェント駆動回路を有するコンピュータに関連する。

## 【0002】

## 【従来の技術及びその課題】

長年にわたり、ポータブル・コンピュータの大きさ及び重さが減少されてくるにつれて、ポータブル・コンピュータの人気が高まってきている。初期のポータブル・コンピュータは、運ぶことはできたため「かろうじて運搬可能な (luggable)」コンピュータとして知られていたが、デスクトップ・コンピュータと比較してわずかに小さく軽いだけであった。「ラップトップ」コンピュータは、より小型でより軽量であったが、回路の殆どが拡張ボードのオプションのないラップトップのマザーボードに設計される必要があったため、概して機能性や適応性に欠けていた。

## 【0003】

「ノートブック」コンピュータは、ラップトップ・コンピュータに比べ、著しくより小型でより軽量である。これらのコンピュータは、ブリーフケースに入れ容易に運ぶことができる。デスクトップ・コンピュータとは異なり、ノートブック・コンピュータは一般に、付加メモリ以外の周辺機器用の内部バス・スロットを備えていない。ハードドライブ、シリアル及びパラレル・ポート、及び時にはモデムなどの多くの一般的な周辺機器が、ノートブック・コンピュータのシステム・ボードに組込まれる。ネットワーク・インターフェース及びより高速のモデムなどの他の周辺機器は、外部接続可能な一つ又はそれ以上の周辺スロットを介してユーザに用いられる。過去に幾つかの専用スロットが用いられてきたが、周辺スロットを提供する殆どのノートブック・コンピュータは、一つ又はそれ以上の P C M C I A (PC カードとしても知られている) スロット、又は P C M C I A の後継であるカード・バス・スロット (ここでは総称して「周辺スロット」と呼ぶ) を用いている。

## 【0004】

フロッピー・ドライブは特殊な問題を提起する。一般にフロッピー・ドライブは、プログラムをロードし、他のコンピュータで用いるためにデータを転送し、少量のデータをアーカイブするために主として用いられる。フロッピー・ドライブは頻繁には用いられないため、コンピュータのパラレル・ポートへのインターフェースを有するフロッピー・ドライブが用いられる。同様に、C D - R O M ドライブやテープ・ドライブなどの他のデータ・ドライブも、コンピュータへ接続するためにパラレル・ポートを用いる。

## 【0005】

パラレル・ポートを介してインターフェースするデータ・ドライブの一つの欠点は、ドライブの駆動に關係する。パラレル・ポートは、データ信号を含む低電圧レベル以外は、接続されるデバイスに電力を供給しない。従って、パラレル・ポートを介してインターフェースするデータ・ドライブは、典型的に、個別のポートを介してデータ・ドライブに接続される A C / D C コンバータを用いる専用の電力供給源を有する。個別の電力供給源を用いることにより、外部データ・ドライブの携帯性が損なわれ不便になる。外部電力が必要な場合、A C 電源が使えないか又は不便な場所に設置されている多くの状況において、データ・ドライブを作動できない。

## 【0006】

別の設計により、データ信号及び電力の両方を供給する専用フロッピー・ポートが提供されるが、この設計には、付加するコネクタのコスト及び重量が加わり、フロッピー・ドライブのための専用インターフェースが必要となる。

## 【0007】

10

20

30

40

50

従って、外部データ・ドライブがそれを介して電力を受けることのできる標準コネクタを有するコンピュータ装置がこの分野で必要とされている。

#### 【0008】

##### 【課題を達成するための手段及び作用】

本発明は処理回路と、処理回路に結合される入力／出力ポートを有するコンピュータ装置を提供する。入力／出力ポートは信号を転送する複数の入力／出力ピンを有する。データ・ドライブ検出回路は、入力／出力ポート・コネクタへのデータ・ドライブの接続を検出し、電力スイッチ回路は検出されたデータ・ドライブを駆動するためピンの少なくとも一つに選択的に電力を供給する。

#### 【0009】

本発明は、従来技術に比べ著しい利点を提供する。第1に、コンピュータのパラレル・ポートは、付加的な電源又は個別のポートなく直接データ・ドライブを駆動することが可能である。第2に、この設計は現存のパラレル・ポート・データ・ドライブへの極く僅かな変更しか必要としない。現存のコンピュータ設計を、パラレル・ポートを介してデータ・ドライブに電力を供給するように、容易に適応させることができる。

#### 【0010】

##### 【実施例】

本発明の一実施例を図面を参照して説明する。

本発明は図1から図5の図面を参照することによって最もよく理解される。同様の番号が別の図面の同様の要素に用いられている。

10

20

#### 【0011】

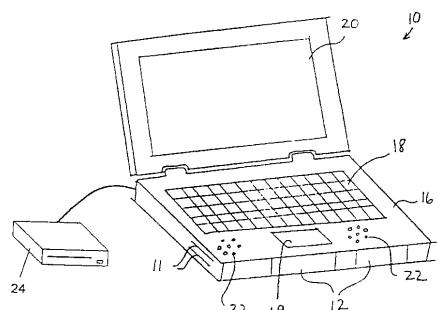

図1は、P C M C I A又はカード・バス・モジュール、ネットワーク・インターフェース、ハード・ドライブ又はサウンド・カード等の2つの周辺機器を受ける2つの周辺機器用アッセンブリ11を有するノートブック・コンピュータ装置10の斜視図を示す。モジュラー・ベイ12は、フロッピードライブ、ハードディスク・ドライブ、CD-R OM、光磁気ディスク(MO)、バッテリー、又はセルラー・テレコミュニケーション・デバイス等のより大きなデバイスに用いられる。コンピュータ装置10は、コンピュータ電子機器が中に搭載されるメイン・ハウジング16を有する。周辺機器用アッセンブリ11は、そのハウジングを介しアクセスし得る。キーボード18は、メイン・ハウジング16の上部に配置される。好ましい実施例においてキーボード18は、タッチパッド19のようなポイントティング・デバイスを有する。ディスプレイ20は、メインハウジング16に取付けられる。典型的に、ディスプレイ20は、コンピュータ10が使用されているときメインハウジング16から折り開かれ、コンピュータ10が使用されていないとき携帯できるようにメインハウジング16と同一平面にたたまれるように、ヒンジでメインハウジング16に取付けられる。マルチメディア・コンピュータ用に、メインハウジング16にスピーカ22が提供されて示されている。

30

#### 【0012】

フロッピードライブ24は、コンピュータ10のパラレル・ポート(図示せず)に接続される。フロッピードライブ24は、コンピュータのパラレル・ポートを介してデータを受信及び送信できるタイプであり、そのようなドライブはノートブック・コンピュータの分野では典型的である。フロッピードライブ24は個別の電源を用いず、その電力をパラレル・ポートを介してノートブック・コンピュータのバッテリから受ける。本発明では、パラレル・ポート・フロッピードライブと関連して説明するが、パラレル・ポートCD-R OM、高密度の取外し可能なディスク・ドライブ、及びパラレル・ポート・テープ・ドライブ等の他の種類のデータ・ドライブも、図3から図5に示される回路を用いてパラレル・ポートを介して電力を受けるように適応させることが可能である。

40

#### 【0013】

図1は特定のノートブック・コンピュータ設計を示すが、多くの変更が成され得ることに注意されたい。例えば、マウスやトラックボール又はインテグレイテッド・ジョイスティックなどの多くの異なるポイントティング・デバイスが用いられ得る。当技術に習熟した者

50

であれば周知である様に、スピーカ及びモジュラ・ベイなどの他の特性はオプションであり、本発明を実行するのに必ずしも必要ではない。

【0014】

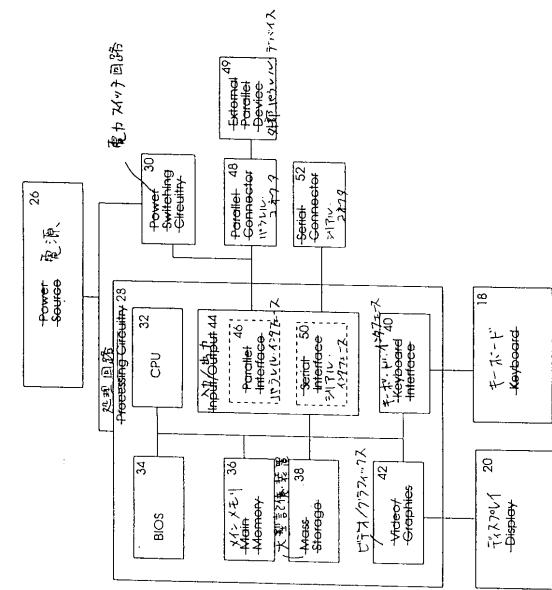

図2は、IBM PC互換のアーキテクチャ用のコンピュータ10の基本的ブロック図を示す。電源26(即ち、ポータブル・コンピュータ用バッテリー又はAC/DCコンバータ)は、処理回路28、ディスプレイ20、キーボード18、及び電力スイッチ回路30に結合される。処理回路28は、CPU(中央処理装置)32、BIOS(ベイシック・インプット・アウトプット・システム)34、メイン・メモリ36、大型記憶装置38、キーボード・インターフェース40、ビデオ回路42(フレーム・バッファを含む)、及び入力/出力回路44を有する。処理回路28の全体の設計は従来通りであり、当技術に習熟した者には周知な様に、処理回路の設計の詳細は変えることが可能である。入力/出力回路44のパラレル・ポート・インターフェース46は、外部デバイス49への物理的接続を提供するパラレル・ポート・コネクタ48に接続される。同様に、入力/出力回路44のシリアル・ポート・インターフェース50は、外部シリアル・デバイスへの物理的接続を提供するシリアル・ポート・コネクタ52に接続される。電力スイッチ回路30はパラレル・ポート・コネクタ48及び電源26に結合される。

10

【0015】

動作において、パラレル・ポートは、(1)パラレル・ポートを介して電力を受けないプリンタ又は他のデバイスに、又は(2)パラレル・ポートを介して電力を受けることのできるフロッピー・ドライブ又は他のデータ・ドライブに結合され得る。デバイスがある場合は、どのデバイスがパラレル・ポートに接続されるかに応じて、電力スイッチ回路30は、(1)パラレル・ポート・コネクタ48を介して電力をディスエーブルするか、又は(2)パラレル・ポート・コネクタ48の一つ又はそれ以上のパラレル・ポート・ピンを介して供給される電力をイネーブルする。

20

【0016】

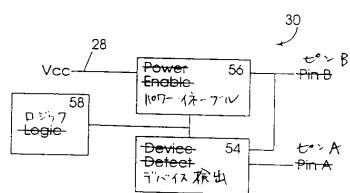

電力スイッチ回路30のブロック図が図3に示されている。デバイス検出回路54は、パラレル・ポート・コネクタ48のピンA及びピンBに結合される。デバイス検出回路54の出力は、パワー・イネーブル回路56及びロジック58に結合される。パワー・イネーブル回路56は、電源Vcc及びピンBに結合される。

30

【0017】

動作において、デバイス検出回路は、ピンA及びピンB上の外部デバイス49への接続に応じて、プリンタ又はフロッピーのどちらがパラレル・ポートに結合される(又はいずれも結合されない)かを検出する。フロッピー(又は他の同様に構成されたデータ・ドライブ)がパラレル・ポート・コネクタ48に結合される場合、パワー・イネーブル回路56はピンBに電力を流す。プリンタがパラレル・ポート・コネクタ48に接続される場合、パワー・イネーブル回路はピンBへの電力をディスエーブルする。

【0018】

好ましい実施例において、ピンAはパラレル・インターフェース上のピン「20」であり、ピンBはパラレル・インターフェース上のピン「24」である。パラレル・ポート・コネクタ48にプラグされる外部デバイス29がないとき、ピンA及びピンBはどちらも浮遊する。プリンタがパラレル・ポート・コネクタ48にプラグされるとき、ピンA及びピンBはどちらもプリンタによって接地に結合される。以下に詳しく説明するように、図示された実施例のパラレル・ポート・コネクタ48に接続されるパラレル・ポート・フロッピー・ドライブは、ピンAを接地し、フロッピー・ドライブのパワー・レールをピンBに結合する。

40

【0019】

パラレル・ポート・コネクタのピン「20」及び「24」は、図示された実施例では電力スイッチ回路と共に用いられているが、パラレル・ポート・コネクタ48に結合されるデバイスを識別するために他のピンを用いることもできる。

【0020】

50

ロジック 5 8 も、パラレル・ポート・コネクタ 4 8 へのフロッピー・ドライブの接続を検出する。好ましい実施例において、ロジック 5 8 は、フロッピー・ドライブがパラレル・ポート 4 8 に接続されるか又はパラレル・ポート 4 8 から接続を解除されるとき、必ず S M I (システム・マネジメント・インターフェース) を生成する。これにより、システムのオペレーティング・システムが現在のハードウェア構成を説明する構成情報を再算出することが可能になる。S M I 処理ルーティンは、典型的にシステム B I O S にセットされる。

#### 【0021】

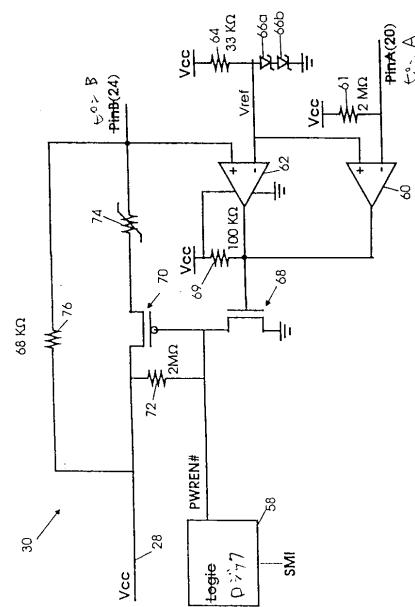

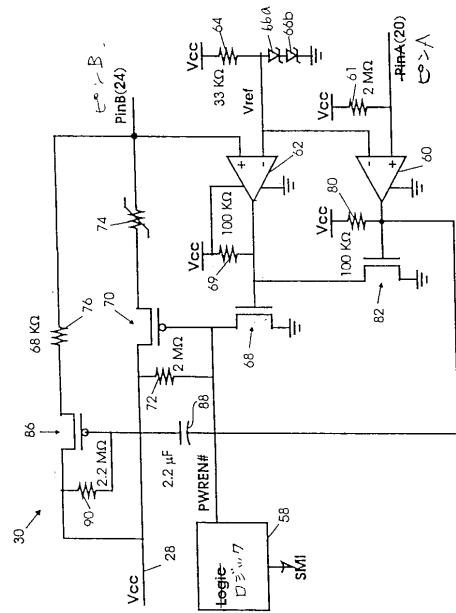

図 4 は、好ましいレジスタ (抵抗) 値を有する電力スイッチ回路 3 0 の第 1 の実施例の略図を示す。ピン A は演算増幅器 (以下「オペ・アンプ」) 6 0 の反転入力に結合される。ピン A はプル・アップ・レジスタ 6 1 (2 M) を介して  $V_{cc}$  にも結合される。オペ・アンプ 6 0 の非反転入力は、オペ・アンプ 6 2 の反転入力と基準電圧  $V_{ref}$  とに結合される。 $V_{ref}$  は、プル・アップ・レジスタ 6 4 (33 K) を介して  $V_{cc}$  に結合され、及びショットキー・ダイオード 6 6 a 及び 6 6 b を介して接地に結合されるノードで生成される。従って、 $V_{ref}$  は約 0.6 - 0.7 ボルトである。オペ・アンプ 6 0 及び 6 2 の出力は、N チャネル・トランジスタ 6 8 のゲートと  $V_{cc}$  との間に結合されるプル・アップ・レジスタ 6 9 (100 K) と共に、N チャネル・トランジスタ 6 8 のゲートに結合される。N チャネル・トランジスタ 6 8 のソースは接地に結合され、N チャネル・トランジスタ 6 8 のドレインは P チャネル・トランジスタ 7 0 のゲートに結合される。P チャネル・トランジスタ 7 0 のゲートは更に、レジスタ 7 2 (2 M) を介し P チャネル・トランジスタ 7 0 のソースに、及びロジック 5 8 に結合される。P チャネル・トランジスタ 7 0 のゲートの信号は、P W R E N # 信号として示される。

#### 【0022】

P チャネル・トランジスタ 7 0 のソースは、電源 ( $V_{cc}$ ) 2 8 に更に結合される。P チャネル・トランジスタ 7 0 のドレインは、熱保護レジスタ (T P R) 7 4 の第 1 の端子に結合される。T P R 7 4 の第 2 の端子は、ピン B に結合される。レジスタ 7 6 (68 K) は電源 2 8 に結合される第 1 の端子と、ピン B に結合される第 2 の端子とを有する。ピン B は、オペ・アンプ 6 2 の非反転入力に更に結合される。

#### 【0023】

図 4 の回路の動作は、3 つの起こり得る状態と関連して説明される。(1) パラレル・ポート・コネクタ 4 8 に結合される外部デバイス 2 9 がない。(2) フロッピー・ドライブがパラレル・ポート・コネクタ 4 8 に結合される。(3) プリンタがパラレル・ポート・コネクタ 4 8 に結合される。

#### 【0024】

パラレル・ポート・コネクタ 4 8 に結合される外部デバイス 2 9 がない第 1 のケースにおいて、パラレル・ポート・コネクタ 4 8 のピン A はプル・アップ・レジスタ 6 1 を介して  $V_{cc}$  まで引き寄せられる。従って、反転入力は、非反転入力電圧 ( $V_{ref}$ ) より高い電圧 ( $V_{cc}$ ) を有し、オペ・アンプ 6 0 はその出力をゼロボルトに保つ。結果として、N チャネル・トランジスタ 6 8 のゲートはゼロボルトに保たれ、それによりトランジスタ 6 8 をオフにする。N チャネル・トランジスタ 6 8 がオフになると、P チャネル・トランジスタ 7 0 のゲートはプル・アップ・レジスタ 7 2 を介して  $V_{cc}$  まで引き寄せられる。このため、P チャネル・トランジスタ 7 0 はオフにされ、約 68 K の高抵抗レベルを有するレジスタ 7 6 を介する以外ピン B からの電源 2 8 の結合を解除する。しかし、ピン B は浮遊しているため、電流はレジスタ 7 6 を介して流れない。

#### 【0025】

フロッピー・ドライブ又は他の適切に構成されたデータ・ドライブがパラレル・ポート・コネクタ 4 8 に結合される第 2 のケースにおいて、パラレル・ポート・コネクタ 4 8 のピン A はプル・アップ・レジスタ 6 1 を介する電圧に打ち勝つフロッピー・ドライブ上の接地まで引き寄せられる。従って、反転入力は非反転入力より低い電圧を有し、オペ・アンプ 6 0 は、それが N チャネル・トランジスタ 6 8 をオンにしないオープン・ドレイン・モードにある。ピン B は、同等の抵抗 ( $R_{if}$ ) および静電容量 ( $C_{if}$ ) を有するフロッピー

・ ドライブのパワー・レールに結合される。レジスタ 7 6 を介する電流は、オペ・アンプ 6 2 の非反転入力での電圧が  $V_{ref}$  より大きいように  $C_{if}$  を充電する。従って、オペ・アンプ 6 2 はオープン・ドレイン・モードにあり、N チャネル・トランジスタのゲートはプル・アップ・レジスタ 6 9 を介して  $V_{cc}$  まで引き寄せられる。

【 0 0 2 6 】

トランジスタ 6 8 がイネーブルされると、P チャネル・トランジスタ 7 0 のゲートは接地まで引き上げられ、フロッピー・ドライブを駆動するためピン B へトランジスタ 7 0 のソースおよびドレインを介して  $V_{cc}$  を流すことが可能となる。TPR 7 4 は、過度の熱が発生した場合、電流の流れを止めるヒューズの役目をする。

【 0 0 2 7 】

プリンタがパラレル・ポート・コネクタ 4 8 に結合される第 3 のケースの場合、ピン A 及びピン B はいずれも（通常の方法で）接地に接続される。そのため、ピン A がオペ・アンプ 6 0 をオープン・ドレイン出力にセットする一方、ピン B はゼロボルトのままである（レジスタ 7 6 を介する電流が接地されたピン B を充電することができないため）。従って、N チャネル・トランジスタ 6 8 はオフにされ、P チャネル・トランジスタ 7 0 はそのゲートがレジスタ 7 2 を介して  $V_{cc}$  まで引き寄せられるためオフにされる。トランジスタ 7 2 がオフにされることにより、高抵抗レベルを有するレジスタ 7 6 を介する以外、ピン B は電源 2 8 から結合を解除され、僅かな量（約 0.07 ミリアンプ）の電流のみがピン B へ流れようになる。

【 0 0 2 8 】

レジスタ 7 6 を介してプリンタへ流れる電流の量は小さいが、ノートブック・コンピュータのバッテリー寿命を伸ばすためには、この電流をなくすことが望ましい。図 5 は図 4 の回路と同じ電力スイッチ機能を行い、一方、パラレル・ポート・コネクタ 4 8 がプリンタに接続される間電力消費を減少する回路を示す。

【 0 0 2 9 】

図説のため、図 4 の参照番号の多くが図 5 に取り入れられている。ピン A はオペ・アンプ 6 0 の非反転入力に結合される（図 4 では、ピン A はオペ・アンプ 6 0 の反転入力に結合されたことに注意されたい。）。ピン A はプル・アップ・レジスタ 6 1 を介して  $V_{cc}$  にも結合される。オペ・アンプ 6 0 の反転入力は、オペ・アンプ 6 2 の反転入力、及びプル・アップ・レジスタ 6 4 を介して  $V_{cc}$  に結合され且つショットキー・ダイオード 6 6 a 及び 6 6 b を介して接地に結合されるノードで生成される基準電圧  $V_{ref}$  に結合される。このため、 $V_{ref}$  は約 0.6 - 0.7 ボルトである。オペ・アンプ 6 0 の出力は、プル・アップ・レジスタ 8 0 (100 K) を介して  $V_{cc}$  に、及び N チャネル・トランジスタ 8 2 のゲートに結合される。N チャネル・トランジスタ 8 2 は、接地に接続されるソースと、及び、オペアンプ 6 2 の出力と N チャネル・トランジスタ 6 8 のゲートと  $V_{cc}$  との間に結合されるプル・アップ・レジスタ 6 9 と共に N チャネル・トランジスタ 6 8 のゲートに結合されるドレインとを有する。N チャネル・トランジスタ 6 8 のソースは接地に結合され、N チャネル・トランジスタ 6 8 のドレインは P チャネル・トランジスタ 7 0 のゲートに結合される。P チャネル・トランジスタ 7 0 のゲートは、レジスタ 7 2 を介し P チャネル・トランジスタ 7 0 のソースにも結合され、さらにロジック 5 8 に結合される。P チャネル・トランジスタ 7 0 のゲートの信号は、P W R E N # 信号として示される。

【 0 0 3 0 】

P チャネル・トランジスタ 7 0 のソースは、電源 ( $V_{cc}$ ) 2 8 にも結合される。P チャネル・トランジスタ 7 0 のドレインは、熱保護レジスタ (TPR) 7 4 の第 1 の端子に結合される。熱保護レジスタ (TPR) 7 4 の第 2 の端子はピン B に結合される。オペ・アンプ 6 0 の出力はキャパシタ 8 8 (2.2  $\mu$  F) を介して P チャネル・トランジスタ 8 6 のゲートに結合される。P チャネル・トランジスタ 8 6 のゲートはレジスタ 9 0 (2.2 M) を介して P チャネル・トランジスタ 8 6 のソースにも結合される。P チャネル・トランジスタ 8 6 のソースは  $V_{cc}$  にも結合される。レジスタ 7 6 は P チャネル・トランジスタ 8 6 のドレインに結合される第 1 の端子と、ピン B に結合される第 2 の端子を有する

10

20

30

40

50

。ピンBはオペ・アンプ62の非反転入力にも接続される。

【0031】

図5の回路の動作は3つの起こり得る状態と関連して説明される。(1)パラレル・ポート・コネクタ48に結合される外部デバイス29がない。(2)フロッピードライブがパラレル・ポート・コネクタ48に結合される。(3)プリンタがパラレル・ポート・コネクタ48に結合される。

【0032】

パラレル・ポート・コネクタ48に結合される外部デバイス29がない第1のケースにおいて、ピンAはプル・アップ・レジスタ61を介して $V_{cc}$ まで引きあげられる。オペ・アンプ60の非反転入力は $V_{cc}$ であるため、 $V_{ref}$ に接続されるオペ・アンプ60の反転入力での電圧より高く、オペ・アンプ60の出力はオープン・ドレインであり、Nチャネル・トランジスタ82のゲートは $V_{cc}$ まで引き寄せられる。トランジスタ82はイネーブルされ、トランジスタ68のゲートは接地まで引き寄せられ、トランジスタ68をオフにする。同様にPチャネル・トランジスタ70は、そのゲートがレジスタ72を介して $V_{cc}$ まで引き寄せられるためオフにされる。Pチャネル・トランジスタ86もオフにされる。

10

【0033】

従って、Pチャネル・トランジスタ70またはPチャネル・トランジスタ86のいずれかを介して流す適当な電流がない。さらに、Pチャネル・トランジスタ86がこの状況でイネーブルされたとしても、この地点でピンBに結合されるデバイスはなく、そのためPチャネル・トランジスタ86を介して流し得る電流はない。

20

【0034】

フロッピードライブがパラレル・ポート・コネクタ48に結合される第2のケースにおいて、ピンAは接地に結合され、それにより非反転入力が反転入力より低い電圧であるため、オペ・アンプ60からゼロボルト出力が生成される。結果として、Nチャネル・トランジスタ82はオフにされる。トランジスタ86( $V_{cc}$ であり得る)のゲートとオペ・アンプ60(ゼロボルトである)の出力との間に結合されるキャパシタ88は、その端子を通って $V_{cc}$ の電位までオーバータイム充電される。充電の速度は、レジスタ90及びキャパシタ88の値によって調整され得る。

【0035】

キャパシタ88が充電される間、Pチャネル・トランジスタ86のゲートは接地から $V_{cc}$ に転移する。従って、フロッピードライブがパラレル・ポート・コネクタ48に接続されるときPチャネル・トランジスタ86は内的にイネーブルされ、そのゲートがトランジスタ86のスレッショルド電圧内の電圧に達するとオフにされる。Pチャネル・トランジスタ86がオンにされると、電流はレジスタ76を介してピンBに流れ、ピンBを $V_{ref}$ より高い電圧まで充電し、オペ・アンプ62の出力をオープン・ドレイン・モードにする(place)。Nチャネル・トランジスタ68のゲートは $V_{cc}$ まで引き寄せられ、それによりトランジスタ68をイネーブルする。トランジスタ68はPチャネル・トランジスタ70のゲートを接地まで引き寄せ、電流がPチャネル・トランジスタ70を介してピンBへ流れるようにする。このためフロッピードライブは、Pチャネル・トランジスタ70を介して駆動され得る。

30

【0036】

キャパシタ88が充電された後、Pチャネル・トランジスタ86はオフにされる。Pチャネル・トランジスタ70がオンになった後Pチャネル・トランジスタ86がオフである限り、電源自体はピンBを $V_{cc}$ より上に保つため、Pチャネル・トランジスタ70は電源からピンBへ電流を流し続ける。

40

【0037】

プリンタがパラレル・ポート・コネクタ48に結合される場合、ピンA及びピンBの両方が接地まで引き寄せられる。フロッピードライブの場合と同じく、接地されたピンAはトランジスタ82をオフにし、キャパシタ88に充電させる。キャパシタ88が充電すると、Pチャネル・トランジスタ86がイネーブルされるが、ピンBが接地であるため、ピ

50

ンBを $V_{ref}$ より上の電圧に充電することはできない。したがって、オペ・アンプ62の出力はゼロボルトのままであり、Nチャネル・トランジスタ68及びPチャネル・トランジスタ70をオフに保つ。キャパシタ88が所定の電位まで充電された後、Pチャネル・トランジスタ86がオフになるとき、電流はPチャネル・トランジスタ86を介してストップされる。そのため、ピンBへ流れる電流はなくなる。

#### 【0038】

従って、フロッピー・ドライブ又はプリンタなどのデバイスへの接続に応じ、図5の回路は、ピンBへ電流を流すためにタイミング回路を用いる。そのデバイスが適切に構成されたピンBを有するフロッピー・ドライブである場合、電流は $V_{ref}$ を越える電圧までピンBを充電し、Pチャネル・トランジスタ70をオンにし、デバイスを駆動する。そのデバイスがプリンタであり、ピンBが接地される場合、所定の時間（例えば10秒）後にタイミング回路はオフになり、デバイスに電流は流れなくなる。充電時間は式 $T = 1.61 \times R \times C$ によって決定され得、ここでRはレジスタ90の値で単位はオーム、Cはキャパシタ88の値で単位はファラッドである。

#### 【0039】

本発明の詳細な説明が或る例示用の実施例に関してなされたが、これらの実施例の種々の変形及び他の実施例は、この技術の分野の習熟者に想起され得る。例えば、Nチャネル・トランジスタは、NPNトランジスタ、JFET（接合電界効果）トランジスタ、又はBJT（バイポーラ接合）トランジスタで置き換えてよい。Pチャネル・トランジスタ及び関連するレジスタは、ハイブリッドMOSFETトランジスタ（テキサス・インスツルメンツ・インコーポレイテッド製のTPS20120など）又はPNPトランジスタを用いて置換され得る。キャパシタ88、Pチャネル・トランジスタ86及びレジスタ90を含むタイミング回路は、低インピーダンス・コイルを有するリレー、低イネーブルを有するフォト・スイッチなどの多数のタイミング回路で置き換えられ得る。本発明は、特許請求の範囲を越えることなく、あらゆる変形又は他の実施例を包含する。

#### 【0040】

以上の説明に関して更に次の項を開示する。

（1）コンピュータ装置であって、

処理回路と、

信号を転送するための複数の入力／出力ピンを含み、前記処理回路に結合される入力／出力ポート・コネクタと、

前記入力／出力ポート・コネクタへのデータ・ドライブの接続を検出するデータ・ドライブ検出回路と、

検出されたデータ・ドライブを駆動するため前記ピンの一つに選択的に電力を供給するための電力スイッチ回路と、

を含むコンピュータ装置。

#### 【0041】

（2）第1項に記載のコンピュータであって、前記データ・ドライブ検出回路は、第1のピン上の所定の信号を検出する回路と、

前記第1のピン上の前記所定の信号の検出に応じて第2のピンに電流を供給する回路と、前記第2のピン上の電圧に応じて所定の出力を生成する回路と、

を含むコンピュータ。

（3）第1項に記載のコンピュータであって、前記所定の信号は接地電圧信号であるコンピュータ。

（4）第1項に記載のコンピュータであって、前記第2のピンは、プリンタが前記入力／出力ポートに接続される場合は接地に、前記入力／出力ポートがデータ・ドライブに結合される場合はロードに接続されるコンピュータ。

（5）第1項に記載のコンピュータであって、前記入力／出力ポート・コネクタがパラレル・ポート・コネクタであるコンピュータ。

（6）第2項に記載のコンピュータであって、前記データ・ドライブ検出回路は、更に

10

20

30

40

50

前記第2のピンへの電流をディスエーブルする回路を含むコンピュータ。

(7) 第6項に記載のコンピュータであって、電流をディスエーブルする前記回路は、所定時間後に前記第2のピンへの電流をディスエーブルする回路を含むコンピュータ。

(8) 第1項に記載のコンピュータであって、オーバーヒーティングに応じて前記データ・ドライブへの電力をディスエーブルする熱保護回路を更に含むコンピュータ。

【0042】

(9) コンピュータであって、

処理回路と、

接続されたデータ・ドライブ又はプリンタのいずれか一方に信号を転送するための複数の入力／出力ピンを有する、前記処理回路に結合されるパラレル・ポート・コネクタと、

データ・ドライブ又はプリンタのいずれが前記パラレル・ポート・コネクタに接続されているかを検出するためのデータ・ドライブ検出回路と、

10

検出されたデータ・ドライブを駆動するため前記ピンの一つに選択的に電力を供給し、検出されたプリンタへの電力をディスエーブルする電力スイッチ回路

とを含むコンピュータ。

【0043】

(10) 第9項に記載のコンピュータであって、前記データ検出回路は、前記第1のピン及び基準電圧に結合される第1の演算増幅器と、第2のピン及び前記基準電圧に結合される第2の演算増幅器とを含み、前記第1の演算増幅器の出力は前記第1のピンが所定の電圧に結合されているかどうかに応じ、前記第2の演算増幅器の出力は前記第2のピンが電圧レールに結合されているかどうかに応答するコンピュータ。

20

(11) 第10項に記載のコンピュータであって、前記データ・ドライブ検出回路は、前記第2のピンに電流を供給するための回路を更に含むコンピュータ。

(12) 第11項に記載のコンピュータであって、前記第2のピンに電流を供給するための回路は、所定時間の期間、前記第2のピンに電流を供給するための回路を含むコンピュータ。

(13) 第9項に記載のコンピュータであって、前記電力スイッチ回路はトランジスタを含むコンピュータ。

(14) 第9項に記載のコンピュータであって、前記データ・ドライブ検出回路の出力に応じて、データ・ドライブが前記パラレル・ポート・コネクタに結合されるかどうかを表す信号を生成するロジックを更に含むコンピュータ。

30

(15) 複数のピンを有する入力／出力ポート・コネクタに結合されるデバイスに選択的に電力を供給する回路であって、

前記入力／出力ポート・コネクタへの前記デバイスの接続を検出するためのデバイス検出回路と、

前記入力／出力ポート・コネクタの第1のピンに結合されるパワー・レールを前記デバイスが有するかどうかを判定するためのデバイス識別回路と、

前記デバイス識別回路に応じてデバイスを駆動するため前記第1のピンに選択的に電力を供給するための電力スイッチ回路

とを含む回路。

40

(16) 第15項に記載の電力供給回路であって、前記デバイス検出回路は、第2のピン上の接地信号に応答する回路を含む電力供給回路。

(17) 第15項に記載の電力供給回路であって、前記識別回路は、前記第1のピンがパワー・レールに結合されるかどうかに応じて識別信号を生成するための回路を含む電力供給回路。

(18) 第17項に記載の電力供給回路であって、識別信号を生成するため前記回路は、前記第1のピンに電流を供給するための回路を含む電力供給回路。

(19) 第17項に記載の電力供給回路であって、識別信号を生成するため前記回路は、所定の期間、前記第1のピンに電流を供給する回路を含む電力供給回路。

(20) 第15項に記載の電力供給回路であって、前記電力スイッチ回路は、前記識別

50

信号に応じて前記第1のピンに電流を流すための回路を含む電力供給回路。

(21) 第18項に記載の電力供給回路であって、前記電力スイッチ回路は、前記識別信号によって駆動される制御ゲートを有するトランジスタを含む電力供給回路。

【0044】

(22) 複数のピンを有する入力／出力ポート・コネクタに結合されるデバイスに電力を供給する方法であって、

入力／出力ポート・コネクタへのデバイスの接続を検出し、

前記入力／出力ポート・コネクタの第1のピンに結合されるパワー・レールをデバイスが有するかどうかを判定し、

前記判定工程に応じて、デバイスを駆動するため前記第1のピンに電源を結合する工程を含む方法。

10

(23) 第22項に記載の方法であって、前記検出工程は、第2のピンが接地に接続されるかどうかを検出する工程を含む方法。

(24) 第22項に記載の方法であって、前記判定工程は、第1のピンがパワー・レール結合されるかどうかに応じて識別信号を生成する工程を含む方法。

(25) 第24項に記載の方法であって、前記生成工程は、前記第1のピンに電流を供給する工程を含む方法。

(26) 第24項に記載の方法であって、前記生成工程は、所定の時間の期間、前記第1のピンに電流を供給する工程を含む方法。

(27) 第22項に記載の方法であって、前記結合工程は、前記識別信号に応じて第1のピンに電源を結合する工程を含む方法。

20

【0045】

(28) パラレル・ポート・コネクタ48を介してパラレル・ポート・フロッピー・ドライブに電力を供給することを含むノートブック・コンピュータ10。コンピュータ10は、プリンタ又はフロッピー・ドライブのいずれがパラレル・ポート・コネクタ48に接続されるかを検出する電力スイッチ回路30を有する。フロッピー・ドライブ24が接続される場合、パラレル・ポート・コネクタ48を介して電力がイネーブルされる。プリンタが接続される場合は、パラレル・ポート・コネクタ48を介して電力がディスエーブルされる。

【図面の簡単な説明】

30

【図1】外部データ・ドライブに結合されるコンピュータの斜視図。

【図2】図1のコンピュータのブロック図。

【図3】図2の電力スイッチ回路のブロック図。

【図4】入力／出力ポートを介して外部データ・ドライブを駆動する回路の第1の実施例の略図。

【図5】入力／出力ポートを介して外部データ・ドライブを駆動する回路の第2の実施例の略図。

【符号の説明】

10 コンピュータ

24 フロッピー・ドライブ

40

30 電力スイッチ回路

48 パラレル・ポート・コネクタ

【図1】

【図2】

【図3】

【図4】

【 図 5 】

---

フロントページの続き

(72)発明者 フワンソー チョイ

アメリカ合衆国カリフォルニア州クパーチノ, ビスタ コート 20256

(72)発明者 マンポ クウォン

アメリカ合衆国カリフォルニア州サノウゼ, アーズレイ コート 1140

(72)発明者 セオン エス.シン

アメリカ合衆国カリフォルニア州クパーチノ, シダー スプリング コート 11656

審査官 内田 正和

(56)参考文献 特開平10-074120 (JP, A)

米国特許第05408669 (US, A)

特開昭63-018485 (JP, A)

特開平02-028816 (JP, A)

特開昭63-206112 (JP, A)

特開昭57-025123 (JP, A)

特開平06-038357 (JP, A)

特開平07-311634 (JP, A)

特開平07-210273 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 1/26

G06F 3/00