(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6224520号

(P6224520)

(45) 発行日 平成29年11月1日(2017.11.1)

(24) 登録日 平成29年10月13日(2017.10.13)

(51) Int.Cl.

H05K 3/28 (2006.01)

F 1

H05K 3/28

B

請求項の数 4 (全 53 頁)

(21) 出願番号 特願2014-105400 (P2014-105400)

(22) 出願日 平成26年5月21日 (2014.5.21)

(65) 公開番号 特開2015-216332 (P2015-216332A)

(43) 公開日 平成27年12月3日 (2015.12.3)

審査請求日 平成28年3月31日 (2016.3.31)

(31) 優先権主張番号 特願2013-107932 (P2013-107932)

(32) 優先日 平成25年5月22日 (2013.5.22)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2013-125178 (P2013-125178)

(32) 優先日 平成25年6月14日 (2013.6.14)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2013-131839 (P2013-131839)

(32) 優先日 平成25年6月24日 (2013.6.24)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005980

三菱製紙株式会社

東京都墨田区両国二丁目10番14号

(72) 発明者 豊田 裕二

東京都墨田区両国2丁目10番14号三菱

製紙株式会社内

(72) 発明者 後閑 寛彦

東京都墨田区両国2丁目10番14号三菱

製紙株式会社内

(72) 発明者 川合 宣行

東京都墨田区両国2丁目10番14号三菱

製紙株式会社内

(72) 発明者 中川 邦弘

東京都墨田区両国2丁目10番14号三菱

製紙株式会社内

最終頁に続く

(54) 【発明の名称】配線基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板を有し、回路基板の両表面にソルダーレジスト層を有し、ソルダーレジスト層から接続パッドの一部が露出している配線基板の製造方法において、

(A1) 絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板の両表面に、厚さの異なる第一ソルダーレジスト層が形成される工程、

(C2) 第二面の第一ソルダーレジスト層に対して、後工程である工程(D1)において現像される領域以外の部分が露光される工程、

(B) 第一面において、薄膜化処理液によって、接続パッドの厚さ以下になるまで、非露光部の第一ソルダーレジスト層が薄膜化されて、接続パッドの一部を露出する工程、

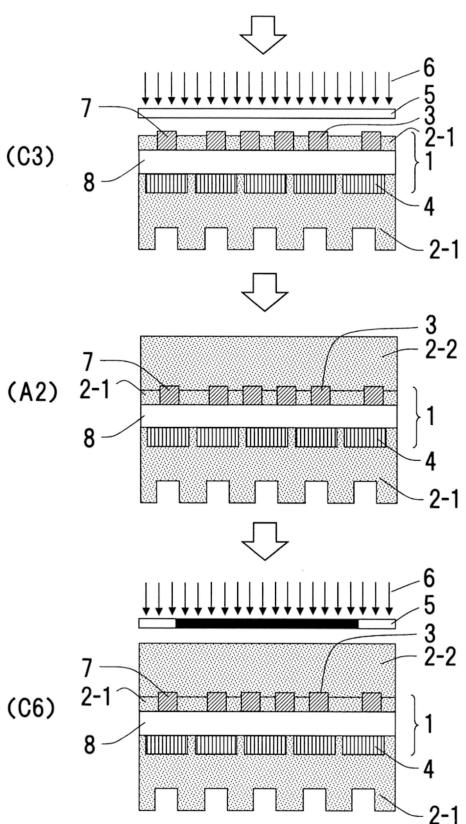

(C3) 第一面の第一ソルダーレジスト層に対して、工程(B)において薄膜化された領域部分が露光される工程、

(A2) (C3) 工程まで完了した回路基板の第一面の第一ソルダーレジスト層上に、第二ソルダーレジスト層が形成される工程、

(C6) 第一面の第二ソルダーレジスト層に対して、後工程である工程(B3)において薄膜化される領域以外の部分が露光される工程、

(B3) 第一面において、薄膜化処理液によって、接続パッドが露出しない範囲で、非露光部の第二ソルダーレジスト層が薄膜化される工程、

(C7) 第一面の第二ソルダーレジスト層に対して、後工程である工程(D1)において

10

20

現像される領域以外の部分が露光される工程、

(D 1) 第一面の非露光部の第二ソルダーレジスト層及び第二面の非露光部の第一ソルダーレジスト層が、現像液によって除去される工程、

を含むことを特徴とする配線基板の製造方法。

**【請求項 2】**

工程 (C 3) 及び工程 (C 7) における露光が、酸素雰囲気下での非接触露光方式によつて行われる請求項 1 記載の配線基板の製造方法。

**【請求項 3】**

工程 (C 3) 及び工程 (C 7) における露光量が、工程 (C 6) における露光量の 1 倍以上 5 倍以下である請求項 1 又は 2 記載の配線基板の製造方法。

10

**【請求項 4】**

工程 (B) 及び工程 (B 3) におけるソルダーレジスト層の薄膜化処理が、薄膜化処理面を上にして行われる請求項 1 ~ 3 のいずれかに記載の配線基板の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は配線基板の製造方法に関し、より詳しくは、半導体チップや他のプリント配線板等の電子部品を接続するための複数の接続パッドを有する配線基板の製造方法に関する。

**【背景技術】**

**【0002】**

各種電気機器内部の配線基板は、その片面又は両表面に、絶縁層と、絶縁層の表面に形成された導体配線とを有する回路基板を有している。また、配線基板の回路基板表面には、半田付け不要な導体配線に半田が付着しないようにするために、半田付けされない部分全面にソルダーレジスト層が形成されている。このソルダーレジスト層は、導体配線の酸化防止、電気絶縁及び外部環境からの保護という役割を果たしている。

**【0003】**

また、配線基板上に半導体チップ等の電子部品を搭載する場合、配線基板の表面には、半導体チップ、他のプリント配線板等の電子部品と接続するための多数の接続パッドが形成されている。接続パッドは、回路基板表面の導体配線の全体又は一部をソルダーレジスト層から露出させることにより作製されている。近年、この接続パッドの高密度化が進んでおり、配置される接続パッド同士のピッチが狭くなつていて、例えば 50  $\mu\text{m}$  以下の狭ピッチもある。

20

**【0004】**

高密度に配置された接続パッドに電子部品を搭載する方法として、フリップチップ接続による方法がある。フリップチップ接続とは、配線基板上に設けた電子部品接続用接続パッドの一部を電子部品の電極端子の配置に対応した並びに露出させ、この電子部品接続用接続パッドの露出部と電子部品の電極端子とを対向させ、半田バンプを介して電気的に接続することをいう。

30

**【0005】**

接続パッドには、ソルダーレジスト層を部分的に除去し、接続パッド表面の全体又は一部を露出させている SMD (S o l d e r M a s k D e f i n e d) 構造と、ソルダーレジスト層を部分的に除去し、接続パッドを完全に露出させている NSMD (N o n S o l d e r M a s k D e f i n e d) 構造がある。

40

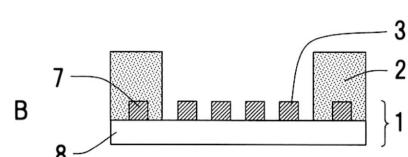

**【0006】**

図 1 A は、SMD 構造を有する配線基板の一例を示す概略断面図である。絶縁層 8 表面に導体配線 7 と導体配線の一部である接続パッド 3 が設けられた回路基板 1 表面上にソルダーレジスト層 2 が形成されている。接続パッド 3 はその周辺近傍がソルダーレジスト層 2 によって被覆されている。そのため、機械的衝撃による接続パッド 3 の剥れや接続パッド 3 からの引き出し配線におけるネック部の断線が起こりにくいという利点がある。その反

50

面、電子部品の電極端子とこれに対応する接続パッド3との電気的な接続を確実に固定するため、接続パッド3の露出面に形成する接合部に必要な半田量を確保する必要があり、接続パッド3が大型化してしまうため、電子部品の小型化及び高性能化に伴う接続パッド3の高密度化の要求に対応することが難しくなってきている。

#### 【0007】

図1Bは、NSMD構造を有する配線基板の一例を示す概略断面図である。絶縁層8表面に導体配線7と導体配線の一部である接続パッド3が設けられた回路基板1表面にソルダーレジスト層2が形成されている。ソルダーレジスト層2の同一開口内に複数の接続パッド3が配置されていて、これらの接続パッド3はソルダーレジスト層2から露出している。NSMD構造では、接続パッド3は、その周辺近傍のソルダーレジスト層2が完全に除去され、接続パッド3の側面が完全に露出している。そのため、SMD構造と比較して、小さな接続パッド3でも接続パッド3と半田との接着強度を確保することができる。その反面、接続パッド3の側面が完全に露出することによって、接続パッド3と絶縁層8との間の接着強度が低下するおそれがある。また、狭ピッチで配置した接続パッド3では、後工程における無電解ニッケル／金めっきで、接続パッド3間で短絡が発生する場合や、接続パッド3上に半田バンプを配設しようとすると、溶融した半田が隣接する接続パッド3にまで流出し、接続パッド3間で短絡する場合がある。

#### 【0008】

接続パッドと絶縁層との間の接着強度の問題を解決するために、レーザー光照射によって回路基板表面に設けたソルダーレジスト層の一部に深さ0～15μm程度の開口部を形成することにより、接続パッド側面の一部がソルダーレジスト層から露出した構造をもつプリント配線板を製造する方法が提案されている（例えば、特許文献1参照）。特許文献1に記載された方法で得られたプリント配線板を用いることによって、ソルダーレジスト層の下部に存在する接続パッドを完全に露出させたプリント配線板と比較して、接続パッドと絶縁層との間の接着強度を向上させることが可能となる。

#### 【0009】

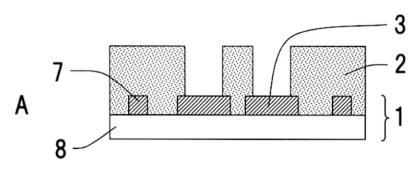

また、狭ピッチで配置した接続パッド3における短絡の問題を解決するために、隣接する接続パッド3間にソルダーレジスト層2が充填された配線基板を製造する方法が提案されている（例えば、特許文献2参照）。特許文献2の方法によると、図2に示すような、接続パッド3間にソルダーレジスト層2が充填され、かつ、充填されているソルダーレジスト層2の厚さが接続パッド3の厚さ以下であるNSMD構造を形成することができる。具体的には、回路基板1上にソルダーレジスト層2を形成し、ソルダーレジスト層2の厚さが接続パッド3の厚さ以下になるまで薄膜化される領域以外の部分を露光後、アルカリ水溶液である薄膜化処理液によって、接続パッド3の厚さ以下になるまで非露光部のソルダーレジスト層2を薄膜化する。これにより、接続パッド3の厚さ以下の部分と接続パッド3の厚さ超の部分を含む多段構造を有するソルダーレジスト層2が形成され、接続パッド3となる一部の導体配線が露出している配線基板を製造することができる。

#### 【0010】

通常、電子部品を搭載する配線基板では、裏面には外部接続用接続パッドが高密度で多数形成されている。外部接続用接続パッドも、回路基板裏面の導体配線の一部がソルダーレジスト層から露出することにより作製されている。この外部接続用接続パッドの露出部とマザーボード等の外部電気基板の導体配線とを対向させ、半田バンプを介して電気的に接続する。

#### 【0011】

回路基板の両面にソルダーレジスト層を形成する場合、接続パッド上のソルダーレジスト層の厚さは、接続パッドを含むその周囲の導体配線の密度によって変化する。例えば、導体配線の密度が小さい場合、導体配線間の隙間に充填されるソルダーレジスト層の量が多くなり、接続パッド上のソルダーレジスト層の厚さは薄くなる傾向がある。一方、導体配線の密度が大きい場合、導体配線間の隙間に充填されるソルダーレジスト層の量が少くなり、接続パッド上のソルダーレジスト層の厚さは厚くなる傾向がある。

10

20

30

40

50

## 【0012】

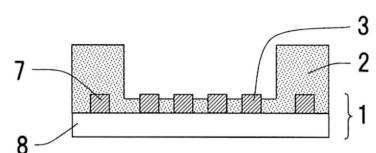

フリップチップ接続により電子部品を搭載する配線基板の場合、表面の電子部品接続用接続パッドを含むその周囲の導体配線の密度に比べ、裏面の外部接続用接続パッドを含むその周囲の導体配線の密度が大きい場合がある。そのため、裏面の外部接続用接続パッド上のソルダーレジスト層の厚さが、表面の電子部品接続用接続パッド上のソルダーレジスト層の厚さよりも厚くなる場合がある。薄膜化処理液によってソルダーレジスト層を薄膜化して接続パッドを露出させる方法において、両面同時に薄膜化しようとした場合、次のような問題が生じる場合があった。

## 【0013】

まず、表面のソルダーレジスト層2を電子部品接続用接続パッド3の厚さ以下になるまで薄膜化することを基準とした場合、裏面のソルダーレジスト層2も同時に表面と同じ量だけ薄膜化されるが、裏面のソルダーレジスト層2が表面のソルダーレジスト層2よりも厚いことから、裏面の外部接続用接続パッド4上にソルダーレジスト層2が残渣として残り、この残渣によって電気的絶縁不良が発生するという問題が生じる場合があった（図3）。

10

## 【0014】

反対に、裏面のソルダーレジスト層2を外部接続用接続パッド4の厚さ以下になるまで薄膜化することを基準とした場合、表面のソルダーレジスト層2も同時に裏面と同じ量だけ薄膜化されるが、裏面のソルダーレジスト層2が表面のソルダーレジスト層2よりも厚いことから、表面の電子部品接続用接続パッド3間を充填しているソルダーレジスト層2の厚さが、所望の厚さよりも薄くなってしまい、隣接する電子部品接続用接続パッド3間の短絡が発生するという問題が生じる場合があった。

20

## 【0015】

ところで、回路基板上に電子部品をフリップチップ接続したプリント配線板では、電子部品と回路基板との接続信頼性を確保するために、電子部品と回路基板との空隙をアンダーフィル（封止樹脂）で充填して補強する。補強効果を確保するためには、電子部品と回路基板の空隙に充分な量のアンダーフィルを充填しなければならない。しかしながら、特許文献1によって得られるプリント配線板を使用してフリップチップ接続を行った場合、補強効果を確保するために充分なアンダーフィルを充填した際に、アンダーフィルが電子部品と回路基板の空隙から周囲へ溢れてしまい、電気的な作動に悪影響を及ぼす場合があった。そのため、アンダーフィルが周囲に溢れてしまうことを防止するために、ダム構造を有するプリント配線板が提案されている（例えば、特許文献3～5参照）。

30

## 【0016】

特許文献3には、導体回路を有する回路基板上にソルダーレジスト層を形成した後、部分露光を行い、その後未露光部を現像処理することで、ソルダーレジスト層から接続パッド上部を部分的に露出させる開口部を形成し、次に2回目の部分露光を行い、その後2回目の部分露光の未露光部をデスマニア処理によって薄膜化し、ダム形状を形成する方法が開示されている。この方法によるソルダーレジスト層の開口部は、SMD構造であるため、電子部品の電極端子とこれに対応する接続パッドとの電気的な接続を確実に固定することが難しく、接続パッドと半田ボールの電気的な接続が不十分となる場合があった。また、この方法によるダム構造の形成はデスマニア処理によって行われているため、ソルダーレジスト層が粗面化されることでソルダーレジスト層の強度が低下してしまい、プリント配線板の信頼性が充分に確保できない場合があった。

40

## 【0017】

特許文献4には、導体回路を有する回路基板上にソルダーレジスト層を形成した後、部分露光を行い、その後未露光部を現像処理することで、ソルダーレジスト層から接続パッドを完全に露出させる開口部を形成し、次に2回目のソルダーレジストを形成した後、1回目の部分露光領域よりも1回り大きな未露光部が発生する2回目の部分露光を行い、その後未露光部を現像することによってダム形状を形成する方法が開示されている。この方法によるソルダーレジスト層の開口部は、NSMD構造であり、接続パッドはその周辺近

50

傍のソルダーレジスト層が完全に除去され、接続パッドの側面が完全に露出することによって、接続パッドと絶縁層との間の接着強度が低下するおそれがある。

【0018】

特許文献5には、導体回路を有する回路基板上にソルダーレジスト層を形成した後、部分露光工程を行い、その後未露光部のソルダーレジスト層を薄膜化することでソルダーレジスト層に開口部とダム形状を形成する方法が開示されている。この方法によるソルダーレジスト層の開口部は、SMD構造であり、接続パッドはその周辺近傍がソルダーレジスト層に被覆されているため、電子部品の電極端子とこれに対応する接続パッドとの電気的な接続を確実に固定することが難しく、接続パッドと半田ボールの電気的な接続が不十分となる場合があった。

10

【先行技術文献】

【特許文献】

【0019】

【特許文献1】特許3346263号公報

【特許文献2】国際公開第2012/043201号パンフレット

【特許文献3】特開2012-238668号公報

【特許文献4】特開平05-226505号公報

【特許文献5】特開2011-77191号公報

【発明の概要】

【発明が解決しようとする課題】

20

【0020】

本発明の課題は、絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板を有し、回路基板の両表面にソルダーレジスト層を有し、ソルダーレジスト層から接続パッドの一部が露出している配線基板の製造方法において、配線基板の両表面で、ソルダーレジスト層から露出している接続パッド間で電気的な短絡がなく、露出している接続パッド上にソルダーレジスト層の残渣が残らない配線基板の製造方法を提供することである。また、本発明の他の課題は、接続パッドと絶縁層及び接続パッドと半田との接着強度が高く、アンダーフィル流出による電気的作動不良が無く、ソルダーレジスト層の強度が高いプリント配線板を得ることができるプリント配線板の製造方法を提供することである。

30

【課題を解決するための手段】

【0021】

本発明者らは、上記課題を解決するために鋭意検討した結果、下記発明によって、上記課題を解決できることを見出した。

【0022】

(1) 絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板を有し、回路基板の両表面にソルダーレジスト層を有し、ソルダーレジスト層から接続パッドの一部が露出している配線基板の製造方法において、

(A) 絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板の両表面に、厚さの異なるソルダーレジスト層が形成される工程、

40

(C1) 第二面のソルダーレジスト層よりも厚さが薄い第一面のソルダーレジスト層に対して、後工程である工程(B)において薄膜化される領域以外の部分が露光される工程、

(C2) 第二面のソルダーレジスト層に対して、後工程である工程(D)において現像される領域以外の部分が露光される工程、

(B) 第一面において、薄膜化処理液によって、接続パッドの厚さ以下になるまで、非露光部のソルダーレジスト層が薄膜化されて、接続パッドの一部を露出する工程、

(C3) 第一面のソルダーレジスト層に対して、工程(B)において薄膜化された領域部分が露光される工程、

(D) 第二面の非露光部のソルダーレジスト層が、現像液によって除去される工程、

を含むことを特徴とする配線基板の製造方法。

50

## 【0023】

(2) 絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板を有し、回路基板の両表面にソルダーレジスト層を有し、ソルダーレジスト層から接続パッドの一部が露出している配線基板の製造方法において、

(A) 絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板の両表面に、厚さの異なるソルダーレジスト層が形成される工程、

(C1) 第二面のソルダーレジスト層よりも厚さが薄い第一面のソルダーレジスト層に対して、後工程である工程(B1)において薄膜化される領域以外の部分が露光される工程、

(C2) 第二面のソルダーレジスト層に対して、後工程である工程(D)において現像される領域以外の部分が露光される工程、

(B1) 第一面において、薄膜化処理液によって、接続パッドが露出しない範囲で、非露光部のソルダーレジスト層が薄膜化される工程、

(C4) 第一面のソルダーレジスト層に対して、後工程である工程(B2)において薄膜化される領域以外の部分が露光される工程、

(B2) 第一面において、薄膜化処理液によって、接続パッドの厚さ以下になるまで、非露光部のソルダーレジスト層が薄膜化されて、接続パッドの一部を露出する工程、

(C5) 第一面のソルダーレジスト層に対して、工程(B2)において薄膜化された領域部分が露光される工程、

(D) 第二面の非露光部のソルダーレジスト層が、現像液によって除去される工程、

を含むことを特徴とする配線基板の製造方法。

## 【0024】

(3) 絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板を有し、回路基板の両表面にソルダーレジスト層を有し、ソルダーレジスト層から接続パッドの一部が露出している配線基板の製造方法において、

(A1) 絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板の両表面に、厚さの異なる第一ソルダーレジスト層が形成される工程、

(C1) 第二面の第一ソルダーレジスト層よりも厚さが薄い第一面の第一ソルダーレジスト層に対して、後工程である工程(B)において薄膜化される領域以外の部分が露光される工程、

(C2) 第二面の第一ソルダーレジスト層に対して、後工程である工程(D1)において現像される領域以外の部分が露光される工程、

(B) 第一面において、薄膜化処理液によって、接続パッドの厚さ以下になるまで、非露光部の第一ソルダーレジスト層が薄膜化されて、接続パッドの一部を露出する工程、

(C3) 第一面の第一ソルダーレジスト層に対して、工程(B)において薄膜化された領域部分が露光される工程、

(A2) (C3) 工程まで完了した回路基板の第一面の第一ソルダーレジスト層上に、第二ソルダーレジスト層が形成される工程、

(C6) 第一面の第二ソルダーレジスト層に対して、後工程である工程(D1)において現像される領域以外の部分が露光される工程、

(D1) 第一面の非露光部の第二ソルダーレジスト層及び第二面の非露光部の第一ソルダーレジスト層が、現像液によって除去される工程、

を含むことを特徴とする配線基板の製造方法。

## 【0025】

(4) 絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板を有し、回路基板の両表面にソルダーレジスト層を有し、ソルダーレジスト層から接続パッドの一部が露出している配線基板の製造方法において、

(A1) 絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板の両表面に、厚さの異なる第一ソルダーレジスト層が形成される工程、

(C1) 第二面の第一ソルダーレジスト層よりも厚さが薄い第一面の第一ソルダーレジス

10

20

30

40

50

ト層に対して、後工程である工程（B）において薄膜化される領域以外の部分が露光される工程、

（C2）第二面の第一ソルダーレジスト層に対して、後工程である工程（D）において現像される領域以外の部分が露光される工程、

（B）第一面において、薄膜化処理液によって、接続パッドの厚さ以下になるまで、非露光部の第一ソルダーレジスト層が薄膜化されて、接続パッドの一部を露出する工程、

（C3）第一面の第一ソルダーレジスト層に対して、工程（B）において薄膜化された領域部分が露光される工程、

（D）第二面の非露光部の第一ソルダーレジスト層が、現像液によって除去される工程、

（A2）（D）工程まで完了した回路基板の第一面の第一ソルダーレジスト層上に、第二ソルダーレジスト層が形成される工程、

（C6）第一面の第二ソルダーレジスト層に対して、後工程である工程（D2）において現像される領域以外の部分が露光される工程、

（D2）第一面の非露光部の第二ソルダーレジスト層が、現像液によって除去される工程

、

を含むことを特徴とする配線基板の製造方法。

【0026】

（5）絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板を有し、回路基板の両表面にソルダーレジスト層を有し、ソルダーレジスト層から接続パッドの一部が露出している配線基板の製造方法において、

20

（A1）絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板の両表面に、厚さの異なる第一ソルダーレジスト層が形成される工程、

（C2）第二面の第一ソルダーレジスト層に対して、後工程である工程（D1）において現像される領域以外の部分が露光される工程、

（B）第一面において、薄膜化処理液によって、接続パッドの厚さ以下になるまで、非露光部の第一ソルダーレジスト層が薄膜化されて、接続パッドの一部を露出する工程、

（C3）第一面の第一ソルダーレジスト層に対して、工程（B）において薄膜化された領域部分が露光される工程、

（A2）（C3）工程まで完了した回路基板の第一面の第一ソルダーレジスト層上に、第二ソルダーレジスト層が形成される工程、

30

（C6）第一面の第二ソルダーレジスト層に対して、後工程である工程（B3）において薄膜化される領域以外の部分が露光される工程、

（B3）第一面において、薄膜化処理液によって、接続パッドが露出しない範囲で、非露光部の第二ソルダーレジスト層が薄膜化される工程、

（C7）第一面の第二ソルダーレジスト層に対して、後工程である工程（D1）において現像される領域以外の部分が露光される工程、

（D1）第一面の非露光部の第二ソルダーレジスト層及び第二面の非露光部の第一ソルダーレジスト層が、現像液によって除去される工程、

を含むことを特徴とする配線基板の製造方法。

【0027】

40

・（6）工程（C1）の前に工程（C2）を行う上記（1）～（4）のいずれかに記載の配線基板の製造方法。

・（7）工程（C1）と工程（C2）を同時に行う上記（1）～（4）のいずれかに記載の配線基板の製造方法。

【0028】

（8）工程（C3）における露光が、酸素雰囲気下での非接触露光方式によって行われる上記（1）、（3）、（4）のいずれかに記載の配線基板の製造方法。

（9）工程（C3）及び工程（C7）における露光が、酸素雰囲気下での非接触露光方式によって行われる上記（5）記載の配線基板の製造方法。

（10）工程（C4）及び工程（C5）における露光が、酸素雰囲気下での非接触露光方

50

式によって行われる上記(2)に記載の配線基板の製造方法。

【0029】

(11) 工程(C3)における露光量が、工程(C1)における露光量の1倍以上5倍以下である上記(1)、(3)、(4)、(8)のいずれかに記載の配線基板の製造方法。

(12) 工程(C3)及び工程(C7)における露光量が、工程(C6)における露光量の1倍以上5倍以下である上記(5)又は(9)記載の配線基板の製造方法。

(13) 工程(C4)及び工程(C5)における露光量が、工程(C1)における露光量の1倍以上5倍以下である上記(2)又は(10)に記載の配線基板の製造方法。

【0030】

(14) 工程(B)におけるソルダーレジスト層の薄膜化処理が、薄膜化処理面を上にして行われる上記(1)、(3)、(4)、(8)、(11)のいずれかに記載の配線基板の製造方法。 10

(15) 工程(B)及び工程(B3)におけるソルダーレジスト層の薄膜化処理が、薄膜化処理面を上にして行われる上記(5)、(9)、(12)のいずれかに記載の配線基板の製造方法。

(16) 工程(B1)及び工程(B2)におけるソルダーレジスト層の薄膜化処理が、薄膜化処理面を上にして行われる上記(2)、(10)、(13)のいずれかに記載の配線基板の製造方法。

【発明の効果】

【0031】

本発明によれば、絶縁層と、絶縁層の表面に形成された接続パッドとを両表面に有する回路基板を有し、回路基板の両表面にソルダーレジスト層を有し、ソルダーレジスト層から接続パッドの一部が露出している配線基板の製造方法において、配線基板の両表面で、ソルダーレジスト層から露出している接続パッド間で電気的な短絡がなく、また、露出している接続パッド上にソルダーレジスト層の残渣が残らない配線基板の製造方法を提供することができる。また、本発明によれば、接続パッドと絶縁層及び接続パッドと半田との接着強度が高く、アンダーフィル流出による電気的作動不良が無く、ソルダーレジスト層の強度が高いプリント配線板を得ることができるプリント配線板の製造方法を提供することができる。

【図面の簡単な説明】

【0032】

【図1】配線基板の一例を示す概略断面図である。

【図2】配線基板の一例を示す概略断面図である。

【図3】配線基板の一例を示す概略断面図である。

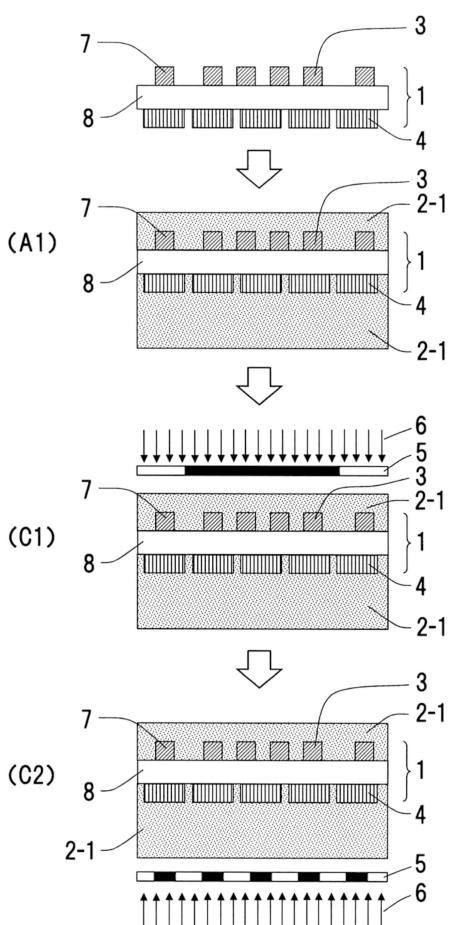

【図4-1】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図4-2】本発明の配線基板の製造方法の一例を示す断面工程図である。

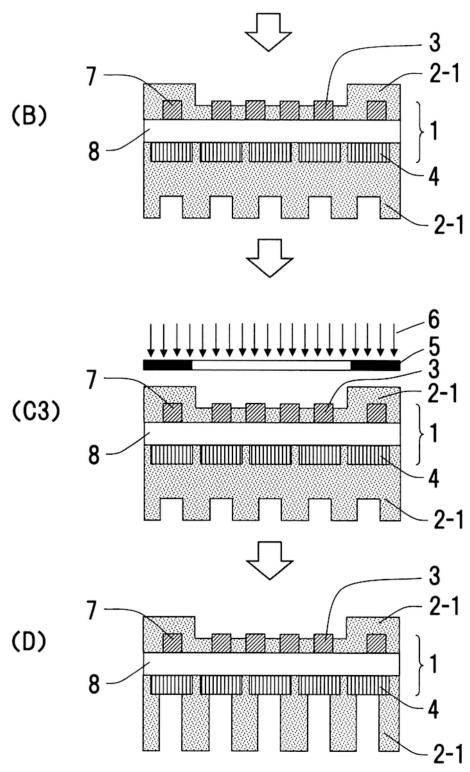

【図5-1】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図5-2】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図5-3】本発明の配線基板の製造方法の一例を示す断面工程図である。

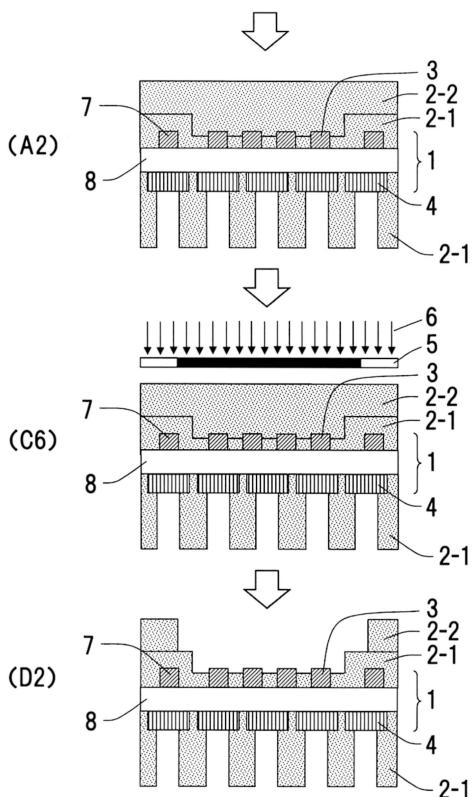

【図6-1】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図6-2】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図6-3】本発明の配線基板の製造方法の一例を示す断面工程図である。

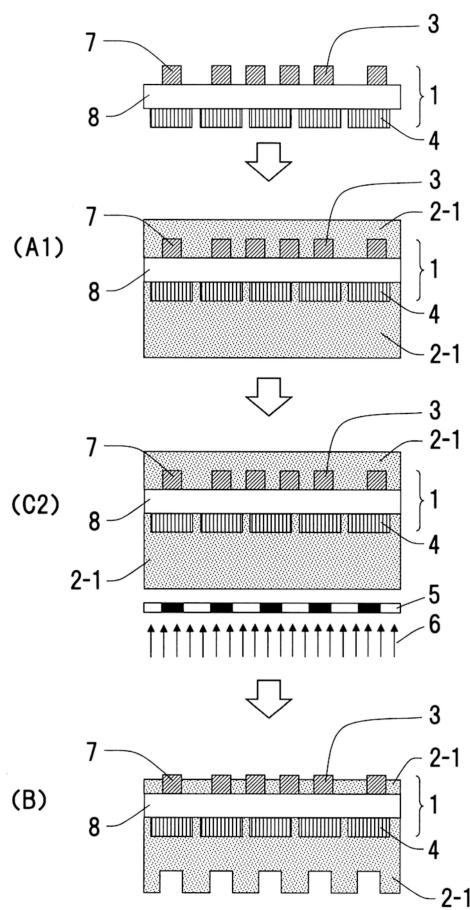

【図7-1】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図7-2】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図7-3】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図8-1】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図8-2】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図8-3】本発明の配線基板の製造方法の一例を示す断面工程図である。

【図9】本発明によって製造できる配線基板の一例を示す概略断面図である。

【図10】本発明によって製造できる配線基板の一例を示す概略断面図である。

10

20

30

40

50

【図11】本発明によって製造できる配線基板の一例を示す概略断面図である。

【図12】本発明によって製造できる配線基板の一例を示す概略断面図である。

【図13】多層回路基板の一例を示す概略断面図である。

【発明を実施するための形態】

【0033】

以下、本発明の配線基板の製造方法について詳細に説明する。

【0034】

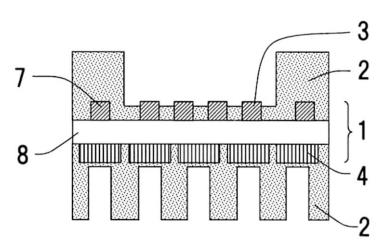

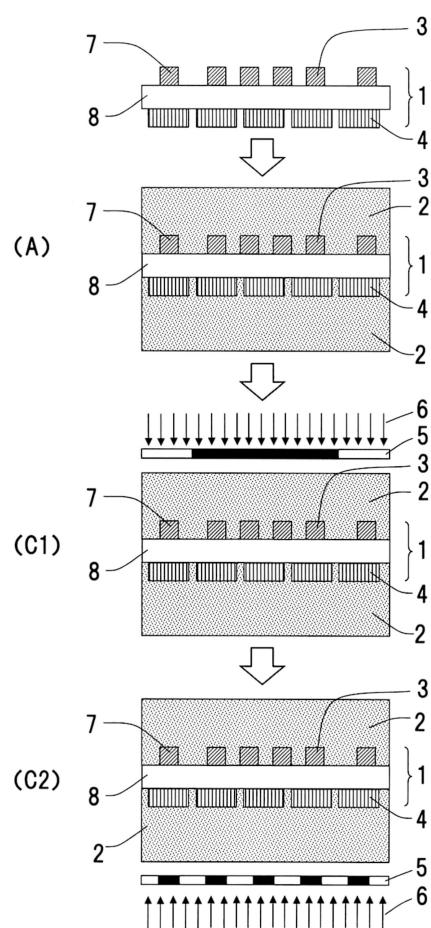

図4-1および図4-2は、配線基板の製造方法(1)の一例を示す断面工程図である。絶縁層8と、絶縁層8の表面に形成された導体配線7とを両表面に有する回路基板を準備する。導体配線7の一部は、接続パッド3及び4である。工程(A)では、回路基板1の両表面において、全面を覆うようにソルダーレジスト層2を形成する。第一面と第二面のソルダーレジスト層2の形成は、両表面同時でも、片面ずつでもよいが、形成するソルダーレジスト層の厚さに応じて、過剰に熱硬化しないような加熱条件を設定する必要がある。両表面におけるソルダーレジスト層2の厚さは異なっており、厚さの薄い方が「第一面」であり、厚さの厚い方が「第二面」である。両表面において、ソルダーレジスト層2を同じ条件で形成した場合、ソルダーレジスト層2の厚さは、各面の接続パッド3及び4を含む導体配線7の密度によって変化する。図4-1では、上側の第一面に比べて、下側の第二面の方が導体配線7の密度が大きく、第二面の導体配線7上のソルダーレジスト層2の厚さが、第一面の導体配線7上のソルダーレジスト層2の厚さよりも厚くなる。なお、電子部品を搭載する配線基板の場合、表面の電子部品接続用接続パッド3を含むその周囲の導体配線7の密度に比べ、裏面の外部接続用接続パッド4を含むその周囲の導体配線7の密度が大きい場合があり、表面が第一面であり、裏面が第二面である。

【0035】

工程(C1)では、第一面のソルダーレジスト層2に対して、後工程である工程(B)において薄膜化される領域以外の部分を露光する。工程(C2)では、第二面のソルダーレジスト層2に対して、後工程である工程(D)において現像される領域以外の部分を露光する。ソルダーレジスト層2の露光された部分は、ソルダーレジストが光重合し、薄膜化工程及び現像工程に対して耐性を有するようになる。

【0036】

工程(B)では、第一面において、薄膜化処理液によって、接続パッド3の厚さ以下になるまで、非露光部のソルダーレジスト層2を薄膜化して、接続パッド3の一部を露出させる。電子部品を搭載する配線基板の場合、この工程(B)において露出した接続パッド3が電子部品接続用接続パッド3として使用される。工程(B)では、第二面の非露光部のソルダーレジスト層2も同時に薄膜化されるが、第一面の接続パッド3上のソルダーレジスト層2よりも第二面の接続パッド4上のソルダーレジスト層2の方が厚いため、接続パッド4上にソルダーレジスト層2の残渣が残る。

【0037】

工程(C3)では、第一面のソルダーレジスト層2に対して、工程(B)で薄膜化された領域部分を露光する。ソルダーレジスト層2の露光された部分は、ソルダーレジストが光重合し、現像工程に対して耐性を有するようになる。

【0038】

工程(D)では、第二面において、非露光部のソルダーレジスト層2を、現像液によって除去し、接続パッド4の一部を露出させる。工程(D)により、接続パッド4上に残っていたソルダーレジスト層2の残渣が除去される。電子部品を搭載する配線基板の場合、この工程(D)において露出した接続パッド4が外部接続用接続パッド4として使用される。第一面のソルダーレジスト層2において、工程(B)で薄膜化された領域部分は、工程(D)の前に行われる工程(C3)において露光され、現像工程に対する耐性を有しているので、現像液によって除去されない。

【0039】

配線基板の製造方法(1)では、工程(C1)の露光領域を任意の形状に変化させるこ

10

20

30

40

50

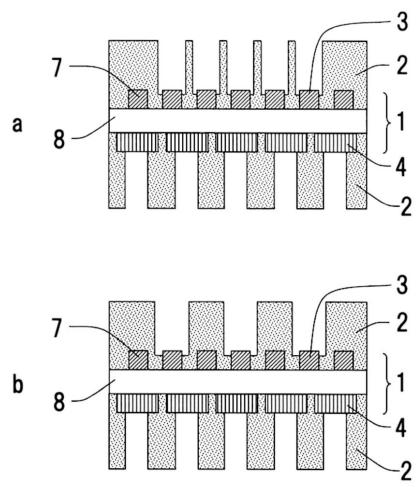

とが可能であり、露光領域の変更により、例えば、図9に示す断面形状の配線基板を作製することが可能である。図9のaでは、第一面の接続パッド3の間にソルダーレジスト層2の凸部が形成されている。図9のbでは、第一面において、ソルダーレジスト層2から露出した接続パッド3とソルダーレジスト層2で被覆されている導体配線7が交互に並んでいる。

#### 【0040】

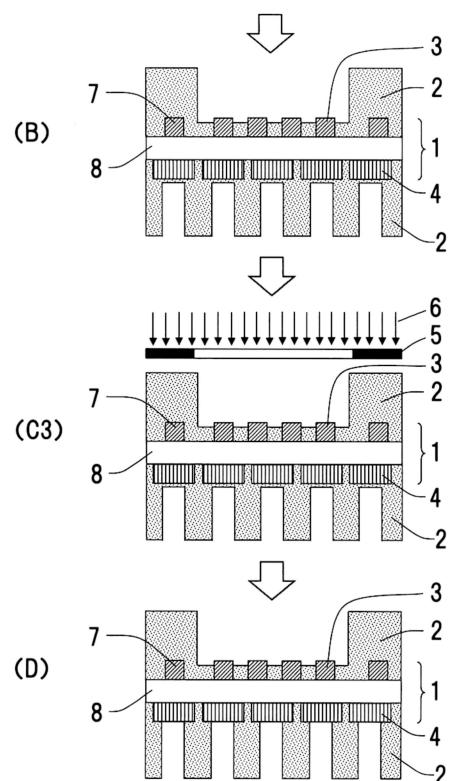

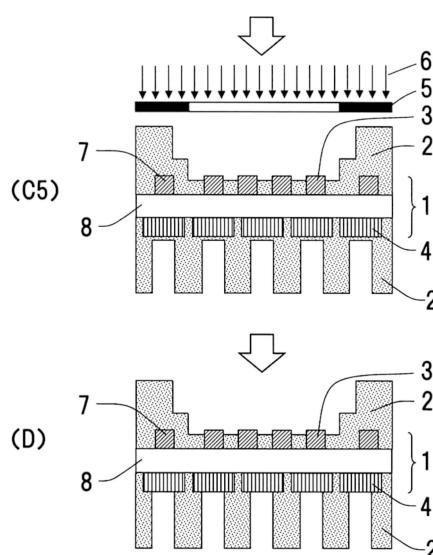

図5-1、図5-2および図5-3は、配線基板の製造方法(2)の一例を示す断面工程図である。配線基板の製造方法(1)との違いは、第一面において、ソルダーレジスト層2の露光工程と薄膜化工程がそれぞれ一回ずつ追加されている点である。フリップチップ接続により電子部品を配線基板に搭載する場合、電子部品と配線基板の熱膨張係数の差によって、熱衝撃が加わった際、接続部に応力が集中し、接続部の変形や破壊が起こることがある。接続部へ応力が集中するのを防ぎ、接続信頼性を向上させるために、電子部品と配線基板の間がアンダーフィルと呼ばれる樹脂組成物で封止されるのが一般的である。配線基板の製造方法(2)によって、電子部品と配線基板の間に充填するアンダーフィルを堰き止めるためのダム構造を有する二段構造のソルダーレジスト層を形成することができる。

10

#### 【0041】

工程(A)では、回路基板1の両表面において、全面を覆うようにソルダーレジスト層2を形成する。工程(C1)では、第一面のソルダーレジスト層2に対して、後工程である工程(B1)において薄膜化される領域以外の部分を露光する。工程(C2)では、第二面のソルダーレジスト層2に対して、後工程である工程(D)において現像される領域以外の部分を露光する。

20

#### 【0042】

工程(B1)では、第一面において、薄膜化処理液によって、接続パッド3が露出しない範囲で、非露光部のソルダーレジスト層2を薄膜化する。工程(B1)では、第二面の非露光部のソルダーレジスト層2も同時に薄膜化される。

#### 【0043】

工程(C4)では、第一面のソルダーレジスト層2に対して、後工程である工程(B2)において薄膜化される領域以外の部分を露光する。

#### 【0044】

30

工程(B2)では、第一面において、薄膜化処理液によって、接続パッド3の厚さ以下になるまで、非露光部のソルダーレジスト層2を薄膜化して、接続パッド3の一部を露出させる。電子部品を搭載する配線基板の場合、この工程(B2)において露出した接続パッド3が電子部品接続用接続パッド3として使用される。工程(B2)では、第二面の非露光部のソルダーレジスト層2も同時に薄膜化されるが、第一面の接続パッド3上のソルダーレジスト層2よりも第二面の接続パッド4上のソルダーレジスト層2の方が厚いため、接続パッド4上にソルダーレジスト層2の残渣が残る。

#### 【0045】

工程(C5)では、第一面のソルダーレジスト層2に対して、工程(B2)で薄膜化された領域部分を露光する。

40

#### 【0046】

工程(D)では、第二面において、非露光部のソルダーレジスト層2を、現像液によって除去し、接続パッド4の一部を露出させる。工程(D)により、接続パッド4上に残っていたソルダーレジスト層2の残渣が除去される。電子部品を搭載する配線基板の場合、この工程(D)において露出した接続パッド4が外部接続用接続パッド4として使用される。

#### 【0047】

配線基板の製造方法(2)では、工程(C4)の露光領域を任意の形状に変化させることができ可能であり、露光領域の変更により、例えば、図10に示す断面形状の配線基板を作製することが可能である。図10のcでは、第一面の接続パッド3の間にソルダーレジス

50

ト層 2 の凸部が形成されている。図 10 の d では、第一面において、ソルダーレジスト層 2 から露出した接続パッド 3 とソルダーレジスト層 2 で被覆されている導体配線 7 が交互に並んでいる。

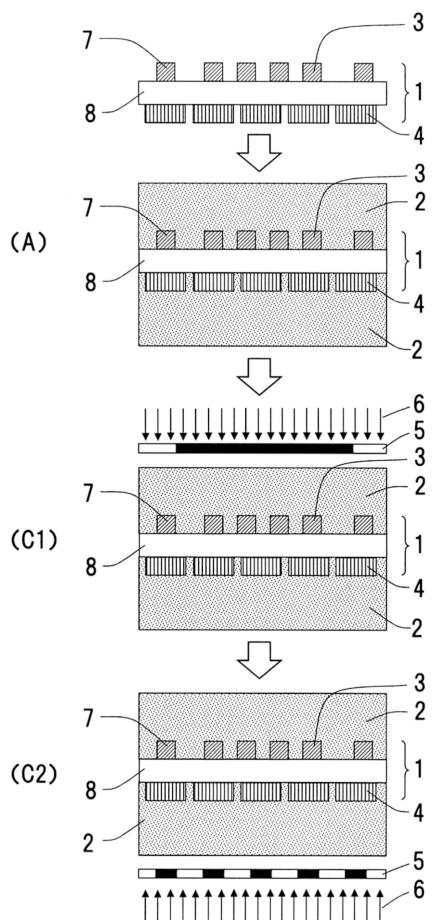

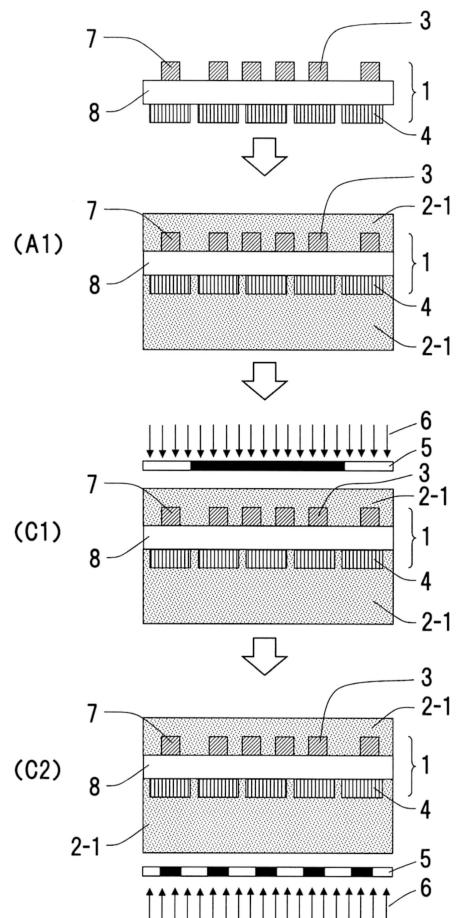

【 0 0 4 8 】

図 6 - 1、図 6 - 2 および図 6 - 3 は、配線基板の製造方法 (3) の一例を示す断面工程図である。配線基板の製造方法 (2) との違いは、第一面のソルダーレジスト層が第一ソルダーレジスト層 2 - 1 と第二ソルダーレジスト層 2 - 2 から構成されている点である。配線基板の製造方法 (3) では、第一面の非露光部の第一ソルダーレジスト層 2 - 1 の厚さを接続パッド 3 の厚さ以下になるまで薄膜化した後、第一ソルダーレジスト層 2 - 1 の表面上に第二ソルダーレジスト層 2 - 2 を形成し、露光した後、非露光部の第二ソルダーレジスト層 2 - 2 を現像処理する。これによって、配線基板の製造方法 (2) を用いた場合と同じく、電子部品と配線基板の間に充填するアンダーフィルを堰き止めるためのダム構造を有する二段構造のソルダーレジスト層を形成することができる。

【 0 0 4 9 】

工程 (A 1) では、回路基板 1 の第一面と第二面において、厚さの異なる第一ソルダーレジスト層 2 - 1 を形成する。第一面と第二面の第一ソルダーレジスト層 2 - 1 の形成は、両表面同時でも、片面ずつでもよいが、形成するソルダーレジスト層の厚さに応じて、過剰に熱硬化しないような加熱条件を設定する必要がある。

【 0 0 5 0 】

工程 (C 1) では、第二面の第一ソルダーレジスト層 2 - 1 よりも厚さが薄い第一面の第一ソルダーレジスト層 2 - 1 に対して、後工程である工程 (B) において薄膜化される領域以外の部分を露光する。工程 (C 2) では、第二面の第一ソルダーレジスト層 2 - 1 に対して、後工程である工程 (D 1) において現像される領域以外の部分を露光する。

【 0 0 5 1 】

工程 (B) では、第一面において、薄膜化処理液によって、接続パッド 3 の厚さ以下になるまで、非露光部の第一ソルダーレジスト層 2 - 1 を薄膜化して、接続パッド 3 の一部を露出させる。工程 (B) では、第二面の非露光部の第一ソルダーレジスト層 2 - 1 も同時に薄膜化される。しかし、第一面の接続パッド 3 上の第一ソルダーレジスト層 2 - 1 よりも第二面の接続パッド 4 上の第一ソルダーレジスト層 2 - 1 の方が厚いため、接続パッド 4 上に第一ソルダーレジスト層 2 - 1 の残渣が残る。

【 0 0 5 2 】

工程 (C 3) では、第一面の第一ソルダーレジスト層 2 - 1 に対して、工程 (B) において薄膜化された領域部分を露光する。

【 0 0 5 3 】

工程 (A 2) では、工程 (C 3) まで完了した回路基板の第一面の第一ソルダーレジスト層 2 - 1 上に、第二ソルダーレジスト層 2 - 2 を形成する。この時、第一面の第二ソルダーレジスト層 2 - 2 にかかる加熱条件を調整して、第二面の第一ソルダーレジスト層 2 - 1 の非露光部が過剰に熱硬化しないようにする。

【 0 0 5 4 】

工程 (C 6) では、第一面の第二ソルダーレジスト層 2 - 2 に対して、後工程である工程 (D 1) において現像される領域以外の部分を露光する。

【 0 0 5 5 】

工程 (D 1) では、第一面の非露光部の第二ソルダーレジスト層 2 - 2 及び第二面の非露光部の第一ソルダーレジスト層 2 - 1 を、現像液によって除去し、接続パッド 3 及び 4 の一部を露出させる。工程 (D 1) により、接続パッド 4 上に残っていた第一ソルダーレジスト層 2 - 1 の残渣が除去される。電子部品を搭載する配線基板の場合、この工程 (D 1) において露出した接続パッド 3 が電子部品接続用接続パッド 3 として使用され、接続パッド 4 が外部接続用接続パッド 4 として使用される。

【 0 0 5 6 】

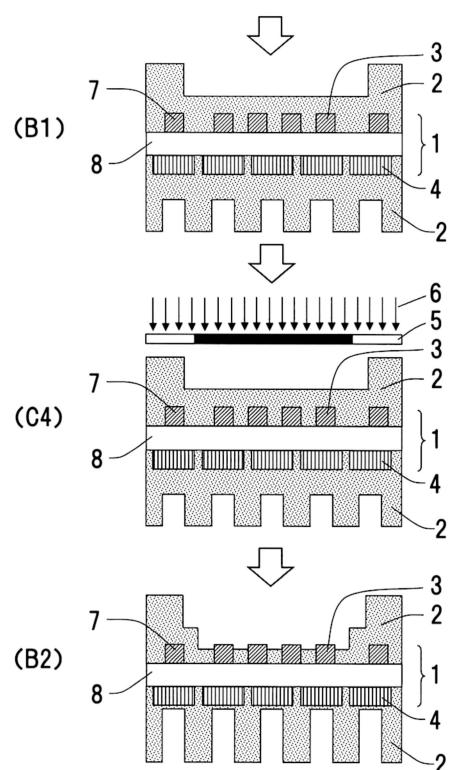

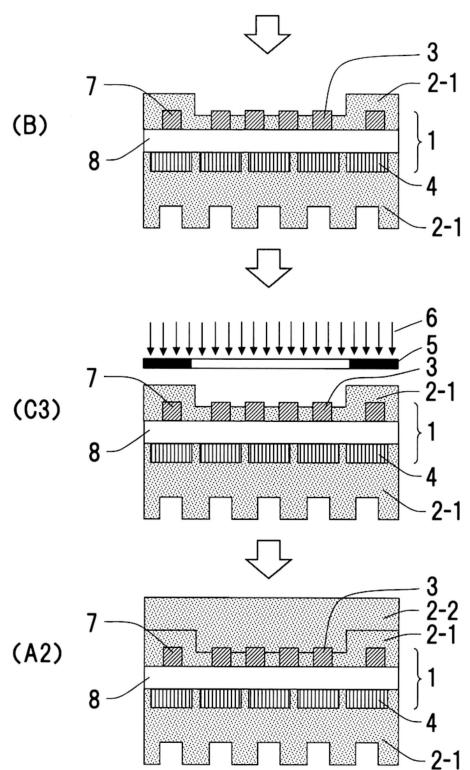

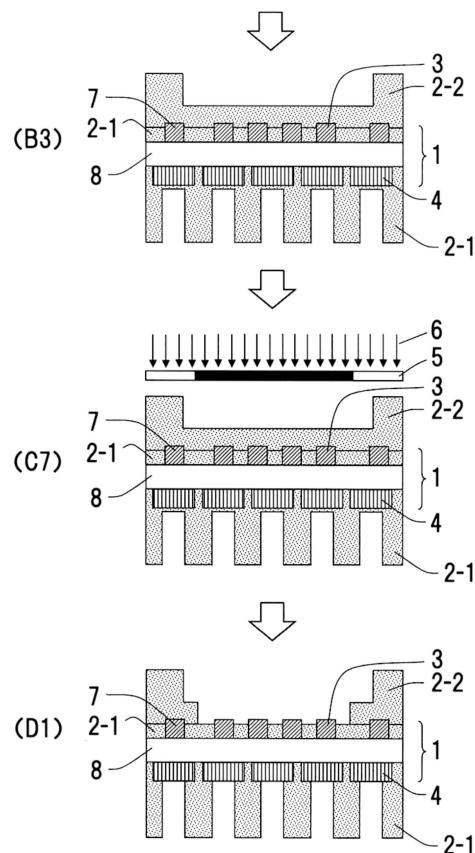

図 7 - 1、図 7 - 2 および図 7 - 3 は、配線基板の製造方法 (4) の一例を示す断面工

10

20

30

40

50

程図である。配線基板の製造方法(3)との違いは、第一面の第二ソルダーレジスト層2-2を形成する前に、第二面の第一ソルダーレジスト層2-1を現像液によって除去する点である。先に第二面の非露光部の第一ソルダーレジスト層2-1を現像液によって除去することによって、第一面の第二ソルダーレジスト層2-2を形成する際に、第二面の非露光部の第一ソルダーレジスト層2-1が同時に加熱されて過剰に熱硬化しないように加熱条件を調整する必要がなくなる。配線基板の製造方法(4)では、配線基板の製造方法(2)及び(3)を用いた場合と同じく、電子部品と配線基板の間に充填するアンダーフィルを堰き止めるためのダム構造を有する二段構造のソルダーレジスト層を形成することができる。

## 【0057】

10

工程(A1)では、回路基板1の第一面と第二面において、厚さの異なる第一ソルダーレジスト層2-1を形成する。工程(C1)では、第二面の第一ソルダーレジスト層2-1よりも厚さが薄い第一面の第一ソルダーレジスト層2-1に対して、後工程である工程(B)において薄膜化される領域以外の部分を露光する。工程(C2)では、第二面の第一ソルダーレジスト層2-1に対して、後工程である工程(D)において現像される領域以外の部分を露光する。

## 【0058】

20

工程(B)では、第一面において、薄膜化処理液によって、接続パッド3の厚さ以下になるまで、非露光部の第一ソルダーレジスト層2-1を薄膜化して、接続パッド3の一部を露出させる。工程(B)では、第二面の非露光部の第一ソルダーレジスト層2-1も同時に薄膜化される。しかし、第一面の接続パッド3上の第一ソルダーレジスト層2-1よりも第二面の接続パッド4上の第一ソルダーレジスト層2-1の方が厚いため、接続パッド4上に第一ソルダーレジスト層2-1の残渣が残る。

## 【0059】

工程(C3)では、第一面の第一ソルダーレジスト層2-1に対して、工程(B)において薄膜化された領域部分を露光する。

## 【0060】

30

工程(D)では、第二面の非露光部の第一ソルダーレジスト層2-1を、現像液によって除去し、接続パッド4の一部を露出させる。工程(D)により、接続パッド4上に残っていた第一ソルダーレジスト層2-1の残渣が除去される。電子部品を搭載する配線基板の場合、この工程(D)において露出した接続パッド4が外部接続用接続パッド4として使用される。

## 【0061】

工程(A2)では、工程(D)まで完了した回路基板の第一面の第一ソルダーレジスト層2-1上に、第二ソルダーレジスト層2-2を形成する。

## 【0062】

工程(C6)では、第一面の第二ソルダーレジスト層2-2に対して、後工程である工程(D2)において現像される領域以外の部分を露光する。

## 【0063】

40

工程(D2)では、第一面の非露光部の第二ソルダーレジスト層2-2を、現像液によって除去し、接続パッド3の一部を露出させる。電子部品を搭載する配線基板の場合、この工程(D2)において露出した接続パッド3が電子部品接続用接続パッド3として使用される。

## 【0064】

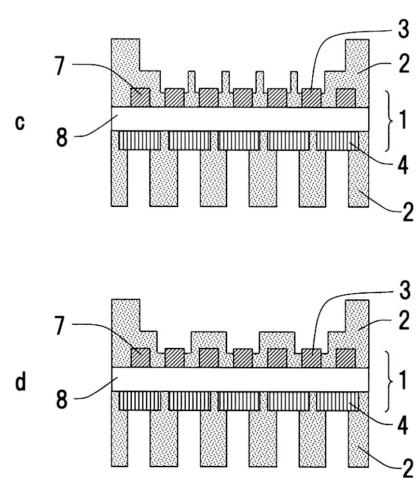

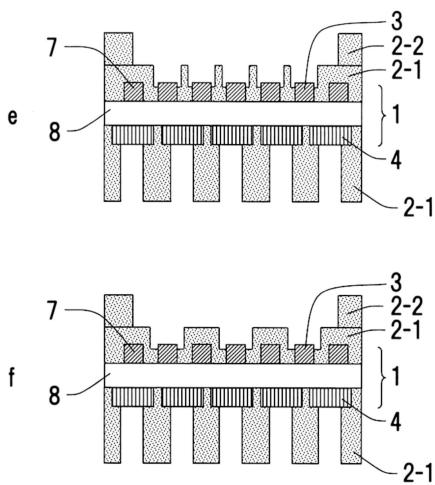

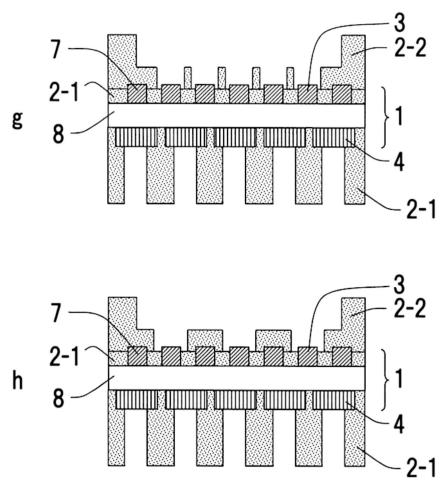

配線基板の製造方法(3)及び(4)では、工程(C1)の露光領域を任意の形状に変化させることができあり、露光領域の変更により、例えば、図11に示す断面形状の配線基板を作製することが可能である。図11のeでは、第一面の接続パッド3の間に第一ソルダーレジスト層2-1の凸部が形成されている。図11のfでは、第一ソルダーレジスト層2-1から露出した接続パッド3と第一ソルダーレジスト層2-1で被覆されている導体配線7が交互に並んでいる。

50

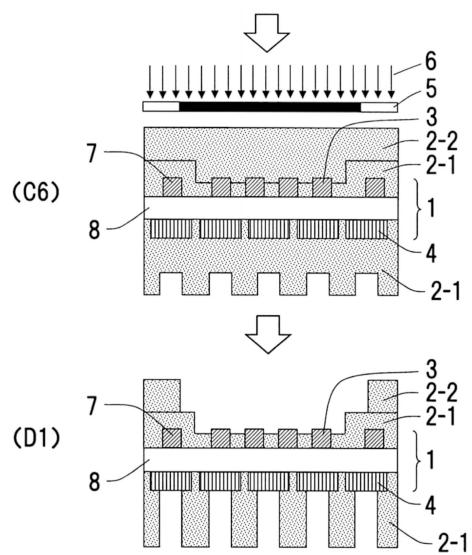

## 【0065】

図8-1、図8-2および図8-3は、配線基板の製造方法(5)の一例を示す断面工程図である。配線基板の製造方法(5)では、第一面において、第一ソルダーレジスト層2-1に露光を行う前に第一ソルダーレジスト層2-1の厚さを接続パッド3の厚さ以下になるまで薄膜化処理する。その後、第一ソルダーレジスト層2-1の表面上に第二ソルダーレジスト層2-2を形成し、露光した後、非露光部の第二ソルダーレジスト層2-2を薄膜化処理し、その後、再度露光を行い、残った非露光部の第二ソルダーレジスト層2-2を現像処理する。配線基板の製造方法(5)では、配線基板の製造方法(2)～(4)を用いた場合と同じく、電子部品と配線基板の間に充填するアンダーフィルを堰き止めるためのダム構造を有する二段構造のソルダーレジスト層を形成することができる。 10

## 【0066】

工程(A1)では、回路基板1の第一面と第二面において、厚さの異なる第一ソルダーレジスト層2-1を形成する。工程(C2)では、第二面の第一ソルダーレジスト層2-1に対して、後工程である工程(D1)において現像される領域以外の部分を露光する。

## 【0067】

工程(B)では、第一面において、薄膜化処理液によって、接続パッド3の厚さ以下になるまで、非露光部の第一ソルダーレジスト層2-1を薄膜化して、全ての接続パッド3の一部を露出させる。工程(B)では、第二面の非露光部の第一ソルダーレジスト層2-1も同時に薄膜化される。しかし、第一面の接続パッド3上の第一ソルダーレジスト層2-1よりも第二面の接続パッド4上の第一ソルダーレジスト層2-1の方が厚いため、接続パッド4上に第一ソルダーレジスト層2-1の残渣が残る。 20

## 【0068】

工程(C3)では、第一面の第一ソルダーレジスト層2-1に対して、工程(B)において薄膜化された領域部分を露光する。

## 【0069】

工程(A2)では、工程(C3)まで完了した回路基板の第一面の第一ソルダーレジスト層2-1上に、第二ソルダーレジスト層2-2を形成する。

## 【0070】

工程(C6)では、第一面の第二ソルダーレジスト層2-2に対して、後工程である工程(B3)において薄膜化される領域以外の部分を露光する。 30

## 【0071】

工程(B3)では、第一面において、薄膜化処理液によって、接続パッド3が露出しない範囲で、非露光部の第二ソルダーレジスト層2-2を薄膜化する。工程(B3)では、第二面の非露光部の第一ソルダーレジスト層2-1も同時に薄膜化される。しかし、接続パッド4上に第一ソルダーレジスト層2-1の残渣が残る場合がある。

## 【0072】

工程(C7)では、第一面の第二ソルダーレジスト層2-2に対して、後工程である工程(D1)において現像される領域以外の部分を露光する。

## 【0073】

工程(D1)では、第一面の非露光部の第二ソルダーレジスト層2-2及び第二面の非露光部の第一ソルダーレジスト層2-1を、現像液によって除去し、接続パッド3の一部を再び露出させ、同時に接続パッド4の一部を露出させる。工程(D1)により、接続パッド4上に残っていた第一ソルダーレジスト層2-1の残渣が除去される。電子部品を搭載する配線基板の場合、この工程(D1)において露出した接続パッド3が電子部品接続用接続パッド3として使用され、接続パッド4が外部接続用接続パッド4として使用される。 40

## 【0074】

配線基板の製造方法(5)では、工程(C7)の露光領域を任意の形状に変化させることが可能であり、露光領域の変更により、例えば、図12に示す断面形状の配線基板を作製することが可能である。図12のgでは、第一面の接続パッド3の間に第二ソルダーレ 50

ジスト層 2 - 2 の凸部が形成されている。図 12 の h では、第一ソルダーレジスト層 2 - 1 から露出した接続パッド 3 と第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 で被覆されている導体配線 7 が交互に並んでいる。

【 0 0 7 5 】

本発明に係わる回路基板 1 とは、絶縁層 8 と、絶縁層 8 の表面に形成された接続パッド 3 及び 4 を有する。絶縁層 8 の表面には、導体配線 7 が形成されていて、接続パッド 3 及び 4 は導体配線 7 の一部である。本発明に係わる配線基板は、回路基板 1 の両表面にソルダーレジスト層 2 を有し、ソルダーレジスト層 2 から接続パッド 3 及び 4 の一部が露出している。電子部品を搭載する配線基板の場合、表面に電子部品接続用接続パッド 3 を有し、裏面に外部接続用接続パッド 4 を有する。表面の電子部品接続用接続パッド 3 と電子部品を接合し、裏面の外部接続用接続パッド 4 と外部電気基板の導体配線を接合する。

10

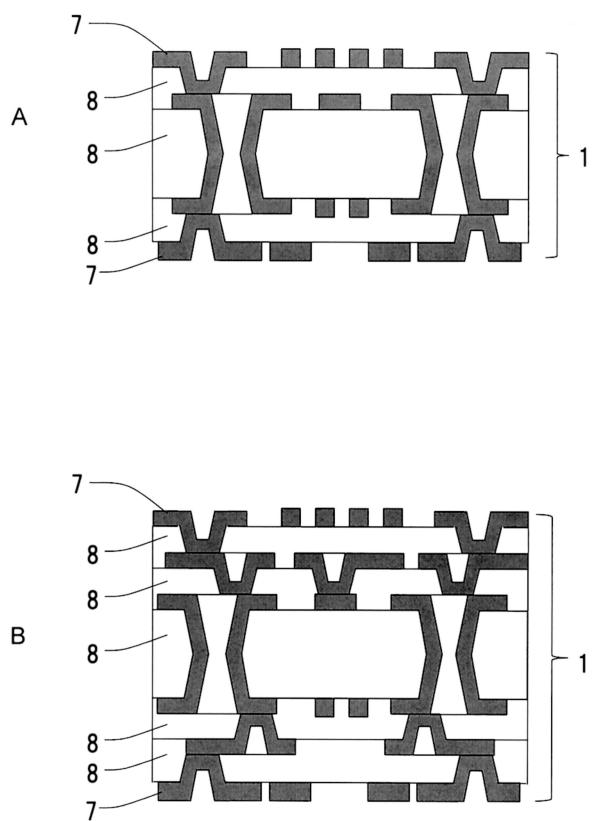

【 0 0 7 6 】

本発明に係わる回路基板は、例えば、導体配線が配設された絶縁基板にビルドアップ用の絶縁層や導体配線を交互に積層して作製される。図 13 A, B は、導体配線が配設された絶縁基板にビルドアップ用の絶縁層や導体配線を交互に積層して作製された回路基板の一例を示す概略断面図である。本発明の配線基板の製造方法の一例を示した断面工程図である図 4 - 1 ~ 図 8 - 3、本発明によって製造できる配線基板の一例を示す概略断面図である図 9 ~ 12 には、絶縁層 8 を一層有し、絶縁層 8 の両表面に形成された導体配線 7 を有する回路基板 1 が記載されているが、本発明の配線基板の製造方法に使用される回路基板 1 としては、図 13 A, B のように、導体配線が配設された絶縁基板にビルドアップ用の絶縁層や導体配線を交互に積層して作製され、絶縁層 8 と、絶縁層 8 の表面に形成された導体配線 7 とを両表面に有する回路基板 1 が含まれる。絶縁基板としては、例えば、ガラスクロスにビスマレイミドトリアジン樹脂やエポキシ樹脂等の熱硬化性樹脂を含浸させた電気絶縁材料等からなる樹脂製基板が挙げられる。ビルドアップ用の絶縁層としては、例えば、絶縁基板と同様にガラスクロスに熱硬化性樹脂を含浸させた電気絶縁材料、エポキシ樹脂等の熱硬化性樹脂に酸化ケイ素等の無機フィラーを分散させた電気絶縁材料等が挙げられる。導体配線は、例えば、サブトラクティブ法、セミアディティブ法、アディティブ法等によって形成される。サブトラクティブ法では、例えば、絶縁層上に銅層を形成した後にエッチングレジスト層を形成し、露光、現像、エッチング、レジスト剥離を実施して、導体配線を形成する。セミアディティブ法では、絶縁層の表面に無電解銅めっきにより電解銅めっき用の下地金属層を設ける。次に、導体配線に対応した開口を有するめっきレジスト層を形成し、電解銅めっきによって露出した下地金属層の表面に電解銅めっき層を形成する。その後、めっきレジスト層を剥離し、露出した下地金属層をフラッシュエッチングで除去することによって導体配線を形成する。

20

【 0 0 7 7 】

電子部品を搭載する配線基板の場合、配線基板の表面の接続パッドは、電子部品と接続するための接続用パッドである。電子部品は、この接続パッドと半田バンプを介して電気的に接続されることにより、配線基板にフリップチップ実装される。ソルダーレジスト層との密着性を向上させるために、接続パッド表面を粗面化処理することもできるし、カップリング剤処理することもできる。配線基板の裏面の接続パッドは、外部接続するための接続用パッドである。半田バンプを介して、この接続パッドとマザーボード等の外部電気基板の導体配線を電気的に接続されることにより、マザーボードにフリップチップ実装される。

30

【 0 0 7 8 】

本発明に係わるソルダーレジストとしては、アルカリ現像型のソルダーレジストが使用できる。また、1液性、2液性、どちらの液状レジストであってもよく、ドライフィルム状レジストであってもよい。ソルダーレジストは、例えば、アルカリ可溶性樹脂、単官能アクリルモノマー、多官能アクリルモノマー、光重合開始剤、エポキシ樹脂、無機フィラー等を含有してなる。

40

【 0 0 7 9 】

50

アルカリ可溶性樹脂としては、光硬化性と熱硬化性の両方の特性を持つアルカリ可溶性樹脂が挙げられ、例えば、ノボラック型エポキシ樹脂にアクリル酸を付加させてエポキシアクリレート化した樹脂の2級の水酸基に酸無水物を付加させた樹脂が挙げられる。多官能アクリルモノマーとしては、例えば、トリメチロールプロパントリアクリレート (Trimethylol Propane Triacrylate)、ジペンタエリスリトリールヘキサアクリレート (Di-pentaerythritol Hexaacrylate)、ペンタエリスリトリールトリアクリレート (Pentaerythritol Triacrylate) 等が挙げられる。光重合開始剤としては、2-メチル-1-(4-メチルチオフェニル)-2-モルフォリノプロパン-1-オン (2-Methyl-1-(4-Methylthiophenyl)-2-Morpholinopropan-1-one) 等が挙げられる。エポキシ樹脂は、硬化剤として用いられる。アルカリ可溶性樹脂のカルボン酸と反応させることで架橋させ、耐熱性や耐薬品性の特性の向上を図っているが、カルボン酸とエポキシは常温でも反応が進むために、保存安定性が悪く、アルカリ現像型ソルダーレジストは一般的に使用前に混合する2液性の形態をとっている場合が多い。無機フィラーとしては、例えば、タルク、シリカ、硫酸バリウム、酸化チタン、酸化亜鉛等が挙げられる。

#### 【0080】

ソルダーレジスト層は、回路基板の両表面において、全面を覆うようにして形成される。ソルダーレジスト層の形成には、例えば、液状レジストであれば、スクリーン印刷法、ロールコート法、スプレー法、浸漬法、カーテンコート法、バーコート法、エアナイフ法、ホットメルト法、グラビアコート法、刷毛塗り法、オフセット印刷法を用いることができる。また、フィルム状レジストであれば、ラミネート法や真空ラミネート法が用いられる。

#### 【0081】

配線基板の製造方法(1)及び(2)における工程(A)で形成されるソルダーレジスト層2と、配線基板の製造方法(3)～(5)における工程(A1)で形成される第一ソルダーレジスト層2-1は、回路基板の両表面において厚さが異なっていて、厚さの薄い方が「第一面」であり、厚さの厚い方が「第二面」である。回路基板の両表面にソルダーレジスト層を形成させる際、両表面で同じ条件を設定するのが一般的である。これは、ソルダーレジストが熱硬化性を持つことに由来する。液状レジストの場合、塗布後に脱溶媒のための加熱乾燥が必要となるため、各表面で塗布量が異なると、各表面で乾燥条件を変更しなければならないが、その際に過剰に熱硬化しないような条件を設定しなければならない。また、ドライフィルム状レジストの場合、ラミネート時に加熱が必要となるため、各表面で厚さが違うドライフィルム状レジストを使用すると、各表面でラミネート時の加熱条件を変えなければならないが、その際に過剰に熱硬化しないような条件を設定しなければならない。このように各表面におけるソルダーレジスト層の厚さ、加熱乾燥条件等を変えるのではなく、両表面におけるソルダーレジスト層の種類、厚さ、加熱乾燥条件等を同条件にした方が、作業工程を簡易にすることができます。

#### 【0082】

回路基板の両表面にソルダーレジスト層を同条件で形成した場合、ソルダーレジスト層の厚さは、各面の接続パッドを含むその周囲の導体配線の密度によって変化する。例えば、電子部品を搭載する配線基板において、裏面の外部接続用接続パッドがエリアアレイ型に配列されている場合、表面の電子部品接続用接続パッドを含むその周囲の導体配線の密度に比べ、裏面の外部接続用接続パッドを含むその周囲の導体配線の密度が大きくなる。その結果、裏面の外部接続用接続パッド上のソルダーレジスト層の厚さは、表面の電子部品接続用接続パッド上のソルダーレジスト層の厚さよりも厚くなる。この場合、表面が第一面であり、裏面が第二面である。

#### 【0083】

本発明に係わるソルダーレジスト層が薄膜化される工程とは、薄膜化処理液によって非露光部のソルダーレジスト層成分をミセル化させるミセル化処理(薄膜化処理)、次にミ

セル除去液によってミセルを除去するミセル除去処理を含む工程である。さらに、除去しきれなかったミセルや残存している薄膜化処理液及びミセル除去液を水洗によって洗い流す水洗処理、水洗水を除去する乾燥処理を含んでもよい。

【0084】

薄膜化処理（ミセル化処理）とは、薄膜化処理液によって、非露光部のソルダーレジスト層成分をミセル化し、このミセルを薄膜化処理液に対して不溶化する処理である。

【0085】

本発明に係わる薄膜化処理液には、アルカリ水溶液を使用することができる。薄膜化処理液として使用できるアルカリ水溶液としては、アルカリ金属ケイ酸塩（Alkali Metal Silicate）、アルカリ金属水酸化物（Alkali Metal Hydroxide）、アルカリ金属リン酸塩（Alkali Metal Phosphate）、アルカリ金属炭酸塩（Alkali Metal Carbonate）、アンモニウムリン酸塩、アンモニウム炭酸塩等の無機アルカリ性化合物の水溶液；モノエタノールアミン、ジエタノールアミン、トリエタノールアミン、メチルアミン、ジメチルアミン、エチルアミン、ジエチルアミン、トリエチルアミン、シクロヘキシリルアミン、テトラメチルアンモニウムヒドロキシド（Tetramethylammonium Hydroxide、TMAH）、テトラエチルアンモニウムヒドロキシド、トリメチル-2-ヒドロキシエチルアンモニウムヒドロキサイド（コリン、Choline）等の有機アルカリ性化合物の水溶液が挙げられる。アルカリ金属としては、リチウム、ナトリウム、カリウム等が挙げられる。上記無機アルカリ性化合物及び有機アルカリ性化合物は、単独で用いてもよいし、複数組み合わせて用いてもよい。無機アルカリ性化合物と有機アルカリ性化合物を組み合わせて用いてもよい。

【0086】

また、ソルダーレジスト層表面をより均一に薄膜化するために、薄膜化処理液に、硫酸塩、亜硫酸塩を添加することもできる。硫酸塩又は亜硫酸塩としては、リチウム、ナトリウム又はカリウム等のアルカリ金属硫酸塩又は亜硫酸塩、マグネシウム、カルシウム等のアルカリ土類金属硫酸塩又は亜硫酸塩が挙げられる。

【0087】

薄膜化処理液としては、これらの中でも特に、アルカリ金属炭酸塩、アルカリ金属リン酸塩、アルカリ金属水酸化物、アルカリ金属ケイ酸塩から選ばれる無機アルカリ性化合物、及び、TMAH（テトラメチルアンモニウムヒドロキシド）、コリンから選ばれる有機アルカリ性化合物のうち少なくともいずれか1種を含み、該無機アルカリ性化合物及び有機アルカリ性化合物の含有量が3～25質量%である薄膜化処理液が、表面をより均一に薄膜化できるため、好適に使用できる。3質量%未満では、薄膜化する処理でムラが発生しやすくなる場合がある。また、25質量%を超えると、無機アルカリ性化合物の析出が起こりやすく、液の経時安定性、作業性に劣る場合がある。アルカリ性化合物の含有量は5～20質量%がより好ましく、7～15質量%がさらに好ましい。薄膜化処理液のpHは10以上とすることが好ましい。また、界面活性剤、消泡剤、溶剤等を適宜添加することもできる。

【0088】

ソルダーレジスト層の薄膜化においては、ソルダーレジスト層中に含まれる薄膜化処理液に不溶な無機フィラーの存在が無視できない。無機フィラーのサイズはその種類にもよるが、ナノフィラーと呼ばれるサブミクロンオーダーのものから、大きいものでは数十ミクロンのものまで、ある程度の粒度分布を持って、層中に30～70質量%の含有量で存在している。薄膜化は、アルカリ性化合物がソルダーレジスト層中に浸透した後、ソルダーレジスト層成分のミセル化とミセル除去過程によって進行するが、不溶性の無機フィラーの存在により、アルカリ性化合物の浸透が抑制され、薄膜化速度が遅くなることがある。

【0089】

このような無機フィラーによるアルカリ性化合物の浸透阻害に対し、薄膜化処理液のp

10

20

30

40

50

Hは12.5以上とするのが良く、13.0以上とするのがさらに好ましい。薄膜化処理液のpHが高いほど、アルカリ性化合物が浸透した際のソルダーレジスト層の膨潤が大きくなり、無機フィラーによる浸透阻害の影響を受けにくくなる。

#### 【0090】

本発明において、薄膜化によって、第一面の接続パッドの一部を露出させる場合、この露出した接続パッドは電子部品接続用接続パッドとして使用できる。通常、接続パッド表面は粗面化され、そのアンカー効果によって接続パッドとソルダーレジスト層の密着性が向上し、長時間に渡って高い絶縁信頼性が維持される。従来のソルダーレジストパターン形成では、ソルダーレジスト層を除去して接続パッド表面を露出させる際、分散能力に優れた低濃度の炭酸ナトリウム水溶液を現像液として用いるのが一般的で、接続パッド表面にはソルダーレジスト層の残渣はほとんど発生しない。しかし、低濃度の炭酸ナトリウム水溶液を用いてソルダーレジスト層の薄膜化を行うと、面内均一に薄膜化することができず、面内ムラが発生する。

#### 【0091】

薄膜化処理液の温度は、15～35が好ましく、さらに好ましくは20～30である。温度が低すぎると、ソルダーレジスト層へのアルカリ性化合物の浸透速度が遅くなる場合があり、所望の厚さを薄膜化するのに長時間要する。一方、温度が高すぎると、ソルダーレジスト層成分のミセル化と同時にミセル除去過程が進行することにより、面内で膜厚ムラが発生しやすくなる場合があるため好ましくない。

#### 【0092】

薄膜化処理液による薄膜化処理では、浸漬処理、パドル処理、スプレー処理、ブラッシング、スクレーピング等の方法を用いることができるが、浸漬処理が好ましい。浸漬処理以外の処理方法は、薄膜化処理液中に気泡が発生しやすく、その発生した気泡が薄膜化中にソルダーレジスト層表面に付着して、膜厚が不均一となる場合がある。スプレー処理等を使用する場合には、気泡が発生しないように、スプレー圧をできるだけ小さくすることが好ましい。

#### 【0093】

薄膜化処理液による薄膜化処理の後には、薄膜化処理液に対して不溶化されたソルダーレジスト層成分のミセルを除去するミセル除去処理において、ミセル除去液をスプレーすることによって、一挙にミセルを溶解除去する。

#### 【0094】

ミセル除去液としては、水道水、工業用水、純水等を用いることができる。また、アルカリ金属炭酸塩、アルカリ金属リン酸塩、アルカリ金属ケイ酸塩から選ばれる無機アルカリ性化合物のうち少なくともいずれか1種を含むpH5～10の水溶液をミセル除去液として用いることによって、薄膜化処理液で不溶化されたソルダーレジスト層成分が再分散しやすくなる。ミセル除去液のpHが5未満の場合、ソルダーレジスト層成分が凝集し、不溶性のスラッジとなって、薄膜化したソルダーレジスト層表面に付着するおそれがある。一方、ミセル除去液のpHが10を超えた場合、ソルダーレジスト層成分のミセル化とミセル除去過程が同時に促進され、面内で膜厚ムラが発生しやすくなることがある。また、ミセル除去液は、硫酸、リン酸、塩酸などを用いて、pHを調整することができる。

#### 【0095】

ミセル除去処理におけるスプレーの条件について説明する。スプレーの条件（温度、時間、スプレー圧）は、薄膜化処理されるソルダーレジスト層の溶解速度に合わせて適宜調整される。具体的には、処理温度は10～50が好ましく、より好ましくは22～50である。水溶液の温度が10未満ではソルダーレジスト層成分の溶解不良が起こり、粗面化された接続パッド表面にソルダーレジスト層の残渣が残りやすい場合がある。一方、50を超えると、水溶液の蒸発や連続運転での温度管理の問題、装置設計上の制約が発生する場合があり好ましくない。また、スプレー圧は0.01～0.5MPaとするのが好ましく、より好ましくは0.1～0.3MPaがより好ましい。ミセル除去液の供給流量は、ソルダーレジスト層1cm<sup>2</sup>当たり0.030～1.0L/minが好ましく、

10

20

30

40

50

0.050～1.0 L/min がより好ましく、0.10～1.0 L/min がさらに好ましい。供給流量がこの範囲であると、薄膜化後のソルダーレジスト層表面に不溶解成分を残すことなく、面内略均一にミセルを除去することができる。ソルダーレジスト層 1 cm<sup>2</sup>当たりの供給流量が 0.030 L/min 未満では、ソルダーレジスト層の不溶解成分が残る場合がある。一方、供給流量が 1.0 L/min を超えると、供給のために必要なポンプなどの部品が巨大になり、大掛かりな装置が必要となる場合がある。さらに、1.0 L/min を超えた供給量では、ソルダーレジスト層成分の溶解除去に与える効果が変わらなくなることがある。

#### 【0096】

配線基板の製造方法(1)及び(2)における工程(A)、配線基板の製造方法(3)～(5)における工程(A1)及び(A2)において、第一面に形成されたソルダーレジスト層2、第一ソルダーレジスト層2-1、第二ソルダーレジスト層2-2の厚さと、配線基板の製造方法(1)、(3)～(5)における工程(B)、配線基板の製造方法(2)における工程(B1)及び(B2)、配線基板の製造方法(5)における工程(B3)において、第一面の非露光部のソルダーレジスト層2、第一ソルダーレジスト層2-1、第二ソルダーレジスト層2-2を薄膜化した量とによって、第一面の露出した接続パッド3周囲のソルダーレジスト層2、第一ソルダーレジスト層2-1の厚さ及びアンダーフィル堰き止め用のダムの一部となるソルダーレジスト層2、第一ソルダーレジスト層2-1、第二ソルダーレジスト層2-2の厚さが決定される。また、本発明では、0.01～500 μm の範囲で薄膜化量を適宜自由に調整することができる。接続パッドの厚さ以下になるまで薄膜化されたソルダーレジスト層2、第一ソルダーレジスト層2-1表面から露出した接続パッド3表面までの高さは、後で必要な半田量に応じて適宜調整する。また、アンダーフィル堰き止め用のダムの一部となるソルダーレジスト層2、第一ソルダーレジスト層2-1、第二ソルダーレジスト層2-2の厚さは、電子部品の大きさや電子部品の接続端子の大きさや電子部品と配線基板間に充填するアンダーフィルの量に応じて適宜調整する。

#### 【0097】

配線基板の製造方法(6)は、配線基板の製造方法(1)～(4)において、工程(C1)の前に工程(C2)を行う。また、配線基板の製造方法(7)は、配線基板の製造方法(1)～(4)において、工程(C1)と工程(C2)を同時に行う。このように、配線基板の製造方法(1)～(4)では、工程(C1)と工程(C2)の順番を入れ替えることもできるし、工程(C1)と工程(C2)を同時に行うこともできる。

#### 【0098】

配線基板の製造方法(1)における工程(C1)では、第一面のソルダーレジスト層2に対して、後工程である工程(B)において薄膜化される領域以外の部分が選択的に露光される。配線基板の製造方法(2)における工程(C1)では、第一面のソルダーレジスト層2に対して、後工程である工程(B1)において薄膜化される領域以外の部分が選択的に露光される。配線基板の製造方法(3)及び(4)における工程(C1)では、第一面の第一ソルダーレジスト層2-1に対して、後工程である工程(B)において薄膜化される領域以外の部分が選択的に露光される。配線基板の製造方法(2)における工程(C4)では、第一面のソルダーレジスト層2に対して、後工程である工程(B2)において薄膜化される領域以外の部分が選択的に露光される。配線基板の製造方法(3)における工程(C6)及び配線基板の製造方法(5)における工程(C7)では、第一面の第二ソルダーレジスト層2-2に対して、後工程である工程(D1)において現像される領域以外の部分を選択的に露光する。配線基板の製造方法(4)における工程(C6)では、第一面の第二ソルダーレジスト層2-2に対して、後工程である工程(D2)において現像される領域以外の部分を選択的に露光する。配線基板の製造方法(5)における工程(C6)では、第一面の第二ソルダーレジスト層2-2に対して、後工程である工程(B3)において薄膜化される領域以外の部分を露光する。露光されたソルダーレジストは光重合し、ソルダーレジスト層2、第一ソルダーレジスト層2-1、第二ソルダーレジスト層2

10

20

30

40

50

- 2 が硬化する。図 4 - 1 ~ 図 8 - 3 では、フォトマスク 5 を介して活性光線 6 を露光しているが、直接描画方式で行つてもよい。露光方式としては、例えば、キセノンランプ、高圧水銀灯、低圧水銀灯、超高压水銀灯、UV 蛍光灯を光源とした反射画像露光方式、フォトマスクを用いた密着露光方式、プロキシミティ方式、プロジェクション方式やレーザー走査露光方式等が挙げられる。第一面において「薄膜化される領域」とは、例えば、接続パッド上や接続パッド間を含む接続パッド周囲の領域である。より具体的には、電子部品を搭載するための実装領域とその周囲である。

#### 【 0 0 9 9 】

配線基板の製造方法 (1) 及び (2) における工程 (C 2) では、第二面のソルダーレジスト層 2 に対して、後工程である工程 (D) において現像される領域以外の部分が選択的に露光される。配線基板の製造方法 (4) における工程 (C 2) では、第二面の第一ソルダーレジスト層 2 - 1 に対して、後工程である工程 (D) において現像される領域以外の部分が選択的に露光される。配線基板の製造方法 (3) 及び (5) における工程 (C 2) では、第二面の第一ソルダーレジスト層 2 - 1 に対して、後工程である工程 (D 1) において現像される領域以外の部分が選択的に露光される。露光されたソルダーレジストは光重合し、ソルダーレジスト層 2、第一ソルダーレジスト層 2 - 1 が硬化する。露光方式としては、上述した配線基板の製造方法 (1) における工程 (C 1) 等と同様の方式を使用することができる。第二面において「現像される領域」とは、例えば、接続パッド上や接続パッド間を含む接続パッド周囲の領域である。より具体的には、外部電気基板の導体配線と実装するためにエリアアレイ (Area array) 型に配置された接続パッドの一部を露出させる円形の開口部領域である。

#### 【 0 1 0 0 】

配線基板の製造方法 (1) における工程 (C 3) では、第一面のソルダーレジスト層 2 に対して、工程 (B) において薄膜化された領域部分が露光される。配線基板の製造方法 (3) ~ (5) における工程 (C 3) では、第一面の第一ソルダーレジスト層 2 - 1 に対して、工程 (B) において薄膜化された領域部分が露光される。配線基板の製造方法 (2) における工程 (C 5) では、第一面のソルダーレジスト層 2 に対して、工程 (B 2) において薄膜化された領域部分が露光される。露光方式としては、上述した配線基板の製造方法 (1) における工程 (C 1) 等と同様の方式を使用することができる。配線基板の製造方法 (1)、(3) ~ (5) における工程 (C 3) や配線基板の製造方法 (2) における工程 (C 5) の後には、非露光部のソルダーレジスト層 2、第一ソルダーレジスト層 2 - 1、第二ソルダーレジスト層 2 - 2 が現像除去される工程 (配線基板の製造方法 (1)、(2) 及び (4) における工程 (D)、配線基板の製造方法 (3) 及び (5) における工程 (D 1)、配線基板の製造方法 (4) における工程 (D 2) ) があるため、最終的にソルダーレジスト層を形成させる領域を露光してソルダーレジストを光重合させる必要がある。配線基板の製造方法 (1)、(3)、(4) における工程 (C 3) において露光する部分は、少なくとも工程 (B) で薄膜化された領域を含み、工程 (C 1) で露光した部分と工程 (B) で薄膜化された領域との境界部を含めることが好ましい。また、配線基板の製造方法 (2) における工程 (C 5) において露光する部分は、少なくとも工程 (B 2) で薄膜化された領域を含み、工程 (C 4) で露光した部分と工程 (B 2) で薄膜化された領域との境界部を含めることが好ましい。

#### 【 0 1 0 1 】

配線基板の製造方法 (1) ~ (4) における工程 (C 1)、配線基板の製造方法 (1)、(3) ~ (5) における工程 (C 3)、配線基板の製造方法 (1) ~ (5) における工程 (C 2)、配線基板の製造方法 (2) における工程 (C 4) 及び (C 5)、配線基板の製造方法 (3) ~ (5) における工程 (C 6)、配線基板の製造方法 (5) における工程 (C 7) における露光量は、ソルダーレジストの感光感度に応じて適宜決定される。より詳しくは、配線基板の製造方法 (1)、(3) ~ (5) における工程 (B)、配線基板の製造方法 (2) における工程 (B 1) 及び (B 2)、配線基板の製造方法 (5) における工程 (B 3) において使用される薄膜化処理液、又は、配線基板の製造方法 (1)、(2)

10

20

30

40

50

)、(4)における工程(D)、配線基板の製造方法(3)及び(5)における工程(D1)、配線基板の製造方法(4)における工程(D2)において使用される現像液に対して、ソルダーレジストが溶解又は膨潤しない程度に、ソルダーレジストを光重合させて硬化させることができればよく、通常100~600mJ/cm<sup>2</sup>である。

#### 【0102】

配線基板の製造方法(1)、(3)、(4)における工程(C3)、配線基板の製造方法(2)における工程(C4)及び(C5)、配線基板の製造方法(5)における工程(C3)及び工程(C7)における露光は、酸素雰囲気下での非接触露光方式で行うことが好ましい。非接触露光方式としては、フォトマスクと配線基板の間に隙間を設けて非接触で露光を行うプロキシミティ方式、プロジェクション方式や、フォトマスクを用いない直接描画方式が挙げられる。ソルダーレジスト層2、第一ソルダーレジスト層2-1、第二ソルダーレジスト層2-2上に支持層フィルムがない状態で酸素雰囲気下での非接触露光を行うことによって、各ソルダーレジスト層の表層付近(ソルダーレジスト層表面からの深さが0~0.5μm程度)の光重合が酸素の影響により阻害されて未硬化部分となり、表層から離れた部位のみが硬化する。そのため、配線基板の製造方法(1)における工程(D)、配線基板の製造方法(2)における工程(B2)及び(D)、配線基板の製造方法(3)における工程(D1)、配線基板の製造方法(4)における工程(D)及び(D2)、配線基板の製造方法(5)における工程(D1)によって、表層付近の未硬化部分が除去され、ソルダーレジスト層2、第一ソルダーレジスト層2-1、第二ソルダーレジスト層2-2の表面が粗面化する。配線基板の表面にある電子部品接続用接続パッドの周囲のソルダーレジスト層表面が平滑な場合よりも粗面化された場合の方が、アンダーフィルとの密着性がより強固になり、結果として熱衝撃によって電子部品と配線基板の接続部に応力が集中するのを防ぐことができ、接続信頼性がより高くなる。酸素雰囲気下での非接触方式露光によってソルダーレジスト層2、第一ソルダーレジスト層2-1、第二ソルダーレジスト層2-2の表面が粗面化することにより、アンダーフィルとの密着性が向上し、高い接続信頼性が得られる。アンダーフィルとの密着性を向上させるのに好ましいソルダーレジスト層の表面粗さRaは、0.30μm以上0.50μm以下である。表面粗さRaが0.50μmを超えると、ソルダーレジストの強度が低くなつて、絶縁信頼性が得られなくなる場合がある。表面粗さRaは算術平均表面粗さである。

#### 【0103】

配線基板の製造方法(1)、(3)、(4)における工程(C3)、配線基板の製造方法(2)における工程(C4)及び(C5)における露光量は、工程(C1)における露光量の1倍以上5倍以下であることが好ましく、さらに好ましくは、1.5倍以上3倍以下である。同様に、配線基板の製造方法(5)における工程(C3)及び工程(C7)における露光量は、工程(C6)における露光量の1倍以上5倍以下であることが好ましく、さらに好ましくは、1.5倍以上3倍以下である。酸素雰囲気下での非接触露光において、ソルダーレジストが溶解又は膨潤しない程度に硬化させるのに必要な露光量に対し、さらに多くの露光量を与えることによって、ソルダーレジスト層の表面の酸素による重合阻害を必要最小限に抑えることができる。露光量は多いほど、重合阻害の抑制には効果があるが、一方で、露光量が多くなりすぎると、ソルダーレジストの解像性が悪化するだけでなく、露光時間が長くなりすぎるため好ましくない。

#### 【0104】

配線基板の製造方法(1)、(3)~(5)における工程(B)、配線基板の製造方法(2)における工程(B2)では、第一面において、薄膜化処理液によって、接続パッド3の厚さ以下になるまで、非露光部のソルダーレジスト層2、第一ソルダーレジスト層2-1が薄膜化されて、接続パッド3の一部を露出させる。配線基板の製造方法(2)における工程(B1)、配線基板の製造方法(5)における工程(B3)では、第一面において、薄膜化処理液によって、接続パッド3が露出しない範囲で、非露光部のソルダーレジスト層2、第二ソルダーレジスト層2-2が薄膜化される。フィルム状レジストを使用し、支持層フィルムが設けられている場合には、支持層フィルムを剥がしてから薄膜化を行

10

20

30

40

50

う。

【0105】

配線基板の製造方法(1)、(3)～(5)における工程(B)、配線基板の製造方法(2)における工程(B2)では、薄膜化後のソルダーレジスト層2、第一ソルダーレジスト層2-1の厚さが、第一面の露出した接続パッド3の厚さと同じか、それよりも薄くなるまで薄膜化を行う。薄膜化後のソルダーレジスト層2、第一ソルダーレジスト層2-1の厚さが薄すぎると、露出した接続パッド3間の電気絶縁が不十分になり、無電解ニッケル／金めっきの短絡が発生する場合や、接続パッド3間で半田による短絡が発生する場合がある。そのため、薄膜化後のソルダーレジスト層2、第一ソルダーレジスト層2-1の厚さは、接続パッド3の厚さの3分の1以上であることが好ましく、より好ましくは3分の2以上であるのがよい。10

【0106】

配線基板の製造方法(1)における工程(B)、配線基板の製造方法(2)における工程(B1)及び(B2)において、第一面の非露光部のソルダーレジスト層2を薄膜化すると、第二面の非露光部のソルダーレジスト層2も同時に薄膜化される。配線基板の製造方法(3)～(5)における工程(B)において、第一面の非露光部の第一ソルダーレジスト層2-1を薄膜化すると、第二面の非露光部の第一ソルダーレジスト層2-1も同時に薄膜化される。配線基板の製造方法(5)における工程(B3)において、第一面の非露光部の第二ソルダーレジスト層2-2を薄膜化すると、第二面の非露光部の第一ソルダーレジスト層2-1も同時に薄膜化される。第二面の薄膜化量は、第二面における非露光部のソルダーレジスト層2、第一ソルダーレジスト層2-1の熱硬化状態によって異なるが、両表面において同じ加熱条件でソルダーレジスト層2、第一ソルダーレジスト層2-1が形成されている場合、通常、第一面と第二面の非露光部のソルダーレジスト層2、第一ソルダーレジスト層2-1は同時に同量薄膜化される。20

【0107】

配線基板の製造方法(1)、(3)～(5)における工程(B)、配線基板の製造方法(2)における工程(B1)及び(B2)、配線基板の製造方法(5)における工程(B3)において、薄膜化処理は、第一面を上にして行うことが好ましい。薄膜化処理の処理方式としては、薄膜化処理液中に気泡が発生しにくいため、浸漬処理が有効である。万が一、薄膜化処理液中に気泡が発生した場合には、気泡は薄膜化処理液中を浮上し、下面(第二面)のソルダーレジスト層2、第一ソルダーレジスト層2-1表面に付着する。この気泡の付着によって、第二面における薄膜化後の膜厚が不均一となる場合がある。しかし、後工程である配線基板の製造方法(1)、(2)、(4)における工程(D)、配線基板の製造方法(3)及び(5)における工程(D1)、配線基板の製造方法(4)における工程(D2)において、第二面の非露光部のソルダーレジスト層2、第一ソルダーレジスト層2-1は現像除去されるため、最終的に膜厚ムラが問題となることはない。30

【0108】

配線基板の製造方法(1)及び(2)における工程(D)では、現像によって、第二面の非露光部のソルダーレジスト層2を除去する。配線基板の製造方法(4)における工程(D)では、現像によって、第二面の非露光部の第一ソルダーレジスト層2-1を除去する。配線基板の製造方法(3)及び(5)における工程(D1)では、現像によって、第一面の非露光部の第二ソルダーレジスト層2-2及び第二面の非露光部の第一ソルダーレジスト層2-1を除去する。配線基板の製造方法(4)における工程(D2)では、現像によって、第一面の非露光部の第二ソルダーレジスト層2-2を除去する。現像方法としては、使用するソルダーレジストに見合った現像液を用い、回路基板の両表面にスプレーを噴射して、各ソルダーレジスト層の不要な部分を除去する。現像液には、希薄なアルカリ水溶液が使用され、一般的には、0.3～3質量%の炭酸ナトリウム水溶液や炭酸カリウム水溶液が使用される。40

【実施例】

【0109】

以下、実施例によって本発明をさらに詳しく説明するが、本発明はこの実施例に限定されるものではない。

【0110】

実施例1～6は、図4-1および図4-2に示した配線基板の製造方法(1)に関する例である。

【0111】

(実施例1)

<工程(A)>

セミアディティブ法を用いて、両表面に導体配線7が形成された回路基板1(面積170mm×200mm、導体厚さ15μm、基板厚さ0.4mm)を作製した。表面(第一面)側には電子部品接続用接続パッド3として使用される線幅25μm、間隔50μmの導体配線がある。裏面(第二面)側には外部接続用接続パッド4として使用される直径600μmの円形状の導体配線が形成されている。次に、真空ラミネータを用いて、厚さ25μmのソルダーレジストフィルム(太陽インキ製造(株)製、商品名: PFR-800AUS410)を上記回路基板1の両表面に真空熱圧着させた(ラミネート温度75、吸引時間30秒、加圧時間10秒)。これにより、ソルダーレジスト層2が形成された。第一面のソルダーレジスト層2では、絶縁層8表面からの厚さが30μmであり、電子部品接続用接続パッド3上の厚さは15μmであった。第二面のソルダーレジスト層2では、絶縁層8表面からの厚さが38μmであり、外部接続用接続パッド4上の厚さが23μmであった。導体配線の密度がより小さい第一面では、導体配線の密度がより大きい第二面に比べ、ソルダーレジスト層2の厚さが8μm薄くなっていた。

【0112】

<工程(C1)>

第一面のソルダーレジスト層2に対して、複数の電子部品接続用接続パッド3の端部から200μm離れた外周よりも外側の領域に活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

【0113】

<工程(C2)>

第二面のソルダーレジスト層2に対して、外部接続用接続パッド4上に直径500μmの円形開口部領域を設けるべく、円形開口部領域以外に活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

【0114】

<工程(B)>

第一面及び第二面のソルダーレジスト層2上の支持層フィルムを剥離した後、10質量%のメタケイ酸ナトリウム水溶液(液温25)を薄膜化処理液として用いて、第一面上にして薄膜化処理液に回路基板1を50秒間浸漬させてミセル化処理(薄膜化処理)を行った。その後、ミセル除去液(液温25)のスプレーによるミセル除去処理、水洗処理(液温25)及び乾燥処理を行い、第一面の非露光部のソルダーレジスト層2の厚さが電子部品接続用接続パッド3の表面下5.0μmになるまで、平均20μmのソルダーレジスト層2を薄膜化した。光学顕微鏡で観察したところ、第一面のソルダーレジスト層2の表面に処理ムラはなく、良好な面内均一性が得られた。一方、第二面においても、平均20μmのソルダーレジスト層2が薄膜化されていたが、薄膜化処理液中の気泡が第二面の非露光部のソルダーレジスト層2に付着し、膜厚不均一となっている箇所があった。また、外部接続用接続パッド4上には約3μmのソルダーレジスト層2の残渣が残っていた。

【0115】

<工程(C3)>

第一面のソルダーレジスト層2に対して、工程(B)において薄膜化された領域部分及びその薄膜化された領域の境界部から200μm外側までの領域に、活性光線6が照射されるようなパターンのフォトマスク5を用いて、酸素雰囲気下での非接触露光により、露

光量 4 0 0 mJ / cm<sup>2</sup> で露光を行った。

【 0 1 1 6 】

< 工程 ( D ) >

1 質量 % の炭酸ナトリウム水溶液 ( 液温度 3 0 、スプレー圧 0 . 1 5 M P a ) を用いて 3 0 秒間現像を行い、第二面の非露光部のソルダーレジスト層 2 を除去した。光学顕微鏡で観察した結果、第一面及び第二面ともに、電子部品接続用接続パッド 3 及び外部接続用接続パッド 4 上にソルダーレジスト層 2 の残渣は見られなかった。また、第一面では、電子部品接続用接続パッド 3 の表面下 5 . 5 μm まで、電子部品接続用接続パッド 3 間にソルダーレジスト層 2 が充填されていた。工程 ( C 3 ) における酸素雰囲気下での非接触露光により、電子部品接続用接続パッド 3 間のソルダーレジスト層 2 表面の光重合が抑制され、結果として、ソルダーレジスト層 2 の厚さが 0 . 5 μm 減少していた。

【 0 1 1 7 】

次に、第一面及び第二面のソルダーレジスト層 2 を硬化させるため、露光量 1 0 0 0 mJ / cm<sup>2</sup> で全面露光し、続いて、1 5 0 で 6 0 分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ 1 5 μm の導体配線 7 が厚さ 3 0 μm のソルダーレジスト層 2 によって被覆され、厚さ 1 5 μm の電子部品接続用接続パッド 3 が露出しており、隣接する電子部品接続用接続パッド 3 間に厚さ 9 . 5 μm のソルダーレジスト層 2 が充填されていた。また、第二面では、厚さ 1 5 μm の外部接続用接続パッド 4 上の一部に、厚さ 3 8 μm 、直径 5 0 0 μm のソルダーレジスト層 2 の円形開口部が形成されていて、外部接続用接続パッド 4 の一部が露出していた。

【 0 1 1 8 】

次に、隣接する電子部品接続用接続パッド 3 間のソルダーレジスト層 2 の表面粗さを測定した。超深度形状測定顕微鏡 ( 株式会社キーエンス ( K E Y E N C E ) 製、品番「 V K - 8 5 0 0 」 ) を用いて表面粗さを測定したところ、表面粗さ R a は 0 . 4 0 μm であった。

【 0 1 1 9 】

超深度形状測定顕微鏡 ( 株式会社キーエンス製、品番「 V K - 8 5 0 0 」 ) による算術平均表面粗さ R a は、 J I S B 0 6 0 1 - 1 9 9 4 表面粗さ - 定義に準じた計算式を用いている。なお、測定領域は 9 0 0 μm<sup>2</sup> 、基準長さは 4 0 μm とした。

【 0 1 2 0 】

( 実施例 2 )

工程 ( C 1 ) と工程 ( C 2 ) の順番を入れ替えた以外は実施例 1 と同じ方法で、工程 ( A ) ~ 工程 ( D ) までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド 3 及び外部接続用接続パッド 4 上にソルダーレジスト層 2 の残渣は見られなかった。また、また、第一面では、電子部品接続用接続パッド 3 の表面下 5 . 5 μm まで、電子部品接続用接続パッド 3 間にソルダーレジスト層 2 が充填されていた。工程 ( C 3 ) における酸素雰囲気下での非接触露光により、電子部品接続用接続パッド 3 間のソルダーレジスト層 2 表面の光重合が抑制され、結果としてソルダーレジスト層 2 の厚さが 0 . 5 μm 減少していた。

【 0 1 2 1 】

次に、第一面及び第二面のソルダーレジスト層 2 を硬化させるため、露光量 1 0 0 0 mJ / cm<sup>2</sup> で全面露光し、続いて、1 5 0 で 6 0 分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ 1 5 μm の導体配線 7 が厚さ 3 0 μm のソルダーレジスト層 2 によって被覆され、厚さ 1 5 μm の電子部品接続用接続パッド 3 が露出しており、隣接する電子部品接続用接続パッド 3 間に厚さ 9 . 5 μm のソルダーレジスト層 2 が充填されていた。また、第二面では、厚さ 1 5 μm の外部接続用接続パッド 4 上の一部に、厚さ 3 8 μm 、直径 5 0 0 μm のソルダーレジスト層の円形開口部が形成されていて、外部接続用接続パッド 4 の一部が露出していた。

【 0 1 2 2 】

次に、隣接する電子部品接続用接続パッド 3 間のソルダーレジスト層 2 の表面粗さを測

10

20

30

40

50

定したところ、表面粗さ  $R_a$  は 0.40  $\mu\text{m}$  であった。

【0123】

(実施例3)

工程 (C3) における露光量を 200  $\text{mJ/cm}^2$  とした以外は実施例1と同じ方法で、工程 (A) ~ 工程 (D) までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上にソルダーレジスト層2の残渣は見られなかった。第一面では、電子部品接続用接続パッド3の表面下 6.0  $\mu\text{m}$  まで、電子部品接続用接続パッド3間にソルダーレジスト層2が充填されていた。工程 (C3) における酸素雰囲気下での非接触露光により、電子部品接続用接続パッド3間にソルダーレジスト層2表面の光重合が抑制され、結果としてソルダーレジスト層2の厚さが 1.0  $\mu\text{m}$  減少していた。10

【0124】

次に、第一面及び第二面のソルダーレジスト層2を硬化させるため、露光量 1000  $\text{mJ/cm}^2$  で全面露光し、続いて、150  $\text{mJ}$  で 60 分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ 15  $\mu\text{m}$  の導体配線7が厚さ 30  $\mu\text{m}$  のソルダーレジスト層2によって被覆され、厚さ 15  $\mu\text{m}$  の電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ 9.0  $\mu\text{m}$  のソルダーレジスト層2が充填されていた。また、第二面では、厚さ 15  $\mu\text{m}$  の外部接続用接続パッド4上の一とに、厚さ 38  $\mu\text{m}$ 、直径 500  $\mu\text{m}$  のソルダーレジスト層2の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。20

【0125】

次に、隣接する電子部品接続用接続パッド3間にソルダーレジスト層2の表面粗さを測定したところ、表面粗さ  $R_a$  は 0.50  $\mu\text{m}$  であった。

【0126】

(実施例4)

工程 (C3) における露光量を 1000  $\text{mJ/cm}^2$  とした以外は実施例1と同じ方法で、工程 (A) ~ 工程 (D) までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上にソルダーレジスト層2の残渣は見られなかった。また、第一面では、電子部品接続用接続パッド3の表面下 5.0  $\mu\text{m}$  まで、電子部品接続用接続パッド3間にソルダーレジスト層2が充填されていた。工程 (C3) における酸素の重合阻害による第一面のソルダーレジスト層2の膜減りは確認されなかった。30

【0127】

次に、第一面及び第二面のソルダーレジスト層2を硬化させるため、露光量 1000  $\text{mJ/cm}^2$  で全面露光し、続いて、150  $\text{mJ}$  で 60 分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ 15  $\mu\text{m}$  の導体配線7が厚さ 30  $\mu\text{m}$  のソルダーレジスト層2によって被覆され、厚さ 15  $\mu\text{m}$  の電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ 10.0  $\mu\text{m}$  のソルダーレジスト層2が充填されていた。また、第二面では、厚さ 15  $\mu\text{m}$  の外部接続用接続パッド4上の一とに、厚さ 38  $\mu\text{m}$ 、直径 500  $\mu\text{m}$  のソルダーレジスト層2の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。40

【0128】

次に、隣接する電子部品接続用接続パッド3間にソルダーレジスト層2の表面粗さを測定したところ、表面粗さ  $R_a$  は 0.30  $\mu\text{m}$  であった。

【0129】

(実施例5)

工程 (C3) における露光を、酸素雰囲気下において直接描画装置（商品名：L I - 8500、大日本スクリーン製造社製）を用いて露光量 400  $\text{mJ/cm}^2$  で行った以外は実施例1と同じ方法で、工程 (A) ~ 工程 (D) までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド450

上にソルダーレジスト層2の残渣は見られなかった。また、第一面では、電子部品接続用接続パッド3の表面下5.5μmまで、電子部品接続用接続パッド3間にソルダーレジスト層2が充填されていた。工程(C3)における酸素雰囲気下での非接触露光により、電子部品接続用接続パッド3間にソルダーレジスト層2表面の光重合が抑制され、結果としてソルダーレジスト層2の厚さが0.5μm減少していた。

【0130】

次に、第一面及び第二面のソルダーレジスト層2を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmのソルダーレジスト層2によって被覆され、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ9.5μmのソルダーレジスト層2が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上的一部に、厚さ38μm、直径500μmのソルダーレジスト層の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

【0131】

次に、隣接する電子部品接続用接続パッド3間にソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.40μmであった。

【0132】

(実施例6)

工程(C3)において、密着露光方式にて露光を行った以外は、実施例1と同じ方法で、工程(A)～工程(D)までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上にソルダーレジスト層2の残渣は見られなかった。また、第一面では、電子部品接続用接続パッド3の表面下5.0μmまで、電子部品接続用接続パッド3間にソルダーレジスト層2が充填されていた。工程(C3)において、密着露光時のエア抜きを十分行うことにより、非酸素雰囲気下で露光を行ったため、ソルダーレジスト層2表面が粗面化せず、結果として、ソルダーレジスト層2の厚さは減少しなかった。

【0133】

次に、第一面及び第二面のソルダーレジスト層2を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmのソルダーレジスト層2によって被覆され、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ10μmのソルダーレジスト層2が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上的一部に、厚さ38μm、直径500μmのソルダーレジスト層2の円形開口部が形成されていて、導体パッド4が露出していた。

【0134】

次に、隣接する電子部品接続用接続パッド3間にソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.10μmであった。

【0135】

実施例1～6では、隣接する電子部品接続用接続パッド3間に十分な厚さのソルダーレジスト層2があるため、電子部品を実装する際に半田による電気的な短絡が起きるのを確実に防ぐことができた。また、外部接続用接続パッド4上にソルダーレジスト層2の残渣が存在しないため、外部電気基板に実装する際にも電気的絶縁不良が発生しない信頼性の高い配線基板を作製することができた。実施例1～6を比較すると、電子部品接続用接続パッド3間にソルダーレジスト層2の表面が平滑である実施例6で製造された配線基板よりも、実施例1～5で製造された配線基板の方が、アンダーフィルとの密着性が高く、接続信頼性が優れていた。

【0136】

(比較例1)

10

20

30

40

50

## &lt;工程(A)&gt;

セミアディティブ法を用いて、両表面に導体配線7が形成された回路基板1(面積170mm×200mm、導体厚さ15μm、基板厚さ0.4mm)を作製した。表面(第一面)には電子部品接続用接続パッド3として使用される線幅25μm、間隔50μmの導体配線がある。裏面(第二面)には外部接続用接続パッド4として使用される直径600μmの円形状の導体配線が形成されている。次に、真空ラミネータを用いて、厚さ25μmのソルダーレジストフィルム(太陽インキ製造(株)製、商品名: P F R - 8 0 0 A U S 4 1 0)を上記回路基板1の両表面に真空熱圧着させた(ラミネート温度75、吸引時間30秒、加圧時間10秒)。これにより、ソルダーレジスト層2が形成された。第一面のソルダーレジスト層2では、絶縁層8表面からの厚さが30μmであり、電子部品接続用接続パッド3上の厚さは15μmであった。第二面のソルダーレジスト層2では、絶縁層8表面からの厚さが38μmであり、外部接続用接続パッド4上の厚さが23μmであった。導体配線の密度がより小さい第一面では、導体配線の密度がより大きい第二面に比べ、ソルダーレジスト層2の厚さが8μm薄くなっていた。

## 【0137】

## &lt;工程(C1)&gt;

第一面のソルダーレジスト層2に対して、複数の電子部品接続用接続パッド3の端部から200μm離れた外周よりも外側の領域に活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

## 【0138】

## &lt;工程(C2)&gt;

第二面のソルダーレジスト層2に対して、外部接続用接続パッド4上に直径500μmの円形開口部領域を設けるべく、円形開口部領域以外に活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

## 【0139】

## &lt;工程(B)&gt;

第一面及び第二面のソルダーレジスト層2上の支持層フィルムを剥離した後、10質量%のメタケイ酸ナトリウム水溶液(液温25)を薄膜化処理液として用いて、第一面上にして薄膜化処理液に回路基板1を50秒間浸漬させてミセル化処理(薄膜化処理)を行った。その後、ミセル除去液(液温25)のスプレーによるミセル除去処理、水洗処理(液温25)及び乾燥処理を行い、第一面の非露光部のソルダーレジスト層2の厚さが電子部品接続用接続パッド3の表面下5.0μmになるまで、平均20μmのソルダーレジスト層2を薄膜化した。光学顕微鏡で観察したところ、第一面のソルダーレジスト層2の表面に処理ムラはなく、良好な面内均一性が得られた。一方、第二面のソルダーレジスト層2も平均20μm薄膜化されていたが、薄膜化処理液中の気泡が第二面の非露光部のソルダーレジスト層2に付着し、膜厚不均一となっている箇所があった。また、外部接続用接続パッド4には約3μmのソルダーレジスト層2の残渣が残っていた。

## 【0140】

次に、第一面及び第二面のソルダーレジスト層2を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmのソルダーレジスト層2によって被覆され、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ10.0μmのソルダーレジスト層2が充填されていた。また、第二面は厚さ15μmの外部接続用接続パッド4上的一部に、厚さ38μm、直径500μmのソルダーレジスト層2の円形開口部が形成されていたが、外部接続用接続パッド4上には厚さ3μmのソルダーレジスト層2の残渣が残っていた。

## 【0141】

電子部品を実装する際、隣接する電子部品接続用接続パッド3間に十分な厚さのソルダーレジスト層2があり、半田による電気的な短絡を確実に防ぐことができたが、外部電気

10

20

30

40

50

基板に実装する際、外部接続用接続パッド4上に残ったソルダーレジスト層2の残渣によって、半田バンプ接続において電気的絶縁不良が発生した。

【0142】

隣接する電子部品接続用接続パッド3間のソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.03μmであった。電子部品接続用接続パッド3間のソルダーレジスト表面が平滑である比較例1で製造された配線基板よりも、実施例1～5で製造された配線基板の方が、アンダーフィルとの密着性が高く、接続信頼性が優れていた。

【0143】

実施例7～11は、図5-1、図5-2および図5-3に示した配線基板の製造方法(2)に関する例である。

10

【0144】

(実施例7)

<工程(A)>

セミアディティブ法を用いて、両表面に導体配線7が形成された回路基板1(面積170mm×200mm、導体厚さ15μm、基板厚さ0.4mm)を作製した。表面(第一面)には電子部品接続用接続パッド3として使用される線幅25μm、間隔50μmの導体配線がある。裏面(第二面)には外部接続用接続パッド4として使用される直径600μmの円形状の導体配線が形成されている。次に、真空ラミネータを用いて、厚さ25μmのソルダーレジストフィルム(太陽インキ製造(株)製、商品名:PF R-800 A U S 410)を上記回路基板1の両表面に真空熱圧着させた(ラミネート温度75、吸引時間30秒、加圧時間10秒)。これにより、ソルダーレジスト層2が形成された。第一面のソルダーレジスト層2では、絶縁層8表面からの厚さが30μmであり、電子部品接続用接続パッド3上の厚さは15μmであった。第二面のソルダーレジスト層2では、絶縁層8表面からの厚さが38μmであり、外部接続用接続パッド4上の厚さが23μmであった。導体配線の密度がより小さい第一面では、導体配線の密度がより大きい第二面に比べ、ソルダーレジスト層2の厚さが8μm薄くなっていた。

20

【0145】

<工程(C1)>

第一面のソルダーレジスト層2に対して、複数の電子部品接続用接続パッド3の端部から400μm離れた外周よりも外側の領域に活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

30

【0146】

<工程(C2)>

第二面のソルダーレジスト層2に対して、外部接続用接続パッド4上に直径500μmの円形開口部領域を設けるべく、円形開口部領域以外に活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

【0147】

<工程(B1)>

第一面及び第二面のソルダーレジスト層2上の支持層フィルムを剥離した後、10質量%のメタケイ酸ナトリウム水溶液(液温25)を薄膜化処理液として用いて、第一面上にして薄膜化処理液に回路基板1を25秒間浸漬させてミセル化処理(薄膜化処理)を行った。その後、ミセル除去液(液温25)のスプレーによるミセル除去処理、水洗処理(液温25)及び乾燥処理を行い、第一面の非露光部のソルダーレジスト層2の厚さが電子部品接続用接続パッド3の表面上5.0μmになるまで、平均10μmのソルダーレジスト層2を薄膜化した。光学顕微鏡で観察したところ、第一面のソルダーレジスト層2の表面に処理ムラはなく、良好な面内均一性が得られた。一方、第二面のソルダーレジスト層2も平均10μm薄膜化されていたが、薄膜化処理液中の気泡が第二面の非露光部のソルダーレジスト層2に付着し、膜厚不均一となっている箇所があった。また、外部接続用接続パッド4には約13μmのソルダーレジスト層2の残渣が残っていた。

40

【0148】

50

## &lt;工程(C4)&gt;

第一面のソルダーレジスト層2に対して、複数の電子部品接続用接続パッド3の端部から200μm離れた外周よりも外側の領域に、活性光線6が照射されるようなパターンのフォトマスク5を用いて、酸素雰囲気下での非接触露光により、露光量400mJ/cm<sup>2</sup>で露光を行った。

## 【0149】

## &lt;工程(B2)&gt;

10 10質量%のメタケイ酸ナトリウム水溶液(液温25)を薄膜化処理液として用いて、第一面を上にして薄膜化処理液に回路基板1を25秒間浸漬させてミセル化処理(薄膜化処理)を行った。その後、ミセル除去液(液温25)のスプレーによるミセル除去処理、水洗処理(液温25)及び乾燥処理を行い、第一面の非露光部のソルダーレジスト層2の厚さが電子部品接続用接続パッド3の表面下5.0μmになるまで、平均10μmのソルダーレジスト層2を薄膜化した。光学顕微鏡で観察したところ、第一面のソルダーレジスト層2の表面に処理ムラはなく、良好な面内均一性が得られた。工程(C4)における酸素雰囲気下での非接触露光により、第一面に配置された電子部品接続用接続パッド3の端部から200μm離れた外周から400μm離れた外周までの領域のソルダーレジスト層2表面の光重合が抑制され、結果としてソルダーレジスト層2の厚さが0.5μm減少した。一方、第二面のソルダーレジスト層2も平均10μm薄膜化されていたが、薄膜化処理液中の気泡が第二面の非露光部のソルダーレジスト層2に付着し、膜厚不均一となっている箇所があった。また、外部接続用接続パッド4には約3μmのソルダーレジスト層2の残渣が残っていた。

## 【0150】

## &lt;工程(C5)&gt;

第一面のソルダーレジスト層2に対して、工程(B2)において薄膜化された領域部分及びその薄膜化された領域の境界部から200μm外側までの領域に、活性光線6が照射されるようなパターンのフォトマスク5を用いて、酸素雰囲気下での非接触露光により、露光量400mJ/cm<sup>2</sup>で露光を行った。

## 【0151】

## &lt;工程(D)&gt;

11 11質量%の炭酸ナトリウム水溶液(液温度30、スプレー圧0.15MPa)を用いて30秒間現像を行い、第二面の非露光部のソルダーレジスト層2を除去した。光学顕微鏡で観察した結果、第一面及び第二面ともに、電子部品接続用接続パッド3及び外部接続用接続パッド4上にソルダーレジスト層2の残渣は見られなかった。また、第一面では、電子部品接続用接続パッド3の表面下5.5μmまで、電子部品接続用接続パッド3間にソルダーレジスト層2が充填されていた。工程(C4)及び(C5)における酸素雰囲気下での非接触露光により、第一面では、工程(C1)における密着露光で活性光線6が照射された領域以外のソルダーレジスト層2表面の光重合が抑制され、結果として、ソルダーレジスト層2の厚さが0.5μm減少していた。

## 【0152】

次に、第一面及び第二面のソルダーレジスト層2を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと19.5μmのソルダーレジスト層2によって被覆され、その段差に相当する厚さ10.5μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ9.5μmのソルダーレジスト層2が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上的一部分に、厚さ38μm、直径500μmのソルダーレジスト層2の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

## 【0153】

10

20

30

40

50

次に、第一面に配置された複数の電子部品接続用接続パッド3の端部から200μm離れた外周と該端部から400μm離れた外周との間の領域にある厚さ19.5μmのソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.40μmであった。また、隣接する電子部品接続用接続パッド3間のソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.40μmであった。

#### 【0154】

##### (実施例8)

工程(C1)と工程(C2)の順番を入れ替えた以外は実施例7と同じ方法で、工程(A)～工程(D)までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上にソルダーレジスト層2の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド3の表面下5.5μmまでソルダーレジスト層2が充填されていた。工程(C4)及び(C5)における酸素雰囲気下での非接触露光により、第一面では、工程(C1)における密着露光で活性光線6が照射された領域以外のソルダーレジスト層2表面の光重合が抑制され、結果として、ソルダーレジスト層2の厚さが0.5μm減少していた。

#### 【0155】

次に、第一面及び第二面のソルダーレジスト層2を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと19.5μmのソルダーレジスト層2によって被覆され、その段差に相当する厚さ10.5μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ9.5μmのソルダーレジスト層2が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上的一部分に、厚さ38μm、直径500μmのソルダーレジスト層2の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

#### 【0156】

次に、第一面に配置された複数の電子部品接続用接続パッド3の端部から200μm離れた外周と該端部から400μm離れた外周との間の領域にある厚さ19.5μmのソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.40μmであった。また、隣接する電子部品接続用接続パッド3間のソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.40μmであった。

#### 【0157】

##### (実施例9)

工程(C4)及び(C5)における露光量を200mJ/cm<sup>2</sup>とした以外は実施例7と同じ方法で、工程(A)～工程(D)までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上にソルダーレジスト層2の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド3の表面下6.0μmまでソルダーレジスト層2が充填されていた。工程(C4)及び(C5)における酸素雰囲気下での非接触露光により、第一面では、工程(C1)における密着露光で活性光線6が照射された領域以外のソルダーレジスト層2表面の光重合が抑制され、結果として、ソルダーレジスト層2の厚さが1.0μm減少していた。

#### 【0158】

次に、第一面及び第二面のソルダーレジスト層2を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと19μmのソルダーレジスト層2によって被覆され、その段差に相当する厚さ11μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ9.0μmのソルダーレジスト層2が充填されていた。また、第二面では、厚さ15μmの外部

10

20

30

40

50

接続用接続パッド4上的一部分に、厚さ38μm、直径500μmのソルダーレジスト層2の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

【0159】

次に、第一面に配置された複数の電子部品接続用接続パッド3の端部から200μm離れた外周と該端部から400μm離れた外周との間の領域にある厚さ19μmのソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.50μmであった。また、隣接する電子部品接続用接続パッド3間のソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.50μmであった。

【0160】

(実施例10)

10

工程(C4)及び(C5)における露光量を1000mJ/cm<sup>2</sup>とした以外は実施例6と同じ方法で、工程(A)～工程(D)までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上にソルダーレジスト層2の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド3の表面下5.0μmまでソルダーレジスト層2が充填されており、工程(C4)及び(C5)における酸素の重合阻害による第一面のソルダーレジスト層2の膜減りは確認されなかった。

【0161】

次に、第一面及び第二面のソルダーレジスト層2を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150℃で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと20μmのソルダーレジスト層2によって被覆され、その段差に相当する厚さ10μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ10.0μmのソルダーレジスト層2が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上的一部分に、厚さ38μm、直径500μmのソルダーレジスト層2の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

20

【0162】

次に、第一面に配置された複数の電子部品接続用接続パッド3の端部から200μm離れた外周と該端部から400μm離れた外周との間の領域にある厚さ20μmのソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.30μmであった。また、隣接する電子部品接続用接続パッド3間のソルダーレジスト層2の表面粗さを測定したところ、表面粗さRaは0.30μmであった。

30

【0163】

(実施例11)

工程(C4)及び(C5)において、密着露光方式にて露光を行った以外は、実施例7と同じ方法で、工程(A)～工程(D)までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上にソルダーレジスト層2の残渣は見られなかった。また、第一面では、電子部品接続用接続パッド3の表面下5.0μmまで、電子部品接続用接続パッド3間にソルダーレジスト層2が充填されていた。工程(C4)及び(C5)において、密着露光時のエア抜きを十分行うことにより、非酸素雰囲気下で露光を行ったため、ソルダーレジスト層2表面が粗面化せず、結果として、ソルダーレジスト層2の厚さは減少しなかった。

40

【0164】

次に、第一面及び第二面のソルダーレジスト層2を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150℃で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと20μmのソルダーレジスト層2によって被覆され、その段差に相当する厚さ10μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ10.0μmのソルダーレジスト層2が充填されていた。

50

0  $\mu\text{m}$  のソルダーレジスト層 2 が充填されていた。また、第二面では、厚さ 15  $\mu\text{m}$  の外部接続用接続パッド 4 上の一部に、厚さ 38  $\mu\text{m}$ 、直径 500  $\mu\text{m}$  のソルダーレジスト層 2 の円形開口部が形成されていて、外部接続用接続パッド 4 の一部が露出していた。

#### 【 0 1 6 5 】

次に、第一面に配置された複数の電子部品接続用接続パッド 3 の端部から 200  $\mu\text{m}$  離れた外周と該端部から 400  $\mu\text{m}$  離れた外周との間の領域にある厚さ 20  $\mu\text{m}$  のソルダーレジスト層 2 の表面粗さを測定したところ、表面粗さ  $R_a$  は 0.10  $\mu\text{m}$  であった。また、隣接する電子部品接続用接続パッド 3 間のソルダーレジスト層 2 の表面粗さを測定したところ、表面粗さ  $R_a$  は 0.10  $\mu\text{m}$  であった。

#### 【 0 1 6 6 】

実施例 7～11 では、隣接する電子部品接続用接続パッド 3 間に十分な厚さのソルダーレジスト層 2 があるため、電子部品を実装する際に半田による電気的な短絡が起きるのを確実に防ぐことができた。外部接続用接続パッド 4 上にソルダーレジスト層 2 の残渣が存在しないため、外部電気基板に実装する際にも電気的絶縁不良が発生しない信頼性の高い配線基板を作製することができた。実施例 7～11 を比較すると、電子部品接続用接続パッド 3 間及び周囲のソルダーレジスト層 2 の表面が平滑である実施例 11 で製造された配線基板よりも、実施例 7～10 で製造された配線基板の方が、アンダーフィルとの密着性が高く、接続信頼性が優れていた。

#### 【 0 1 6 7 】

( 比較例 2 )

< 工程 ( A ) >

セミアディティブ法を用いて、両表面に導体配線 7 が形成された回路基板 1 (面積 170  $\text{mm} \times 200 \text{ mm}$ 、導体厚さ 15  $\mu\text{m}$ 、基板厚さ 0.4  $\text{mm}$  ) を作製した。表面 (第一面) には電子部品接続用接続パッド 3 として使用される線幅 25  $\mu\text{m}$ 、間隔 50  $\mu\text{m}$  の導体配線がある。裏面 (第二面) には外部接続用接続パッド 4 として使用される直径 600  $\mu\text{m}$  の円形状の導体配線が形成されている。次に、真空ラミネータを用いて、厚さ 25  $\mu\text{m}$  のソルダーレジストフィルム (太陽インキ製造 (株) 製、商品名: P F R - 800 A U S 410 ) を上記回路基板 1 の両表面に真空熱圧着させた (ラミネート温度 75°、吸引時間 30 秒、加圧時間 10 秒)。これにより、ソルダーレジスト層 2 が形成された。第一面のソルダーレジスト層 2 では、絶縁層 8 表面からの厚さが 30  $\mu\text{m}$  であり、電子部品接続用接続パッド 3 上の厚さは 15  $\mu\text{m}$  であった。第二面のソルダーレジスト層 2 では、絶縁層 8 表面からの厚さが 38  $\mu\text{m}$  であり、外部接続用接続パッド 4 上の厚さが 23  $\mu\text{m}$  であった。導体配線の密度がより小さい第一面では、導体配線の密度がより大きい第二面に比べ、ソルダーレジスト層 2 の厚さが 8  $\mu\text{m}$  薄くなっていた。

#### 【 0 1 6 8 】

< 工程 ( C 1 ) >

第一面のソルダーレジスト層 2 に対して、複数の電子部品接続用接続パッド 3 の端部から 200  $\mu\text{m}$  離れた外周よりも外側の領域に活性光線 6 が照射されるようなパターンのフォトマスク 5 を用いて、露光量 200  $\text{mJ} / \text{cm}^2$  で密着露光を行った。

#### 【 0 1 6 9 】

< 工程 ( C 2 ) >

第二面のソルダーレジスト層 2 に対して、外部接続用接続パッド 4 上に直径 500  $\mu\text{m}$  の円形開口部領域を設けるべく、円形開口部領域以外に活性光線 6 が照射されるようなパターンのフォトマスク 5 を用いて、露光量 200  $\text{mJ} / \text{cm}^2$  で密着露光を行った。

#### 【 0 1 7 0 】

< 工程 ( B 1 ) >

第一面及び第二面のソルダーレジスト層 2 上の支持層フィルムを剥離した後、10 質量 % のメタケイ酸ナトリウム水溶液 (液温 25°) を薄膜化処理液として用いて、第一面上にして薄膜化処理液に回路基板 1 を 25 秒間浸漬させてミセル化処理 (薄膜化処理) を行った。その後、ミセル除去液 (液温 25°) のスプレーによるミセル除去処理、水洗処

10

20

30

40

50

理（液温 25℃）及び乾燥処理を行い、第一面の非露光部のソルダーレジスト層 2 の厚さが電子部品接続用接続パッド 3 の表面上 5.0 μm になるまで、平均 10 μm のソルダーレジスト層 2 を薄膜化した。光学顕微鏡で観察したところ、第一面のソルダーレジスト層 2 の表面に処理ムラはなく、良好な面内均一性が得られた。一方、第二面のソルダーレジスト層 2 も平均 10 μm 薄膜化されていたが、薄膜化処理液中の気泡が第二面の非露光部のソルダーレジスト層 2 に付着し、膜厚不均一となっている箇所があった。また、外部接続用接続パッド 4 には約 13 μm のソルダーレジスト層 2 の残渣が残っていた。

#### 【0171】

<工程 (C4)>

第一面のソルダーレジスト層 2 に対して、複数の電子部品接続用接続パッド 3 の端部から 200 μm 離れた外周と該端部から 400 μm 離れた外周との間の領域に、活性光線 6 が照射されるようなパターンのフォトマスク 5 を用いて、酸素雰囲気下での非接触露光により、露光量 400 mJ/cm<sup>2</sup> で露光を行った。

10

#### 【0172】

<工程 (B2)>

10 質量% のメタケイ酸ナトリウム水溶液（液温 25℃）を薄膜化処理液として用いて、第一面を上にして薄膜化処理液に回路基板 1 を 25 秒間浸漬させてミセル化処理（薄膜化処理）を行った。その後、ミセル除去液（液温 25℃）のスプレーによるミセル除去処理、水洗処理（液温 25℃）及び乾燥処理を行い、第一面の非露光部のソルダーレジスト層 2 の厚さが電子部品接続用接続パッド 3 の表面下 5.0 μm になるまで、平均 10 μm のソルダーレジスト層 2 を薄膜化した。光学顕微鏡で観察したところ、第一面のソルダーレジスト層 2 の表面に処理ムラはなく、良好な面内均一性が得られた。工程 (C4) における酸素雰囲気下での非接触露光により、第一面に配置された電子部品接続用接続パッド 3 の端部から 200 μm 離れた外周から 400 μm 離れた外周までの領域のソルダーレジスト層 2 表面の光重合が抑制され、結果としてソルダーレジスト層 2 の厚さが 0.5 μm 減少した。一方、第二面のソルダーレジスト層 2 も平均 10 μm 薄膜化されていたが、薄膜化処理液中の気泡が第二面の非露光部のソルダーレジスト層 2 に付着し、膜厚不均一となっている箇所があった。また、外部接続用接続パッド 4 には約 3 μm のソルダーレジスト層 2 の残渣が残っていた。

20

#### 【0173】

30

次に、第一面及び第二面のソルダーレジスト層 2 を硬化させるため、露光量 1000 mJ/cm<sup>2</sup> で全面露光し、続いて、150℃ で 60 分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ 15 μm の導体配線 7 が厚さ 30 μm と 19.5 μm のソルダーレジスト層 2 によって被覆され、その段差に相当する厚さ 10.5 μm のアンダーフィル堰き止め用ダムが形成されていた。また、厚さ 15 μm の電子部品接続用接続パッド 3 が露出しており、隣接する電子部品接続用接続パッド 3 間に厚さ 9.5 μm のソルダーレジスト層 2 が充填されていた。また、第二面は厚さ 15 μm の外部接続用接続パッド 4 上の一部に、厚さ 38 μm、直径 500 μm のソルダーレジスト層 2 の円形開口部が形成されていたが、外部接続用接続パッド 4 上には 3 μm のソルダーレジスト層 2 の残渣が残っていた。

40

#### 【0174】

電子部品を実装する際、隣接する電子部品接続用接続パッド 3 間に十分な厚さのソルダーレジスト層 2 があり、半田による電気的な短絡を確実に防ぐことができるが、外部電気基板に実装する際、外部接続用接続パッド 4 上に残ったソルダーレジスト層 2 の残渣によって、半田バンプ接続において電気的絶縁不良が発生した。

#### 【0175】

隣接する電子部品接続用接続パッド 3 間のソルダーレジスト層 2 の表面粗さを測定したところ、表面粗さ Ra は 0.03 μm であった。電子部品接続用接続パッド 3 間のソルダーレジスト表面が平滑である比較例 2 で製造された配線基板よりも、実施例 7 ~ 11 で製造された配線基板の方が、アンダーフィルとの密着性が高く、接続信頼性が優れていた。

50

## 【0176】

実施例12～16は、図6-1、図6-2および図6-3に示した配線基板の製造方法(3)に関する例である。

## 【0177】

(実施例12)

<工程(A1)>

セミアディティブ法を用いて、両表面に導体配線7が形成された回路基板1(面積170mm×200mm、導体厚さ15μm、基板厚さ0.4mm)を作製した。表面(第一面)には電子部品接続用接続パッド3として使用される線幅25μm、間隔50μmの導体配線がある。裏面(第二面)には外部接続用接続パッド4として使用される直径600μmの円形状の導体配線が形成されている。次に、真空ラミネータを用いて、厚さ15μmのソルダーレジストフィルム(太陽インキ製造(株)製、商品名: P F R - 8 0 0 A U S 4 1 0)を上記回路基板1の表面に、厚さ25μmのソルダーレジストフィルム(太陽インキ製造(株)製、商品名: P F R - 8 0 0 A U S 4 1 0)を上記回路基板1の裏面に真空熱圧着させた(ラミネート温度75、吸引時間30秒、加圧時間10秒)。これにより、第一ソルダーレジスト層2-1が形成された。第一面の第一ソルダーレジスト層2-1では、絶縁層8表面からの厚さが20μmであり、電子部品接続用接続パッド3上の厚さは5μmであった。第二面の第一ソルダーレジスト層2-1では、絶縁層8表面からの厚さが38μmであり、外部接続用接続パッド4上の厚さが23μmであった。

## 【0178】

<工程(C1)>

第一面の第一ソルダーレジスト層2-1に対して、複数の電子部品接続用接続パッド3の端部から200μm離れた外周よりも外側の領域に活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

## 【0179】

<工程(C2)>

第二面の第一ソルダーレジスト層2-1に対して、外部接続用接続パッド4上に直径500μmの円形開口部領域を設けるべく、円形開口部領域以外に活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

## 【0180】

<工程(B)>

第一面及び第二面の第一ソルダーレジスト層2-1上の支持層フィルムを剥離した後、10質量%のメタケイ酸ナトリウム水溶液(液温25)を薄膜化処理液として用いて、第一面を上にして薄膜化処理液に回路基板1を25秒間浸漬させてミセル化処理(薄膜化処理)を行った。その後、ミセル除去液(液温25)のスプレーによるミセル除去処理、水洗処理(液温25)及び乾燥処理を行い、第一面の非露光部の第一ソルダーレジスト層2-1の厚さが電子部品接続用接続パッド3の表面下5.0μmになるまで、平均10μmの第一ソルダーレジスト層2-1を薄膜化した。光学顕微鏡で観察したところ、第一面の第一ソルダーレジスト層2-1の表面に処理ムラはなく、良好な面内均一性が得られた。一方、第二面の第一ソルダーレジスト層2-1も平均10μm薄膜化されていたが、薄膜化処理液中の気泡が第二面の非露光部の第一ソルダーレジスト層2-1に付着し、膜厚不均一となっている箇所があった。また、外部接続用接続パッド4には約13μmの第一ソルダーレジスト層2-1の残渣が残っていた。

## 【0181】

<工程(C3)>

第一面の第一ソルダーレジスト層2-1に対して、工程(B)において薄膜化された領域に、活性光線6が照射されるようなパターンのフォトマスク5を用いて、酸素雰囲気下での非接触露光により、露光量400mJ/cm<sup>2</sup>で露光を行った。

## 【0182】

10

20

30

40

50

## &lt;工程(A2)&gt;

真空ラミネータを用いて、厚さ15μmのソルダーレジストフィルム(太陽インキ製造(株)製、商品名: PFR-800 AUS410)を、工程(C3)まで完了した回路基板1の第一面の第一ソルダーレジスト層2-1上に、真空熱圧着させた(ラミネート温度75°、吸引時間30秒、加圧時間10秒)。これにより、第一面の第二ソルダーレジスト層2-2が形成された。第一面の第二ソルダーレジスト層2-2では、絶縁層8表面からの厚さが30μmであった。

## 【0183】

## &lt;工程(C6)&gt;

第一面の第二ソルダーレジスト層2-2に対して、電子部品接続用接続パッド3の端部から400μm離れた外周よりも外側の領域に、活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

## 【0184】

## &lt;工程(D1)&gt;

1質量%の炭酸ナトリウム水溶液(液温度30°、スプレー圧0.15MPa)を用いて30秒間現像を行い、第一面の非露光部の第二ソルダーレジスト層2-2及び第二面の非露光部の第一ソルダーレジスト層2-1を除去した。これによって、アンダーフィル堰き止め用ダムを形成するとともに、第二ソルダーレジスト層2-2によって覆われていた第一ソルダーレジスト層2-1から露出した状態の電子部品接続用接続パッド3とその周囲の第一ソルダーレジスト層2-1が再び露出した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上に第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド3の表面下5.5μmまで第一ソルダーレジスト層2-1が充填されていた。工程(C3)における酸素雰囲気下での非接触露光により、第一面に配置された電子部品接続用接続パッド3間の第一ソルダーレジスト層2-1表面の光重合が抑制され、結果として、第一面の第一ソルダーレジスト層2-1の厚さが0.5μm減少していた。

## 【0185】

次に、第一面の第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2並びに第二面の第一ソルダーレジスト層2-1を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150°で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと20μmの第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2によって被覆され、その段差に相当する厚さ10μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ9.5μmの第一ソルダーレジスト層2-1が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上の一部に、厚さ38μm、直径500μmの第一ソルダーレジスト層2-1の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

## 【0186】

次に、第一面に配置された複数の電子部品接続用接続パッド3の端部から200μm離れた外周と該端部から400μm離れた外周との間の領域にある厚さ20μmの第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.05μmであった。また、隣接する電子部品接続用接続パッド3間の領域の第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.40μmであった。

## 【0187】

## (実施例13)

工程(C1)と工程(C2)の順番を入れ替えた以外は実施例12と同じ方法で、工程(A1)～工程(D1)までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上に第一ソルダーレジス

10

20

30

40

50

ト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド 3 の表面下 5 . 5  $\mu\text{m}$ まで第一ソルダーレジスト層 2 - 1 が充填されていた。工程 (C 3) における酸素雰囲気下での非接触露光により、第一面に配置された電子部品接続用接続パッド 3 間の第一ソルダーレジスト層 2 - 1 表面の光重合が抑制され、結果として、第一ソルダーレジスト層 2 - 1 の厚さが 0 . 5  $\mu\text{m}$ 減少していた。

【 0 1 8 8 】

次に、第一面の第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 並びに第二面の第一ソルダーレジスト層 2 - 1 を硬化させるため、露光量 1 0 0 0  $\text{mJ/cm}^2$  で全面露光し、続いて、150 で 60 分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ 15  $\mu\text{m}$  の導体配線 7 が厚さ 30  $\mu\text{m}$  と 20  $\mu\text{m}$  の第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 によって被覆され、その段差に相当する厚さ 10  $\mu\text{m}$  のアンダーフィル堰き止め用ダムが形成されていた。また、厚さ 15  $\mu\text{m}$  の電子部品接続用接続パッド 3 が露出しており、隣接する電子部品接続用接続パッド 3 間に厚さ 9 . 5  $\mu\text{m}$  の第一ソルダーレジスト層 2 - 1 が充填されていた。また、第二面では、厚さ 15  $\mu\text{m}$  の外部接続用接続パッド 4 上の一部に、厚さ 38  $\mu\text{m}$ 、直径 500  $\mu\text{m}$  の第一ソルダーレジスト層 2 - 1 の円形開口部が形成されていて、外部接続用接続パッド 4 の一部が露出していた。

【 0 1 8 9 】

次に、第一面に配置された複数の電子部品接続用接続パッド 3 の端部から 200  $\mu\text{m}$  離れた外周と該端部から 400  $\mu\text{m}$  離れた外周との間の領域にある厚さ 20  $\mu\text{m}$  の第一ソルダーレジスト層 2 - 1 の表面粗さを測定したところ、表面粗さ  $R_a$  は 0 . 05  $\mu\text{m}$  であった。また、隣接する電子部品接続用接続パッド 3 間の領域の第一ソルダーレジスト層 2 - 1 の表面粗さを測定したところ、表面粗さ  $R_a$  は 0 . 40  $\mu\text{m}$  であった。

【 0 1 9 0 】

( 実施例 1 4 )

工程 (C 3) における露光量を 200  $\text{mJ/cm}^2$  とした以外は実施例 1 2 と同じ方法で、工程 (A 1) ~ 工程 (D 1) までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド 3 及び外部接続用接続パッド 4 上に第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド 3 の表面下 6 . 0  $\mu\text{m}$ まで第一ソルダーレジスト層 2 - 1 が充填されていた。工程 (C 3) における酸素雰囲気下での非接触露光により、第一面に配置された電子部品接続用接続パッド 3 間の第一ソルダーレジスト層 2 - 1 表面の光重合が抑制され、結果として、第一ソルダーレジスト層 2 - 1 の厚さが 1 . 0  $\mu\text{m}$  減少していた。

【 0 1 9 1 】

次に、第一面の第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 並びに第二面の第一ソルダーレジスト層 2 - 1 を硬化させるため、露光量 1 0 0 0  $\text{mJ/cm}^2$  で全面露光し、続いて、150 で 60 分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ 15  $\mu\text{m}$  の導体配線 7 が厚さ 30  $\mu\text{m}$  と 20  $\mu\text{m}$  の第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 によって被覆され、その段差に相当する厚さ 10  $\mu\text{m}$  のアンダーフィル堰き止め用ダムが形成されていた。また、厚さ 15  $\mu\text{m}$  の電子部品接続用接続パッド 3 が露出しており、隣接する電子部品接続用接続パッド 3 間に厚さ 9 . 0  $\mu\text{m}$  の第一ソルダーレジスト層 2 - 1 が充填されていた。また、第二面では、厚さ 15  $\mu\text{m}$  の外部接続用接続パッド 4 上の一部に、厚さ 38  $\mu\text{m}$ 、直径 500  $\mu\text{m}$  の第一ソルダーレジスト層 2 - 1 の円形開口部が形成されていて、外部接続用接続パッド 4 の一部が露出していた。

【 0 1 9 2 】

次に、第一面に配置された複数の電子部品接続用接続パッド 3 の端部から 200  $\mu\text{m}$  離れた外周と該端部から 400  $\mu\text{m}$  離れた外周との間の領域にある厚さ 20  $\mu\text{m}$  の第一ソル

10

20

30

40

50

ダーレジスト層 2 - 1 の表面粗さを測定したところ、表面粗さ  $R_a$  は  $0.05 \mu m$  であった。また、隣接する電子部品接続用接続パッド 3 間の領域の第一ソルダーレジスト層 2 - 1 の表面粗さを測定したところ、表面粗さ  $R_a$  は  $0.50 \mu m$  であった。

【0193】

(実施例 15)

工程 (C3) における露光量を  $1000 mJ/cm^2$  とした以外は実施例 12 と同じ方法で、工程 (A1) ~ 工程 (D1) までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド 3 及び外部接続用接続パッド 4 上に第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド 3 の表面下  $5.0 \mu m$  まで第一ソルダーレジスト層 2 - 1 が充填されており、工程 (C3) における酸素の重合阻害による第一面の第一ソルダーレジスト層 2 - 1 の膜減りは確認されなかった。

10

【0194】

次に、第一面の第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 並びに第二面の第一ソルダーレジスト層 2 - 1 を硬化させるため、露光量  $1000 mJ/cm^2$  で全面露光し、続いて、 $150$  で 60 分間熱硬化処理を施した。光学顕微鏡で観察した結果、第一面では、厚さ  $15 \mu m$  の導体配線 7 が厚さ  $30 \mu m$  と  $20 \mu m$  の第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 によって被覆され、その段差に相当する厚さ  $10 \mu m$  のアンダーフィル堰き止め用ダムが形成されていた。また、厚さ  $15 \mu m$  の電子部品接続用接続パッド 3 が露出しており、隣接する電子部品接続用接続パッド 3 間に厚さ  $10.0 \mu m$  の第一ソルダーレジスト層 2 - 1 が充填されていた。また、第二面では、厚さ  $15 \mu m$  の外部接続用接続パッド 4 上の一部に、厚さ  $38 \mu m$ 、直径  $500 \mu m$  の第一ソルダーレジスト層 2 - 1 の円形開口部が形成されていて、外部接続用接続パッド 4 の一部が露出していた。

20

【0195】

次に、第一面に配置された複数の電子部品接続用接続パッド 3 の端部から  $200 \mu m$  離れた外周と該端部から  $400 \mu m$  離れた外周との間の領域にある厚さ  $20 \mu m$  の第一ソルダーレジスト層 2 - 1 の表面粗さを測定したところ、表面粗さ  $R_a$  は  $0.05 \mu m$  であった。また、隣接する電子部品接続用接続パッド 3 間の領域の第一ソルダーレジスト層 2 - 1 の表面粗さを測定したところ、表面粗さ  $R_a$  は  $0.30 \mu m$  であった。

30

【0196】

(実施例 16)

工程 (C3) において、密着露光方式にて露光を行った以外は、実施例 12 と同じ方法で、工程 (A1) ~ 工程 (D1) までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド 3 及び外部接続用接続パッド 4 上に第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド 3 の表面下  $5.0 \mu m$  まで第一ソルダーレジスト層 2 - 1 が充填されていた。工程 (C3) において、密着露光時のエア抜きを十分に行うことにより、非酸素雰囲気下で露光を行ったため、第一ソルダーレジスト層 2 - 1 表面が粗面化せず、結果として、第一ソルダーレジスト層 2 - 1 の厚さは減少しなかった。

40

【0197】

次に、第一面の第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 並びに第二面の第一ソルダーレジスト層 2 - 1 を硬化させるため、露光量  $1000 mJ/cm^2$  で全面露光し、続いて、 $150$  で 60 分間熱硬化処理を施した。光学顕微鏡で観察した結果、第一面では、厚さ  $15 \mu m$  の導体配線 7 が厚さ  $30 \mu m$  と  $20 \mu m$  の第一ソルダーレジスト層 2 - 1 及び第二ソルダーレジスト層 2 - 2 によって被覆され、その段差に相当する厚さ  $10 \mu m$  のアンダーフィル堰き止め用ダムが形成されていた。また、厚さ  $15 \mu m$  の電子部品接続用接続パッド 3 が露出しており、隣接する電子部品接続用接続パッド 3 間に厚さ  $10.0 \mu m$  の第一ソルダーレジスト層 2 - 1 が充填されていた。また、第二面では、厚さ  $15 \mu m$  の外部接続用接続パッド 4 上の一部に、厚さ  $38 \mu m$ 、直径  $500 \mu m$  の第一ソルダーレジスト層 2 - 1 の円形開口部が形成されていて、外部接続用接続パッド 4 の一部が露出していた。

50

$\mu\text{m}$  の第一ソルダーレジスト層 2 - 1 の円形開口部が形成されていて、外部接続用接続パッド 4 の一部が露出していた。

【 0 1 9 8 】

次に、第一面に配置された複数の電子部品接続用接続パッド 3 の端部から  $200\mu\text{m}$  離れた外周と該端部から  $400\mu\text{m}$  離れた外周との間の領域にある厚さ  $20\mu\text{m}$  の第一ソルダーレジスト層 2 - 1 の表面粗さを測定したところ、表面粗さ  $R_a$  は  $0.05\mu\text{m}$  であった。また、隣接する電子部品接続用接続パッド 3 間の第一ソルダーレジスト層 2 - 1 の表面粗さを測定したところ、表面粗さ  $R_a$  は  $0.10\mu\text{m}$  であった。

【 0 1 9 9 】

実施例 12 ~ 16 では、隣接する電子部品接続用接続パッド 3 間に十分な厚さの第一ソルダーレジスト層 2 - 1 があるため、電子部品を実装する際に半田による電気的な短絡が起きるのを確実に防ぐことができた。外部接続用接続パッド 4 上に第一ソルダーレジスト層 2 - 1 の残渣が存在しないため、外部電気基板に実装する際にも電気的絶縁不良が発生しない信頼性の高い配線基板を作製することができた。実施例 12 ~ 16 を比較すると、電子部品接続用接続パッド 3 間の第一ソルダーレジスト層 2 - 1 の表面が平滑である実施例 16 で製造された配線基板よりも、実施例 12 ~ 15 で製造された配線基板の方が、アンダーフィルとの密着性が高く、接続信頼性が優れていた。

【 0 2 0 0 】

実施例 17 ~ 21 は、図 7 - 1、図 7 - 2 および図 7 - 3 に示した配線基板の製造方法 (4) に関する例である。

【 0 2 0 1 】

(実施例 17)

<工程 (A1)>

セミアディティブ法を用いて、両表面に導体配線 7 が形成された回路基板 1 (面積  $170\text{mm} \times 200\text{mm}$ 、導体厚さ  $15\mu\text{m}$ 、基板厚さ  $0.4\text{mm}$  ) を作製した。表面 (第一面) には電子部品接続用接続パッド 3 として使用される線幅  $25\mu\text{m}$ 、間隔  $50\mu\text{m}$  の導体配線がある。裏面 (第二面) には外部接続用接続パッド 4 として使用される直径  $600\mu\text{m}$  の円形状の導体配線が形成されている。次に、真空ラミネータを用いて、厚さ  $15\mu\text{m}$  のソルダーレジストフィルム (太陽インキ製造 (株) 製、商品名: PFR-800 AUS410) を上記回路基板 1 の表面に、厚さ  $25\mu\text{m}$  のソルダーレジストフィルム (太陽インキ製造 (株) 製、商品名: PFR-800 AUS410) を上記回路基板 1 の裏面に真空熱圧着させた (ラミネート温度  $75^\circ\text{C}$  、吸引時間 30 秒、加圧時間 10 秒)。これにより、第一ソルダーレジスト層 2 - 1 が形成された。第一面の第一ソルダーレジスト層 2 - 1 では、絶縁層 8 表面からの厚さが  $20\mu\text{m}$  であり、電子部品接続用接続パッド 3 上の厚さは  $5\mu\text{m}$  であった。第二面の第一ソルダーレジスト層 2 - 1 では、絶縁層 8 表面からの厚さが  $38\mu\text{m}$  であり、外部接続用接続パッド 4 上の厚さが  $23\mu\text{m}$  であった。

【 0 2 0 2 】

<工程 (C1)>

第一面の第一ソルダーレジスト層 2 - 1 に対して、複数の電子部品接続用接続パッド 3 の端部から  $200\mu\text{m}$  離れた外周よりも外側の領域に活性光線 6 が照射されるようなパターンのフォトマスク 5 を用いて、露光量  $200\text{mJ/cm}^2$  で密着露光を行った。

【 0 2 0 3 】

<工程 (C2)>

第二面の第一ソルダーレジスト層 2 - 1 に対して、外部接続用接続パッド 4 上に直径  $500\mu\text{m}$  の円形開口部領域を設けるべく、円形開口部領域以外に活性光線 6 が照射されるようなパターンのフォトマスク 5 を用いて、露光量  $200\text{mJ/cm}^2$  で密着露光を行った。

【 0 2 0 4 】

<工程 (B)>

第一面及び第二面の第一ソルダーレジスト層 2 - 1 上の支持層フィルムを剥離した後、

10

20

30

40

50

10 質量%のメタケイ酸ナトリウム水溶液(液温25℃)を薄膜化処理液として用いて、第一面を上にして薄膜化処理液に回路基板1を25秒間浸漬させてミセル化処理(薄膜化処理)を行った。その後、ミセル除去液(液温25℃)のスプレーによるミセル除去処理、水洗処理(液温25℃)及び乾燥処理を行い、第一面の非露光部の第一ソルダーレジスト層2-1の厚さが電子部品接続用接続パッド3の表面下5.0μmになるまで、平均10μmの第一ソルダーレジスト層2-1を薄膜化した。光学顕微鏡で観察したところ、第一面の第一ソルダーレジスト層2-1の表面に処理ムラはなく、良好な面内均一性が得られた。一方、第二面の第一ソルダーレジスト層2-1も平均10μm薄膜化されていたが、薄膜化処理液中の気泡が第二面の非露光部の第一ソルダーレジスト層2-1に付着し、膜厚不均一となっている箇所があった。また、外部接続用接続パッド4には約13μmの第一ソルダーレジスト層2-1の残渣が残っていた。 10

【0205】

<工程(C3)>

第一面の第一ソルダーレジスト層2-1に対して、工程(B)において薄膜化された領域に、活性光線6が照射されるようなパターンのフォトマスク5を用いて、酸素雰囲気下での非接触露光により、露光量400mJ/cm<sup>2</sup>で露光を行った。

【0206】

<工程(D)>

1質量%の炭酸ナトリウム水溶液(液温度30℃、スプレー圧0.15MPa)を用いて30秒間現像を行い、第二面の非露光部の第一ソルダーレジスト層2-1を除去した。 20

【0207】

<工程(A2)>

真空ラミネータを用いて、厚さ15μmのソルダーレジストフィルム(太陽インキ製造(株)製、商品名: PFR-800 AUS410)を、工程(D)まで完了した回路基板1の第一面の第一ソルダーレジスト層2-1上に、真空熱圧着させた(ラミネート温度75℃、吸引時間30秒、加圧時間10秒)。これにより、第一面の第二ソルダーレジスト層2-2が形成された。第一面の第二ソルダーレジスト層2-2では、絶縁層8表面からの厚さが30μmであった。

【0208】

<工程(C6)>

第一面の第二ソルダーレジスト層2-2に対して、電子部品接続用接続パッド3の端部から400μm離れた外周よりも外側の領域に、活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。 30

【0209】

<工程(D2)>

1質量%の炭酸ナトリウム水溶液(液温度30℃、スプレー圧0.15MPa)を用いて30秒間現像を行い、第一面の非露光部の第二ソルダーレジスト層2-2を除去した。これによって、アンダーフィル堰き止め用ダムを形成するとともに、第二ソルダーレジスト層2-2によって覆われていた第一ソルダーレジスト層2-1から露出した状態の電子部品接続用接続パッド3とその周囲の第一ソルダーレジスト層2-1が再び露出した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上に第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド3の表面下5.5μmまで第一ソルダーレジスト層2-1が充填されていた。工程(C3)における酸素雰囲気下での非接触露光により、第一面に配置された電子部品接続用接続パッド3間の第一ソルダーレジスト層2-1表面の光重合が抑制され、結果として、第一面の第一ソルダーレジスト層2-1の厚さが0.5μm減少していた。 40

【0210】

次に、第一面の第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2並びに第二面の第一ソルダーレジスト層2-1を硬化させるため、露光量1000mJ/cm<sup>2</sup> 50

<sup>2</sup>で全面露光し、続いて、150で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと20μmの第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2によって被覆され、その段差に相当する厚さ10μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ9.5μmの第一ソルダーレジスト層2-1が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上の一とに、厚さ38μm、直径500μmの第一ソルダーレジスト層2-1の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

## 【0211】

10

次に、第一面に配置された複数の電子部品接続用接続パッド3の端部から200μm離れた外周と該端部から400μm離れた外周との間の領域にある厚さ20μmの第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.05μmであった。また、隣接する電子部品接続用接続パッド3間に厚さ20μmの第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.40μmであった。

## 【0212】

## (実施例18)

工程(C1)と工程(C2)の順番を入れ替えた以外は実施例17と同じ方法で、工程(A1)～工程(D2)までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上に第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド3の表面下5.5μmまで第一ソルダーレジスト層2-1が充填されていた。工程(C3)における酸素雰囲気下での非接触露光により、第一面に配置された電子部品接続用接続パッド3間に第一ソルダーレジスト層2-1表面の光重合が抑制され、結果として、第一面の第一ソルダーレジスト層2-1の厚さが0.5μm減少していた。

20

## 【0213】

次に、第一面の第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2並びに第二面の第一ソルダーレジスト層2-1を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと20μmの第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2によって被覆され、その段差に相当する厚さ10μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ9.5μmの第一ソルダーレジスト層2-1が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上の一とに、厚さ38μm、直径500μmの第一ソルダーレジスト層2-1の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

30

## 【0214】

40

次に、第一面に配置された複数の電子部品接続用接続パッド3の端部から200μm離れた外周と該端部から400μm離れた外周との間の領域にある厚さ20μmの第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.05μmであった。また、隣接する電子部品接続用接続パッド3間に厚さ20μmの第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.40μmであった。

## 【0215】

## (実施例19)

工程(C3)における露光量を200mJ/cm<sup>2</sup>とした以外は実施例17と同じ方法で、工程(A1)～工程(D2)までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上に第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2の残渣は見られなかった。また、

50

第一面に配置された電子部品接続用接続パッド3の表面下6.0μmまで第一ソルダーレジスト層2-1が充填されていた。工程(C3)における酸素雰囲気下での非接触露光により、第一面に配置された電子部品接続用接続パッド3間の第一ソルダーレジスト層2-1表面の光重合が抑制され、結果として、第一面の第一ソルダーレジスト層2-1の厚さが1.0μm減少していた。

【0216】

次に、第一面の第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2並びに第二面の第一ソルダーレジスト層2-1を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと20μmの第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2によって被覆され、その段差に相当する厚さ10μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ9.0μmの第一ソルダーレジスト層2-1が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上的一部に、厚さ38μm、直径500μmの第一ソルダーレジスト層2-1の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

【0217】

次に、第一面に配置された複数の電子部品接続用接続パッド3の端部から200μm離れた外周と該端部から400μm離れた外周との間の領域にある厚さ20μmの第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.05μmであった。また、隣接する電子部品接続用接続パッド3間の領域の第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.50μmであった。

【0218】

(実施例20)

工程(C3)における露光量を1000mJ/cm<sup>2</sup>とした以外は実施例17と同じ方法で、工程(A1)～工程(D2)までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上に第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド3の表面下5.0μmまで第一ソルダーレジスト層2-1が充填されており、工程(C3)における酸素の重合阻害による第一面の第一ソルダーレジスト層2-1の膜減りは確認されなかった。

【0219】

次に、第一面の第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2並びに第二面の第一ソルダーレジスト層2-1を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150で60分間熱硬化処理を施して、配線基板を得た。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと20μmの第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2によって被覆され、その段差に相当する厚さ10μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ10.0μmの第一ソルダーレジスト層2-1が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上的一部に、厚さ38μm、直径500μmの第一ソルダーレジスト層2-1の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

【0220】

次に、第一面に配置された複数の電子部品接続用接続パッド3の端部から200μm離れた外周と該端部から400μm離れた外周との間の領域にある厚さ20μmの第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.05μmであった。また、隣接する電子部品接続用接続パッド3間の領域の第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.30μmであった。

## 【0221】

## (実施例21)

工程(C3)において、密着露光方式にて露光を行った以外は、実施例17と同じ方法で、工程(A1)～工程(D2)までを実施した。光学顕微鏡で観察した結果、第一面及び第二面ともに電子部品接続用接続パッド3及び外部接続用接続パッド4上に第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2の残渣は見られなかった。また、第一面に配置された電子部品接続用接続パッド3の表面下5.0μmまで第一ソルダーレジスト層2-1が充填されていた。工程(C3)において、密着露光時のエア抜きを十分に行うことにより、非酸素雰囲気下で露光を行ったため、第一ソルダーレジスト層2-1表面が粗面化せず、結果として、第一ソルダーレジスト層2-1の厚さは減少しなかった。

10

## 【0222】

次に、第一面の第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2並びに第二面の第一ソルダーレジスト層2-1を硬化させるため、露光量1000mJ/cm<sup>2</sup>で全面露光し、続いて、150℃で60分間熱硬化処理を施した。光学顕微鏡で観察した結果、第一面では、厚さ15μmの導体配線7が厚さ30μmと20μmの第一ソルダーレジスト層2-1及び第二ソルダーレジスト層2-2によって被覆され、その段差に相当する厚さ10μmのアンダーフィル堰き止め用ダムが形成されていた。また、厚さ15μmの電子部品接続用接続パッド3が露出しており、隣接する電子部品接続用接続パッド3間に厚さ10.0μmの第一ソルダーレジスト層2-1が充填されていた。また、第二面では、厚さ15μmの外部接続用接続パッド4上的一部に、厚さ38μm、直径500μmの第一ソルダーレジスト層2-1の円形開口部が形成されていて、外部接続用接続パッド4の一部が露出していた。

20

## 【0223】

次に、第一面に配置された複数の電子部品接続用接続パッド3の端部から200μm離れた外周と該端部から400μm離れた外周との間の領域にある厚さ20μmの第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.05μmであった。また、隣接する電子部品接続用接続パッド3間の第一ソルダーレジスト層2-1の表面粗さを測定したところ、表面粗さRaは0.10μmであった。

## 【0224】

実施例17～21では、隣接する電子部品接続用接続パッド3間に十分な厚さの第一ソルダーレジスト層2-1があるため、電子部品を実装する際に半田による電気的な短絡が起きるのを確実に防ぐことができた。外部接続用接続パッド4上に第一ソルダーレジスト層2-1の残渣が存在しないため、外部電気基板に実装する際にも電気的絶縁不良が発生しない信頼性の高い配線基板を作製することができた。実施例17～21を比較すると、電子部品接続用接続パッド3間の第一ソルダーレジスト層2-1の表面が平滑である実施例21で製造された配線基板よりも、実施例17～20で製造された配線基板の方が、アンダーフィルとの密着性が高く、接続信頼性が優れていた。

30

## 【0225】

実施例22～25は、図8-1、図8-2および図8-3に示した配線基板の製造方法(5)に関する例である。

40

## 【0226】

## (実施例22)

## &lt;工程(A1)&gt;

セミアディティブ法を用いて、両表面に導体配線7が形成された回路基板1(面積170mm×200mm、導体厚さ15μm、基板厚さ0.4mm)を作製した。表面(第一面)には電子部品接続用接続パッド3として使用される線幅25μm、間隔50μmの導体配線がある。裏面(第二面)には外部接続用接続パッド4として使用される直径600μmの円形状の導体配線が形成されている。次に、真空ラミネータを用いて、厚さ15μmのソルダーレジストフィルム(太陽インキ製造(株)製、商品名:PF800AUS410)を上記回路基板1の表面に、厚さ25μmのソルダーレジストフィルム(太

50

陽インキ製造（株）製、商品名：P F R - 8 0 0 A U S 4 1 0 を上記回路基板1の裏面に真空熱圧着させた（ラミネート温度75、吸引時間30秒、加圧時間10秒）。これにより、第一ソルダーレジスト層2-1が形成された。第一面の第一ソルダーレジスト層2-1では、絶縁層8表面からの厚さが20μmであり、電子部品接続用接続パッド3上の厚さは5μmであった。第二面の第一ソルダーレジスト層2-1では、絶縁層8表面からの厚さが38μmであり、外部接続用接続パッド4上の厚さが23μmであった。

【0227】

<工程（C2）>

第二面の第一ソルダーレジスト層2-1に対して、外部接続用接続パッド4上に直径500μmの円形開口部領域を設けるべく、円形開口部領域以外に活性光線6が照射される10ようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

【0228】

<工程（B）>

第一面及び第二面の第一ソルダーレジスト層2-1上の支持層フィルムを剥離した後、10質量%のメタケイ酸ナトリウム水溶液（液温25）を薄膜化処理液として用いて、第一面を上にして薄膜化処理液に回路基板1を25秒間浸漬させてミセル化処理（薄膜化処理）を行った。その後、ミセル除去液（液温25）のスプレーによるミセル除去処理、水洗処理（液温25）及び乾燥処理を行い、第一面の非露光部の第一ソルダーレジスト層2-1の厚さが電子部品接続用接続パッド3の表面下5.0μmになるまで、平均10μmの第一ソルダーレジスト層2-1を薄膜化した。光学顕微鏡で観察したところ、第一面の第一ソルダーレジスト層2-1の表面に処理ムラはなく、良好な面内均一性が得られた。一方、第二面の第一ソルダーレジスト層2-1も平均10μm薄膜化されていたが、薄膜化処理液中の気泡が第二面の非露光部の第一ソルダーレジスト層2-1に付着し、膜厚不均一となっている箇所があった。また、外部接続用接続パッド4には約13μmの第一ソルダーレジスト層2-1の残渣が残っていた。

【0229】

<工程（C3）>

第一面の第一ソルダーレジスト層2-1に対して、工程（B）において薄膜化された領域に、活性光線6が照射されるようなパターンのフォトマスク5を用いて、酸素雰囲気下での非接触露光により、露光量400mJ/cm<sup>2</sup>で露光を行った。

【0230】

<工程（A2）>

真空ラミネータを用いて、厚さ20μmのソルダーレジストフィルム（太陽インキ製造（株）製、商品名：P F R - 8 0 0 A U S 4 1 0 ）を、工程（C）まで完了した回路基板1の第一面の第一ソルダーレジスト層2-1上に、真空熱圧着させた（ラミネート温度75、吸引時間30秒、加圧時間10秒）。これにより、第一面の第二ソルダーレジスト層2-2が形成された。第一面の第二ソルダーレジスト層2-2では、絶縁層8表面からの厚さが30μmであった。

【0231】

<工程（C6）>

第一面の第二ソルダーレジスト層2-2に対して、電子部品接続用接続パッド3の端部から400μm離れた外周よりも外側の領域に、活性光線6が照射されるようなパターンのフォトマスク5を用いて、露光量200mJ/cm<sup>2</sup>で密着露光を行った。

【0232】

<工程（B3）>

第一面の第二ソルダーレジスト層2-2上の支持層フィルムを剥離した後、10質量%のメタケイ酸ナトリウム水溶液（液温25）を薄膜化処理液として用いて、第一面を上にして薄膜化処理液に回路基板1を25秒間浸漬させてミセル化処理（薄膜化処理）を行った。その後、ミセル除去液（液温25）のスプレーによるミセル除去処理、水洗処理

10

20

30

40

50

(液温 25 ) 及び乾燥処理を行い、第一面の非露光部の第二ソルダーレジスト層 2 - 2 の厚さが電子部品接続用接続パッド 3 の表面上 5 . 0  $\mu\text{m}$  になるまで、平均 10  $\mu\text{m}$  の第二ソルダーレジスト層 2 - 2 を薄膜化した。光学顕微鏡で観察したところ、第一面の第二ソルダーレジスト層 2 - 2 の表面に処理ムラはなく、良好な面内均一性が得られた。一方、第二面の第一ソルダーレジスト層 2 - 1 も平均 10  $\mu\text{m}$  薄膜化されていたが、薄膜化処理液中の気泡が第二面の非露光部の第一ソルダーレジスト層 2 - 1 に付着し、膜厚不均一となっている箇所があった。また、外部接続用接続パッド 4 には約 3  $\mu\text{m}$  の第一ソルダーレジスト層 2 - 1 の残渣が残っていた。

【 0233 】

< 工程 ( C7 ) >

10

第一面の第二ソルダーレジスト層 2 - 2 に対して、電子部品接続用接続パッド 3 の端部から 200  $\mu\text{m}$  離れた外周よりも外側の領域に、活性光線 6 が照射されるようなパターンのフォトマスク 5 を用いて、酸素雰囲気下での非接触露光により、露光量 400  $\text{mJ/cm}^2$  で露光を行った。

【 0234 】

< 工程 ( D1 ) >