(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3883713号

(P3883713)

(45) 発行日 平成19年2月21日(2007.2.21)

(24) 登録日 平成18年11月24日(2006.11.24)

(51) Int.CI.

F 1

**H04B** 1/707 (2006.01)

**H04L** 7/00 (2006.01)H04J 13/00

H04L 7/00

D

C

請求項の数 1 (全 16 頁)

(21) 出願番号

特願平10-282258

(22) 出願日

平成10年10月5日(1998.10.5)

(65) 公開番号

特開2000-115025(P2000-115025A)

(43) 公開日

平成12年4月21日(2000.4.21)

審査請求日

平成14年7月30日(2002.7.30)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100074099

弁理士 大菅 義之

(74) 代理人 100067987

弁理士 久木元 彰

(72) 発明者 松山 幸二

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 清水 昌彦

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

最終頁に続く

(54) 【発明の名称】拡散符号及びタイミング検出装置及びその方法

## (57) 【特許請求の範囲】

## 【請求項 1】

受信信号と所定の共通の拡散符号との間で相対的にタイミングをずらして相関を求める第1相関算出を行い、該第1相関算出により得られたタイミングに基づいて複数種類の拡散符号との間で相関を求める第2相関算出を行う、直接拡散CDMAに対応した移動局において、

受信信号を記憶する記憶部と、

該第1相関算出のために行う前記受信信号と前記所定の共通の拡散符号との間の演算は、該受信信号を該記憶部に記憶せずに行い、該第2相関算出は、前記第1相関算出後に該記憶部に記憶した受信信号を用い、かつ、前記第1相関算出により得られた複数のタイミングについて相関を求ることを許容する制御部と、

を備えたことを特徴とする移動局。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、スペクトラム通信システム、あるいは、CDMA通信システムにおいて、逆拡散符号及び逆拡散タイミングの検出装置、及びその方法に関する。

## 【0002】

## 【従来の技術】

基地局から移動局への通信において、非同期CDMA方式では初期同期もしくはハンドオ

ーバー時における基地局補足において、逆拡散符号及び逆拡散タイミングを検出する必要がある。ここで、ハンドオーバー時とは、移動端末を持ったユーザがある基地局から他の基地局に移動することである。この場合、移動局（移動端末）は、非同期で信号を送出している各基地局からの信号を取得するために、その基地局が使っている逆拡散符号及び逆拡散タイミングを検出する必要があるが、そのための信号として、止り木チャネルと呼ばれる、同期確立用のチャネルが設けられている。止り木チャネルの一部または、全てのデータシンボルの拡散符号は、各基地局共通もしくは、いくつかの候補しかないので、所定の逆拡散符号を使用することによって、止り木チャネルを補足することができる。以下、止り木チャネルの一部または、全てのデータシンボルの拡散符号が、各基地局共通もしくは、少数の候補しかしないシステムを前提に説明するが、これは、止り木チャネルの拡散符号が多種類あると、同期確立に必要な時間が多く必要になり、実用的ではないからである。しかし、止り木チャネルの補足方法は多くの種類が考えられるので、必ずしも止り木チャネルの拡散符号が各基地共通あるいは、少数のみしか設けられていない必要はなく、以下に説明する本発明の構成に影響を与えるものではない。

#### 【0003】

止り木チャネルの一部あるいは全てのデータシンボルの拡散符号が各基地共通あるいは、少数のみの場合の同期確立の手順としては以下のようになる。

1. 止り木チャネルの拡散符号が各基地局共通の場合は逆拡散タイミングはこの共通の符号の一部をマッチドフィルタ等の相関器で相関値の検出を行い、最大の相関値となるタイミングを同期タイミングとして検出することができる。

2. 止り木チャネルの拡散符号にいくつかの候補がある場合は、候補となる拡散符号全てに対して上記1の動作を行うことで最大の相関値となる拡散符号とタイミングを同期タイミングとして検出することができる。なお、CDMA通信を含むスペクトラム拡散通信においては、拡散符号と逆拡散符号とは符号としては同じ物である。

3. 止り木チャネルの拡散符号の一部が各基地局共通の場合は、はじめに各基地局共通の符号により逆拡散タイミングを補足し、次に共通でない符号に対していくつかの候補の拡散符号で逆拡散し、各基地局共通でない符号を検出することもできる。

#### 【0004】

1、2、3の処理の後、基地局固有の符号を補足するとき、基地局固有の拡散符号に幾つかの候補がある場合は、2.の処理と同じ処理であると考えることが出来る。幾つかの候補の拡散符号での相関をとる場合、候補分の逆拡散を繰り返す。

#### 【0005】

止り木チャネルの拡散符号に幾つかの候補があることと基地局固有の符号に幾つかの候補があることは、処理としては同等なため、以降は基地局固有の拡散符号を検出する構成について説明する。この場合、止り木チャネルの場合と異なって、拡散符号は各基地局毎に異なっており、その数も少数とは限らない。

#### 【0006】

##### 【発明が解決しようとする課題】

初期同期およびクロック同期がとれていない場合、候補分の逆拡散を繰り返す処理に時間がかかると、基地局と移動局のクロックタイミング用の局部発振器の偏差のため、徐々にタイミングがずれることにより、全候補の符号の正しい相関値が得られない可能性がある。また、処理中にフェージングの影響により受信電力が変化し、正しく相関値の比較ができる可能性がある。

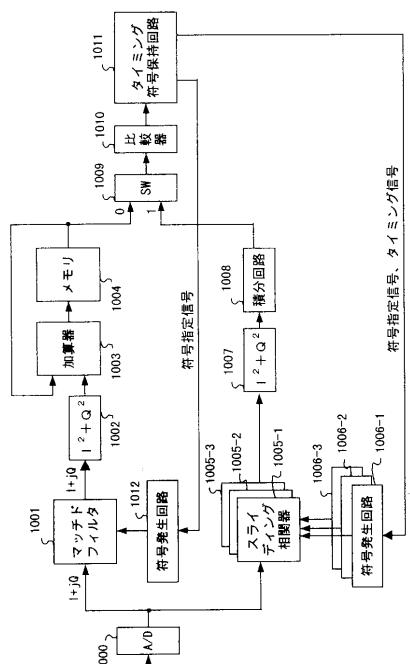

#### 【0007】

この課題を解決する手段として、従来は図10のような構成が提案されている。

まず、止り木チャネルによる同期タイミングを取得するため、受信された信号は、A/D変換器1000によって、デジタル信号に変換される。なお、以下の説明において、受信信号の処理はデジタル処理することを前提に説明するが、必ずしもデジタルである必要はなく、アナログ処理する構成とすることも可能である。受信されたIフェーズとQフェーズの信号は、それぞれマッチドフィルタ1001及びスライディング相関器1005-1

10

20

30

40

50

～1005-3に送られる。同図で $I + jQ$ と記載されているのは、本来、Iフェーズの信号とQフェーズの信号をそれぞれ処理する構成を記載すべきところを省略して記載したものである。Iフェーズの信号のキャリアとQフェーズの信号のキャリアとは、互いに位相が90°ずれているので、Iフェーズの信号とQフェーズの信号とを $I + jQ$ というように、複素数として記述することにより、システムの理解をしやすくするものである。

#### 【0008】

マッチドフィルタ1001は、本来Iフェーズ用とQフェーズ用とが設けられているが、上記した理由により、あたかも複素数の信号（複素信号）を1つのマッチドフィルタ1001で処理するように記載している。マッチドフィルタ1001には、タイミング符号保持回路1011からの符号指定信号が入力されることにより、逆拡散符号を生成する符号発生回路1012から逆拡散符号が入力される。マッチドフィルタ1001は、逆拡散タイミングをずらしながら相關値を得て電力化器1002に入力する。電力化器1002でIフェーズの相關値とQフェーズの相關値の2乗和が算出される。これは、フェージング等の影響により、IフェーズやQフェーズの信号の位相が回転することにより、後段の積算値の算出の際に、不当に相關値の和が小さな値になってしまわないようとするためである。不当に相關値の和が小さな値になってしまふと、本来正しい拡散符号を使って、正しいタイミングで逆拡散を行ったとしても、相關値の和が小さいことにより、逆拡散符号とタイミングが正しいことを認識することが出来なくなってしまうためである。

#### 【0009】

電力化器1002で上記処理を施された相關値は、加算器1003及びメモリ1004からなる積算部に入力され、入力信号の複数シンボル分の相關値が積算される。入力信号の複数シンボルにわたって積算された相關値は、スイッチ1009に入力される。止り木チャネルを検出している場合には、メモリ1004からの相關値の積算値が比較器1010に入力される。比較器1010には、各タイミングで得られた相關値の積算値が入力される。比較器1010は、積算値が所定の値より大きいか否かを判断し、信号を出力する。止り木チャネルの拡散符号が各基地局共通の場合には、正しい逆拡散タイミングの取得のためのみの動作となる。タイミング符号保持回路1011は、比較器1010からの出力を基に、止り木チャネルの捕捉に使用した逆拡散符号が正しいか、あるいは、正しい逆拡散タイミングはどれかを判断し、逆拡散符号が正しくない場合には、符号発生回路1012に別の逆拡散符号を出力させて、マッチドフィルタ1001で同期タイミングの検出を繰り返させる。

#### 【0010】

タイミング符号保持回路1011は、止り木チャネルの拡散符号が各基地局に共通の場合には、マッチドフィルタ1001から出力される、各逆拡散タイミングの相關値の積算値を比較し、正しい逆拡散タイミングを判断して、同期検出を行う。止り木チャネルの拡散符号が複数ある場合には、止り木チャネルの拡散符号の候補の数だけ、相關値の積算値を保持しておき、最も積算値の大きい場合に、正しい逆拡散符号を使い、正しい逆拡散タイミングで処理を行ったとして、同期検出を行う。

#### 【0011】

タイミング符号保持回路1011は、止り木チャネルの捕捉で得た、同期タイミング信号を符号発生回路1006-1～1006-3に送ると共に、各基地局独自の拡散符号を検出するために、逆拡散符号の候補となる符号を符号発生回路1006-1～1006-3に、取得した同期タイミングで出力させる。スライディング相関器1005-1～1005-3は、マッチドフィルタ1001とは異なり、所定のタイミングにおいてのみの相關値しか検出できない構成となっているが、マッチドフィルタ1001よりもかなりハードウェア構成が小さくなるので、回路構成上、また電力消費量の面からもマッチドフィルタ1001を使うよりも有利である。スライディング相関器1005-1～1005-3の一構成例については後述する。

#### 【0012】

同図の構成においては、スライディング相関器1005-1～1005-3及び符号発生

10

20

30

40

50

回路 1006-1 ~ 1006-3 は 3 つ設けられており、タイミング符号保持回路 1011 で取得された同期タイミングを前後に僅かにずらしたタイミングでも逆拡散による相関値を取得する構成としている。これは、基地局のクロックと移動局のクロックの周波数の偏差により、一度同期タイミングを取得しても、次第にずれが生じることを考慮に入れたものである。この構成によれば、タイミングのずれが少々生じても逆拡散を上手く行うことが出来ることが知られている。

#### 【0013】

スライディング相関器 1005-1 ~ 1005-3 から出力された相関値は、電力化器 1007 で、前述したように、I フェーズの相関値と Q フェーズの相関値の 2 乗和に変換される。そして、積分回路 1008 で、入力信号の逆拡散符号の複数のシンボル分の 2 乗和を積算し、スイッチ 1009 に入力する。各基地局に固有の拡散符号を検出する場合には、スイッチ 1009 は、積分回路 1008 からの信号を比較器 1010 に出力するように切り換えられる。比較器 1010 では、2 乗和の積算値が所定値よりも大きいか否かを判断し、結果をタイミング符号保持回路 1011 に送る。タイミング符号保持回路 1011 では、比較器 1010 の比較結果から、相関値の積算値の最も大きいものに対応する逆拡散符号がこれから受信しようとする基地局が使用している拡散符号であると判断し、以後、この逆拡散符号を使用して、通信を行う。

#### 【0014】

このように、同図の構成では、クロックタイミング用の局部発振器の偏差に応じた範囲の逆拡散を複数の相関器を用い、初期に検出したタイミングの前後でも逆拡散を行い、そのなかで最も大きい相関値を選ぶ。しかし、この方法では、タイミングずれにたいしては有効だが、フェージングの影響は除去できない。

#### 【0015】

本発明は、タイミングずれ及びフェージングの影響を無くして、通信に必要な逆拡散符号と、逆拡散のタイミングを検出することのできる装置を提供することである。

#### 【0016】

##### 【課題を解決するための手段】

本発明の検出装置は、直接拡散 C D M A 信号の復調器において、送信されてきた信号を記憶する記憶手段と、逆拡散符号の候補となる符号を順次生成する符号発生手段と、該記憶手段に記憶された信号を読み出し、該符号で逆拡散する相関値取得手段と、該相関値取得手段で得られた相関値が最大もしくは基準値以上となる場合に対応するときに、逆拡散に使用した符号を送信側の拡散符号として検出する検出手段とを備えることを特徴とする。

#### 【0017】

本発明の検出方法は、直接拡散 C D M A 信号の復調器における拡散符号及び逆拡散タイミング検出方法であって、( a ) 送信されてきた信号を記憶するステップと、( b ) 逆拡散符号の候補となる符号を順次生成するステップと、( c ) 該ステップ( a )で記憶された信号を読み出し、該符号で逆拡散するステップと、( d ) 該ステップ( c )で得られた相関値が最大もしくは基準値以上となる場合に対応するときに、逆拡散に使用した符号を送信側の拡散符号として検出するステップとを備えることを特徴とする。

#### 【0018】

本発明の第 2 の側面の検出装置は、スペクトラム拡散通信における復調器において、送信されてきた信号を記憶する記憶手段と、逆拡散符号の候補となる符号を生成する符号発生手段と、該記憶手段に記憶された信号を読み出し、該符号の位相をずらしながら逆拡散する相関値取得手段と、該相関値取得手段で得られた相関値が最大もしくは基準値以上となる場合に対応するときに、逆拡散に使用した符号の位相を逆拡散タイミングとして検出する検出手段とを備えることを特徴とする。

#### 【0019】

本発明によれば、受信した信号を一旦、メモリ等の記憶手段に記憶し、記憶手段から信号を読み出して、相関値を取るようにしている。従って、受信した信号をそのまま逆拡散する場合に、フェージング等の影響によって相関値が信号の強度の揺らぎに伴い、相関値の

10

20

30

40

50

大きさが変化してしまうことを防ぐことができる。従って、複数の拡散符号に対して、相関値を求める間に信号の強度が変わり、本来、最大の相関値を示すべき符号の相関値が、本来小さな相関値となるべき符号の相関値より小さくなってしまうことがない。すなわち、正確に符号の判別を行うことが出来る。

#### 【0020】

また、同様に、逆拡散タイミングを検出する場合にも、メモリに記憶した信号を使用して相関値を得、最大もしくは基準値以上の値に対応する場合の相関値が得られたときの逆拡散タイミングを取得する。よって、フェージングによる影響を除去することが出来、正確なタイミング検出を行うことが出来る。

#### 【0021】

10

#### 【発明の実施の形態】

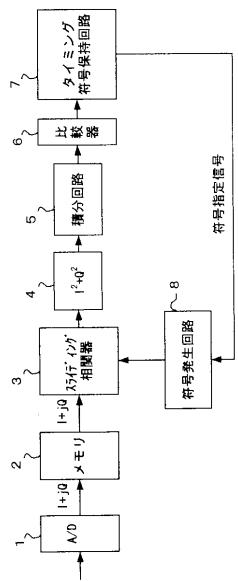

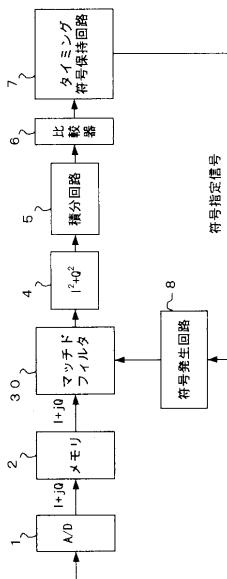

図1は、共通のコードおよび基地局固有のコードをスライディング相関器によって行う、本発明の第1の実施形態を示す図である。

#### 【0022】

主に符号発生回路8、スライディング相関器3、メモリ2、積分回路5、比較器6、タイミング符号保持回路7からなる。なお、以下の説明において、前述した意味での複素信号を処理する構成を説明する。

#### 【0023】

動作手順を以下に示す。

1. 止り木チャネルの受信複素信号をA/D変換器1でデジタル信号に変換した後、電圧値をメモリ2に保存する。メモリ2から順次電圧データを読み出し、スライディング相関器3により逆拡散する。このとき符号発生回路8は共通の拡散符号を順次タイミングをシフトして発生する。電力化器4で、複素信号の2乗絶対値を生成する。雑音の影響を低減するため積分回路5で複数のシンボルに対し積算し、実質的な平均化を行う。比較器6により最大の、または、大きなものからm個のタイミングを逆拡散タイミングとしてタイミング符号保持回路7に保持する。

20

#### 【0024】

2. 各基地局に固有の拡散符号で拡散された複素信号に対し、手順1で検出したm通りのタイミングに対して、順次候補となる符号によりスライディング相関器3を用いて相関値を検出する。このとき符号発生回路8は基地局固有の拡散符号の候補k通りを発生する。

30

#### 【0025】

3. 比較器6により相関出力が大きなものからn個の拡散符号を検出する。タイミングと符号と相関値を、タイミング符号保持回路7に保持する。

3で得られた最大の相関値が得られるタイミングおよび符号を、逆拡散タイミング及び基地局の符号として逆拡散符号及び逆拡散タイミングの検出を終了する。なお、複数のスライディング相関器を用い、それぞれに異なるタイミングでの逆拡散を平行して行わせることによって、処理時間を短縮することもできる。

#### 【0026】

すなわち、A/D変換された入力複素信号は、電圧値をメモリ2に記憶され、この記憶された入力複素信号を使って、基地局固有の拡散符号の特定や逆拡散タイミングの検出を行う。逆拡散タイミングは、入力複素信号がメモリ2に記憶された時点を不図示のクロックで計測しておき、基地局固有の拡散符号が繰り返す時間を周期として、伝送されてくる信号に対して逆拡散を行うタイミングを取得する。つまり、メモリ2から複素信号が読み出されるタイミングと、符号発生回路8が逆拡散符号を出力するタイミングの差を保持しておき、相関値の高くなるタイミングの差を同期する場合として特定し、この差を入力複素信号がメモリ2に記憶されたタイミングと合わせて考慮することにより、送信されてくる信号に対する同期タイミングとする。また、基地局固有の拡散符号の特定は、符号発生回路8が順次、候補となる逆拡散符号を出力し、相関値が高くなる符号を、基地局固有の拡散符号とし、後の通信における逆拡散に使用する。

40

#### 【0027】

50

符号発生回路 8 が逆拡散符号を出力するタイミングを変えるのは、スライディング相関器 3 が相関値の検出は可能であるが、タイミングを検出する構成を有していないために、特定のタイミングにおける相関値しか得られないからである。従って、逆拡散符号をスライディング相関器 3 に入力するタイミングを変えることによって、様々なタイミングにおける相関値を得るようにしている。電力化器 4 は、前述した理由と同じ理由で設けられいる。

#### 【 0 0 2 8 】

このように、拡散符号の特定及び逆拡散タイミングの特定に使用する信号をメモリ 2 に記憶しておき、全てのタイミング及び全ての候補の符号に対し、処理が終わるまで、メモリ 2 に記憶されている信号を使用することにより、フェージングの影響を除去することができる。すなわち、繰り返し伝送されてくる伝送信号を受信しながら、受信した信号に対し、タイミング検出及び符号の特定を行っていると、移動局が移動することにより、フェージングが生じ、信号の強度が変化する。従って、信号に逆拡散符号を掛けて得る相関値も信号の強度の変化を反映して、値が大きくなったり小さくなったりする。よって、例えば、同期したタイミングで逆拡散をした場合の相関値を得た時の信号の強度が小さい場合には、他の同期していないタイミングでの相関値よりも小さくなってしまう可能性がある。すると、相関値の大小で同期タイミングを正確に検出することが不可能となってしまう。基地局固有の拡散符号を検出する場合も同様であって、正しい逆拡散符号を使用している場合の相関値が、フェージングの影響により、誤った逆拡散符号を使用している場合よりも小さくなってしまう可能性がある。

10

20

#### 【 0 0 2 9 】

ところが、メモリ 2 に記憶された信号を使用すれば、逆拡散を行う信号の強度が、タイミングの検出、あるいは、符号の特定の間変化しないので、上記したような問題は生じない。すなわち、フェージングによる影響を全く無くすことが出来る。

#### 【 0 0 3 0 】

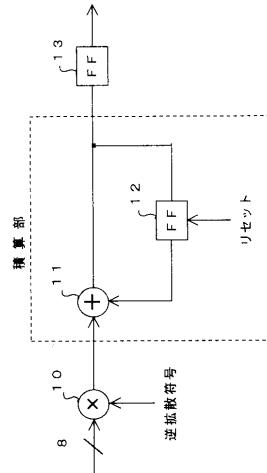

図 2 は、スライディング相関器の構成例を示す図である。

スライディング相関器は、入力信号に逆拡散符号をチップ毎に乗算する乗算器 10、加算器 11 とフリップフロップ 12 とからなる積算部、及び積算結果を保持するフリップフロップ 13 とからなる。入力する信号はアナログでもデジタルでも同様であるが、ここでは、8 ビットのデジタル信号を想定している。乗算器 10 は、例えば、排他論理和器 (EX - OR) であり、入力した信号に、逆拡散符号を乗算して、逆拡散を行うものである。このとき、逆拡散符号は、所定のタイミングで乗算器 10 に入力される。この所定のタイミングが逆拡散タイミングとなる。乗算器 10 で逆拡散された信号は、積算部に入力される。先ず、信号は、加算器 11 を通って、フィードバック経路を介して、フリップフロップ 12 に入力される。フリップフロップ 12 の値は、逆拡散符号の 1 チップ分遅れて、加算器 11 に入力され、次に入力された逆拡散符号の 1 チップ分の逆拡散値と加算される。これを、入力信号の 1 シンボル分行って、積算値が得られると、フリップフロップ 12 にリセット信号が入力される。また、積算値は、フリップフロップ 13 に保持されて、出力される。

30

#### 【 0 0 3 1 】

このように、スライディング相関器は、マッチドフィルタと異なり、あるタイミングで入力された逆拡散符号に対してのみ相関値を検出して、出力するものである。

40

#### 【 0 0 3 2 】

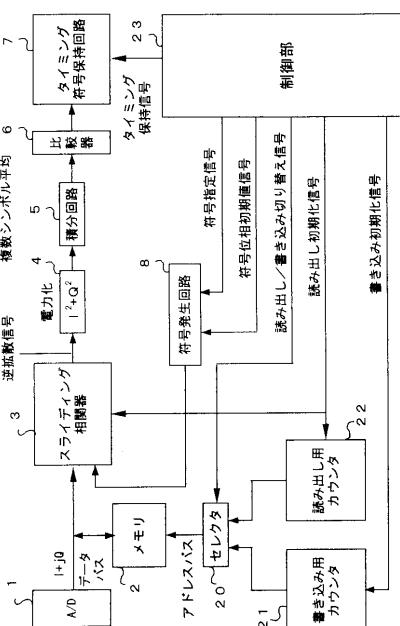

図 3 は、第 1 の実施形態のメモリアクセス動作を行う構成を説明する図である。

同図において、図 1 と同じ構成要素には同じ参照符号を付している。

#### 【 0 0 3 3 】

図 1 で説明した構成のほかに、メモリ 2 に入力信号を記憶させたり、メモリ 2 から信号を読み出す処理を行うための制御部 23 が設けられる。制御部 23 は、メモリ 2 に読み出しあるいは書き込みのいずれをすべきかの指示の入力を切り替えるセレクタ 20 に、いずれを行うべきかを示す読み出し / 書き込み切り替え信号を入力する。メモリ 2 に入力信号を

50

記憶する場合には、制御部23は、書き込み用カウンタ（アドレスをカウントする）21に書き込み初期化信号を入力して、書き込みを行うべき先頭アドレスを出力させる。このとき、セレクタ20は、入力ポートとして書き込み用カウンタ21からの入力ポートを選択しており、書き込み用カウンタ21からのアドレスがメモリ2に入力される。そして、メモリ2は、書き込み状態となり、A/D変換器1からの入力信号がメモリ2に入力される。

#### 【0034】

メモリ2に信号が記憶されると、制御部23からは、読み出し用カウンタ22及びスライディング相関器3に読み出し初期化信号が入力されると共に、読み出し/書き込み切り替え信号がセレクタ20に入力される。読み出し用カウンタ22からは、メモリ2からの読み出しアドレスが出力され、セレクタ20を介してメモリ2に入力される。すると、記憶されていた信号がメモリ2から読み出され、スライディング相関器3に入力される。このとき、制御部23からは、符号発生回路8に対し、どのような逆拡散符号を出力すべきかを指示する符号指定信号と、逆拡散符号をどのタイミングで出力すべきかを指示する符号位相初期値信号が入力される。符号発生回路8は、符号指定信号と符号位相初期値信号の指示に従って、符号を発生し、スライディング相関器3に入力する。また、制御部23からの読み出し初期化信号はスライディング相関器3に入力されて、スライディング相関器3を新しい相関値検出処理のためにリセットする。例えば、図2のフリップフロップ12、13を共にリセットする等である。更に、制御部23は、符号発生回路8に入力した符号位相初期値信号の値から逆拡散タイミングを取得して、タイミング符号保持回路にタイミング保持信号として出力する。

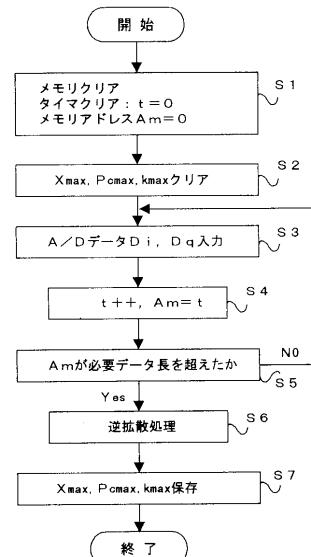

図4～図6は、第1の実施形態における処理の流れを説明するフローチャートである。

#### 【0035】

図4は、全体の処理の流れを示すフローチャートである。

まず、ステップS1で、処理を開始するために、メモリ、タイマ、メモリアドレスそれぞれをクリアする。また、ステップS2で、相関値の積算値の最大値 $X_{max}$ 、積算値が最大値を示す場合の逆拡散符号の位相 $P_{cmax}$ 、候補となる逆拡散符号の内、最大の積算値を示すものを特定する番号 $k_{max}$ をクリアする。ステップS3で、A/D変換器によってデジタル信号に変換された、Iフェーズ信号値 $D_i$ 、Qフェーズ信号値 $D_q$ をメモリに記憶する。ステップS4で、タイマ値のインクリメントに従って、メモリアドレス $A_m$ を設定し、ステップS5で、信号が入力されたアドレスの数が必要なデータ長を超えたか否か判断する。ここで、 $A_m$ は一般に、メモリのアドレスであるが、同図の説明では、入力された信号の先頭から順次番号付けていったものとなっている。また、入力信号は、拡散符号の1チップ毎に1つのアドレスに格納されるものとしている。ステップS5で、必要なデータ長だけ信号が記憶されていないと判断された場合には、ステップS3に戻って、更に信号を読み込む。ステップS5で、必要なデータ長だけメモリに記憶されたと判断された場合には、ステップS6に進む。ステップS6では、逆拡散処理を行い、ステップS7で最大の相関値 $X_{max}$ 、対応する符号の位相 $P_{cmax}$ 、及び符号を特定する番号 $k_{max}$ を保存し、処理を終了する。

#### 【0036】

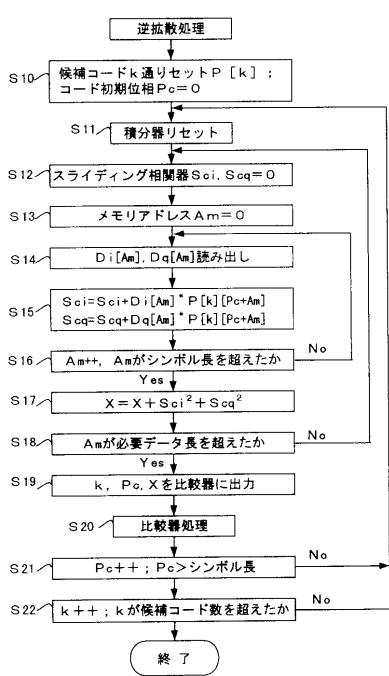

図5は、図4の逆拡散処理を示すフローチャートである。

まず、ステップS10で、逆拡散に使用する候補となる符号 $P[k]$ 及び、符号の初期位相 $P_c = 0$ をセットする。ここで、 $P[k]$ は、 $k$ によって特定される符号を示すものとする。ステップS11で、積分回路をリセットし、ステップS12で、スライディング相関器のIフェーズの相関値 $S_{ci}$ 、及びQフェーズの相関値 $S_{cq}$ を“0”リセットする。また、ステップS13でメモリアドレス $A_m$ も“0”にリセットする。

#### 【0037】

次に、ステップS14でメモリ内のアドレス $A_m$ で示される場所に記憶されているIフェーズの信号値 $D_i[A_m]$ 及びQフェーズの信号値 $D_q[A_m]$ をメモリから読み出す。そして、ステップS15で、逆拡散演算を行う。すなわち、アドレスあるいは、入力データ

10

20

30

40

50

タの先頭から A m チップ番目の信号値 D i [ A m ]、D q [ A m ] と、k で特定される符号 P [ k ] の P c + A m チップ番目の値 P [ k ] [ P c + A m ] とを乗算する。ステップ S 16 で、A m をインクリメントし、A m がシンボル長を超えたか否かを判断する。ステップ S 16 で、シンボル長を越えていない場合には、ステップ S 14 に戻って、次の信号値を読み出し、ステップ S 15 で逆拡散すると共に、逆拡散値を積算する。ステップ S 16 で、A m がシンボル長を超えた場合には、ステップ S 15 で 1 シンボルに渡る逆拡散が終わったことになるので、ステップ S 17 で、I フェーズと Q フェーズの間の位相の回転による影響を抑制するための電力化 ( $S_c i^2 + S_c q^2$ ) を行う。ステップ S 18 で、A m が必要データ長を超えたか否かを判断し、必要データ長を越えていない場合には、ステップ S 12 に戻って、次のシンボルの逆拡散を行う。

10

#### 【0038】

ステップ S 18 で、A m が必要データ長を越えていた場合には、ステップ S 17 で必要データ長に含まれるシンボル分だけ電力化した値が積算されているので、この積算値 X、積算値 X を得たときの符号の位相 P c、及び、符号を特定する番号 k を比較器に出力する(ステップ S 19)。比較器では、ステップ S 20 の比較器処理が行われる。ステップ S 21 で、符号の位相値 P c (今の場合、シンボルの先頭から順次付けられた番号となっている) をインクリメントし、P c がシンボル長を超えたか否かが判断される。P c がシンボル長を越えていない場合には、全ての位相について処理をしていないので、ステップ S 11 に戻って処理を繰り返す。ステップ S 21 で、P c がシンボル長を越えていると判断された場合には、全ての位相について処理をしたことになるので、ステップ S 22 で、符号を特定する番号 k をインクリメントし、k の値が候補となる符号の数を超えたか、すなわち、全ての候補の符号に対し、処理を完了したかが判断される。k が候補の符号の数を越えていない場合には、全ての符号に対し処理を終了していないので、ステップ S 11 にもどって、処理を繰り返す。k が候補の符号の数を越えている場合には、処理を終了する。

20

#### 【0039】

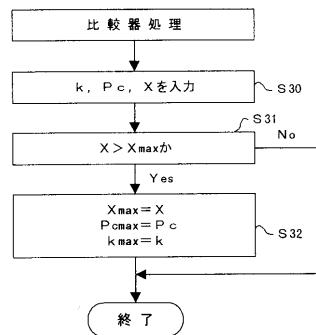

図 6 は、図 5 の比較器処理を説明するフローチャートである。

ステップ S 30 では、図 5 のステップ S 19 で出力された、符号を特定する番号 k、逆拡散符号の位相 P c、及び積算値 X を入力する。ステップ S 31 で、現在設定されている積算値の最大値 X max よりも、現在処理して得た積算値の方が大きいか否かが判断される。現在の値が最大値以下の場合には、処理を終了する。現在の値の方が大きい場合には、ステップ S 32 で、現在の X、P c、k を X max、P c max、k max に設定して、処理を終了する。

30

#### 【0040】

上記した、図 4 ~ 図 6 の処理により、相関値の積算値が最大になる符号及び逆拡散符号を乗算するときの位相を知ることが出来る。

なお、以上の説明では、入力信号のサンプリングレートはチップレートであって、オーバサンプリングを行わない場合を説明したが、実際には、入力信号のレベルに揺らぎがあるので、チップレートよりも大きなレートでオーバサンプリングし、1 チップの中で最もレベルの高い値を使用して処理をするようにする。この場合、逆拡散符号を乗算するときの位相をサンプリングレートの単位で変化させるようにするとともに、逆拡散処理を行う場合の、信号値の読み出しアドレスや、逆拡散符号のチップを指定する方法を変える必要があるが、これは当業者によれば、容易に理解されるであろう。

40

#### 【0041】

図 7 は、共通のコード及び基地局固有のコードをマッチドフィルタによって行う本発明の第 2 の実施形態を示す図である。

なお、同図において、図 1 と同じ構成要素には同じ参照符号を付してある。

#### 【0042】

主に符号発生回路 8、マッチドフィルタ 30、メモリ 2、積分回路 5、比較器 6、タイミング符号保持回路 7 からなる。

動作手順を以下に示す。

50

**【0043】**

1. 止り木チャネルの受信複素信号をA / D変換器1でデジタル信号に変換したものの電圧値をメモリ2に保存する。メモリ2から順次電圧データを読み出し、マッチドフィルタ30により逆拡散する。IフェーズとQフェーズの信号の逆拡散結果を電力化器4で電力値に変換する。そして、雑音の影響を低減するため積分回路5で複数のシンボルにわたって積算し、実質的な平均化を行う。比較器6により最大の、または、大きなものから、または基準値以上のm個のタイミングを逆拡散タイミングとしてタイミング符号保持回路7に保持する。

**【0044】**

2. 次に、各基地局固有の拡散符号で拡散された複素信号を、手順1で検出したm通りのタイミングに対して、順次候補となる符号によりマッチドフィルタ30を用いて相関値を検出する。このとき符号発生回路8は基地局固有の拡散符号の候補k通りを発生する。

10

**【0045】**

3. 比較器6により相関出力が大きなものからn個の拡散符号を検出する。タイミングと符号と相関値を、タイミング符号保持回路7に保持する。

3で得られた最大の相関値が得られるタイミングおよび符号を、逆拡散タイミング及び基地局の符号として逆拡散符号及び逆拡散タイミングの検出を終了する。なお、複数のマッチドフィルタ30を用いて、複数の逆拡散符号に対し平行して処理を行い、処理時間を短縮することもできる。

**【0046】**

20

すなわち、A / D変換された入力信号は、メモリ2に記憶される。次に、不図示の制御部からメモリ2に読み出し信号が入力され、記憶された信号が出力される。符号発生回路8は、タイミング符号保持回路7からの指示に基づいて、マッチドフィルタ30に逆拡散符号を送る。このとき、マッチドフィルタ30は、相関値を取る。このとき、マッチドフィルタ30は、装置内のクロックに従って、逆拡散符号を受信信号に乗算するタイミングをずらしながら相関値を出力するので、最大の相関値が得られたタイミングから逆拡散符号を受信信号に乗算すべきタイミングを知ることができる。符号発生回路8は、第1の実施形態とは異なり、符号の位相を調整して出力する必要はない。

**【0047】**

30

マッチドフィルタ30で得られた相関値は、電力化器4によって電力に変換され、積分回路5で積算された後、比較器6で、積算値が所定の値よりも大きい値を示しているか否かを判断し、符号及び逆拡散タイミングが正しいと判断される符号及び逆拡散タイミングをタイミング符号保持回路7に送る。タイミング符号保持回路7は、順次符号発生回路8に対し、異なる逆拡散符号出力するように指示し、候補となる逆拡散符号で順次逆拡散をマッチドフィルタ30に行わせる。そして、最大の相関値を示す符号とタイミング、あるいは、所定の基準値以上の相関値を示す複数の符号及びタイミングをタイミング符号保持回路7内に保持する。

**【0048】**

40

本実施形態においては、マッチドフィルタを用いているので、相関器のハードウェア構成としては大きくなってしまうが、符号発生回路8から符号を出力する時の位相を制御する必要はなく、最大相関値を示す逆拡散タイミングも同時に得られる。

**【0049】**

例えば、スライディング相関器を使用する場合、タイミング検出に必要な時間と、符号判定に必要な時間が大きく異なる時、必要とされるメモリの容量がタイミング検出に使用するものと、符号判定に使用するものとで大きく異なる場合がある。ところが、マッチドフィルタを使用する場合には、タイミング判定は電力によっておこない、マッチドフィルタにより瞬時の電力を検出し、さらに共通の符号の出現周期で電力を積分することで、メモリの容量を削減することができる。

**【0050】**

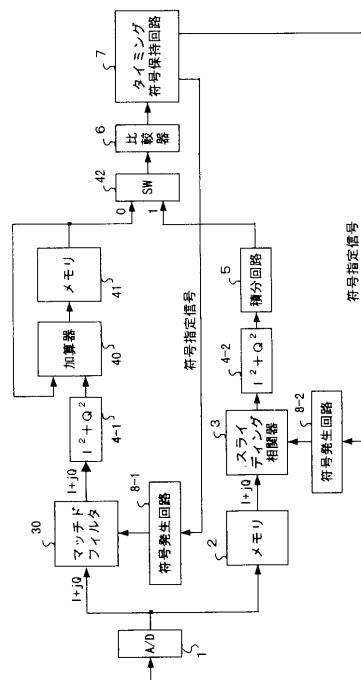

図8は、逆拡散タイミングの検出は共通のコードをマッチドフィルタによって行い、基地

50

局固有のコードを本方式を用いて行う場合の本発明の第3の実施形態を示す図である。

**【0051】**

なお、同図において、前述の構成要素と同じ構成要素には同じ参照符号を付してある。主に符号発生回路8-1、8-2、マッチドフィルタ30、スライディング相関器30、メモリ2、メモリ41、比較器6、スイッチ42、タイミング符号保持回路7からなる。

**【0052】**

動作手順を以下に示す。

1. 先ず、止り木チャネルの検出において、スイッチ42で入力0を選択する。受信複素信号をマッチドフィルタにより共通の拡散符号を検出する。IフェーズとQフェーズの信号を電力化器4-1によって電力化する。雑音の影響を低減するためメモリ41と加算器40を用いて積分器とし、同一タイミングの信号の平均化を行う。メモリ41には電力として保存する。積算による平均化終了後、メモリ41から順次電力データを読み出し、比較器42により最大の、または、大きなものから、または基準値以上のm個のタイミングを逆拡散タイミングとしてタイミング符号保持回路7に保持する。

**【0053】**

2. 各基地局固有の符号の検出において、スイッチ42で入力1を選択する。受信複素信号の電圧値をメモリ2に保存する。メモリ2保存後、手順1で検出したm通りのタイミングに対して、順次候補となる符号によりスライディング相関器3を用いて相関値を検出する。

**【0054】**

3. 比較器3により相関出力が大きなものからn個の拡散符号を検出する。タイミングと符号と相関値を、タイミング符号保持回路7に保持する。

3で得られた最大の相関値が得られるタイミング及び符号を、逆拡散タイミング及び基地局の符号として逆拡散符号および逆拡散タイミングの検出を終了する。

**【0055】**

止り木チャネルの検出においては、止り木チャネルの符号が表れている信号が所定の間隔で繰り返し送られており、受信信号のS/N比を向上するために、これらを複数周期にわたって繰り返し逆拡散する場合は、第1の実施形態のように一旦メモリ2に記憶してから逆拡散すると、メモリ2に記憶すべき信号の量が大きくなり、メモリ2も大型化してしまう。そこで、止り木チャネルの検出に関してのみ、マッチドフィルタ30を使用して、リアルタイムで相関値とタイミングを検出し、タイミング符号保持回路7に記憶するようにする。そして、基地局に固有の符号を検出する場合には、メモリ2に一旦記憶し、フェージングの影響を除去して、相関値とタイミングを取得することにより、ハードウェアの規模を最小限に抑え、効率的な同期タイミングの取得、及び符号の判定を行うことができる。各基地局に固有の符号は、通常連続して送信されてくるので、スライディング相関器3等による処理を連続して行っていれば、S/N比の良い検出を行うことができる。

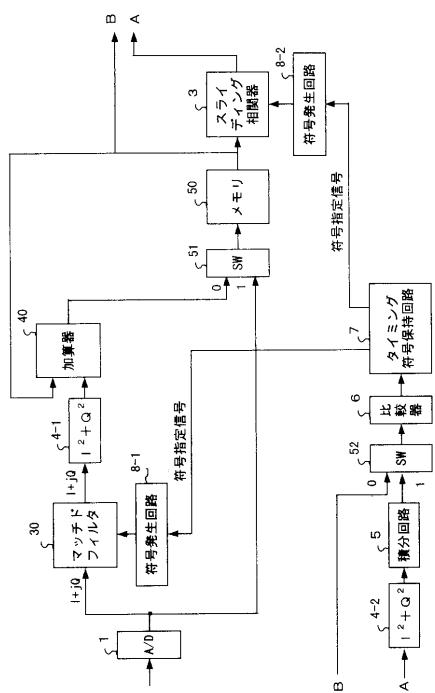

**【0056】**

図9は、第3の実施形態において、メモリ2とメモリ41を共有する場合の本発明の第4の実施形態を示す図である。

本実施形態では、上記第3の実施形態の場合のようにメモリ2とメモリ41が同じ時間に動作する必要がないシステムの場合、メモリ2とメモリ41とを共有することにより回路規模を縮小できる。

**【0057】**

なお、同図において、図8と同じ構成要素には同じ参照符号を付してある。

主に符号発生回路8-1、8-2、マッチドフィルタ30、スライディング相関器3、メモリ50、比較器6、スイッチ51、スイッチ52、タイミング符号保持回路7からなる。

**【0058】**

動作手順を以下に示す。基本的には第3の実施形態と同等である。

10

20

30

40

50

1. 先ず、止り木チャネルの受信において、スイッチ 5 1 で入力 0 を選択する。スイッチ 5 2 で入力 0 を選択する。受信複素信号をマッチドフィルタ 3 0 により共通の拡散符号を検出する。電力化器 4 - 1 で信号を電力化する。そして、雑音の影響を低減するためメモリ 5 0 と加算器 4 0 を用いて積分器とし、同一タイミングの信号の平均化を行う。メモリ 5 0 には電力として保存する。平均化終了後、メモリ 5 0 から順次電力データを読み出し、比較器 6 により最大の、または、大きなものから、または基準値以上の m 個のタイミングを逆拡散タイミングとしてタイミング符号保持回路に保持する。

#### 【 0 0 5 9 】

2. 次に、各基地局に固有の符号を検出する際に、スイッチ 5 1 で入力 1 を選択する。スイッチ 5 2 で入力 1 を選択する。受信複素信号の電圧値をメモリ 5 0 に保存する。メモリ 5 0 に保存の後、手順 1 で検出した m 通りのタイミングに対して、順次候補となる符号によりスライディング相関器 3 を用いて相関値を検出する。10

#### 【 0 0 6 0 】

3. 比較器 6 により相関出力が大きなものから n 個の拡散符号を検出する。タイミングと符号と相関値を、タイミング符号保持回路 7 に保持する。

3 で得られた最大の相関値が得られるタイミング及び符号を、逆拡散タイミング及び基地局の符号として逆拡散符号及び逆拡散タイミングの検出を終了する。

#### 【 0 0 6 1 】

本実施形態によれば、マッチドフィルタ 3 0 を使った止り木チャネルの検出と、各基地局に固有の符号の検出は同時に行われないという見識に基づいて、メモリ 5 0 を共用している。従って、メモリの数を減らすことが出来、ハードウェアの小型化に寄与する。また、メモリ 5 0 が使われない時間を少なくすることにより、ハードウェア資源の有効利用にもつながる。20

#### 【 0 0 6 2 】

本実施形態においては、止り木チャネルの受信の際には、A / D 変換器 1 によってデジタル信号になった入力信号をマッチドフィルタ 3 0 で逆拡散する。止り木チャネルを検出するための逆拡散符号は、タイミング符号保持回路 7 からの指示を受けた符号発生回路 8 - 1 が発生する。得られた相関値は、電力化器 4 - 1 で電力化され、加算器 4 0 に入力される。加算器 4 0 では、1 つ前のシンボルの相関値と加算され、スイッチ 5 1 を経て、メモリ 5 0 に記憶される。メモリ 5 0 に記憶された加算値は、フィードバック経路を経て、加算器 4 0 に入力され、1 つ後のシンボルの相関値と加算される。このようにして、複数のシンボルについて相関値が積算されると、スイッチ 5 2 の入力 0 に印加され、比較器 6 に入力され、タイミング符号保持回路 7 に逆拡散を行うべきタイミングが通知される。30

#### 【 0 0 6 3 】

各基地局に固有の符号を判定する場合には、デジタル化された入力信号は、スイッチ 5 1 の入力 1 を介してメモリ 5 0 に記憶される。メモリ 5 0 に記憶された信号は、順次、第 1 の実施形態で説明したような手順により、スライディング相関器 3 に入力され、タイミング符号保持回路 7 から指示を受けた符号発生回路 8 - 2 から所定の位相で出力される逆拡散符号によって、逆拡散される。逆拡散された結果の相関値は、電力化器 4 - 2 に入力されて、電力化される。そして、積分回路 5 で S / N 比を良くするために積分され、スイッチ 5 2 を介して、比較器 6 に入力される。比較器 6 の比較結果から、基地局が使用している符号及び逆拡散タイミングがタイミング符号保持回路 7 に入力される。40

#### 【 0 0 6 4 】

なお、上記各実施形態において、複数の電圧 - 電力変換器（電力化器 :  $I^2 + Q^2$ ）や符号発生器が記述されている場合は、セレクタ、スイッチ等で共通化することもできる。また、実施形態は全てデジタル回路での構成としているが、アナログ回路での実現も可能である。そのため、A / D 変換器の位置または個数は必要に応じて必要な場所に必要なだけ設ければ良い。

#### 【 0 0 6 5 】

また、フェージングの影響を受けた信号がメモリに保持されることも考えられる。この様50

な場合、後段で相関値を順次検出した結果、全てが所定閾値に達しない場合に保持されたデータが異常と判断し、再度入力するデータを入力保持し、相関値を再度検出することにより、正しい符号検出を行うことが出来る。

**【0066】**

**【発明の効果】**

複数の符号により逆拡散を繰り返しても、正しく相関値の比較ができる、逆拡散のタイミングおよび符号検出の精度が向上する。

**【図面の簡単な説明】**

【図1】共通のコードおよび基地局固有のコードをスライディング相関器によって行う、本発明の第1の実施形態を示す図である。 10

【図2】スライディング相関器の構成例を示す図である。

【図3】第1の実施形態のメモリアクセス動作を行う構成を説明する図である。

【図4】第1の実施形態における処理の流れを説明するフローチャート（その1）である。 10

【図5】第1の実施形態における処理の流れを説明するフローチャート（その2）である。

【図6】第1の実施形態における処理の流れを説明するフローチャート（その3）である。

【図7】共通のコード及び基地局固有のコードをマッチドフィルタによって行う本発明の第2の実施形態を示す図である。 20

【図8】逆拡散タイミングの検出は共通のコードをマッチドフィルタによって行い、基地局固有のコードを本方式を用いて行う場合の本発明の第3の実施形態を示す図である。

【図9】第3の実施形態において、メモリ2とメモリ41を共有する場合の本発明の第4の実施形態を示す図である。

【図10】従来の拡散符号及びタイミング検出装置の構成を示す図である。

**【符号の説明】**

1 A / D 変換器

2、41、50 メモリ

3 スライディング相関器

4、4-1、4-2 電力化器

5 積分回路

6 比較器

7 タイミング符号保持回路

8、8-1、8-2 符号発生回路

10 乗算器

11、40 加算器

12、13 フリップフロップ

20 セレクタ

21 書き込み用カウンタ

22 読み出し用カウンタ

23 制御部

30 マッチドフィルタ

42、51、52 スイッチ

10

20

30

40

【図1】

共通のコードおよび基地局固有のコードをスライディング相関器によって行う、本発明の第1の実施形態を示す図

【図2】

スライディング相関器の構成例を示す図

【図3】

第1の実施形態のメモリアクセス動作を行う構成を説明する図

【図4】

第1の実施形態における処理の流れを説明するフローチャート(その1)

【図5】

第1の実施形態における処理の流れを説明する

フローチャート(その2)

第1の実施形態における処理の流れを

説明するフローチャート(その3)

【図7】

共通のコード及び基地局固有のコードを

マッチドフィルタによって行う

本発明の第2の実施形態を示す図

【図8】

逆拡散タイミングの検出は共通のコードを

マッチドフィルタによって行い、

基地局固有のコードを本方式を用いて行う場合の

本発明の第3の実施形態を示す図

【図9】

第3の実施形態において、メモリ2とメモリ4.1を

共有する場合の本発明の第4の実施形態を示す図

【図10】

従来の拡散符号及びタイミング検出装置の

構成を示す図

---

フロントページの続き

(72)発明者 井上 武志

神奈川県横浜市港北区新横浜2丁目3番9号 富士通ディジタル・テクノロジ株式会社内

審査官 岡 裕之

(56)参考文献 特開平10-126378 (JP, A)

国際公開第95/007577 (WO, A1)

特開昭63-073731 (JP, A)

特開平09-064846 (JP, A)

特開平10-032523 (JP, A)

特開平11-098112 (JP, A)

特開平10-200447 (JP, A)

特開平09-046174 (JP, A)

特開平06-077931 (JP, A)

特開平05-260437 (JP, A)

樋口 健一 (外2名), ロングコードを用いたDS-CDMA基地局間非同期セルラ方式における2段階セルサーチ法, 電気情報通信学会技術研究報告, 1996年 8月 9日, 信学技報 Vol. 96 No. 213, P51-56, RCS96-73

(58)調査した分野(Int.Cl., DB名)

H04B 1/707

H04L 7/00