(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-501692

(P2006-501692A)

(43) 公表日 平成18年1月12日(2006.1.12)

|                       |            |             |

|-----------------------|------------|-------------|

| (51) Int.C1.          | F 1        | テーマコード (参考) |

| HO1L 21/822 (2006.01) | HO1L 27/04 | A 5FO38     |

| HO1L 27/04 (2006.01)  | HO1L 27/04 | H           |

審査請求 未請求 予備審査請求 未請求 (全 13 頁)

|                                        |                                                                                                                                                                                                                                      |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 特願2005-501980 (P2005-501980) | (71) 出願人 501411651<br>エイチアールエル ラボラトリーズ, エル<br>エルシー<br>H R L LABORATORIES, L<br>LC<br>アメリカ合衆国, 90265-4799<br>カリフォルニア州, マリブ, マリブ キャ<br>ニオン ロード 3011<br>3011 Malibu Canyon<br>Road, Malibu, CA 90<br>265-4799, United States of America |

| (86) (22) 出願日 平成15年9月23日 (2003.9.23)   |                                                                                                                                                                                                                                      |

| (85) 翻訳文提出日 平成17年3月25日 (2005.3.25)     |                                                                                                                                                                                                                                      |

| (86) 國際出願番号 PCT/US2003/030212          |                                                                                                                                                                                                                                      |

| (87) 國際公開番号 WO2004/030097              |                                                                                                                                                                                                                                      |

| (87) 國際公開日 平成16年4月8日 (2004.4.8)        |                                                                                                                                                                                                                                      |

| (31) 優先権主張番号 60/414,216                |                                                                                                                                                                                                                                      |

| (32) 優先日 平成14年9月27日 (2002.9.27)        |                                                                                                                                                                                                                                      |

| (33) 優先権主張国 米国(US)                     |                                                                                                                                                                                                                                      |

| (31) 優先権主張番号 10/635,790                |                                                                                                                                                                                                                                      |

| (32) 優先日 平成15年8月5日 (2003.8.5)          |                                                                                                                                                                                                                                      |

| (33) 優先権主張国 米国(US)                     |                                                                                                                                                                                                                                      |

最終頁に続く

(54) 【発明の名称】リバースエンジニアリングを防ぐための導電性チャネル擬似ブロック方法及びその回路

## (57) 【要約】

リバースエンジニアリングに対して集積回路を偽造するための技術及び構造。集積回路構造は、制御された輪郭を有する材料の複数の層により構成されている。シリサイド金属の層は基盤の活性領域の上に設けられ、活性領域に隣接するチャネル接続の上に隙間を有する。そのチャネルは、導電性であるか絶縁性であるかがリバースエンジニアリングの下で識別可能であるようにみえる、チャネルブロック構造を有する。

**【特許請求の範囲】****【請求項 1】**

少なくとも 2 つの活性領域；

前記の少なくとも 2 つの活性領域の間の電気的接続を与える電気導電性のドープされたチャネル；

前記電気的導電性チャネルの第 1 部分の上に設けられた第 1 導電性層； 及び

前記電気的導電性チャネルの第 2 部分の上に設けられた第 2 導電性層であって、前記第 1 導電性層と前記第 2 導電性層とは互いに距離を置いている、第 2 導電性層；

から構成されることを特徴とする半導体接続。

**【請求項 2】**

請求項 1 に記載の半導体接続であって、前記第 1 導電性層と前記第 2 導電性層はシリサイド層である、ことを特徴とする半導体接続。

**【請求項 3】**

請求項 1 に記載の半導体接続であって、前記電気的導電性のドープされたチャネルは：

前記の少なくとも 2 つの活性領域の第 1 の一に隣接する第 1 のドープされたチャネル領域；

前記の少なくとも 2 つの活性領域の第 2 の一に隣接する第 2 のドープされたチャネル領域； 及び

前記の第 1 のドープされたチャネル領域と前記の第 2 のドープされたチャネル領域との間ににおいて処理されたチャネルロック構造；

から構成される、ことを特徴とする半導体接続。

**【請求項 4】**

請求項 3 に記載の半導体接続であって、前記の第 1 のドープされたチャネル領域、前記の第 2 のドープされたチャネル領域及び前記チャネルロック構造は、前記チャネルロック構造が擬似チャネルロック構造であるように、同じタイプの導電性を有する、ことを特徴とする半導体接続。

**【請求項 5】**

請求項 3 に記載の半導体接続であって、前記の少なくとも 2 つの活性領域は第 1 のドープされた接続を有し、前記チャネルロック構造は第 2 の第 1 のドープされた接続を有し、前記の第 2 のドープされた接続は前記の第 1 のドープされた接続より濃度が小さい、ことを特徴とする半導体接続。

**【請求項 6】**

形成された複数の導電性チャネルを有する集積回路であって：

関連するチャネルをロックされたチャネルが導電性でないようにする、関連するチャネルロックを各々有する前記の複数の導電性チャネルの選択された導電性チャネルの一と；

関連するチャネルをロックされた擬似チャネルが導電性でないようにしない、関連する擬似チャネルロックを各々有する前記の複数のチャネルの他の導電性チャネルと；

を有する集積回路であり、

チャネルをロックされたチャネルは、リバースエンジニアリング技術を適用する間に集積回路が平面図的に視認されるとき、アーチファクトエッジの存在により前記のチャネルをロックされた擬似チャネルを偽造する；

ことを特徴とする集積回路。

**【請求項 7】**

困難であるリバースエンジニアリングを行う方法であって：

少なくとも 2 つの活性領域の間に電気導電性のドープされたチャネルを形成する段階；

前記の電気導電性のドープされたチャネルの第 1 部分に対して第 1 導電性層の上に第 1 導電性層を設ける段階；

前記の電気導電性のドープされたチャネルの第 2 部分に対して第 2 導電性層の上に第 1 導電性層を設ける段階であって、前記第 1 導電性層及び前記第 2 導電性層は互いに距離を

10

20

30

40

50

置いている、段階；

を有することを特徴とする方法。

**【請求項 8】**

請求項 7 に記載の方法であって、前記の電気導電性のドープされたチャネルを形成する段階は、前記の電気導電性のドープされたチャネルにおいてチャネルブロック構造の画像を生成する手順と含み、それにより、前記の電気導電性のドープされたチャネルは、リバースエンジニアにはチャネルブロックされたか又はチャネルブロックされた可能性があるよう に見えるが、前記の電気導電性のドープされたチャネルチャネルブロックされていない、ことを特徴とする方法。

**【請求項 9】**

請求項 8 に記載の方法であって、前記チャネルブロック構造は、前記の少なくとも 2 つの活性領域を生成するために用いられるドーパント濃度より低いドーパント濃度を用いて生成されている、ことを特徴とする方法。

**【請求項 10】**

請求項 7 に記載の方法であって、前記第 1 導電性層と前記第 2 導電性層はシリサイド層である、ことを特徴とする方法。

**【請求項 11】**

集積回路デザインを保護する方法であって：

非導電性のチャネルをブロックされたチャネルに関連する導電性層のエッジを規定する段階；及び

前記の非導電性のチャネルをブロックされたチャネルのために前記導電性層の前記エッジと同じ相対位置にチャネルをブロックされた擬似チャネルに関連する導電性層のエッジを位置付ける段階；

から構成されることを特徴とする方法。

**【請求項 12】**

請求項 11 に記載の方法であって、前記導電性層はシリサイドである、ことを特徴とする方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、一般に、集積回路 (IC) 及び半導体デバイスに関し、更には、半導体デバイスがどのように機能するかを、リバースエンジニアが見分けることを困難にする偽装技術を集積回路及び半導体デバイスが用いる製造方法に関する。

**【背景技術】**

**【0002】**

本発明は、本発明と同様の発明者による次の米国特許に関連する。

(1) 米国特許第 5,866,933 号明細書、米国特許第 5,783,375 号明細書及び米国特許第 6,294,816 号明細書は、CMOS 回路におけるトランジスタが p+ 及び n+ ソース / ドレインマスクを変更することによりトランジスタ間の注入された（それ故、隠されて埋め込まれた）線によりどのように接続されるかを記載している。それらの注入された相互接続は、リバースエンジニアには実質的に同一に見える 3 - input AND 回路又は OR 回路を製造するために用いられる。又、埋め込まれた相互接続は、トランジスタ間であって、それ故、それらの機能間の接続性を理解しようするために非常に深いところまでリバースエンジニアが IC を調査することを強いる。

(2) 米国特許第 5,783,846 号明細書、米国特許第 5,930,663 号明細書及び米国特許第 6,064,110 号明細書は、用いられている CMOS 技術の略最小フィーチャサイズの長さを用いて、トランジスタ間の注入された接続線が挿入された隙間に有するように、ソース / ドレイン注入マスクにおける更なる変更について記載している。この隙間が一種類の注入により“満たされる”場合であって、それが他の種類の注入により“満たされる”場合、その線は導通しない。意図的な隙間は“チャネルブロック”と呼

10

20

30

40

50

ばれている。リバースエンジニアは、用いられるC M O Sプロセスの最小フィーチャサイズにおける注入の種類を解くことに基づいて接続性を決定することを強いられる。

(3) 米国特許第6,117,762号明細書においてな、リバースエンジニアから半導体集積回路を保護するための方法及び装置について記載している。半導体のアクティブな領域が基板において形成され、選択的基板領域に形成されたシリサイド領域により他の領域と少なくとも1つのアクティブ領域を相互接続するための選択的基板領域及び半導体アクティブ領域の少なくとも1つのアクティブ領域の両方に対して、シリサイド層が形成される。

#### 【0003】

複雑な集積回路及び半導体デバイスの構築は、そのようなデバイスの設計において必要とされる高度な技術能力による膨大な時間を費やしてなされるため、非常に費用がかかることとなる。更に、集積回路は、ファームウェアの形式のソフトウェアが符合化される読み出し専用メモリ及び/又はEEPROMを含むことができる。更に、集積回路は、しばしば、情報の暗号化を含むアプリケーションにおいて用いられ、それ故、そのような機密情報を保つために、そのようなデバイスをリバースエンジニアリングされないようにすることが望ましい。従って、集積回路および他の半導体デバイスをリバースエンジニアリングされることから守るための種々の理由が存在している。

#### 【0004】

リバースエンジニアを寄せ付けないように、リバースエンジニアにとって集積回路が非常に難しいものとするために、当該技術分野において種々の技術が知られている。そのような技術の1つは、トランジスタ間の接続を決定することを困難にし、リバースエンジニアに各々のトランジスタ（特に、C M O Sデバイスに対する各々のC M O Sトランジスタ対）を注意深く分析することを課し、集積回路をリバースエンジニアリングするために自動回路及びパターン認識技術を用いる試みを阻止するものである。集積回路は、10万個又は10億個ものトランジスタを有するため、リバースエンジニアにデバイスにおける各々のトランジスタを注意深く分析することを課すことにより、デバイスを成功裏にリバースエンジニアリングしようとするリバースエンジニアの努力を効果的に台無しにすることができます。

#### 【0005】

シリサイドのような導電性層は、反お伝いデバイスの製造の中で、しばしば用いられる。今日のC M O Sデバイスにおいては、特に、0.5μmより小さいサイズのフィーチャにおいて、ゲート、ソース及びドレイン接触の導電性を改善するために、シリサイド層が用いられている。一般的なデザインルールに従って、いずれのソース/ドレイン注入を用いる注入領域がシリサイド化される。

#### 【0006】

1つの一般的なリバースエンジニアリング技術は、化学的機械的研磨方法（C M P）により完成I Cのデレイヤリングを含む。C M Pプロセスは、ある条件下で、シリサイドが形成されたところと形成されなかったところとの間の領域、即ち、シリサイドブロックマスク段階により規定される領域をあらわにする。このような領域は、ある種の化学的エッチングの下で、純粋のシリコン領域に対してシリサイド化された領域のエッチング速度が異なることによりトポグラフィにおける差が観測されるため、あらわにされることが可能である。リバースエンジニアは、シリサイド化領域対非シリサイド化領域に注目することにより、デバイスの機能に関して妥当な仮定を設けることが可能である。このような情報は、次いで、他の類似するデバイスの自動分類のためのデータベースに記憶されることができる。

#### 【0007】

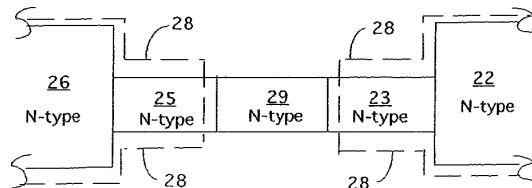

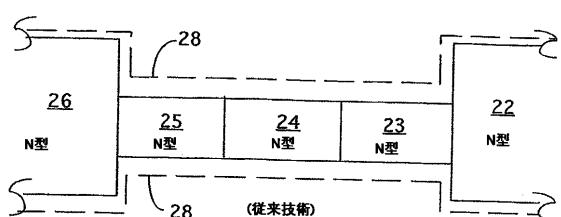

リバースエンジニアリングに対して保護する幾つかの方法は、C M Pのような、幾つかのリバースエンジニアリング技術の下で、発見可能である。図1A及び1Bは、米国特許第5,783,846号明細書、米国特許第5,930,663号明細書及び米国特許第6,064,110号明細書に従って作製されたトランジスタをC M Pにより処理した後

10

20

30

40

50

のアーチファクトを示している。米国特許第5,783,846号明細書、米国特許第5,930,663号明細書及び米国特許第6,064,110号明細書は、図1Aに示すように、基板における電気導電性のドープしたインプラント23乃至25と同様の導電性のドープした回路要素26、22（即ち、ソース／ドレイン領域）の接続を隠すことを開示している。基板における電気導電性のドープしたインプラント23乃至25は、ソース／ドレイン領域と同じ処理段階の間に備えられることが可能であり、それ故、同じドーピングレベルを有し、同様にシリサイド化される。更に、図1Bに示すように、リバースエンジニアを更に混乱させるために、電気導電性のドープしたインプラントは異なるタイプの導電性に選択的にドープされ、チャネルブロック構造27を形成する。そのチャネルブロック構造は一のドープした回路要素から他への電気接続を回避する。シリサイドによる1つのドープした回路要素26から他2への電気接続を回避するために、シリサイドプロックマスクを変更する。ソース／ドレインインプラントを用いて、シリサイド層がいずれのインプラント領域に亘って存在することを可能にする代わりに、シリサイドプロックマスクは、チャネルブロック構造27に対してシリサイド層が形成されないように変更される。

10

20

30

#### 【0008】

図1A及び1Bにおいては、シリサイドのアーチファクトエッジを破線で示している。図1Aにおいては、シリサイドは、ドープした領域22乃至26の全てが同じタイプの導電性ドーパントでドープされているため、ドープされた領域22乃至26のすべてを覆うことが可能である。図1Bにおいては、シリサイドがドープされる領域27を覆わないようするように、シリサイドプロックマスクが用いられる。リバースエンジニアは、ベアシリコン表面における適切なステイン／エッチングの後、この領域を視認し、シリサイドのアーチファクトエッジ28を検出することができる。そのシリサイドのアーチファクトエッジはシリサイド化領域と非シリサイド化領域との界面に形成されている。図1Bに示す構造に対して、リバースエンジニアは、図に示すように、アーチファクトエッジ28が、示されている2つのシリサイド化された部分の間の割り込み30を有するとき、そのような割り込み30は、下にある導電性インプラントが非導電性チャネルブロック構造27を含むことを意味すると、恐らく結論付ける。この情報は、それ故、データベースに入力され、自動パターン認識技術が、非導電性チャネルブロック構造27を示すように、その割り込み30を有するパターンを認識するために用いられることが可能である。それ故、この回路偽装技術の効果は低減される。

30

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

従って、リバースエンジニアを混乱させるようにアーチファクトエッジを用いる半導体デバイス及び半導体デバイスの製造方法を提供するための要請が存在している。形成された実際のデバイスを示すアーチファクトエッジがリバースエンジニアを更に混乱させ、デバイスの実際の構成であって、それ故、デバイスの機能に関して誤った結論をもたらす。

40

#### 【課題を解決するための手段】

#### 【0010】

本発明の目的は、リバースエンジニアを非常に困難にし、リバースエンジニアが典型的な結論の有効性を疑う理由を与えられるように、同様の下にある処理及び回路フィーチャを示さないアーチファクトを与えることによりリバースエンジニアリング処理中、明らかにされるアーチファクトのリバースエンジニアによる調査を混乱させることである。これは、本発明を採用したチップをリバースエンジニアリングすることを、全く不可能でないにしても、非常に実際的でないようになる可能性があり、本発明を採用したチップをリバースエンジニアリングすることにより非常に時間を要するようにすることに関して、リバースエンジニアの努力を専一層困難にする、と考えられる。リバースエンジニアによるアーチファクトの調査を混乱させることにより、リバースエンジニアは、リバースエンジニアリングの作業を極めて時間を要するようになる全ての注入チャネルを調査するよう強

50

いられる。

【0011】

本発明の重要な特徴は、リバースエンジニアリングをさせないようにされるべき回路構成の機能に対する付加又は変更に依存せず、いずれの付加的な処理段階又は装置を必要としないことである。それに代えて、リバースエンジニアリングに対する非常に効果的な抑制力は、基本回路構成に対して処理時間及び複雑性を追加することがない合理化された方法で達成される。

【0012】

ここで名前を連ねている本発明者は、このような技術の一般領域であって、集積回路デバイスをリバースエンジニアリングすることを非常に困難にするために集積回路デバイスの偽装に関連して、以前に特許出願し、特許登録されている。本発明は、リバースエンジニアを更に混乱させるために上記の参照特許文献における技術と適合するようにして用いられることができる。

【0013】

本発明は、対象のチップに関して、1000個の事例の1つのみにおいて用いられる可能性があるが、リバースエンジニアは、リバースエンジニアが理解している各々のトランジスタ又は接続に対して、本発明により変更された可能性が非常に低いことを、十分知っている各々のトランジスタ又は接続を非常に注意深く見る必要がある。リバースエンジニアは、見つけることが不可能なものを見つけなければならないことに直面することになる。本発明は又、何度も用いられることが可能であり、即ち、全てのCMOSの対において、それ故、リバースエンジニアは各々のチャネルを調査することを強いられ、これにより、リバースエンジニアリングを非常に現実的でないものにされる。

【0014】

要約すると、一般に、本発明は、デバイスの真の構造を表さず、誤りに導くアーチファクトをリバースエンジニアリングすることをもたらす、導電性層ブロックマスクを変更した半導体デバイス及び半導体デバイスを製造する方法から構成される。

【0015】

他の特徴において、本発明は、集積回路構造を偽装するために提供される。その集積回路構造は、輪郭が制御された材料の複数の層により構成される。シリサイド層は、制御された輪郭を有する前記の複数の層の間に配置される。半導体と信じているリバースエンジニアを混乱させるために用いられるシリサイド層は1つの構造を有し、実際には、シリサイド層は他の構造を有する。

【発明を実施するための最良の形態】

【0016】

以下、本発明について、本発明の好適な実施形態を示す添付図を参照して、詳細に説明する。本発明は、多くの種々の形態に具現化することが可能であり、ここで記載する実施形態に限定されるとみなされるべきではない。

【0017】

当該技術分野においては、周知の多くの半導体デバイス製造方法がある。以下の説明は、半導体デバイスの製造方法に関する詳細は含んでいない。むしろ、リバースエンジニアを更に混乱させるために、半導体の製造中に用いられる導電性層ブロックマスクを変更することに重点をおいている。

【0018】

本発明は、リバースエンジニアリングデバイスが他のリバースエンジニアリング検出防止技術を用いて製造されたときを、リバースエンジニアが理解することが可能であるシリサイド層のアーチファクトエッジを利用する。

【0019】

上記のようなリバースエンジニアリング検出防止技術においては、チャネルブロック構造はリバースエンジニアを混乱させるために用いられる。図1Bに示すように、チャネルブロック構造27は、チャネル領域23、25と異なるタイプのドーパントを有し、すぐ

10

20

30

40

50

上のシリサイドにおいて割り込み 30 を有する。C M P のようなリバースエンジニアリング処理を用いた後、シリサイド層のアーチファクトエッジ 28 は、図 1 A 及び 1 B を比較することから理解されるように、チャネルブロック構造 27 は 2 つのチャネル領域 23 と 25 との間の電気接続を遮るために用いられたことをリバースエンジニアに明らかにすることが可能である。チャネル領域とチャネルブロック構造とにおいて用いられるタイプのドーパントは、殆どのリバースエンジニアリング処理に対して、容易に利用可能ではない。それ故、リバースエンジニアは、導電性チャネルがチャネルブロックを有するかどうかを判定するために、シリサイド層のアーチファクトエッジ 28 のような、他の方法に依存することを強いられる。

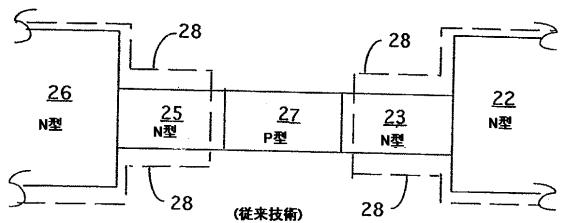

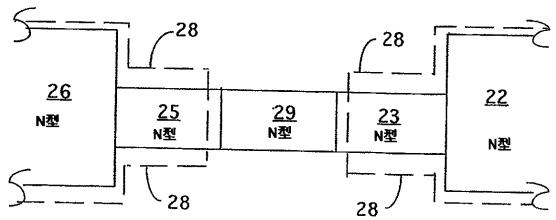

## 【0020】

10

図 2 は、本発明に従って製造されたデバイスのシリサイド層のアーチファクトエッジ 28 を示している。シリサイドブロックマスクは、シリサイド層が擬似チャネルブロック構造 29 を完全に覆わないようにするために好適に変更される。擬似チャネルブロック構造 29 は、チャネル領域 23、25 と同じタイプの導電性を有する。それ故、チャネル領域 23、25 に接続している、覆っているシリサイド層の有無は、チャネルによる導電性に対する影響を有しない。しかしながら、シリサイド層が擬似チャネルブロック構造 29 を完全に覆わないようにするためにシリサイドブロックマスクを変更することにより、割り込み 30 を伴うアーチファクトエッジ 28 は、チャネルが電気的に接続され、即ち、図 2 のアーチファクトエッジ 28 が図 1 B のアーチファクトエッジと同等であることを示しているように、リバースエンジニアにはみえる。それ故、リバースエンジニアは、アーチファクトエッジ 28 が視認できるとき、下のチャネルの接続に関して不正確な仮定に結論付ける、即ち、彼らは、チャネルブロックがあるべき位置にあること（彼らが本発明を知らない場合）若しくは、（1）チャネルブロック 27 が存在するかどうかを検査すること、又は（2）チャネルブロック 27 の存在に関して仮定を設けること（彼らが本発明を知っている場合）を仮定する。

20

## 【0021】

30

回路を更に偽装するために、チャネルブロック構造 29 において用いられるドーパントのタイプは、低濃度にドープされたドレイン（L D D）又は低密度にドープされた（L D D）ソースが形成されると同時に、形成されることが可能である。それ故、ステイン及びエッチング処理を用いる場合でさえ、リバースエンジニアは、ソースインプラント 22 及びドレインインプラント 26 の非常に高いドーズ量に対して、2 つのタイプのインプラント間の、即ち、N 型対 P 型のインプラントについての差を識別する膨大な困難な時間を必要とする。更に、L D D 処理による擬似チャネルブロック構造 29 を形成することにより、チャネルブロック構造 29 は、破壊の考慮のために、寸法をより小さくすることができる。

## 【0022】

40

好適な本発明の製造方法においては、半導体チップの製造のデザインルールは、注入されない領域がシリサイド化されないようにするように変更される。更に、デザインルールは又、リバースエンジニアによる検出を更に回避するために、チャネルブロック構造 29 が小さく且つ低濃度にドープされるように変更されることが可能である。

## 【0023】

50

デザインルールの変更においては、図 2 に示すような、実際の導電性チャネルのアーチファクトエッジが、図 1 B に示すような、非導電性チャネルのアーチファクトエッジの配置に適合することを確実にすることが重要である。例示目的のために、図 1 B におけるアーチファクトエッジ 28 は図 2 のアーチファクトエッジ 28 に適合する。当業者が理解できるであろうように、アーチファクト 28 は、図 1 B 又は 2 において具体的に支援しているように位置付けられる必要はない。それに代えて、アーチファクトエッジは、チャネルに沿ってどこにでも存在することが可能である。しかしながら、（1）シリサイド層は電気的接続を提供しない（即ち、シリサイド層は意図的なブロック又は擬似ブロックを有するチャネルを完全に覆わない）こと、及び（2）電気的接続についてのアーチファクトエ

ッジ 2 8 は、電気的接続（即ち、正接続）に対するアーチファクトエッジ 2 8 が非電気的接続（即ち、誤接続）に対するアーチファクトエッジ 2 8 と比較的同じであること、は重要である。従って、単一の集積回路デバイスにおいて、図 1 A、1 B 及び 2 全てに示すタイプの導電性チャネルと非導電性チャネルとを含むことが望ましく、リバースエンジニアが保ち続ける図 1 B 及び 2 を参照して、図に示し且つ説明したタイプのチャネルを混合して用いることが望ましい。

#### 【 0 0 2 4 】

当業者は、図 1 A、1 B 及び 2 が P 型チャネルブロック構造 2 7 と共に N 型のドープされた領域 2 2 乃至 2 5 及び 2 9 を用いる一方、その逆に、図 1 A、1 B 及び 2 が N 型チャネルブロック構造 2 7 と共に P 型のドープされた領域 2 2 乃至 2 5 及び 2 9 を用いること 10 有効である。

#### 【 0 0 2 5 】

更に、本発明は、好適には、本発明が用いられる複数のトランジスタ回路を完全に無効にするばかりでなく、予期しない又は非直感的な方法で回路を機能させるようにする。例えば、O R ゲートであるように見えるものが、反対に、実際には A N D ゲートとして機能することが可能である。又は、反転入力として見えるものが、実際には、非反転であることが可能である。実際には、可能性が無限であり、リバースエンジニアが、これらの技術が利用される集積回路デバイスをどのようにリバースエンジニアリングするかを発見するために前進するのではなく、諦めてしまう程、非常に厄介であることをリバースエンジニアに認めさせることとなる。

#### 【 0 0 2 6 】

又、単一の集積回路（I C）において何度も、図 1 B 及び 2 の技術を用いることが望ましい。その場合、リバースエンジニアが、導電性チャネルの上に、図 1 B 及び 2 を参照して上で述べたシリサイドアーチファクトに遭遇するとき、リバースエンジニアは、チャネルブロックがあるべき位置にあるか否かを判定することができない。リバースエンジニアは、チャネルブロックの存在に関する仮定を構築する必要があるか又は、シリサイド開口におけるチャネルの導電性のタイプに対して調査するために非常に高度で時間を費やす必要のある技術を用いる必要がある。図 1 B 及び 2 の構造が所定の I C において何百回か見出された場合、リバースエンジニアは、シリサイド開口におけるチャネルの導電性のタイプに対する調査するために高度で時間を費やす必要のある技術又は各々の時点に対して仮定を設けるかどうかに拘らず、各々の及び全ての有効な時点において、チャネルブロックが利用できるか否かを確認するように試みることにおいて、やる気をくじかれる問題点を有する。

#### 【 0 0 2 7 】

最終的に、開示している方法及び装置は、集積回路デバイスがリバースエンジニアリングされないようにするために用いられることが可能である、他の偽装技術と互換性がある。それ故、この方法及び装置は、集積回路デバイスを成功裏にリバースエンジニアリングされないようにするために、所定の集積回路デバイスとともに用いられる多くの技術の 1 つであることが可能である。

#### 【 0 0 2 8 】

特定の好適な実施形態に結び付けて、本発明について説明したが、ここでは、当業者に対して、変更自体が確かに示唆されている。従って、本発明は、同時提出の特許請求の範囲に定める場合を除き、開示した実施形態に限定されるものではない。

#### 【 図面の簡単な説明 】

#### 【 0 0 2 9 】

【図 1 A】金属層及び酸化物層全ての導電性チャネルから取り除いた後にリバースエンジニアが見る、従来技術におけるシリサイド層のアーチファクトエッジについて示す図である。

【図 1 B】チャネルブロックを含む導電性チャネルから金属層及び酸化物層全ての取り除いた後にリバースエンジニアが見る、従来技術におけるシリサイド層のアーチファクトエ 50

ッジについて示す図である。

【図2】本発明の一実施形態に従って、金属層及び酸化物層全ての取り除いた後にリバースエンジニアが見る、シリサイド層のアーチファクトエッジについて示す図である。

【図1A】

【図1B】

【図2】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US 03/30212

A. CLASSIFICATION OF SUBJECT MATTER

IPC 7 H01L23/58 G11C7/24 G06K19/073 H01L21/285

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H01L G11C G06K

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category * | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                            | Relevant to claim No. |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X          | US 6 326 675 B1 (DE MUIZON EMMANUEL ET AL) 4 December 2001 (2001-12-04)<br>column 1, line 30 -column 2, line 43<br>column 3, line 47-57<br>column 3, line 58 -column 4, line 26;<br>figure 1<br>column 4, line 7-58; figures 2-7<br>-& WO 00 55889 A<br>21 September 2000 (2000-09-21)<br>--- | 1-12                  |

| A          | US 6 064 110 A (BAUKUS JAMES P ET AL)<br>16 May 2000 (2000-05-16)<br>column 2, line 19-64<br>column 6, line 10-21<br>column 8, line 1-54; figures 4A,4B<br>---                                                                                                                                | 1-12<br>-/-           |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

## \* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

\*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

\*&\* document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

4 February 2004

12/02/2004

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

Corchia, A

## INTERNATIONAL SEARCH REPORT

|                                                 |

|-------------------------------------------------|

| International Application No<br>PCT/US 03/30212 |

|-------------------------------------------------|

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                                                                                 |                       |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category                                             | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                              | Relevant to claim No. |

| A                                                    | US 6 117 762 A (BAUKUS JAMES P ET AL)<br>12 September 2000 (2000-09-12)<br>column 1, line 65 -column 2, line 34<br>column 4, line 14-54; figures 3,4<br>-----<br>A US 5 834 356 A (PRAMANIK DIPANKAR ET AL)<br>10 November 1998 (1998-11-10)<br>column 1, line 44-63; figure 1<br>column 5, line 51 -column 6, line 26;<br>figures 2-7<br>----- | 1-12                  |

|                                                      |                                                                                                                                                                                                                                                                                                                                                 | 1-12                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International Application No

PCT/US 03/30212

| Patent document cited in search report |    | Publication date |                                  | Patent family member(s)                                                             | Publication date                                                                 |

|----------------------------------------|----|------------------|----------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| US 6326675                             | B1 | 04-12-2001       | AU<br>CN<br>EP<br>JP<br>WO<br>US | 3737800 A<br>1296638 T<br>1082757 A1<br>2002539636 T<br>0055889 A1<br>2001041431 A1 | 04-10-2000<br>23-05-2001<br>14-03-2001<br>19-11-2002<br>21-09-2000<br>15-11-2001 |

| US 6064110                             | A  | 16-05-2000       | US<br>US<br>EP<br>JP<br>JP       | 5930663 A<br>5783846 A<br>0764985 A2<br>3172672 B2<br>9092727 A                     | 27-07-1999<br>21-07-1998<br>26-03-1997<br>04-06-2001<br>04-04-1997               |

| US 6117762                             | A  | 12-09-2000       | AU<br>EP<br>JP<br>WO             | 4244000 A<br>1183729 A1<br>2003520417 T<br>0065654 A1                               | 10-11-2000<br>06-03-2002<br>02-07-2003<br>02-11-2000                             |

| US 5834356                             | A  | 10-11-1998       | NONE                             |                                                                                     |                                                                                  |

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(71)出願人 505108281

レイセオン カンパニー

RAYTHEON COMPANY

アメリカ合衆国 02173 マサチューセッツ州 レキシントン スプリング ストリート 1

41

(74)代理人 100070150

弁理士 伊東 忠彦

(74)代理人 100091214

弁理士 大貫 進介

(74)代理人 100107766

弁理士 伊東 忠重

(72)発明者 チョウ , ラップ - ウイ

アメリカ合衆国 カリフォルニア州 91030 サウス・パサディナ カミーノ・リンドー 1

684

(72)発明者 クラーク , ウィリアム エム , ジュニア

アメリカ合衆国 カリフォルニア州 93012 カマリロ パキータ・ストリート 1137

(72)発明者 ハービソン , ギャヴィン ジェイ

アメリカ合衆国 カリフォルニア州 90292 マリーナ・デル・レイ ヴィア・マリーナ 4

127 415号

(72)発明者 ボウクス , ジェイムズ ピー

アメリカ合衆国 カリフォルニア州 91361 ウエストレイク・ヴィレッジ ドラムクリフ・

コート 1718

F ターム(参考) 5F038 BH20 CD19 DF10 EZ12 EZ20