# (19) 대한민국특허청(KR) (12) 등록특허공보(B1)

| (51) Int. CI. <sup>6</sup><br>H01L 23/28 |                                                                            | (45) 공고일자<br>(11) 등록번호<br>(24) 등록일자 | 2000년01월15일<br>10-0236633<br>1999년10월04일 |

|------------------------------------------|----------------------------------------------------------------------------|-------------------------------------|------------------------------------------|

| (21) 출원번호<br>(22) 출원일자                   | 10-1996-0046948<br>1996년 10월 19일                                           | (65) 공개번호<br>(43) 공개일자              | 특 1998-0028019<br>1998년07월 15일           |

| (73) 특허권자                                | 아남반도체주식회사 김규현                                                              |                                     |                                          |

| (72) 발명자                                 | 서울특별시 성동구 성수동 2가 280-8<br>하선호<br>경기도 고양시 일산동 1055번지 후곡마을 708동 1402호<br>허영욱 |                                     |                                          |

|                                          |                                                                            |                                     |                                          |

|                                          | 경기도 성남시 분당구 수내동 55 롯데아파트 132-1504<br>한병준                                   |                                     |                                          |

| (74) 대리인                                 | 서울특별시 송파구 방이동 올림픽아파트 125동 502호<br>서만규                                      |                                     |                                          |

| <i>시기기 · 이기취</i>                         |                                                                            |                                     |                                          |

#### (54) 인쇄회로기판 스트립 구조와 이를 이용한 반도체 패키지 제조방법

### 요약

본 발명은 인쇄 회로 기판 스트립 구조와 이를 이용한 반도체 패키지 제조 방법에 관한 것으로, 반도체 칩 안착 영역과, 상기 반도체 칩 안착 영역의 주변에 방사상으로 회로 패턴이 형성된 카파 트레이스와, 상기 카파 트레이스에 형성된 전도성 비아 홀과, 상기 전도성 비아 홀의 외측으로 형성된 사각 형상의 싱귤레이션부로 구성된 다수의 인쇄 회로 기판 유닛이 일체로 연결되어서 이루어진 인쇄 회로 기판 스트립에 있어서, 상기 각각의 인쇄 회로 기판 유닛에 사각 형상의 컷팅부가 적어도 한개 이상 형성된 것과, 상기 컷팅부가 형성된 개별 인쇄 회로 기판 유닛이 인쇄 회로 기판 스트립에서 착탈 가능하도록 형성된 인쇄 회로 기판 스트립 구조와 이를 이용한 반도체 패키지 제조 방법을 제공함으로서 생산성 및 수율을 향상 시킬 수 있는 효과가 있다.

#### 대표도

### 명세서

#### 도면의 간단한 설명

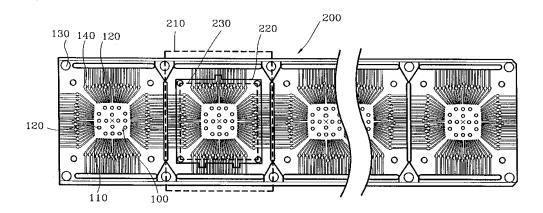

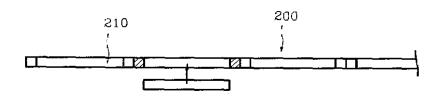

제1도는 일반적인 인쇄 회로 기판 스트립 구조를 나타낸 평면도이다.

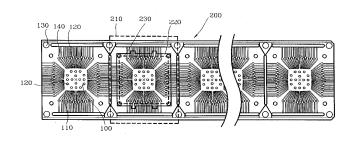

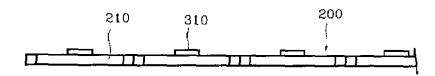

제2도는 본 발명의 제1실시예인 인쇄 회로 기판 스트립 구조를 나타낸 평면도이다.

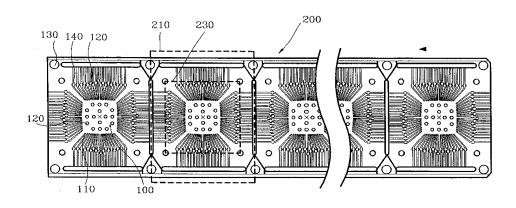

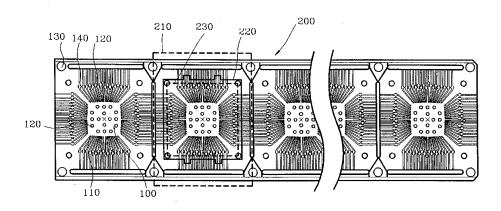

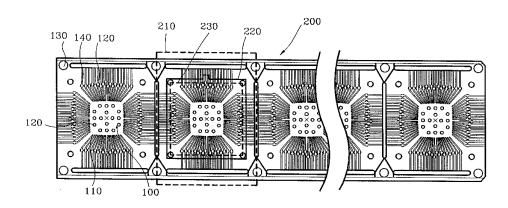

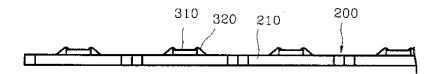

제3(a)도 및 제3(b)도는 본 발명의 제2실시예인 인쇄 회로 기판 스트립 구조를 나타낸 평면도이다.

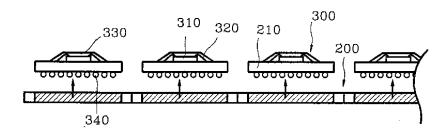

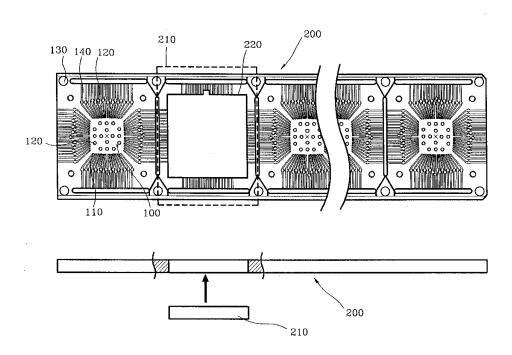

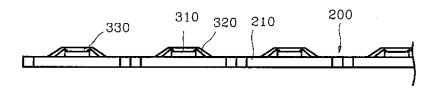

제4도는 본 발명에 의한 인쇄 회로 기판 유닛의 교체 상태를 나타낸 상태도이다.

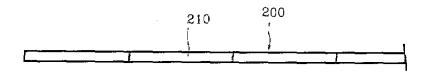

제5(a)도 내지 제5(h)도는 본 발명의 제3실시예인 반도체 패키지 제조 방법을 나타낸 상태도이다.

\* 도면의 주요부분에 대한 부호의 설명

100 : 반도체 칩 안착 영역

120 : 전도성 비아 홀

140 : 카파 트레이스

150 : 솔더 마스크

200 : 인쇄 회로 기판 스트립 210 : 인쇄 회로 기판 유닛

220 : 컷팅부 230 : 싱귤레이션부 300 : 반도체 패키지 310 : 반도체 칩 320 : 전도성 와이어 330 : 봉지재

340 : 솔더 볼

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술분야 및 그 분야의 종래기술

본 발명은 인쇄 회로 기판 스트립 구조와 이를 이용한 반도체 패키지 제조 방법에 관한 것으로, 보다 상세하게 설명하면 반도체 패키지의 한 구성 재료인 인쇄 회로 기판 스트립에서 불량의 인쇄 회로 기판 유닛을 양품의 인쇄 회로 기판 유닛으로 용이하게 교체할 수 있는 인쇄 회로 기판 스트립 구조를 제공함으로서 반도체 패키지의 생산성 및 수율을 향상시킬 수 있는 인쇄 회로 기판 스트립 구조와 이를 이용한 반도체 패키지 제조 방법에 관한 것이다.

일반적으로 인쇄 회로 기판(Printed Circuit Board)은 반도체 칩의 회로 설계에 입각하여 반도체 칩의 입/출력 패드(Input/Output Pad)가 접속되는 전기 배선등을 카파 트레이스(Copper Trace)라는 수단을 이용하여 포토 에칭(Photo Etching)등의 기술에 의해 강체 또는 유연성(세라믹 또는 유기질)의 섭스트레이트 (Substrate) 위에 적층시킨 기판으로 그 용도는 메인 보드(Main Board)로의 전기 배선과 반도체 칩 장착의 두 기능을 동시에 수행하는 자재를 말한다. 이러한 인쇄 회로 기판은 섭스트레이트 재료에 얇은 카파트레이스를 적층시킨 섭스트레이트를 출발 재료로 하여 불필요한 카파 트레이스 부분을 에칭 등으로 제거함으로서 카파 트레이스 패턴(Pattern)을 형성하는 에치드 포일(Etched Foil) 방법 또는 섭스트레이트 재료의 필요한 카파 트레이스 부분에만 선택적으로 카파를 도금하여 전도성 배선 패턴을 형성하는 애디티브 (Additive) 방법 등이 있다.

이러한 인쇄 회로 기판은 IC(Integrated Circuit), LSI(Large Scale Integrated Circuit)등 고밀도의 입/ 출력 핀 수를 가진 반도체 칩의 요구를 만족할 수 있도록 배선의 고밀도화와 배선의 고신뢰성을 기대할 수 있기 때문에 최근의 볼 그리드 어레이 패키지(Ball Grid Array Package), 핀 그리드 어레이 패키지 (Pin Grid Array Package), 칩 사이즈 패키지(Chip Size Package) 등에 주로 이용되는 추세에 있다.

실제로 상기한 인쇄 회로 기판은 제1도의 평면도에 도시된 바와 같이, 우선 다수의 인쇄 회로 기판 유닛 (210)이 연결되어 하나의 인쇄 회로 기판 스트립(200)을 구성하고 있으며, 상기 각각의 인쇄 회로 기판 유닛(210)은 다음과 같이 이루어져 있다.

중앙부에는 다수의 전도성 비아 홀(120)이 형성된 사각의 반도체 칩 안착 영역(100)과, 상기 반도체 칩 안착 영역(100)의 주변에 방사상으로 그리고 고밀도로 형성된 카파 트레이스(140)(배선 영역)와, 상기 카파 트레이스(140)의 중간 지점에 형성된 전도성 비아 홀(120)과, 상기 인쇄 회로 기판의 가장 자리에 형성된 로딩홀(130) 등을 포함하여 이루어져 있다. 여기서 상기 반도체 칩 안착 영역(100) 근처의 카파 트레이스(140)에는 나중에 반도체 칩과의 와이어 본딩을 용이하게 하기 위해 금(Au) 또는 은(Ag)으로 도금된 도금 영역(110)이 형성되어 있고, 상기한 인쇄 회로 기판 유닛(210)은 보통 4~8개가 연결되어 하나의인쇄 회로 기판 스트립(200)을 이루고 있다. 또한 부호 230은 반도체 패키지 제조 단계의 마지막 단계에서 각각의 반도체 패키지로 절단되어 싱귤레이션 될 영역인 싱귤레이션부를 나타낸 것이다.

이러한 구조의 인쇄 회로 기판 유닛을 이용하여 종래에 반도체 패키지가 제조되는 과정을 간단히 설명하면 다음과 같다.

- 1. 다수의 인쇄 회로 기판 유닛으로 이루어진 인쇄 회로 기판 스트립에 반도체 칩이 접착제에 의해 반도체 칩 안착 영역에 안착되는 반도체 칩 접착 공정.

- 2. 상기 반도체 칩의 입/출력 패드와 인쇄 회로 기판 유닛에 형성된 카파 트레이스를 전도성 금속 세선을 이용하여 본딩하는 와이어 본딩(Wire Bonding) 공정.

- 3. 상기 반도체 칩과 와이어 등을 외부의 환경으로부터 보호하기 위해 에폭시 몰딩 컴파운드(Epoxy Molding Compound) 또는 액상 봉지재(Glob Top)를 이용하여 봉지하는 몰딩(Molding) 공정.

- 4. 상기 자재에서 메인 보드로의 신호 입/출력 단자인 솔더 볼(Solder Ball)을 융착 시키는 솔더 볼 융착 공정.

- 5. 상기 인쇄 회로 기판 스트립에서 각각의 반도체 패키지로 절단하는 싱귤레이션(Singulation) 공정 등 으로 이루어져 있다.

여기서 주목할 만한 것은, 상기 모든 단계에서의 인쇄 회로 기판 유닛은 반도체 패키지의 수율 향상을 위하여 다수의 인쇄 회로 기판 유닛이 연결되어 형성된 인쇄 회로 기판 스트립 채로 취급된다는 것이다. 그러나 제조 단계에 있어서, 인쇄 회로 기판 스트립에서 어느 하나의 인쇄 회로 기판 유닛에 불량이 발생한다면 그 인쇄 회로 기판 유닛에 불량 표식만을 할 뿐 반도체 칩 접착 공정, 와이어 본딩 공정, 몰딩공정은 동일하게 이루어진다는 것이다. 즉 제조 공정상에 발생되는 불량 인쇄 회로 기판 유닛이 정상 자재와동일하게 취급되고 공정이 완료된 후에나 그 불량 인쇄 회로 기판 유닛 즉, 불량 반도체 패키지만을 골라내어 폐기 처분함으로서 오히려 반도체 패키지의 수율 저하 및 생산성을 저하시키는 문제점이 발생하는

것이다.

#### 발명이 이루고자 하는 기술적 과제

본 발명은 상기와 같은 문제점을 해결하기 위해 발명한 것으로 반도체 패키지 제조 공정상의 한 구성 재료인 인쇄 회로 기판 스트립에서 불량의 인쇄 회로 기판 유닛을 양품의 인쇄 회로 기판 유닛으로 용이하게 교체할 수 있는 인쇄 회로 기판 스트립 구조를 마련하여 반도체 패키지를 제조함으로서 반도체 패키지의 생산성 및 수율을 향상시킬 수 있는 인쇄 회로 기판 스트립과 이를 이용한 반도체 패키지 제조 방법을 제공하는데 있다.

### 발명의 구성 및 작용

상기한 목적을 달성하기 위하여 본 발명에 의한 인쇄 회로 기판 스트립은, 반도체 칩 안착 영역과, 상기 반도체 칩 안착 영역의 주변에 방사상으로 회로 패턴이 형성된 카파 트레이스와, 상기 카파 트레이스에 형성된 전도성 비아 홀과, 상기 전도성 비아 홀의 외측으로 형성된 사각 형상의 싱귤레이션부로 구성된 다수의 인쇄 회로 기판 유닛이 일체로 연결되어서 이루어진 인쇄 회로 기판 스트립에 있어서, 상기 각각 의 인쇄 회로 기판 유닛에 사각 형상의 컷팅부를 적어도 한 개 이상 형성하고, 상기 컷팅부가 형성된 개 별 인쇄 회로 기판 유닛이 인쇄 회로 기판 스트립에서 착탈 가능하도록 형성한 것을 그 특징으로 한다.

여기서, 상기 컷팅부의 영역은 싱귤레이션부보다 크거나 같게 형성하며, 그 컷팅부에는 적어도 하나 이상 의 요철들을 서로 대칭으로 형성하거나 비대칭으로 형성하여 본 발명의 목적을 달성할 수도 있다.

상기한 목적을 달성하기 위하여 상기 인쇄 회로 기판 스트립을 이용한 반도체 패키지 제조 방법은, 먼저 상기 인쇄 회로 기판 스트립을 검사하는 단계와, 상기 인쇄 회로 기판 스트립에서 불량 인쇄 회로 기판 유닛을 확인하여 컷팅하는 단계와, 상기 컷팅된 불량 인쇄 회로 기판 유닛을 인쇄 회로 기판 스트립으로 부터 제거 한후, 별도의 양호한 인쇄 회로 기판 유닛으로 상기 인쇄 회로 기판 스트립에 교체하는 단계와, 상기 각각의 인쇄 회로 기판 유닛에 반도체 칩을 부착하는 반도체 칩 부착 단계와, 상기 반도체 칩과 회로 패턴인 카파 트레이스를 전도성 와이어로 본딩하는 와이어 본딩 단계와, 상기 반도체 칩과 전 도성 와이어 등을 봉지재로 감싸는 몰딩 단계와, 상기 각각의 인쇄 회로 기판 유닛에 솔더 볼을 부착하는 솔더볼 부착 단계와, 상기 인쇄 회로 기판 스트립으로부터 각각의 반도체 패키지로 절단하는 싱귤레이션 단계로 이루어진 것을 그 특징으로 한다.

여기서 상기 교체되는 불량 인쇄 회로 기판 유닛의 형상과 양호한 인쇄 회로 기판 유닛의 형상은 동일하게 형성한다.

또한 상기 반도체 칩 부착 단계 후에 인쇄 회로 기판 유닛상의 반도체 칩 부착 상태를 검사하여 불량 인쇄 회로 기판 유닛을 제거하고, 양호한 인쇄 회로 기판 유닛 또는 반도체 칩이 양호하게 부착된 양호한인쇄 회로 기판 유닛중 어느 하나를 선택하여 교체할 수 있다.

또한, 상기 와이어 본딩 단계 후에 인쇄 회로 기판 유닛상의 와이어 본딩 상태를 검사하여 불량 인쇄 회로 기판 유닛을 제거하고, 양호한 인쇄 회로 기판 유닛, 반도체 칩이 양호하게 부착된 양호한 인쇄 회로 기판 유닛, 또는 와이어 본딩이 양호하게 된 양호한 인쇄 회로 기판 유닛중 어느 하나를 선택하여 교체할수도 있다.

더불어, 상기 솔더 볼 부착 단계전 솔더 볼 랜드를 전기적으로 검사하여 불량 인쇄 회로 기판 유닛을 제 거하고, 몰딩이 완료된 양호한 인쇄 회로 기판 유닛으로 교체할 수도 있다.

상기와 같이 교체되는 양호한 인쇄 회로 기판 유닛은 제거되는 불량 인쇄 회로 기판 유닛과 동일한 반도 체 패키지 제조 단계의 상태에 있는 것을 사용함이 바람직하다.

이하, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 본 발명에 의한 인쇄 회로 기판 스트립 구조와 이를 이용한 반도체 패키지 제조 방법을 용이하게 실시할 수 있을 정도로 첨부된 도면을 참조하여 본 발명의 가장 바람직한 실시예를 상세하게 설명하면 다음과 같다.

제2도는 본 발명의 제1실시예인 인쇄 회로 기판 스트립(200)의 구조를 나타낸 평면도이다.

인쇄 회로 기판 스트립(200)은 보통 4~8개의 개별 인쇄 회로 기판 유닛(210)이 연결되어 이루어져 있으며 그 각각의 인쇄 회로 기판 유닛(210)의 구조는 다음과 같다.

중앙부에는 반도체 칩 안착 영역(100)이 형성되어 있으며, 상기 반도체 칩안착 영역(100)의 주변으로는 방사상으로 세밀하게 카파 트레이스(140)로서 회로 패턴이 형성되어 있다. 상기 반도체 칩 안착 영역(100)에는 반도체 칩에 그라운드 또는 파워 제공을 위해 다수의 전도성 비아 홀(120)이 형성되어 있으며 카파 트레이스(140)에도 반도체 칩으로부터의 시그널을 메인 보드에 전달시키기 위해 전도성 비아 홀(120)이 다수 형성되어 있다. 또한 상기 카파 트레이스(140)의 전도성 비아홀(120) 외측으로는 사각 형상의 싱귤레이션부(230)가 형성되어 있으며, 그 싱귤레이션부(230) 외곽으로는 상기 인쇄 회로 기판 유닛(210)이 불량으로 확인될 경우 양호한 인쇄 회로 기판 유닛(210)으로 교체하기 위해 적어도 하나 이상의 컷팅부(220)가 형성되어 있다. 상기 컷팅부(220)는 그 인쇄 회로 기판 유닛(210)이 불량으로 확인될 경우에만 실시하는 것으로 양품의 인쇄 회로 기판 유닛(210)에는 형성하지 않는다.

여기서 상기 컷팅부(220)가 형성된 인쇄 회로 기판 유닛(210)은 인쇄 회로 기판 스트립(200)에서 착탈 가능한 구조로 되어 있으며, 상기 컷팅부(220)의 영역은 싱귤레이션부(230)보다 크거나 같게 형성할 수 있다. 또한 상기 컷팅부(220)에는 적어도 하나 이상의 요철들을 서로 대칭시켜 형성함이 바람직하다.

한편, 당업자는 상기 불량의 인쇄 회로 기판 유닛(210)의 컷팅 수단으로, 싱귤레이션 작업에 이용되는 장비를 이용하여 실시할 수 있음을 쉽게 알 수 있을 것이다.

제3(a)도 및 제3(b)도는 본 발명의 제2실시예인 인쇄 회로 기판 스트립(200)의 구조를 나타낸 평면도로서

상기 인쇄 회로 기판 스트립(200)에서 절단되는 불량의 인쇄 회로 기판 유닛(210)의 형태는 한 방향에만 요철을 형성하거나 또는 비대칭의 요철을 갖는 형태로 컷팅된 것을 알 수 있다. 한편 상기 컷팅된 불량인쇄 회로 기판 유닛(210)의 자리에는 양품의 인쇄 회로 기판 유닛(210)이 삽입되어 고정될 수 있도록 동일한 모양으로 절단된 양품의 인쇄 회로 기판 유닛(210)을 준비하는 것은 당연하다.

상기한 바와 같이 한 방향으로 또는 비대칭으로 요철을 형성한 이유는 양품의 인쇄 회로 기판 유닛(210)을 삽입하여 교체시 그 방향성을 유지시키기 위함이다. 즉 상기 인쇄 회로 기판 유닛(210)이 불량의 인쇄회로 기판 유닛(210)이 제거된 인쇄회로 기판 스트립(200)에 삽입될 때에 전, 후 또는 좌, 우 면이 바뀌지 않은 상태에서 삽입될 수 있도록 구별하여 반도체 패키지(300) 제조 공정중에 불량이 발생하지 않토록하기 위함인 것이다. 또한 그 양품의 인쇄회로 기판 유닛(210)이 삽입되어 접촉되는 면적을 최대로 함으로서 그 접착력을 더욱 향상시키기 위함이기도 하다.

제4도는 본 발명에 의한 인쇄 회로 기판 유닛(210)의 교체 상태를 나타낸 상태도로서 불량의 인쇄 회로 기판 유닛(210)이 제거된 자리에 양품의 인쇄 회로 기판 유닛(210)이 삽입되어 고정되는 것을 나타낸 것이다.

상기한 양품의 인쇄 회로 기판 유닛(210)은 한 번 삽입되어 고정되면 어느 정도의 힘이 가해지기 전까지는 상기 인쇄 회로 기판 스트립(200)에서 분리되지 않는 데 그 이유는 상기 인쇄 회로 기판 유닛(210)의 재료인 솔더 마스크(150), 섭스 트레이트, 카파 트레이스(140)의 컷팅되는 면이 불규칙적이고 까칠까칠하게 약간 돌출되어 형성되기 때문에 양품의 인쇄 회로 기판 유닛(210)이 삽입되었을 경우 그 인쇄 회로 기판 유닛(210)을 용이하게 고정시키는 것이다. 또한 상기와 같은 성질로 인해 반도체 칩 접착 공정, 와이어 본딩 공정, 몰딩 공정 등에서 상기 교체된 인쇄 회로 기판 유닛(210)이 인쇄 회로 기판 스트립(200)에서 분리되지 않고 원활하게 공정이 수행 될 수 있는 것이다.

이제까지의 설명에서는 인쇄 회로 기판 유닛이 착탈식으로 교체되는 것에 한하여 설명하였으나, 본 발명은 이러한 실시예에 의해 한정되는 것은 아니며 다양한 변형된 실시예를 가질 수 있다. 예컨데, 인쇄 회로 기판 스트립에서 불량 인쇄 회로 기판 유닛 전체를 일정 모양으로 컷팅하여 제거하고, 양호한 인쇄 회로 기판 유닛 전체를 접착제를 이용하여 접착하여 사용할 수도 있다. 즉, 인쇄 회로 기판 스트립에서 유닛과 유닛의 경계 부분을 따라 일단 또는 양단을 완전히 컷팅하여 불량 인쇄 회로 기판 유닛을 제거한후, 상기 인쇄 회로 기판 스트립의 컷팅된 면과 대응하는 모양으로 컷팅된 양호한 인쇄 회로 기판 유닛을 접착제로 접착하여 사용할 수 있을 것이다. 이때, 상기 컷팅된 면의 면적은 최대한 넓게 확보함으로써 접착제와의 접착력이 향상되도록 함이 바람직하다. 즉, 유닛과 유닛의 경계 부분을 따라서 대략 "S" 자형으로 컷팅하거나, 또는 다수회 절곡된 라인 형태로 컷팅함으로써 그 컷팅된 면의 면적을 최대한 확보함이바람직하다.

제5(a)도 내지 제5(h)도는 본 발명의 제3실시예로 상기 인쇄 회로 기판 스트립(200)을 이용하여 반도체 패키지(300)를 제조하는 방법을 도시한 것이며, 본 발명에 의한 반도체 패키지(300)의 제조 방법은 다음과 같이 이루어져 있다.

- 1. 반도체 칩 안착 영역(100)과, 상기 반도체 칩 안착 영역(100)의 주변에 방사상으로 회로 패턴이 형성된 카파 트레이스(140)와, 상기 카파 트레이스(140)에 형성된 전도성 비아 홀(120)과, 상기 전도성 비아홀(120)의 외측으로 형성된 사각 형상의 싱귤레이션부(230)로 구성된 다수의 인쇄 회로 기판 유닛(210)이일체로 연결되어서 이루어진 인쇄 회로 기판 스트립(200)에 있어서 상기 각 구성 요소의 불량 여부를 검사하는 단계(제5(a)도).

- 2. 상기 인쇄 회로 기판 스트립(200)에서 불량 인쇄 회로 기판 유닛(210)을 확인하여 싱귤레이션부(230)보다 크거나 같은 크기로 컷팅부(220)를 형성하고 컷팅하여 제거하는 단계(제5(b)도).

- 3. 상기 컷팅된 불량 인쇄 회로 기판 유닛(210)의 영역에 별도의 양호한 인쇄 회로 기판 유닛(210)을 준비하여 상기 인쇄 회로 기판 스트립(200)에서 교체하는 단계(제5(c)도).

- 4. 상기 인쇄 회로 기판 스트립(200)의 반도체 칩 안착 영역(100)에 접착제로서 반도체 칩(310)을 부착하는 반도체 칩 부착 단계(제5(d)도).

- 5. 상기 반도체 칩(310)의 입/출력 패드와 회로 패턴인 카파 트레이스(140)를 전도성 와이어(320)로 본딩하는 와이어 본딩 단계(제5(e)도).

- 6. 상기 반도체 칩(310)과 전도성 와이어(320) 등을 외부의 환경으로부터 보호하기 위해 에폭시 몰딩 컴 파운드나 액상 봉지재등의 봉지재(330)를 이용하여 감싸는 몰딩 단계(제5(f)도).

- 7. 상기 인쇄 회로 기판 스트립(200)의 저면에 반도체 칩(310)의 입/출력 수단인 솔더 볼(340)을 리플로 우 하여 융착하는 솔더 볼 융착 단계(제5(g)도).

- 8. 상기 인쇄 회로 기판 스트립(200)에서 각각의 반도체 패키지(300)로 싱귤 레이션부(230)를 따라서 싱귤레이션 시키는 단계(제5(h)도).

여기서, 상기 교체되는 양호한 인쇄 회로 기판 유닛(210)의 형상은 컷팅되는 불량 인쇄 회로 기판의 형상 과 동일한 것을 사용한다.

또한, 상기 각 구성 요소의 불량 여부를 검사하는 단계는 각 단계 즉, 반도체칩 부착 단계(제5(d)도), 와이어 본딩 단계(제5(e)도), 몰딩 단계(제5(f)도), 솔더 볼 융착 단계(제5(h)도) 등에서 실시될 수 있고, 상기 검사 결과 불량으로 판정된 인쇄 회로 기판 유닛(210)은 각 단계에 상응하는 인쇄 회로 기판 유닛 또는 그 이전 단계의 것으로 교체될 수 있다.

이를 보다 상세히 설명하면, 상기 제조 단계에서 반도체 칩 부착 단계후에 인쇄 회로 기판 유닛(210)상의 반도체 칩(310) 부착 상태를 검사하여, 불량 인쇄 회로 기판 유닛(210)(즉, 반도체 칩의 부착 상태가 불 량인 것)으로 확인되면 이를 제거하고, 양호한 인쇄 회로 기판 유닛(210) 또는 반도체 칩(310)이 양호하 게 부착된 양호한 인쇄 회로 기판 유닛(210)중 어느 하나를 선택하여 교체할 수 있다. 이때, 상기 반도체 칩(310)의 불량은 통상 반도체 칩(310)이 규정치 이상으로 틸트(Tilt)되어 부착되었거나, 또는 접착제가 반도체 칩(310)의 상면까지 타고 올라와 와이어 본딩될 부분을 오염시켰거나, 접착제가 인쇄 회로 기판 유닛(210)에 형성된 카파 트레이스를 오염시켜 와이어 본딩이 불가능한 것 등을 감지하고, 이를 불량 인쇄 회로 기판 유닛(210)으로 확인하여 제거한다.

또한, 상기 와이어 본딩 단계 후에 인쇄 회로 기판 유닛(210)상의 와이어 본딩 상태를 검사하여 불량 인쇄 회로 기판 유닛(210)을 제거하고, 양호한 인쇄 회로 기판 유닛(210), 반도체 칩(310)이 양호하게 부착된 양호한 인쇄 회로 기판 유닛(210), 또는 와이어 본딩이 양호하게 된 양호한 인쇄 회로 기판 유닛(210)중 어느 하나로 교체할 수 있다. 즉, 반도체 칩(310)과 인쇄 회로 기판 유닛(210)의 카파 트레이스를 전기적으로 연결하는 와이어가 서로 쇼트되었거나, 또는 불완전하게 와이어 본딩되었거나, 또는 단란된 와이어가 있을 경우 이를 불량 인쇄 회로 기판 유닛(210)으로 판단하여 제거하게 된다.

더불어, 상기 솔더 볼(340) 부착 단계전에 상기 솔더 볼이 부착될 인쇄 회로 기판 유닛(210)의 솔더 볼 랜드를 전기적으로 검사하여 인쇄 회로 기판 유닛(210)의 불량 여부를 판단하게 되는데 이때 불량으로 판 단된 인쇄 회로 기판 유닛(210)을 제거하고, 이 제거된 부분에 몰딩이 완료된 양호한 인쇄 회로 기판 유 닛(210)을 끼워 넣을 수도 있으며, 이렇게 하여 불필요한 솔더 볼(340)의 낭비를 방지할 수 있게 된다.

한편, 상술한 것 외에 상기 교체되는 양호한 인쇄 회로 기판 유닛(210)은 제거되는 불량 인쇄 회로 기판 유닛(210)과 동일한 반도체 패키지(300) 제조 단계의 상태에 있는 것 또는 상술한대로 그 이전 단계에 있 는 것을 사용함이 바람직하다.

본 발명은 비록 이상에서와 같은 실시예들에 한하여만 설명하였지만, 여기에 만 한정되지 않으며 본 발명의 범주와 사상에서 벗어남 없이 여러 가지의 변형과 수정이 이루어 질 수 있을 것이다.

#### 발명의 효과

따라서 본 발명은, 다수의 인쇄 회로 기판 유닛으로 이루어진 인쇄 회로 기판 스트립에서 불량 인쇄 회로 기판 유닛을 사각 모양의 컷팅부를 형성하여 컷팅한 다음 양호한 인쇄 회로 기판 유닛으로 교체한 것과 이를 이용한 반도체 패키지 제조 방법을 제공함으로서, 반도체 패키지의 생산성 및 수율 향상의 효과를 가져온다.

### (57) 청구의 범위

#### 청구항 1

반도체 칩 안착 영역과, 상기 반도체 칩 안착 영역의 주변에 방사상으로 회로 패턴이 형성된 카파 트레이스와, 상기 카파 트레이스에 형성된 전도성 비아 홀과, 상기 전도성 비아 홀의 외측으로 형성된 사각 형상의 싱귤레이션부로 구성된 다수의 인쇄 회로 기판 유닛이 일체로 연결되어서 이루어진 인쇄 회로 기판스트립에 있어서, 상기 각각의 인쇄 회로 기판 유닛에 사각 형상의 컷팅부가 적어도 한 개 이상 형성된 것과, 상기 컷팅부가 형성된 개별 인쇄 회로 기판 유닛이 인쇄 회로 기판 스트립에서 착탈 가능하도록 형성된 것을 특징으로 하는 인쇄 회로 기판 스트립 구조.

#### 청구항 2

제1항에 있어서, 상기 컷팅부의 영역은 싱귤레이션부보다 크거나 같게 형성된 것을 특징으로 하는 인쇄회로 기판 스트립 구조.

#### 청구항 3

제1항 또는 제2항 중 어느 한 항에 있어서, 상기 컷팅부에는 적어도 하나 이상의 요철들이 서로 대칭으로 형성된 것을 특징으로 하는 인쇄 회로 기판 스트립 구조.

#### 청구항 4

제1항 또는 제2항 중 어느 한 항에 있어서, 상기 컷팅부에는 적어도 하나 이상의 요철들이 서로 비대칭으로 형성된 것을 특징으로 하는 인쇄 회로 기판 스트립 구조.

#### 청구항 5

반도체 칩 안착 영역과, 상기 반도체 칩 안착 영역의 주변에 방사상으로 회로 패턴이 형성된 카파 트레이스와, 상기 카파 트레이스에 형성된 전도성 비아 홀과, 상기 전도성 비아 홀의 외측으로 형성된 사각 형상의 싱귤레이션부로 구성된 다수의 인쇄 회로 기판 유닛이 일체로 연결되어서 이루어진 인쇄 회로 기판스트립을 검사하는 단계와, 상기 인쇄 회로 기판스트립중 불량 인쇄 회로 기판 유닛을 확인하여 컷팅하는 단계와, 상기 컷팅된 불량 인쇄 회로 기판 유닛을 인쇄 회로 기판스트립으로부터 제거 한 후, 별도의양호한 인쇄 회로 기판 유닛으로 상기 인쇄 회로 기판스트립에서 교체하는 단계와, 상기 각각의 인쇄 회로 기판 유닛에 반도체 칩을 부착하는 반도체 칩 부착 단계와, 상기 반도체 칩과 회로 패턴인 카파 트레이스를 전도성 와이어로 본딩하는 와이어 본딩 단계와, 상기 반도체 칩과 전도성 와이어 등을 봉지재로감싸는 몰딩 단계와, 상기 각각의 인쇄 회로 기판 유닛에 솔더 볼을 부착하는 솔더 볼 부착 단계와, 상기인쇄 회로 기판 스트립에서 각각의 반도체 패키지로 절단하는 싱귤레이션 단계로 이루어진 것을 특징으로하는 반도체 패키지 제조 방법.

#### 청구항 6

제5항에 있어서, 상기 교체되는 불량 인쇄 회로 기판 유닛의 형상과 양호한 인쇄 회로 기판의 형상은 동 일한 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 청구항 7

제5항에 있어서, 상기 반도체 칩 부착 단계 후에 인쇄 회로 기판 유닛상의 반도체 칩 부착 상태를 검사하여 불량 인쇄 회로 기판 유닛을 제거하고 양호한 인쇄 회로 기판 유닛으로 교체하는 단계를 더 포함하여 이루어진 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 청구항 8

제5항에 있어서, 상기 와이어 본딩 단계 후에 인쇄 회로 기판 유닛상의 와이어 본딩 상태를 검사하여 불량 인쇄 회로 기판 유닛을 제거하고 양호한 인쇄 회로 기판 유닛으로 교체하는 단계를 더 포함하여 이루어진 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 청구항 9

제5항에 있어서, 상기 솔더 볼 부착 단계전 솔더 볼 랜드를 전기적으로 검사하여 불량 인쇄 회로 기판 유닛을 제거하고, 몰딩이 완료된 양호한 인쇄 회로 기판 유닛으로 교체하는 단계를 더 포함하여 이루어진 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 청구항 10

제5항 내지 제9항 중 어느 한 항에 있어서, 상기 교체되는 양호한 인쇄 회로 기판 유닛은 제거되는 불량 인쇄 회로 기판 유닛과 동일한 반도체 패키지 제조 단계 또는 그 이전 단계의 상태에 있는 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 도면

#### 도면1

#### 도면2

### 도면3a

### 도면3b

### 도면4

## 도면5a

# 도면5b

# *도면5c*

# 도면5d

## *도면5e*

## 도면5f

도면5g

### *도면5*h