(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6147785号

(P6147785)

(45) 発行日 平成29年6月14日(2017.6.14)

(24) 登録日 平成29年5月26日(2017.5.26)

(51) Int.Cl.

F 1

|              |           |      |       |      |

|--------------|-----------|------|-------|------|

| HO1L 29/786  | (2006.01) | HO1L | 29/78 | 612C |

| HO1L 21/8234 | (2006.01) | HO1L | 29/78 | 618B |

| HO1L 27/06   | (2006.01) | HO1L | 27/06 | 102A |

| HO1L 27/08   | (2006.01) | HO1L | 27/08 | 331E |

| HO1L 27/088  | (2006.01) | HO1L | 29/78 | 616V |

請求項の数 2 (全 80 頁) 最終頁に続く

|              |                                   |

|--------------|-----------------------------------|

| (21) 出願番号    | 特願2015-36246 (P2015-36246)        |

| (22) 出願日     | 平成27年2月26日(2015.2.26)             |

| (62) 分割の表示   | 特願2010-44930 (P2010-44930)<br>の分割 |

| 原出願日         | 平成22年3月2日(2010.3.2)               |

| (65) 公開番号    | 特開2015-135977 (P2015-135977A)     |

| (43) 公開日     | 平成27年7月27日(2015.7.27)             |

| 審査請求日        | 平成27年2月27日(2015.2.27)             |

| (31) 優先権主張番号 | 特願2009-51857 (P2009-51857)        |

| (32) 優先日     | 平成21年3月5日(2009.3.5)               |

| (33) 優先権主張国  | 日本国(JP)                           |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 木村 肇<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| 審査官       | 小堀 行彦                                          |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁面を有する基板上に、透光性を有する第1の導電層と、第2の導電層とを積層し、前記第2の導電層上に第1のマスクを形成し、

前記第1のマスクを用いて前記第1の導電層及び前記第2の導電層をエッチングして、第3の導電層と、前記第3の導電層上の第4の導電層と、第5の導電層と、前記第5の導電層上の第6の導電層と、を形成し、

前記第1のマスクを後退させて第2のマスクを形成し、

前記第2のマスクを用いて、前記第4の導電層をエッチングして前記第3の導電層上に第7の導電層を形成するとともに、前記第6の導電層を除去し、

前記第3の導電層及び前記第5の導電層と接するように、透光性を有する半導体層を形成し、

前記半導体層を覆う領域を有する絶縁層を形成し、

前記絶縁層上に、透光性を有する第8の導電層と、第9の導電層とを積層し、

前記第9の導電層上に第3のマスクを形成し、

前記第3のマスクを用いて前記第8の導電層及び前記第9の導電層をエッチングして、前記半導体層と重なる領域を有する第10の導電層と、前記第10の導電層上の第11の導電層とを形成し、

前記第3のマスクを後退させて第4のマスクを形成し、

前記第4のマスクを用いて前記第11の導電層をエッチングして、前記第10の導電層

10

20

上に第12の導電層を形成し、

前記第3の導電層は、前記半導体層と接する領域において、第1の電極としての機能を有し、

前記第5の導電層は、前記半導体層と接する領域において、第2の電極としての機能を有し、

前記第3の導電層及び前記第7の導電層は、第1の配線としての機能を有し、

前記第10の導電層及び前記第12の導電層は、第2の配線としての機能を有し、

前記第10の導電層は、前記半導体層上において、第3の電極として機能する領域を有し、

前記第10の導電層は、前記第3の電極として機能する前記領域において、前記第12の導電層と重ならならず、10

前記第3のマスクを用いたエッチング工程において、前記絶縁層を介して前記第5の導電層と重なる領域を有する第13の導電層と、前記第13の導電層上の第14の導電層とを形成し、

前記第4のマスクを用いたエッチング工程において、前記14の導電層を除去し、

前記第13導電層と、前記第5の導電層の前記第13の導電層と重なる部分と、を含む容量が形成されることを特徴とする半導体装置の作製方法。

#### 【請求項2】

請求項1において、

前記半導体層は、In、Ga、及びZnを含む酸化物半導体を有することを特徴とする半導体装置の作製方法。20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

技術分野は、半導体装置、表示装置、発光装置、またはそれらの製造方法に関するものである。特に、酸化物半導体を用いた薄膜トランジスタ（以下、TFTという）を有する半導体装置に関する。

##### 【背景技術】

##### 【0002】

現在、液晶表示装置に代表される表示装置のスイッチング素子として、アモルファスシリコン等のシリコン層をチャネル層として用いた薄膜トランジスタ（TFT）が広く用いられている。アモルファスシリコンを用いた薄膜トランジスタは、電界効果移動度が低いもののガラス基板の大面積化に対応することができるという利点を有している。30

##### 【0003】

また、近年、半導体特性を示す金属酸化物を用いて薄膜トランジスタを作製し、電子デバイスや光デバイスに応用する技術が注目されている。例えば、金属酸化物の中で、酸化タンゲステン、酸化錫、酸化インジウム、酸化亜鉛などは半導体特性を示すことが知られている。このような金属酸化物で構成される透明半導体層をチャネル形成領域とする薄膜トランジスタが開示されている（例えば、特許文献1参照）。

##### 【0004】

また、トランジスタのチャネル層を、透光性を有する酸化物半導体層で形成すると共に、ゲート電極、ソース電極、ドレイン電極も透光性を有する透明導電膜で形成することによって、開口率を向上させる技術が検討されている（例えば、特許文献2参照）。

##### 【0005】

開口率を向上することにより、光利用効率が向上し、表示装置の省電力化及び小型化を達成することが可能となる。その一方で、表示装置の大型化や、携帯機器への応用化の観点からは、開口率の向上と共にさらなる消費電力の低減が求められている。

##### 【0006】

なお、電気光学素子の透明電極に対する金属補助配線の配線方法として、透明電極の上下どちらかで、透明電極と導通がとれるように金属補助配線と透明電極が重なるように配線50

されるものが知られている（例えば、特許文献3参照）。

#### 【0007】

なお、アクティブマトリクス基板に設けられる付加容量電極をITO、SnO<sub>2</sub>等の透明導電膜からなるものとし、付加容量用電極の電気抵抗を小さくするため、金属膜から成る補助配線を付加容量用電極に接して設ける構成が知られている（例えば、特許文献4参照）。

#### 【0008】

なお、非晶質酸化物半導体膜を用いた電界効果型トランジスタにおいて、ゲート電極、ソース電極及びドレイン電極の各電極を形成する材料は、インジウム錫酸化物（ITO）、インジウム亜鉛酸化物、ZnO、SnO<sub>2</sub>などの透明電極や、Al、Ag、Cr、Ni、Mo、Au、Ti、Taなどの金属電極、または、これらを含む合金の金属電極などを用いることができ、それらを2層以上積層して接触抵抗を低減し、または、界面強度を向上させてもよいことは知られている（例えば、特許文献5参照）。

#### 【0009】

なお、アモルファス酸化物半導体を用いるトランジスタのソース電極、ドレイン電極およびゲート電極、補助容量電極の材料として、インジウム（In）、アルミ（Al）、金（Au）、銀（Ag）等の金属や、酸化インジウム（In<sub>2</sub>O<sub>3</sub>）、酸化スズ（SnO<sub>2</sub>）、酸化亜鉛（ZnO）、酸化カドミウム（CdO）、酸化インジウムカドミウム（CdIn<sub>2</sub>O<sub>4</sub>）、酸化カドミウムスズ（Cd<sub>2</sub>SnO<sub>4</sub>）、酸化亜鉛スズ（Zn<sub>2</sub>SnO<sub>4</sub>）等の酸化物材料を用いることができ、ゲート電極、ソース電極及びドレイン電極の材料は、全て同じでもよく、異なっても良いことが知られている（例えば、特許文献6、7参照）。

#### 【先行技術文献】

##### 【特許文献】

##### 【0010】

【特許文献1】特開2004-103957号公報

【特許文献2】特開2007-81362号公報

【特許文献3】特開平2-82221号公報

【特許文献4】特開平2-310536号公報

【特許文献5】特開2008-243928号公報

【特許文献6】特開2007-109918号公報

【特許文献7】特開2007-115807号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0011】

そこで、本明細書等（少なくとも、明細書、特許請求の範囲、および図面を含む）において開示する発明の一態様は、開口率の高い半導体装置を提供することを課題とする。または、開示する発明の一態様は、消費電力の低い半導体装置を提供することを課題とする。または、開示する発明の一態様は、配線抵抗の低い半導体装置を提供することを課題とする。または、開示する発明の一態様は、信号波形のなまりを低減する半導体装置を提供することを課題とする。または、開示する発明の一態様は、導電率の高い配線を提供することを課題とする。または、開示する発明の一態様は、透過率の高い半導体装置を提供することを課題とする。または、開示する発明の一態様は、大画面化された半導体装置を提供することを課題とする。または、開示する発明の一態様は、プロセス工程数の増加を抑えた半導体装置を提供することを課題とする。または、開示する発明の一態様は、コントラストが向上した半導体装置を提供することを課題とする。または、開示する発明の一態様は、レイアウトの自由度が高い半導体装置を提供することを課題とする。または、開示する発明の一態様は、S値（sub threshold swing value）の小さい半導体装置を提供することを課題とする。なお、これらの課題は、他の課題の存在を妨げるものではない。また、開示する発明の一態様が、上記の課題の全てを解決する必要は

10

20

30

40

50

ないものとする。

【課題を解決するための手段】

【0012】

本明細書等において開示する発明の一態様では、トランジスタを、透光性を有する材料を用いて形成する。より詳細には、次の通りである。

【0013】

本明細書等において開示する発明の一態様は、絶縁面を有する基板と、基板上に設けられた透光性を有する第1の電極（ソース電極）と、基板上に設けられた透光性を有する第2の電極（ドレイン電極）と、第1の電極および第2の電極と電気的に接続するように設けられた透光性を有する半導体層（半導体層）と、第1の電極と電気的に接続された第1の配線（ソース配線）と、少なくとも半導体層を覆うように設けられた絶縁層（ゲート絶縁層）と、半導体層と重なる領域の絶縁層上に設けられた透光性を有する第3の電極（ゲート電極）と、第3の電極と電気的に接続された第2の配線（ゲート配線）と、を有することを特徴とする半導体装置である。10

【0014】

また、本明細書等において開示する発明の別の一態様は、絶縁面を有する基板上に、透光性を有する第1の導電層と、第2の導電層とを積層して形成し、第2の導電層上に第1のマスクを形成し、第1のマスクを用いて第1の導電層をエッチングして第1の電極および第2の電極を形成すると共に、第2の導電層をエッチングして第3の導電層を形成し、第1のマスクを後退させて、第2のマスクを形成し、第2のマスクを用いて第3の導電層をエッチングして第1の配線を形成し、第1の電極および第2の電極と電気的に接続する透光性を有する半導体層を形成し、半導体層を覆うように絶縁層を形成し、絶縁層上に、透光性を有する第4の導電層と、第5の導電層とを積層して形成し、第5の導電層上に第3のマスクを形成し、第3のマスクを用いて第4の導電層をエッチングして第3の電極を形成すると共に、第5の導電層をエッチングして第6の導電層を形成し、第3のマスクを後退させて、第4のマスクを形成し、第4のマスクを用いて第6の導電層をエッチングして第2の配線を形成することを特徴とする半導体装置の作製方法である。20

【0015】

なお、上記において、第2の電極と電気的に接続された透光性を有する第4の電極（画素電極）を設けても良い。また、絶縁層を介して第2の電極の一部と重なる領域に設けられ、かつ第3の電極と同一層でなる第5の電極（容量電極）と、第5の電極と電気的に接続され、かつ第2の配線と同一層でなる第3の配線（容量配線）と、を設けても良い。30

【0016】

また、上記において、半導体層は、インジウム、ガリウムおよび亜鉛を含む酸化物半導体からなることが好ましい。また、第1の電極、第2の電極、および第3の電極は、インジウム錫酸化物、酸化珪素を含むインジウム錫酸化物、有機インジウム、有機スズ、酸化亜鉛、窒化チタン、酸化亜鉛を含むインジウム亜鉛酸化物、酸化亜鉛にガリウムを添加した材料、酸化スズ、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、のいずれかからなることが好ましい。40

【0017】

また、上記において、第1の配線および第2の配線は、遮光性を有することが好ましい。また、第1の配線と第2の配線との交差部分に、半導体層と同一層でなる層を設けることが好ましい。これにより、配線が交差することに起因して生じる容量を低減することができるため、信号波形のなまりを抑制することができる。特に、大型の半導体装置ではその効果が著しい。

【0018】

本明細書等において開示する発明に用いることができる酸化物半導体の一例としては、 $In_2MO_3 (ZnO)_m$  ( $m > 0$ ) で表記されるものがある。ここで、Mは、ガリウム (Ga)、鉄 (Fe)、ニッケル (Ni)、マンガン (Mn) 及びコバルト (Co) から選ば50

れた一の金属元素または複数の金属元素を示す。例えば、MとしてGaが選択される場合には、Gaのみの場合の他に、GaとNiや、GaとFeなど、Ga以外の上記金属元素が選択される場合を含む。また、上記酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、または該遷移金属の酸化物が含まれているものがある。本明細書等においては、上記酸化物半導体のうち、Mとして少なくともガリウムを含むものをIn-Ga-Zn-O系酸化物半導体と呼び、当該材料を用いた薄膜をIn-Ga-Zn-O系非単結晶膜と呼ぶことがある。

#### 【0019】

さらに、上記において、多階調マスクを用いることにより、1枚のマスク（レチクル）で、透光性を有する領域（透過率の高い領域）と、透光性を有しない領域（透過率の低い領域）とを形成することができる。これにより、マスク数の増加を抑制できる。10

#### 【0020】

なお、本明細書等において、半導体装置とは、半導体特性を利用することで機能し得る装置全般を指し、半導体回路、表示装置、電気光学装置、発光表示装置、電子機器などは全て半導体装置に含まれる。

#### 【0021】

また、本明細書等において表示装置とは、画像表示デバイス、発光デバイス、または光源（照明装置含む）を指す。ここで、コネクター、例えば、FPC（Flexible printed circuit）やTAB（Tape Automated Bonding）テープ、TCP（Tape Carrier Package）などが取り付けられたモジュール、TABテープやTCPの先にプリント配線基板が設けられたモジュール、表示素子にCOG（Chip On Glass）方式によりIC（集積回路）が直接実装されたモジュールなどは全て表示装置に含まれる。20

#### 【0022】

なお、スイッチは、様々な形態のものを用いることができる。例としては、電気的スイッチや機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、特定のものに限定されない。例えば、スイッチとして、トランジスタ（例えば、バイポーラトランジスタ、MOSトランジスタなど）、ダイオード（例えば、PNダイオード、PINダイオード、ショットキーダイオード、MIM（Metal Insulator Metal）ダイオード、MIS（Metal Insulator Semiconductor）ダイオード、ダイオード接続のトランジスタなど）などを用いることが出来る。または、これらを組み合わせた論理回路をスイッチとして用いることが出来る。30

#### 【0023】

機械的なスイッチの例としては、デジタルマイクロミラーデバイス（DMD）のように、MEMS（マイクロ・エレクトロ・メカニカル・システム）技術を用いたスイッチがある。そのスイッチは、機械的に動かすことが出来る電極を有し、その電極が動くことによって、導通と非導通とを制御して動作する。

#### 【0024】

スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性（導電型）は特に限定されない。ただし、オフ電流を抑えたい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LDD領域を有するトランジスタやマルチゲート構造を有するトランジスタ等がある。または、スイッチとして動作させるトランジスタのソース端子の電位が、低電位側電源（Vss、GND、0Vなど）の電位に近い値で動作する場合はNチャネル型トランジスタを用いることが望ましい。反対に、ソース端子の電位が、高電位側電源（Vddなど）の電位に近い値で動作する場合はPチャネル型トランジスタを用いることが望ましい。なぜなら、Nチャネル型トランジスタではソース端子が低電位側電源の電位に近い値で動作するとき、Pチャネル型トランジスタではソース端子が高電位側電源の電位に近い値で動作するとき、ゲートとソースの間の電圧の絶対値を大きくできるため、スイッチとして、より正確な動作を行うことができるからである。さらに4050

、トランジスタがソースフォロワ動作をしてしまうことが少ないため、出力電圧の大きさが小さくなってしまうことが少ないからである。

#### 【0025】

なお、Nチャネル型トランジスタとPチャネル型トランジスタの両方を用いて、CMOS型のスイッチをスイッチとして用いてもよい。CMOS型のスイッチにすると、Pチャネル型トランジスタまたはNチャネル型トランジスタのどちらか一方のトランジスタが導通すれば電流が流れるため、スイッチとして機能しやすくなる。例えば、スイッチへの入力信号の電圧が高い場合でも、低い場合でも、適切に電圧を出力させることが出来る。さらに、スイッチをオンまたはオフさせるための信号の電圧振幅値を小さくすることが出来るので、消費電力を小さくすることも出来る。

10

#### 【0026】

なお、スイッチとしてトランジスタを用いる場合、スイッチは、入力端子（ソース端子またはドレイン端子の一方）と、出力端子（ソース端子またはドレイン端子の他方）と、導通を制御する端子（ゲート端子）とを有している。一方、スイッチとしてダイオードを用いる場合、スイッチは、導通を制御する端子を有していない場合がある。そのため、トランジスタよりもダイオードをスイッチとして用いた方が、端子を制御するための配線を少なくすることが出来る。

#### 【0027】

なお、AとBとが接続されている、と明示的に記載する場合は、AとBとが電気的に接続されている場合と、AとBとが機能的に接続されている場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。

20

#### 【0028】

例えば、AとBとが電気的に接続されている場合として、AとBとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオードなど）が、AとBとの間に1個以上接続されていてもよい。あるいは、AとBとが機能的に接続されている場合として、AとBとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（DA変換回路、AD変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフト回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動增幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、AとBとの間に1個以上接続されていてもよい。例えば、AとBとの間に別の回路を挟んでいても、Aから出力された信号がBへ伝達される場合は、AとBとは機能的に接続されているものとする。

30

#### 【0029】

なお、AとBとが電気的に接続されている、と明示的に記載する場合は、AとBとが電気的に接続されている場合（つまり、AとBとの間に別の素子や別の回路を挟んで接続されている場合）と、AとBとが機能的に接続されている場合（つまり、AとBとの間に別の回路を挟んで機能的に接続されている場合）と、AとBとが直接接続されている場合（つまり、AとBとの間に別の素子や別の回路を挟まずに接続されている場合）とを含むものとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続されている、とのみ明示的に記載されている場合と同じであるとする。

40

#### 【0030】

なお、表示素子、表示素子を有する装置である表示装置、発光素子、発光素子を有する装置である発光装置は、様々な形態を用い、また、様々な素子を有することが出来る。例えば、表示素子、表示装置、発光素子または発光装置としては、EL（エレクトロルミネッセンス）素子（有機物及び無機物を含むEL素子、有機EL素子、無機EL素子）、LE

50

D（白色LED、赤色LED、緑色LED、青色LEDなど）、トランジスタ（電流に応じて発光するトランジスタ）、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ（GLV）、プラズマディスプレイパネル（PDP）、デジタルマイクロミラーデバイス（DMD）、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有することができる。なお、EL素子を用いた表示装置としてはELディスプレイなど、電子放出素子を用いた表示装置としてはフィールドエミッショニスプレイ（FED）やSED方式平面型ディスプレイ（SED：Surface-conduction Electron-emitter Display）など、液晶素子を用いた表示装置としては液晶ディスプレイ（透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ）など、電子インクや電気泳動素子を用いた表示装置としては電子ペーパーなどがある。

10

### 【0031】

なお、EL素子とは、陽極と、陰極と、陽極と陰極との間に挟まれたEL層とを有する素子である。なお、EL層としては、1重項励起子からの発光（蛍光）を利用するもの、3重項励起子からの発光（燐光）を利用するもの、1重項励起子からの発光（蛍光）を利用するものと3重項励起子からの発光（燐光）を利用するものとを含むもの、有機物によって形成されたもの、無機物によって形成されたもの、有機物によって形成されたものと無機物によって形成されたものとを含むもの、高分子の材料、低分子の材料、高分子の材料と低分子の材料とを含むものなどを有することができる。ただし、これに限定されず、EL素子として様々なものを有することができる。

20

### 【0032】

なお、電子放出素子とは、陰極に高電界を集中して電子を引き出す素子である。例えば、電子放出素子として、スピント型、カーボンナノチューブ（CNT）型、金属 絶縁体 金属を積層したMIM（Metal-Insulator-Metal）型、金属 絶縁体 半導体を積層したMIS（Metal-Insulator-Semiconductor）型、MOS型、シリコン型、薄膜ダイオード型、ダイヤモンド型、表面伝導エミッタSCD型、金属 絶縁体 半導体 - 金属型等の薄膜型、HEED型、EL型、ポーラスシリコン型、表面伝導（SCE）型などを有することができる。ただし、これに限定されず、電子放出素子として様々なものを有することができる。

30

### 【0033】

なお、液晶素子とは、液晶の光学的変調作用によって光の透過または非透過を制御する素子であり、一対の電極、及び液晶により構成される。なお、液晶の光学的変調作用は、液晶にかかる電界（横方向の電界、縦方向の電界又は斜め方向の電界を含む）によって制御される。なお、液晶素子としては、ネマチック液晶、コレステリック液晶、スマートチック液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶（PDLC）、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高分子液晶、プラズマアドレス液晶（PALC）、バナナ型液晶などを挙げることができる。また、液晶の駆動方式としては、TN（Twisted Nematic）モード、STN（Super Twisted Nematic）モード、IPS（In-Plane-Switching）モード、FFS（Fringe Field Switching）モード、MVA（Multi-domain Vertical Alignment）モード、PVA（Patterned Vertical Alignment）モード、ASV（Advanced Super View）モード、ASM（Axially Symmetric aligned Micro-cell）モード、OCB（Optically Compensated Birefringence）モード、ECB（Electrically Controlled Birefringence）モード、FLC（Ferroelectric Liquid Crystal）モード、AFLC（AntiFerroelectric Liquid Crystal）モード、PDLC（Polymer Dispersed Liquid

40

50

C r y s t a l ) モード、ゲストホストモード、ブルー相 ( B l u e P h a s e ) モードなどを用いることができる。ただし、これに限定されず、液晶素子及びその駆動方法として様々なものを用いることができる。

#### 【 0 0 3 4 】

なお、電子ペーパーの表示方法としては、分子により表示されるもの（光学異方性、染料分子配向など）、粒子により表示されるもの（電気泳動、粒子移動、粒子回転、相変化など）、フィルムの一端が移動することにより表示されるもの、分子の発色／相変化により表示されるもの、分子の光吸収により表示されるもの、電子とホールが結合して自発光により表示されるものなどをいう。例えば、電子ペーパーとして、マイクロカプセル型電気泳動、水平移動型電気泳動、垂直移動型電気泳動、球状ツイストボール、磁気ツイストボール、円柱ツイストボール方式、帯電トナー、電子粉流体、磁気泳動型、磁気感熱式、エレクトロウェッティング、光散乱（透明／白濁変化）、コレステリック液晶／光導電層、コレステリック液晶、双安定性ネマチック液晶、強誘電性液晶、2色性色素・液晶分散型、可動フィルム、ロイコ染料による発消色、フォトクロミック、エレクトロクロミック、エレクトロデポジション、フレキシブル有機 E Lなどを用いることができる。ただし、これに限定されず、電子ペーパー及びその表示方法として様々なものを用いることができる。ここで、マイクロカプセル型電気泳動を用いることによって、電気泳動方式の欠点である泳動粒子の凝集、沈殿を解決することができる。電子粉流体は、高速応答性、高反射率、広視野角、低消費電力、メモリ性などのメリットを有する。

#### 【 0 0 3 5 】

なお、プラズマディスプレイパネルは、電極を表面に形成した基板と、電極及び微小な溝を表面に形成し且つ溝内に蛍光体層を形成した基板とを狭い間隔で対向させて、希ガスを封入した構造を有する。あるいは、プラズマディスプレイパネルは、プラズマチューブを上下からフィルム状の電極で挟み込んだ構造とすることも可能である。プラズマチューブとは、ガラスチューブ内に、放電ガス、 R G B それぞれの蛍光体などを封止したものである。なお、電極間に電圧をかけることによって紫外線を発生させ、蛍光体を光らせることで、表示を行うことができる。なお、プラズマディスプレイパネルとしては、 D C 型 P D P 、 A C 型 P D P でもよい。ここで、プラズマディスプレイパネルの駆動方法としては、 A W S ( A d d r e s s W h i l e S u s t a i n ) 駆動、サブフレームをリセット期間、アドレス期間、維持期間に分割する A D S ( A d d r e s s D i s p l a y S e p a r a t e d ) 駆動、 C L E A R ( H I C O N T R A S T & L O W E N E R G Y A D D R E S S & R E D U C T I O N O F F A L S E C O N T O U R S E Q U E N C E ) 駆動、 A L I S ( A l t e r n a t e L i g h t i n g o f S u r f a c e s ) 方式、 T E R E S ( T e c h n o l o g y o f R e c i p r o c a l S u s t a i n e r ) 駆動などを用いることができる。ただし、これに限定されず、プラズマディスプレイパネルの駆動方法として様々なものを用いることができる。

#### 【 0 0 3 6 】

なお、光源を必要とする表示装置、例えば、液晶ディスプレイ（透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ）、グレーティングライトバルブ ( G L V ) を用いた表示装置、デジタルマイクロミラーデバイス ( D M D ) を用いた表示装置などの光源としては、エレクトロルミネッセンス、冷陰極管、熱陰極管、 L E D 、レーザー光源、水銀ランプなどを用いることができる。ただし、これに限定されず、光源として様々なものを用いることができる。

#### 【 0 0 3 7 】

なお、トランジスタとして、様々な形態のトランジスタを用いることが出来る。よって、用いるトランジスタの種類に限定はない。例えば、非晶質シリコン、多結晶シリコン、微結晶（マイクロクリスタル、ナノクリスタル、セミアモルファスとも言う）シリコンなどに代表される非単結晶半導体膜を有する薄膜トランジスタ ( T F T ) などを用いることが出来る。 T F T を用いる場合、様々なメリットがある。例えば、単結晶シリコンの場合よ

10

20

30

40

50

りも低い温度で製造できるため、製造コストの削減、又は製造装置の大型化を図ることができる。製造装置を大きくできるため、大型基板上に製造できる。これにより、同時に複数の表示装置を製造できるため、製造コストを抑制できる。さらに、製造温度が低いため、耐熱性の低い基板を用いることができる。これにより、ガラス基板などの透光性を有する基板上にトランジスタを製造できる。そして、透光性を有する基板上のトランジスタを用いて表示素子での光の透過を制御することが出来る。あるいは、トランジスタの膜厚が小さいため、トランジスタを構成する膜の一部は、光を透過させることができる。そのため、開口率が向上させることができる。

#### 【0038】

なお、多結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。その結果、ゲートドライバ回路（走査線駆動回路）やソースドライバ回路（信号線駆動回路）、信号処理回路（信号生成回路、ガンマ補正回路、D/A変換回路など）を基板上に一体形成することが出来る。10

#### 【0039】

なお、微結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。このとき、レーザー照射を行うことなく、熱を加えるだけで、結晶性を向上させることも可能である。その結果、ソースドライバ回路の一部（アナログスイッチなど）およびゲートドライバ回路（走査線駆動回路）を基板上に一体形成することが出来る。さらに、結晶化のためにレーザー照射を行わない場合は、シリコンの結晶性のムラを抑えることができる。そのため、質の高い表示が可能である。20

#### 【0040】

ただし、触媒（ニッケルなど）を用いずに、多結晶シリコンや微結晶シリコンを製造することは可能である。

#### 【0041】

なお、シリコンの結晶性を、多結晶または微結晶などへと向上させることは、パネル全体で行なうことが望ましいが、それに限定されない。パネルの一部の領域のみにおいて、シリコンの結晶性を向上させててもよい。選択的に結晶性を向上させることは、レーザー光を選択的に照射することなどにより可能である。例えば、画素以外の領域である周辺回路領域にのみ、レーザー光を照射してもよい。または、ゲートドライバ回路、ソースドライバ回路等の領域にのみ、レーザー光を照射してもよい。あるいは、ソースドライバ回路の一部（例えば、アナログスイッチ）の領域にのみ、レーザー光を照射してもよい。その結果、回路を高速に動作させる必要がある領域にのみ、シリコンの結晶性を向上させることができる。画素領域は、高速に動作させる必要性が低いため、結晶性が向上されなくても、問題なく画素回路を動作させることができる。結晶性を向上させる領域が少なくて済むため、製造工程も短くすることが出来、スループットが向上し、製造コストを低減させることが出来る。必要とされる製造装置の数も少なくて済むため、製造コストを低減させる（増大させない）ことが出来る。30

#### 【0042】

または、半導体基板やSOI基板などを用いてトランジスタを形成することが出来る。これらにより、特性やサイズや形状などのバラツキが少なく、電流供給能力が高く、サイズの小さいトランジスタを製造することができる。これらのトランジスタを用いると、回路の低消費電力化、又は回路の高集積化を図ることができる。

#### 【0043】

または、ZnO、a-InGaZnO、IZO、ITO、SnO、TiO、AlZnSnO (AZTO) などの化合物半導体または酸化物半導体を有するトランジスタや、さらに、これらの化合物半導体または酸化物半導体を薄膜化した薄膜トランジスタなどを用いることが出来る。これらにより、製造温度を低くでき、例えば、室温でトランジスタを製造することが可能となる。その結果、耐熱性の低い基板、例えばプラスチック基板やフィル4050

ム基板に直接トランジスタを形成することが出来る。なお、これらの化合物半導体または酸化物半導体を、トランジスタのチャネル部分に用いるだけでなく、それ以外の用途で用いることも出来る。例えば、これらの化合物半導体または酸化物半導体を抵抗素子、画素電極、透光性を有する電極として用いることができる。さらに、それらをトランジスタと同時に成膜又は形成できるため、コストを低減できる。また、SiGe、GaAs、などの半導体を用いても良い。

#### 【0044】

または、インクジェットや印刷法を用いて形成したトランジスタなどを用いることが出来る。これらにより、室温で製造、低真空中で製造、又は大型基板上に製造することができる。マスク（レチクル）を用いなくても製造することが可能となるため、トランジスタのレイアウトを容易に変更することが出来る。さらに、レジストを用いる必要がないので、材料費が安くなり、工程数を削減できる。さらに、必要な部分にのみ膜を付けるため、全面に成膜した後でエッティングする、という製法よりも、材料が無駄にならず、低コストにできる。

10

#### 【0045】

または、有機半導体やカーボンナノチューブを有するトランジスタ等を用いることができる。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。このような基板を用いた半導体装置は、衝撃に強くすることができる。

#### 【0046】

さらに、様々な構造のトランジスタを用いることができる。例えば、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどをトランジスタとして用いることが出来る。MOS型トランジスタを用いることにより、トランジスタのサイズを小さくすることが出来る。よって、多数のトランジスタを搭載することができる。バイポーラトランジスタを用いることにより、大きな電流を流すことが出来る。よって、高速に回路を動作させることができる。

20

#### 【0047】

なお、MOS型トランジスタ、バイポーラトランジスタなどを1つの基板に混在させて形成してもよい。これにより、低消費電力、小型化、高速動作などを実現することができる。

#### 【0048】

30

その他、様々なトランジスタを用いることができる。

#### 【0049】

なお、トランジスタは、様々な基板を用いて形成することが出来る。基板の種類は、特定のものに限定されることはない。その基板としては、例えば、単結晶基板（例えばシリコン基板）、SOI基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タンゲステン基板、タンゲステン・ホイルを有する基板、可撓性基板などを用いることが出来る。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニオホウケイ酸ガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート（PET）、ポリエチレンナフタレート（PEN）、ポリエーテルサルファン（PES）に代表されるプラスチック、又はアクリル等の可撓性を有する合成樹脂などがある。他にも、貼り合わせフィルム（ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなど）、纖維状の材料を含む紙、基材フィルム（ポリエチレン、ポリアミド、ポリイミド、無機蒸着フィルム、紙類等）などがある。または、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板としては、単結晶基板、SOI基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、木材基板、布基板（天然纖維（絹、綿、麻）、合成纖維（ナイロン、ポリウレタン、ポリエステル）若しくは再生纖維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、ゴム基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板などを用いることができる。あ

40

50

るいは、人などの動物の皮膚（表皮、真皮）又は皮下組織を基板として用いてもよい。または、ある基板を用いてトランジスタを形成し、その基板を研磨して薄くしてもよい。研磨される基板としては、単結晶基板、S O I 基板、ガラス基板、石英基板、プラスチック基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板などを用いることができる。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。

#### 【 0 0 5 0 】

なお、トランジスタの構成は、様々な形態をとることができ、特定の構成に限定されない。例えば、ゲート電極が2個以上のマルチゲート構造を適用することができる。マルチゲート構造にすると、チャネル領域が直列に接続されるため、複数のトランジスタが直列に接続された構成となる。マルチゲート構造により、オフ電流の低減、トランジスタの耐圧向上（信頼性の向上）を図ることができる。あるいは、マルチゲート構造により、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、電圧・電流特性の傾きをフラットにすることができる。電圧・電流特性の傾きがフラットである特性を利用すると、理想的な電流源回路や、非常に高い抵抗値をもつ能動負荷を実現することが出来る。その結果、特性のよい差動回路やカレントミラー回路を実現することが出来る。

10

#### 【 0 0 5 1 】

別の例として、チャネルの上下にゲート電極が配置されている構造を適用することができる。チャネルの上下にゲート電極が配置されている構造により、チャネル領域が増えるため、電流値の増加を図ることができる。または、チャネルの上下にゲート電極が配置されている構造により、空乏層ができやすくなるため、S 値の改善を図ることができる。なお、チャネルの上下にゲート電極が配置される構成により、複数のトランジスタが並列に接続されたような構成となる。

20

#### 【 0 0 5 2 】

チャネル領域の上にゲート電極が配置されている構造、チャネル領域の下にゲート電極が配置されている構造、正スタガ構造、逆スタガ構造、チャネル領域を複数の領域に分けた構造、チャネル領域を並列に接続した構造、またはチャネル領域が直列に接続する構成も適用できる。さらに、チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なっている構造も適用できる。チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なる構造によつて、チャネル領域の一部に電荷が溜まることにより動作が不安定になることを防ぐことができる。あるいは、L D D 領域を設けた構造を適用できる。L D D 領域を設けることにより、オフ電流の低減、又はトランジスタの耐圧向上（信頼性の向上）を図ることができる。あるいは、L D D 領域を設けることにより、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、電圧・電流特性の傾きがフラットな特性にすることができる。

30

#### 【 0 0 5 3 】

なお、トランジスタは、様々なタイプを用いることができ、様々な基板を用いて形成させることができる。したがつて、所定の機能を実現させるために必要な回路の全てを、同一の基板に形成することも可能である。例えば、所定の機能を実現させるために必要な回路の全てを、ガラス基板、プラスチック基板、単結晶基板、またはS O I 基板などの様々な基板を用いて形成することも可能である。所定の機能を実現させるために必要な回路の全てが同じ基板を用いて形成されることにより、部品点数の削減によるコストの低減、又は回路部品との接続点数の低減による信頼性の向上を図ることができる。あるいは、所定の機能を実現させるために必要な回路の一部が、ある基板に形成され、所定の機能を実現させるために必要な回路の別の一部が、別の基板に形成されていることも可能である。つまり、所定の機能を実現させるために必要な回路の全てが同じ基板を用いて形成されていなくてよい。例えば、所定の機能を実現させるために必要な回路の一部は、ガラス基板上にトランジスタにより形成され、所定の機能を実現させるために必要な回路の別の一

40

50

部は、単結晶基板に形成され、単結晶基板を用いて形成されたトランジスタで構成された I C チップを COG ( C h i p O n G l a s s ) でガラス基板に接続して、ガラス基板上にその I C チップを配置することも可能である。あるいは、その I C チップを T A B ( T a p e A u t o m a t e d B o n d i n g ) やプリント基板を用いてガラス基板と接続することも可能である。このように、回路の一部が同じ基板に形成されていることにより、部品点数の削減によるコストの低減、又は回路部品との接続点数の低減による信頼性の向上を図ることができる。あるいは、駆動電圧が高い部分及び駆動周波数が高い部分の回路は、消費電力が大きくなってしまうので、そのような部分の回路は同じ基板に形成せず、そのかわりに、例えば、単結晶基板にその部分の回路を形成して、その回路で構成された I C チップを用いるようにすれば、消費電力の増加を防ぐことができる。

10

#### 【 0 0 5 4 】

なお、一画素とは、明るさを制御できる要素一つ分を示すものとする。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。従って、そのときは、R ( 赤 ) G ( 緑 ) B ( 青 ) の色要素からなるカラー表示装置の場合には、画像の最小単位は、R の画素と G の画素と B の画素との三画素から構成されるものとする。なお、色要素は、三色に限定されず、三色以上を用いても良いし、RGB 以外の色を用いても良い。例えば、白色を加えて、RGBW ( W は白 ) としても可能である。あるいは、RGB に、例えば、イエロー、シアン、マゼンタ、エメラルドグリーン、朱色などを一色以上追加することも可能である。あるいは、例えば、RGB の中の少なくとも一色に類似した色を、RGB に追加することも可能である。例えば、R、G、B1、B2 としてもよい。B1 と B2 とは、どちらも青色であるが、少し波長が異なっている。同様に、R1、R2、G、B とすることも可能である。このような色要素を用いることにより、より実物に近い表示を行うことができる。このような色要素を用いることにより、消費電力を低減することが出来る。別の例としては、一つの色要素について、複数の領域を用いて明るさを制御する場合は、その領域一つ分を一画素とすることも可能である。よって、一例として、面積階調を行う場合または副画素 ( サブ画素 ) を有している場合、一つの色要素につき、明るさを制御する領域が複数あり、その全体で階調を表現するが、明るさを制御する領域の一つ分を一画素とすることも可能である。よって、その場合は、一つの色要素は、複数の画素で構成されることとなる。あるいは、明るさを制御する領域が一つの色要素の中に複数あっても、それらをまとめて、一つの色要素を 1 画素としてもよい。よって、その場合は、一つの色要素は、一つの画素で構成されることとなる。あるいは、一つの色要素について、複数の領域を用いて明るさを制御する場合、画素によって、表示に寄与する領域の大きさが異なっている場合がある。あるいは、一つの色要素につき複数ある、明るさを制御する領域において、各々に供給する信号を僅かに異ならせるようにして、視野角を広げるようにしてよい。つまり、一つの色要素について、複数個ある領域が各々有する画素電極の電位が、各々異なっていることも可能である。その結果、液晶分子に加わる電圧が各画素電極によって各々異なる。よって、視野角を広くすることが出来る。

20

#### 【 0 0 5 5 】

なお、一画素 ( 三色分 ) と明示的に記載する場合は、R と G と B の三画素分を一画素と考える場合であるとする。一画素 ( 一色分 ) と明示的に記載する場合は、一つの色要素につき、複数の領域がある場合、それらをまとめて一画素と考える場合であるとする。

30

#### 【 0 0 5 6 】

なお、画素は、マトリクス状に配置 ( 配列 ) されている場合がある。ここで、画素がマトリクスに配置 ( 配列 ) されているとは、縦方向もしくは横方向において、画素が直線上に並んで配置されている場合、又はギザギザな線上に配置されている場合を含む。よって、例えば三色の色要素 ( 例えば RGB ) でフルカラー表示を行う場合に、ストライプ配置されている場合、又は三つの色要素のドットがデルタ配置されている場合も含む。さらに、ペイヤー配置されている場合も含む。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。これにより、低消費電力化、又は表示素子の長寿命化を図ることが

40

50

できる。

【0057】

なお、画素に能動素子を有するアクティブマトリクス方式、または、画素に能動素子を有しないパッシブマトリクス方式を用いることが出来る。

【0058】

アクティブマトリクス方式では、能動素子（アクティブ素子、非線形素子）として、トランジスタだけでなく、さまざまな能動素子（アクティブ素子、非線形素子）を用いることが出来る。例えば、MIM（Metal Insulator Metal）やTFD（Thin Film Diode）などを用いることも可能である。これらの素子は、製造工程が少ないため、製造コストの低減、又は歩留まりの向上を図ることが出来る。さらに、素子のサイズが小さいため、開口率を向上させることができ、低消費電力化や高輝度化をはかることが出来る。10

【0059】

なお、アクティブマトリクス方式以外のものとして、能動素子（アクティブ素子、非線形素子）を用いないパッシブマトリクス型を用いることも可能である。能動素子（アクティブ素子、非線形素子）を用いないため、製造工程が少なく、製造コストの低減、又は歩留まりの向上を図ることができる。能動素子（アクティブ素子、非線形素子）を用いないため、開口率を向上させることができ、低消費電力化や高輝度化をはかることが出来る。

【0060】

なお、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第1端子、第2端子と表記する場合がある。あるいは、それぞれを第1電極、第2電極と表記する場合がある。あるいは、第1領域、第2領域と表記する場合がある。20

【0061】

なお、トランジスタは、ベースとエミッタとコレクタとを含む少なくとも三つの端子を有する素子であってもよい。この場合も同様に、エミッタとコレクタとを、第1端子、第2端子などと表記する場合がある。30

【0062】

なお、ゲートとは、ゲート電極とゲート配線（ゲート線、ゲート信号線、走査線、走査信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ゲート電極とは、チャネル領域を形成する半導体と、ゲート絶縁膜を介してオーバーラップしている部分の導電膜のことを言う。なお、ゲート電極の一部は、LDD（Lightly Doped Drain）領域またはソース領域（またはドレイン領域）と、ゲート絶縁膜を介してオーバーラップしている場合もある。ゲート配線とは、各トランジスタのゲート電極の間を接続するための配線、各画素の有するゲート電極の間を接続するための配線、又はゲート電極と別の配線とを接続するための配線のことを言う。40

【0063】

ただし、ゲート電極としても機能し、ゲート配線としても機能するような部分（領域、導電膜、配線など）も存在する。そのような部分（領域、導電膜、配線など）は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。つまり、ゲート電極とゲート配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているゲート配線の一部とチャネル領域がオーバーラップしている場合、その部分（領域、導電膜、配線など）はゲート配線として機能しているが、ゲート電極としても機能していることになる。よって、そのような部分（領域、導電膜、配線など）は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。50

## 【0064】

なお、ゲート電極と同じ材料で形成され、ゲート電極と同じ島（アイランド）を形成してつながっている部分（領域、導電膜、配線など）も、ゲート電極と呼んでも良い。同様に、ゲート配線と同じ材料で形成され、ゲート配線と同じ島（アイランド）を形成してつながっている部分（領域、導電膜、配線など）も、ゲート配線と呼んでも良い。このような部分（領域、導電膜、配線など）は、厳密な意味では、チャネル領域とオーバーラップしていない場合、又は別のゲート電極と接続させる機能を有していない場合がある。しかし、製造時の仕様などの関係で、ゲート電極またはゲート配線と同じ材料で形成され、ゲート電極またはゲート配線と同じ島（アイランド）を形成してつながっている部分（領域、導電膜、配線など）がある。よって、そのような部分（領域、導電膜、配線など）もゲート電極またはゲート配線と呼んでも良い。10

## 【0065】

なお、例えば、マルチゲートのトランジスタにおいて、1つのゲート電極と、別のゲート電極とは、ゲート電極と同じ材料で形成された導電膜で接続される場合が多い。そのような部分（領域、導電膜、配線など）は、ゲート電極とゲート電極とを接続させるための部分（領域、導電膜、配線など）であるため、ゲート配線と呼んでも良いが、マルチゲートのトランジスタを1つのトランジスタと見なすことも出来るため、ゲート電極と呼んでも良い。つまり、ゲート電極またはゲート配線と同じ材料で形成され、ゲート電極またはゲート配線と同じ島（アイランド）を形成してつながっている部分（領域、導電膜、配線など）は、ゲート電極やゲート配線と呼んでも良い。さらに、例えば、ゲート電極とゲート配線とを接続させている部分の導電膜であって、ゲート電極またはゲート配線とは異なる材料で形成された導電膜も、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。20

## 【0066】

なお、ゲート端子とは、ゲート電極の部分（領域、導電膜、配線など）または、ゲート電極と電気的に接続されている部分（領域、導電膜、配線など）について、その一部分のことを言う。

## 【0067】

なお、ある配線を、ゲート配線、ゲート線、ゲート信号線、走査線、走査信号線などと呼ぶ場合、その配線にトランジスタのゲートが接続されていない場合もある。この場合、ゲート配線、ゲート線、ゲート信号線、走査線、走査信号線は、トランジスタのゲートと同じ層で形成された配線、トランジスタのゲートと同じ材料で形成された配線またはトランジスタのゲートと一緒に成膜された配線を意味している場合がある。例としては、保持容量用配線、電源線、基準電位供給配線などがある。30

## 【0068】

なお、ソースとは、ソース領域とソース電極とソース配線（ソース線、ソース信号線、データ線、データ信号線等とも言う）とを含んだ全体、もしくは、それらの一部のことを言う。ソース領域とは、P型不純物（ボロンやガリウムなど）やN型不純物（リンやヒ素など）が多く含まれる半導体領域のことを言う。従って、少しだけP型不純物やN型不純物が含まれる領域、いわゆる、LDD（Lightly Doped Drain）領域は、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソース領域と電気的に接続されて配置されている部分の導電層のことを言う。ただし、ソース電極は、ソース領域も含んでソース電極と呼ぶこともある。ソース配線とは、各トランジスタのソース電極の間を接続するための配線、各画素の有するソース電極の間を接続するための配線、又はソース電極と別の配線とを接続するための配線のことを言う。40

## 【0069】

しかしながら、ソース電極としても機能し、ソース配線としても機能するような部分（領域、導電膜、配線など）も存在する。そのような部分（領域、導電膜、配線など）は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。つまり、ソース電極とソース配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているソース配線の一部とソース領域とがオーバーラップしている場合、その部分（領域、導電膜50

、配線など)はソース配線として機能しているが、ソース電極としても機能することになる。よって、そのような部分(領域、導電膜、配線など)は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

#### 【0070】

なお、ソース電極と同じ材料で形成され、ソース電極と同じ島(アイランド)を形成してつながっている部分(領域、導電膜、配線など)や、ソース電極とソース電極とを接続する部分(領域、導電膜、配線など)も、ソース電極と呼んでも良い。さらに、ソース領域とオーバーラップしている部分も、ソース電極と呼んでも良い。同様に、ソース配線と同じ材料で形成され、ソース配線と同じ島(アイランド)を形成してつながっている領域も、ソース配線と呼んでも良い。このような部分(領域、導電膜、配線など)は、厳密な意味では、別のソース電極と接続させる機能を有していない場合がある。しかし、製造時の仕様などの関係で、ソース電極またはソース配線と同じ材料で形成され、ソース電極またはソース配線とつながっている部分(領域、導電膜、配線など)がある。よって、そのような部分(領域、導電膜、配線など)もソース電極またはソース配線と呼んでも良い。10

#### 【0071】

なお、例えば、ソース電極とソース配線とを接続させている部分の導電膜であって、ソース電極またはソース配線とは異なる材料で形成された導電膜も、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

#### 【0072】

なお、ソース端子とは、ソース領域や、ソース電極や、ソース電極と電気的に接続されている部分(領域、導電膜、配線など)について、その一部分のことを言う。20

#### 【0073】

なお、ある配線を、ソース配線、ソース線、ソース信号線、データ線、データ信号線などと呼ぶ場合、その配線にトランジスタのソース(ドレイン)が接続されていない場合もある。この場合、ソース配線、ソース線、ソース信号線、データ線、データ信号線は、トランジスタのソース(ドレイン)と同じ層で形成された配線、トランジスタのソース(ドレイン)と同じ材料で形成された配線またはトランジスタのソース(ドレイン)と一緒に成膜された配線を意味している場合がある。例としては、保持容量用配線、電源線、基準電位供給配線などがある。

#### 【0074】

なお、ドレインについては、ソースと同様である。30

#### 【0075】

なお、半導体装置とは半導体素子(トランジスタ、ダイオード、サイリスタなど)を含む回路を有する装置のことをいう。さらに、半導体特性を利用することで機能しうる装置全般を半導体装置と呼んでもよい。または、半導体材料を有する装置のことを半導体装置と言う。

#### 【0076】

なお、表示装置とは、表示素子を有する装置のことを言う。なお、表示装置は、表示素子を含む複数の画素を含んでいても良い。なお、表示装置は、複数の画素を駆動させる周辺駆動回路を含んでいても良い。なお、複数の画素を駆動させる周辺駆動回路は、複数の画素と同一基板上に形成されてもよい。なお、表示装置は、ワイヤボンディングやバンプなどによって基板上に配置された周辺駆動回路、いわゆる、チップオングラス(COG)で接続されたICチップ、または、TABなどで接続されたICチップを含んでいても良い。なお、表示装置は、ICチップ、抵抗素子、容量素子、インダクタ、トランジスタなどが取り付けられたフレキシブルプリントサーキット(FPC)を含んでもよい。なお、表示装置は、フレキシブルプリントサーキット(FPC)などを介して接続され、ICチップ、抵抗素子、容量素子、インダクタ、トランジスタなどが取り付けられたプリント配線基板(PWB)を含んでいても良い。なお、表示装置は、偏光板または位相差板などの光学シートを含んでいても良い。なお、表示装置は、照明装置、筐体、音声入出力装置、光センサなどを含んでいても良い。4050

**【 0 0 7 7 】**

なお、照明装置は、バックライトユニット、導光板、プリズムシート、拡散シート、反射シート、光源（ＬＥＤ、冷陰極管など）、冷却装置（水冷式、空冷式）などを有していても良い。

**【 0 0 7 8 】**

なお、発光装置とは、発光素子などを有している装置のことをいう。表示素子として発光素子を有している場合は、発光装置は、表示装置の具体例の一つである。

**【 0 0 7 9 】**

なお、反射装置とは、光反射素子、光回折素子、光反射電極などを有している装置のことをいう。

10

**【 0 0 8 0 】**

なお、液晶表示装置とは、液晶素子を有している表示装置をいう。液晶表示装置には、直視型、投写型、透過型、反射型、半透過型などがある。

**【 0 0 8 1 】**

なお、駆動装置とは、半導体素子、電気回路、電子回路を有する装置のことを言う。例えば、ソース信号線から画素内への信号の入力を制御するトランジスタ（選択用トランジスタ、スイッチング用トランジスタなどと呼ぶことがある）、画素電極に電圧または電流を供給するトランジスタ、発光素子に電圧または電流を供給するトランジスタなどは、駆動装置の一例である。さらに、ゲート信号線に信号を供給する回路（ゲートドライバ、ゲート線駆動回路などと呼ぶことがある）、ソース信号線に信号を供給する回路（ソースドライバ、ソース線駆動回路などと呼ぶことがある）などは、駆動装置の一例である。

20

**【 0 0 8 2 】**

なお、表示装置、半導体装置、照明装置、冷却装置、発光装置、反射装置、駆動装置などは、互いに重複して有している場合がある。例えば、表示装置が、半導体装置および発光装置を有している場合がある。あるいは、半導体装置が、表示装置および駆動装置を有している場合がある。

**【 0 0 8 3 】**

なお、Aの上にBが形成されている、あるいは、A上にBが形成されている、と明示的に記載する場合は、Aの上にBが直接接して形成されていることに限定されない。直接接してはいない場合、つまり、AとBと間に別の対象物が介在する場合も含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

30

**【 0 0 8 4 】**

従って例えば、層Aの上に（もしくは層A上に）、層Bが形成されている、と明示的に記載されている場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、別の層（例えば層Cや層Dなど）は、単層でもよいし、複層でもよい。

**【 0 0 8 5 】**

さらに、Aの上方にBが形成されている、と明示的に記載されている場合についても同様であり、Aの上にBが直接接していることに限定されず、AとBとの間に別の対象物が介在する場合も含むものとする。従って例えば、層Aの上方に、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層（例えば層Cや層Dなど）が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、別の層（例えば層Cや層Dなど）は、単層でもよいし、複層でもよい。

40

**【 0 0 8 6 】**

なお、Aの上にBが形成されている、A上にBが形成されている、又はAの上方にBが形成されている、と明示的に記載する場合、斜め上にBが形成される場合も含むこととする。

50

**【0087】**

なお、Aの下にBが、あるいは、Aの下方にBが、の場合についても、同様である。

**【0088】**

なお、明示的に単数として記載されているものについては、単数であることが望ましい。ただし、これに限定されず、複数であることも可能である。同様に、明示的に複数として記載されているものについては、複数であることが望ましい。ただし、これに限定されず、単数であることも可能である。

**【0089】**

なお、図において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

10

**【0090】**

なお、図は、理想的な例を模式的に示したものであり、図に示す形状又は値などに限定されない。例えば、製造技術による形状のばらつき、誤差による形状のばらつき、ノイズによる信号、電圧、若しくは電流のばらつき、又は、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

**【0091】**

なお、専門用語は、特定の実施の形態、又は実施例などを述べる目的で用いられる場合が多く、これに限定されない。

**【0092】**

なお、定義されていない文言（専門用語又は学術用語などの科学技術文言を含む）は、通常の当業者が理解する一般的な意味と同等の意味として用いることが可能である。辞書等により定義されている文言は、関連技術の背景と矛盾がないような意味に解釈されることが好ましい。

20

**【0093】**

なお、第1、第2、第3などの語句は、様々な要素、部材、領域、層、区域を他のものと区別して記述するために用いられる。よって、第1、第2、第3などの語句は、要素、部材、領域、層、区域などの数を限定するものではない。さらに、例えば、「第1の」を「第2の」又は「第3の」などと置き換えることが可能である。

**【0094】**

なお、「上に」、「上方に」、「下に」、「下方に」、「横に」、「右に」、「左に」、「斜めに」、「奥に」、又は、「手前に」、などの空間的配置を示す語句は、ある要素又は特徴と、他の要素又は特徴との関連を、図によって簡単に示すために用いられる場合が多い。ただし、これに限定されず、これらの空間的配置を示す語句は、図に描く方向に加えて、他の方向を含むことが可能である。例えば、Aの上にB、と明示的に示される場合は、BがAの上にあることに限定されない。図中のデバイスは反転、又は $180^{\circ}$ 回転することが可能なので、BがAの下にあることを含むことが可能である。このように、「上に」という語句は、「上に」の方向に加え、「下に」の方向を含むことが可能である。ただし、これに限定されず、図中のデバイスは様々な方向に回転することが可能なので、「上に」という語句は、「上に」、及び「下に」の方向に加え、「横に」、「右に」、「左に」、「斜めに」、「奥に」、又は、「手前に」などの他の方向を含むことが可能である。

30

**【発明の効果】****【0095】**

本明細書等により開示される発明の一態様では、トランジスタおよび保持容量の少なくとも一部に、透光性を有する材料を用いる。これにより、トランジスタや保持容量が存在する領域においても光を透過させることができるとなるため、開口率を向上させることができる。また、トランジスタと別の素子（例えば、別のトランジスタ）とを接続する配線、または容量素子と別の素子（例えば、別の容量素子）とを接続する配線を、抵抗率が低い（導電率が高い）材料を用いて形成する場合には、信号波形のなまりを低減し、配線抵抗による電圧降下を抑制することができる。これにより、半導体装置の消費電力を低減するこ

40

50

とができる。また、半導体装置の大型化（大画面化）が容易となる。

【図面の簡単な説明】

【0096】

【図1】半導体装置の平面図および断面図である。

【図2】半導体装置の作製方法を説明する断面図である。

【図3】半導体装置の作製方法を説明する断面図である。

【図4】半導体装置の作製方法を説明する断面図である。

【図5】半導体装置の作製方法を説明する断面図である。

【図6】半導体装置の平面図および断面図である。

【図7】半導体装置の平面図および断面図である。

【図8】半導体装置の平面図および断面図である。

【図9】半導体装置の平面図および断面図である。

【図10】半導体装置の平面図および断面図である。

【図11】半導体装置の平面図および断面図である。

【図12】半導体装置の平面図および断面図である。

【図13】半導体装置の作製方法を説明する断面図である。

【図14】半導体装置の作製方法を説明する断面図である。

【図15】半導体装置の作製方法を説明する断面図である。

【図16】半導体装置の作製方法を説明する断面図である。

【図17】多階調マスクの構成を説明する断面図である。

【図18】半導体装置の平面図および断面図である。

【図19】半導体装置の平面図および断面図である。

【図20】半導体装置の平面図および断面図である。

【図21】半導体装置の平面図および断面図である。

【図22】半導体装置を説明する平面図および断面図である。

【図23】半導体装置を説明する図である。

【図24】半導体装置を説明する断面図である。

【図25】半導体装置を説明する断面図である。

【図26】半導体装置を説明する平面図および断面図である。

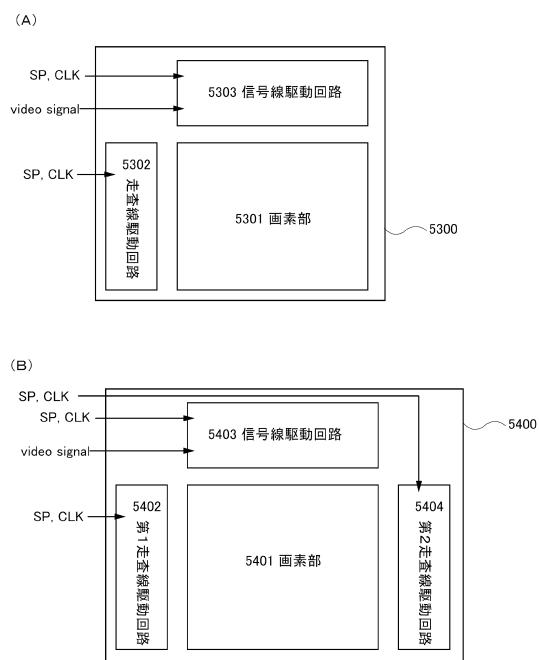

【図27】半導体装置を説明する図である。

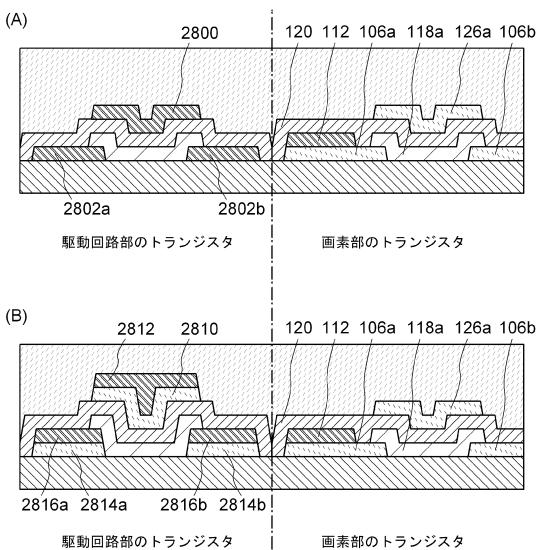

【図28】半導体装置を説明する断面図である。

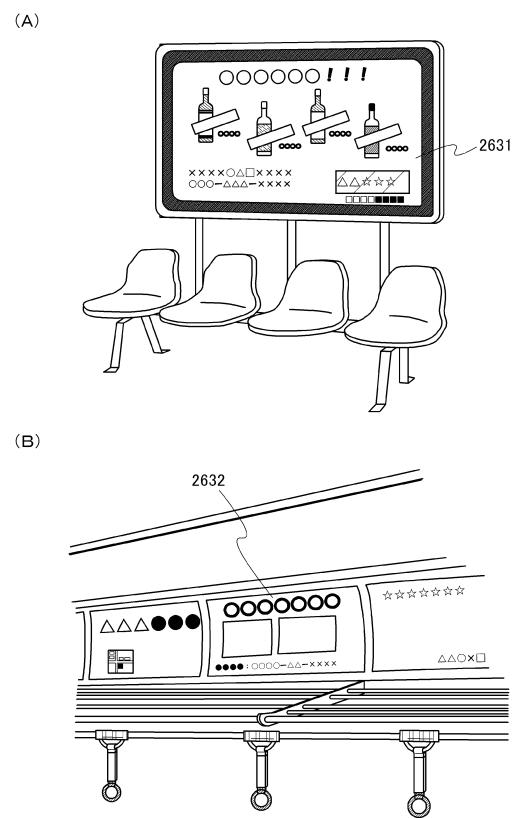

【図29】電子ペーパーの使用形態の例を説明する図である。

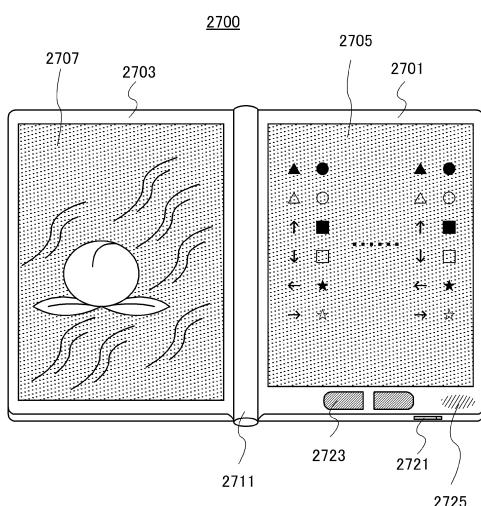

【図30】電子書籍の例を示す外観図である。

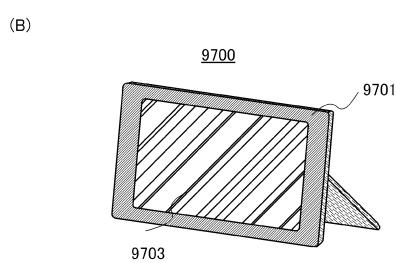

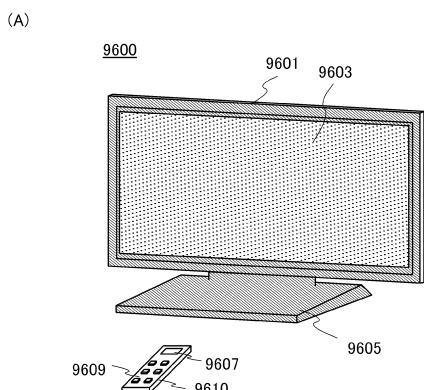

【図31】テレビジョン装置およびデジタルフォトフレームの例を示す外観図である。

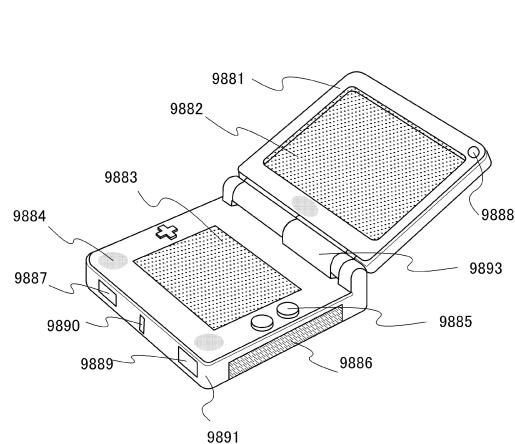

【図32】遊技機の例を示す外観図である。

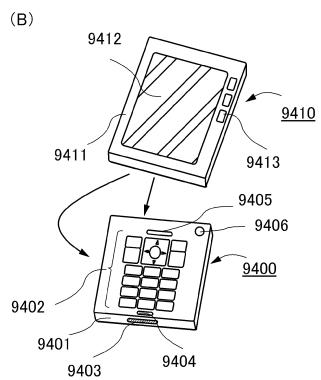

【図33】携帯電話機の例を示す外観図である。

【図34】半導体装置の作製方法を説明する断面図である。

【図35】半導体装置を説明する断面図である。

【図36】半導体装置の作製方法を説明する断面図である。

【図37】半導体装置を説明する平面図および断面図である。

【図38】半導体装置を説明する平面図および断面図である。

【図39】半導体装置を説明する図である。

【図40】半導体装置を説明する図である。

【図41】半導体装置を説明する図である。

【図42】半導体装置を説明する図である。

【図43】半導体装置を説明する図である。

【発明を実施するための形態】

【0097】

以下、実施の形態について、図面を用いて詳細に説明する。但し、発明は以下に示す実施の形態の記載内容に限定されず、本明細書等において開示する発明の趣旨から逸脱するこ

10

20

30

40

50

となく形態および詳細を様々に変更し得ることは当業者にとって自明である。また、異なる実施の形態に係る構成は、適宜組み合わせて実施することが可能である。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を用い、その繰り返しの説明は省略する。

#### 【0098】

なお、ある一つの実施の形態の中で述べる内容（一部の内容でもよい）は、その実施の形態で述べる別の内容（一部の内容でもよい）、及び／又は、一つ若しくは複数の別の実施の形態で述べる内容（一部の内容でもよい）に対して、適用、組み合わせ、又は置き換えなどを行うことが出来る。

#### 【0099】

なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。

#### 【0100】

なお、ある一つの実施の形態において述べる図（一部でもよい）は、その図の別の部分、その実施の形態において述べる別の図（一部でもよい）、及び／又は、一つ若しくは複数の別の実施の形態において述べる図（一部でもよい）に対して、組み合わせることにより、さらに多くの図を構成させることが出来る。

#### 【0101】

なお、ある一つの実施の形態において述べる図または文章において、その一部分を取り出して、発明の一態様を構成することは可能である。したがって、ある部分を述べる図または文章が記載されている場合、その一部分の図または文章を取り出した内容も、発明の一態様として開示されているものであり、発明の一態様を構成することが可能であるものとする。そのため、例えば、能動素子（トランジスタ、ダイオードなど）、配線、受動素子（容量素子、抵抗素子など）、導電層、絶縁層、半導体層、有機材料、無機材料、部品、基板、モジュール、装置、固体、液体、気体、動作方法、製造方法などが単数又は複数記載された図面（断面図、平面図、回路図、ブロック図、フローチャート、工程図、斜視図、立面図、配置図、タイミングチャート、構造図、模式図、グラフ、表、光路図、ベクトル図、状態図、波形図、写真、化学式など）または文章において、その一部分を取り出して、発明の一態様を構成することが可能であるものとする。

#### 【0102】

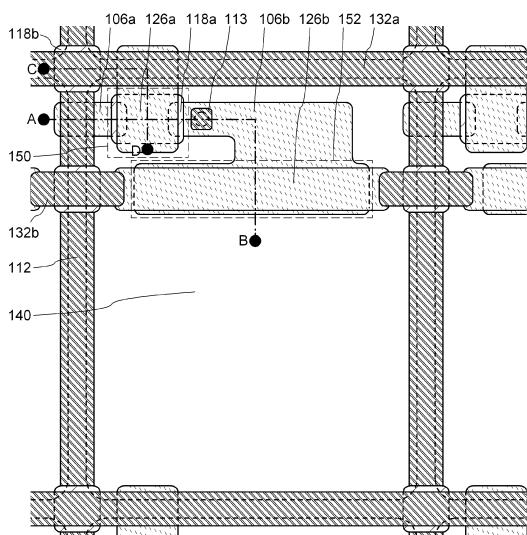

（実施の形態1）

本実施の形態では、半導体装置及びその作製方法について、図1乃至図11を用いて説明する。

#### 【0103】

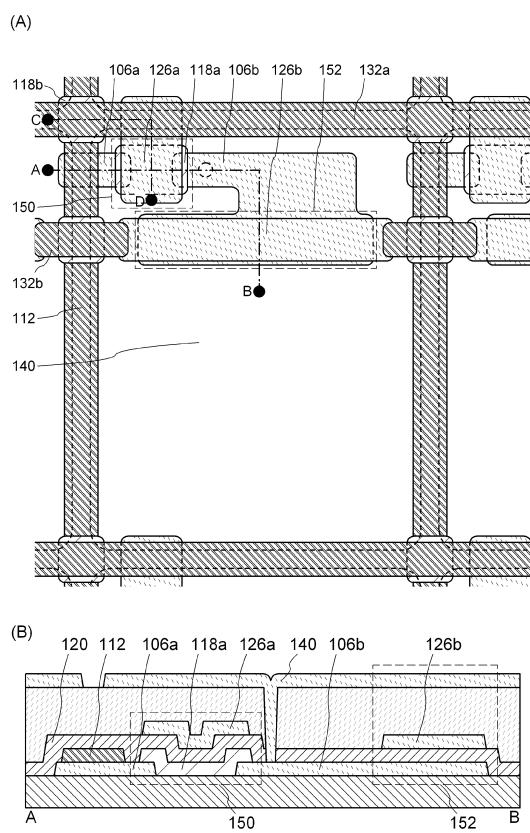

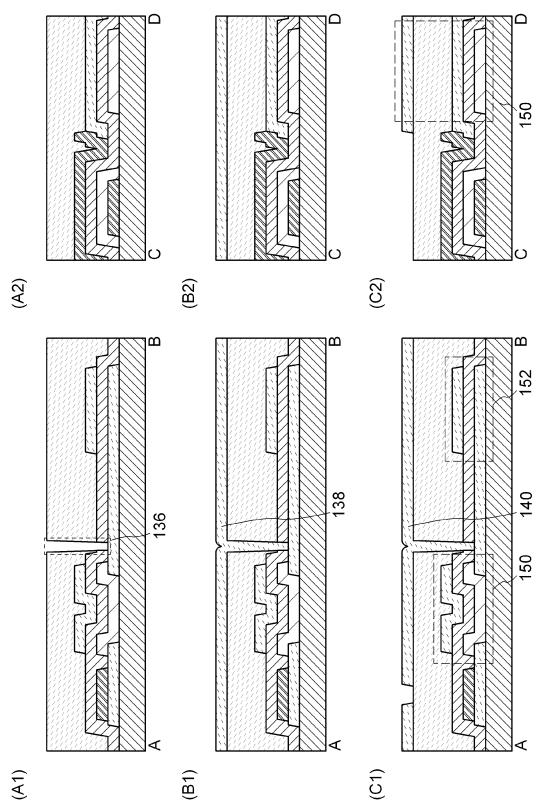

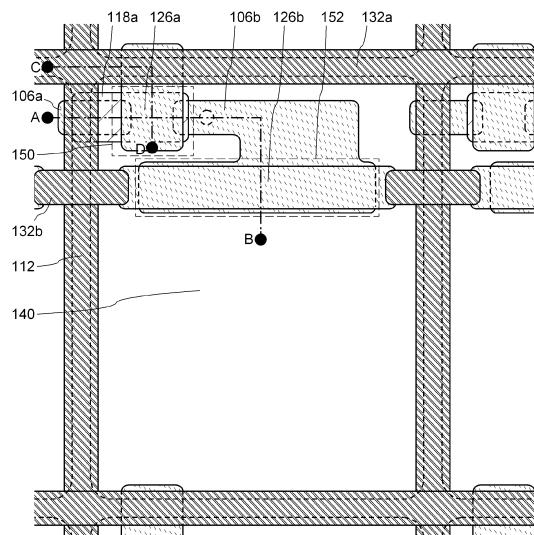

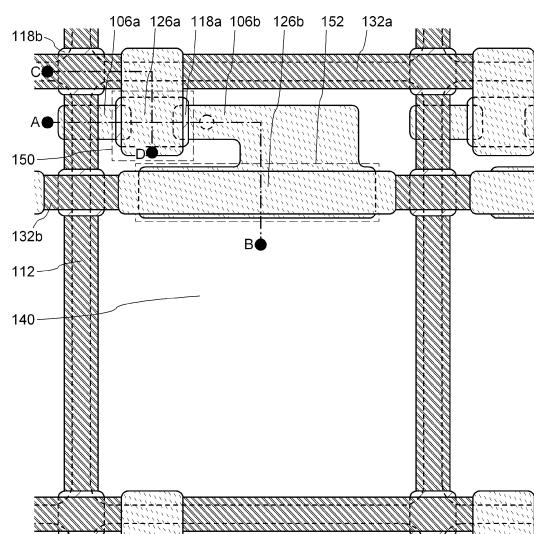

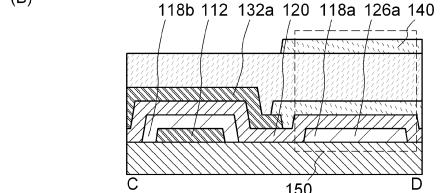

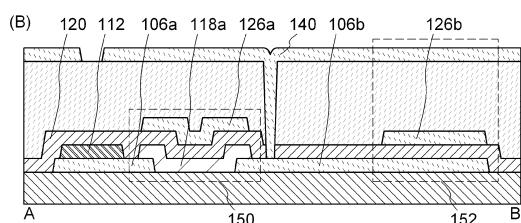

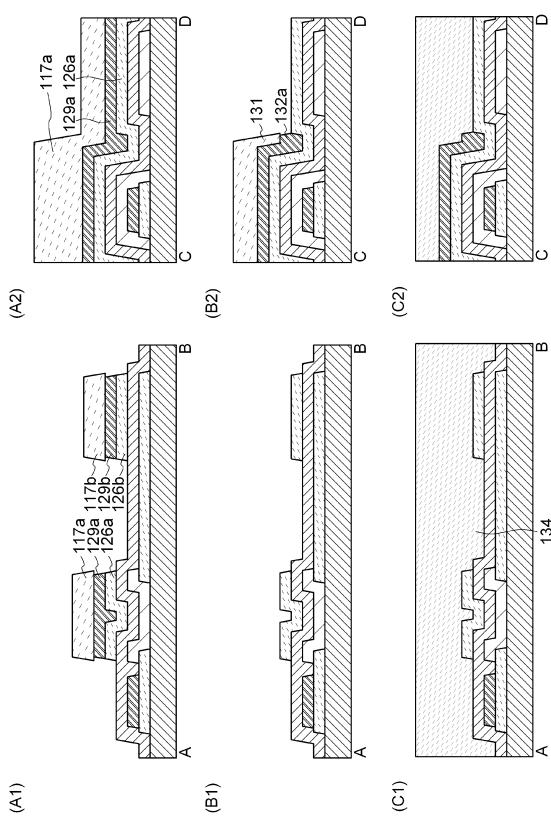

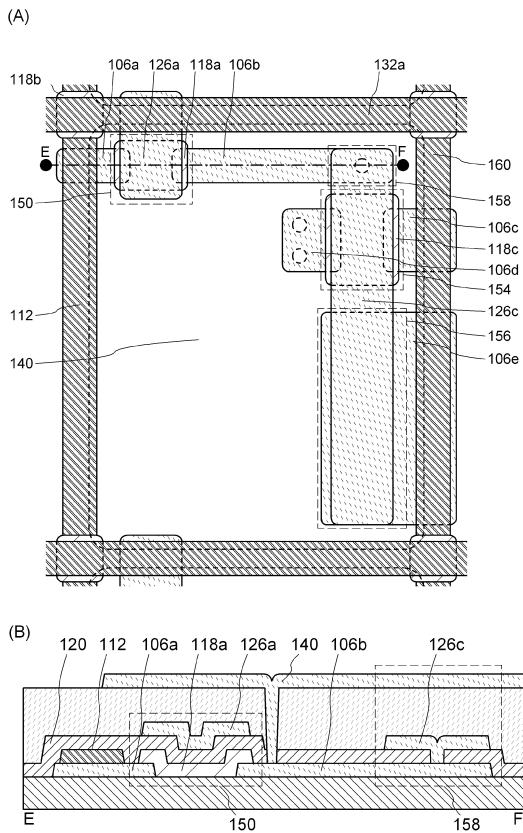

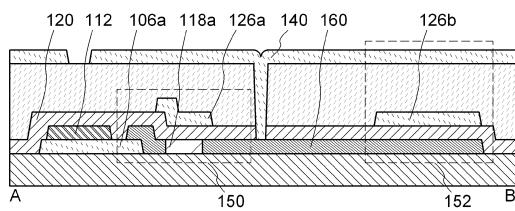

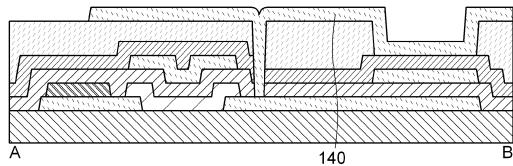

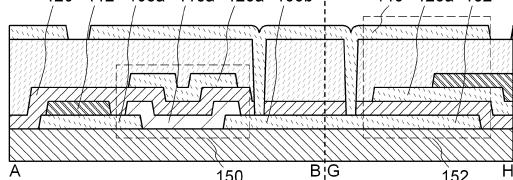

図1には、本実施の形態に係る半導体装置の構成の一例を示す。本実施の形態では、半導体装置として、特に液晶表示装置について説明しているが、開示される発明はこれに限定されない。エレクトロルミネッセンス表示装置（EL表示装置）や、電気泳動素子を用いた表示装置（いわゆる電子ペーパー）などへの適用は、もとより可能である。また、表示装置以外の他の半導体装置への適用も可能である。なお、図1(A)は平面図であり、図1(B)は図1(A)のA-Bにおける断面図である。

#### 【0104】

図1(A)に示す半導体装置は、ソース配線として機能する導電層112と、導電層112と交差し、ゲート配線として機能する導電層132aおよび容量配線として機能する導電層132bと、導電層132aと導電層112の交差部付近のトランジスタ150と、導電層132bと電気的に接続された保持容量152と、を有する画素部を備えている（図1(A)、図1(B)参照）。なお、本明細書等において、画素部とは、ゲート配線として機能する導電層およびソース配線として機能する導電層に囲まれた領域のことを指す。また、図1(A)において、導電層112と、導電層132aおよび導電層132bとは90°の角度で交差しているが、開示する発明は当該構成に限定されない。すなわち、導電層112と、導電層132aおよび導電層132bとが90°以外の角度で交差して

10

20

30

40

50

いても良い。

#### 【0105】

トランジスタ150は、ソース電極として機能する導電層106aと、ドレイン電極として機能する導電層106bと、半導体層118aと、ゲート絶縁層120と、ゲート電極として機能する導電層126aと、で構成されるいわゆるトップゲート型のトランジスタである(図1(A)、図1(B)参照)。また、保持容量152は、導電層106bと、ゲート絶縁層120と、導電層126bと、導電層140とで構成されている。より詳細には、導電層106bと導電層126bとの間、および導電層126bと導電層140との間に容量が形成される。なお、トランジスタにおけるソース電極およびドレイン電極は、キャリアの流れる方向によってその機能が入れ替わることがあるから、ソース電極およびドレイン電極の称呼は便宜的なものに過ぎない。つまり、各種導電層の機能が、上記称呼に限定して解釈されるものではない。10

#### 【0106】

ここで、トランジスタ150を構成する導電層106a、導電層106b、半導体層118a、導電層126a、および保持容量152を構成する導電層126bは、透光性を有する材料で形成されている。これにより、画素の開口率向上が実現されている。

#### 【0107】

また、導電層106aと電気的に接続される導電層112、および導電層126aと電気的に接続される導電層132aは、低抵抗材料で形成されている。このため、配線抵抗を低減し、消費電力を低減することができる。また、導電層112および導電層132aは遮光性を有する材料で形成されている。このため、画素間を遮光することができる。20

#### 【0108】

なお、上記において透光性を有するとは、少なくとも、導電層112や導電層132aと比較して、可視域(400nm～800nm程度)における光の透過率が高いことを意味する。

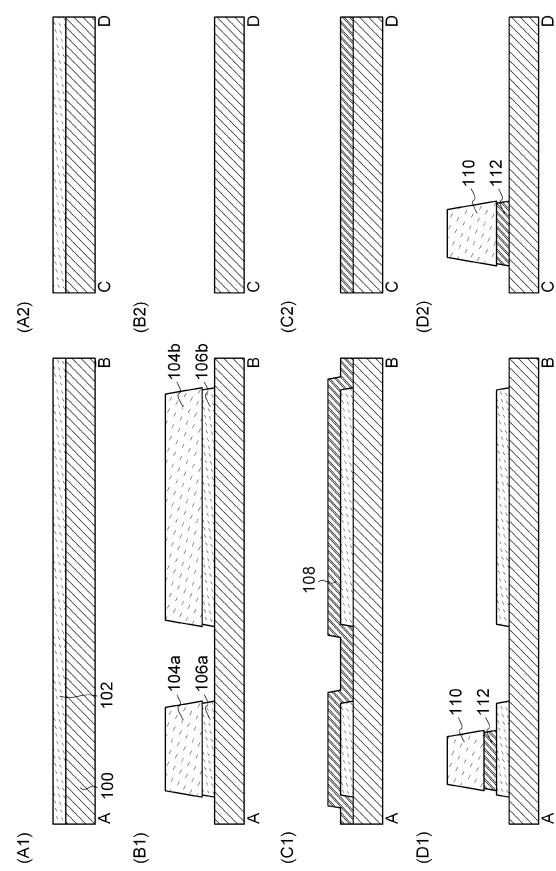

#### 【0109】

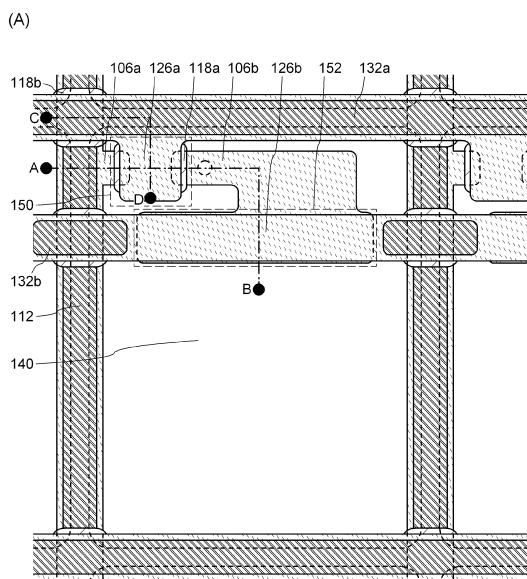

次に、半導体装置の作製方法の一例について説明する。

#### 【0110】

はじめに、絶縁面を有する基板100上に導電層102を形成する(図2(A1)、図2(A2)参照)。30

#### 【0111】

絶縁面を有する基板100としては、例えば、液晶表示装置などに使用される可視光透過性を有するガラス基板を用いることができる。上記のガラス基板は無アルカリガラス基板であることが好ましい。無アルカリガラス基板には、例えば、アルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。他にも、絶縁面を有する基板100として、セラミック基板、石英基板、サファイア基板などの絶縁体からなる絶縁性基板、珪素などの半導体材料からなる半導体基板の表面を絶縁材料で被覆した基板、金属やステンレスなどの導電体からなる導電性基板の表面を絶縁材料で被覆した基板、などを用いることができる。ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)に代表される可撓性を有する合成樹脂を用いても良い。40

#### 【0112】

図示しないが、絶縁面を有する基板100上には下地膜を設けるとよい。下地膜は、基板100からのアルカリ金属(Li、Cs、Na等)やアルカリ土類金属(Ca、Mg等)、その他の不純物の拡散を防止する機能を有する。つまり、下地膜を設けることより、半導体装置の信頼性向上という課題を解決することができる。下地膜は、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜などから選ばれた一または複数の絶縁層により形成することができる。例えば、基板側から窒化シリコン膜と酸化シリコン膜を順に積層した構成とすると好ましい。窒化シリコン膜の不純物に対する50

ブロッキング効果が高いためである。一方で、窒化シリコン膜が半導体と接する場合には不具合が発生する可能性もあるため、半導体と接する膜として、酸化シリコン膜を形成するのがよい。

#### 【0113】

なお、本明細書等において、酸化窒化物とは、その組成において、窒素よりも酸素の含有量（原子数）が多いものを示し、例えば、酸化窒化シリコンとは、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以下、シリコンが25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の範囲で含まれるものという。また、窒化酸化物とは、その組成において、酸素よりも窒素の含有量（原子数）が多いものを示し、例えば、窒化酸化シリコンとは、酸素が5原子%以上30原子%以下、窒素が20原子%以上55原子%以下、シリコンが25原子%以上35原子%以下、水素が10原子%以上25原子%以下の範囲で含まれるものという。但し、上記範囲は、ラザフォード後方散乱法（RBS：Rutherford Backscattering Spectrometry）や、水素前方散乱法（HFS：Hydrogen Forward Scattering）を用いて測定した場合のものである。また、構成元素の含有比率の合計は100原子%を超えない。

#### 【0114】

導電層102は、インジウム錫酸化物（Indium Tin Oxide：ITO）、酸化珪素を含むインジウム錫酸化物（ITSO）、有機インジウム、有機スズ、酸化亜鉛（ZnO）、窒化チタン等の透光性（可視光透過性）を有する材料を用いて形成すると良い。また、酸化亜鉛を含むインジウム亜鉛酸化物（Indium Zinc Oxide：IZO）、酸化亜鉛にガリウム（Ga）を添加した材料、酸化スズ（SnO<sub>2</sub>）、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物などを用いてもよい。導電層102は単層構造としても良いし、積層構造としても良いが、積層構造とする場合には、光透過率が十分に高くなるように導電層102を形成することが望ましい。なお、導電層102の作製方法としてはスパッタリング法を用いることが好ましいが、これに限る必要はない。

#### 【0115】

次に、導電層102上にレジストマスク104aおよびレジストマスク104bを形成し、当該レジストマスク104aおよびレジストマスク104bを用いて導電層102を選択的にエッチングして、導電層106aおよび導電層106bを形成する（図2（B1）、図2（B2）参照）。上記のエッチングとしては、ウエットエッチング、ドライエッチングのいずれを用いても良い。なお、上記エッチングの後にはレジストマスク104a、レジストマスク104bは除去する。導電層106aおよび導電層106bは、後に形成される絶縁層などの被覆性を向上し、段切れを防止するために、その端部がテーパー形状となるように形成することが好ましい。このように、導電層をテーパー形状となるように形成することで、半導体装置の歩留まり向上という課題を解決することができる。

#### 【0116】

導電層106aはトランジスタのソース電極として、導電層106bはトランジスタのドレイン電極および保持容量の電極（容量電極）として機能する。なお、各種導電層の機能は、ソース電極またはドレイン電極の称呼に限定して解釈されるものではない。

#### 【0117】

次に、導電層106aおよび導電層106bを覆うように導電層108を形成する（図2（C1）、図2（C2）参照）。なお、ここでは、導電層106aおよび導電層106bを覆うように導電層108を形成するが、開示される発明はこれに限定されない。

#### 【0118】

導電層108は、アルミニウム（Al）、タンゲステン（W）、チタン（Ti）、タンタル（Ta）、モリブデン（Mo）、ニッケル（Ni）、白金（Pt）、銅（Cu）、金（Au）、銀（Ag）、マンガン（Mn）、ネオジム（Nd）、ニオブ（Nb）、クロム（Cr）

10

20

30

40

50

C<sub>r</sub>)、セリウム(Ce)などの金属材料、またはこれらの金属材料を主成分とする合金材料、またはこれらの金属材料を成分とする窒化物を用いて、単層構造または積層構造で形成することができる。例えば、導電層108は、アルミニウムなどの抵抗が低い材料で形成することが望ましい。

#### 【0119】

導電層106a上に導電層108を形成した場合、これらの導電層が反応してしまう場合がある。例えば、導電層106aにITOを用い、導電層108にアルミニウムを用いた場合、化学反応が生じ得る。このような反応を避けるために、導電層108を、高融点材料と低抵抗材料との積層構造としても良い。より具体的には、例えば、導電層108の導電層106aと接する領域を高融点材料で形成し、導電層108の導電層106aと接触しない領域を低抵抗材料で形成すると好適である。10

#### 【0120】

上記高融点材料としては、モリブデン、チタン、タングステン、タンタル、クロムなどが挙げられる。低抵抗材料としては、アルミニウム、銅、銀などが挙げられる。

#### 【0121】

もちろん、導電層108を3層以上の積層構造としても良い。この場合、例えば、1層目がモリブデン、2層目がアルミニウム、3層目がモリブデンの積層構造、または、1層目がモリブデン、2層目がネオジムを微量に含むアルミニウム、3層目がモリブデンの積層構造とすることができる。導電層108をこのような積層構造とすることにより、ヒロックの発生を防止することができる。これにより、半導体装置の信頼性向上という課題を解決することができる。20

#### 【0122】

次に、導電層108上にレジストマスク110を形成し、当該レジストマスク110を用いて導電層108を選択的にエッチングして、導電層112を形成する(図2(D1)、図2(D2)参照)。なお、導電層112はソース配線としての機能を有する。また、導電層112は遮光性を有する材料を用いて形成されているため、遮光機能を有する。レジストマスク110は、導電層112の形成後に除去される。

#### 【0123】

なお、本実施の形態においては、導電層106aおよび導電層106bを形成した後、導電層112を形成する工程について説明したが、開示される発明はこれに限定して解釈されない。例えば、導電層106aおよび導電層106bと、導電層112の形成順序を入れ替えてても良い。つまり、ソース配線として機能する導電層112を形成した後に、ソース電極として機能する導電層106aおよび導電層106bを形成することもできる(図6(A)、図6(B)参照)。なお、図6においては、導電層126aおよび導電層126bと、導電層132aおよび導電層132bの形成順序は入れ替えていないが、導電層126aおよび導電層126bと、導電層132aおよび導電層132bの形成順序を入れ替えてても良い。30

#### 【0124】

また、導電層108をエッチングして導電層112を形成する際に、後にコンタクトホールが形成される領域に導電層113を形成しても良い(図7(A)、図7(B)参照)。このような構成を採用することで、コンタクトホールが形成される領域を遮光することができる。これにより、コンタクト領域における電極(画素電極)の表面凹凸による表示不具合を低減できるため、コントラスト向上や、光漏れ低減といった効果が得られる。すなわち、表示特性の向上という課題を解決することができる。なお、当該構成は液晶表示装置において特に効果的であるが、他の半導体装置に適用しても良いことは言うまでもない。この場合、遮光が必要な領域に導電層113を適宜形成すれば良い。40

#### 【0125】

次に、少なくとも導電層106aおよび導電層106bを覆うように半導体層114を形成する(図3(A1)、図3(A2)参照)。本実施の形態では、導電層106a、導電層106b、導電層112を覆うように、基板100上に半導体層114を形成する。50

## 【0126】

半導体層114は、In-Ga-Zn-O系の酸化物半導体材料をはじめ、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、Zn-O系など、各種の酸化物半導体材料を用いて形成することができる。また、その他の材料を用いることも可能である。例えば、In-Ga-Zn-O系の酸化物半導体材料による半導体層114は、In、Ga、Znを含む酸化物半導体ターゲット(  $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 1$  )を用いたスパッタ法で形成することができる。スパッタの条件は、例えば、基板100とターゲットとの距離を30mm~500mm、圧力を0.1Pa~2.0Pa、直流(DC)電源を0.25kW~5.0kW(直径8インチのターゲット使用時)、雰囲気をアルゴン雰囲気、酸素雰囲気、またはアルゴンと酸素との混合雰囲気とすることができます。なお、半導体層114として、ZnO系非単結晶膜を用いても良い。また、半導体層114の膜厚は、5nm~200nm程度とすればよい。

## 【0127】

上記のスパッタ法としては、スパッタ用電源に高周波電源を用いるRFスパッタ法や、DCスパッタ法、パルス的に直流バイアスを加えるパルスDCスパッタ法などを用いることができる。なお、パルス直流(DC)電源を用いると、ごみが軽減でき、膜厚分布も均一となるため好ましい。この場合、半導体装置の歩留まり向上、信頼性向上といった課題を解決することができる

## 【0128】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置を用いてもよい。多元スパッタ装置では、同一チャンバーで異なる複数の膜を形成することも、同一チャンバーで複数種類の材料を同時にスパッタして一の膜を形成することもできる。さらに、チャンバー内部に磁界発生機構を備えたマグネットロンスパッタ装置を用いる方法(マグネットロンスパッタ法)や、マイクロ波を用いて発生させたプラズマを用いるECRスパッタ法等を用いてもよい。また、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物を形成するリアクティブスパッタ法や、成膜中に基板にも電圧を印加するバイアススパッタ法等を用いてもよい。

## 【0129】

なお、半導体層114を形成する前に、半導体層114の被形成面(例えば、導電層106aおよび導電層106bの表面、下地膜を形成した場合には下地膜の表面を含む)にプラズマ処理を行ってもよい。プラズマ処理を行うことにより、被形成面に付着しているゴミなどを除去することができる。また、上述のプラズマ処理を行った後、大気に曝すことなく半導体層114を形成することにより、導電層106aおよび導電層106bと、半導体層114との電気的接続を良好に行うことができる。つまり、半導体装置の歩留まり向上、信頼性向上といった課題を解決することが可能である。

## 【0130】

なお、本実施の形態においては、半導体層114として酸化物半導体材料を用いる場合について説明しているが、開示する発明の一態様はこれに限定されない。酸化物半導体材料以外の半導体材料、化合物半導体材料等であっても、厚みを小さくすることにより、透光性を確保できる場合がある。このため、酸化物半導体材料に代えて、他の半導体材料を用いても良い。上記他の半導体材料の一例としては、シリコンやガリウム、ガリウムヒ素などの各種無機半導体材料、カーボンナノチューブなどの有機半導体材料、これらの混合材料などを挙げることができる。これらの材料を、単結晶、多結晶、微結晶(マイクロクリスタル、ナノクリスタルを含む)、非晶質といった各種態様で用いて半導体層114とすれば良い。

## 【0131】

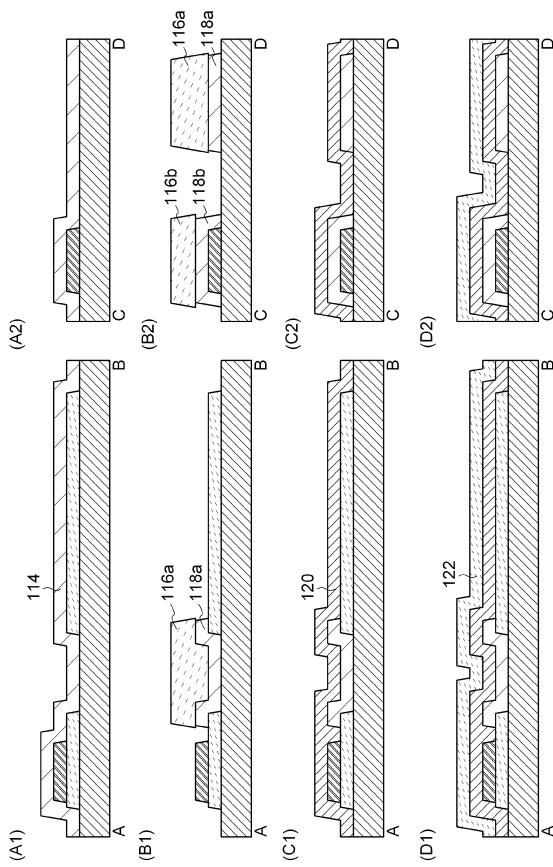

次に、半導体層114上にレジストマスク116aおよびレジストマスク116bを形成し、当該レジストマスク116aおよびレジストマスク116bを用いて半導体層114

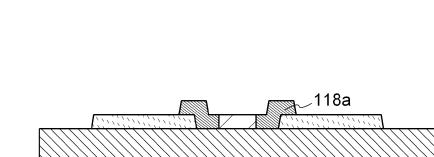

を選択的にエッティングして、半導体層 118a および半導体層 118b を形成する（図 3 (B1)、図 3 (B2) 参照）。半導体層 118a および半導体層 118b は島状に形成される。ここで、半導体層 118a はトランジスタの活性層となる。また、半導体層 118b は、配線間に生じる寄生容量を緩和する役割を果たす。なお、本実施の形態においては、半導体層 118b を形成する場合について説明しているが、半導体層 118b は必須の構成要素ではない。

#### 【0132】

また、上記のレジストマスクはスピンコート法などの方法を用いて形成しても良いが、液滴的吐出法やスクリーン印刷法などを用いる場合には、レジストマスクを選択的に形成することができる。この場合、生産性向上という課題を解決することが可能である。

10

#### 【0133】

半導体層 114 のエッティングの方法としては、ウェットエッティングまたはドライエッティングを用いることができる。ここでは、酢酸と硝酸と磷酸との混合液を用いたウェットエッティングにより、半導体層 114 の不要な部分を除去して、半導体層 118a および半導体層 118b を形成する。なお、上記エッティングの後にはレジストマスク 116a およびレジストマスク 116b は除去する。上記のウェットエッティングに用いることができるエッチャント（エッティング液）は半導体層 114 をエッティングできるものであればよく、上述したものに限られない。

#### 【0134】

ドライエッティングを行う場合は、例えば、塩素を含有するガス、または塩素を含有するガスに酸素が添加されたガスを用いると良い。塩素と酸素を含有するガスを用いることで、導電層や下地膜と、半導体層 114 とのエッティング選択比がとりやすくなるためである。

20

#### 【0135】

ドライエッティングに用いるエッティング装置としては、反応性イオンエッティング法 (RIE 法) を用いたエッティング装置や、ECR (Electron Cyclotron Resonance) や ICP (Inductively Coupled Plasma) などの高密度プラズマ源を用いたドライエッティング装置を用いることができる。また、ICP エッティング装置と比べて広い面積に渡って一様な放電が得られる E CCP (Enhanced Capacitively Coupled Plasma) モードのエッティング装置を用いても良い。E CCP モードのエッティング装置であれば、基板として第 10 世代以降の基板を用いるような場合においても対応が容易である。

30

#### 【0136】

なお、本実施の形態において示すように、トランジスタのソース電極として機能する導電層 106a、および、トランジスタのドレイン電極として機能する導電層 106b 上に半導体層 118a を形成する場合には、半導体層 118a の薄膜化が容易である。半導体層 118a が導電層 106a および導電層 106b 上に存在する場合には、逆の場合とは異なり、導電層をエッティングする際のオーバーエッティングによる半導体層 118a の消失の問題が生じないためである。このように、半導体層 118a の薄膜化が実現されることで、電圧印加時の空乏化が容易になり、S 値を小さくすることができる。また、オフ電流を小さくすることも可能である。つまり、半導体装置の高性能化という課題を解決することが可能である。なお、半導体層 118a は、ソース配線として機能する導電層 112 や、ソース電極として機能する導電層 106a、ゲート配線として機能する導電層 132a、ゲート電極として機能する導電層 126a などと比較して薄く形成されることが好適である。

40

#### 【0137】

その後、200 ~ 600、代表的には 300 ~ 500 の熱処理を行うと良い。ここでは、窒素雰囲気下で 350、1 時間の熱処理を行う。この熱処理により半導体層 118a および半導体層 118b の半導体特性を向上させることができる。なお、上記熱処理のタイミングは、半導体層 118a および半導体層 118b の形成後であれば特に限定されない。

50

**【 0 1 3 8 】**

なお、本実施の形態においては、導電層 106a および導電層 106b を形成した後、導電層 112 を形成し、その後、半導体層 118a を形成する工程について説明したが、開示される発明はこれに限定して解釈されない。例えば、導電層 106a および導電層 106b を形成した後、半導体層 118a を形成し、その後、導電層 112 を形成する工程を採用しても良い(図 8(A)、図 8(B) 参照)。この場合、半導体層 118a とのコンタクト抵抗を低減することができるという効果がある。

**【 0 1 3 9 】**

なお、導電層 106a および導電層 106b は、導電層 112 と比較して薄く形成するといい。導電層 106a および導電層 106b を薄く形成することにより、抵抗は高くなるが、透過率を一層向上させることができると有利である。もちろん、開示する発明の一態様をこれに限定して解釈する必要はない。

10

**【 0 1 4 0 】**

次に、半導体層 118a および半導体層 118b を覆うように、ゲート絶縁層 120 を形成する(図 3(C1)、図 3(C2) 参照)。

**【 0 1 4 1 】**

ゲート絶縁層 120 は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜、または酸化タンタル膜の単層構造または積層構造とすることができる。例えば、スパッタ法や CVD 法などを用いて、50 nm 以上 250 nm 以下の厚さで形成すれば良い。ここでは、ゲート絶縁層 120 として、スパッタ法を用いて、酸化シリコン膜を 100 nm の厚さで形成する。なお、ゲート絶縁層 120 は、透光性を有していることが好ましい。

20

**【 0 1 4 2 】**

次に、ゲート絶縁層 120 上に、導電層 122 を形成する(図 3(D1)、図 3(D2) 参照)。導電層 122 は、導電層 102 と同様の材料、作製方法により形成することができる。導電層 122 の詳細については、導電層 102 に係る説明を参照することができるから、ここでは省略する。なお、導電層 122 は透光性を有することが望ましい。

**【 0 1 4 3 】**

なお、導電層 102 と導電層 122 と同じ材料を用いて形成する場合には、材料および製造装置を共有することが容易になるため、低コスト化、スループットの向上などに寄与する。もちろん、同じ材料を用いて導電層 102 および導電層 122 を形成することは、必須の要件ではない。

30

**【 0 1 4 4 】**

次に、導電層 122 上にレジストマスク 124a およびレジストマスク 124b を形成し、当該レジストマスク 124a およびレジストマスク 124b を用いて導電層 122 を選択的にエッチングして、導電層 126a および導電層 126b を形成する(図 4(A1)、図 4(A2) 参照)。上記のエッチングとしては、ウエットエッチング、ドライエッチングのいずれを用いても良い。なお、上記エッチングの後にはレジストマスク 124a、レジストマスク 124b は除去する。導電層 126a はトランジスタのゲート電極として、導電層 126b は保持容量の電極(容量電極)として機能する。

40

**【 0 1 4 5 】**

なお、導電層 106b と導電層 126b とが重畠する領域の面積は適宜変更することができる。本実施の形態において示すように、導電層 106b と導電層 126b とは透光性を有する材料を用いて形成されているため、重畠する領域の面積を増大させて容量値を増加させる場合であっても、開口率を低下させずに済むという利点がある。つまり、容量値の増加という課題を、開口率の低下を伴わずに解決することができる。

**【 0 1 4 6 】**

また、本実施の形態においては、ソース電極として機能する導電層 106a およびドレン電極として機能する導電層 106b と、ゲート電極として機能する導電層 126a の一

50

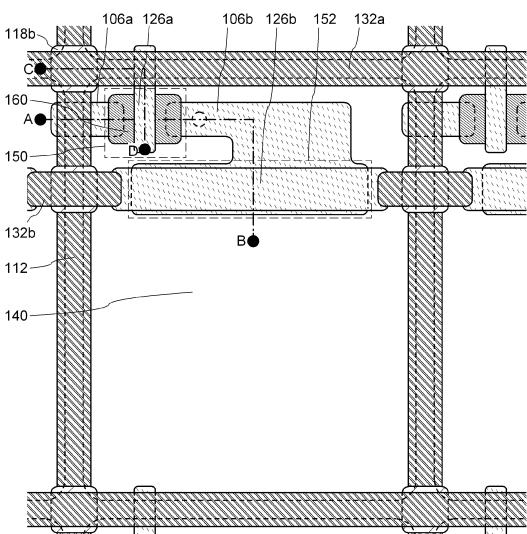

部が重畠するように導電層 106a、導電層 106b、導電層 126a を形成しているが、半導体層 118a の一部の導電性を高めることができる場合には、導電層 106a または導電層 106b と、導電層 126a とを重畠させない構成としても良い（図 9（A）、図 9（B）参照）。この場合、少なくとも導電層 106a または導電層 106b と、導電層 126a とが重畠しない領域 160 の導電性を高めることになる。図 9 中において、領域 160 は、半導体層 118a の導電層 106a と隣接する領域または導電層 106b と隣接する領域にあたる。なお、領域 160 は、導電層 126a と重畠しても良いし、重畠しなくとも良い。また、領域 160 は、導電層 106a または導電層 106b と重畠する領域であることが好ましいが、この限りではない。

## 【0147】

10

半導体層 118a に酸化物半導体材料を用いる場合において、領域 160 の導電性を高める方法としては、例えば、水素を選択的に添加する方法がある。半導体層として酸化物半導体材料を用いない場合には、その材料にあわせて導電性を高める方法を選択すればよい。例えば、シリコン系の材料を用いて半導体層 118a を形成する場合には、リンやボロンなど、所定の導電性を付与する不純物元素を添加すればよい。

## 【0148】

このように、導電層 106a または導電層 106b と、導電層 126a とを重畠させない構成とすることにより、導電層 106a（または導電層 106b）と導電層 126a との重畠に起因する寄生容量を低減することができる。つまり、半導体装置の特性向上という課題を解決することができる。

20

## 【0149】

なお、上記水素の添加は、半導体層 114 の形成後、半導体層 118a の形成後、絶縁層 120 の形成後、導電層 126a の形成後など、各種工程後のいずれかに行うことができる。例えば、半導体層 118 の形成後に水素を添加する場合には、半導体層 118a 上に選択的にレジストマスク 170 を形成して（図 34（A）参照）、水素 190 を添加することにより（図 34（B）参照）、領域 160 を形成することができる（図 34（C）参照）。この場合、半導体装置の構成を図 35（A）や図 35（B）のようにすることも可能である。領域 160 では導電性が高められており、別途導電層 106b などを設ける必要性が低下するためである。ここで、図 35（A）は導電層 106b を設けない構成を、図 35（B）は導電層 106a および導電層 106b を設けない構成を示している。なお、導電層 126a を形成した後に水素を添加する場合には、導電層 126a をマスクとして、自己整合的に水素を添加することが可能である。

30

## 【0150】

次に、導電層 126a および導電層 126b を覆うように、導電層 128 を形成する（図 4（B1）、図 4（B2）参照）。導電層 128 は、導電層 108 と同様の材料、作製方法により形成することができる。導電層 128 の詳細については、導電層 108 に係る説明を参照することができるから、ここでは省略する。この場合にも、導電層 108 と導電層 128 とを同じ材料を用いて形成することにより、低コスト化、スループットの向上などが実現されるため好ましい。

## 【0151】

40

次に、導電層 128 上にレジストマスク 130 を形成し、当該レジストマスク 130 を用いて導電層 128 を選択的にエッティングして、導電層 132a および導電層 132b を形成する（図 4（C1）、図 4（C2）参照、導電層 132b については図 1（A）参照）。なお、導電層 132a はゲート配線として、導電層 132b は容量配線として機能する。また、導電層 132a は遮光性を有する材料を用いて形成されているため、遮光機能を有する。レジストマスク 130 は、導電層 132a および導電層 132b の形成後に除去される。

## 【0152】

なお、本実施の形態においては、導電層 126a および導電層 126b を形成した後、導電層 132a および導電層 132b を形成する工程について説明したが、開示される発明

50

はこれに限定して解釈されない。例えば、導電層 126a および導電層 126b と、導電層 132a および導電層 132b の形成順序を入れ替えてても良い。つまり、ゲート配線として機能する導電層 132a および容量配線として機能する導電層 132b を形成した後に、ゲート電極として機能する導電層 126a および保持容量の電極として機能する導電層 126b を形成することもできる（図 10（A）、図 10（B）参照）。なお、図 10においては、導電層 106a および導電層 106b と、導電層 112 の形成順序は入れ替えていないが、導電層 106a および導電層 106b と、導電層 112 の形成順序を入れ替えてても良い。

#### 【0153】

なお、導電層 126a および導電層 126b は、導電層 132a などと比較して薄く形成すると良い。導電層 126a および導電層 126b を薄く形成することにより、抵抗は高くなるが、透過率を一層向上させることができると有利である。もちろん、開示する発明の一態様をこれに限定して解釈する必要はない。

#### 【0154】

また、導電層 126b 上に残存するように導電層 132b を形成しても良い（図 11（A）、図 11（B）参照）。このように、導電層 132b を形成することにより、容量配線の配線抵抗を低減することができる。なお、導電層 126b 上における導電層 132b の幅は、導電層 126b と比較して十分に小さくすることが好ましい。このように導電層 132b を形成することにより、容量配線の配線抵抗を低減するという課題を、実質的な開口率の低下なしに解決することができる。

#### 【0155】

次に、ゲート絶縁層 120、導電層 126a、導電層 126b、導電層 132a、導電層 132b を覆うように絶縁層 134 を形成する（図 4（D1）、図 4（D2）参照）。絶縁層 134 の表面は、後の電極（画素電極）の被形成面となるため、平坦に形成することが好ましい。特に、開示する発明の一態様においては、透光性を有する材料を用いて各種素子を形成することが可能であるため、これらの素子が形成されている領域をも表示領域（開口領域）として利用することができる。したがって、素子や配線に起因する凹凸を緩和するように絶縁層 134 を形成することは極めて有益である。

#### 【0156】

絶縁層 134 は、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の酸素または窒素を含有する材料からなる絶縁膜、DLC（ダイヤモンドライクカーボン）等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる膜、などの単層構造または積層構造とすることができます。例えば、窒化シリコンを有する膜は、不純物をプロッキングする効果が高いため、素子の信頼性向上に好適である。また、有機材料を有する膜は、凹凸を緩和する機能が高いため、素子の特性向上に好適である。なお、絶縁層 134 を、窒化珪素を有する膜と、有機材料を有する膜との積層構造とする場合には、図中下側（素子に近い側）に窒化珪素を有する膜を配置し、上側（画素電極の被形成面側）に有機材料を有する膜を配置することが好適である。絶縁層 134 は、十分な透光性を有していることが好ましい。

#### 【0157】

なお、絶縁層 134 を絶縁層 134a と絶縁層 134b の二層構造とする場合には（図 36（A）参照）、絶縁層 134b の導電層 126b と重畠する領域をエッチングにより除去することで（図 36（B）参照）、導電層 126b と、後に形成される導電層 140 との間に形成される容量の容量値を増加させることができる（図 36（C）参照）。なお、開示する発明の一態様は上記に限定されず、絶縁層 134 を三層以上の多層構造としても良い。

#### 【0158】

カラーフィルタとしての機能を有するように絶縁層 134 を形成しても良い。このように、素子を形成する基板にカラーフィルタを形成することにより、対向基板などを貼り合わ

10

20

30

40

50

せる際の位置合わせが容易となる。もちろん、絶縁層134にカラーフィルタとしての機能を有せしめることに限定されず、別途カラーフィルタとして機能する層を基板100上に形成しても良い。なお、開示する発明の一態様では、遮光性を有する材料を用いてソース配線やゲート配線などを形成している。これにより、ブラックマスク（ブラックマトリクス）を別途形成することなく、画素間を遮光することができる。つまり、ブラックマスクを別途形成する場合と比較して、工程を簡略化しつつ、高性能な半導体装置を提供することができる。もちろん、開示する発明の一態様をこれに限定して解釈する必要はなく、別途ブラックマスクを形成しても良い。

#### 【0159】

なお、絶縁層134が無くとも大きな不都合が生じない場合には、絶縁層134を形成しない構成とすることができます。この場合、工程を簡略化することができるというメリットがある。

10

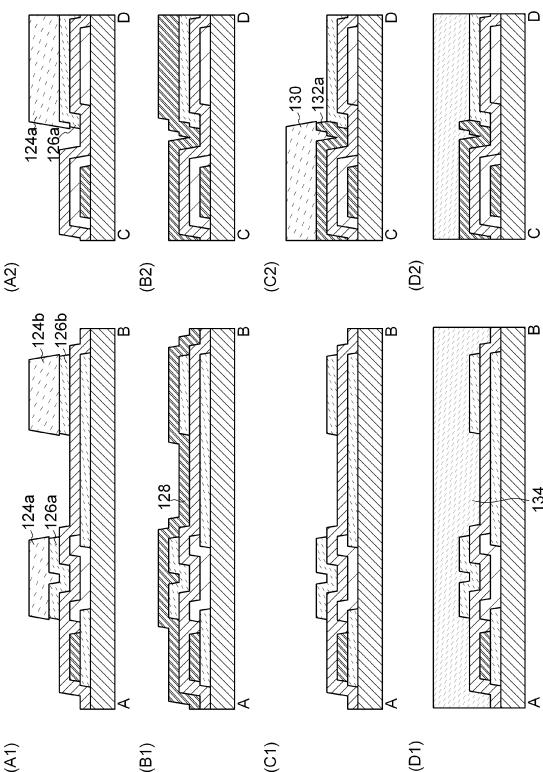

#### 【0160】

その後、絶縁層134に導電層106bに達するコンタクトホール136を形成し、導電層106bの表面の一部を露出させる（図5（A1）、図5（A2）参照）。

#### 【0161】

そして、絶縁層134を覆うように、導電層138を形成する（図5（B1）、図5（B2）参照）。絶縁層134にはコンタクトホールが形成されているため、導電層106bと導電層138とは電気的に接続されることになる。

#### 【0162】

導電層138は、導電層102や導電層122と同様の材料、作製方法により形成することができる。導電層138の詳細については、導電層102や導電層122に係る説明を参照することができるから、ここでは省略する。なお、導電層138は透光性を有することが望ましい。この場合にも、導電層102や導電層122と導電層138と同じ材料を用いて形成することにより、低コスト化、スループットの向上などが実現されるため好ましい。

20

#### 【0163】

次に、導電層138上にレジストマスクを形成し、当該レジストマスクを用いて導電層138を選択的にエッチングして、導電層140を形成する（図5（C1）、図5（C2）参照）。ここで、導電層140は、画素電極としての機能を有する。

30

#### 【0164】

なお、導電層140は、その端部が、導電層112または導電層132aと重なるように形成することが好ましい。このように導電層140を形成することで、画素の開口率を最大化すると共に不要な光漏れなどを抑制することが可能となる。これにより、コントラストが向上するという効果が得られる。つまり、表示装置の特性向上という課題を解決することができる。

#### 【0165】

図中には示さないが、導電層138から形成される導電層を用いて、ソース配線、ソース電極、ゲート配線、ゲート電極、容量配線、容量電極、などを互いに接続させることができる。つまり、導電層138から形成される導電層を、各種配線として機能させることができる。

40

#### 【0166】

以上により、透光性を有するトランジスタ150および透光性を有する保持容量152を備えた半導体装置を作製することができる（図5（C1）、図5（C2）参照）。

#### 【0167】

このように、透光性を有する材料を用いてトランジスタ150および保持容量152を形成することにより、ソース電極やドレイン電極、ゲート電極などが形成された領域においても光を透過させることができるために、画素の開口率を向上させることができる。また、ソース配線やゲート配線、容量配線として機能する導電層を、低抵抗材料を用いて形成することにより、配線抵抗を低減し、消費電力を低減することができる。また、信号の波形

50

のなまりを低減し、配線抵抗に起因する電圧降下を抑制することができる。さらに、遮光性を有する材料を用いてソース配線やゲート配線などを形成することにより、ブラックマスク（ブラックマトリクス）を別途形成することなく、画素間を遮光することができる。つまり、ブラックマスクを別途形成する場合と比較して、工程を簡略化しつつ、高性能な半導体装置を提供することができる。

#### 【0168】

また、透光性を有する材料を用いて容量電極を形成することにより、容量電極の面積を十分に大きくすることができます。つまり、保持容量の容量値を十分に大きくすることが可能である。これにより、画素電極の電位保持特性が向上し、表示品質が向上する。また、フィードスルー電位を小さくすることができる。また、クロストークを低減することができる。10

#### 【0169】

また、透光性を有する材料を用いてトランジスタ150を形成するため、トランジスタ150におけるチャネル長（L）やチャネル幅（W）の設計の自由度が極めて高い（レイアウトの自由度が高い）。これは、開口率がチャネル長やチャネル幅の影響を受けないためである。なお、駆動回路などの透光性が不要な対象に対して上記素子を用いる場合には、透光性を有しない材料を用いて形成しても良い。この場合、画素部に用いる素子と、それ以外の領域（例えば駆動回路）に用いる素子とを作り分けることができる。

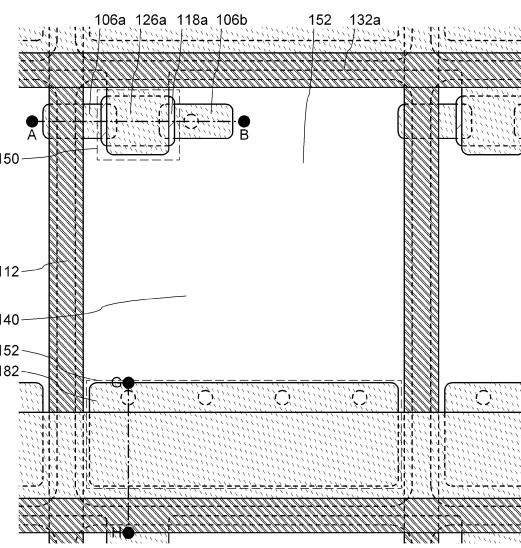

#### 【0170】

図37および図38に、半導体装置の別の構成例を示す。図37は、ソース配線として機能する導電層112が、ソース電極としての機能を備え、ゲート配線として機能する導電層132aが、ゲート電極としての機能を備えた一例である。ここで、導電層112および導電層132aは導電性の高い材料を用いて形成することができる。一方で、ドレイン電極として機能する導電層106bは、透光性を有する材料を用いて形成されることが好みしい。なお、容量配線として機能する導電層180は、導電性の高い材料を用いて形成しても良いし、透光性を有する材料を用いて形成しても良い。図38は、ゲート電極として機能する導電層126aが、保持容量の一方の電極としての機能を備えた一例である。すなわち、前段または後段のゲート配線として機能する導電層（導電層132aに対応）が容量配線としての機能を備えていることになる。ここで、導電層106aまたは導電層106bと同じ工程で形成される導電層182は、保持容量の他方の電極としての機能を備えている。導電層182は、画素部と重畠する領域に形成されるから、透光性を有する材料を用いて形成されることが好みしい。2030

#### 【0171】

なお、トランジスタにおけるチャネル長（L）やチャネル幅（W）は、導電層132aなどの幅より大きいものとすることが可能である。これは、半導体層118aが光透過性を有する材料で形成されているため、開口率が半導体層118aの大きさに依存しないことによる。ただし、開示する発明の一態様がこれに限定して解釈されるものではない。トランジスタは並列または直列に複数配置しても良い。これにより、トランジスタ数を増加させることができる。

#### 【0172】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。40

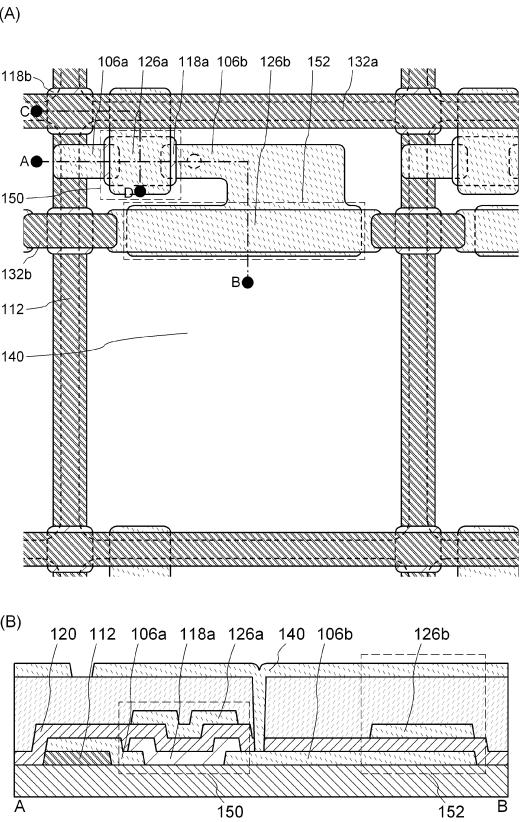

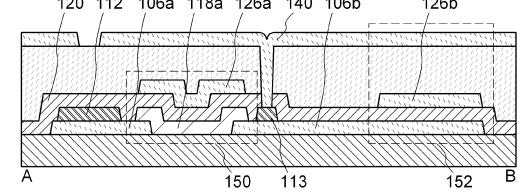

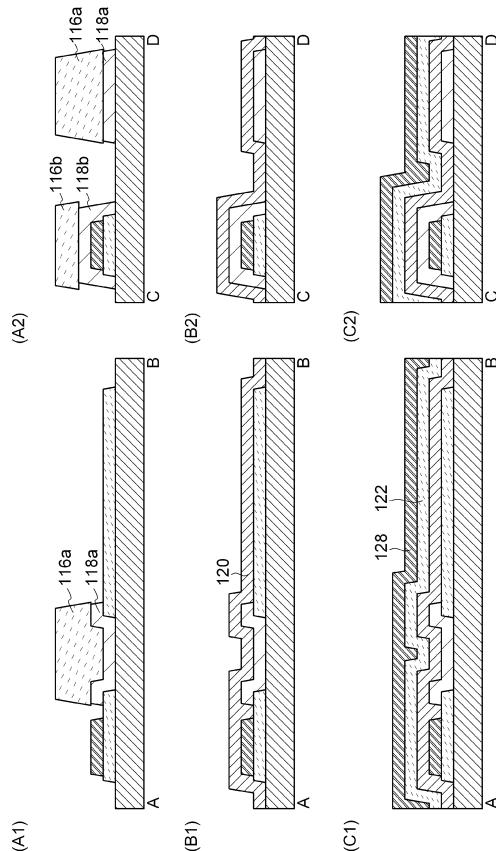

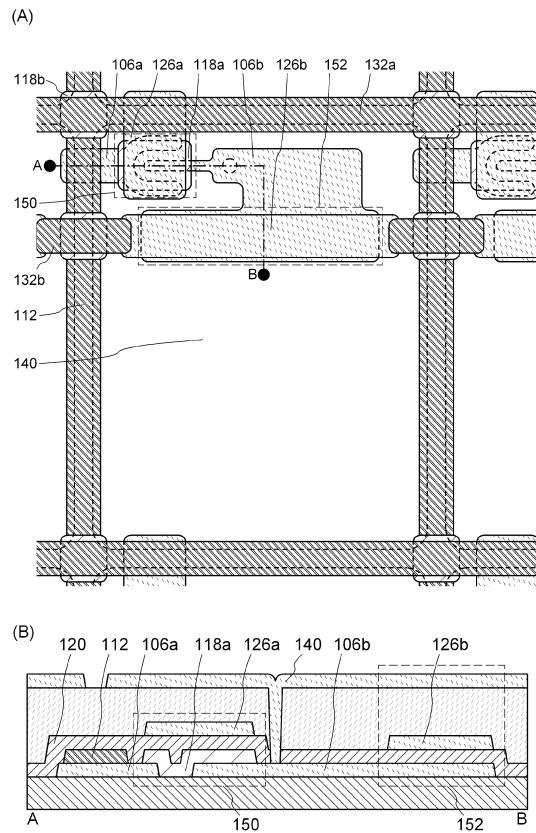

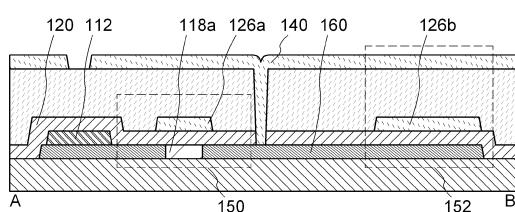

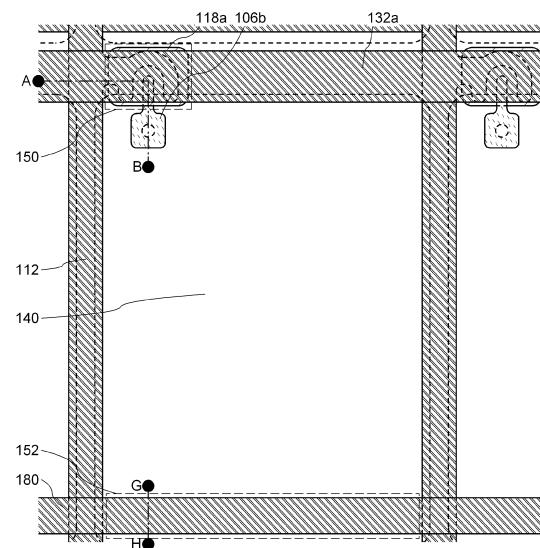

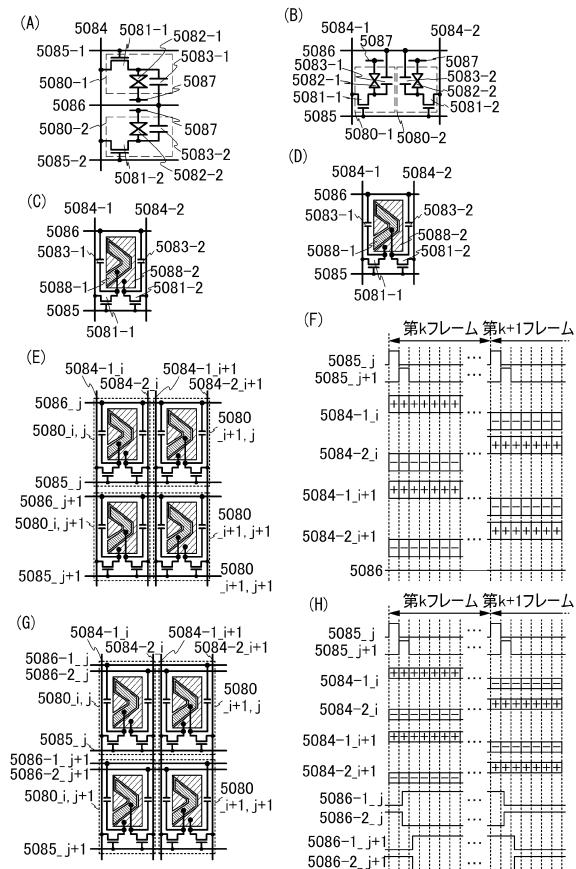

#### 【0173】

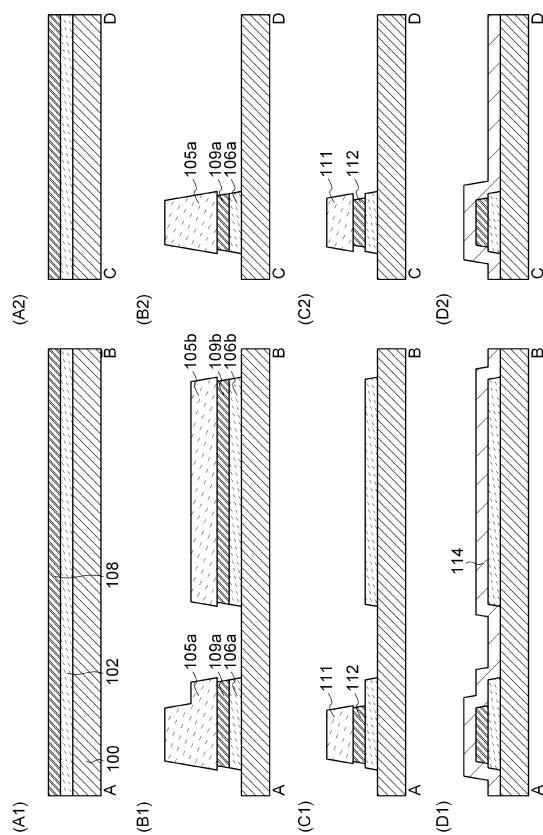

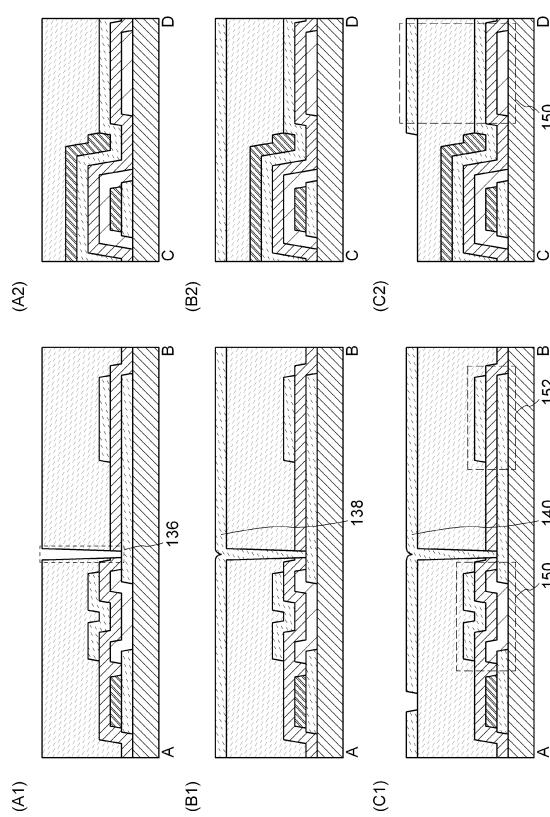

##### （実施の形態2）

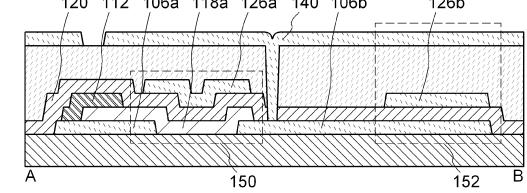

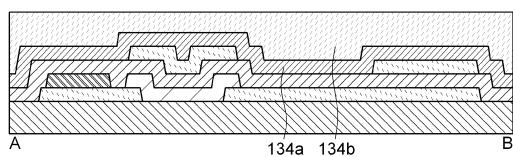

本実施の形態では、半導体装置の作製方法の他の一例について、図12乃至図16を用いて説明する。なお、本実施の形態に係る半導体装置の作製方法は、多くの部分で実施の形態1に係る作製方法と共通している。したがって、以下においては、重複する構成、重複する符号などの説明は省略する。

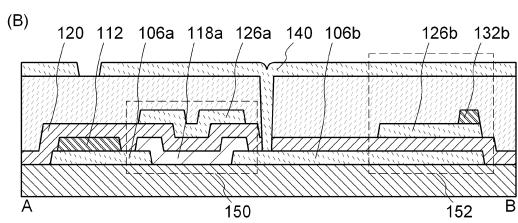

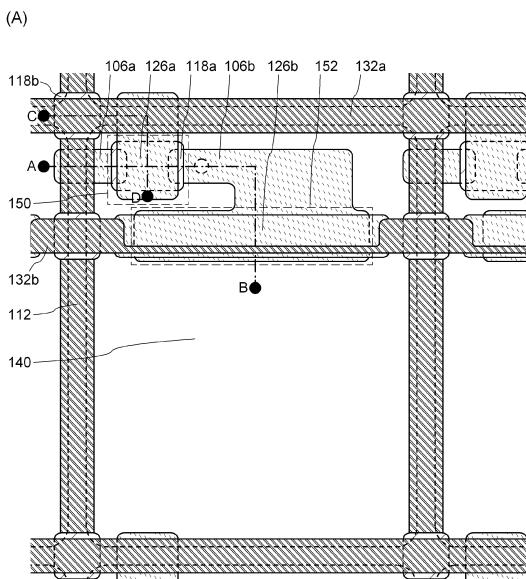

#### 【0174】

図12に、本実施の形態に係る半導体装置の構成の一例を示す。図12に係る構成では、遮光性を有する導電層（例えば、導電層112、導電層132a、導電層132bなど）50

の下層には、透光性を有する導電層（例えば、導電層106a、導電層126a、導電層126bなど）が存在している（図12（A）、図12（B）参照）。なお、図12（A）は平面図であり、図12（B）は図12（A）のA-Bにおける断面図である。

#### 【0175】

次に、半導体装置の作製方法の一例について説明する。

#### 【0176】

はじめに、絶縁面を有する基板100上に導電層102および導電層108を順に積層して形成する（図13（A1）、図13（A2）参照）。絶縁面を有する基板100、導電層102、導電層108の詳細については実施の形態1を参照することができる。

#### 【0177】

図示しないが、絶縁面を有する基板100上には下地膜を設けるとよい。下地膜の詳細についても実施の形態1を参照することができる。なお、開示する発明の一態様は下地膜を設けることに限定されない。

#### 【0178】

次に、導電層108上にレジストマスク105aおよびレジストマスク105bを形成し、当該レジストマスク105aおよびレジストマスク105bを用いて導電層102および導電層108を選択的にエッチングして、導電層106a、導電層106b、導電層109a、導電層109bを形成する（図13（B1）、図13（B2）参照）。

#### 【0179】

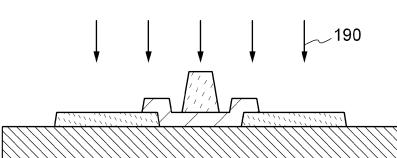

本実施の形態に係る半導体装置の作製方法と、実施の形態1に係る半導体装置の作製方法との相違点の一は、導電層102および導電層108のエッチング工程にある。本実施の形態においては、エッチング工程において用いるレジストマスク105aおよびレジストマスク105bを、多階調マスクを用いて形成している。

#### 【0180】

多階調マスクとは、多段階の光量で露光を行うことが可能なマスクである。多階調マスクを用いることで、例えば、露光、半露光、未露光といった3段階の光量で露光を行うことができる。つまり、多階調マスクを用いることにより、一度の露光及び現像で、複数（代表的には二種類）の厚さを有するレジストマスクを形成することができる。そのため、多階調マスクを用いることで、フォトマスクの使用数を削減することができる。

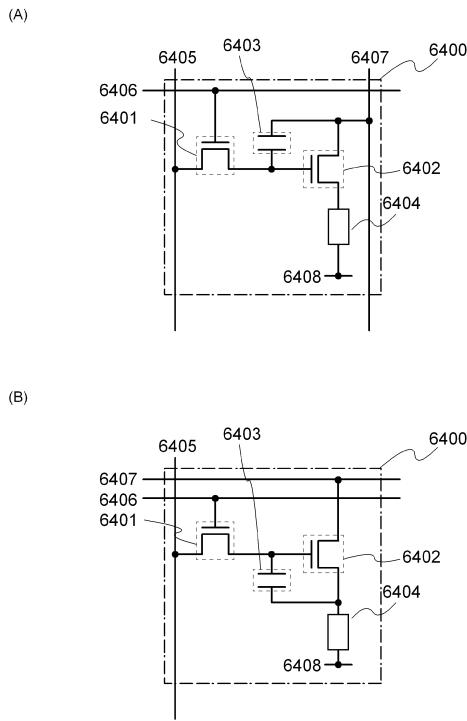

#### 【0181】

代表的な多階調マスクとしては、グレートーンマスクやハーフトーンマスクがある。グレートーンマスクは、透光性を有する基板上に遮光性を有する材料層により形成された遮光部と、該遮光性を有する材料層に設けられたスリット部で構成される。スリット部は露光に用いる光の解像度限界以下の間隔で設けられたスリット（ドットやメッシュなどを含む）を有することで、光の透過率を制御する機能を有する。なお、スリット部に設けられるスリットは周期的なものであってもよいし、非周期的なものであってもよい。ハーフトーンマスクは、透光性を有する基板上に遮光性を有する材料層により形成された遮光部と、所定の透光性を有する材料層により形成された半透過部で構成される。半透過部は、その材料層の材質や厚さに応じた光の透過率を有する。半透過部における透過率は、概ね10%～70%の範囲となっている。

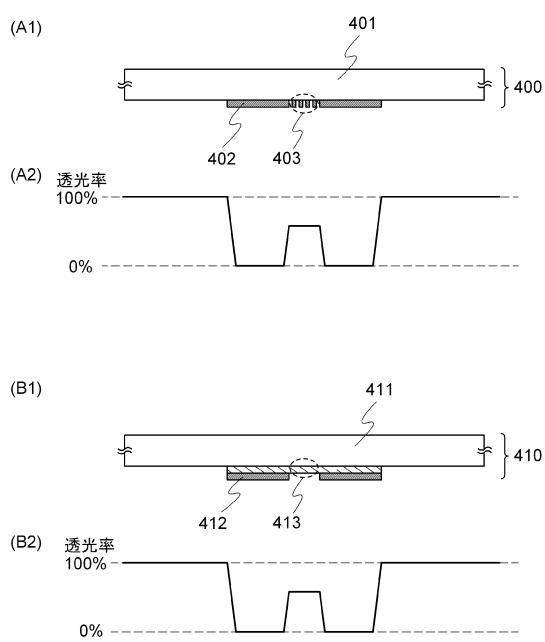

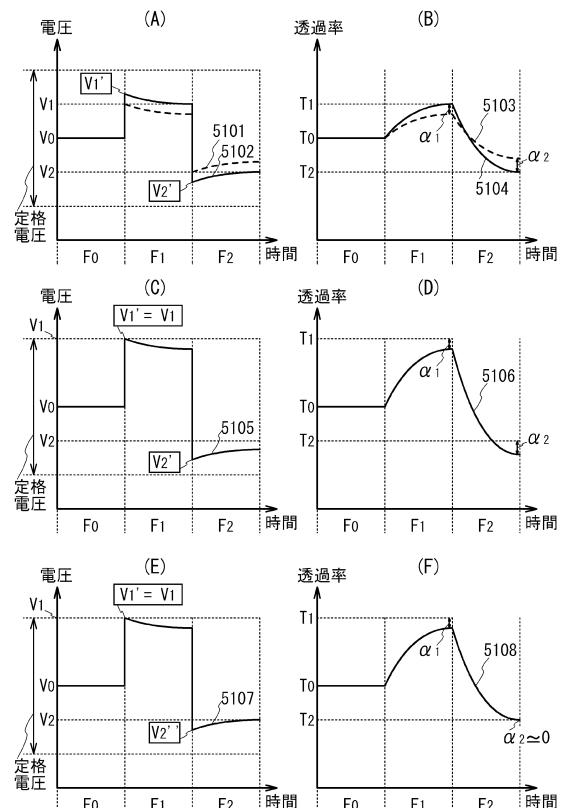

#### 【0182】

図17に、代表的な多階調マスクの断面を示す。図17（A1）は、グレートーンマスク400を示しており、図17（B1）は、ハーフトーンマスク410を示している。

#### 【0183】

図17（A1）に示すグレートーンマスク400は、透光性を有する基板401に遮光性を有する材料層により形成された遮光部402、および遮光性を有する材料層のパターンにより形成されたスリット部403で構成されている。

#### 【0184】

スリット部403は、露光に用いる光の解像度限界以下の間隔で設けられたスリットを有する。透光性を有する基板401としては、石英等を用いることができる。遮光部402

10

20

30

40

50

およびスリット部 403 を構成する遮光層は、金属膜を用いて形成すればよく、好ましくはクロム又は酸化クロム等により形成される。図 17 (A1) に示すグレートーンマスク 400 に光を照射する場合には、図 17 (A2) に示される透過率が得られる。

#### 【0185】

図 17 (B1) に示すハーフトーンマスク 410 は、透光性を有する基板 411 上に遮光性を有する材料層により形成された遮光部 412、および所定の透光性を有する材料層により形成された半透過部 413 で構成されている。

#### 【0186】

半透過部 413 は、MoSiN、MoSi、MoSiO、MoSiON、CrSi 等の材料層を用いて形成することができる。遮光部 412 は、グレートーンマスクの遮光部と同様の材料を用いて形成すればよい。なお、図 17 (B1) において、遮光部 412 は、所定の透光性を有する材料層と、遮光性を有する材料層の積層構造で形成されている。図 17 (B1) に示すハーフトーンマスク 410 に光を照射する場合には、図 17 (B2) に示される透過率が得られる。

10

#### 【0187】

上記のような多階調マスクを用いて、露光および現像を行うことで、膜厚の異なる領域を有するレジストマスク 105a を形成することができる。

#### 【0188】

導電層 102 および導電層 108 のエッティングには、ウエットエッティング、ドライエッティングのいずれを用いても良い。ただし、この段階においては、導電層 102 および導電層 108 が共にエッティングされることが必要である。当該エッティングにより、トランジスタのソース電極として機能する導電層 106a と、トランジスタのドレイン電極および保持容量の電極として機能する導電層 106b の形状が確定する。

20

#### 【0189】

次に、レジストマスク 105a を後退させてレジストマスク 111 を形成すると共に、レジストマスク 105b を除去し、レジストマスク 111 を用いて導電層 109a を選択的にエッティングして導電層 112 を形成し、あわせて導電層 109b を除去する（図 13 (C1)、図 13 (C2) 参照）。レジストマスク 105a を後退させる手段（およびレジストマスク 105b を除去する手段）としては、例えば、酸素プラズマを用いたアッシング処理などがあるが、上記手段はこれに限定する必要はない。

30

#### 【0190】

導電層 109a のエッティングおよび導電層 109b の除去には、ウエットエッティング、ドライエッティングのいずれを用いても良い。ただし、この段階においては、導電層 106a（導電層 106b）と、導電層 109a（導電層 109b）との選択比が取れる条件でエッティングを行う。つまり、当該エッティングによって導電層 106a および導電層 106b の形状が大きく変化しないことが重要になる。当該エッティングにより、トランジスタのソース配線として機能する導電層 112 の形状が確定する。ここで、導電層 112 は遮光性を有する材料を用いて形成されているため、遮光機能を有する。

#### 【0191】

なお、上記エッティングの後にはレジストマスク 111 は除去する。上記の各種導電層は、後に形成される絶縁層などの被覆性を向上し、段切れを防止するために、その端部がテーパー形状となるように形成することが好ましい。このように、導電層をテーパー形状となるように形成することで、半導体装置の歩留まり向上という課題を解決することができる。ひいては、半導体装置の製造コスト抑制につながる。

40

#### 【0192】

また、導電層 109a をエッティングして導電層 112 を形成する際に、後にコンタクトホールが形成される領域に導電層を形成しても良い（実施の形態 1 における図 7 (A)、図 7 (B) に対応）。このような構成を採用することで、コンタクトホールが形成される領域を遮光することができる。これにより、コンタクト領域における電極（画素電極）の表面凹凸による表示不具合を低減できるため、コントラストが向上する。つまり、表示特性

50

の向上という課題を解決することができる。なお、当該構成は液晶表示装置において特に効果的であるが、他の半導体装置に適用しても良いことは言うまでもない。この場合、遮光が必要な領域に導電層を適宜形成すれば良い。

#### 【0193】

次に、少なくとも導電層106aおよび導電層106bを覆うように半導体層114を形成する(図13(D1)、図13(D2)参照)。本実施の形態では、導電層106a、導電層106b、導電層112を覆うように、基板100上に半導体層114を形成する。半導体層114の詳細については実施の形態1を参照することができる。

#### 【0194】

なお、半導体層114を形成する前に、半導体層114の被形成面(例えば、導電層106aおよび導電層106bの表面、下地膜を形成した場合には下地膜の表面を含む)にプラズマ処理を行ってもよい。プラズマ処理を行うことにより、被形成面に付着しているゴミなどを除去することができる。また、上述のプラズマ処理を行った後、大気に曝すことなく半導体層114を形成することにより、導電層106aおよび導電層106bと、半導体層114との電気的接続を良好に行うことができる。つまり、半導体装置の歩留まり向上、信頼性向上といった課題を解決することができる。

#### 【0195】

次に、半導体層114上にレジストマスク116aおよびレジストマスク116bを形成し、当該レジストマスク116aおよびレジストマスク116bを用いて半導体層114を選択的にエッチングして、半導体層118aおよび半導体層118bを形成する(図14(A1)、図14(A2)参照)。該工程の詳細についても実施の形態1を参照することができる。

#### 【0196】

その後、200～600、代表的には300～500の熱処理を行うと良い。ここでは、窒素雰囲気下で350、1時間の熱処理を行う。この熱処理により半導体層118aおよび半導体層118bの半導体特性を向上させることができる。なお、上記熱処理のタイミングは、半導体層118aおよび半導体層118bの形成後であれば特に限定されない。

#### 【0197】

次に、半導体層118aおよび半導体層118bを覆うように、ゲート絶縁層120を形成する(図14(B1)、図14(B2)参照)。ゲート絶縁層120の詳細については、実施の形態1を参照することができる。

#### 【0198】

次に、ゲート絶縁層120上に、導電層122および導電層128を順に積層して形成する(図14(C1)、図14(C2)参照)。導電層122、導電層128の詳細については実施の形態1を参照することができる。

#### 【0199】

図示しないが、絶縁面を有する基板100上には下地膜を設けるとよい。下地膜の詳細についても実施の形態1を参照することができる。

#### 【0200】

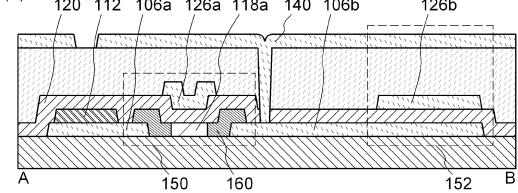

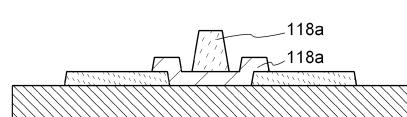

次に、導電層128上にレジストマスク117aおよびレジストマスク117bを形成し、当該レジストマスク117aおよびレジストマスク117bを用いて導電層122および導電層128を選択的にエッチングして、導電層126a、導電層126b、導電層129a、導電層129bを形成する(図15(A1)、図15(A2)参照)。

#### 【0201】

本実施の形態に係る半導体装置の作製方法と、実施の形態1に係る半導体装置の作製方法との相違点の一は、導電層122および導電層128のエッチング工程にある。本実施の形態においては、エッチング工程において用いるレジストマスク117aおよびレジストマスク117bを、多階調マスクを用いて形成している。多階調マスクその他の詳細については、レジストマスク105aおよびレジストマスク105bに係る記載を参照すれば

10

20

30

40

50

よい。

【0202】

多階調マスクを用いて露光および現像を行うことで、膜厚の異なる領域を有するレジストマスク117aを形成することができる。

【0203】

導電層122および導電層128のエッティングには、ウエットエッティング、ドライエッティングのいずれを用いても良い。ただし、この段階においては、導電層122および導電層128が共にエッティングされることが必要である。当該エッティングにより、トランジスタのゲート電極として機能する導電層126a、および保持容量の電極として機能する導電層126bの形状が確定する。

10

【0204】

次に、レジストマスク117aを後退させてレジストマスク131を形成すると共に、レジストマスク117bを除去し、レジストマスク131を用いて導電層129aを選択的にエッティングして導電層132aおよび導電層132bを形成し、あわせて導電層129bを除去する(図15(B1)、図15(B2)参照、導電層132bについては図12(A)参照)。レジストマスク117aを後退させる手段(およびレジストマスク117bを除去する手段)や、導電層129aのエッティング(導電層129bの除去)の詳細については、レジストマスク105aを後退させる手段(およびレジストマスク105bを除去する手段)や、導電層109aのエッティング(導電層109bの除去)の記載を参照することができる。なお、この段階においては、導電層126a(導電層126b)と、導電層129a(導電層129b)との選択比が取れる条件でエッティングを行う。つまり、当該エッティングによって導電層126aおよび導電層126bの形状が大きく変化しないことが重要になる。当該エッティングにより、トランジスタのゲート配線として機能する導電層132aおよび保持容量の配線として機能する導電層132bの形状が確定する。ここで、導電層132aは遮光性を有する材料を用いて形成されているため、遮光機能を有する。

20

【0205】

なお、上記エッティングの後にはレジストマスク131は除去する。上記の各種導電層は、後に形成される絶縁層などの被覆性を向上し、段切れを防止するために、その端部がテーパー形状となるように形成することが好ましい。このように、導電層をテーパー形状となるように形成することで、半導体装置の歩留まり向上という課題を解決することができる。

30

【0206】

なお、導電層106bと導電層126bとが重畳する領域の面積は適宜変更することができる。本実施の形態において示すように、導電層106bと導電層126bとは透光性を有する材料を用いて形成されているため、重畳する領域の面積を増大させて容量値を増加させる場合であっても、開口率を低下させずに済むという利点がある。つまり、容量値の増加という課題を、開口率の低下を伴わずに解決することができる。

【0207】

また、本実施の形態においては、ソース電極として機能する導電層106aおよびドレン電極として機能する導電層106bと、ゲート電極として機能する導電層126aの一部が重畳するように導電層106a、導電層106b、導電層126aを形成しているが、半導体層118aの一部の導電性を高めることができる場合には、導電層106aまたは導電層106bと、導電層126aとを重畳させない構成としても良い(実施の形態1における図9(A)、図9(B)に対応)。詳細については実施の形態1を参照することができる。このように、導電層106aまたは導電層106bと、導電層126aとを重畳させない構成とすることにより、導電層106a(または導電層106b)と導電層126aとの重畳に起因する寄生容量を低減することができる。つまり、半導体装置の特性向上という課題を解決することができる。

40

【0208】

50

また、導電層 126b 上に残存するように導電層 132b を形成しても良い（実施の形態 1 における図 11 (A)、図 11 (B) に対応）。このように、導電層 132b を形成することにより、容量配線の配線抵抗を低減することができる。なお、導電層 126b 上における導電層 132b の幅は、導電層 126b と比較して十分に小さくすることが好ましい。このように導電層 132b を形成することにより、容量配線の配線抵抗を低減するという課題を、実質的な開口率の低下なしに解決することができる。

#### 【0209】

次に、ゲート絶縁層 120、導電層 126a、導電層 126b、導電層 132a、導電層 132b を覆うように絶縁層 134 を形成する（図 15 (C1)、図 15 (C2) 参照）。絶縁層 134 の詳細については実施の形態 1 を参照することができる。

10

#### 【0210】

なお、絶縁層 134 が無くとも大きな不都合が生じない場合には、絶縁層 134 を形成しない構成とすることができる。この場合、工程を簡略化することができるというメリットがある。

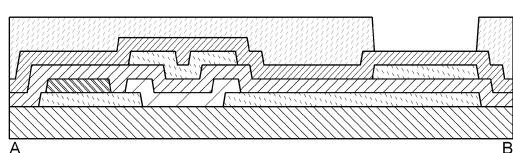

#### 【0211】

その後、絶縁層 134 に導電層 106b に達するコンタクトホール 136 を形成し、導電層 106b の表面の一部を露出させる（図 16 (A1)、図 16 (A2) 参照）。

#### 【0212】

そして、絶縁層 134 を覆うように、導電層 138 を形成する（図 16 (B1)、図 16 (B2) 参照）。絶縁層 134 にはコンタクトホールが形成されているため、導電層 106b と導電層 138 とは電気的に接続されることになる。導電層 138 の詳細については実施の形態 1 を参照することができる。

20

#### 【0213】

次に、導電層 138 上にレジストマスクを形成し、当該レジストマスクを用いて導電層 138 を選択的にエッチングして、導電層 140 を形成する（図 16 (C1)、図 16 (C2) 参照）。ここで、導電層 140 は、画素電極としての機能を有する。導電層 140 その他の詳細についても実施の形態 1 を参照することができる。

#### 【0214】

以上により、透光性を有するトランジスタ 150 および透光性を有する保持容量 152 を備えた半導体装置を作製することができる（図 16 (C1)、図 16 (C2) 参照）。

30

#### 【0215】

なお、本実施の形態においては、多階調マスクを用いて各種配線や電極を形成しているが、開示する発明の一態様はこれに限定して解釈されない。導電層 106a や導電層 112 の形成工程、または導電層 126a や導電層 132a の形成工程のいずれか一方のみを、多階調マスクを用いる方法で行っても良い。

#### 【0216】

本実施の形態では、多階調マスクを用いてレジストマスクを形成し、エッチングを行っている。このため、フォトマスクの使用数を抑え、工程数を減少させることができる。つまり、半導体装置の製造コストを抑制するという課題を解決することができる。

#### 【0217】

40

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

#### 【0218】

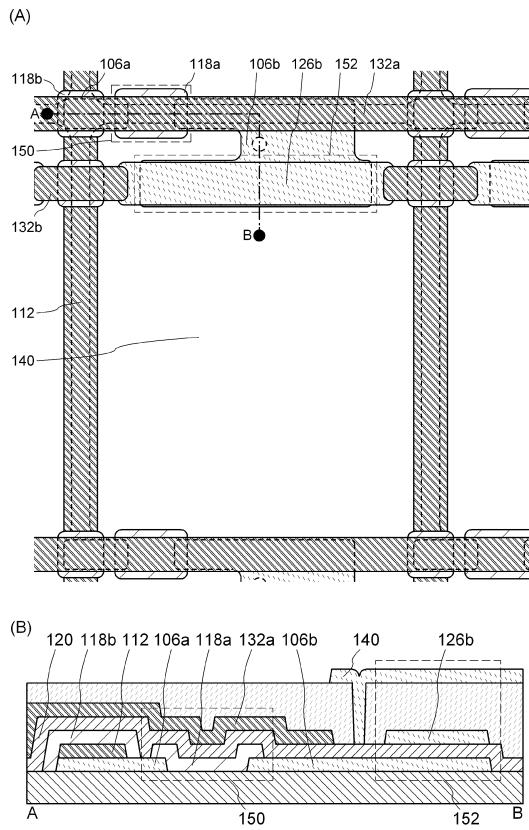

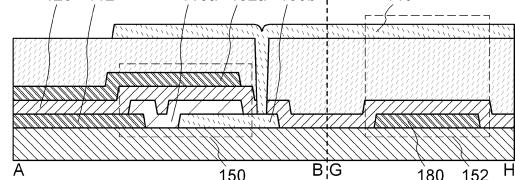

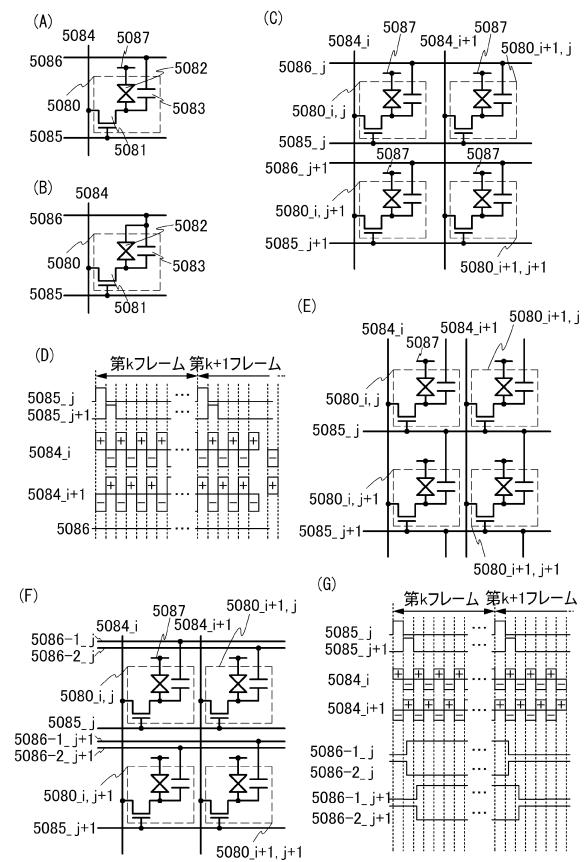

##### (実施の形態 3)

本実施の形態では、半導体装置の他の例について、図 18 乃至図 21 を用いて説明する。なお、本実施の形態に係る半導体装置は、多くの部分で実施の形態 1 に係る半導体装置と共通している。したがって、以下においては、重複する構成、重複する符号などの説明は省略する。

#### 【0219】

図 18 は、本実施の形態に係る半導体装置の構成の一例である。当該構成は、特に、エレクトロルミネッセンス表示装置（EL 表示装置）に用いるのに好適であるが、開示される

50

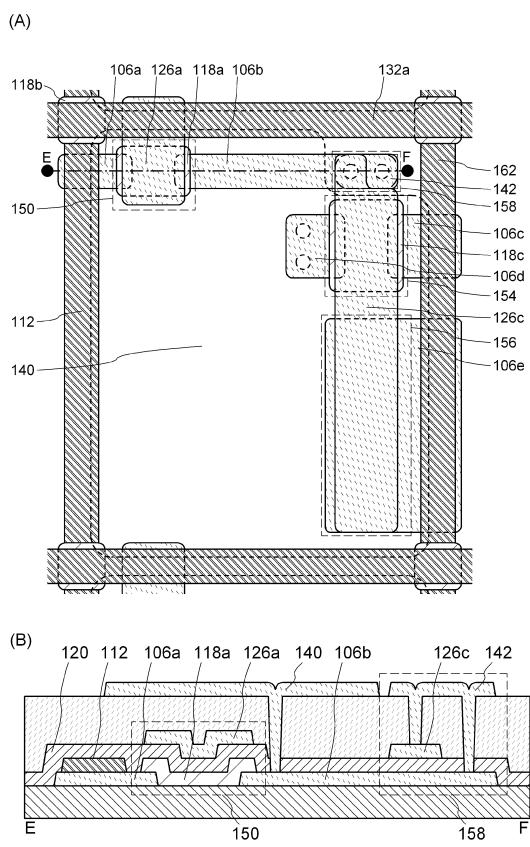

発明はこれに限定されない。なお、図18(A)は平面図であり、図18(B)は図18(A)のE-Fにおける断面図である。

#### 【0220】

図18(A)に示す半導体装置は、ソース配線として機能する導電層112と、導電層112と同様にして形成された電源配線として機能する導電層162と、導電層112および導電層162と交差し、ゲート配線として機能する導電層132aと、導電層132aと導電層112の交差部付近のトランジスタ150と、導電層162と電気的に接続されたトランジスタ154と、導電層162と電気的に接続された保持容量156と、を有する画素部を備えている(図18(A)、図18(B)参照)。なお、図18(A)において、導電層112および導電層162と、導電層132aとは90°の角度で交差しているが、開示する発明は当該構成に限定されない。

10

#### 【0221】

トランジスタ150は、ソース電極として機能する導電層106aと、ドレイン電極として機能する導電層106bと、半導体層118aと、ゲート絶縁層120と、ゲート電極として機能する導電層126aと、で構成されるいわゆるトップゲート型のトランジスタである(図18(A)、図18(B)参照)。同様に、トランジスタ154は、ソース電極として機能する導電層106cと、ドレイン電極として機能する導電層106dと、半導体層118cと、ゲート絶縁層120と、ゲート電極として機能する導電層126cと、で構成される。また、保持容量156は、導電層106eと、ゲート絶縁層120と、導電層126cと、で構成されている。なお、上記においても、ソース電極およびドレン電極の称呼は便宜的なものに過ぎない。

20

#### 【0222】

ここで、導電層112と導電層106aは電気的に接続されており、導電層106bと導電層126cとは、接続部158において、導電層142を介して電気的に接続されている(図18(A)、図18(B)参照)。また、導電層162と導電層106cは電気的に接続されており、導電層106dと導電層140は電気的に接続されており、導電層162と導電層106eは電気的に接続されている。なお、画素電極として機能する導電層140と導電層142とは同一の工程で作製することができる。また、導電層106dと導電層140とを接続するためのコンタクトホール、導電層106bと導電層142とを接続するためのコンタクトホール、導電層126cと導電層142とを接続するためのコンタクトホールは、同一の工程で作製することができる。

30

#### 【0223】

トランジスタ150を構成する導電層106a、導電層106b、半導体層118a、導電層126a、トランジスタ154を構成する導電層106c、導電層106d、半導体層118c、導電層126c、および保持容量156を構成する導電層106eは、透光性を有する材料で形成されている。これにより、画素の開口率向上が実現されている。

#### 【0224】

また、導電層112、導電層132a、および導電層162は、低抵抗材料で形成されている。このため、配線抵抗を低減し、消費電力を低減することができる。また、導電層112、導電層132a、および導電層162は、遮光性を有する材料で形成されている。このため、画素間を遮光することができる。

40

#### 【0225】

なお、上記においては、一つの画素に二つのトランジスタを有する場合について説明しているが、開示される発明はこれに限定されない。一つの画素に三つ以上のトランジスタを設けることもできる。

#### 【0226】

図19は、本実施の形態に係る半導体装置の構成の他の一例である。当該構成は、特に、エレクトロルミネッセンス表示装置(E-L表示装置)に用いるのに好適であるが、開示される発明はこれに限定されない。なお、図19(A)は平面図であり、図19(B)は図19(A)のE-Fにおける断面図である。

50

**【0227】**

図19に示される構成は、基本的には、図18に示される構成と同様である。図18に示される構成との相違点は接続部158にあり、図18では、導電層106bと導電層126cが導電層142を介して接続されているのに対して、図19では、導電層106bと導電層126cが直接接続されている(図19(A)、図19(B)参照)。この場合、導電層142が不要となるため、画素電極として機能する導電層140をより大きくすることが可能であり、図18に示される構成と比較して開口率を向上させることができる。なお、導電層106bと導電層126cとの電気的接続を実現するためには、導電層126cの形成前に、ゲート絶縁層120に対してコンタクトホールを形成しておく必要がある。

10

**【0228】**

図20は、本実施の形態に係る半導体装置の構成の他の一例である。当該構成は、表示装置に用いるのに好適であるが、開示される発明はこれに限定されない。なお、図20(A)は平面図であり、図20(B)は図20(A)のA-Bにおける断面図である。

**【0229】**

図20に示される構成は、基本的には、図1に示される構成と同様である。図1に示される構成との相違点は、ソース電極として機能する導電層106aとドレイン電極として機能する導電層106bの形状にある。より具体的には、図20に示される構成において、チャネル形成領域の形状がU字型となるように導電層106aと導電層106bが形成されている(図20(A)、図20(B)参照)。これにより、同じ面積のトランジスタを形成する場合でも、チャネル幅(W)を大きくすることが可能である。なお、チャネル形成領域の形状はU字型に限定されず、求められるチャネル幅に応じて適宜その形状を変更することができる。

20

**【0230】**

図21は、本実施の形態に係る半導体装置の構成の他の一例である。当該構成は、表示装置に用いるのに好適であるが、開示される発明はこれに限定されない。なお、図21(A)は平面図であり、図21(B)は図21(A)のA-Bにおける断面図である。

**【0231】**

図21に示される構成は、図1に示される構成と類似している。図1に示される構成との相違点は、ゲート配線として機能する導電層132aがゲート電極としても機能する点にある(図21(A)、図21(B)参照)。つまり、図21においては、導電層126aに対応する導電層が存在しない。導電層132aは低抵抗材料を用いて形成することができるから、ゲート電極として導電層126a(透光性材料を用いた導電層)を用いる場合と比較して、半導体層118aに対する電界を一様なものとすることができます。このため、トランジスタ150の素子特性を向上させることができる。

30

**【0232】**

なお、図21においては、導電層126aを設けない構成を採用しているが、開示される発明はこれに限定されない。導電層132aと電気的に接続された導電層126aを設けても良い。また、図21においては導電層106aを形成しているが、導電層106aを設けずに、導電層106aの機能を導電層112に兼ねさせてても良い。これは、ソース電極の機能を有する導電層が、ゲート配線として機能する導電層の下部に形成されることになるため、透光性を有する材料を用いてソース電極として機能する導電層を形成する必要性が低下することによる。この場合、少なくとも導電層106bと、導電層126bとを、透光性を有する材料によって形成すればよい。

40

**【0233】**

また、本実施の形態に係る構成を、多階調マスクを用いる場合に採用することができるのではない。多階調マスクを用いる場合には、導電層126aが導電層132aの下部に形成される。

**【0234】**

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

50

**【0235】**

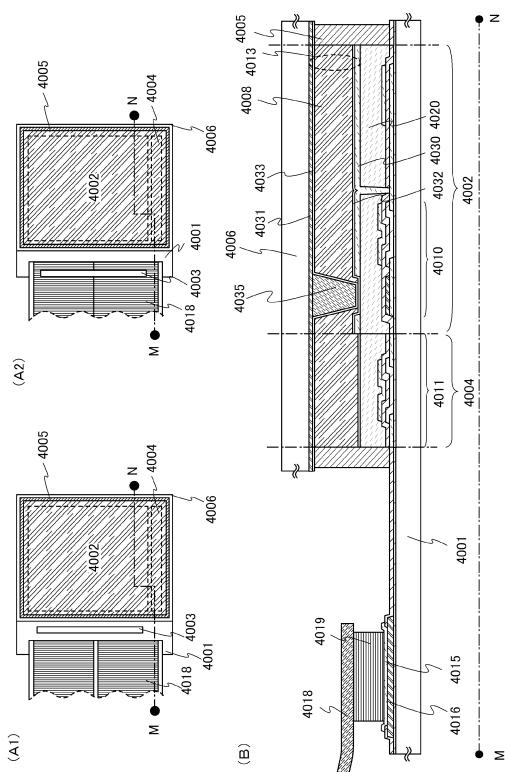

(実施の形態4)

本実施の形態では、薄膜トランジスタを作製し、該薄膜トランジスタを、画素部や周辺回路部（駆動回路など）に用いて表示機能を有する半導体装置（表示装置）を作製する場合について説明する。周辺回路部の一部または全部を、画素部と同じ基板上に一体形成することにより、システムオンパネルを形成することができる。

**【0236】**

表示装置は表示素子を含む。表示素子としては液晶素子（液晶表示素子ともいう）や、発光素子（発光表示素子ともいう）などを用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL（E1e 10 control Luminescence）、有機EL等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体を適用しても良い。

**【0237】**

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。さらに、表示装置を構成する素子基板は、電流を表示素子に供給するための手段を各画素に備える。素子基板は、具体的には、表示素子の画素電極が形成された状態であっても良いし、画素電極となる導電層の成膜後、エッチング前の状態であっても良い。

**【0238】**

以下、本実施の形態では、液晶表示装置の一例について示す。図22は、第1の基板4001上に形成された薄膜トランジスタ4010、薄膜トランジスタ4011および液晶素子4013を、第2の基板4006とシール材4005によって封止した、パネルの平面図および断面図である。ここで、図22(A1)および図22(A2)は平面図を示し、図22(B)は、図22(A1)および図22(A2)のM-Nにおける断面図に相当する。

20

**【0239】**

第1の基板4001上に設けられた画素部4002および走査線駆動回路4004を囲むようにして、シール材4005が設けられている。また、画素部4002と走査線駆動回路4004の上に、第2の基板4006が設けられている。つまり、画素部4002と走査線駆動回路4004は、第1の基板4001とシール材4005と第2の基板4006とによって、液晶層4008と共に封止されている。また、第1の基板4001上のシール材4005によって囲まれる領域とは異なる領域に、別途用意された基板上に単結晶半導体または多結晶半導体で形成された信号線駆動回路4003が実装されている。

30

**【0240】**

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG法、ワイヤボンディング法、TAB法などを適宜用いることができる。図22(A1)は、COG法により信号線駆動回路4003を実装する例であり、図22(A2)は、TAB法により信号線駆動回路4003を実装する例である。

**【0241】**

また、第1の基板4001上に設けられた画素部4002と走査線駆動回路4004は、薄膜トランジスタを複数有しており、図22(B)では、画素部4002に含まれる薄膜トランジスタ4010と、走査線駆動回路4004に含まれる薄膜トランジスタ4011を例示している。薄膜トランジスタ4010、薄膜トランジスタ4011上には絶縁層4020が設けられている。

40

**【0242】**

薄膜トランジスタ4010、薄膜トランジスタ4011には、先の実施の形態などに示すトランジスタを適用することができる。なお、本実施の形態において、薄膜トランジスタ4010、薄膜トランジスタ4011はnチャネル型トランジスタとした。

**【0243】**

また、液晶素子4013が有する画素電極層4030は、薄膜トランジスタ4010と電

50

気的に接続されている。そして、液晶素子 4013 の対向電極層 4031 は第 2 の基板 4006 上に形成されている。上記の画素電極層 4030 と対向電極層 4031、液晶層 4008 により、液晶素子 4013 が形成される。なお、画素電極層 4030、対向電極層 4031 には、それぞれ配向膜として機能する絶縁層 4032、絶縁層 4033 が設けられ、画素電極層 4030 および対向電極層 4031 は、これらを介して液晶層 4008 を挟持している。

#### 【0244】

なお、第 1 の基板 4001、第 2 の基板 4006 としては、ガラス、金属（代表的にはステンレス）、セラミックス、プラスチックなどを用いることができる。プラスチックとしては、FRP (Fiberglass-Reinforced Plastics) 基板、PVF (ポリビニルフルオライド) フィルム、ポリエステルフィルム、アクリル樹脂フィルムなどを用いることができる。また、アルミニウム箔を PVF フィルムやポリエステルフィルムで挟んだ構造のシートを用いることもできる。10

#### 【0245】

また、画素電極層 4030 と対向電極層 4031 との間の距離（セルギャップ）を制御するために、柱状のスペーサ 4035 が設けられている。柱状のスペーサ 4035 は絶縁膜を選択的にエッチングすることで得られる。なお、柱状のスペーサに代えて球状のスペーサを用いていても良い。また、対向電極層 4031 は、薄膜トランジスタ 4010 と同一基板上に設けられる共通電位線と電気的に接続される。例えば、一対の基板間に配置される導電性粒子を介して、対向電極層 4031 と共通電位線とを電気的に接続することができる。なお、導電性粒子はシール材 4005 に含有させると良い。20

#### 【0246】

また、配向膜が不要なブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、昇温によってコレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、5重量%以上のカイラル剤を混合させた液晶組成物を用いると良い。これにより、温度範囲を改善することができる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答時間が  $10 \mu s \sim 100 \mu s$  と短く、光学的等方性を有するため配向処理が不要であり、視野角依存性が小さい、といった特徴を有している。

#### 【0247】

なお、本実施の形態では透過型液晶表示装置の一例を示しているが、これに限定されず、反射型液晶表示装置としても良いし、半透過型液晶表示装置としても良い。30

#### 【0248】

また、本実施の形態で示す液晶表示装置では、基板の外側（視認側）に偏光板を設け、内側に着色層、および表示素子に用いる電極層を設ける例について示すが、偏光板は基板の内側に設けてもよい。また、偏光板と着色層の積層構造も本実施の形態に限定されず、偏光板及び着色層の材料や作製工程条件によって適宜設定すればよい。また、遮光膜として、ブラックマスク（ブラックマトリクス）を設けてもよい。

#### 【0249】

また、本実施の形態では、薄膜トランジスタの表面凹凸を低減するため、先の実施の形態で得られた薄膜トランジスタを絶縁層 4020 で覆う構成を採用しているが、開示される発明はこれに限定されない。40

#### 【0250】

絶縁層 4020 としては、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k 材料）、シロキサン系樹脂、PSG (リンガラス)、BPSG (リンボロンガラス) 等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させて、絶縁層 4020 を形成してもよい。

#### 【0251】

ここで、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成された Si-O50

- S i 結合を含む樹脂に相当する。置換基としては、有機基（例えばアルキル基やアリール基）やフルオロ基を用いても良い。また、有機基はフルオロ基を有していても良い。

#### 【 0 2 5 2 】

絶縁層 4 0 2 0 の形成方法は、特に限定されず、その材料に応じて、スパッタ法、S O G 法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。

#### 【 0 2 5 3 】

画素電極層 4 0 3 0 、対向電極層 4 0 3 1 は、酸化タンゲスタンを含むインジウム酸化物、酸化タンゲスタンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（ITOともいう）、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

#### 【 0 2 5 4 】

また、画素電極層 4 0 3 0 、対向電極層 4 0 3 1 に、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いても良い。導電性組成物を用いて形成した画素電極は、シート抵抗が  $1 . 0 \times 10^4 / \text{sq}$  以下、波長 550 nm における透光率が 70 % 以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率は 0 . 1 · cm 以下であることが好ましい。

#### 【 0 2 5 5 】

導電性高分子としては、いわゆる 電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの 2 種以上の共重合体などがあげられる。

#### 【 0 2 5 6 】

信号線駆動回路 4 0 0 3 、走査線駆動回路 4 0 0 4 、画素部 4 0 0 2 などに与えられる各種信号は、F P C 4 0 1 8 から供給されている。

#### 【 0 2 5 7 】

また、接続端子電極 4 0 1 5 は、液晶素子 4 0 1 3 が有する画素電極層 4 0 3 0 と同じ導電膜から形成され、端子電極 4 0 1 6 は、薄膜トランジスタ 4 0 1 0 、薄膜トランジスタ 4 0 1 1 のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

#### 【 0 2 5 8 】

接続端子電極 4 0 1 5 は、F P C 4 0 1 8 が有する端子と、異方性導電膜 4 0 1 9 を介して電気的に接続されている。

#### 【 0 2 5 9 】

なお、図 2 2 においては、信号線駆動回路 4 0 0 3 を別途形成し、第 1 の基板 4 0 0 1 に実装する例を示しているが、本実施の形態はこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

#### 【 0 2 6 0 】

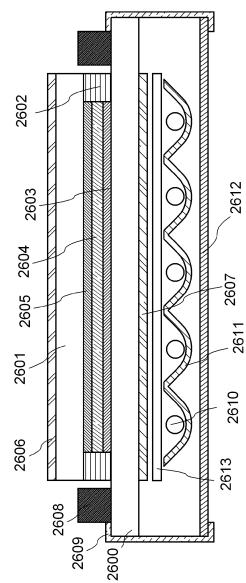

図 2 3 は、半導体装置の一形態に相当する液晶表示モジュールに、T F T 基板 2 6 0 0 を用いる例を示している。

#### 【 0 2 6 1 】

図 2 3 では、T F T 基板 2 6 0 0 と対向基板 2 6 0 1 がシール材 2 6 0 2 により固着され、その間にT F T 等を含む素子層 2 6 0 3 、配向膜や液晶を含む液晶層 2 6 0 4 、着色層 2 6 0 5 などが設けられることにより表示領域が形成されている。着色層 2 6 0 5 はカラー表示を行う場合に必要であり、R G B 方式の場合には、赤、緑、青の各色に対応した着色層が、各画素に対応して設けられている。T F T 基板 2 6 0 0 と対向基板 2 6 0 1 の外側には偏光板 2 6 0 6 、偏光板 2 6 0 7 、拡散板 2 6 1 3 が配設されている。また、光源は冷陰極管 2 6 1 0 と反射板 2 6 1 1 により構成されている。回路基板 2 6 1 2 は、フレキシブル配線基板 2 6 0 9 によりT F T 基板 2 6 0 0 の配線回路部 2 6 0 8 と接続され、

10

20

30

40

50

これによって、コントロール回路や電源回路などの外部回路が液晶モジュールに組みこまれる。また、偏光板と液晶層との間には、位相差板を設けても良い。

#### 【0262】

液晶の駆動方式としては、TN (Twisted Nematic) モード、IPS (In-Plane-Switching) モード、FFS (Fringe Field Switching) モード、MVA (Multi-domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment) モード、ASM (Axially Symmetric aligned Micro-cell) モード、OCB (Optical Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、AFLC (AntiFerroelectric Liquid Crystal) モードなどを用いることができる。10

#### 【0263】

以上の工程により、高性能な液晶表示装置を作製することができる。本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

#### 【0264】

##### (実施の形態5)

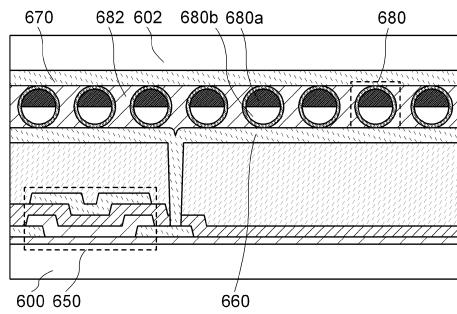

本実施の形態では、図24を参照して半導体装置の一例であるアクティブマトリクス型の電子ペーパーについて説明する。半導体装置に用いられる薄膜トランジスタ650は、先の実施の形態で示す薄膜トランジスタと同様に作製することができる。20

#### 【0265】

図24に示す電子ペーパーは、ツイストボール表示方式を用いたものの一例である。ツイストボール表示方式とは、白と黒に塗り分けられた球形粒子を第1の電極層及び第2の電極層の間に配置し、第1の電極層及び第2の電極層に電位差を生じさせることによって、球形粒子の向きを制御して、表示を行う方法である。

#### 【0266】

基板600上に設けられた薄膜トランジスタ650は開示する発明の薄膜トランジスタであり、半導体層が、その上方のゲート電極層と、その下方のソース電極層またはドレイン電極層とによって挟まれた構造を有している。なお、ソース電極層またはドレイン電極層は、絶縁層に形成されたコンタクトホールを介して、第1の電極層660と電気的に接続している。基板602には第2の電極層670が設けられており、第1の電極層660と第2の電極層670との間には、黒色領域680a及び白色領域680bを有する球形粒子680が設けられている。また、球形粒子680の周囲は樹脂等の充填材682で満たされている(図24参照)。図24において、第1の電極層660が画素電極に相当し、第2の電極層670が共通電極に相当する。第2の電極層670は、薄膜トランジスタ650と同一基板上に設けられる共通電位線と電気的に接続される。30

#### 【0267】

ツイストボールの代わりに、電気泳動表示素子を用いることも可能である。その場合、例えば、透明な液体と、正に帯電した白い微粒子と負に帯電した黒い微粒子とを封入した直径 $10\mu m \sim 200\mu m$ 程度のマイクロカプセルを用いる。第1の電極層と第2の電極層によって電場が与えられると、白い微粒子と黒い微粒子が互いに逆方向に移動し、白または黒が表示される。電気泳動表示素子は液晶表示素子に比べて反射率が高いため、補助ライトが不要であり、また、明るさが十分ではない場所であっても表示部を認識することが可能である。また、表示部に電源が供給されない場合であっても、一度表示した像を保持することが可能であるという利点を有している。40

#### 【0268】

以上のように、開示する発明を用いることで高性能な電子ペーパーを作製することができる。なお、本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

#### 【0269】

##### (実施の形態6)

10

20

30

40

50

本実施の形態では、半導体装置として発光表示装置の例を示す。表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

#### 【0270】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア（電子および正孔）が再結合することにより発光する。このようなメカニズムから、該発光素子は、電流励起型の発光素子と呼ばれる。

10

#### 【0271】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー・アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。

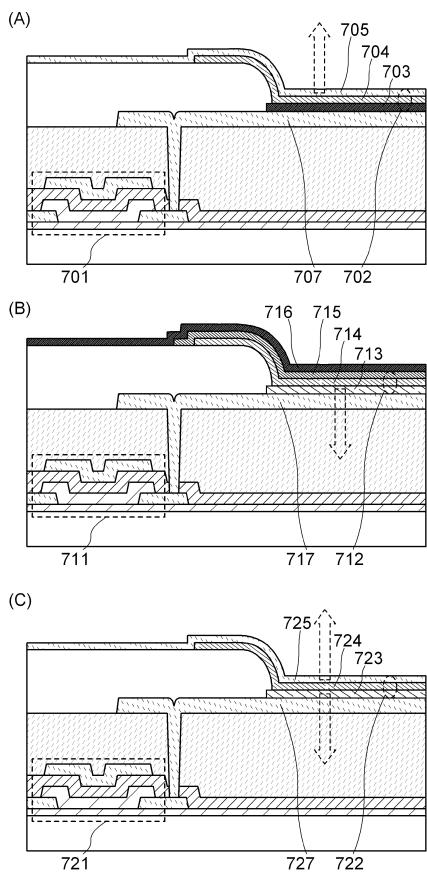

#### 【0272】

発光素子の構成について、図25を用いて説明する。ここでは、駆動用TFTがn型の場合を例に挙げて、画素の断面構造について説明する。図25(A)、図25(B)、図25(C)の半導体装置に用いられるTFT701、TFT711、TFT721は、先の実施の形態で示す薄膜トランジスタと同様に作製することができる。

20

#### 【0273】

発光素子は、光を取り出すために、陽極または陰極の少なくとも一方が透明になっている。ここで、透明とは、少なくとも発光波長における透過率が十分に高いことを意味する。光の取り出し方式としては、基板上に薄膜トランジスタ及び発光素子を形成し、該基板とは反対側の面から光を取り出す上面射出方式（上面取り出し方式）や、基板側の面から光を取り出す下面射出方式（下面取り出し方式）、基板側およびその反対側の面から光を取り出す両面射出方式（両面取り出し方式）などがある。

30

#### 【0274】

上面射出方式の発光素子について図25(A)を参照して説明する。

#### 【0275】

図25(A)は、発光素子702から発せられる光が陽極705側に抜ける場合の、画素の断面図を示している。ここでは、駆動用TFT701と電気的に接続された透光性を有する導電層707上に、発光素子702が形成されており、陰極703上に発光層704、陽極705が順に積層されている。陰極703としては、仕事関数が小さく、光を反射する導電膜を用いることができる。例えば、Ca、Al、MgAg、AlLi等の材料を用いて陰極703を形成することが望ましい。発光層704は、単層で構成されていても、複数の層が積層されるように構成されていても良い。複数の層で構成されている場合、陰極703上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層すると良いが、もちろん、これらの層を全て設ける必要はない。陽極705は光を透過する導電性材料を用いて形成する。例えば、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(ITOともいう)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いれば良い。

40

#### 【0276】

陰極703及び陽極705で発光層704を挟んだ構造を、発光素子702と呼ぶことができる。図25(A)に示した画素の場合、発光素子702から発せられる光は、矢印で

50

示すように陽極 705 側に射出される。発光素子 702 の構造は、マイクロキャビティ構造としても良い。これにより、取り出し波長を選択することが可能となるため、色純度を向上させることができる。なお、この場合には、取り出し波長にあわせて発光素子 702 を構成する各層の厚みを設定することになる。また、所定の反射率を有する材料を用いて電極を形成すると良い。

#### 【0277】

陽極 705 の上には、窒化シリコン、酸化シリコンなどを含む絶縁層を形成しても良い。これにより、発光素子の劣化を抑制することができる。

#### 【0278】

次に、下面射出方式の発光素子について図 25 (B) を参照して説明する。

10

#### 【0279】

図 25 (B) は、発光素子 712 から発せられる光が陰極 713 側に抜ける場合の、画素の断面図を示している。ここでは、駆動用 TFT711 と電気的に接続された透光性を有する導電層 717 上に、発光素子 712 の陰極 713 が形成されており、陰極 713 上に発光層 714、陽極 715 が順に積層されている。なお、陽極 715 が透光性を有する場合、該陽極 715 上を覆うように遮光膜 716 を設けても良い。陰極 713 は、図 25 (A) の場合と同様に、仕事関数が小さい導電性材料を用いることができる。ただしその膜厚は、光を透過する程度（好ましくは、5 nm ~ 30 nm 程度）とする。例えば 20 nm 程度の膜厚を有するアルミニウム膜を、陰極 713 として用いることができる。発光層 714 は、図 25 (A) と同様に、単層で構成されていても、複数の層が積層されるように構成されていても良い。陽極 715 は、光を透過する必要はないが、図 25 (A) と同様に、透光性を有する導電性材料を用いて形成しても良い。遮光膜 716 には、光を反射する金属等を用いることができるが、これに限定されない。なお、遮光膜 716 に反射機能を有せしめることにより、光の取り出し効率を向上させることができる。

20

#### 【0280】

陰極 713 及び陽極 715 で、発光層 714 を挟んだ構造を発光素子 712 と呼ぶことができる。図 25 (B) に示した画素の場合、発光素子 712 から発せられる光は、矢印で示すように陰極 713 側に射出される。発光素子 712 の構造は、マイクロキャビティ構造としても良い。また、陽極 715 の上には絶縁層を形成しても良い。

#### 【0281】

30

次に、両面射出方式の発光素子について、図 25 (C) を参照して説明する。

#### 【0282】

図 25 (C) は、駆動用 TFT721 と電気的に接続された透光性を有する導電層 727 上に、発光素子 722 の陰極 723 が形成されており、陰極 723 上に発光層 724、陽極 725 が順に積層されている。陰極 723 は、図 25 (A) の場合と同様に、仕事関数が小さい導電性材料を用いることができる。ただしその膜厚は、光を透過する程度とする。例えば 20 nm の膜厚を有するアルミニウム膜を、陰極 723 として用いることができる。発光層 724 は、図 25 (A) と同様に、単層で構成されていても、複数の層が積層されるように構成されていても良い。陽極 725 は、図 25 (A) と同様に、透光性を有する導電性材料を用いて形成することができる。

40

#### 【0283】

陰極 723 と、発光層 724 と、陽極 725 とが重なった構造を発光素子 722 と呼ぶことができる。図 25 (C) に示した画素の場合、発光素子 722 から発せられる光は、矢印で示すように陽極 725 側と陰極 723 側の両方に射出される。発光素子 722 の構造は、マイクロキャビティ構造としても良い。また、陽極 725 の上には絶縁層を形成しても良い。

#### 【0284】

なお、ここでは、発光素子として有機 EL 素子について述べたが、発光素子として無機 EL 素子を設けることも可能である。また、ここでは、発光素子の駆動を制御する薄膜トランジスタ（駆動用 TFT）と発光素子が電気的に接続されている例を示したが、駆動用 T

50

F Tと発光素子との間に電流制御用T F Tが接続されている構成であってもよい。

**【0285】**

なお、本実施の形態で示す半導体装置は、図25に示した構成に限定されるものではなく、各種の変形が可能である。

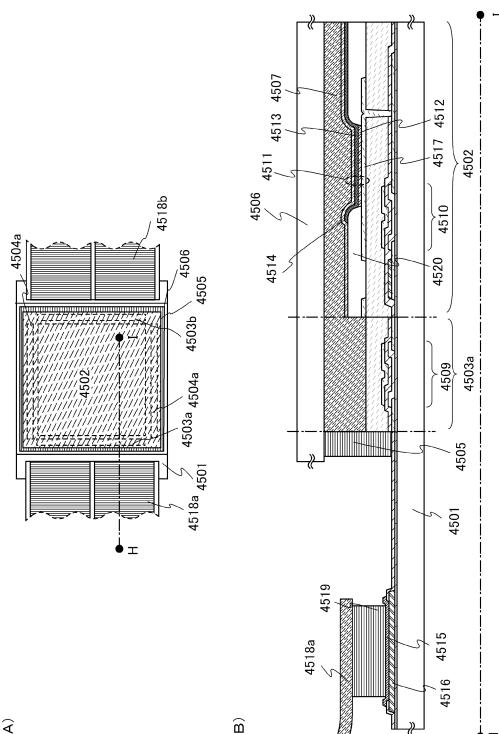

**【0286】**

次に、半導体装置の一形態に相当する発光表示パネル（発光パネルともいう）の外観及び断面について、図26を参照して説明する。図26は、第1の基板4501上に形成された薄膜トランジスタ4509、薄膜トランジスタ4510および発光素子4511を、第2の基板4506とシール材4505によって封止したパネルの平面図および断面図である。ここで、図26(A)は平面図を示し、図26(B)は、図26(A)のH-Iにおける断面図に相当する。10

**【0287】**

第1の基板4501上に設けられた画素部4502、信号線駆動回路4503a、信号線駆動回路4503b、走査線駆動回路4504a、走査線駆動回路4504bを囲むようにして、シール材4505が設けられている。また、画素部4502、信号線駆動回路4503a、信号線駆動回路4503b、走査線駆動回路4504a、走査線駆動回路4504bの上に第2の基板4506が設けられている。つまり、画素部4502、信号線駆動回路4503a、信号線駆動回路4503b、走査線駆動回路4504a、走査線駆動回路4504bは、第1の基板4501とシール材4505と第2の基板4506とによって、充填材4507と共に密封されている。このように、気密性が高く、脱ガスの少ない保護フィルム（貼り合わせフィルム、紫外線硬化樹脂フィルム等）やカバー材などを用いてパッケージング（封入）することが好ましい。20

**【0288】**

また、第1の基板4501上に設けられた画素部4502、信号線駆動回路4503a、信号線駆動回路4503b、走査線駆動回路4504a、走査線駆動回路4504bは、薄膜トランジスタを複数有しており、図26(B)では、画素部4502に含まれる薄膜トランジスタ4510と、信号線駆動回路4503aに含まれる薄膜トランジスタ4509を例示している。

**【0289】**

薄膜トランジスタ4509、薄膜トランジスタ4510は、先の実施の形態において示したトランジスタを適用することができる。なお、本実施の形態において、薄膜トランジスタ4509、薄膜トランジスタ4510はnチャネル型トランジスタである。30

**【0290】**

また、4511は発光素子に相当し、発光素子4511が有する画素電極である第1の電極層4517は、薄膜トランジスタ4510のソース電極層またはドレイン電極層と電気的に接続されている。なお、発光素子4511の構成は、第1の電極層4517、第2の電極4512、電界発光層4513、第3の電極層4514の積層構造であるが、本実施の形態に示した構成に限定されない。発光素子4511から取り出す光の方向などに合わせて、上記構成は適宜変更することができる。

**【0291】**

隔壁4520は、有機樹脂膜、無機絶縁膜、有機ポリシリコンなどを用いて形成する。特に、感光性を有する材料を用いて第1の電極層4517上に開口部を形成し、その開口部の側壁が、連続した曲率を持つ傾斜面となるようにすることが好ましい。

**【0292】**

電界発光層4513は、単層で構成されていても、複数の層が積層されるように構成されても良い。

**【0293】**

発光素子4511に酸素、水素、水、二酸化炭素等が侵入しないように、第3の電極層4514及び隔壁4520上に保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、DLC膜等を形成することができる。50

**【 0 2 9 4 】**

また、信号線駆動回路 4 5 0 3 a、信号線駆動回路 4 5 0 3 b、走査線駆動回路 4 5 0 4 a、走査線駆動回路 4 5 0 4 b、画素部 4 5 0 2 などに与えられる各種信号は、F P C 4 5 1 8 a、F P C 4 5 1 8 b から供給されている。

**【 0 2 9 5 】**

本実施の形態では、接続端子電極 4 5 1 5 が、発光素子 4 5 1 1 の第 1 の電極層 4 5 1 7 と同じ導電膜から形成され、端子電極 4 5 1 6 は、薄膜トランジスタ 4 5 0 9 や薄膜トランジスタ 4 5 1 0 のソース電極層及びドレイン電極層と同じ導電膜から形成される例について示している。

**【 0 2 9 6 】**

接続端子電極 4 5 1 5 は、F P C 4 5 1 8 a が有する端子と、異方性導電膜 4 5 1 9 を介して電気的に接続されている。

**【 0 2 9 7 】**

発光素子 4 5 1 1 からの光の取り出し方向に位置する基板は、透光性を有さなければならぬ。透光性を有する基板としては、ガラス板、プラスチック板、ポリエステルフィルム、アクリルフィルムなどがある。

**【 0 2 9 8 】**

充填材 4 5 0 7 としては、窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂や熱硬化樹脂などを用いることができる。例えば、P V C (ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、P V B (ポリビニルブチラル)、E V A (エチレンビニルアセテート)などを用いることができる。本実施の形態では、充填材として窒素を用いる例について示している。

**【 0 2 9 9 】**

必要であれば、発光素子の射出面に偏光板、円偏光板（楕円偏光板を含む）、位相差板（1/4 板、1/2 板）、カラーフィルタなどの光学フィルムを設けてもよい。また、表面には反射防止処理を施しても良い。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

**【 0 3 0 0 】**