(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4724413号

(P4724413)

(45) 発行日 平成23年7月13日(2011.7.13)

(24) 登録日 平成23年4月15日(2011.4.15)

|                     |                |

|---------------------|----------------|

| (51) Int.Cl.        | F 1            |

| HO4N 1/46 (2006.01) | HO4N 1/46 Z    |

| GO6T 1/00 (2006.01) | GO6T 1/00 510  |

| GO6T 1/60 (2006.01) | GO6T 1/60 450G |

| HO4N 1/60 (2006.01) | HO4N 1/40 D    |

| HO4N 9/67 (2006.01) | HO4N 9/67 Z    |

請求項の数 7 (全 25 頁)

(21) 出願番号 特願2004-342262 (P2004-342262)

(22) 出願日 平成16年11月26日 (2004.11.26)

(65) 公開番号 特開2006-157252 (P2006-157252A)

(43) 公開日 平成18年6月15日 (2006.6.15)

審査請求日 平成19年11月19日 (2007.11.19)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 伊藤 忠幸

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 豊田 好一

最終頁に続く

(54) 【発明の名称】データ分類方法

## (57) 【特許請求の範囲】

## 【請求項 1】

N 次元直交座標 (Nは4以上の整数) 上の各単位超立体の頂点に対応するデータを格納した  $(M+1) \times 2^{(N-M)}$  個のサブメモリ (MはNより小さい整数) のいずれかから前記対応するデータを読み出すために、前記 N 次元直交座標上の各単位超立体の頂点を  $(M+1) \times 2^{(N-M)}$  通りのいずれかに分類する方法であって、

それが複数のビットで表わされる N 個の成分からなる頂点の座標値のうち M 個の成分を選択する選択工程と、

前記選択工程により選択された M 個の成分の総和を算出する第 1 の算出工程と、

前記第 1 の算出工程により算出された総和を、  $(M+1)$  で割った余りを算出する第 2 の算出工程と、 10

前記選択工程により選択されなかった  $(N-M)$  個の成分のそれぞれの所定のビット位置の値によりなる整数を  $(M+1)$  倍した結果を、前記第 2 の算出工程により算出された余りに加算して、前記頂点を  $(M+1) \times 2^{(N-M)}$  個のグループのいずれかに分類するための指標値を算出する第 3 の算出工程と、

前記第 3 の算出工程により算出された指標値が示すグループに前記頂点を分類する分類工程とを有することを特徴とするデータ分類方法。

## 【請求項 2】

N 次元直交座標 (Nは4以上の整数) 上の各単位超立体の頂点に対応するデータを格納した  $(M+1) \times 2^{(N-M)}$  個のサブメモリ (MはNより小さい整数) のいずれかから前記

対応するデータを読み出すために、前記N次元直交座標上の各単位超立体の頂点を $(M+1) \times 2^{(N-M)}$ 通りのいずれかに分類する方法であって、

それがN個の成分からなる頂点の座標値のうちM個の成分を選択する選択工程と、

前記選択工程により選択されたM個の成分の総和を算出する第1の算出工程と、

前記第1の算出工程により算出された総和を、 $(M+1)$ で割った余りを算出する第2の算出工程と、

前記選択工程により選択されなかった $(N-M)$ 個の成分のそれが奇数か偶数かを示す値によりなる整数を $(M+1)$ 倍した結果を、前記第2の算出工程により算出された余りに加算して、前記頂点を $(M+1) \times 2^{(N-M)}$ 個のグループのいずれかに分類するための指標値を算出する第3の算出工程と、 10

前記第3の算出工程により算出された指標値が示すグループに、前記頂点を分類する分類工程とを有することを特徴とするデータ分類方法。

#### 【請求項3】

前記第3の算出工程は、以下の式を用いて指標値 $i_d$ を算出することを特徴とする請求項1又は2に記載のデータ分類方法。ここで、前記式は、

#### 【数1】

$$i_d = [\sum_{j=0}^{M-1} X_j] \% (M+1) + (M+1) \times \sum_{j=M}^{N-1} \{ (X_j \% 2) << (j-M) \}$$

10

20

である。

ただし、%は、割り算の余りであることを表す。

#### 【請求項4】

前記Mは3であり、

前記分類工程は、前記頂点を、 $2^{N-1}$ 個のグループに分類することを特徴とする請求項1又は2に記載のデータ分類方法。

#### 【請求項5】

前記Mは $(N-1)$ であり、

前記分類工程は、前記頂点を、 $(N \times 2)$ 個のグループに分類することを特徴とする請求項1又は2に記載のデータ分類方法。 30

#### 【請求項6】

N次元直交座標（Nは4以上の整数）上の各単位超立体の頂点に対応するデータを格納した $(M+1) \times 2^{(N-M)}$ 個のサブメモリ（MはNより小さい整数）のいずれかから前記対応するデータを読み出すために、前記N次元直交座標上の各単位超立体の頂点を $(M+1) \times 2^{(N-M)}$ 通りのいずれかに分類する方法であって、

それが複数のビットで表わされるN個の成分からなる頂点の座標値のうちM個の成分を選択する選択工程と、

前記選択工程により選択されたM個の成分の総和と、前記選択工程により選択されなかった $(N-M)$ 個の成分のそれぞれの所定のビット位置の値によりなる整数を $(M+1)$ 倍した結果とを加算する第1の算出工程と、 40

前記第1の算出工程による加算の結果を、 $(M+1) \times 2^{(M-N)}$ で割った余りを算出する第2の算出工程と、

前記第2の算出工程により算出された余りを、前記頂点を $(M+1) \times 2^{(N-M)}$ 個のグループのいずれかに分類するための指標値として用いて、前記頂点を前記指標値が示すグループに分類する分類工程とを有することを特徴とするデータ分類方法。

#### 【請求項7】

N次元直交座標（Nは4以上の整数）上の各単位超立体の頂点に対応するデータを格納した $(M+1) \times 2^{(N-M)}$ 個のサブメモリ（MはNより小さい整数）のいずれかから前記対応するデータを読み出すために、前記N次元直交座標上の各単位超立体の頂点を $(M+1) \times 2^{(N-M)}$ 通りのいずれかに分類する方法であって、

40

50

1)  $\times 2^{(N-M)}$ 通りのいずれかに分類する方法であって、

それがN個の成分からなる頂点の座標値のうちのM個の成分を選択する選択工程と、

前記選択工程により選択されたM個の成分の総和と、前記選択工程により選択されなかつた(N - M)個の成分のそれが奇数か偶数かを示す値によりなる整数を(M + 1)倍した結果とを加算する第1の算出工程と、

前記第1の算出工程による加算の結果を、(M + 1)  $\times 2^{(M-N)}$ で割った余りを算出する第2の算出工程と、

前記第2の算出工程により算出された余りを、前記頂点を(M + 1)  $\times 2^{(N-M)}$ 個のグループのいずれかに分類するための指標値として用いて、前記頂点を前記指標値が示すグループに分類する分類工程とを有することを特徴とするデータ分類方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データ分類方法に関し、特に、N次元ベクトル信号を補間するために用いて好適なものである。

【背景技術】

【0002】

近年、入力機器としては、スキャナ、ビデオカメラなどが普及している。一方、出力機器としては、インクジェット、染料熱昇華型あるいは電子写真などの方式を用いた、各種カラープリンタが普及している。これらのカラー入力機器及び出力機器は、それぞれ固有の色空間を有しており、例えばあるスキャナで得たカラー画像をそのまま別のカラープリンタに転送して印刷した場合、印刷されたカラー画像の色がスキャナによって読み取られたオリジナルのカラー画像の色と一致することはほとんどない。

【0003】

このようなカラー画像等に対するデバイス間での色再現性の問題を解決するためには、入力機器の色空間を出力機器の色空間に変換する処理("色空間変換"と呼ぶ)が必要となり、入力機器及び出力機器の色彩再現性能を高めるために、色空間変換機能が入力機器及び出力機器に搭載されている。

【0004】

ここで色空間変換とは、具体的には入力 補正、輝度濃度変換、マスキング、黒生成、UCR、出力 補正等の一連の画像処理全体、もしくはその中の一定の処理を指す。一般的には、入力機器の3色(例えば、レッド、ブルー、グリーンの3色、以下、"RGB"と略称する)のデジタル画像信号を同時に参照して、出力機器の3色(例えば、シアン、マゼンタ、イエローの3色、以下、"CMY"と略称する)あるいは4色(例えば、シアン、マゼンタ、イエロー、ブラックの4色、以下、"CMYK"と略称する)のデジタル画像信号に変換することが多い。また電子写真方式の複写機の場合、稼働時間とともにプリンタのエンジン特性が変化するため、定期的なキャリブレーションが必要となる。このような場合は、入力機器の4色(例えば、"CMYK")から出力機器の4色(例えば、"CMYK")への変換も必要となる。

【0005】

以上のような色空間変換方法を実現するための第1の従来技術として、色変換の結果が記憶された3D-LUT(3次元ルックアップ・テーブル)を8個のメモリに分けて記憶し、この3D-LUTから参照値を並列に読み出すことで、三次元立方体[トライリニア]補間法や三次元四面体補間法を高速に実行する技術が開示されている(特許文献1を参照)。

【0006】

かかる技術では、補間に使用する単位超立体の各頂点に対応する参照値がすべて異なるメモリに記憶されることで、メモリから参照値を読み出すときにアクセスが競合することはなくなるようにしている。また、3D-LUTを重複することなく均等に8

10

20

30

40

50

個のメモリに分割して記憶している（以後、多次元 LUT から参照値を並列に読み出すために多次元 LUT を複数のメモリに分割して記憶した場合、それら複数のメモリをそれぞれ“サブメモリ”と呼ぶことにする）。なお、第 1 の従来技術では、三次元補間法に限定した記載しかなされていないが、第 1 の従来技術を用いて多次元補間演算を行なう場合には、多次元 LUT を  $2^N$  個のサブメモリに分割して記憶すればよいことになる。

#### 【0007】

また、3D-LUT を重複することなく 4 つのサブメモリに分割して記憶し、参照値を並列に読み出すことで三次元四面体補間法を高速に実行する第 2 の従来技術が開示されている（特許文献 2 を参照）。

かかる技術では、三次元四面体補間法の場合、選択された四面体の頂点に対応する 4 つの参照値を並列に読み出して、補間演算を高速化できるようにしている。また、第 2 の従来技術においても、前述した第 1 の従来技術と同様に、3D-LUT を重複することなく均等に 4 個のサブメモリに分割して記憶しており、各サブメモリから参照値を読み出すときにアクセスが競合することはない。

さらに、第 2 の従来技術における LUT を多次元化して分割している。したがって、N 次元入力の超四面体（N+1 面体）補間法を行なう場合、多次元（N 次元）LUT を（N+1）個のサブメモリに分割して記憶できる。

このように、第 2 の従来技術は、使用的するサブメモリの個数が少ないという点で、前述した第 1 の従来技術よりは優位である。

#### 【0008】

【特許文献 1】米国特許 4 837722 号明細書

【特許文献 2】特開平 10-307911 号公報

【発明の開示】

【発明が解決しようとする課題】

#### 【0009】

前述した第 1 の従来技術では、単位超立体の頂点に対応する N 個の参照値をそれぞれ独立した N 個のサブメモリに記憶し、多次元 LUT を  $2^N$  個に分割している。そのため、多次元四面体補間法以外の補間法（例えば、多次元立体[トライリニア]補間法、多次元三角柱[プリズム]補間法など）を用いても実現することが可能であるという利点を持っている。

しかしながら、多次元四面体補間法を採用することが前提になっている場合、補間演算に必要な（N+1）個の参照値をサブメモリから並列に読み出すために、メモリインターフェースなどのメモリ周辺回路を  $2^N$  個持つ必要があり、余剰回路が多くなるという問題がある。

#### 【0010】

また、前述した第 2 の従来技術では、多次元四面体補間法のみに限定することで、多次元（N 次元）LUT を最小限の個数（（N+1）個）のサブメモリに分割して記憶している。そのため、メモリ周辺回路も最適な規模であるという利点を持っている。

しかしながら、N が（2 の幕乗 - 1）でないときには、サブメモリの個数も 2 の幕乗にならない。例えば、N が 4 の場合には、サブメモリの個数は 5 個となる。そして、第 2 の従来技術をハードウェア化する場合には、2 進法で取り扱うことができない。そのため、N が（2 の幕乗 - 1）でないときには、サブメモリをアクセスするためのアドレスを生成するときに割り算器が必要となり、シフト演算やビットマスクだけでアドレス生成できないという問題が生じる。また、一般的にメモリは、2 の幕乗のワード数で製品化されているため、市場に流通しているメモリを利用してサブメモリを構成する場合、第 2 の従来技術ではワード数が余剰なメモリを採用しなければならないという問題が生じる。

#### 【0011】

本発明は、以上のような問題に鑑みてなされたものであり、色空間の変換などにおいて 行われる単位超立方体の頂点の分類を高速に行なえるように することができる、小さな回路規模で実現できるようにすることを目的とする。

10

20

30

40

50

## 【課題を解決するための手段】

## 【0012】

本発明のデータ分類方法は、N次元直交座標（Nは4以上の整数）上の各単位超立体の頂点に対応するデータを格納した（M+1）×2<sup>(N-M)</sup>個のサブメモリ（MはNより小さい整数）のいずれかから前記対応するデータを読み出すために、前記N次元直交座標上の各単位超立体の頂点を（M+1）×2<sup>(N-M)</sup>通りのいずれかに分類する方法であって、それぞれが複数のビットで表わされるN個の成分からなる頂点の座標値のうちM個の成分を選択する選択工程と、前記選択工程により選択されたM個の成分の総和を算出する第1の算出工程と、前記第1の算出工程により算出された総和を、（M+1）で割った余りを算出する第2の算出工程と、前記選択工程により選択されなかった（N-M）個の成分のそれぞれの所定のビット位置の値によりなる整数を（M+1）倍した結果を、前記第2の算出工程により算出された余りに加算して、前記頂点を（M+1）×2<sup>(N-M)</sup>個のグループのいずれかに分類するための指標値を算出する第3の算出工程と、前記第3の算出工程により算出された指標値が示すグループに前記頂点を分類する分類工程とを有することを特徴とする。

また、本発明の他の態様例では、N次元直交座標（Nは4以上の整数）上の各単位超立体の頂点に対応するデータを格納した（M+1）×2<sup>(N-M)</sup>個のサブメモリ（MはNより小さい整数）のいずれかから前記対応するデータを読み出すために、前記N次元直交座標上の各単位超立体の頂点を（M+1）×2<sup>(N-M)</sup>通りのいずれかに分類する方法であって、それがN個の成分からなる頂点の座標値のうちM個の成分を選択する選択工程と、前記選択工程により選択されたM個の成分の総和を算出する第1の算出工程と、前記第1の算出工程により算出された総和を、（M+1）で割った余りを算出する第2の算出工程と、前記選択工程により選択されなかった（N-M）個の成分のそれが奇数か偶数かを示す値によりなる整数を（M+1）倍した結果を、前記第2の算出工程により算出された余りに加算して、前記頂点を（M+1）×2<sup>(N-M)</sup>個のグループのいずれかに分類するための指標値を算出する第3の算出工程と、前記第3の算出工程により算出された指標値が示すグループに、前記頂点を分類する分類工程とを有することを特徴とする。

また、本発明のその他の態様例では、N次元直交座標（Nは4以上の整数）上の各単位超立体の頂点に対応するデータを格納した（M+1）×2<sup>(N-M)</sup>個のサブメモリ（MはNより小さい整数）のいずれかから前記対応するデータを読み出すために、前記N次元直交座標上の各単位超立体の頂点を（M+1）×2<sup>(N-M)</sup>通りのいずれかに分類する方法であって、それが複数のビットで表わされるN個の成分からなる頂点の座標値のうちM個の成分を選択する選択工程と、前記選択工程により選択されたM個の成分の総和と、前記選択工程により選択されなかった（N-M）個の成分のそれぞれの所定のビット位置の値によりなる整数を（M+1）倍した結果とを加算する第1の算出工程と、前記第1の算出工程による加算の結果を、（M+1）×2<sup>(M-N)</sup>で割った余りを算出する第2の算出工程と、前記第2の算出工程により算出された余りを、前記頂点を（M+1）×2<sup>(N-M)</sup>個のグループのいずれかに分類するための指標値として用いて、前記頂点を前記指標値が示すグループに分類する分類工程とを有することを特徴とする。

また、本発明のその他の態様例では、N次元直交座標（Nは4以上の整数）上の各単位超立体の頂点に対応するデータを格納した（M+1）×2<sup>(N-M)</sup>個のサブメモリ（MはNより小さい整数）のいずれかから前記対応するデータを読み出すために、前記N次元直交座標上の各単位超立体の頂点を（M+1）×2<sup>(N-M)</sup>通りのいずれかに分類する方法であって、それがN個の成分からなる頂点の座標値のうちM個の成分を選択する選択工程と、前記選択工程により選択されたM個の成分の総和と、前記選択工程により選択されなかった（N-M）個の成分のそれが奇数か偶数かを示す値によりなる整数を（M+1）倍した結果とを加算する第1の算出工程と、前記第1の算出工程による加算の結果を、（M+1）×2<sup>(M-N)</sup>で割った余りを算出する第2の算出工程と、前記第2の算出工程により算出された余りを、前記頂点を（M+1）×2<sup>(N-M)</sup>個のグループのいずれかに分類するための指標値として用いて、前記頂点を前記指標値が示すグループに分類する分類

10

20

30

40

50

工程とを有することを特徴とする。

**【発明の効果】**

**【0016】**

本発明によれば、N次元超四面体（N+1面体）上の単位超立方体の頂点の分類を高速に行なえるようにすることが、小さな回路規模で実現できる。

**【発明を実施するための最良の形態】**

**【0017】**

以下に説明する本発明の実施形態では、色空間の変換を実現する方法として、色空間を変換した結果をルックアップ・テーブル（LUT）としてメモリに予め記憶しておき、入力されたデジタル画像信号に対して、そのLUTを用いて色空間を変換し、その変換結果を出力する。10

**【0018】**

そして、このLUTを用いた色空間の変換方法において、LUTのメモリを削減するため補間演算を併用する。3色入力のデジタル画像信号に対する色空間変換は、三次元補間演算を用いて実現される。また、4色入力のデジタル画像信号に対する色空間変換は、四次元補間演算を用いて実現される。

**【0019】**

そこで、まず、3色入力のデジタル画像信号に対して、三次元ルックアップ・テーブル（3D-LUT）と、三次元補間演算とを併用した色空間変換方法について説明する。

入力デジタル画像信号（R、G、B）は、上位ビットと下位ビットとに分離される。20 上位ビットは、3D-LUTを用いて行なう補間演算に必要な複数の参照値を取り出すときに使用される。また、下位ビットは、重み係数gとして補間演算に使用される。そして、重み係数gと3D-LUTから取り出された参照値との積和演算により補間値を計算する。

**【0020】**

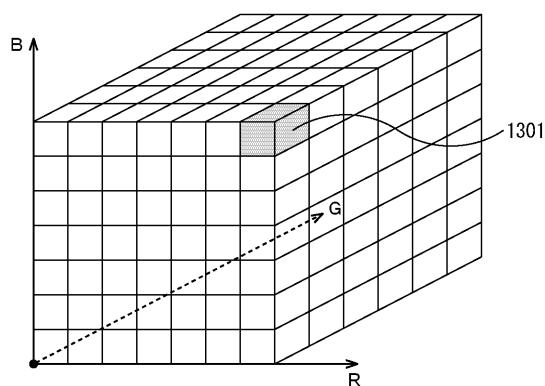

図13は、三次元入力の色空間（RGB空間）を、各軸方向に限定数で分割することで、単位立体に分割した状態を示している。この単位立体の頂点における色空間変換後の色データが、参照値として3D-LUTに記憶されている。3つのデジタル画像信号の上位ビットを色空間の座標と考え、補間演算に使用する単位立体を選択し（例えば、図13に示す単位立体1301）、単位立体の頂点に対応する参照値を補間演算に使用する。30

**【0021】**

このときに使用される三次元補間演算の方法として四面体補間法がある。

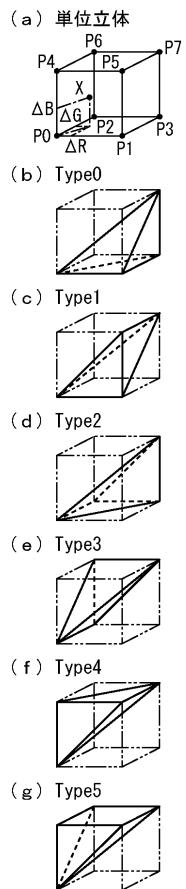

この補間法は、図14（b）～（g）に示すように、単位立体（例えば、図13に示す単位立体1301）を6つの四面体に分割して（以下、分割した6つの四面体をそれぞれType 0～Type 5と称する）、入力座標がどの四面体に属するかによって、以下の（1式）～（6式）を用いて補間演算する。なお、以下の（1式）～（6式）では、図14（a）に示す単位立体の頂点に対応する参照値を、それぞれP0～P7とし、重み係数gをR、G、Bとしている。また、Type 0からType 5の四面体のうち、どの四面体を選択するかは、これら重み係数R、G、Bの大小関係により決定される。

**【0022】**

Type 0のとき（R > G > B）

$$X = P_0 + (P_1 - P_0) \times R + (P_3 - P_0) \times G + (P_7 - P_0) \times B \quad \cdot \\ \cdot \cdot \cdot (1\text{式})$$

Type 1のとき（R > B > G）

$$X = P_0 + (P_1 - P_0) \times R + (P_7 - P_0) \times G + (P_5 - P_0) \times B \quad \cdot \\ \cdot \cdot \cdot (2\text{式})$$

Type 2のとき（G > R > B）

$$X = P_0 + (P_3 - P_0) \times R + (P_2 - P_0) \times G + (P_7 - P_0) \times B \quad \cdot \\ \cdot \cdot \cdot (3\text{式})$$

Type 3のとき（G > B > R）

10

20

30

40

50

$X = P_0 + (P_7 - P_0) \times R + (P_2 - P_0) \times G + (P_6 - P_0) \times B \dots$

$\dots$  (4式)

Type 4 のとき ( $B > R > G$ )

$X = P_0 + (P_5 - P_0) \times R + (P_7 - P_0) \times G + (P_4 - P_0) \times B \dots$

$\dots$  (5式)

Type 5 のとき ( $B > G > R$ )

$X = P_0 + (P_7 - P_0) \times R + (P_6 - P_0) \times G + (P_4 - P_0) \times B \dots$

$\dots$  (6式)

#### 【0023】

また、これまで説明した三次元四面体補間法を多次元化することも可能である。以下に 10

多次元超四面体補間法について説明する。

図13に示す三次元直交座標に固定された空間を多次元化して、N次元直交座標に固定された空間にした場合、図13に示す単位立体は、多次元の単位超立体（N次元超立体、もしくは超六面体と呼ぶ）に多次元化される。そして、三次元四面体補間法で使用された四面体は、この多次元化により超四面体と呼ばれる（N+1）面体に多次元化される。

#### 【0024】

この超四面体は、単位超立体の基準点と対角点とを結ぶ線と、超立体の互いに直交し、且つ連結しているN本の稜線とによって形成される。そして、1つの単位超立体を分割してN!個の超四面体を作ることができる。単位超立体から超四面体を切り出す過程で選択したN本の稜線は、互いに垂直であり、且つN次元直交座標の各軸方向にそれぞれ平行である。このため、各軸方向の出力変移量の線形和を基準点出力値に加算した値が多次元補間演算の出力となる。したがって、選択された稜線の両端点における参照値の差分値に、各稜線上での基準点からの距離を乗算して、それら乗算値を基準点の参照値に累積加算することで補間演算を行なえる。

#### 【0025】

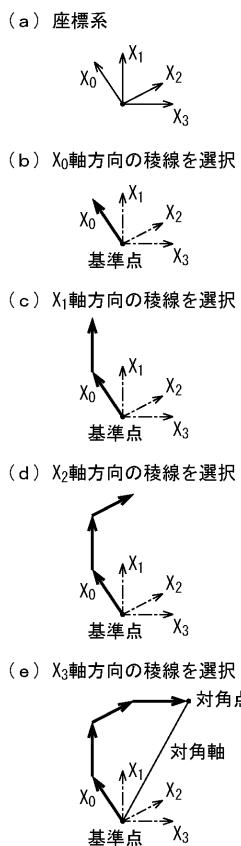

次に、四次元空間 ( $X_0, X_1, X_2, X_3$ ) を例に挙げて、四次元超四面体補間法のおける稜線の選択方法を説明する。図15は、入力座標を ( $X_0<i>+ X_0, X_1<j>+ X_1, X_2<k>+ X_2, X_3<l>+ X_3$ ) とし、この入力座標と基準点座標 ( $X_0<i>, X_1<j>, X_2<k>, X_3<l>$ ) との差 ( $-X_0, -X_1, -X_2, -X_3$ ) の大小関係が、{  $X_0 > X_1 > X_2 > X_3$  } の場合において、稜線を選択する方法を示している。

#### 【0026】

まず、図15(b)に示すように、入力座標と基準点座標との変移量が最も大きい  $X_0$  に対応する  $X_0$  軸と平行で、且つ基準点を端点にもつ稜線、つまり点 ( $X_0<i>, X_1<j>, X_2<k>, X_3<l>$ ) と点 ( $X_0<i+1>, X_1<j>, X_2<k>, X_3<l>$ ) を両端点に持つ稜線が選択される。

次に、図15(c)に示すように、入力座標と基準点座標との変移量が2番目に大きい  $X_1$  に対応する  $X_1$  軸と平行で、且つ点 ( $X_0<i+1>, X_1<j>, X_2<k>, X_3<l>$ ) を端点にもつ稜線、つまり、点 ( $X_0<i+1>, X_1<j>, X_2<k>, X_3<l>$ ) と点 ( $X_0<i+1>, X_1<j+1>, X_2<k>, X_3<l>$ ) を両端点に持つ稜線が選択される。

#### 【0027】

次に、図15(d)に示すように、入力座標と基準点座標との変移量が3番目に大きい  $X_2$  に対応する  $X_2$  軸と平行で、且つ点 ( $X_0<i+1>, X_1<j+1>, X_2<k>, X_3<l>$ ) を端点にもつ稜線、つまり、点 ( $X_0<i+1>, X_1<j+1>, X_2<k>, X_3<l>$ ) と点 ( $X_0<i+1>, X_1<j+1>, X_2<k+1>, X_3<l>$ ) を両端点に持つ稜線が選択される。

最後に、図15(e)に示すように、入力座標と基準点座標との変移量が最も小さい  $X_3$  に対応する  $X_3$  軸と平行で、且つ点 ( $X_0<i+1>, X_1<j+1>, X_2<k+1>, X_3<l>$ ) を端点にもつ稜線、つまり、点 ( $X_0<i+1>, X_1<j+1>, X_2<k+1>, X_3<l>$ ) と点 ( $X_0<i+1>, X_1<j+1>, X_2<k+1>, X_3<l+1>$ ) を両端点に持つ稜線が選択される。

#### 【0028】

最終的に、点 ( $X_0<i>, X_1<j>, X_2<k>, X_3<l>$ ) 、 ( $X_0<i+1>, X_1<j>, X_2<k>, X_3<l>$ ) 、 ( $X_0<i+1>, X_1<j+1>, X_2<k>, X_3<l>$ ) 、 ( $X_0<i+1>, X_1<j+1>, X_2<k+1>, X_3<l>$ ) 、 ( $X_0<i+1>, X_1<j+1>, X_2<k+1>, X_3<l+1>$ ) とを両端点に持つ稜線が選択される。

10

20

30

40

50

,  $X_2 < k+1 >$ ,  $X_3 < l+1 >$ ) の 5 つの頂点で構成される超四面体(5面体)が決定される。このとき、基準点( $X_0 < i >$ ,  $X_1 < j >$ ,  $X_2 < k >$ ,  $X_3 < l >$ )から最も遠い点( $X_0 < i+1 >$ ,  $X_1 < j+1 >$ ,  $X_2 < k+1 >$ ,  $X_3 < l+1 >$ )を対角点と呼び、基準点と対角点とを結ぶ線を対角線と呼ぶことにする。

### 【0029】

多次元超四面体補間法は、基準点と対角点とが、入力座標と基準点座標との差( $X_0$ ,  $X_1$ ,  $X_2$ ,  $X_3$ )の大小関係にかかわらず、必ず超四面体の頂点として選択されるという特徴を持つ。そこで、単位超立体から入力座標に対応する超四面体を選択する工程は、基準点をスタート、対角点をゴール、各稜線をスタートからゴールまでの経路と見立てれば、基準点から対角点までの経路を選択する経路選択問題と考えることができる。

この場合、経路の採り得る"場合の数"は、 $2^4 (= 4! = 4 \times 3 \times 2 \times 1)$ 通りになり、四次元補間演算では単位超立体を 24 個の超四面体に分割できることが分かる。同様に、N 次元補間演算の場合、単位超立体を  $N!$  個の超四面体に分割できることが分かる。

### 【0030】

次に、N 次元補間演算について説明する。N 次元直交座標に固定された空間( $X_0, X_1, \dots, X_{N-1}$ )上の座標( $X_0 < i >$ ,  $X_1 < j >$ ,  $X_2 < k >$ , ...,  $X_{N-2} < a >$ ,  $X_{N-1} < b >$ )の参照値を、 $P < i, j, k, \dots, a, b >$ とする。また、ある入力座標によって選択された超立体の基準点の座標を( $X_0 < i >$ ,  $X_1 < j >$ ,  $X_2 < k >$ , ...,  $X_{N-2} < a >$ ,  $X_{N-1} < b >$ )とし、入力座標と基準点座標との差を( $X_0$ ,  $X_1$ ,  $X_2$ , ...,  $X_{N-2}$ ,  $X_{N-1}$ )とする。そして、 $\{X_0 > X_1 > X_2 > \dots > X_{N-2} > X_{N-1}\}$ の関係が成り立つ場合、以下の(7式)を用いて補間値 X を求めることができる。

### 【0031】

#### 【数1】

$$\begin{aligned}

X = & P < i, j, k, \dots, a, b > \\

& + (P < i+1, j, k, \dots, a, b > - P < i, j, k, \dots, a, b >) \times \Delta X_0 \\

& + (P < i+1, j+1, k, \dots, a, b > - P < i+1, j, k, \dots, a, b >) \times \Delta X_1 \\

& + (P < i+1, j+1, k+1, \dots, a, b > - P < i+1, j+1, k, \dots, a, b >) \times \Delta X_2 \\

& + \\

& \dots \\

& + \\

& + (P < i+1, j+1, k+1, \dots, a+1, b > - P < i+1, j+1, k+1, \dots, a, b >) \\

& \quad \times \Delta X_{N-2} \\

& + (P < i+1, j+1, k+1, \dots, a+1, b+1 > - P < i+1, j+1, k+1, \dots, a+1, b >) \\

& \quad \times \Delta X_{N-1} \\

& \quad \dots \quad (7\text{式})

\end{aligned}$$

### 【0032】

#### (第1の実施形態)

次に、本発明の第1の実施形態について説明する。

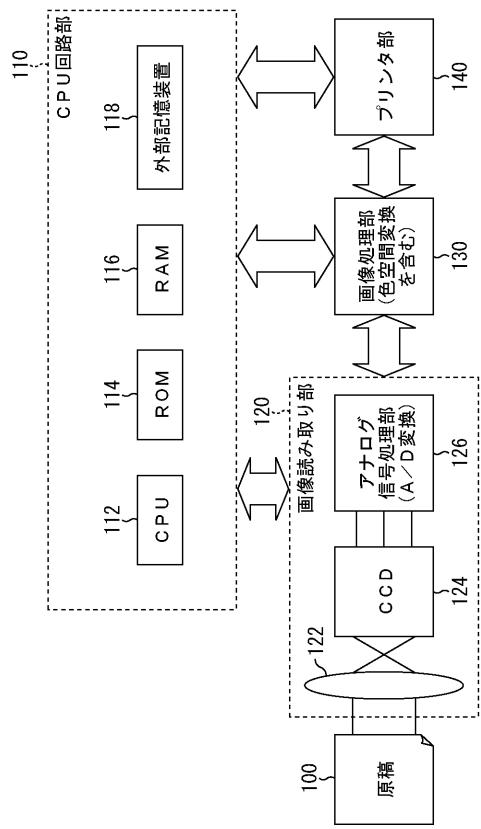

図1に、カラー複写機の全体構成の一例を示す。

図1において、画像読み取り部120は、レンズ122、CCDセンサ124、及びアナログ信号処理部126等を備えて構成される。レンズ122を介しCCDセンサ124に結像された原稿100の画像が、CCDセンサ124によりR(Red), G(Green), B(Blue)のアナログ電気信号に変換される。

### 【0033】

アナログ信号に変換された画像情報は、アナログ信号処理部126に入力され、R, G, Bの各色毎に補正等が行われた後にアナログ・デジタル変換(A/D変換)される。デ

10

20

30

40

50

ジタル化されたフルカラー信号（以下、デジタル画像信号という）は、画像処理部130に入力される。画像処理部130は、デジタル画像信号に対し、入力補正、色空間変換、濃度補正、及びスクリーン処理を施し、これらの処理が施された後のデジタル画像信号をプリンタ部140へ出力する。

#### 【0034】

プリンタ部140は、例えば、レーザ等からなる露光制御部（図示せず）、画像形成部（図示せず）、及び転写紙の搬送制御部（図示せず）等により構成され、入力されたデジタル画像信号により転写紙上に画像を記録する。

また、CPU回路部110は、演算制御用のCPU112、固定データやプログラムを格納するROM114、データの一時保存やプログラムのロードに使用されるRAM116、及び外部記憶装置118等を備えて構成され、画像読み取り部120、画像処理部130、及びプリンタ部140等を制御し、カラー複写機のシーケンスを統括的に制御する。外部記憶装置118は、カラー複写機が使用するパラメータやプログラムを記憶するディスク等の媒体であり、RAM116のデータやプログラム等は、外部記憶装置118からロードされる構成としても構わない。

#### 【0035】

本実施形態の多次元補間装置は、例えば画像処理部130で行なわれる色空間変換を実現している。なお、本発明は、図1に示したようなカラー複写機に限定されるものではなく、プリンタやPC（パーソナルコンピュータ）に実施することもできる。以下、図2を用いて、本実施形態の多次元補間装置の回路構成と処理の流れについて詳しく説明する。

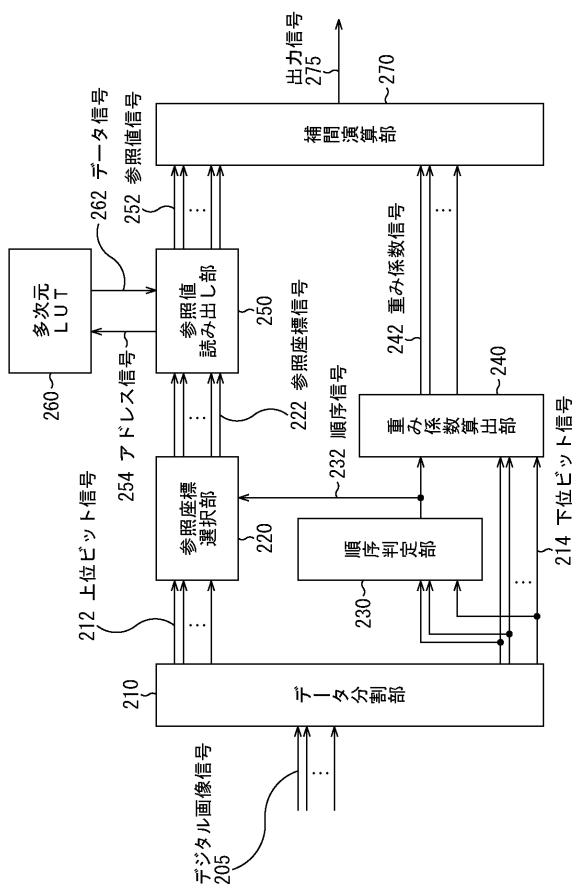

本実施形態の多次元補間装置は、N次元の入力信号に対し補間演算を行い、新たな信号を出力する。まず、デジタル画像信号205が多次元補間装置に入力される。このデジタル画像信号205は、N入力の信号である。デジタル画像信号205は、データ分割部210で上位ビット信号212と下位ビット信号214とに分割される。

#### 【0036】

デジタル画像信号205がN入力の信号であるため、デジタル画像信号205を分割して得られた上位ビット信号212と下位ビット信号214は、ともにN本の信号となる。一般的に、上位ビット信号212は、補間演算のときに使用される単位超立体の個数に応じてそのビット深度が決定される。例えば、N次元空間のある軸について単位超立体が( $2^{x-1}$ )個ある場合、その軸に対応する上位ビット信号212のビット深度はxビットとなる。また、一般的に、下位ビット信号214は、デジタル画像信号205のビット深度から上位ビット信号212のビット深度を差し引いた、残りのビット深度で表現される。

#### 【0037】

次に、順序判定部230は、N本の下位ビット信号214を受け取り、下位ビット信号214の大小関係を判定し、判定した結果を順序信号232として出力する。この順序信号232は、前述した単位超立体から補間演算に使用する超四面体(N+1面体)の稜線を選択する工程に従って予め定められたN!通りの稜線選択パターンを指示する信号である。

#### 【0038】

参照座標選択部220は、順序判定部230の判定結果である順序信号232に従い、補間演算に必要となる(N+1)個の参照値252を多次元LUT260から読み出すための座標を決定し、決定した座標を、(N+1)本の参照座標信号222として出力する。

#### 【0039】

また同様に、重み係数算出部240は、下位ビット信号214をもとに、補間演算の重み係数信号242を算出し、補間演算部270に出力する。なお、下位ビット信号214をもとに、補間演算の重み係数信号242を算出する方法としては、例えば、対応表となるテーブルを予めROMに格納しておき、該当する補間演算の重み係数信号242をROMから読み出すことで、下位ビット信号214を補間演算の重み係数信号242に変換する方法や、予め定められた計算式により算出する方法などが挙げられる。

#### 【0040】

10

20

30

40

50

また、参照値読み出し部 250 は、(N + 1) 本の参照座標信号 222 を用いて多次元 LUT 260 から (N + 1) 個の参照値を読み出し、読み出した参照値を参照値信号 252 として出力する。多次元 LUT 260 は、複数個のサブメモリで実現されている。参照値読み出し部 250 は、サブメモリの個数と等しい数のアドレス信号 254 を各サブメモリに出力して各サブメモリにアクセスし、各サブメモリからデータ信号 262 を受け取る。

補間演算部 270 は、(N + 1) 本の参照値信号 252 と、N 本の補間演算の重み係数信号 242 とを受け、前述した補間演算式に従い補間演算を行い、1 本の出力信号 275 を出力する。

#### 【0041】

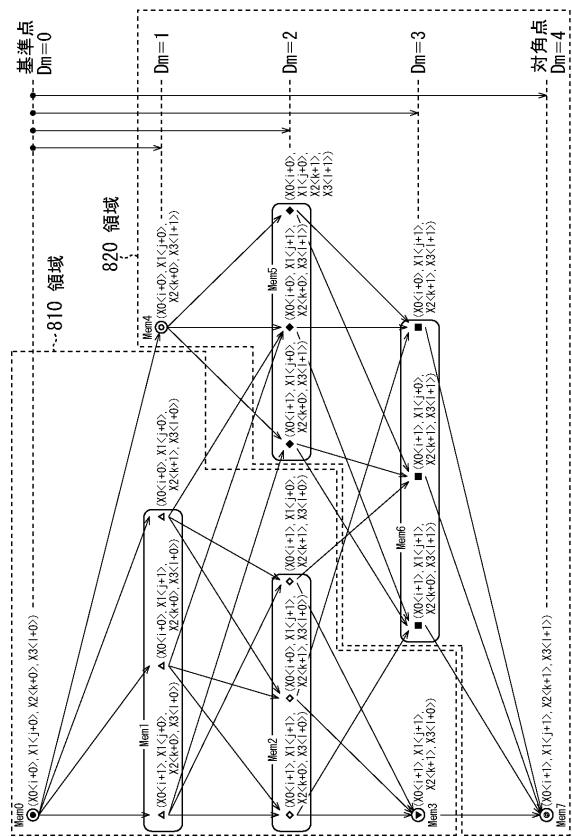

次に、N 次元超四面体補間法において、多次元 LUT 260 の参照値を重複することなく、 $2^{N-1}$  個のサブメモリに分割して記憶する方法の一例について説明する。

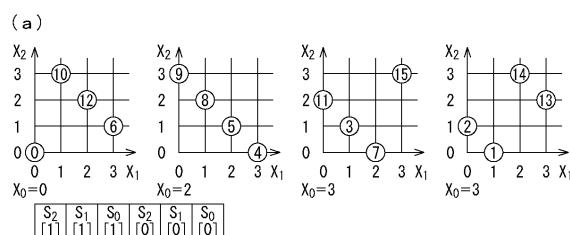

図 3 に、四次元超四面体補間法に従って、基準点から対角点までの単位立体の各頂点を、四次元マンハッタン距離を用いて分類した結果を示す。

#### 【0042】

ここで、N 次元マンハッタン距離 Dm は、N 次元直交座標に固定された空間上の 2 点 A ( $X_0 < i_1 >, X_1 < j_1 >, X_2 < k_1 >, \dots, X_{N-2} < a_1 >, X_{N-1} < b_1 >$ ) と、B ( $X_0 < i_2 >, X_1 < j_2 >, X_2 < k_2 >, \dots, X_{N-2} < a_2 >, X_{N-1} < b_2 >$ ) との距離であり、以下の(8式)で定義されるものである。

$$Dm = |X_0 < i_1 > - X_0 < i_2 >| + |X_1 < j_1 > - X_1 < j_2 >| + |X_2 < k_1 > - X_2 < k_2 >| + \dots + |X_{N-2} < a_1 > - X_{N-2} < a_2 >| + |X_{N-1} < b_1 > - X_{N-1} < b_2 >| \quad \dots \quad (8\text{式})$$

#### 【0043】

そして、三次元四面体補間法では、多次元 LUT を  $2^2$  個のサブメモリに分割して記憶することを利用し、四次元の単位超立体の基準点 ( $X_0 < i >, X_1 < j >, X_2 < k >, X_3 < l >$ ) から点 ( $X_0 < i+1 >, X_1 < j+1 >, X_2 < k+1 >, X_3 < l >$ ) までの  $2^3$  個の頂点に対し、三次元四面体補間法における多次元 LUT の分割記憶方法を適用する(図 3 の領域 810)。

#### 【0044】

単位超立体から補間演算に使用する超四面体を選択する工程は、基準点からどの頂点を通って対角点に到達するかという経路選択問題と考えられるため、マンハッタン距離 Dm が同一の頂点群からは常に 1 つの頂点のみが選択される。つまり、マンハッタン距離 Dm が同一の頂点群を同じサブメモリに記憶した場合は、そのサブメモリから異なる 2 つの頂点は同時には読み出されることはない。そのため、サブメモリへのアクセスが競合することはない。

図 3 においては、Mem0、Mem1、Mem2、Mem3 と記載された太線で囲まれた頂点が同一のサブメモリに記憶され、三次元四面体補間法では、各頂点が 4 個のサブメモリに分割して記憶されることが理解できる。

#### 【0045】

また、残った単位超立体の  $2^3$  個の頂点 ( $X_0 < i >, X_1 < j >, X_2 < k >, X_3 < l+1 >$ ) ~ ( $X_0 < i+1 >, X_1 < j+1 >, X_2 < k+1 >, X_3 < l+1 >$ ) に対し、さらに三次元四面体補間法における多次元 LUT の分割記憶方法を適用する(図 3 の領域 820)。

#### 【0046】

最終的には、図 3 に示す Mem0, ..., Mem7 と記載された太線で囲まれた頂点が同一のサブメモリに記憶され、多次元 LUT 260 は、( $2 \times 2^2$ ) 個のサブメモリに分割される。同様に、N 次元超四面体補間法においても、 $2^3$  個の頂点 ( $X_0 < i >, X_1 < j >, X_2 < k >, \dots$ ) ~ ( $X_0 < i+1 >, X_1 < j+1 >, X_2 < k+1 >, \dots$ ) ごとに、三次元四面体補間法における多次元 LUT の分割記憶方法を適用すればよい。

#### 【0047】

前記  $2^3$  個の頂点は、 $2^{N-3}$  組あり、1 つの組が  $2^2$  個のサブメモリに記憶されるので、多次元 LUT 260 は、全部で  $2^{N-1}$  個のサブメモリに分割されることとなる。このように常に  $2^2$  個のサブメモリを単位としてサブメモリの数が増加していく。以後、増加の単位をクラスタリング単位と呼び、この単位の数だけサブメモリが集まつたものをクラスター

10

20

30

40

50

・サブメモリと呼び、前記 $2^{N-3}$ 組をクラスタ数と呼ぶことにする。また、1つのクラスタ・サブメモリを当てはめる入力次元数をベースm（第1の実施の形態の場合、"m = 3"）と呼ぶこととする。

#### 【0048】

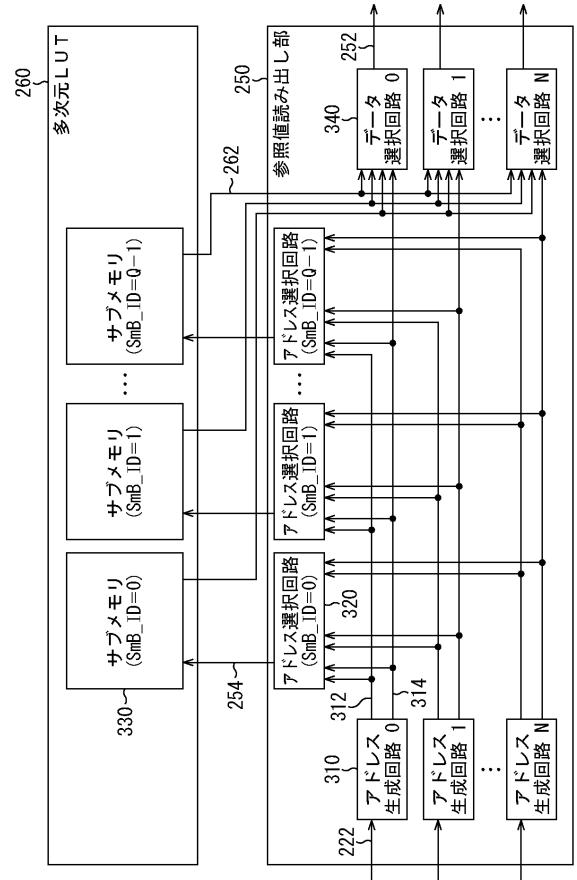

次に、図4を用いて、参照値読み出し部250と多次元LUT260について詳細に説明する。

図4において、(N+1)個のアドレス生成回路310が、(N+1)個の参照座標信号222をそれぞれ受けて、アドレス信号312と、サブメモリ・バンク選択信号314とを算出する。参照値読み出し部250には、各サブメモリに対応するアドレス選択回路320があり、各アドレス選択回路320は、(N+1)組のアドレス信号312と、サブメモリ・バンク選択信号314とを受ける。

10

#### 【0049】

各アドレス選択回路320は、自身に対応付けられているサブメモリ・バンクID"SmB\_ID"と、入力されたサブメモリ・バンク選択信号314とが等しいアドレス信号254を、(N+1)本のアドレス信号312の中から1つ選択し、選択したアドレス信号254を用いて、サブメモリ330にアクセスする。

#### 【0050】

次に、(N+1)個のデータ選択回路340は、サブメモリ330から出力されたサブメモリの個数と等しい数のデータ信号262と、対応するアドレス生成回路310から出力されたサブメモリ・バンク選択信号314とを受け取り、サブメモリ・バンク選択信号314と等しいサブメモリ・バンクID"SmB\_ID"を有するサブメモリ330から出力されたデータ信号262のみを選択し、選択したデータ信号262を参照値252として出力する。

20

#### 【0051】

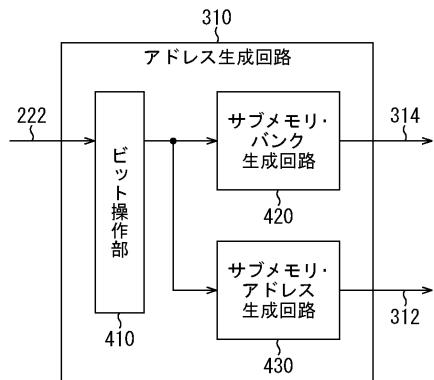

次に、アドレスを生成する方法の一例を説明する。図5に、アドレス生成回路310の構成の一例を示す。

図5において、アドレス生成回路310は、ビット操作部410、サブメモリ・バンク生成回路420、及びサブメモリ・アドレス生成回路430を備えて構成され、N次元参照座標信号222({S<sub>0</sub>, S<sub>1</sub>, ..., S<sub>t</sub>, ..., S<sub>N-1</sub>})が参照座標選択部220から入力される。

30

#### 【0052】

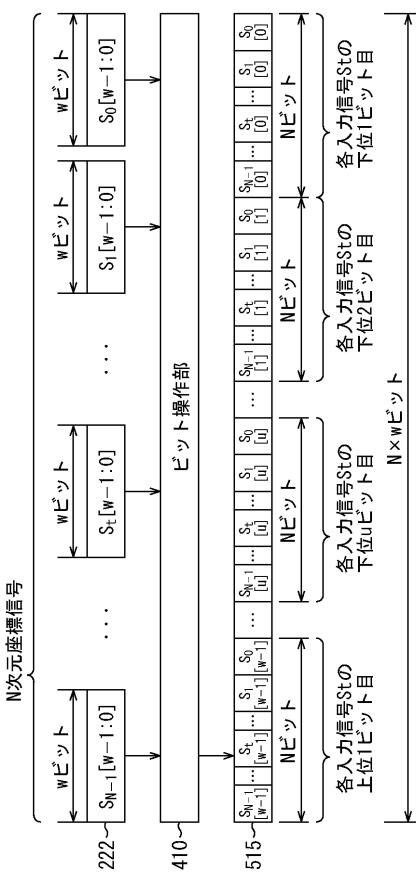

図6に、ビット操作部410がN次元参照座標信号222のビットを操作する方法の一例を示す。

図6において、それぞれがwビットのビット深度を有するN個のN次元参照座標信号222を、ビット操作部410が、下位ビットから所定の形式に並べ替え、(N×w)ビットの信号515を作る。図6に示す例では、まず、ビット操作部410は、N個の参照座標信号222の下位1ビット目だけを取り出し、Nビットの信号[S<sub>N-1</sub>[0], ..., S<sub>t</sub>[0], ..., S<sub>1</sub>[0], S<sub>0</sub>[0]]を作る。

#### 【0053】

次に、ビット操作部410は、N個のN次元参照座標信号222の下位2ビット目だけを取り出し、Nビットの信号[S<sub>N-1</sub>[1], ..., S<sub>t</sub>[1], ..., S<sub>1</sub>[1], S<sub>0</sub>[1]]を作る。さらに、ビット操作部410は、N個の参照座標信号222の下位uビット目だけを取り出し、Nビットの信号[S<sub>N-1</sub>[u], ..., S<sub>t</sub>[u], ..., S<sub>1</sub>[u], S<sub>0</sub>[u]]を作る。こうして、N個の参照座標信号222の最上位のNビットの信号[S<sub>N-1</sub>[w-1], ..., S<sub>t</sub>[w-1], ..., S<sub>1</sub>[w-1], S<sub>0</sub>[w-1]]まで同様の操作を行い、図6に示すように各Nビットの信号を連結して(N×w)ビットの信号515を作る。

40

#### 【0054】

このように、N個のN次元参照座標信号222のビットを操作（ビット操作）することで、多次元LUT260の単位超立体の個数を容易に増やすことができる。例えば、サブ

50

メモリ330の容量が大きくてよい多次元補間装置で多次元LUT260を拡張する場合には、N次元参照座標信号222のビット深度をwビットから( $w+1$ )ビットに変更し、ビット操作部410の出力の上位にNビットの信号[ $S_{N-1}[w], \dots, S_t[w]$ ,  $\dots, S_1[w], S_0[w]$ ]を連結すればよい。しかも、拡張されたビットは、拡張前のアドレスの上位に連結されるので(アドレスの生成方法については後述する)、拡張前の多次元補間装置と拡張後の多次元補間装置とで、アドレスとデータとの関係に互換性を持たせることができる。

#### 【0055】

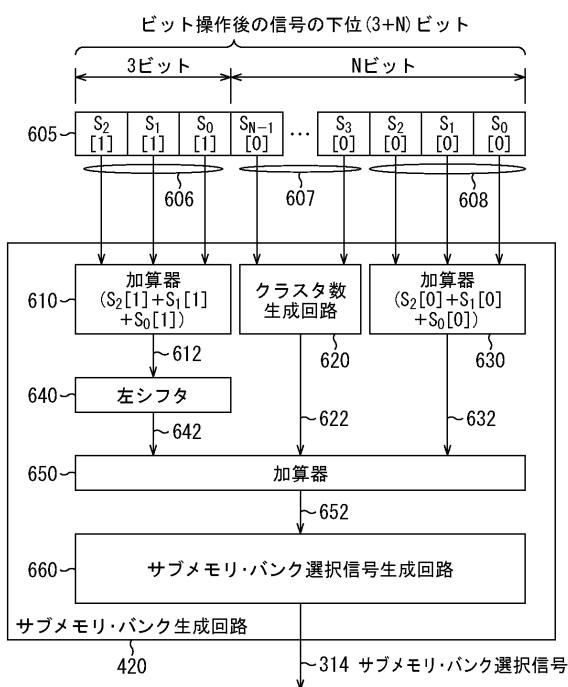

次に、図7を用いて、サブメモリ・バンク生成回路420の詳細について説明する。

図7において、ビット操作部410から出力された( $N \times w$ )ビットの信号515の下位( $3+N$ )ビットの信号605が、サブメモリ・バンク生成回路420に入力される。

この信号605の下位3ビットの信号608は、加算器630にて加算処理される。加算処理された値( $S_2[0] + S_1[0] + S_0[0]$ )は、信号632として出力される。

#### 【0056】

同様に、上位3ビットの信号606は、加算器610にて加算処理される。加算処理された値( $S_2[1] + S_1[1] + S_0[1]$ )612は、左シフタ640により1ビットだけ左シフトされ(加算処理された値 $612 << 1$ )、シフトされた値が信号642として出力される。

また、クラスタ数生成回路620は、1を入力値607だけ左シフトし( $1 << \text{入力値} 607$ )、シフトした値を信号622として出力する。

さらに、前記信号622、632、642は、加算器650にて加算された後、サブメモリ・バンク選択信号生成回路660にて下位( $N-1$ )ビットのみが取り出され、取り出された信号は、サブメモリ・バンク選択信号314として出力される。

#### 【0057】

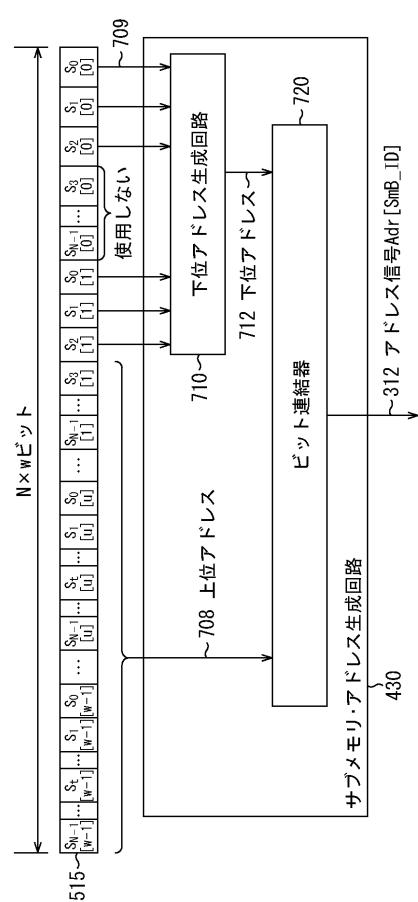

次に、図8を用いて、サブメモリ・アドレス生成回路430の詳細について説明する。

サブメモリ・アドレス生成回路430は、ビット操作部410から出力された( $N \times w$ )ビットの信号515をもとに、サブメモリ330にアクセスするためのアドレス信号312を生成する。

ビット操作部410から出力された( $N \times w$ )ビットの信号515の下位( $3+N$ )ビットのうち、6ビットの信号709が、下位アドレス生成回路710に入力され、4ビットのアドレス下位信号712が作成される。なお、残りのビットは、サブメモリ・バンク信号314を生成するために使用され、サブメモリ・アドレス生成回路430では使用されない。

最後に、ビット連結器720を用いて、アドレス上位信号708と、4ビットのアドレス下位信号712とをビット連結し、連結した信号をアドレス信号312として出力する。

#### 【0058】

ここで、下位アドレス生成回路710についてさらに詳細に説明する。

下位アドレス生成回路710に入力される6ビットの信号709は、3次元入力信号{ $S_0, S_1, S_2$ }の下位2ビットの信号により形成されており、3D-LUTの座標に対応している。これまで説明してきたように、この $4 \times 4 \times 4$ の3D-LUTが、4つのサブメモリ330に分割されるため、この6ビットの信号709は4つのサブメモリ330における参照値のすべてに対応している。

#### 【0059】

しかしながら、必要とするアドレス下位信号712は、サブメモリ330ごとの下位4ビットのアドレス信号であるため、この6ビットをそのまま使用することはできない。表1に、サブメモリ330ごとに分類した6ビットの入力信号709と、出力となる4ビットのアドレス下位信号712との対応関係を示す。

#### 【0060】

【表1】

| 入力            |               |               |               | 出力  |

|---------------|---------------|---------------|---------------|-----|

| Smb_ID[1:0]=0 | Smb_ID[1:0]=1 | Smb_ID[1:0]=2 | Smb_ID[1:0]=3 |     |

| 0x00          | 0x01          | 0x03          | 0x07          | 0x0 |

| 0x0b          | 0x02          | 0x05          | 0x09          | 0x1 |

| 0x0d          | 0x04          | 0x06          | 0x0a          | 0x2 |

| 0x0e          | 0x0f          | 0x08          | 0x0c          | 0x3 |

| 0x13          | 0x17          | 0x10          | 0x11          | 0x4 |

| 0x15          | 0x19          | 0x1b          | 0x12          | 0x5 |

| 0x16          | 0x1a          | 0x1d          | 0x14          | 0x6 |

| 0x18          | 0x1c          | 0x1e          | 0x1f          | 0x7 |

| 0x23          | 0x27          | 0x20          | 0x21          | 0x8 |

| 0x25          | 0x29          | 0x2b          | 0x22          | 0x9 |

| 0x26          | 0x2a          | 0x2d          | 0x24          | 0xa |

| 0x28          | 0x2c          | 0x2e          | 0x2f          | 0xb |

| 0x30          | 0x31          | 0x33          | 0x37          | 0xc |

| 0x3b          | 0x32          | 0x35          | 0x39          | 0xd |

| 0x3d          | 0x34          | 0x36          | 0x3a          | 0xe |

| 0x3e          | 0x3f          | 0x38          | 0x3c          | 0xf |

## 【0061】

図9は、 $4 \times 4 \times 4$ の3D-LUT内で、サブメモリ・バンクID ("Smb\_ID=0")に対応する参照値の位置を、アドレスが小さい順にマークして示した図である（図9の丸付き数字0～15）。図9(a)において、マークされていない箇所の参照値は、他のサブメモリ330に記憶されていることを意味する。

## 【0062】

表1のようなテーブルを作成し、 $4 \times 4 \times 4$ の3D-LUTを回路内にテーブルROMとして実装することで、6ビットの入力信号709を4ビットのアドレス下位信号712に容易に変換できる。

## 【0063】

また、 $4 \times 4 \times 4$ の3D-LUT内の点在する参照点を予め整理し、図9(b)及び図9(c)に示すように、 $4 \times 4$ の参照点にまとめれば、テーブルROMは不要となる。図9(b)に示すようにして参照点を整理した場合には、アドレス下位信号712は、[S<sub>2</sub>[1], S<sub>2</sub>[0], S<sub>1</sub>[1], S<sub>1</sub>[0]]の順でビット連結した信号となる。また、図9(c)に示すようにして参照点を整理した場合には、アドレス下位信号712は、[S<sub>2</sub>[1], S<sub>1</sub>[1], S<sub>2</sub>[0], S<sub>1</sub>[0]]の順でビット連結した信号となる。

## 【0064】

ここで、表2に、前述した第1の従来技術及び第2の従来技術と、本実施形態とを比較した結果を示す。

## 【0065】

10

20

30

40

【表2】

| N次元                   | 3     | 4      | 5         | 6          |

|-----------------------|-------|--------|-----------|------------|

| 参照値の総数<br>( $16^N$ 点) | 4,096 | 65,536 | 1,048,576 | 16,777,216 |

| サブメモリの個数              |       |        |           |            |

| 第1の従来技術               | 8     | 16     | 32        | 64         |

| 第2の従来技術               | 4     | 5      | 6         | 7          |

| 本実施形態                 | NA    | 8      | 16        | 32         |

| サブメモリ当たりの参照値の数        |       |        |           |            |

| 第1の従来技術               | 512   | 4,096  | 32,768    | 262,144    |

| 第2の従来技術               | 1,024 | 13,108 | 174,763   | 2,396,746  |

| 本実施形態                 | NA    | 8,192  | 65,536    | 524,288    |

## 【0066】

表2から分かるように、本実施形態では、サブメモリの数を、第1の従来技術の半分にすることができる。また、第2の従来技術と違い、本実施形態では、分割後のサブメモリ1つ当たりに記憶される参照値の数を常に2の幂乗個にすることができる。さらに、N次元入力(Nは4以上の整数)の超四面体補間法において、基本となる3次元入力からアドレスの下位4ビットが常に決定されることになる。そのため、アドレスの下位4ビットを生成する回路は、Nの値が変わっても同一の回路となる。

## 【0067】

また、第2の従来技術では、アドレス生成のために割り算器が必要になるため、アドレス生成回路を小規模化するためにはNの値ごとにテーブルROMの内容を変えるなどの工夫が必要となり、Nの値ごとにアドレス生成回路を再設計する必要がある。これに対して、前述したように、本実施形態では、Nの値が变ってもアドレス生成回路を再利用でき、容易に多次元化に対応できる。さらに、多次元LUTの単位超立体の個数の増加に伴い、N次元入力信号のビット深度が増加した場合でも、アドレス生成時のビット操作を行なうことで容易に対応できる。すなわち、本実施形態では、N次元入力信号の入力数とビット深度との両方に対し拡張性のある多次元補間装置を実現することができる。

## 【0068】

以上のように、本実施形態によれば、N次元入力(Nは4以上の整数)の超四面体補間法において、基本となる3次元入力からアドレスの下位4ビットが常に決定され、アドレスの下位4ビットを生成する回路はNの値が变っても同一の回路となる。そのため、アドレス生成回路を再利用でき、容易に多次元化に対応できる。また、多次元LUTの単位超立体の個数が増加することに伴って、N次元入力信号のビット深度が増加した場合でも、アドレス生成時のビット操作を行なうだけで、N次元入力信号のビット深度の増加に容易に対応することができる。すなわち、本実施形態によれば、N次元入力信号の入力数とビット深度との両方に対し拡張性のある多次元補間装置を提供することができる。特に、四次元超四面体(5面体)補間法に対して、本実施形態の多次元補間装置を適用する場合、サブメモリ330の個数は、必須となる5個よりは多いが、最も小さい2の幂乗数(=2<sup>3</sup>個)となるため効果が高い。

## 【0069】

## (第2の実施形態)

次に、本発明の第2の実施形態について説明する。前述した第1の実施形態では、基本となる3次元入力(ベースm=3)に対し、サブメモリを2<sup>2</sup>個単位(クラスタリング単位=2<sup>2</sup>)で当てはめることで、多次元LUTを分割して記憶するようにした。四次元超四面体補間法に適用する場合には、前記単位のサブメモリ(クラスタ・サブメモリ)が2

10

20

30

40

50

組（クラスタ数 =  $2^{4-3}$ ）必要となる。多次元 LUT にサブメモリを分割して記憶する方法は、第 1 の実施形態で説明した方法に限るわけではなく、アドレス生成回路が複雑になるという問題はあるが、一般化することができる。なお、本実施形態の説明において、前述した第 1 の実施形態と同一の部分については、図 1 ~ 図 9 に付した符号と同一の符号を付すなどして詳細な説明を省略する。

#### 【0070】

基本となる入力次元数であるベース  $m$  に対してクラスタリング単位は、 $(m + 1)$  となる。N 次元超四面体補間法に適用する場合、クラスタ数は  $2^{N-m}$  となる。N 次元超四面体補間法に必要となるサブメモリの総数  $N S m B$  は、 $N > m$  が成立する場合、以下の（9式）のようになる。

10

$$N S m B = (m + 1) \times 2^{N-m} \quad \dots \quad (9\text{式})$$

#### 【0071】

基本となる入力次元数であるベース  $m$  と、N 次元超四面体補間法を用いた場合のサブメモリの総数との対応関係は、表 3 に示したようになる。

#### 【0072】

#### 【表 3】

| 入力次元数<br>ベース $m$ | サブメモリの<br>増加単位 | N 次元のサブメモリ総数 |    |    |    |    |     |     |     |  |

|------------------|----------------|--------------|----|----|----|----|-----|-----|-----|--|

|                  |                | 3            | 4  | 5  | 6  | 7  | 8   | 9   | 10  |  |

| 2                | 3              | 6            | 12 | 24 | 48 | 96 | 192 | 384 | 768 |  |

| 3                | $2^2$          | NA           | 8  | 16 | 32 | 64 | 128 | 256 | 512 |  |

| 4                | 5              | NA           | NA | 10 | 20 | 40 | 80  | 160 | 320 |  |

| 5                | 6              | NA           | NA | NA | 12 | 24 | 48  | 96  | 192 |  |

| 6                | 7              | NA           | NA | NA | NA | 14 | 28  | 56  | 112 |  |

| 7                | $2^3$          | NA           | NA | NA | NA | NA | 16  | 32  | 64  |  |

| 8                | 9              | NA           | NA | NA | NA | NA | NA  | 18  | 36  |  |

| 9                | 10             | NA           | NA | NA | NA | NA | NA  | NA  | 20  |  |

| 10               | 11             | NA           | NA | NA | NA | NA | NA  | NA  | NA  |  |

#### 【0073】

また、多次元 LUT にサブメモリを分割して記憶することを一般化する方法を、ハードウェア化することも可能である。

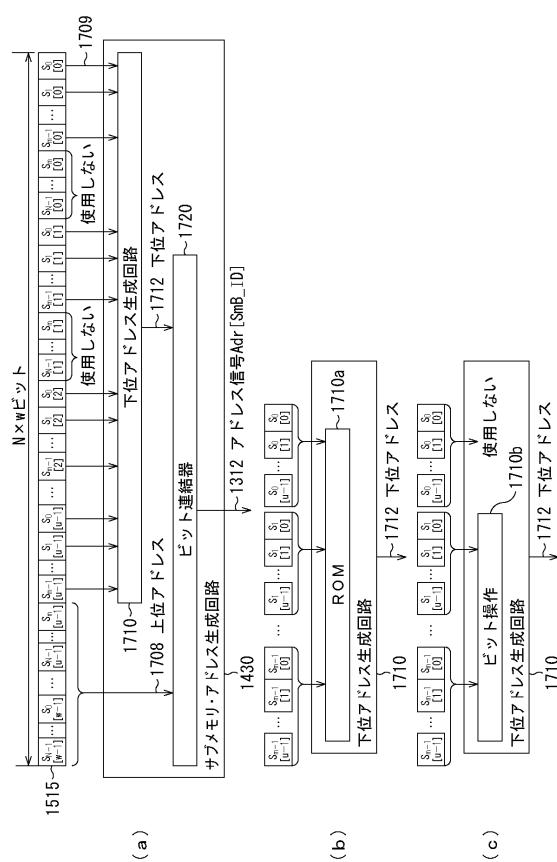

図 10 は、一般化したサブメモリ・バンク生成回路 1420 を示している。

図 10 において、ビット操作部 410 から出力された ( $N \times w$ ) ビットの信号 515 の下位 ( $m + N \times u$ ) ビットの信号 1605 を入力する。ここで、 $u$  は、 $(m + 1)$  を 2 進法で表現することができるビット深度を示す。つまり、 $\log_2(m + 1)$  以上の最小の整数である。この信号 1605 の下位  $m$  ビットの信号 1608 は、加算器 1630 にて加算処理される。加算処理された値 ( $S_{m-1}[0] + \dots + S_1[0] + S_0[0]$ ) は、信号 1632 として出力される。

40

#### 【0074】

同様に、上位  $m$  ビットの信号 1606 は、加算器 1610 にて加算処理される。加算処理された値 ( $S_{m-1}[1] + \dots + S_1[1] + S_0[1]$ ) は、左シフタ 1640 により 1 ビットだけ左シフトされ、シフトされた値が信号 1642 として出力される。そして、図 10 に示す通り、同様の操作を (( $S_{m-1}[u - 1] + \dots + S_1[u - 1] + S_0[u - 1]$ ) <  $u$ ) となるまで行なう。

#### 【0075】

さらに、前述した加算処理により得られた信号 1632 と、シフトされた信号 1642

10

20

30

40

50

50

は、後述する加算器1 6 5 0で加算される。これは、入力されたN個の参照座標信号( $S_0, S_1, \dots, S_t, \dots, S_{N-1}$ )のうち、基本となる入力次元数であるベースmに対応する信号( $S_0, S_1, \dots, S_{m-1}$ )の下位uビットのみを取り出し、その合計を求めていることを意味する。図10に示すサブメモリ・バンク生成回路1420の例では、ビット操作部410の出力に対して処理されるため、加算処理とシフト処理を行なっている。

## 【0076】

また、クラスタ数生成回路1620は、クラスタリング単位( $m+1$ )を入力値1607だけ整数倍した値を信号1622として出力する。

さらに、前記信号1632、1622、1642は、加算器1650にて加算され信号1652として出力される。そして、サブメモリ・バンク選択信号生成回路1660は、

10

$(m+1) \times 2^{N-m}$ で信号1652を割り、その余りがサブメモリ・バンク選択信号1314として出力される。

## 【0077】

以上のように、本実施形態のサブメモリ・バンク生成回路1420では、以下の(10式)に基づく演算を行なってサブメモリ・バンク選択信号1314を生成する回路である。

。

## 【0078】

## 【数2】

$$id = [\sum_{j=0}^{m-1} X_j] \% (m+1) + (m+1) \times \sum_{j=m}^{N-1} \{ (X_j \% 2) << (j-m) \} \quad \dots \quad (10\text{式})$$

## 【0079】

ただし、 $<<$ は、ビットの左シフトを表し、%は、割り算の余りを表す(例えば $a \% b$ は、 $a$ を $b$ で割った余りを表す)。

(10式)の第1項" $X_j \% (M+1)$ "では、0~MのIDを作り、(10式)の第2項" $(M+1) [(X \% 2) << (j-M)]$ "で、 $(M+1)^*0, (M+1)^*1, (M+1)^*2, \dots$ とオフセットを加算する。

図10において、クラスタ数生成回路1620は、選択されなかった( $N - M$ )個の成分について、各々奇数か偶数かを判定し、前記判定結果に基づき( $M+1$ )の倍数を前記余りに加算することによって得られる値を指標値とし、前記指標値に基づいて前記頂点を分類する。第2の実施形態では、クラスタリング単位" $m+1$ "を整数倍する値として、n次元入力( $S_0, S_1, \dots, S_{m-1}, S_m, S_{m+1}, \dots, S_{n-1}$ )信号のうち、( $S_m, S_{m+1}, \dots, S_{n-1}$ )の信号に着目し、そのLSBである( $S_m[0], S_{m+1}[0], \dots, S_{n-1}[0]$ )を使用しているので、結局、( $S_m, S_{m+1}, \dots, S_{n-1}$ )の信号の奇数か偶数かを判定することになる。

なお、第2の実施形態では上記着目した信号のLSBにてバンク信号のオフセットの加算の有無を判断しているが、LSBである必要はなく、

$(S_m[1], S_{m+1}[1], \dots, S_{n-1}[1])$

$(S_m[2], S_{m+1}[2], \dots, S_{n-1}[2])$

$\dots$

$(S_m[w-1], S_{m+1}[w-1], \dots, S_{n-1}[w-1])$

のよう、LSBの代わりに、( $S_m, S_{m+1}, \dots, S_{n-1}$ )のうち定められたビット位置のオン/オフを元にクラスタリング単位( $m+1$ )を整数倍した値を信号1622として出力すればよい。

## 【0080】

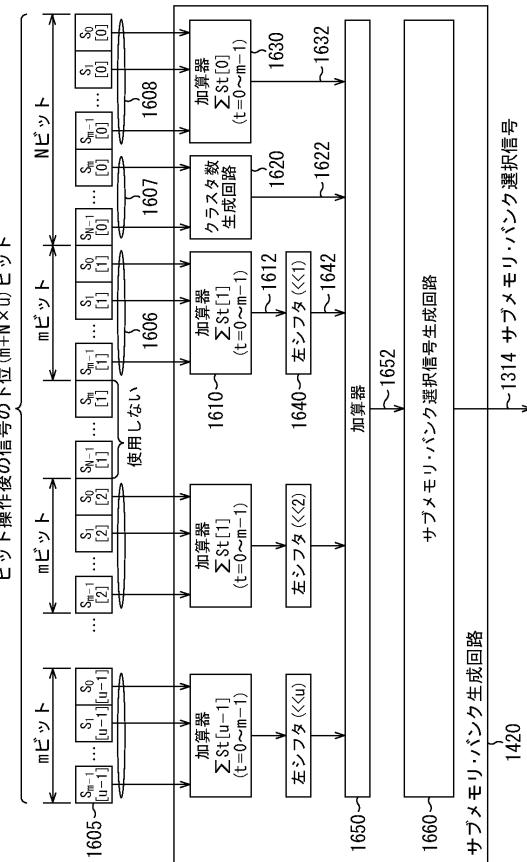

次に、図11を用いて、一般化したサブメモリ・アドレス生成回路1430について説明する。

図11(a)に示すように、サブメモリ・アドレス生成回路1430は、ビット操作部410から出力された( $N \times w$ )ビットの信号1515をもとに、サブメモリ330をアクセスするためのアドレス信号1312を生成する。

## 【0081】

ビット操作部410から出力された( $N \times w$ )ビットの信号1515の下位( $m + N \times u$ )ビットのうち、( $m \times u$ )ビットの信号1709が、下位アドレス生成回路1710に入力され、 $\{(m - 1) \times u\}$ ビットのアドレス下位信号1712が生成される。なお、残りのビットは、サブメモリ・バンク信号1314を生成するために使用され、サブメモリ・アドレス生成回路1430では使用されない。

最後に、ビット連結器1720を用いてアドレス上位信号1708と、 $\{(m - 1) \times u\}$ ビットのアドレス下位信号1712とをビット連結し、連結した信号をアドレス信号1312として出力する。

## 【0082】

10

下位アドレス生成回路1710は、図11(b)に示すように、テーブルROM1710aを用いてアドレス下位信号1712を生成する。このようにした場合、ベースmが大きくなるにつれて、必要となるテーブルROMの大きさは大きくなる。

そこで、ベースmが2の幕乗-1の値(例えば、表3において、ベースmが3及び7)の場合には、下位アドレス生成回路1710を、図11(c)に示すように、ビット操作のみを行なう回路1710bを用いて実現できる。表3から分かるように、8次元超四面体補間法の場合、ベースmが7の構成を用いれば、アドレスの生成が容易となり、且つサブメモリの総数が少ない8次元超四面体補間装置(多次元補間装置)を実現できる。

## 【0083】

20

以上のように、本実施形態によれば、N次元入力(Nは3以上の整数)の超四面体補間法において、基本となる入力次元数であるベースmを( $N - 1$ )とすれば、クラスタリング単位( $m + 1$ )は常にNとなる。したがって、クラスタ数は、 $2^{N-m} = 2^1$ となり、多次元LUTを、( $N \times 2$ )個のサブメモリに分割して記憶することができる。

## 【0084】

## (第3の実施形態)

次に、本発明の第3の実施形態について説明する。本実施形態では、前述した第1の実施形態における多次元LUT260を、外部メモリとキャッシュ機構とを用いて実現するようしている。また、本実施形態における多次元LUTの参照値のビット深度を、8ビットとしている。なお、本実施形態の説明において、前述した第1及び第2の実施形態と同一の部分については、図1～図11に付した符号と同一の符号を付して詳細な説明を省略する。

30

## 【0085】

本実施の形態のキャッシュ機構は、外部メモリをバースト・アクセスすることで、データ更新を高速に行なうことを可能とする。ここで、バースト・アクセスとは、1ワードずつ外部メモリからデータを読み出すのではなく、ある連続する複数のアドレスに対応するデータを一括して読み出す方法である。一般に、SDRAMやDDR-SDRAMなどの汎用メモリは、16バイト(128ビット)単位のバースト・アクセスに対応しており、本実施形態でも、バースト・アクセスの単位を16バイトとする。

## 【0086】

40

よって、キャッシュ機構は、8ビット(参照値のビット深度)×16ワードのデータを1つの単位として外部メモリへアクセスする。図8から分かるように、アドレス上位信号708が、外部メモリへアクセスするためのアドレス信号となり、アドレス下位信号712が、バースト・アクセスによって得られた16バイトのデータの何バイト目のデータかを指示する信号となる。以降、アドレス上位信号とアドレス下位信号という言葉で、両者を区別することとする。

## 【0087】

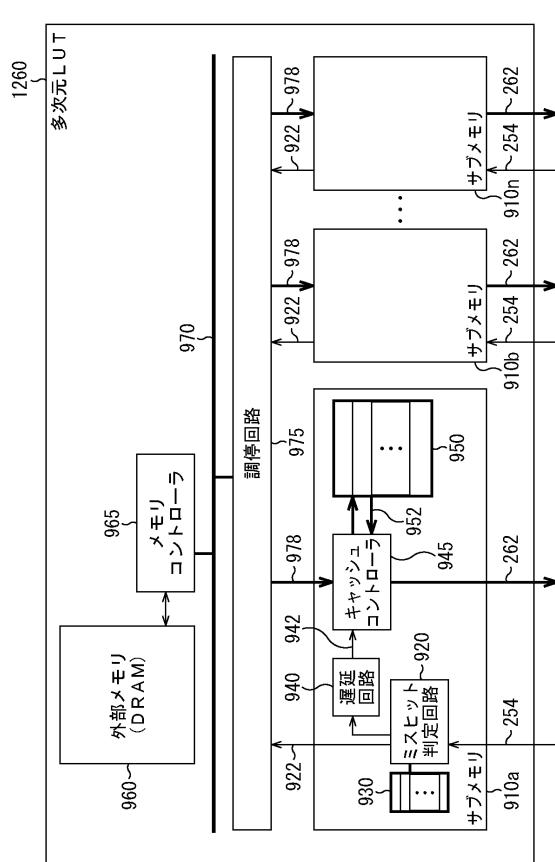

図12に、本実施形態における多次元LUTの構成の一例を示し、この図12を用いて、本実施形態の回路動作について説明する。

アドレス信号254が入力されると、そのアドレス信号254に含まれるアドレス上位信号708をもとに、ミスヒット判定回路920でキャッシュにヒットしたかどうかが判

50

定される。ミスヒット判定回路 920 は、データバッファ 950 に記憶されているデータに対応するアドレスの上位値をタグ RAM 930 に記憶している。

#### 【0088】

ミスヒット判定回路 920 は、外部から入力されるアドレス信号 254 に含まれるアドレス上位信号 708 が、タグ RAM 930 に記憶されているアドレス上位値の 1つと同じであれば、キャッシングにヒットしたと判定する。一方、アドレス上位信号 708 が、どのアドレス上位値とも異なっている場合には、キャッシングにミスヒットしたと判定する。ミスヒットしたと判定した場合、ミスヒット判定回路 920 は、タグ RAM 930 内の任意のタグ番号に記憶されているアドレス上位値を、外部から入力された上位アドレス信号 708 に上書きし、そのタグ番号に対応するデータバッファ 950 内のデータを外部メモリから更新したデータに置き換える。10

#### 【0089】

このデータの置き換え処理を行なうために、まずミスヒット判定回路 920 は、アドレス信号 254 に含まれているアドレス上位信号 708 を、アドレス信号 922 として調停回路 975 に送り、調停回路 975 、バス 970 、及びメモリコントローラ 965 を介して外部メモリ 960 にデータを要求する。調停回路 975 は、各サブメモリに接続されているキャッシング機構から出力される各アドレス信号 922 を調停し、順番にメモリコントローラ 965 へ送る。

#### 【0090】

また、メモリコントローラ 965 から送られてきたデータを、アドレス信号 922 を送った順番で、各サブメモリ 910a ~ 910n に接続されているキャッシング機構に返す。次に、ミスヒット判定回路 920 は、キャッシングにミスヒットしたか否かの判定結果に係わらず、その判定結果を示すフラグと、キャッシングのタグ番号と、アドレス信号 254 に含まれる下位アドレス信号 712 とを、まとめてコマンド信号 942 として遅延回路 940 に送る。なお、サブメモリ 910 の個数は、図 12 に示したものに限定されるものではない。20

#### 【0091】

遅延回路 940 は、FIFO (First-In First-Out) で実現されており、ある程度の数のコマンド信号 942 を蓄えることができる。そのため、ミスヒット判定回路 920 は、FIFO に空き領域がある間は連続して外部メモリ 960 にアドレス信号 922 を先出します。キャッシングコントローラ 945 は、遅延回路 940 からコマンド信号 942 を受け取り、判定結果がヒットならタグ番号に対応するデータバッファ 950 から 16 バイトのデータ 952 を取り出す。次に、アドレス下位信号 712 により出力する 1 バイトのデータを選択し、選択したデータを、データ信号 262 として出力する。30

#### 【0092】

キャッシングコントローラ 945 は、判定結果がミスヒットなら、調停回路 975 からデータ 978 が送られるまで待機する。データ 978 が送られてきた時点で、データ 978 からアドレス下位信号 712 により出力する 1 バイトのデータを選択し、データ信号 262 として出力しつつ、タグ番号に従ってデータ 978 をデータバッファ 950 に書き込んで、データバッファ 950 を更新する。40

#### 【0093】

なお、アドレス上位信号 708 は、図 6 で説明したビット操作が行なわれている。このため、N 次元参照座標信号 ( $S_0, S_1, \dots, S_t, \dots, S_{N-1}$ ) のどの信号の変化に対しても、キャッシングのミスヒット率は、ほぼ均一となる。

#### 【0094】

このように、本実施形態によれば、N 次元入力の超四面体補間装置 (N は 4 以上の整数) において、N の値が変化してもアドレス下位信号 712 は常に 4 ビットとなり、そのため N の値が変化してもキャッシング機構を変える必要がなく、同一の回路を再利用できる。したがって、N の値に係わらず、多次元 LUT を外部メモリとキャッシング機構とを用いて容易に実現できる。50

**【0095】**

(本発明の他の実施形態)

上述した実施形態の機能を実現するべく各種のデバイスを動作させるように、該各種デバイスと接続された装置あるいはシステム内のコンピュータに対し、前記実施形態の機能を実現するためのソフトウェアのプログラムコードを供給し、そのシステムあるいは装置のコンピュータ(CPUあるいはMPU)に格納されたプログラムに従って前記各種デバイスを動作させることによって実施したものも、本発明の範疇に含まれる。

**【0096】**

また、この場合、前記ソフトウェアのプログラムコード自体が上述した実施形態の機能を実現することになり、そのプログラムコード自体、及びそのプログラムコードをコンピュータに供給するための手段、例えば、かかるプログラムコードを格納した記録媒体は本発明を構成する。かかるプログラムコードを記憶する記録媒体としては、例えばフレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM、磁気テープ、不揮発性のメモリカード、ROM等を用いることができる。

10

**【0097】**

また、コンピュータが供給されたプログラムコードを実行することにより、上述の実施形態の機能が実現されるだけでなく、そのプログラムコードがコンピュータにおいて稼働しているOS(オペレーティングシステム)あるいは他のアプリケーションソフト等と共同して上述の実施形態の機能が実現される場合にもかかるプログラムコードは本発明の実施形態に含まれることは言うまでもない。

20

**【0098】**

さらに、供給されたプログラムコードがコンピュータの機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに格納された後、そのプログラムコードの指示に基づいてその機能拡張ボードや機能拡張ユニットに備わるCPU等が実際の処理の一部または全部を行い、その処理によって上述した実施形態の機能が実現される場合にも本発明に含まれることは言うまでもない。

**【0099】**

これまで述べてきたように、本発明の各実施形態では、N次元のデジタル画像信号205を上位ビット信号205と下位ビット信号214とに分割し、分割した上位ビットの信号すべての組み合わせに対応する参照値を重複することなく $2^{N-1}$ 個のサブメモリ330(多次元LUT260)に分割記憶するとともに、補間演算に必要な(N+1)個の参照値を同時に読み出すようにすることにより、補間演算を高速化することができるとともに、割り算器がなくてもサブメモリ330へアクセスするためのアドレスを生成することができるようにして、色空間の変換などの補間演算を高速に行なえるようにすることが、可及的に小さな回路規模で容易に実現できるようにした。さらに、多次元に拡張するに際して、アドレス生成回路やキャッシュ機構の再設計が必要であり、入力数とビット深度との両方に対し拡張性の高い多次元補間装置を提供することができる。

30

**【図面の簡単な説明】****【0100】**

【図1】本発明の第1の実施形態を示し、カラー複写機の全体構成の一例を示すブロック図である。

40

【図2】本発明の第1の実施形態を示し、多次元補間装置の回路構成の一例を示すブロック図である。

【図3】本発明の第1の実施形態を示し、基準点から対角点までの単位立体の各頂点を、四次元マンハッタン距離を用いて分類した結果を示す図である。

【図4】本発明の第1の実施形態を示し、参照値読み出し部と多次元LUTの回路構成の一例を示すブロック図である。

【図5】本発明の第1の実施形態を示し、アドレス生成回路の構成の一例を示すブロック図である。

【図6】本発明の第1の実施形態を示し、ビット操作部がN次元参照座標信号のビットを

50

操作する方法の一例を説明する図である。

【図7】本発明の第1の実施形態を示し、サブメモリ・バンク生成回路の構成の一例を示す図である。

【図8】本発明の第1の実施形態を示し、サブメモリ・アドレス生成回路の構成の一例を示す図である。

【図9】本発明の第1の実施形態を示し、サブメモリ・バンクIDに対応する参照値の位置を、アドレスが小さい順にマークして示した図である。

【図10】本発明の第2の実施形態を示し、一般化したサブメモリ・バンク生成回路の構成の一例を示す図である。

【図11】本発明の第2の実施形態を示し、一般化したサブメモリ・アドレス生成回路の構成の一例を示す図である。 10

【図12】本発明の第3の実施形態を示し、キャッシュ機構をもった多次元LUTの構成の一例を示す図である。

【図13】本発明の実施形態を示し、3D-LUTを用いて三次元補間演算を行なう場合の機能ブロック図である。

【図14】本発明の実施形態を示し、三次元入力の色空間（RGB空間）を単位立体に分割した状態を示す図である。

【図15】本発明の実施形態を示し、四次元超四面体補間法における稜線の選択方法を説明する図である。

【符号の説明】

【0101】

100 原稿

110 CPU回路部

120 画像読み取り部

130 画像処理部

140 プリンタ部

210 データ分割部

220 参照座標選択部

230 順序判定部

240 重み係数算出部

250 参照点読み出し部

260 多次元LUT

270 補間演算部

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 四 9 】

(b)

(c)

【 図 1 1 】

【 図 1 0 】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 特開平10-307911(JP,A)

特開2003-069841(JP,A)

特開平05-284346(JP,A)

特開2000-201278(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 1/46-62