(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6532066号

(P6532066)

(45) 発行日 令和1年6月19日(2019.6.19)

(24) 登録日 令和1年5月31日(2019.5.31)

(51) Int.Cl.

H01L 21/3065 (2006.01)

F 1

|      |        |      |

|------|--------|------|

| H01L | 21/302 | 105A |

| H01L | 21/302 | 101B |

| H01L | 21/302 | 101D |

| H01L | 21/302 | 101C |

請求項の数 20 (全 18 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2017-551300 (P2017-551300)  |

| (86) (22) 出願日 | 平成28年3月29日 (2016.3.29)        |

| (65) 公表番号     | 特表2018-510515 (P2018-510515A) |

| (43) 公表日      | 平成30年4月12日 (2018.4.12)        |

| (86) 國際出願番号   | PCT/US2016/024661             |

| (87) 國際公開番号   | W02016/160778                 |

| (87) 國際公開日    | 平成28年10月6日 (2016.10.6)        |

| 審査請求日         | 平成31年3月29日 (2019.3.29)        |

| (31) 優先権主張番号  | 62/139,795                    |

| (32) 優先日      | 平成27年3月30日 (2015.3.30)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                 |

|-----------|-----------------------------------------------------------------|

| (73) 特許権者 | 000219967<br>東京エレクトロン株式会社<br>東京都港区赤坂五丁目3番1号                     |

| (74) 代理人  | 100107766<br>弁理士 伊東 忠重                                          |

| (74) 代理人  | 100070150<br>弁理士 伊東 忠彦                                          |

| (74) 代理人  | 100091214<br>弁理士 大貫 進介                                          |

| (72) 発明者  | ランジョン、アロック<br>アメリカ合衆国 ニューヨーク州 121<br>18 メカニックビル マイケル ドライ<br>ヴ 4 |

最終頁に続く

(54) 【発明の名称】原子層をエッティングする方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板をエッティングする方法であって、

エッティングプロセスを促進するように構成されたプラズマ処理システム中に前記基板を配置するステップと、

前記基板の露出面の単層をエッティングするために原子層エッティングプロセスサイクルを行うステップであって、該原子層エッティングプロセスサイクルが、

エッチャントを導入することにより、前記基板の前記露出面上に前記エッチャントを含む吸着単層を形成しながら、同時に、前記露出面における全イオン流束よりも大きい前記露出面におけるエッチャントラジカル流束を達成するために目標とされる印加される出力レベルで電磁力を前記プラズマ処理システムに結合させるステップと、

任意の過剰のエッチャントを除去するために前記プラズマ処理システムをバージするステップと、

前記吸着単層を気体イオンに曝露して前記エッチャントの反応を活性化させることにより、前記エッチャントを含む前記吸着単層を脱着させるステップと、

脱着された前記吸着単層を除去するために前記プラズマ処理システムをバージするステップと、、を連続して含む、ステップと、

目標エッティング深さに到達するまで前記原子層エッティングプロセスサイクルを繰り返すステップと、、を含み、

各プロセスサイクルが前記露出面から前記単層をエッティングし、

10

20

印加される前記出力レベルが 50W 以下である、方法。

【請求項 2】

印加される前記出力レベルが 10W 以下である、請求項 1 に記載の方法。

【請求項 3】

前記基板が置かれる基板ホルダに結合されるバイアス出力として、少なくとも部分的に前記電磁力が前記プラズマ処理システムに結合される、請求項 1 に記載の方法。

【請求項 4】

前記電磁力が排他的にバイアス出力として前記基板ホルダに印加される、請求項 3 に記載の方法。

【請求項 5】

前記基板ホルダに対向しつ向かい合う電極へのソース出力として、追加的な電磁力が前記プラズマ処理システムに結合される、請求項 3 に記載の方法。

【請求項 6】

前記基板が置かれる基板ホルダに対向しつ向かい合う電極に結合されるソース出力として、少なくとも部分的に前記電磁力が前記プラズマ処理システムに結合される、請求項 1 に記載の方法。

【請求項 7】

前記電磁力が排他的に前記基板ホルダと反対側の前記電極へのソース出力として印加される、請求項 6 に記載の方法。

【請求項 8】

前記エッチャントがハロゲン元素を含む、請求項 1 に記載の方法。

【請求項 9】

前記エッチャントがハロゲン化物、ハロメタン、ハロシラン又はそれらの 2 種類以上の組み合わせを含む、請求項 8 に記載の方法。

【請求項 10】

前記エッチャントが、  $C_{12}$ 、  $Br_2$ 、  $F_2$ 、  $HBr$ 、  $BCl_3$ 、  $SF_6$ 、  $NF_3$ 、 形態  $C_xF_y$  (ここで、  $x$  及び  $y$  は 0 を超える実数である) のフルオロカーボン化合物、形態  $C_xF_yH_z$  (ここで、  $x$ 、  $y$  及び  $z$  は 0 を超える実数である) のフッ化炭化水素化合物又はそれらの 2 種類以上の任意の組み合わせを含む、請求項 8 に記載の方法。

【請求項 11】

前記出力レベルが、 100 の値を超える前記基板における前記エッチャントラジカル流束の前記全イオン流束に対する比を達成することを目標とされる、請求項 1 に記載の方法。

【請求項 12】

前記出力レベルが、 1000 の値を超える前記基板における前記エッチャントラジカル流束の前記全イオン流束に対する比を達成することを目標とされる、請求項 1 に記載の方法。

【請求項 13】

前記吸着単層を形成するステップが、プロセスサイクル 1 回当たり 2 秒以下にわたって進行する、請求項 1 に記載の方法。

【請求項 14】

前記吸着単層を形成するステップが、プロセスサイクル 1 回当たり 0.5 秒以下にわたって進行する、請求項 1 に記載の方法。

【請求項 15】

前記基板の前記露出面がシリコンを含み、前記エッチャントが  $C_{12}$  を含み、前記気体イオンが  $Ar$  イオンを含む、請求項 1 に記載の方法。

【請求項 16】

基板をエッチングする方法であって、

エッチングプロセスを促進するように構成されたプラズマ処理システム中に前記基板を配置するステップと、

10

20

30

40

50

前記基板の露出面においてプロセスサイクル 1 回当たり基板材料の 1 つの単層をエッチングするステップであって、各プロセスサイクルが吸着ステップ及び脱着ステップを交互に行うステップを含む、ステップとを含み、

前記吸着ステップが、前記基板の前記露出面上にエッチャントを吸着させながら、前記露出面における全イオン流束よりも大きい前記露出面におけるエッチャントラジカル流束を達成するために 50 W 以下で印加される出力レベルで電磁力を前記プラズマ処理システムに結合させるステップを含み、

前記脱着ステップが、吸着された前記エッチャントと基板材料の前記単層との間の反応を活性化させて、反応生成物を脱着させるステップを含む、方法。

【請求項 17】

前記脱着ステップが、前記基板が置かれる基板ホルダに結合されるバイアス出力、及び前記基板ホルダに対向しあつ向かい合う電極に結合されるソース出力として電磁力を前記プラズマ処理システムに結合させながら、希ガスを前記プラズマ処理システム中に流して、前記反応を活性化させるのに十分なエネルギーを有する気体イオンを形成するステップを含む、請求項 16 に記載の方法。

【請求項 18】

前記吸着ステップと前記脱着ステップとの間及び前記脱着ステップの後に、前記プラズマ処理システムをバージするステップをさらに含む、請求項 16 に記載の方法。

【請求項 19】

印加される前記出力レベルが 20 W 以下である、請求項 16 に記載の方法。

10

【請求項 20】

印加される前記出力レベルが、100 の値を超える前記基板における前記エッチャントラジカル流束の前記全イオン流束に対する比を達成するように調節される、請求項 16 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

本出願は、2015 年 3 月 30 日に出願された米国仮特許出願第 62/139,795 号明細書に関連し、及びそれに対する優先権を主張し、同出願の内容全体が参考により本明細書に援用される。

30

【0002】

本発明は、層をパターン化する方法に関し、特に層をエッチングする方法に関連する。

【背景技術】

【0003】

半導体デバイスの製造におけるコスト及び性能の競争力を維持する必要性から、集積回路のデバイス密度を絶えず増加させる要求が高まっている。また、半導体集積回路の小型化とともに高い集積度を実現するために、半導体基板上に形成される回路パターンの大きさを縮小するための堅牢な手法が必要である。これらの傾向及び要求のために、回路パターンのある層から別の層に転写する能力に対する課題が増加し続けている。

40

【0004】

フォトリソグラフィは、マスク上の幾何学的形状及びパターンを半導体ウエハの表面に転写することによる半導体集積回路の製造に使用される中核技術である。基本的には、感光性材料をパターン化された光に露光することで、現像溶液に対するその溶解性を変化させる。画像形成及び現像が行われると、現像化学に対して可溶性となる感光性材料の一部が除去され、回路パターンが残る。

【0005】

さらに、光リソグラフィを進歩させ、その欠陥に対処するため、半導体製造産業がサブ 30 nm 技術ノードに備えて代替的なパターン化方法を確立するために進歩し続けている。多重パターン化と併用される光リソグラフ (193 i)、EUV (極紫外) リソグラフ

50

イ、及びDSA(誘導自己組織化)パターン化は、積極的なパターン化に対して高まる要求に適合するために評価されている有望な候補の一部と見なされている。

#### 【0006】

半導体集積回路の小型化に有利となることを立証できる別の代表的なリソグラフィ技術の1つは原子層エッティング(ATE)である。ATEでは、エッティングされる基板は、最上部の原子層のみに影響するエッチャントを用いて化学処理される。ページステップによって過剰のエッチャントを除去した後、エッティングステップにより、化学処理された最上原子層が除去される。エッティングされた特徴が所望の深さに到達するまで、化学的改質及びエッティングのサイクルを繰り返すことで、1回ごとに1つの単層が除去される。代表的なプロセスの1つでは、シリコンウエハの最上層を塩素と反応させ、次に、塩素化された最上層のアルゴンプラズマ除去が行われる。

10

#### 【0007】

光リソグラフィ及びEUVリソグラフィを含む高度なパターン化技術に合わせて、高度で高感度のエッティング技術は、サブ30nmの特徴を転写する必要がある。追加的に、高度なエッティングスキームは、特にプロファイル制御、異方性、及び速度の要求に適合させる必要がある。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

本発明の実施形態は、層をパターン化する方法に関し、より具体的には、層をエッティングする方法に関する。

20

#### 【課題を解決するための手段】

#### 【0009】

実施形態によると、基板上の層をエッティングする方法が記載される。基板上の層をエッティングする方法は、エッティングプロセスを促進するように構成されたプラズマ処理システム中に基板を配置するステップと、基板の露出面の単層をエッティングするために原子層エッティングプロセスサイクルを行うステップと、目標深さに到達するまで原子層エッティングプロセスサイクルを繰り返すステップとを含む。各プロセスサイクルは、露出面から単層をエッティングする。原子層エッティングプロセスサイクルは、エッチャントを導入することにより、基板の露出面上にエッチャントを含む吸着単層を形成しながら、同時に、基板における全イオン流束よりも大きい基板におけるエッチャントラジカル流束を達成するために目標とされる出力レベルであって、50W以下である出力レベルで電磁力をプラズマ処理システムに結合させるステップと、任意の過剰のエッチャントも除去するためにプラズマ処理システムをページするステップと、吸着単層を気体イオンに曝露してエッチャントの反応を活性化させることにより、吸着単層を脱着させるステップと、プラズマ処理システムを再びページするステップとを連続して含む。

30

#### 【0010】

本発明のさらなる実施形態では、基板をエッティングする方法は、エッティングプロセスを促進するように構成されたプラズマ処理システム中に基板を配置するステップと、基板の露出面においてプロセスサイクル1回当たり基板材料の1つの単層をエッティングするステップとを含む。各プロセスサイクルは、吸着ステップ及び脱着ステップを交互に行うステップを含む。吸着ステップは、基板の露出面上にエッチャントを吸着させながら、露出面における全イオン流束よりも大きい露出面におけるエッチャントラジカル流束を達成するために50W以下の出力レベルで電磁力をプラズマ処理システムに結合させるステップを含み、脱着ステップは、吸着されたエッチャントと基板材料の単層との間の反応を活性化させて、反応生成物を脱着させるステップを含む。

40

#### 【図面の簡単な説明】

#### 【0011】

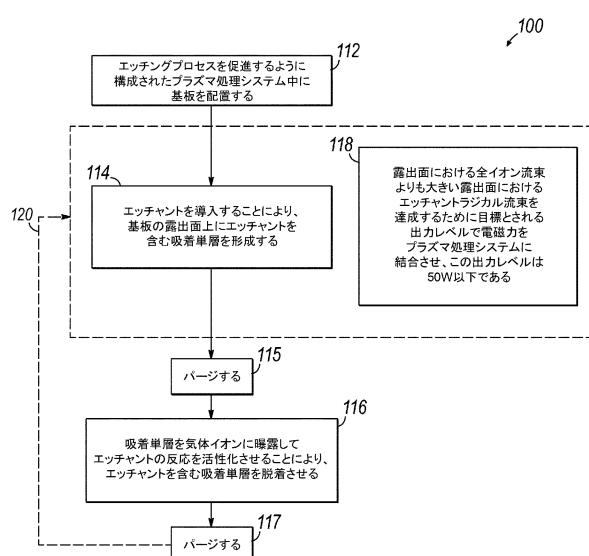

【図1】実施形態による基板上の層をエッティングする方法を示すフローチャートを提示する。

50

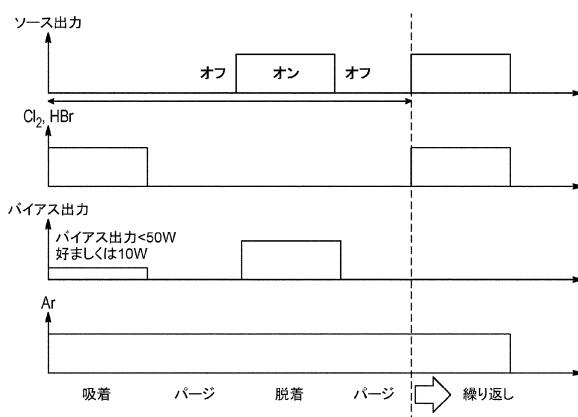

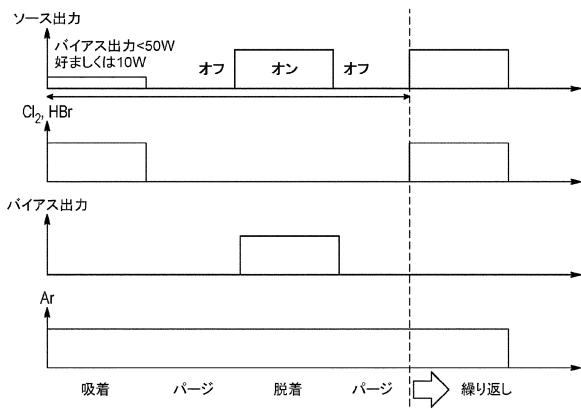

【図2A】基板上の層をエッチングする方法を示す。

【図2B】基板上の層をエッチングする方法を示す。

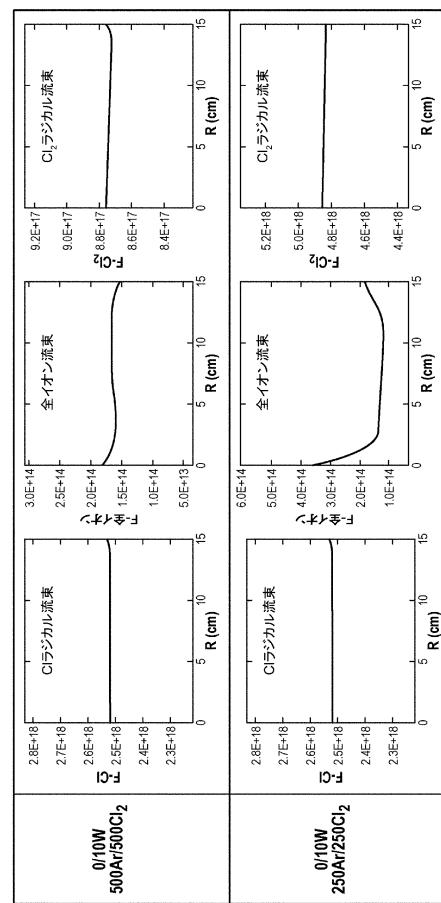

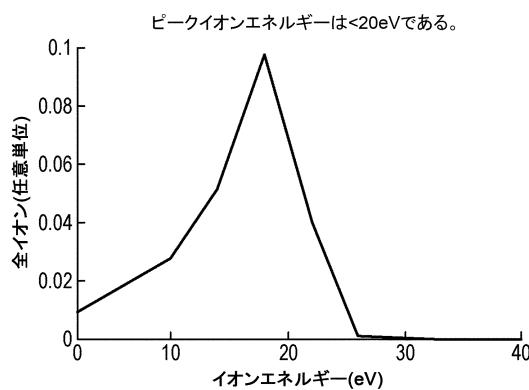

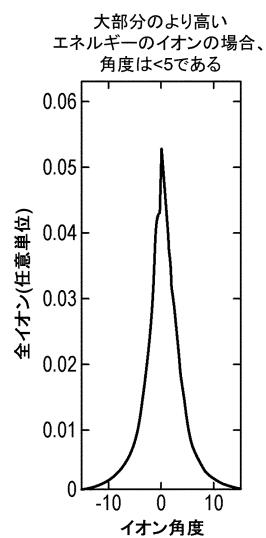

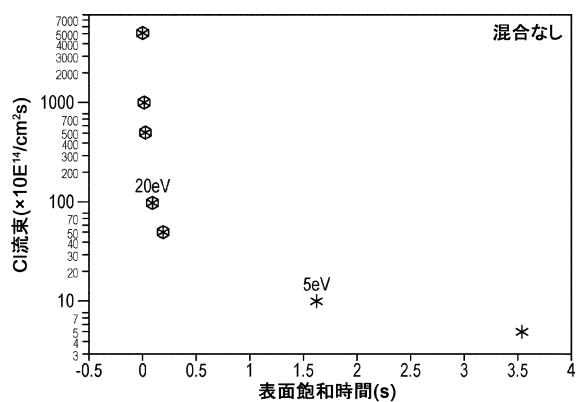

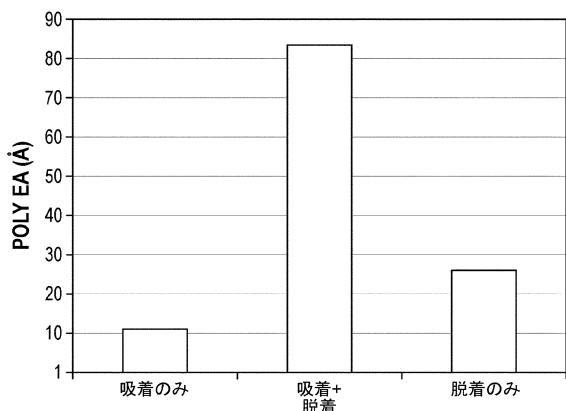

【図3A】実施形態による基板上の層のエッチングの例示的なデータを示す。

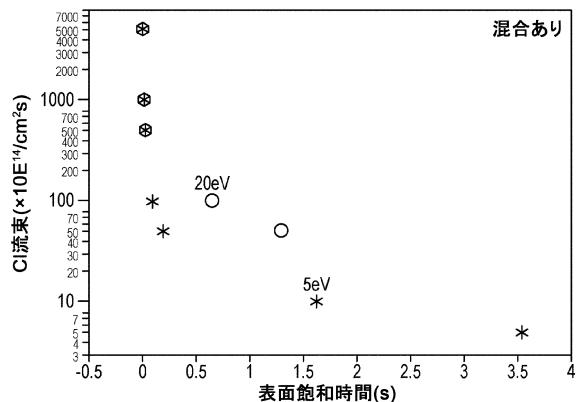

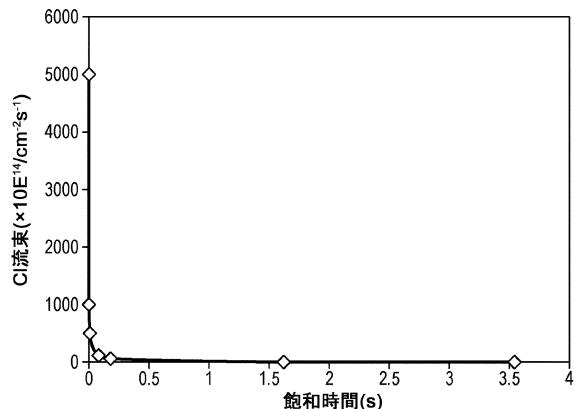

【図3B】実施形態による基板上の層のエッチングの例示的なデータを示す。

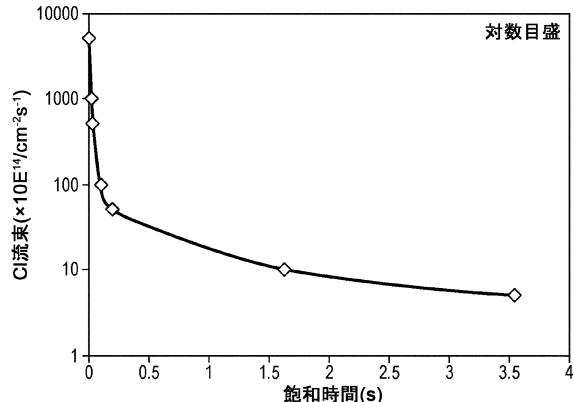

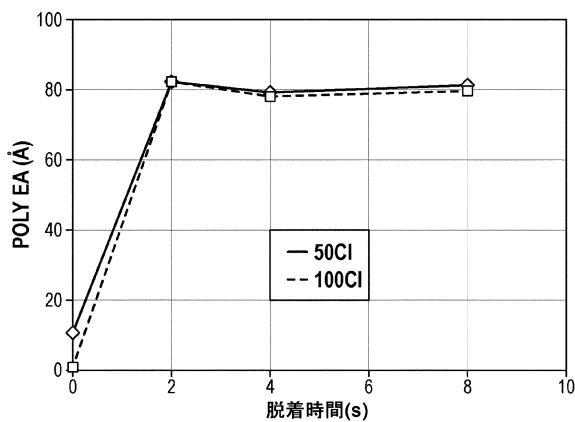

【図3C】実施形態による基板上の層のエッチングの例示的なデータを示す。

【図4A】種々の実施形態による基板上の層のエッチングの例示的なデータを示す。

【図4B】種々の実施形態による基板上の層のエッチングの例示的なデータを示す。

【図4C】種々の実施形態による基板上の層のエッチングの例示的なデータを示す。

【図4D】種々の実施形態による基板上の層のエッチングの例示的なデータを示す。

【図4E】種々の実施形態による基板上の層のエッチングの例示的なデータを示す。

【図4F】種々の実施形態による基板上の層のエッチングの例示的なデータを示す。

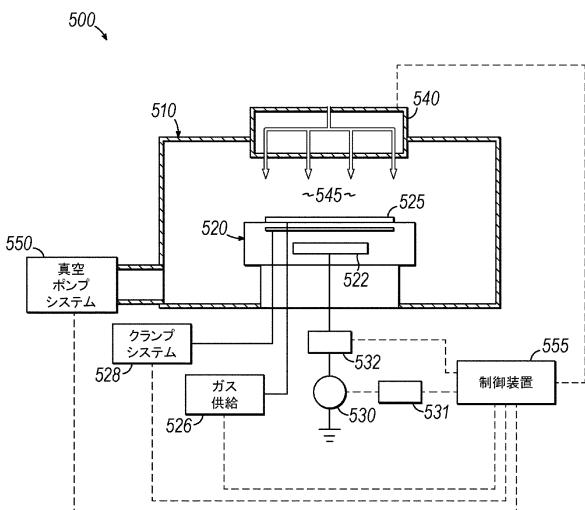

10

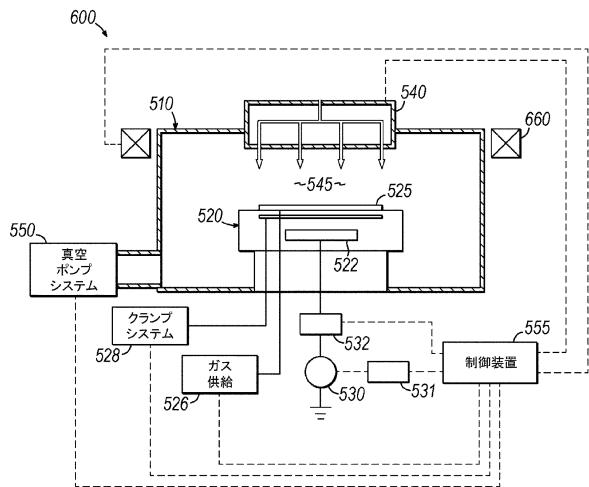

【図5】実施形態によるプラズマ処理システムの概略図を示す。

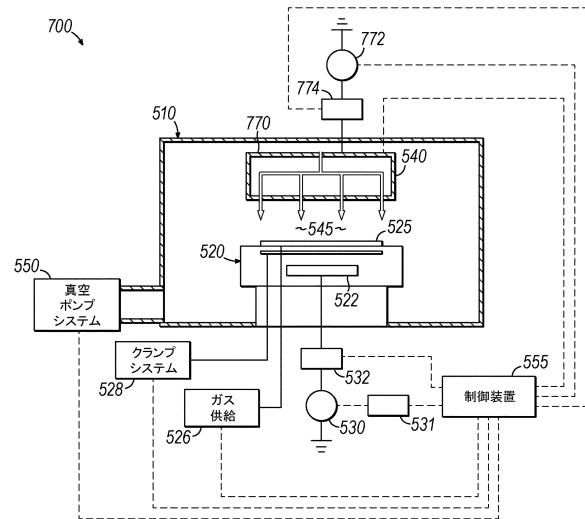

【図6】別の実施形態によるプラズマ処理システムの概略図を示す。

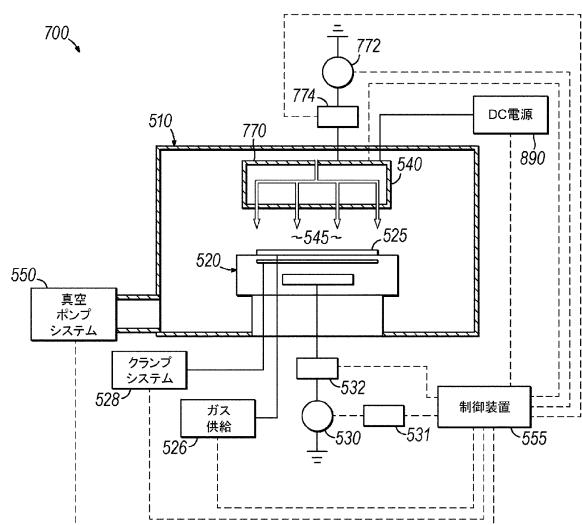

【図7】別の実施形態によるプラズマ処理システムの概略図を示す。

【図8】別の実施形態によるプラズマ処理システムの概略図を示す。

【図9】別の実施形態によるプラズマ処理システムの概略図を示す。

【図10】別の実施形態によるプラズマ処理システムの概略図を示す。

【図11】別の実施形態によるプラズマ処理システムの概略図を示す。

【発明を実施するための形態】

【0012】

20

以下の記載では、説明を目的としており、限定を目的とするものではなく、処理システムの特定の形状、そこで使用される種々の構成要素及びプロセスの説明等の具体的な詳細を記述している。しかし、これらの具体的な詳細から逸脱する別の実施形態で本発明を実施できると理解すべきである。

【0013】

同様に、説明を目的として、本発明の十分な理解を得るために、具体的な数、材料及び構成を記述している。しかし、具体的な詳細を用いずに本発明を実施することが可能である。さらに、図面に示される種々の実施形態は例示的な表現であり、必ずしも縮尺通りに描かれてないことは理解されよう。

【0014】

30

次に、種々の動作は、本発明の理解に最も有用となる方法で複数の別個の動作として説明される。しかし、記載の順序は、これらの動作が必ず順序に依存することを示すものとして解釈すべきではない。特に、これらの動作は、記載される順序で行う必要はない。記載の動作は、記載される実施形態と異なる順序で行うことができる。さらなる実施形態では、種々のさらなる動作を行うことができ、及び／又は記載の動作を省略することができる。

【0015】

本明細書において使用される場合、「放射線感受性材料」という用語は、フォトレジストなどの感光性材料を含むが、必ずしもこれに限定されるものではない。

【0016】

40

本明細書において使用される場合、「基板」は、一般に、本発明により処理される物体を意味する。基板は、デバイス、特に半導体又は他のエレクトロニクスデバイスの任意の材料部分又は構造を含むことができ、たとえば、半導体ウエハなどのベース基板構造又はベース基板構造の上若しくはその上方にある薄膜などの層であってよい。基板は、従来のシリコン基板又は半導体材料の層を含む別のバルク基板であってよい。本明細書において使用される場合、「バルク基板」という用語は、シリコンウエハのみではなく、シリコンオンサファイア（「SOS」）基板及びシリコンオングラス（「SOG」）基板などのシリコンオンインシュレータ（「SOI」）基板、ベース半導体の土台の上のシリコンのエピタキシャル層、ならびに別の半導体又はオプトエレクトロニクス材料、たとえばシリコン・ゲルマニウム、ゲルマニウム、ヒ化ガリウム、窒化ガリウム、及びリン化インジウム

50

も意味し、それらを含んでいる。基板は、ドープされる場合もドープされない場合もある。したがって、基板は、パターン化された又はパターン化されていない任意の特定のベース構造、下にある層、又は上にある層に限定されることを意図するものではなく、むしろ、任意のそのような層又はベース構造、ならびに層及び／又はベース構造の任意の組み合わせを含むことが考慮される。以下の説明では、特定の種類の基板を参照する場合があるが、これは単に説明を目的としており、限定を目的とするものではない。

#### 【0017】

前述のように、高度な方法は、課題に対処し、サブ30nm技術ノードにおける積極的なパターン化に対する要求に適合する必要がある。また、これも記載のように、これらの方法では、それら自体の一連の課題が生じ、これらはエッチングの選択性、速度、及びプロファイル制御の問題として表面化する。パターン化スキームを高選択性エッチングプロセスと問題なく一体化させる能力は、堅牢なパターン転写のために重要となる。

10

#### 【0018】

一例として、回路パターンが最初に形成されると、パターン化された材料は、半導体基板のある領域を覆う保護層として機能し、一方、別の領域は露出し、プラズマエッチングプロセスなどのドライエッチングプロセスを利用して下にある層に回路パターンを転写することができる。パターン化された材料は、特に、光リソグラフィを用いてパターン化された感光性材料、機械的に刻み込まれたパターン化層又は誘導自己組織化層であってよい。最初のパターン化された層中により細い特徴を形成するために、二層マスク又は三層マスクなどの多層スキームを実施することができる。第2又は第3の層が含まれることで、最上パターン化層は、後のドライエッチングプロセスに耐えるために従来選択される厚さよりも薄くなる場合がある。したがって、後のドライエッチング技術に対する要求が高くなる。

20

#### 【0019】

プラズマエッチングプロセスでは、半導体基板は、下にある層を選択的に除去しながら保護層を最小限で除去するエッチング化学に曝露される。下にある層と好都合な反応が可能であり、保護層とのあまり好ましくない反応が最小限となる原子／分子成分を有するイオン化可能な解離性気体混合物から、このエッチング化学が誘導される。プラズマの存在下、このエッチング化学は、エネルギー電子を有するその原子／分子成分の相互作用、たとえば衝突によって形成され、たとえば、その衝突の一部は解離衝突であり、他の衝突はイオン化衝突である。複雑な機構により、特にエッチング選択性、エッチング速度及びプロファイルを含む数種類の相互に関連するエッチング指標に関して許容される値を達成するようにプラズマが操作される。また、前述のように、減少し続けるパターンの大きさとともに、ある材料を別の材料に対して選択的に除去しながら、別のパターン指標（たとえば、粗さ、欠陥など）に十分適合する能力は、堅牢なパターン転写のためにきわめて重要なになってきている。特に、後のドライエッチングプロセスのエッチング選択性により、パターンを下にある層に十分に転写できるようにリソグラフィ層が保護される必要がある。さらに、エッチング選択性は重要な問題であるが、パターン完全性（たとえば、粗さ、欠陥など）も維持される必要があり、より好ましくは改善される必要がある。

30

#### 【0020】

これより図面を参照すると、いくつかの図面にわたって同様の参照番号は同一又は対応する部分を示し、図1、2A及び2Bは、実施形態による基板上の層をエッチングする方法を示す。この方法は、図2A及び2Bに図で示されており、図1にフローチャート100によって示されている。図1に示されるように、フローチャート100は、112において、エッチングプロセスを促進するように構成されたプラズマ処理システム中に基板を配置するステップから始まる。

40

#### 【0021】

基板は、エッチング又はパターン化が行われる層を有するパターン化層を含むことができる。パターン化層により、開放された特徴のパターンを上に有する1つ以上のさらなる層を確定することができる。基板は、デバイス層をさらに含む。デバイス層は、パターン

50

が転写される基板上に任意の薄膜又は構造を含むことができる。たとえば、デバイス層は、シリコン含有反射防止コーティング（「SiARC」）を含むことができる。

【0022】

基板としては、バルクシリコン基板、単結晶シリコン（ドープされたあるいはドープされていない）基板、セミコンダクターオンインシュレータ（SOI）基板又はたとえばSi、SiC、SiGe、SiGeC、Ge、GaAs、InAs、InP、その他のII/V若しくはII/V化合物半導体若しくはそれらの任意の組み合わせを含有する任意の別の半導体基板（II族、III族、V族及びVI族は、元素周期表の古典的な、すなわち古いIUPAC表記法を意味し、改定された、すなわち新しいIUPAC表記によると、これらの族はそれぞれ2族、13族、15族及び16族を意味する）を含むことができる。基板は、任意のサイズのものであってよく、たとえば、200mm（ミリメートル）基板、300mm基板、450mm基板又はさらに大きい基板であってよい。デバイス層は、パターンが転写可能である任意の膜又はデバイス構造を含むことができる。

【0023】

114では、たとえば第1のパルス時間にわたってエッチャントを導入することにより、基板の露出面上にエッチャントを含む吸着单層が形成される。エッチャントは、特に、ハロゲン（たとえば、Cl<sub>2</sub>、F<sub>2</sub>、Br<sub>2</sub>）、ハロゲン化物（HBr）、ハロメタン、ハロシラン、フルオロカーボン、又はハイドロフルオロカーボンなどのハロゲン含有気体を含むことができる（図2A、2B参照）。たとえば、エッチャントは、Cl<sub>2</sub>、Br<sub>2</sub>、F<sub>2</sub>、HBr、BCl<sub>3</sub>、SF<sub>6</sub>、NF<sub>3</sub>、形態C<sub>x</sub>F<sub>y</sub>（ここで、x及びyは0を超える実数である）のフルオロカーボン化合物、形態C<sub>x</sub>F<sub>y</sub>H<sub>z</sub>（ここで、x、y及びzは0を超える実数である）のフッ化炭化水素化合物又はそれらの2種類以上の任意の組み合わせを含むことができる。

【0024】

115では、任意の過剰のエッチャントも除去するためにプラズマ処理システムがページされる。

【0025】

116では、たとえば第2のパルス時間にわたって吸着单層を気体イオン、すなわちプラズマに曝露して、エッチャントの反応を活性化させることにより、吸着单層が脱着される。気体イオンの原料ガスは、たとえばAr、Ne及び/又はHeなどの希ガス又はN、O、C、Hなどの任意の別の元素を含むことができる。第2のパルス時間は3秒以下であってよい。たとえば、第2のパルス時間は、2秒若しくは1秒又はそれらの任意の小数部分であってよい。

【0026】

原料ガスをプラズマ処理システム中に流し、基板が置かれる基板ホルダに結合されるバイアス出力として、及び基板ホルダと対向して向かい合う電極へのソース出力として電磁力をプラズマ処理システムに結合させ、原料ガスのプラズマを発生させて維持することにより、気体イオンを形成することができる。気体イオンが、吸着单層を含む基板の露出面上に、吸着原子と露出面の基板材料の原子との間の反応を活性化させるのに十分なエネルギーで衝撃を与えることで反応生成物が脱着し、それによって单層が除去される。非限定的な例として、バイアス出力は約150Wであってよく、一方、ソース出力は約2500Wである。

【0027】

117では、プラズマ処理システムがもう一度ページされ、この時点で、脱着された吸着单層が除去される。

【0028】

118では、114の吸着单層の形成と同時に、第1のパルス時間中、基板における全イオン流束よりも大きい基板におけるエッチャントラジカル流束を達成するために目標とされる出力レベルで電磁力をプラズマ処理システムに結合させる。出力レベルは50W以下であってよい。実施形態では、出力レベルは、100の値を超える基板におけるエッチャ

10

20

30

40

50

ヤントラジカル流束の全イオン流束に対する比を達成することが目標とされる。別の実施形態では、出力レベルは、1000の値を超える基板におけるエッチャントラジカル流束の全イオン流束に対する比を達成することが目標とされる。

【0029】

118における電磁力は、基板が上に置かれる基板ホルダに結合されるバイアス出力として、少なくとも部分的にプラズマ処理システムに結合されうる。さらに、電磁力は、そのようなバイアス出力として排他的に印加することができる。さらなる電磁力は、基板ホルダと対向しつ向かい合う電極へのソース出力としてプラズマ処理システムに結合されうる。あるいは、電磁力の唯一の供給源は、対向する電極上のソース出力であってよい。バイアス出力として、ソース出力として、又はその両方としてのいずれで印加されるとしても、114における吸着単層の形成中の118における電磁力は、単層の脱着中に116において気体イオンを形成するために印加される出力よりもはるかに小さい。

【0030】

120では、図2A及び2Bに示されるように、目標深さに到達するまで114における吸着単層の形成と116における吸着単層の脱着とを交互に繰り返すことにより、基板の露出面は、プロセスサイクル1回当たり1つの反応層又は単層がエッティングされる。本発明の実施形態によると、114における吸着ステップは、基板における全イオン流束よりも大きい基板におけるエッチャントラジカル流束を達成するための低EM出力を含み、一方、116における脱着ステップは、反応を活性化させかつ反応生成物を脱着させるのに十分なイオンエネルギーに基板を曝露するプラズマを形成するための高EM出力を含む。この交互のステップは、エッチャントガスとイオン用の原料ガスとの間のパルスの気流又は交番する気流を含むことができる。たとえば、図2A及び2Bの図において、Ar流は、記載の連続流ではなく、吸着ステップ中に停止させ、脱着ステップ中にパルスで流すことができる。代替的には、図示するように、Arガスは、バージガスとして及び脱着ステップの原料ガスとして機能させるために、プロセスサイクル全体にわたって連続的に(continuously)流すことができる。連続流は、同じ流量の場合もあり、又は吸着中により少ない流量、脱着中により多い流量を含む場合もある。連続流の場合、原料ガスは、吸着ステップ中の基板及びエッチャントに対して、希ガスなどの非反応性となるべきであり、それにより、プロセスサイクルの脱着ステップ中にプラズマを形成するために十分高いレベルのソース出力及びバイアス出力を供給することで、脱着反応のみが活性化される。

【0031】

限定的なものではなく、単なる例として、プロセスサイクルの総数は、1サイクル~100サイクル、10サイクル~90サイクル、20サイクル~80サイクル又は30サイクル~70サイクルの範囲であってよい。ある実施形態では、エッティングサイクルの総数は、50サイクル、40サイクル、若しくは30サイクル又はそれらの間の任意の整数のサイクルであってよい。各サイクルによって基板から材料の単層が除去されるため、繰り返すべきサイクルの数は、表面をエッティングすべき目標深さによって決定される。基板がエッティングされる速度、すなわちエッティング速度を求めることが可能である。ある実施形態では、エッティング速度は1 / sを超える。たとえば、エッティング速度は、1.1 / s、1.2 / s、1.3 / s、1.4 / s、1.5 / s又はさらに速くてよい。少なくとも1つの実施形態では、エッティング速度は1.3 / sを超える。

【0032】

印加されるEM出力が低出力条件未満(たとえば、50W未満、40W未満、30W未満、20W未満、10W未満など)となる場合、エッチャントの吸着が非常に速くなる。理論によって束縛しようとするものではないが、本発明者らは、このプロセス条件下でラジカル流束がイオン流束よりも大きく(図3A参照)、部分的には基板表面においてイオン流束に対して増加したこのラジカル流速のために、吸着が速い速度で起こりうることを確認した。基板表面におけるラジカル流束のイオン流束に対する比は100を超えることができ、さらには1000を超えることができる。さらに、プロセス条件により、低イオンエネルギー(たとえば20eV未満)及び比較的狭いイオンエネルギー角度分布(たと

10

20

30

40

50

えば5度未満)を実現することができる(図3B、3C参照)。

【0033】

プロセス全体にわたり、プラズマ処理システムに真空を印加することができる。たとえば、真空は、吸着単層の形成及び/又は吸着単層の脱着の間に印加することができる。ある実施形態では、プラズマ処理システム中の圧力は100mTorr以下であってよい。たとえば、プラズマ処理システム中の圧力は約60mTorr以下であってよい。

【0034】

エッチャントがハロゲン含有材料を含む場合、エッチングされる表面のハロゲン化が迅速に起こり、すなわち2秒未満又は1秒未満、さらには0.5秒未満で起こる(図4A~4E参照)。当然ながら、ハロゲン化は、前述の時間の値の任意の小数部分で起こってよい。吸着及び脱着の両方のサイクルを行う場合、エッチング量は、吸着サイクル単独又は脱着サイクル単独のいずれかが行われる場合のエッチング量よりもはるかに多い(図4F参照)。

【0035】

表1は、例示的なプロセスのパラメータを示し、それらの結果は図4Eに示されている。圧力、温度、流量及び組成、ソース出力及びバイアス出力、RDCなどは、別の例ではすべて異なる場合がある。RDC値は、エッチャント及び反応ガスの導入に関するガス流分配パラメータを意味する。ある実施形態では、ガス分配システムは、中央ガス供給ゾーン及び端部ガス分配ゾーンを含むことができる。RDCパラメータの値は、中央及び端部のガス分配ゾーンに分配される気流の相対量を示す。RDC=50の場合、端部ガス分配ゾーンに連結されるガス流は中央ガス分配ゾーンに連結されるガス流と等しく、RDC=5の場合、ガス流の95%が中央ガス分配ゾーンに連結される。RDC値は、本発明において限定されるものではなく、たとえば5(5/95)~20(20/80)又はそれを超えて変動させることができる。

【0036】

【表1】

| ステップ | 圧力<br>[mTorr] | ソース<br>出力<br>[W] | バイアス<br>出力<br>[W] | ガス流 [sccm]      |      | RDC | 温度. [°C]       |                |                     | 時間<br>[s]      | Dyn.<br>Proc. <sup>4</sup> |

|------|---------------|------------------|-------------------|-----------------|------|-----|----------------|----------------|---------------------|----------------|----------------------------|

|      |               |                  |                   | Cl <sub>2</sub> | Ar   |     | C <sup>1</sup> | E <sup>2</sup> | Chill. <sup>3</sup> |                |                            |

| 吸着   | 60            | 0                | 10                | 50,100          | 100  | 5   | 30             | 30             | 10                  | 2              | 30                         |

| 脱着   | 60            | 2500             | 150               | 0               | 1000 | 5   | 30             | 30             | 10                  | V <sup>5</sup> |                            |

<sup>1</sup>電極中央における

<sup>2</sup>電極端部における

<sup>3</sup>冷却システム温度

<sup>4</sup>吸着/脱着サイクルの総数

<sup>5</sup>変動する(たとえば、図4E参照)

【0037】

前述し、表1に示される例で示されるように、ラジカル流束がイオン流束よりも大きくなる場合、ハロゲン化(「吸着」)は迅速に起こり、すなわち2秒未満で起こる。なんらかの特定の理論によって束縛しようと意図するものではないが、増加するC1ラジカル流束のイオン流束に対する増加する比において、(Siをエッチングする場合)表面がSiC1で飽和すると考えられる。さらに、図4Eに示されるデータは、脱着サイクルがある条件下で横ばい状態になりうることを示し、そのため、連続脱着ガス流を用いる場合でさえも、ある時間後にさらなるエッチングが最小限となりうる。たとえば、図4Eに示される結果では、2秒の脱着時間後にエッチング量が横ばいとなる。このような結果は、脱着ガスの消費を最小限にでき、本発明の方法に要する時間を最適化できることを示唆している。換言すると、脱着サイクルは自己制御型である。

10

20

30

40

50

## 【0038】

前述の種々の実施形態による基板上の層をエッティングする方法は、図5～11に示され後述されるプラズマ処理システムのいずれか1つで行うことができる。しかし、議論されるこれらの方法は、この例示的な提示による範囲に限定されるものではない。

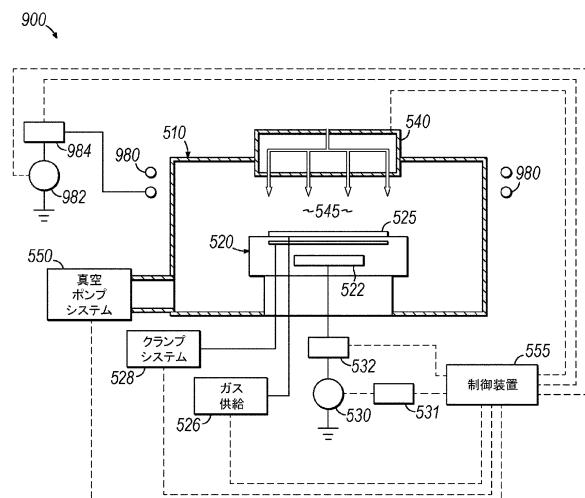

## 【0039】

図5に示される実施形態によると、前述のプロセス条件を実施するために構成されたプラズマ処理システム500は、プラズマ処理チャンバー510、処理される基板525が取り付けられる基板ホルダ520及び真空ポンプシステム550を含む。基板525は、半導体基板、ウエハ、フラットパネルディスプレイ又は液晶ディスプレイであってよい。プラズマ処理チャンバー510は、基板525の表面の近くのプラズマ処理領域545中の10プラズマの発生が促進されるように構成することができる。ガス分配システム540を介してイオン化可能なガス又はプロセスガス混合物が供給される。特定のプロセスガス流の場合、プロセス圧力は真空ポンプシステム550を用いて調節される。あらかじめ決定された材料の処理に特有の材料を得るために、及び／又は基板525の露出面からの材料の除去を促進するために、プラズマを使用することができる。プラズマ処理システム500は、200mm基板、300mm基板又はより大型のものなどの任意の所望のサイズの基板の処理のために構成することができる。

## 【0040】

基板525は、機械的クランプシステム又は電気的クランプシステム（たとえば、静電クランプシステム）などのクランプシステム528によって基板ホルダ520に取り付けることができる。さらに、基板ホルダ520は、基板ホルダ520及び基板525の温度の調節及び／又は制御のために構成される加熱システム（図示せず）又は冷却システム（図示せず）を含むことができる。加熱システム又は冷却システムは、冷却の場合には基板ホルダ520から熱を受け取り熱交換器システム（図示せず）に熱を伝達し、又は加熱の場合には熱交換器から基板ホルダ520に熱を伝達する伝熱流体の再循環流を含むことができる。別の実施形態では、抵抗加熱要素又は熱電気加熱器／冷却器などの加熱／冷却要素を基板ホルダ520、ならびにプラズマ処理チャンバー510のチャンバー壁及びプラズマ処理システム500中の任意の他の構成要素に含むことができる。

## 【0041】

さらに、基板525と基板ホルダ520との間のガスギャップ熱伝導を改善するために、裏面ガス供給システム526により、伝熱ガスを基板525の裏面に供給することができる。高温又は低温における基板の温度制御が必要な場合、このようなシステムを利用することができる。たとえば、裏面ガス供給システムは、2ゾーンガス分配システムを含むことができ、基板525の中央と端部との間でヘリウムガスギャップ圧力が独立に変動することができる。

## 【0042】

図5に示される実施形態では、基板ホルダ520は電極522を含むことができ、それによってRF出力がプラズマ処理領域545中の処理用プラズマに結合される。たとえば、基板ホルダ520は、任意選択のインピーダンス整合ネットワーク532を介したRF発生器530から基板ホルダ520へのRF出力の伝達により、RF電圧で電気的にバイアスをかけることができる。RFバイアスは、電子を加熱してプラズマを形成し維持する機能を果たすことができる。この構成では、システムは反応性イオンエッティング（RIE）反応器として動作することができ、チャンバー及び上部ガス注入電極は、接地面として機能する。RFバイアの典型的な周波数は約0.1MHz～約100MHzの範囲となる。プラズマ処理用の種々のRFシステムが周知であり、さらなる議論は行わない。

## 【0043】

さらに、RF電圧での電極522の電気バイアスは、パルスバイアス信号制御装置531を用いてパルス化することができる。RF発生器530からのRF出力は、たとえばオフ状態とオン状態との間でパルス化することができる。

## 【0044】

10

20

30

40

50

あるいは、R F 出力は、複数の周波数で基板ホルダ電極に印加される。さらに、インピーダンス整合ネットワーク 532 は、反射される出力を減少させることによってプラズマ処理チャンバー 510 中のプラズマへの R F 出力の移動を改善することができる。種々の整合ネットワークトポロジー、たとえば L 型、I 型、T 型など、及び自動制御方法が周知であり、それらを開示されるシステムとともに使用することができる。

#### 【0045】

ガス分配システム 540 は、プロセスガス混合物を導入するためのシャワーヘッド設計を含むことができる。あるいは、ガス分配システム 540 は、プロセスガス混合物を導入し、基板 525 上でのプロセスガス混合物の分配を調節するためのマルチゾーンシャワーヘッド設計を含むことができる。たとえば、マルチゾーンシャワーヘッド設計は、基板 525 上の実質的に中央の領域へのプロセスガスの流れ又は組成の量に対して、基板 525 上の実質的に周辺の領域へのプロセスガスの流れ又は組成を調節するように構成することができる。

#### 【0046】

真空ポンプシステム 550 は、最大約 5000 リットル / 秒 (以上) のポンプ速度が可能なターボ分子真空ポンプ (TMP) と、チャンバー圧力を調節するためのゲートバルブとを含むことができる。ドライプラズマエッチングに使用される従来のプラズマ処理装置では、1000 リットル / 秒 ~ 3000 リットル / 秒の TMP を使用することができる。TMP は、たとえば約 50 m Torr 未満の低圧処理の場合に有用である。高圧処理の場合 (すなわち、約 100 m Torr を超える)、メカニカルブースターポンプ及びドライ粗引きポンプを使用することができる。さらに、チャンバー圧力を監視するための装置 (図示せず) をプラズマ処理チャンバー 510 に連結することができる。

#### 【0047】

制御装置 555 は、マイクロプロセッサと、メモリと、プラズマ処理システム 500 への入力の伝達及び起動を行い、プラズマ処理システム 500 からの出力を監視するのに十分な制御電圧を発生させることができるデジタル I/O ポートとを含む。さらに、制御装置 555 は、R F 発生器 530、パルスバイアス信号制御装置 531、インピーダンス整合ネットワーク 532、ガス分配システム 540 及び真空ポンプシステム 550 並びに基板加熱 / 冷却システム (図示せず)、裏面ガス供給システム 526、及び / 又は静電クラインプシステム 528 に連結することができ、それらと情報交換を行うことができる。たとえば、プラズマエッチングプロセスなどのプラズマ支援プロセスを基板 525 に対して行うためのプロセスレシピによりプラズマ処理システム 500 の前述の構成要素への入力を起動するために、メモリに記憶されたプログラムを利用することができる。

#### 【0048】

制御装置 555 は、プラズマ処理システム 500 に対して近く又は離れてのいずれかで設置することができる。たとえば、制御装置 555 は、直接接続、イントラネット、及び / 又はインターネットを用いてプラズマ処理システム 500 とデータ交換することができる。制御装置 555 は、たとえば顧客サイト (すなわち装置のメーカーなど) でイントラネットに接続することができ、又はたとえばベンダーサイト (すなわち設備の製造元) でイントラネットに接続することができる。これとは別にあるいはこれに加えて、制御装置 555 はインターネットに接続することができる。さらに、別のコンピュータ (すなわち、制御装置、サーバーなど) が、直接接続、イントラネット及び / 又はインターネットによって制御装置 555 にアクセスしてデータ交換を行うことができる。

#### 【0049】

図 6 に示される実施形態では、プラズマ処理システム 600 は、図 5 の実施形態と同様であってよく、図 5 を参照して記載された構成要素に加えて、場合によりプラズマ密度を増加させ、及び / 又はプラズマ処理の均一性を改善するために、固定式、又は機械的若しくは電気的に回転する磁界システム 660 のいずれかをさらに含むことができる。さらに、回転速度及び磁界強度を調節するために、制御装置 555 が磁界システム 660 に連結することができる。回転磁界の設計及び実現は周知であり、さらなる議論は行わない。

10

20

30

40

50

## 【0050】

図7に示される実施形態では、プラズマ処理システム700は、図5又は図6の実施形態と同様であってよく、任意選択のインピーダンス整合ネットワーク774によってRF発生器772からのRF出力を結合可能な上部電極770をさらに含むことができる。上部電極にRF出力を印加するための周波数は約0.1MHz～約200MHzの範囲であってよい。さらに、下部電極への出力の印加のための周波数は約0.1MHz～約100MHzの範囲であってよい。さらに、上部電極770へのRF出力の印加を制御するために、制御装置555がRF発生器772及びインピーダンス整合ネットワーク774に連結される。上部電極の設計及び実現は周知であり、さらなる議論は行わない。上部電極770及びガス分配システム540は、図示されるように同じチャンバーアセンブリ内に設計することができる。あるいは、上部電極770は、基板525の上のプラズマに結合するRF出力分布を調節するためのマルチゾーン電極設計を含むことができる。たとえば、上部電極770は、中央電極及び端部電極にセグメント化することができる。図7に示される実施形態は、たとえばSiARCを含むデバイス層をエッチングするために有利に使用することができる。10

## 【0051】

図8に示される実施形態では、プラズマ処理システム800は、図7の実施形態と同様であってよく、基板525と向かい合う上部電極770に連結した直流(DC)電源890をさらに含むことができる。上部電極770は電極板を含むことができる。この電極板はシリコン含有電極板を含むことができる。さらに、電極板はドープされたシリコンの電極板を含むことができる。DC電源890は可変DC電源を含むことができる。さらに、DC電源890はバイポーラDC電源を含むことができる。DC電源890は、DC電源890の極性、電流、電圧又はオン／オフ状態の監視、調節又は制御の少なくとも1つを行うように構成されたシステムをさらに含むことができる。プラズマが形成されると、DC電源890によって弾道電子ビームの形成が促進される。電気フィルター(図示せず)を用いて、DC電源890からRF出力を分離することができる。20

## 【0052】

たとえば、DC電源890によって上部電極770に印加されるDC電圧は、約-2000ボルト(V)～約1000Vの範囲であってよい。たとえば、DC電圧の絶対値は約100V以上の値を有することができ、又はDC電圧の絶対値は約500V以上の値を有することができる。前述のように、DC電圧は負の極性を有することができる。たとえば、DC電圧は、上部電極770の表面上に生成される自己バイアス電圧よりも大きい絶対値を有する負の電圧であってよい。基板ホルダ520に面する上部電極770の表面は、シリコン含有材料から構成されてよい。30

## 【0053】

図9に示される実施形態では、プラズマ処理システム900は、図5及び6の実施形態と同様であってよく、RF出力がRF発生器982を介して任意選択のインピーダンス整合ネットワーク984を通して結合される誘導コイル980をさらに含むことができる。RF出力は、誘導コイル980から誘電体窓(図示せず)を介してプラズマ処理領域545に誘導結合される。誘導コイル980へのRF出力の印加のための周波数は約10MHz～約100MHzの範囲であってよい。同様に、チャック電極への出力の印加のための周波数は約0.1MHz～約100MHzの範囲であってよい。さらに、誘導コイル980とプラズマ処理領域545中のプラズマとの容量結合を減少させるためにスロット付きファラデーシールド(図示せず)を使用することができる。さらに、誘導コイル980への出力の印加を制御するために、制御装置555をRF発生器982及びインピーダンス整合ネットワーク984に連結することができる。40

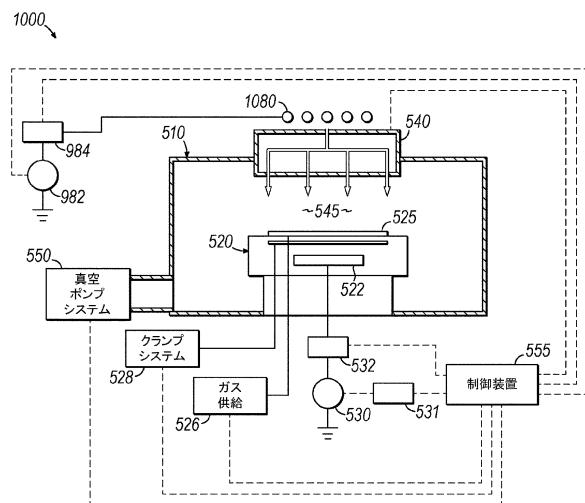

## 【0054】

図10に示されるような別の実施形態では、プラズマ処理システム1000は、図9の実施形態と同様であってよく、トランス結合プラズマ(TCP)反応器のように、上からプラズマ処理領域545と連絡する「スパイラル」コイル又は「パンケーキ」コイルであ50

る誘導コイル 1080 をさらに含むことができる。誘導結合プラズマ ( ICP ) 源又はトランク結合プラズマ ( TCP ) 源の設計及び実現は周知であり、さらなる議論は行わない。

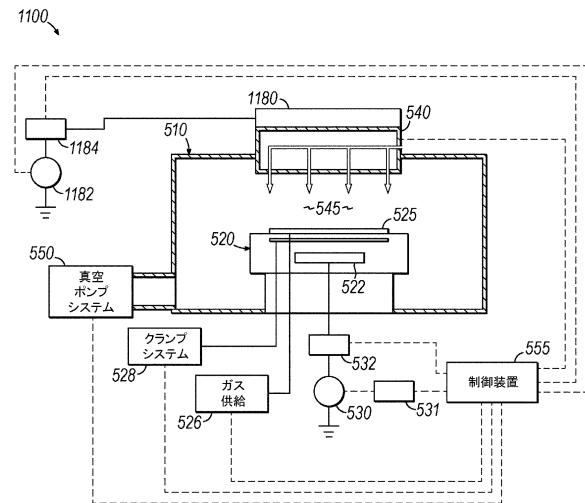

### 【 0055 】

あるいは、プラズマは電子サイクロトロン共鳴 ( ECR ) を用いて形成することができる。さらに別の実施形態では、プラズマはヘリコン波を発射することで形成される。さらに別の実施形態では、プラズマは伝搬表面波から形成される。上記の各プラズマ源は周知であり、さらなる議論は行わない。

### 【 0056 】

図 11 に示される実施形態では、プラズマ処理システム 1100 は、図 5 の実施形態と同様であってよく、表面波プラズマ ( SWP ) 源 1180 をさらに含むことができる。 SWP 源 1180 は、マイクロ波出力がマイクロ波発生器 1182 を介して任意選択のインピーダンス整合ネットワーク 1184 を通して連結されるラジアルラインスロットアンテナなどのスロットアンテナを含むことができる。

10

### 【 0057 】

本発明の特定の実施形態のみを以上に詳細に説明してきたが、当業者であれば、本発明の新規な教示及び利点から実質的に逸脱することなく、実施形態における多くの修正形態が可能であることを容易に理解するものである。したがって、すべてのこのような修正形態を本発明の範囲内に含めることを意図している。

20

【 図 1 】

【 図 2 A 】

【図 2 B】

【図 3 A】

【図 3 B】

【図 3 C】

【図4 A】

【図4 C】

【図4 B】

【図4 D】

【図4 E】

【図5】

【図4 F】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(72)発明者 シェルパ, ソナム

アメリカ合衆国 ニューヨーク州 12203 オールバニー フラー ロード 255 ナンバ

- 244

(72)発明者 ワーン, ミーンメイ

アメリカ合衆国 ニューヨーク州 12203 オールバニー フラー ロード 255 ナンバ

- 244

審査官 宇多川 勉

(56)参考文献 特表2012-529777 (JP, A)

米国特許出願公開第2014/0206192 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3065