(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4127467号

(P4127467)

(45) 発行日 平成20年7月30日(2008.7.30)

(24) 登録日 平成20年5月23日(2008.5.23)

(51) Int.Cl.

F 1

|                    |                  |             |         |

|--------------------|------------------|-------------|---------|

| <b>H01L 29/786</b> | <b>(2006.01)</b> | H01L 29/78  | 6 1 3 A |

| <b>H01L 21/336</b> | <b>(2006.01)</b> | H01L 29/78  | 6 2 7 Z |

| <b>H01L 21/265</b> | <b>(2006.01)</b> | H01L 21/265 | P       |

| <b>G02F 1/1368</b> | <b>(2006.01)</b> | H01L 21/265 | F       |

| <b>G09F 9/30</b>   | <b>(2006.01)</b> | H01L 29/78  | 6 1 7 L |

請求項の数 15 (全 26 頁) 最終頁に続く

(21) 出願番号

特願2001-303671 (P2001-303671)

(22) 出願日

平成13年9月28日 (2001.9.28)

(65) 公開番号

特開2002-222960 (P2002-222960A)

(43) 公開日

平成14年8月9日 (2002.8.9)

審査請求日 平成16年4月2日 (2004.4.2)

(31) 優先権主張番号 特願2000-336836 (P2000-336836)

(32) 優先日 平成12年11月6日 (2000.11.6)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(72) 発明者 中嶋 節男

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 大沼 英人

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 牧田 直樹

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁体上に非晶質半導体層を形成する第1の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第2の工程と、

前記触媒元素の添加された非晶質半導体層を加熱して結晶性半導体層を得る第3の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第4の工程と、

前記ゲート絶縁膜上に導電膜を設け、前記導電膜をエッティングして後にnチャネル型TFTのゲート電極となる第1の導電層および、後にpチャネル型TFTのゲート電極となる第2の導電層を形成する第5の工程と、

前記第1の導電層および前記第2の導電層をマスクにして前記半導体層にn型不純物元素を添加する第6の工程と、

前記第1の導電層および前記第2の導電層をエッティングして、nチャネル型TFTのゲート電極および後にpチャネル型TFTのゲート電極となる第3の導電層をそれぞれ形成する第7の工程と、

前記nチャネル型TFTのゲート電極及び前記第3の導電層をマスクにして前記半導体層にn型不純物元素を添加する第8の工程と、

nチャネル型TFTとなる領域をレジストからなるマスクで覆い、前記第3の導電層をエッティングしてpチャネル型TFTのゲート電極を形成した後、前記pチャネル型TFTの半導体層にp型不純物元素を添加する第9の工程と、を有し、

10

20

前記 n チャネル型 TFT における n 型不純物元素が添加される領域と比較して、前記 p チャネル型 TFT における n 型不純物元素が添加される領域が狭くなるように、前記第 2 の導電層は前記第 1 の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第 3 の導電層は前記 n チャネル型 TFT のゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする半導体装置の作製方法。

### 【請求項 2】

絶縁体上に非晶質半導体層を形成する第 1 の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第 2 の工程と、

前記触媒元素の添加された非晶質半導体層を加熱することにより結晶性半導体層とし、レーザーを照射する方法を用いて前記結晶性半導体層の結晶性を高める第 3 の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第 4 の工程と、

前記ゲート絶縁膜上に導電膜を設け、前記導電膜をエッチングして後に n チャネル型 TFT のゲート電極となる第 1 の導電層および、後に p チャネル型 TFT のゲート電極となる第 2 の導電層を形成する第 5 の工程と、

前記第 1 の導電層および前記第 2 の導電層をマスクにして前記半導体層に n 型不純物元素を添加する第 6 の工程と、

前記第 1 の導電層および前記第 2 の導電層をエッチングして、n チャネル型 TFT のゲート電極および後に p チャネル型 TFT のゲート電極となる第 3 の導電層をそれぞれ形成する第 7 の工程と、

前記 n チャネル型 TFT のゲート電極及び前記第 3 の導電層をマスクにして前記半導体層に n 型不純物元素を添加する第 8 の工程と、

n チャネル型 TFT となる領域をレジストからなるマスクで覆い、前記第 3 の導電層をエッチングして p チャネル型 TFT のゲート電極を形成した後、前記 p チャネル型 TFT の半導体層に p 型不純物元素を添加する第 9 の工程と、を有し、

前記 n チャネル型 TFT における n 型不純物元素が添加される領域と比較して、前記 p チャネル型 TFT における n 型不純物元素が添加される領域が狭くなるように、前記第 2 の導電層は前記第 1 の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第 3 の導電層は前記 n チャネル型 TFT のゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする半導体装置の作製方法。

### 【請求項 3】

絶縁体上に非晶質半導体層を形成する第 1 の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第 2 の工程と、

前記触媒元素の添加された非晶質半導体層を加熱して結晶性半導体層を得る第 3 の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第 4 の工程と、

前記ゲート絶縁膜上に第 1 の導電層を形成する第 5 の工程と、

前記第 1 の導電層をエッチングして、後に n チャネル型 TFT のゲート電極となる第 2 の導電層と、後に p チャネル型 TFT のゲート電極となる第 3 の導電層と、後に画素 TFT のゲート電極となる第 4 の導電層をそれぞれ形成する第 6 の工程と、

前記第 2 の導電層乃至前記第 4 の導電層をマスクにして、前記半導体層に n 型不純物元素を添加する第 7 の工程と、

前記第 2 の導電層、前記第 3 の導電層、前記第 4 の導電層をエッチングして、前記第 2 の導電層より幅の狭い n チャネル型 TFT のゲート電極と、前記第 3 の導電層より幅が狭く後に p チャネル型 TFT のゲート電極となる第 5 の導電層と、前記第 4 の導電層より幅が狭く後に画素 TFT のゲート電極となる第 6 の導電層をそれぞれ形成する第 8 の工程と、

前記 n チャネル型 TFT のゲート電極、前記第 5 の導電層および前記第 6 の導電層をマスクにして前記半導体層に n 型不純物元素を添加する第 9 の工程と、

前記第 5 の導電層および前記第 6 の導電層をエッチングして、後に p チャネル型 TFT のゲート電極となる第 7 の導電層と、画素 TFT のゲート電極をそれぞれ形成する第 10

10

20

30

40

50

の工程と、

前記第7の導電層をエッチングしてpチャネル型TFTのゲート電極を形成する第11の工程と、

前記pチャネル型TFTのゲート電極をマスクにして、前記pチャネル型TFTの半導体層にp型不純物元素を添加する第12の工程と、を有し、

前記nチャネル型TFTにおけるn型不純物元素が添加される領域と比較して、前記pチャネル型TFTにおけるn型不純物元素が添加される領域が狭くなるように、前記第3の導電層は前記第2の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第5の導電層は前記nチャネル型TFTのゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする半導体装置の作製方法。

10

#### 【請求項4】

絶縁体上に非晶質半導体層を形成する第1の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第2の工程と、

前記触媒元素の添加された非晶質半導体層を加熱することにより結晶性半導体層とし、レーザーを照射する方法を用いて前記結晶性半導体層の結晶性を高める第3の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第4の工程と、

前記ゲート絶縁膜上に第1の導電層を形成する第5の工程と、

前記第1の導電層をエッチングして、後にnチャネル型TFTのゲート電極となる第2の導電層と、後にpチャネル型TFTのゲート電極となる第3の導電層と、後に画素TFTのゲート電極となる第4の導電層をそれぞれ形成する第6の工程と、

20

前記第2の導電層乃至前記第4の導電層をマスクにして、前記半導体層にn型不純物元素を添加する第7の工程と、

前記第2の導電層、前記第3の導電層、前記第4の導電層をエッチングして、前記第2の導電層より幅の狭いnチャネル型TFTのゲート電極と、前記第3の導電層より幅が狭く後にpチャネル型TFTのゲート電極となる第5の導電層と、前記第4の導電層より幅が狭く後に画素TFTのゲート電極となる第6の導電層をそれぞれ形成する第8の工程と、

前記nチャネル型TFTのゲート電極、前記第5の導電層および前記第6の導電層をマスクにして前記半導体層にn型不純物元素を添加する第9の工程と、

前記第5の導電層および前記第6の導電層をエッチングして、後にpチャネル型TFTのゲート電極となる第7の導電層と、画素TFTのゲート電極をそれぞれ形成する第10の工程と、

30

前記第7の導電層をエッチングしてpチャネル型TFTのゲート電極を形成する第11の工程と、

前記pチャネル型TFTのゲート電極をマスクにして、前記pチャネル型TFTの半導体層にp型不純物元素を添加する第12の工程と、を有し、

前記nチャネル型TFTにおけるn型不純物元素が添加される領域と比較して、前記pチャネル型TFTにおけるn型不純物元素が添加される領域が狭くなるように、前記第3の導電層は前記第2の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第5の導電層は前記nチャネル型TFTのゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする半導体装置の作製方法。

40

#### 【請求項5】

絶縁体上に非晶質半導体層を形成する第1の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第2の工程と、

前記触媒元素の添加された非晶質半導体層を加熱して結晶性半導体層を得る第3の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第4の工程と、

前記ゲート絶縁膜上に第1の導電層を形成する第5の工程と、

前記第1の導電層をエッチングして、後にnチャネル型TFTのゲート電極となる第2の導電層と、後にpチャネル型TFTのゲート電極となる第3の導電層をそれぞれ形成す

50

る第 6 の工程と、

前記第 6 の工程で形成された前記第 2 の導電層および前記第 3 の導電層をマスクにして、前記半導体層に n 型不純物元素を添加する第 7 の工程と、

前記第 6 の工程で形成された前記第 2 の導電層および前記第 3 の導電層をエッチングして、n チャネル型 TFT のゲート電極と、後に p チャネル型 TFT のゲート電極となる第 4 の導電層をそれぞれ形成する第 8 の工程と、

前記第 8 の工程で形成された前記 n チャネル型 TFT のゲート電極および前記第 4 の導電層をマスクにして前記半導体層に n 型不純物元素を添加する第 9 の工程と、

n チャネル型 TFT をレジストからなるマスクで覆い、前記第 4 の導電層をエッチングして p チャネル型 TFT のゲート電極を形成する第 10 の工程と、

前記 p チャネル型 TFT のゲート電極をマスクにして、前記 p チャネル型 TFT の半導体層に p 型不純物元素を添加する第 11 の工程と、を有し、

前記 n チャネル型 TFT における n 型不純物元素が添加される領域と比較して、前記 p チャネル型 TFT における n 型不純物元素が添加される領域が狭くなるように、前記第 3 の導電層は前記第 2 の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第 4 の導電層は前記 n チャネル型 TFT のゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする半導体装置の作製方法。

#### 【請求項 6】

絶縁体上に非晶質半導体層を形成する第 1 の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第 2 の工程と、

前記触媒元素の添加された非晶質半導体層を加熱することにより結晶性半導体層とし、レーザーを照射する方法を用いて前記結晶性半導体層の結晶性を高める第 3 の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第 4 の工程と、

前記ゲート絶縁膜上に第 1 の導電層を形成する第 5 の工程と、

前記第 1 の導電層をエッチングして、後に n チャネル型 TFT のゲート電極となる第 2 の導電層と、後に p チャネル型 TFT のゲート電極となる第 3 の導電層をそれぞれ形成する第 6 の工程と、

前記第 6 の工程で形成された前記第 2 の導電層および前記第 3 の導電層をマスクにして、前記半導体層に n 型不純物元素を添加する第 7 の工程と、

前記第 6 の工程で形成された前記第 2 の導電層および前記第 3 の導電層をエッチングして、n チャネル型 TFT のゲート電極と、後に p チャネル型 TFT のゲート電極となる第 4 の導電層をそれぞれ形成する第 8 の工程と、

前記第 8 の工程で形成された前記 n チャネル型 TFT のゲート電極および前記第 4 の導電層をマスクにして前記半導体層に n 型不純物元素を添加する第 9 の工程と、

n チャネル型 TFT をレジストからなるマスクで覆い、前記第 4 の導電層をエッチングして p チャネル型 TFT のゲート電極を形成する第 10 の工程と、

前記 p チャネル型 TFT のゲート電極をマスクにして、前記 p チャネル型 TFT の半導体層に p 型不純物元素を添加する第 11 の工程と、を有し、

前記 n チャネル型 TFT における n 型不純物元素が添加される領域と比較して、前記 p チャネル型 TFT における n 型不純物元素が添加される領域が狭くなるように、前記第 3 の導電層は前記第 2 の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第 4 の導電層は前記 n チャネル型 TFT のゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする半導体装置の作製方法。

#### 【請求項 7】

絶縁体上に非晶質半導体層を形成する第 1 の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第 2 の工程と、

前記触媒元素の添加された非晶質半導体層を加熱して結晶性半導体層を得る第 3 の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第 4 の工程と、

前記ゲート絶縁膜上に第 1 の導電層を形成する第 5 の工程と、

10

20

30

40

50

前記第1の導電層をエッチングして、後にnチャネル型TFTのゲート電極となる第2の導電層と、後にpチャネル型TFTのゲート電極となる第3の導電層と、後に画素TFTのゲート電極となる第4の導電層をそれぞれ形成する第6の工程と、

前記第6の工程で形成された前記第2の導電層乃至前記第4の導電層をマスクにして、前記半導体層にn型不純物元素を添加する第7の工程と、

前記第6の工程で形成された前記第2の導電層、前記第3の導電層、前記第4の導電層をエッチングして、nチャネル型TFTのゲート電極と、後にpチャネル型TFTのゲート電極となる第5の導電層と、後に画素TFTのゲート電極となる第6の導電層をそれぞれ形成する第8の工程と、

前記第8の工程で形成された前記nチャネル型TFTのゲート電極、前記第5の導電層および前記第6の導電層をマスクにして前記半導体層にn型不純物元素を添加する第9の工程と、

駆動回路に形成されたnチャネル型TFTをレジストからなるマスクで覆い、前記第5の導電層および前記第6の導電層をエッチングして、後にpチャネル型TFTのゲート電極となる第7の導電層と、画素TFTのゲート電極をそれぞれ形成する第10の工程と、

前記第7の導電層をエッチングしてpチャネル型TFTのゲート電極を形成する第11の工程と、

前記pチャネル型TFTのゲート電極をマスクにして、前記pチャネル型TFTの半導体層にp型不純物元素を添加する第12の工程と、を有し、

前記nチャネル型TFTにおけるn型不純物元素が添加される領域と比較して、前記pチャネル型TFTにおけるn型不純物元素が添加される領域が狭くなるように、前記第3の導電層は前記第2の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第5の導電層は前記nチャネル型TFTのゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする半導体装置の作製方法。

#### 【請求項8】

絶縁体上に非晶質半導体層を形成する第1の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第2の工程と、

前記触媒元素の添加された非晶質半導体層を加熱して結晶性半導体層を得る第3の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第4の工程と、

前記ゲート絶縁膜上に第1の導電層を形成する第5の工程と、

前記第1の導電層をエッチングして、後にnチャネル型TFTのゲート電極となる第2の導電層と、後にpチャネル型TFTのゲート電極となる第3の導電層と、後に画素TFTのゲート電極となる第4の導電層をそれぞれ形成する第6の工程と、

前記第6の工程で形成された前記第2の導電層乃至前記第4の導電層をマスクにして、前記半導体層にn型不純物元素を添加する第7の工程と、

前記第6の工程で形成された前記第2の導電層、前記第3の導電層、前記第4の導電層をエッチングして、nチャネル型TFTのゲート電極と、後にpチャネル型TFTのゲート電極となる第5の導電層と、後に画素TFTのゲート電極となる第6の導電層をそれぞれ形成する第8の工程と、

前記第8の工程で形成された前記nチャネル型TFTのゲート電極、前記第5の導電層および前記第6の導電層をマスクにして前記半導体層にn型不純物元素を添加する第9の工程と、

駆動回路に形成されたnチャネル型TFTをレジストからなるマスクで覆い、前記第5の導電層および前記第6の導電層をエッチングして、後にpチャネル型TFTのゲート電極となる第7の導電層と、画素TFTのゲート電極をそれぞれ形成する第10の工程と、

前記第7の導電層をエッチングしてpチャネル型TFTのゲート電極を形成する第11の工程と、

前記pチャネル型TFTのゲート電極をマスクにして、前記pチャネル型TFTの半導体層にp型不純物元素を添加する第12の工程と、

10

20

30

40

50

加熱処理する第 13 の工程と、

全面を無機層間絶縁膜で覆う第 14 の工程と、

前記無機層間絶縁膜上有機層間絶縁膜を形成する第 15 の工程と、

前記無機層間絶縁膜および有機層間絶縁膜に、前記半導体層に達するコンタクトホールを形成する第 16 の工程と、

前記有機層間絶縁膜上に画素電極を形成する第 17 の工程と、

接続配線を形成する第 18 の工程と、を有し、

前記 n チャネル型 TFT における n 型不純物元素が添加される領域と比較して、前記 p チャネル型 TFT における n 型不純物元素が添加される領域が狭くなるように、前記第 3 の導電層は前記第 2 の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第 5 の導電層は前記 n チャネル型 TFT のゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする 半導体装置 の作製方法。

10

## 【請求項 9】

絶縁体上に非晶質半導体層を形成する第 1 の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第 2 の工程と、

前記触媒元素の添加された非晶質半導体層を加熱して結晶性半導体層を得る第 3 の工程と、

20

前記結晶性半導体層上にゲート絶縁膜を形成する第 4 の工程と、

前記ゲート絶縁膜上に第 1 の導電層を形成する第 5 の工程と、

前記第 1 の導電層をエッチングして、後に n チャネル型 TFT のゲート電極となる第 2 の導電層と、後に p チャネル型 TFT のゲート電極となる第 3 の導電層と、後に画素 TFT のゲート電極となる第 4 の導電層をそれぞれ形成する第 6 の工程と、

前記第 6 の工程で形成された前記第 2 の導電層乃至前記第 4 の導電層をマスクにして、前記半導体層に n 型不純物元素を添加する第 7 の工程と、

20

前記第 6 の工程で形成された前記第 2 の導電層、前記第 3 の導電層、前記第 4 の導電層をエッチングして、n チャネル型 TFT のゲート電極と、後に p チャネル型 TFT のゲート電極となる第 5 の導電層と、後に画素 TFT のゲート電極となる第 6 の導電層をそれぞれ形成する第 8 の工程と、

20

前記第 8 の工程で形成された前記 n チャネル型 TFT のゲート電極、前記第 5 の導電層および前記第 6 の導電層をマスクにして前記半導体層に n 型不純物元素を添加する第 9 の工程と、

30

駆動回路に形成された n チャネル型 TFT をレジストからなるマスクで覆い、前記第 5 の導電層および前記第 6 の導電層をエッチングして、後に p チャネル型 TFT のゲート電極となる第 7 の導電層と、画素 TFT のゲート電極をそれぞれ形成する第 10 の工程と、

30

前記第 7 の導電層をエッチングして p チャネル型 TFT のゲート電極を形成する第 11 の工程と、

30

前記 p チャネル型 TFT のゲート電極をマスクにして、前記 p チャネル型 TFT の半導体層に p 型不純物元素を添加する第 12 の工程と、

30

全面を無機層間絶縁膜で覆う第 13 の工程と、

加熱処理して前記触媒元素をゲッタリングする第 14 の工程と、

前記無機層間絶縁膜上有機層間絶縁膜を形成する第 15 の工程と、

前記無機層間絶縁膜および有機層間絶縁膜に、前記半導体層に達するコンタクトホールを形成する第 16 の工程と、

40

前記有機層間絶縁膜上に画素電極を形成する第 17 の工程と、

接続配線を形成する第 18 の工程と、を有し、

前記 n チャネル型 TFT における n 型不純物元素が添加される領域と比較して、前記 p チャネル型 TFT における n 型不純物元素が添加される領域が狭くなるように、前記第 3 の導電層は前記第 2 の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第 5 の導電層は前記 n チャネル型 TFT のゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする 半導体装置 の作製方法。

50

**【請求項 10】**

絶縁体上に非晶質半導体層を形成する第1の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第2の工程と、

前記触媒元素の添加された非晶質半導体層を加熱することにより結晶性半導体層とし、

レーザーを照射する方法を用いて前記結晶性半導体層の結晶性を高める第3の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第4の工程と、

前記ゲート絶縁膜上に第1の導電層を形成する第5の工程と、

前記第1の導電層をエッチングして、後にnチャネル型TFTのゲート電極となる第2の導電層と、後にpチャネル型TFTのゲート電極となる第3の導電層と、後に画素TFTのゲート電極となる第4の導電層をそれぞれ形成する第6の工程と、

前記第6の工程で形成された前記第2の導電層乃至前記第4の導電層をマスクにして、

前記半導体層にn型不純物元素を添加する第7の工程と、

前記第6の工程で形成された前記第2の導電層、前記第3の導電層、前記第4の導電層

をエッチングして、nチャネル型TFTのゲート電極と、後にpチャネル型TFTのゲー

ト電極となる第5の導電層と、後に画素TFTのゲート電極となる第6の導電層をそれ

ぞれ形成する第8の工程と、

前記第8の工程で形成された前記nチャネル型TFTのゲート電極、前記第5の導電層

および前記第6の導電層をマスクにして前記半導体層にn型不純物元素を添加する第9の

工程と、

駆動回路に形成されたnチャネル型TFTをレジストからなるマスクで覆い、前記第5

の導電層および前記第6の導電層をエッチングして、後にpチャネル型TFTのゲート電

極となる第7の導電層と、画素TFTのゲート電極をそれぞれ形成する第10の工程と、

前記第7の導電層をエッチングしてpチャネル型TFTのゲート電極を形成する第11

の工程と、

前記pチャネル型TFTのゲート電極をマスクにして、前記pチャネル型TFTの半導

体層にp型不純物元素を添加する第12の工程と、

加熱処理する第13の工程と、

全面を無機層間絶縁膜で覆う第14の工程と、

前記無機層間絶縁膜上有機層間絶縁膜を形成する第15の工程と、

前記無機層間絶縁膜および有機層間絶縁膜に、前記半導体層に達するコンタクトホール

を形成する第16の工程と、

前記有機層間絶縁膜上に画素電極を形成する第17の工程と、

接続配線を形成する第18の工程と、を有し、

前記nチャネル型TFTにおけるn型不純物元素が添加される領域と比較して、前記p

チャネル型TFTにおけるn型不純物元素が添加される領域が狭くなるように、前記第3

の導電層は前記第2の導電層よりチャネル長方向の幅が大きくなるように形成され、前記

第5の導電層は前記nチャネル型TFTのゲート電極よりチャネル長方向の幅が大きくな

るように形成されることを特徴とする半導体装置の作製方法。

**【請求項 11】**

絶縁体上に非晶質半導体層を形成する第1の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第2の工程と、

前記触媒元素の添加された非晶質半導体層を加熱することにより結晶性半導体層とし、

レーザーを照射する方法を用いて前記結晶性半導体層の結晶性を高める第3の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第4の工程と、

前記ゲート絶縁膜上に第1の導電層を形成する第5の工程と、

前記第1の導電層をエッチングして、後にnチャネル型TFTのゲート電極となる第2

の導電層と、後にpチャネル型TFTのゲート電極となる第3の導電層と、後に画素TFT

のゲート電極となる第4の導電層をそれぞれ形成する第6の工程と、

前記第6の工程で形成された前記第2の導電層乃至前記第4の導電層をマスクにして、

前記半導体層にn型不純物元素を添加する第7の工程と、

10

20

30

40

50

前記第6の工程で形成された前記第2の導電層、前記第3の導電層、前記第4の導電層をエッチングして、nチャネル型TFTのゲート電極と、後にpチャネル型TFTのゲート電極となる第5の導電層と、後に画素TFTのゲート電極となる第6の導電層をそれぞれ形成する第8の工程と、

前記第8の工程で形成された前記nチャネル型TFTのゲート電極、前記第5の導電層および前記第6の導電層をマスクにして前記半導体層にn型不純物元素を添加する第9の工程と、

駆動回路に形成されたnチャネル型TFTをレジストからなるマスクで覆い、前記第5の導電層および前記第6の導電層をエッチングして、後にpチャネル型TFTのゲート電極となる第7の導電層と、画素TFTのゲート電極をそれぞれ形成する第10の工程と、10

前記第7の導電層をエッチングしてpチャネル型TFTのゲート電極を形成する第11の工程と、

前記pチャネル型TFTのゲート電極をマスクにして、前記pチャネル型TFTの半導体層にp型不純物元素を添加する第12の工程と、

全面を無機層間絶縁膜で覆う第13の工程と、

加熱処理して前記触媒元素をゲッタリングする第14の工程と、

前記無機層間絶縁膜上有機層間絶縁膜を形成する第15の工程と、

前記無機層間絶縁膜および有機層間絶縁膜に、前記半導体層に達するコンタクトホールを形成する第16の工程と、20

前記有機層間絶縁膜上に画素電極を形成する第17の工程と、

接続配線を形成する第18の工程と、を有し、

前記nチャネル型TFTにおけるn型不純物元素が添加される領域と比較して、前記pチャネル型TFTにおけるn型不純物元素が添加される領域が狭くなるように、前記第3の導電層は前記第2の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第5の導電層は前記nチャネル型TFTのゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする半導体装置の作製方法。20

#### 【請求項12】

絶縁体上に非晶質半導体層を形成する第1の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第2の工程と、

前記触媒元素の添加された非晶質半導体層を加熱して結晶性半導体層を得る第3の工程と、30

前記結晶性半導体層上にゲート絶縁膜を形成する第4の工程と、

前記ゲート絶縁膜上に第1の導電層を形成する第5の工程と、

前記第1の導電層をエッチングして、後にnチャネル型TFTのゲート電極となる第2の導電層と、後にpチャネル型TFTのゲート電極となる第3の導電層と、後に画素TFTのゲート電極となる第4の導電層をそれぞれ形成する第6の工程と、

前記第6の工程で形成された前記第2の導電層乃至前記第4の導電層をマスクにして、前記半導体層にn型不純物元素を添加する第7の工程と、

前記第6の工程で形成された前記第2の導電層、前記第3の導電層、前記第4の導電層をエッチングして、nチャネル型TFTのゲート電極と、後にpチャネル型TFTのゲート電極となる第5の導電層と、後に画素TFTのゲート電極となる第6の導電層をそれぞれ形成する第8の工程と、40

前記第8の工程で形成された前記nチャネル型TFTのゲート電極、前記第5の導電層および前記第6の導電層をマスクにして前記半導体層にn型不純物元素を添加する第9の工程と、

駆動回路に形成されたnチャネル型TFTをレジストからなるマスクで覆い、前記第5の導電層および前記第6の導電層をエッチングして、後にpチャネル型TFTのゲート電極となる第7の導電層と、画素TFTのゲート電極をそれぞれ形成する第10の工程と、

前記第7の導電層をエッチングしてpチャネル型TFTのゲート電極を形成する第11の工程と、50

前記 n チャネル型 TFT のゲート電極、前記 p チャネル型 TFT のゲート電極および前記画素 TFT のゲート電極をマスクにして前記ゲート絶縁膜を除去する第 12 の工程と、

前記 n チャネル型 TFT および前記画素 TFT をレジストからなるマスクで覆い、前記 p チャネル型 TFT のゲート電極をマスクにして、前記 p チャネル型 TFT の半導体層に p 型不純物元素を添加する第 13 の工程と、を有し、

前記 n チャネル型 TFT における n 型不純物元素が添加される領域と比較して、前記 p チャネル型 TFT における n 型不純物元素が添加される領域が狭くなるように、前記第 3 の導電層は前記第 2 の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第 5 の導電層は前記 n チャネル型 TFT のゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする半導体装置の作製方法。 10

#### 【請求項 1 3】

絶縁体上に非晶質半導体層を形成する第 1 の工程と、

前記非晶質半導体層に結晶化を助長する触媒元素を添加する第 2 の工程と、

前記触媒元素の添加された非晶質半導体層を加熱することにより結晶性半導体層とし、レーザーを照射する方法を用いて前記結晶性半導体層の結晶性を高める第 3 の工程と、

前記結晶性半導体層上にゲート絶縁膜を形成する第 4 の工程と、

前記ゲート絶縁膜上に第 1 の導電層を形成する第 5 の工程と、

前記第 1 の導電層をエッチングして、後に n チャネル型 TFT のゲート電極となる第 2 の導電層と、後に p チャネル型 TFT のゲート電極となる第 3 の導電層と、後に画素 TFT のゲート電極となる第 4 の導電層をそれぞれ形成する第 6 の工程と、 20

前記第 6 の工程で形成された前記第 2 の導電層乃至前記第 4 の導電層をマスクにして、前記半導体層に n 型不純物元素を添加する第 7 の工程と、

前記第 6 の工程で形成された前記第 2 の導電層、前記第 3 の導電層、前記第 4 の導電層をエッチングして、n チャネル型 TFT のゲート電極と、後に p チャネル型 TFT のゲート電極となる第 5 の導電層と、後に画素 TFT のゲート電極となる第 6 の導電層をそれぞれ形成する第 8 の工程と、

前記第 8 の工程で形成された前記 n チャネル型 TFT のゲート電極、前記第 5 の導電層および前記第 6 の導電層をマスクにして前記半導体層に n 型不純物元素を添加する第 9 の工程と、

駆動回路に形成された n チャネル型 TFT をレジストからなるマスクで覆い、前記第 5 の導電層および前記第 6 の導電層をエッチングして、後に p チャネル型 TFT のゲート電極となる第 7 の導電層と、画素 TFT のゲート電極をそれぞれ形成する第 10 の工程と、 30

前記第 7 の導電層をエッチングして p チャネル型 TFT のゲート電極を形成する第 11 の工程と、

前記 n チャネル型 TFT のゲート電極、前記 p チャネル型 TFT のゲート電極および前記画素 TFT のゲート電極をマスクにして前記ゲート絶縁膜を除去する第 12 の工程と、

前記 n チャネル型 TFT および前記画素 TFT をレジストからなるマスクで覆い、前記 p チャネル型 TFT のゲート電極をマスクにして、前記 p チャネル型 TFT の半導体層に p 型不純物元素を添加する第 13 の工程と、を有し、

前記 n チャネル型 TFT における n 型不純物元素が添加される領域と比較して、前記 p チャネル型 TFT における n 型不純物元素が添加される領域が狭くなるように、前記第 3 の導電層は前記第 2 の導電層よりチャネル長方向の幅が大きくなるように形成され、前記第 5 の導電層は前記 n チャネル型 TFT のゲート電極よりチャネル長方向の幅が大きくなるように形成されることを特徴とする半導体装置の作製方法。 40

#### 【請求項 1 4】

請求項 3 乃至請求項 1 3 のいずれか一において、

前記第 1 の導電層は、第 1 の導電膜及び第 2 の導電膜を積層することにより形成されることを特徴とする半導体装置の作製方法。

#### 【請求項 1 5】

請求項 2 、請求項 4 、請求項 6 、請求項 1 0 、請求項 1 1 または請求項 1 3 において、

前記結晶性半導体膜の結晶性を高めるために照射するレーザーは、パルス発振型の K r F エキシマレーザー、X e C l エキシマレーザー、Y A G レーザ - または Y V O 4 レーザーであることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【発明の属する技術分野】

【0001】

【発明の属する技術分野】

本発明は、絶縁体上の薄膜トランジスタ (Thin Film Transistor:以下、TFT) という) で形成された回路を含む電気光学装置 (半導体装置) およびその作製方法に関する。特に、本発明は、画素部とその周辺に設けられる駆動回路を同一基板上に設けた液晶表示装置に代表される電気光学装置 (半導体装置) およびその電気光学装置 (半導体装置) を表示部に用いた電気器具に関する。

10

【0002】

【従来技術】

近年、ガラスなどの絶縁基板上に形成された非晶質半導体膜 (アモルファスシリコン膜) を結晶化させた多結晶半導体膜 (ポリシリコン膜)、特に結晶性半導体膜 (結晶性シリコン膜) を活性層として利用した TFT がさかんに開発されている。

【0003】

さらに、ガラス基板やプラスチック基板のように、耐熱性の低い基板上に、大面積のポリシリコン膜を形成するプロセスに関して、研究・開発が続けられている。いわゆる低温結晶化技術としては、レーザー光を用いて結晶化する方法や結晶化を助長する触媒元素を添加し加熱処理して結晶化する方法などがあげられる。

20

【0004】

結晶化を助長する触媒元素をアモルファスシリコン膜に添加して加熱処理し結晶化する技術は、特開平7-130652号公報で開示されている。

【0005】

この技術は、触媒元素の作用により、アモルファスシリコン膜の結晶化温度を 50 ~ 100 も引き下げることが可能であり、結晶化に要する時間も 1 / 5 ~ 1 / 10 にまで低減することができるため、耐熱性の低い前述したような基板上にも、大面積の結晶性シリコン膜を形成することが可能になった。また、この技術によって得られる結晶性シリコン膜は優れた結晶性を有することが確認されている。

30

【0006】

【発明が解決しようとする課題】

上述した触媒元素を用いた結晶化技術において、触媒元素として Ni、Co といった金属元素が用いられる。これらの金属元素はシリコン膜中に深いエネルギー準位を形成してキャリアを捕獲し、再結合してしまうため、得られた結晶性シリコン膜を用いて TFT を作製した場合、TFT の電気特性や信頼性に悪影響を及ぼすことが予想できる。

【0007】

また、シリコン膜中に残存した触媒元素が不規則に偏析することも確認されており、特に結晶粒界にこの偏析がみられ、この偏析が微弱な電流の逃げ道 (リークパス) となり、オフ電流 (TFT がオフ状態にある時の電流) の突発的な増加の原因になると考えられる。

40

【0008】

そこで、結晶化の工程が終わったら、速やかに触媒元素を除去する、または電気的な影響を及ぼさない程度にまで低減させる必要があった。この手段としてはゲッタリング効果を利用した技術を用いることができる。

【0009】

ゲッタリングの方法としては、アモルファスシリコン膜を金属元素により結晶化させて結晶性シリコン膜とさせた後、TFT の半導体層のチャネル形成領域となる場所をレジストからなるマスクで覆い、TFT の半導体層のチャネル形成領域以外の領域にゲッタリングに効果的な P などの 15 族元素を高濃度にドーピングしてゲッタリングを促す領域 (以下

50

、ゲッタリングシンクという。)とする方法や、同様にTFTのチャネル形成領域となる領域をレジストからなるマスクで覆い、TFTの半導体層を形成する領域のまわりにPなどの15族の元素を高濃度含んだゲッタリングシンクを設けてゲッタリングする方法などが考えられている。しかし、これらの方法では、マスク形成のための工程が必要となり、マスク数、工程数とも増加してしまうため生産性、歩留まり、製造コストの面で問題がある。

#### 【0010】

また、pチャネル型TFTは、ゲッタリングのためのリンが大量にドーピングされた後に、pチャネル型TFTとするためにp型不純物元素(本実施例ではボロン(B))を添加してソース領域およびドレイン領域を形成することになる。あらかじめドーピングされたリン(P)によるn型付与を反転させるためにかなりの濃度のボロン(B)をドーピングする必要がある。10

#### 【0011】

このため、ドーピング工程におけるスループットの低下、もしくは加熱処理によるソース領域およびドレイン領域の結晶性の改善が困難になるという問題があった。

#### 【0012】

また、ゲッタリング処理を行うためには、半導体層にリン(P)が添加されている必要がある。しかし、pチャネル型TFTとするためには、p型不純物元素(代表的にはボロン(B))を添加する必要もある。pチャネル型TFTの半導体層にボロン(B)を添加する工程に至るまでには、n型不純物元素(リン(P))を添加する工程があるため、このn型をp型に反転できる濃度のp型不純物元素を添加する(カウンタードープ又はクロスドープとも呼ばれる)。添加されるリン(P)の濃度以上にボロン(B)の濃度を高くする必要があるが、あまり不純物濃度が高いとソース・ドレイン領域の抵抗があがってしまい、オン電流が低下する原因となってしまう。さらに、カウンタードープ方式を採用した場合、過剰にアクセプターとなるイオンをドーピングしなければならないため、製造コストや生産性に問題があった。20

#### 【0013】

##### 【課題を解決するための手段】

本発明で開示する電気光学装置(半導体装置)の作製方法を説明する。ゲート絶縁膜上に形成された導電膜(A)および導電膜(B)をエッチングしてゲート電極の形状を形成する際に、nチャネル型TFTのゲート電極は所定の形状にエッチングする。しかし、pチャネル型TFTのゲート電極(C)は、後のn型不純物元素添加工程において、pチャネル型TFTの半導体層にn型不純物元素が添加される領域が大きくなないようにマスクとして用いるため、このエッチング工程において、nチャネル型TFTのゲート電極(B)よりチャネル長方向の幅が大きくなるように導電膜(A)および導電膜(B)をエッチングする。このゲート電極(C)をマスクにして、ゲート電極(C)と重ならない半導体層領域にリン(P)をドープする。なお、リン(P)が打ち込まれた領域は、ゲッタリングシンクとして機能する。30

#### 【0014】

次いで、pチャネル型TFTのゲート電極(D)を所定の形状にエッチングして、所定の形状のゲート電極(E)を得た後、pチャネル型TFTの半導体層にp型を付与するためにボロン(B)をドーピングする。ここまで工程で、pチャネル型TFTの半導体層には、チャネル形成領域、リン(P)とボロン(B)とがドーピングされた領域、ボロン(B)のみがドーピングされた領域が形成される。40

#### 【0015】

本発明によると、ゲッタリングの際に、触媒元素がpチャネル型TFTの半導体層を移動する距離を短くすることができるので、結晶粒界における触媒元素の偏析が減少し、偏析による微弱な電流の逃げ道(リークパス)や、オフ電流(Tの突発的な増加といった現象)を少なくすることができ、TFTの特性や信頼性を向上させることができる。

#### 【0016】

50

20

30

40

50

**【発明の実施の形態】**

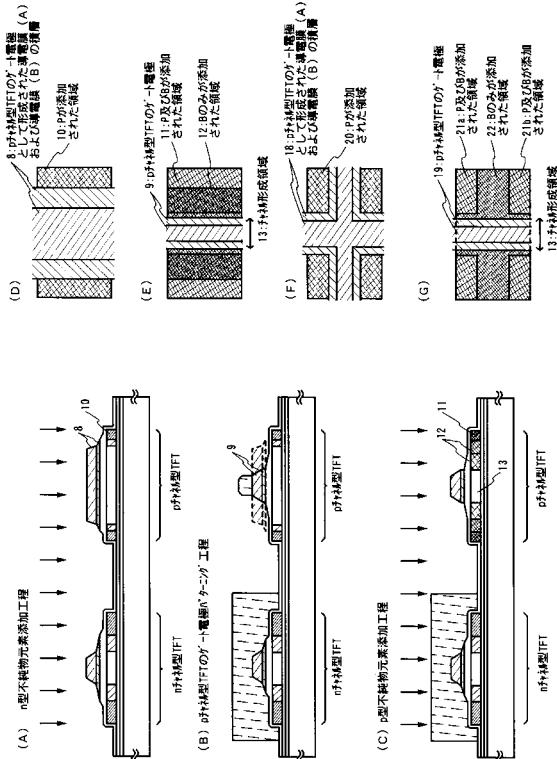

本明細書において開示する発明は、pチャネル型TFTのゲート電極を所定の形状に形成する方法に特徴がある。本発明について、図1を用いて説明する。

**【0017】**

上記のような問題を解決するために、本明細書で開示する発明には、pチャネル型TFTの半導体層に添加されるリン(P)の量を減らすという目的がある。

**【0018】**

触媒元素が結晶粒界で偏析してしまい、これがTFTの特性を悪くする原因になるのを防ぐため、ゲッタリングの際に、チャネル形成領域からソース領域およびドレイン領域へと半導体層の内部を動く触媒元素の移動距離をなるべく短くなるようにしている。

10

**【0019】**

そこで、本発明では、nチャネル型TFTのゲート電極とpチャネル型TFTのゲート電極とを所定の形状にするエッチング工程を別工程にしている。図1(A)で示すように、まずnチャネル型TFTのゲート電極をエッチングにより所定の形状に形成し、n型不純物元素を添加する。この時のpチャネル型TFTの様子を上面から見た図を図1(D)に示す。導電膜(A)および導電膜(B)を所定のゲート電極の形状より大きめにエッチングする。この導電膜(A)および導電膜(B)をゲート電極8という。このゲート電極8をマスクとして用い、n型不純物元素のリンが添加された領域10を形成する。

10

**【0020】**

続いて、図1(B)に示すように、nチャネル型TFTにマスクを形成した後、pチャネル型TFTの導電膜をエッチングして所定の形状のゲート電極9を形成する。その後、図1(C)に示すようにp型不純物元素を添加する。このような工程を採用することにより、pチャネル型TFTにおいて、図1(E)に示すようにn型不純物元素としてリンおよびp型不純物元素としてボロンが添加された領域11およびボロンのみが添加された領域12が形成されるが、カウンタードープとなるリンおよびボロンが添加された領域11を狭くすることができる。なお、所定の形状にエッチングされたゲート電極の下の半導体層には不純物元素は添加されず、チャネル形成領域13となる。

20

**【0021】**

以上のように、pチャネル型TFTの半導体層には、図1(E)に示すように、リン(P)とボロン(B)の両方が添加された領域が形成され、この領域11をゲッタリングシンクとして、本発明の目的を達している。

30

**【0022】**

なお、pチャネル型TFTにおいて、導電膜(A)および導電膜(B)を図1(F)のようにエッチングしてゲート電極18を形成し、このゲート電極18をマスクとしてn型不純物元素を添加してもよい。これにより、図1(F)に示すようなリンのみが添加された領域20が形成される。その後、ゲート電極18を所定の形状にエッチングしてゲート電極19を形成した後、p型不純物元素を添加して、n型不純物元素およびp型不純物元素が添加された領域21a、21bとp型不純物元素のみが添加された領域22を形成する。以上により、図1(G)に示すようなゲッタリングの際に、触媒元素がゲッタリングシンクまで移動する距離が短くなるような構造を実現することもできる。

40

**【0023】**

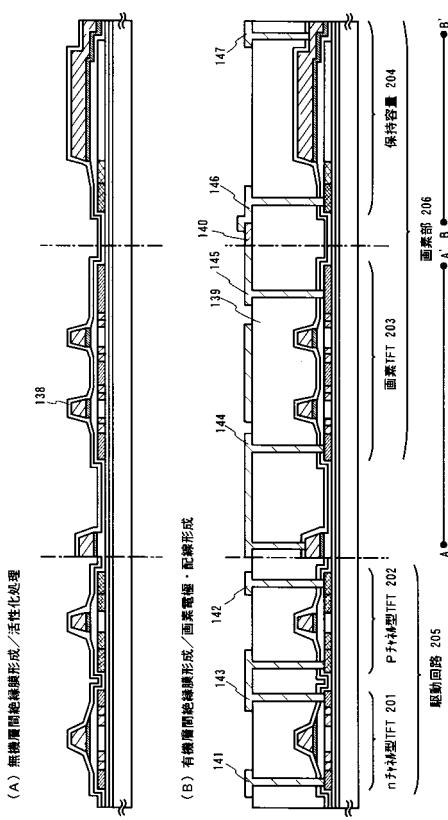

(実施例1)

本発明の実施例を図2～図5を用いて説明する。ここでは画素部の画素TFTと、画素部の周辺に設けられる駆動回路のTFTを同一基板上に作製する方法について工程に従って詳細に説明する。

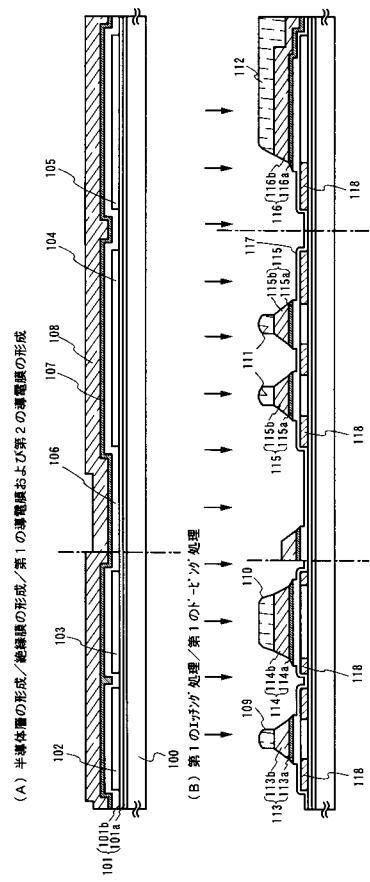

**【0024】**

図3(A)において、基板100には低アルカリガラス基板や石英基板を用いることができる。本実施例では低アルカリガラス基板を用いた。この場合、ガラス歪み点よりも10～20程度低い温度であらかじめ加熱処理しておいても良い。この基板100のTFTを形成する表面には、基板100からの不純物拡散を防ぐために、酸化シリコン膜、窒化

50

シリコン膜または酸化窒化シリコン膜などの下地膜101を形成する。例えば、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜を100nm、同様にSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜を200nmの厚さに積層形成する。

#### 【0025】

次に、20～150nm(好ましくは30～80nm)の厚さで非晶質構造を有する半導体膜を、プラズマCVD法やスパッタ法などの公知の方法で形成する。本実施例では、プラズマCVD法で非晶質シリコン膜を55nmの厚さに形成した。非晶質構造を有する半導体膜としては、非晶質半導体膜や微結晶半導体膜がある。また、下地膜101と非晶質シリコン膜とは同じ成膜法で形成することが可能であるので、両者を連続形成しても良い。下地膜を形成した後、一旦大気雰囲気に晒さないことでその表面の汚染を防ぐことが可能となり、作製するTFTの特性バラツキやしきい値電圧の変動を低減させることができる(図3(A))。

#### 【0026】

そして、特開平7 130652号公報に記載された技術にしたがって、結晶構造を含む半導体膜(本実施例では、結晶性シリコン膜)を形成する。同公報に記載された技術は、非晶質シリコン膜の結晶化に際して、結晶化を助長する触媒元素(Ni、Co、Sn、Pb、Pd、Fe、Cuから選ばれた一種または複数種の元素。代表的にはNiである。)を用いる結晶化手段である。

#### 【0027】

具体的には、非晶質シリコン膜の表面に触媒元素を保持させた状態で加熱処理を行い、非晶質シリコン膜を結晶性シリコン膜に変化させるものである。本実施例では同公報の実施例1に記載された方法を用いるが、実施例2に記載された方法を用いてもよい。なお、結晶性シリコン膜にはいわゆる単結晶シリコン膜もポリシリコン膜も含まれるが、本実施例で形成される結晶性シリコン膜は結晶粒界を有するシリコン膜である。

#### 【0028】

また、触媒元素をアモルファスシリコン膜に添加する方法としては、プラズマドーピング法、蒸着法もしくはスパッタ法等の気相法、もしくは触媒元素を含有する溶液を塗布する方法が採用できる。溶液を用いる方法は、触媒元素の添加量の制御が容易であり、ごく微量な添加を行うのも容易である。

#### 【0029】

また、上述した結晶化法とレーザー結晶化法とを組み合わせることにより、結晶質半導体膜の結晶性をさらに高めることができる。この時使用するレーザーとしては、パルス発振型または連続発光型のKrFエキシマレーザー、XeClエキシマレーザー、YAGレーザーまたはYVO<sub>4</sub>レーザーを用いることができる。これらのレーザーを用いる場合には、レーザー発振器から放出されたレーザー光を光学系で線状に集光し、半導体膜に照射する方法を用いるとよい。結晶化の条件は、実施者が適宜選択すればよい。

#### 【0030】

非晶質シリコン膜を結晶化させると原子の再配列が起こり緻密化するので、作製される結晶質シリコン膜の厚さは当初の非晶質シリコン膜の厚さ(本実施例では55nm)よりも1～15%程度減少した。

#### 【0031】

そして、結晶質シリコン膜を島状に分割して、島状半導体層102～105を形成する。

#### 【0032】

ここで、nチャネル型TFTを形成する島状半導体層102～105の全面にしきい値電圧を制御する目的で $1 \times 10^{16} \sim 5 \times 10^{17}$ atoms/cm<sup>3</sup>程度の濃度でp型を付与する不純物元素としてボロン(B)を添加してもよい。ボロン(B)の添加はイオンドープ法で実施しても良いし、非晶質シリコン膜を成膜するときに同時に添加しておくこともできる。ここでのボロン(B)添加は必ずしも必要でないが、ボロン(B)を添加した半導体層102～105はnチャネル型TFTのしきい値電圧を所定の範囲内に収めるために形成す

10

20

30

40

50

ることが好ましかった。

**【0033】**

次いで、ゲート絶縁膜106をプラズマCVD法またはスパッタ法を用いて10～150nmの厚さでシリコンを含む絶縁膜で形成する。例えば、120nmの厚さで酸化窒化シリコン膜を形成する。ゲート絶縁膜106には、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。

**【0034】**

次に、ゲート電極を形成するために導電膜(A)107および導電膜(B)108を成膜する。本実施例では、導電性の窒化物金属膜から成る導電層(A)107と金属膜から成る導電層(B)108とを積層させた。導電層(B)108はタンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タンゲステン(W)から選ばれた元素、または前記元素を主成分とする合金か、前記元素を組み合わせた合金膜(代表的にはMo-W合金膜、Mo-Ta合金膜)で形成すれば良く、導電層(A)107は窒化タンタル(TaN)、窒化タンゲステン(WN)、窒化チタン(TiN)膜、窒化モリブデン(MoN)で形成する。また、導電層(A)107は代替材料として、タンゲステンシリサイド、チタンシリサイド、モリブデンシリサイドを適用しても良い。導電層(B)は低抵抗化を図るために含有する不純物濃度を低減させると良く、特に酸素濃度に関しては30ppm以下とすると良かった。例えば、タンゲステン(W)は酸素濃度を30ppm以下とすることで20μcm以下の比抵抗値を実現することができた。

**【0035】**

導電層(A)107は10～50nm(好ましくは20～30nm)とし、導電層(B)108は200～400nm(好ましくは250～350nm)とすれば良い。本実施例では、導電層(A)107に30nmの厚さの窒化タンタル膜を、導電層(B)108には350nmのTa膜を用い、いずれもスパッタ法で形成した。このスパッタ法による成膜では、スパッタ用のガスのArに適量のXeやKrを加えておくと、形成する膜の内部応力を緩和して膜の剥離を防止することができる。尚、図示しないが、導電層(A)107の下に2～20nm程度の厚さでリン(P)をドープしたシリコン膜を形成しておくことは有効である。これにより、その上に形成される導電膜の密着性向上と酸化防止を図ると同時に、導電層(A)107または導電層(B)108が微量に含有するアルカリ金属元素がゲート絶縁膜106に拡散するのを防ぐことができる(図3(A))。

**【0036】**

次いで、レジストからなるマスク109～112を形成し、それぞれのTFTのゲート電極および容量配線を形成するための第1のエッチング処理を行う。本実施例では第1のエッチング条件として、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用い、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を25/25/10(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行った。基板側(試料ステージ)にも150WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。この第1のエッチング条件によりW膜をエッチングして第1の導電層の端部をテーパ状とする。

**【0037】**

この後、マスク109～112を除去せずに第2のエッチング条件に変え、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とを用い、それぞれのガス流量比を30/30(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッチングを行った。基板側にも20WのRF(13.56MHz)電力を投入して、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>とを混合した第2のエッチング条件ではW膜およびTaN膜とも同程度にエッチングされる。ここまで工程で、導電膜(A)107および導電膜(B)108からなる端部がテーパ状のnチャネル型TFTのゲート電極(A)113、pチャネル型TFTのゲート電極(C)114、画素TFTのゲート電極(F)115および容量配線116が形成される。なお

10

20

30

40

50

、 p チャネル型 TFT のゲート電極 ( C ) 114 は、 n チャネル型 TFT のゲート電極 ( A ) 113 、画素 TFT のゲート電極 ( F ) 115 よりも大きいサイズに形成されるように設計する。ここまで の工程で、ゲート絶縁膜 106 のマスク 109 ~ 112 に覆われていない領域はエッチングされ薄くなる。なお、第 1 のエッティング処理により形成されたゲート電極 ( A ) 、ゲート電極 ( C ) 、ゲート電極 ( F ) 、容量配線 116 は、第 1 の形状のゲート電極および容量配線とも称することとする。ゲート電極 ( C ) 114 は、後の n 型不純物元素の添加工程において、 p チャネル型 TFT の半導体層の n 型不純物元素が添加される領域が広くならないようにマスクとして用いられるため、 n チャネル型 TFT におけるゲート電極 ( A ) 113 よりも幅が広く形成される。

## 【 0038 】

10

そして、マスク 109 ~ 112 を除去せずに、 n 型不純物元素を添加する処理を行い、不純物領域 118 を形成する ( 図 3 ( B ) ) 。 n 型不純物元素としては、リン ( P ) や砒素 ( As ) を用いれば良く、ここではリン ( P ) を添加すべく、フォスフィン ( PH<sub>3</sub> ) を用いたイオンドープ法を適用した。

## 【 0039 】

さらに、マスク 109 ~ 112 を除去せずに第 2 のエッティング処理を行う。ここでは、エッティング用ガスに CF<sub>4</sub> と Cl<sub>2</sub> と O<sub>2</sub> を用い、それぞれのガス流量比を 20 / 20 / 20 ( sccm ) とし、 1 Pa の圧力でコイル型の電極に 500W の RF ( 13.56 MHz ) 電力を投入して、実質的に負の自己バイアス電圧を印加する。第 2 のエッティング処理条件によると、 W 膜が選択的にエッティングされる。

20

## 【 0040 】

この第 2 のエッティング処理により、導電膜 ( A ) 113a ~ 116a および導電膜 ( B ) 113b ~ 116b がエッティングされ、ゲート電極 ( B ) 119 、ゲート電極 ( D ) 120 、ゲート電極 ( G ) 121 、容量配線 122 が形成される。この工程において所定の形状に形成されているのは、 n チャネル型 TFT のゲート電極 ( B ) 119 、ゲート電極 ( G ) 121 および容量配線 122 であって、 p チャネル型 TFT のゲート電極 ( D ) 120 は、 p チャネル型 TFT の半導体層において、 n 型不純物元素が高濃度に含まれる領域を狭くするためのマスクとして用いるため、所定の形状 ( 他のゲート電極 ( B ) 119 、ゲート電極 ( G ) 121 ) より大きいサイズに形成される。なお、第 2 のエッティング処理により形成されたゲート電極 ( B ) 119 、ゲート電極 ( G ) 121 、ゲート電極 ( D ) 120 、容量配線 122 を第 2 の形状のゲート電極および容量配線とも称することとする。

30

## 【 0041 】

次いで、半導体層に n 型不純物元素を添加する処理を行う。第 2 のエッティング処理により形成されたゲート電極 ( B ) 119 、ゲート電極 ( D ) 120 、ゲート電極 ( G ) 121 をマスクとして用い、導電膜 ( A ) のテーパ状部分の下方の半導体層にも n 型不純物元素が添加されるようにドーピングして、 n 型不純物領域 ( A ) 123a ~ 126a および n 型不純物領域 ( B ) 123b ~ 126b が形成される。このとき形成される不純物領域 123a ~ 126a の不純物 ( リン ( P ) ) 濃度は、  $1 \times 10^{20} \sim 1 \times 10^{21}$  atoms / cm<sup>3</sup> となるようにすればよい。( 本明細書中では、 n 型不純物領域 123a ~ 126a に含まれる n 型不純物元素の濃度を ( n+ ) と表す。 ) さらに、 n 型不純物領域 ( B ) 123b ~ 126b の不純物濃度は、  $5 \times 10^{17} \sim 5 \times 10^{19}$  atoms / cm<sup>3</sup> となるようにすればよい。本明細書中において、 n 型不純物領域 123b ~ 126b に含まれる n 型不純物元素の濃度を ( n- ) と表す。なお、導電層 ( A ) 119a のテーパ状部分と重なる n 型不純物領域 123c は、若干、不純物濃度が低くなるものの、 n 型不純物領域 123b とほぼ同程度の濃度の不純物領域が形成される ( 図 4 ( A ) ) 。

40

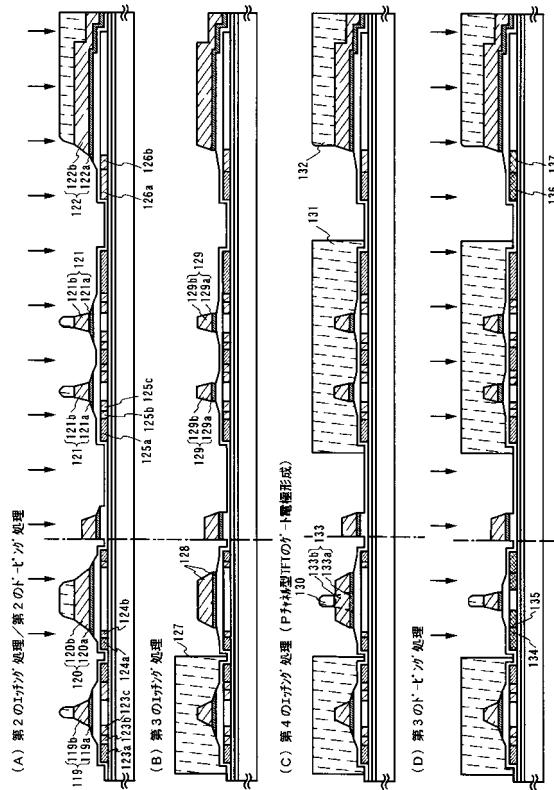

## 【 0042 】

次いで、レジストからなるマスク 109 ~ 112 を除去した後、新たに n チャネル型 TFT を覆うレジストからなるマスク 127 を形成して、第 3 のエッティング処理を行う。エッティング用ガスには、 SF<sub>6</sub> と Cl<sub>2</sub> を用い、それぞれのガス流量比は 50 / 10 ( SCCM )

50

とし、1.3 Pa の圧力でコイル型の電極に 500 W の RF (13.56 MHz) 電力を投入してプラズマを生成し約 30 秒のエッティングを行う。基板側（試料ステージ）には、10 W の RF (13.56 MHz) 電力を投入して、実質的に負の自己バイアス電圧を印加する。以上の工程により、導電膜 (A) 120a、121a がエッティングされた p チャネル型 TFT のゲート電極 (D') 128 および画素 TFT のゲート電極 (H) 129 が形成される。なお、第 3 のエッティング処理により形成されたゲート電極 (D') 128 およびゲート電極 (H) 129 は、第 3 の形状のゲート電極とも称することとする。

#### 【0043】

次いで、p チャネル型 TFT のゲート電極 (D') 128 を所定のサイズにするためのエッティングするためのレジストからなるマスク 130 と画素 TFT および容量配線を覆うレジストからなるマスク 131、132 を形成する。次いで、p チャネル型 TFT のゲート電極 (D') 128 にエッティング処理を行い p チャネル型 TFT のゲート電極 (E) 133 を得る（図 4 (C)）。なお、第 4 のエッティング処理により形成されたゲート電極 (E) 133 は、第 4 の形状のゲート電極とも称することとする。

10

#### 【0044】

次いで、p チャネル型 TFT の半導体層に p 型不純物元素（本実施例ではボロン (B)）を添加して、p 型不純物領域 134～137 を形成する。p 型不純物領域 134、136 の p 型不純物元素の不純物濃度が、 $2 \times 10^{20} \sim 2 \times 10^{21}$  atoms/cm<sup>3</sup> となるように添加する。なお、本実施例では p チャネル型 TFT の半導体層にボロン (B) を添加する前に、ボロン (B) を添加する半導体層の領域の上部に設けられた TaN 膜が除かれているため、ボロン (B) を低加速で添加することができ、添加の際の半導体層へのダメージを少なくすることができる。

20

#### 【0045】

ここまで工程により、それぞれの半導体領域に n 型不純物領域および p 型不純物領域が形成される（図 4 (D)）。

#### 【0046】

次いで、マスク 130～132 を除去して、無機層間絶縁膜 138 を形成する。窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜を 50～500 nm（代表的には 100～300 nm）の厚さで形成する。本実施例では、プラズマ CVD 法により膜厚 150 nm の酸化窒化シリコン膜を形成した。無論、無機層間絶縁膜としては、酸化窒化シリコン膜に限定されるものではなく、他のシリコンを含む絶縁膜を単層または積層構造としてよい。

30

#### 【0047】

次いで、半導体層に添加された不純物元素を活性化する工程を行う。この活性化工程は、ファーネスアニール炉を用いて行う。熱アニール法としては、酸素濃度が 1 ppm 以下、好みしくは、0.1 ppm 以下の窒素雰囲気下で 400～700、代表的には 500～550 で行えばよく、本実施例では、550、4 時間の加熱処理で活性化処理を行った。なお、熱アニール法の他にも、レーザーアニール法、またはラピッドサーマルアニール (RTA) 法を適用することができる。

#### 【0048】

40

なお、本実施例では、上記活性化処理と同時に、結晶化の際に触媒として使用した触媒元素の残留する量を少なくするため、高濃度のリンを含む n 型不純物領域にゲッタリングさせていた。ゲッタリングに必要なリン (P) の濃度は図 4 (B) で形成した不純物領域 (n+) と同程度であり、ここで実施される活性化工程の加熱処理により、n チャネル型 TFT および p チャネル型 TFT のチャネル形成領域から触媒元素をゲッタリングすることができた。得られた TFT はオフ電流値が下がり、結晶性がよいためから高い電界効果移動度が得られ、良好な特性を達成することができる。

#### 【0049】

また、無機層間絶縁膜 138 を形成する前に活性化処理を行ってもよい。ただし、ゲート電極に用いた材料が熱に弱い場合には、本実施例のように配線等を保護する目的で層間絶縁膜

50

(シリコンを主成分とする絶縁膜、例えば窒化珪素膜)を形成した後で活性化処理を行うことが望ましい。

#### 【0050】

さらに、3～100%の水素を含む雰囲気中で、300～550で1～12時間の加熱処理を行い、半導体層を水素化する工程を行う。本実施例では、水素を約3%含む窒素雰囲気下で410、1時間の加熱処理を行う。この工程は、層間絶縁膜に含まれる水素により半導体層のダンギングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行ってもよい。

#### 【0051】

また、活性化処理としてレーザーニール法を用いる場合には、上記水素化を行った後、

エキシマレーザーやYAGレーザー等のレーザー光を照射することが望ましい。

#### 【0052】

次いで、無機層間絶縁膜138上に、有機絶縁物材料からなる有機層間絶縁膜139を形成する。本実施例では、膜厚1.6μmのアクリル樹脂膜を形成した。次いで、各不純物領域に達するコントラクトホールを形成するためのパターニングを行う。

#### 【0053】

この後、透明導電膜を80～120nmの厚さで形成し、パターニングすることによって画素電極140を形成する。透明導電膜には、酸化インジウム酸化亜鉛合金(In<sub>2</sub>O<sub>3</sub>-ZnO)、酸化亜鉛(ZnO)も適した材料であり、さらに可視光の透過率や導電率を高めるためにガリウム(Ga)を添加した酸化亜鉛(ZnO:Ga)等を適用することもできる。

#### 【0054】

そして、駆動回路部205において、不純物領域と電気的に接続する配線141～143を形成する。なお、これらの電極は、膜厚50nmのTi膜と膜厚500nmの合金膜(A1とTiとの合金膜)との積層膜をパターニングして形成する。

#### 【0055】

また、画素部206においては、不純物領域と接する配線144～147を形成する。

#### 【0056】

画素電極140は、配線146により保持容量を形成する一方の電極として機能する半導体層105と電気的に接続される。

#### 【0057】

なお、本実施例では画素電極140として、透明導電膜を用いた例を示したが、反射性を有する導電性材料を用いて画素電極を形成すれば、反射型の表示装置を作製することができる。その場合、電極を作製する工程で画素電極を同時に形成でき、その画素電極の材料としては、A1またはAgを主成分とする膜、またはそれらの積層膜等の反射性がすぐれた材料を用いることが望ましい。

#### 【0058】

こうして同一基板上に、駆動回路のTFTと画素部の画素TFTとを有した基板を完成させることができた。駆動回路にはnチャネル型TFT201、pチャネル型TFT202、画素部には画素TFT203、保持容量204を形成した。なお、本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

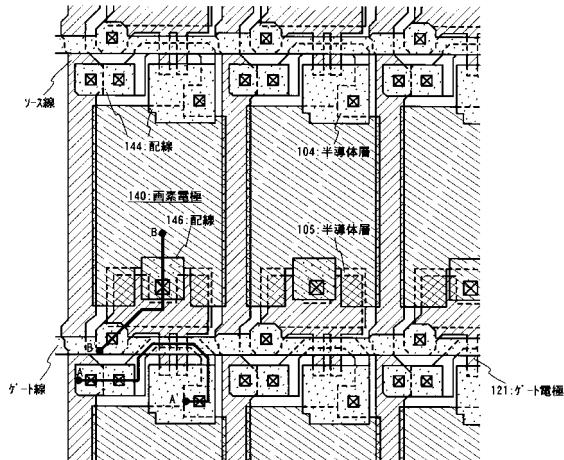

#### 【0059】

ここまで工程により作製されたアクティブマトリクス基板の上面図を図2に示す。なお、図2のA-A'線は、図5(B)のA-A'線に対応し、半導体層104、ゲート電極121、配線144、ゲート線、ソース線が形成されている。同様に図2のB-B'線は、図5(B)のB-B'線に対応し、半導体層105、画素電極140、配線146が形成されている。

#### 【0060】

駆動回路のnチャネル型TFT201は、島状半導体層102にチャネル形成領域、ソース領域またはドレイン領域123a、不純物領域123bおよび第2の形状のゲート電極

10

20

30

40

50

(B) 119と重なる不純物領域123c(以降、このような不純物領域をLovと記す)を有している。このLov領域のチャネル長方向の長さは0.5~3.0μm、好ましくは1.0~1.5μmとした。また、導電膜(A)119aおよび導電膜(B)119bの積層からなる第2の形状のゲート電極(B)119を有している。

#### 【0061】

駆動回路のpチャネル型TFT202は、島状半導体層103にチャネル形成領域、ソース領域またはドレイン領域124a、不純物領域124bを有している。また、導電膜(A)133aおよび導電膜(B)133bの積層からなる第4の形状のゲート電極(E)133を有している。

#### 【0062】

画素部の画素TFT203には、島状半導体層104にチャネル形成領域、ソース領域またはドレイン領域125a、不純物領域125b、125cを有している。また、導電膜(A)129aおよび導電膜(B)129bの積層からなる第3の形状のゲート電極(H)129を有している。

#### 【0063】

さらに、容量配線122と、ゲート絶縁膜と同じ材料から成る絶縁膜と、p型不純物元素が添加された半導体層105とから保持容量204が形成されている。図5では画素TFT203をダブルゲート構造としたが、シングルゲート構造でも良いし、複数のゲート電極を設けたマルチゲート構造としても差し支えない。

#### 【0064】

以上の様に本発明は、画素部および駆動回路が要求する仕様に応じて各回路を構成するTFTの構造を最適化し、半導体装置の動作性能と信頼性を向上させることを可能とすることができる。さらにゲート電極を耐熱性を有する導電性材料で形成することによりLDD領域やソース領域およびドレイン領域の活性化を容易とし、配線を低抵抗材料で形成することにより、配線抵抗を十分低減できる。従って、画素部(画面サイズ)が4インチクラス以上の表示装置に適用することもできる。

#### 【0065】

##### (実施例2)

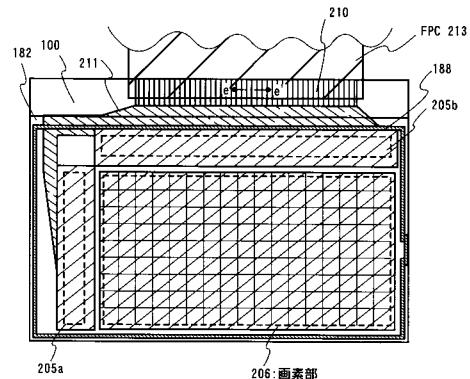

本実施例では、実施例1で作製したアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を以下に説明する。説明には図6を用いる。

#### 【0066】

まず、実施例1に従い、図5(B)の状態のアクティブマトリクス基板を得た後、図5(B)のアクティブマトリクス基板上に配向膜180を形成しラビング処理を行う。なお、本実施例では配向膜180を形成する前に、アクリル樹脂膜等の有機樹脂膜をバターニングすることによって基板間隔を保持するための柱状のスペーサ181を所定の位置に形成した。また、柱状のスペーサに代えて、球状のスペーサを基板全面に散布してもよい。

#### 【0067】

次いで、対向基板182を用意する。この対向基板には、着色層183、184、平坦化膜185を形成する。赤色の着色層183と青色の着色層184とを一部重ねて、第2遮光部を形成する。なお、図6では図示しないが、赤色の着色層と緑色の着色層とを一部重ねて第1遮光部を形成する。

#### 【0068】

ついで、対向電極186を画素部に形成し、対向基板の全面に配向膜187を形成し、ラビング処理を施した。

#### 【0069】

そして、画素部と駆動回路が形成されたアクティブマトリクス基板と対向基板とをシール材188で貼り合わせる。シール材188にはフィラーが混入されていて、このフィラーと柱状スペーサによって均一な間隔を持って2枚の基板が貼り合わせられる。その後、両基板の間に液晶材料189を注入し、封止剤(図示せず)によって完全に封止する。液晶材料189には公知の液晶材料を用いれば良い。このようにして図6に示すアクティブマ

10

20

30

40

50

トリクス型液晶表示装置が完成する。そして、必要があれば、アクティブマトリクス基板または対向基板を所定の形状に分断する。さらに、公知の技術を用いて偏光板等を適宜設けた。そして、公知の技術を用いてFPCを貼りつけた。

**【0070】**

こうして得られた液晶表示パネルの構成を図7の上面図を用いて説明する。なお、図6と対応する部分には同じ符号を用いた。

**【0071】**

図7(A)で示す上面図は、画素部206、駆動回路205a、205b、FPC(フレキシブルプリント配線板:Flexible Printed Circuit)を貼り付ける外部入力端子210、外部入力端子と各回路の入力部までを接続する接続配線211などが形成されたアクティブマトリクス基板と、カラーフィルタなどが設けられた対向基板182とがシール材188を介して貼り合わされている。

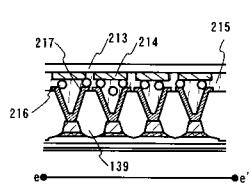

10

**【0072】**

図7(B)は図7(A)で示す外部入力端子210のe-e'線に対する断面図を示している。外部入力端子にはベースフィルム213と配線214から成るFPCが異方性導電性樹脂215で貼り合わされており、さらに補強板で機械的強度を高めている。217は、画素電極140を形成するために成膜した導電膜からなる配線である。導電性粒子216の外径は配線217のピッチよりも小さいので、接着剤215中に分散する量を適當なものとすると隣接する配線と短絡することなく対応するFPC側の配線と電気的な接続を形成することができる。

20

**【0073】**

以上のようにして作製される液晶表示パネルは各種電気器具の表示部として用いることができる。

**【0074】**

(実施例3)

本実施例は、実施例1とは異なる半導体装置の作製方法について説明する。

**【0075】**

実施例1に示した工程に従い、第3のエッティング工程でゲート電極(E)133を形成した後、前記工程で形成したゲート電極(B)119、ゲート電極(E)133、ゲート電極(H)129および容量配線122をマスクにしてゲート電極119、129、133および容量配線122と重ならない領域のゲート絶縁膜117をエッティングして除去する。

30

**【0076】**

ゲート絶縁膜をエッティングして除去しておけば、不純物のドーピング工程の際に、数回におよぶゲート電極のエッティング工程で位置により膜厚がばらついている可能性の高いゲート絶縁膜の複雑な膜厚を考慮する必要がなくなる。

**【0077】**

本実施例は、実施例1、実施例2と組み合わせて適応することができる。

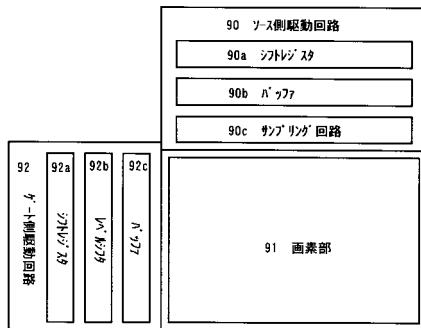

**【0078】**

(実施例4)

本発明を用いて作製された半導体装置におけるブロック図を図8に示す。なお、図8には、アナログ駆動を行うための回路構成が示されている。本実施例は、ソース側駆動回路90、画素部91およびゲート側駆動回路92を有している半導体装置について示している。なお、本明細書中において、駆動回路とはソース側駆動回路およびゲート側駆動回路を含めた総称を指している。

40

**【0079】**

ソース側駆動回路90は、シフトレジスタ90a、バッファ90b、サンプリング回路(トランスマニアゲート)90cを設けている。また、ゲート側駆動回路92は、シフトレジスタ92a、レベルシフタ92b、バッファ92cを設けている。また、必要であればサンプリング回路とシフトレジスタとの間にレベルシフタ回路を設けてよい。

50

**【 0 0 8 0 】**

また、本実施例において、画素部 9 1 は複数の画素からなり、その複数の画素各々が T F T 素子を含んでいる。

**【 0 0 8 1 】**

なお、図示していないが、画素部 9 1 を挟んでゲート側駆動回路 9 2 の反対側にさらにゲート側駆動回路を設けても良い。

**【 0 0 8 2 】**

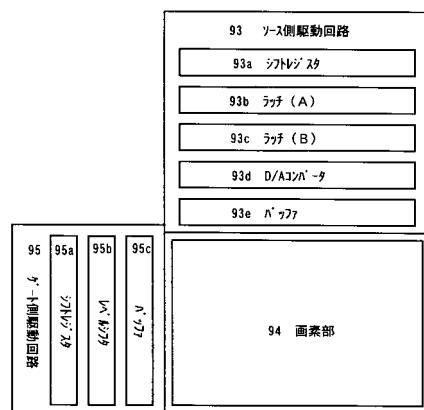

また、デジタル駆動させる場合は、図 9 に示すように、サンプリング回路の代わりにラッチ ( A ) 9 3 b 、ラッチ ( B ) 9 3 c を設ければよい。ソース側駆動回路 9 3 は、シフトレジスタ 9 3 a 、ラッチ ( A ) 9 3 b 、ラッチ ( B ) 9 3 c 、D / A コンバータ 9 3 d 、バッファ 9 3 e を設けている。また、ゲート側駆動回路 9 5 は、シフトレジスタ 9 5 a 、レベルシフタ 9 5 b 、バッファ 9 5 c を設けている。また、必要であればラッチ ( B ) 9 3 c と D / A コンバータ 9 3 d との間にレベルシフタ回路を設けてもよい。10

**【 0 0 8 3 】**

なお、上記構成は、実施例 1 に示した製造工程に従って実現することができる。また、本実施例では画素部と駆動回路の構成のみ示しているが、本発明の製造工程に従えば、メモリやマイクロプロセッサをも形成しうる。

**【 0 0 8 4 】****【 実施例 5 】**

本願発明を実施して形成された C M O S 回路や画素部は様々な半導体装置 ( アクティブマトリクス型液晶ディスプレイ ) に用いることができる。即ち、それら半導体装置を表示部に組み込んだ電気器具全てに本発明を実施できる。20

**【 0 0 8 5 】**

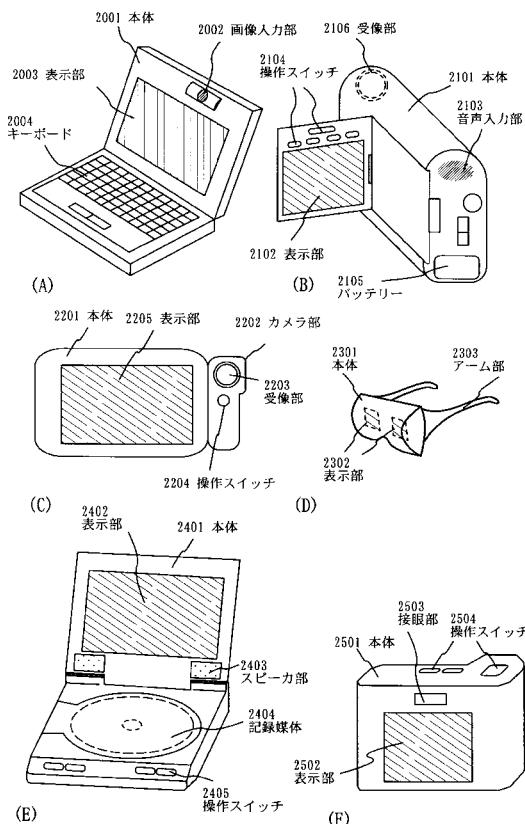

その様な電気器具としては、ビデオカメラ、デジタルカメラ、プロジェクター ( リア型またはフロント型 ) 、ヘッドマウントディスプレイ ( ゴーグル型ディスプレイ ) 、パーソナルコンピュータ、携帯情報端末 ( モバイルコンピュータ、携帯電話または電子書籍等 ) などが挙げられる。それらの一例を図 1 0 、図 1 1 および図 1 2 に示す。

**【 0 0 8 6 】**

図 1 0 ( A ) はパーソナルコンピュータであり、本体 2 0 0 1 、画像入力部 2 0 0 2 、表示部 2 0 0 3 、キーボード 2 0 0 4 等を含む。本発明を画像入力部 2 0 0 2 、表示部 2 0 0 3 やその他の信号制御回路に適用することができる。30

**【 0 0 8 7 】**

図 1 0 ( B ) はビデオカメラであり、本体 2 1 0 1 、表示部 2 1 0 2 、音声入力部 2 1 0 3 、操作スイッチ 2 1 0 4 、バッテリー 2 1 0 5 、受像部 2 1 0 6 等を含む。本発明を表示部 2 1 0 2 やその他の信号制御回路に適用することができる。

**【 0 0 8 8 】**

図 1 0 ( C ) はモバイルコンピュータ ( モービルコンピュータ ) であり、本体 2 2 0 1 、カメラ部 2 2 0 2 、受像部 2 2 0 3 、操作スイッチ 2 2 0 4 、表示部 2 2 0 5 等を含む。本発明は表示部 2 2 0 5 やその他の信号制御回路に適用できる。

**【 0 0 8 9 】**

図 1 0 ( D ) はゴーグル型ディスプレイであり、本体 2 3 0 1 、表示部 2 3 0 2 、アーム部 2 3 0 3 等を含む。本発明は表示部 2 3 0 2 やその他の信号制御回路に適用することができる。40

**【 0 0 9 0 】**

図 1 0 ( E ) はプログラムを記録した記録媒体 ( 以下、記録媒体と呼ぶ ) を用いるプレーヤーであり、本体 2 4 0 1 、表示部 2 4 0 2 、スピーカ部 2 4 0 3 、記録媒体 2 4 0 4 、操作スイッチ 2 4 0 5 等を含む。なお、このプレーヤーは記録媒体として D V D ( D i g t i a l V e r s a t i l e D i s c ) 、 C D 等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部 2 4 0 2 やその他の信号制御回路に適用することができる。50

**【0091】**

図10(F)はデジタルカメラであり、本体2501、表示部2502、接眼部2503、操作スイッチ2504、受像部(図示しない)等を含む。本発明は表示部2502やその他の信号制御回路に適用することができる。

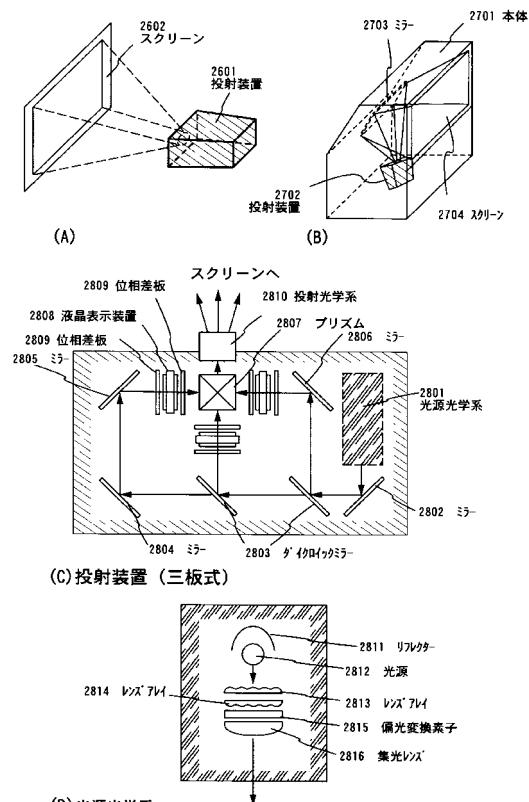

**【0092】**

図11(A)はフロント型プロジェクターであり、投射装置2601、スクリーン2602等を含む。本発明は投射装置2601の一部を構成する液晶表示装置2808や他の信号制御回路に適用することができる。

**【0093】**

図11(B)はリア型プロジェクターであり、本体2701、投射装置2702、ミラー2703、スクリーン2704等を含む。本発明は投射装置2702の一部を構成する液晶表示装置2808や他の信号制御回路に適用することができる。10

**【0094】**

なお、図11(C)は、図11(A)及び図11(B)中における投射装置2601、2702の構造の一例を示した図である。投射装置2601、2702は、光源光学系2801、ミラー2802、2804～2806、ダイクロイックミラー2803、プリズム2807、液晶表示装置2808、位相差板2809、投射光学系2810で構成される。投射光学系2810は、投射レンズを含む光学系で構成される。本実施例は三板式の例を示したが、特に限定されず、例えば単板式であってもよい。また、図11(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。20

**【0095】**

また、図11(D)は、図11(C)中における光源光学系2801の構造の一例を示した図である。本実施例では、光源光学系2801は、リフレクター2811、光源2812、レンズアレイ2813、2814、偏光変換素子2815、集光レンズ2816で構成される。なお、図11(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

**【0096】**

ただし、図11に示したプロジェクターにおいては、透過型の半導体装置を用いた場合を示しており、反射型の半導体装置での適用例は図示していない。30

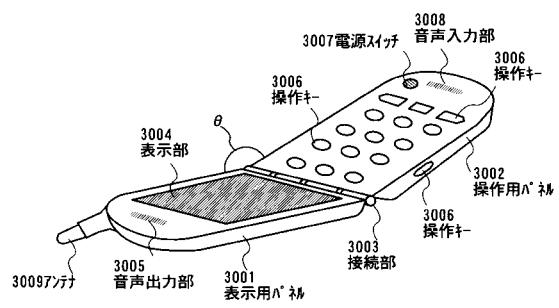

**【0097】**

図12(A)は携帯電話であり、3001は表示用パネル、3002は操作用パネルである。表示用パネル3001と操作用パネル3002とは接続部3003において接続されている。接続部3003における、表示用パネル3001の表示部3004が設けられている面と操作用パネル3002の操作キー3006が設けられている面との角度は、任意に変えることができる。

さらに、音声出力部3005、操作キー3006、電源スイッチ3007、音声入力部3008を有している。本発明は、表示部3004に適用することができる。

**【0098】**

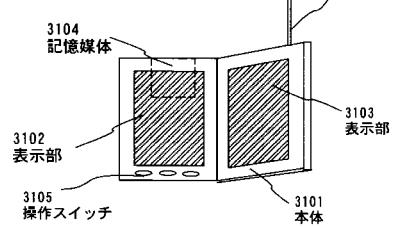

図12(B)は携帯書籍(電子書籍)であり、本体3101、表示部3102、3103、記憶媒体3104、操作スイッチ3105、アンテナ3106等を含む。本発明は表示部3102、3103や他の信号回路に適用することができる。

**【0099】**

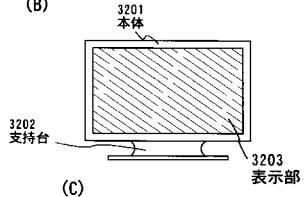

図12(C)はディスプレイであり、本体3201、支持台3202、表示部3203等を含む。本発明は表示部3203に適用することができる。本発明のディスプレイは特に大画面化した場合において有利であり、対角10インチ以上(特に30インチ以上)のディスプレイには有利である。

**【0100】**

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電気器具に適用すること50

が可能である。また、本実施例の電気器具は実施例 1 ~ 4 のどのような組み合わせからなる構成を用いても実現することができる。

### 【0101】

#### 【発明の効果】

本発明によれば、マスク数、工程数を増やすことなく p チャネル型 TFT の半導体層のゲッタリングを十分行うことができ、ソース領域およびドレイン領域の抵抗を下げることができる。また、十分にゲッタリングができるため、触媒元素による悪影響を低減でき、信頼性の高い p チャネル型 TFT を比較的簡便に歩留まりよく作製することができる。

#### 【図面の簡単な説明】

- 【図 1】 本発明の実施形態を示す図。 10

- 【図 2】 本発明の実施例を示す図。

- 【図 3】 本発明の実施例の一例を示す図。

- 【図 4】 本発明の実施例の一例を示す図。

- 【図 5】 本発明の実施例の一例を示す図。

- 【図 6】 本発明の実施例の一例を示す図。

- 【図 7】 本発明の実施例の一例を示す図。

- 【図 8】 本発明の実施例の一例を示す図。

- 【図 9】 本発明の実施例の一例を示す図。

- 【図 10】 本発明を用いて作製された半導体装置を表示部に用いた電気器具の一例を示す図。 20

- 【図 11】 本発明を用いて作製された半導体装置を表示部に用いた電気器具の一例を示す図。

- 【図 12】 本発明を用いて作製された半導体装置を表示部に用いた電気器具の一例を示す図。

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図7】

(A) 上面図

(B) e-e' 断面図

【図8】

【図9】

【図10】

【図11】

【図12】

(A)

(B)

(C)

---

フロントページの続き

| (51)Int.Cl. |                  | F I                    |

|-------------|------------------|------------------------|

| H 0 1 L     | 21/20 (2006.01)  | G 0 2 F 1/1368         |

| H 0 1 L     | 21/322 (2006.01) | G 0 9 F 9/30 3 3 8     |

|             |                  | H 0 1 L 21/20          |

|             |                  | H 0 1 L 29/78 6 2 7 G  |

|             |                  | H 0 1 L 29/78 6 1 7 K  |

|             |                  | H 0 1 L 21/265 6 0 4 M |

|             |                  | H 0 1 L 21/322 R       |

|             |                  | H 0 1 L 29/78 6 1 2 B  |

(72)発明者 松尾 拓哉

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

審査官 河口 雅英

(56)参考文献 特開平08-330602(JP,A)

特開平10-223534(JP,A)

特開平10-335672(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

G02F 1/1368

G09F 9/30

H01L 21/20

H01L 21/265

H01L 21/322

H01L 21/336