(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6035132号

(P6035132)

(45) 発行日 平成28年11月30日(2016.11.30)

(24) 登録日 平成28年11月4日(2016.11.4)

(51) Int.Cl.

F 1

G06F 3/041 (2006.01)

G06F 3/041 412

G06F 3/044 (2006.01)

G06F 3/041 520

G06F 3/041 512

G06F 3/044 120

請求項の数 6 (全 17 頁)

(21) 出願番号

特願2012-267279 (P2012-267279)

(22) 出願日

平成24年12月6日 (2012.12.6)

(65) 公開番号

特開2014-115708 (P2014-115708A)

(43) 公開日

平成26年6月26日 (2014.6.26)

審査請求日

平成27年11月30日 (2015.11.30)

(73) 特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 110000350

ポレール特許業務法人

(74) 代理人 100083552

弁理士 秋田 収喜

(74) 代理人 100103746

弁理士 近野 恵一

(72) 発明者 時田 雅弘

千葉県茂原市早野3300番地 株式会社

ジャパンディスプレイイースト内

(72) 発明者 高畠 昌志

千葉県茂原市早野3300番地 株式会社

ジャパンディスプレイイースト内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1基板と、

第2基板と、

前記第1基板と前記第2基板との間に狭持される液晶とを有する液晶表示パネルを備え、マトリクス状に配置された複数の画素を有する液晶表示装置であって、

前記第2基板は、タッチパネルの検出電極を有し、

前記各画素は、画素電極と対向電極とを有し、

前記対向電極には画像表示に用いられる対向電圧と、タッチ位置の検出に用いられるタッチパネル走査電圧が印加され、

前記対向電極は、複数のブロックに分割されており、

前記分割された各ブロックの対向電極は、連続する複数の表示ラインの各画素に対して共通に設けられており、

前記分割された各ブロックの対向電極は、前記タッチパネルの走査電極を兼用し、

前記各検出電極毎に設けられ、一端が前記各検出電極に接続されるキャリブレーション容量素子を有し、

タッチ位置検出処理前に、前記検出電極に基準電圧がプリチャージされて、キャリブレーション容量素子の前記一端に基準電圧が印加され、かつ、前記キャリブレーション容量素子の他端に基準電圧が印加され、

タッチ位置検出処理時に、前記タッチパネルの走査電極となる対向電極には、前記タッ

チパネル走査電圧が印加され、

かつ、前記各キャリブレーション容量素子の前記他端にキャリブレーション電圧を供給する手段を有することを特徴とする液晶表示装置。

**【請求項 2】**

第 1 基板と、

第 2 基板と、

前記第 1 基板と前記第 2 基板との間に教示される液晶とを有する液晶表示パネルを備え、マトリクス状に配置された複数の画素を有する液晶表示装置であって、

前記第 2 基板は、タッチパネルの検出電極を有し、

前記各画素は、画素電極と対向電極とを有し、

前記対向電極は、複数のブロックに分割されており、

前記分割された各ブロックの対向電極は、連続する複数の表示ラインの各画素に対して共通に設けられており、

前記分割された各ブロックの対向電極は、前記タッチパネルの走査電極を兼用し、前記各ブロックの対向電極には画像表示に用いられる対向電圧と、タッチ位置の検出に用いられるタッチパネル走査電圧が印加され、

前記各検出電極毎に設けられ、一端が前記各検出電極に接続されるキャリブレーション容量素子と、

前記各検出電極と前記分割された各ブロックの対向電極との交点毎のキャリブレーションデータを記憶するメモリ素子とを有し、

タッチ位置検出処理前に、前記検出電極に基準電圧がプリチャージされて、キャリブレーション容量素子の前記一端に基準電圧が印加され、かつ、前記キャリブレーション容量素子の他端に基準電圧が印加され、

タッチ位置検出処理時に、前記タッチパネルの走査電極となる対向電極には、前記タッチパネル走査電圧が印加され、前記メモリ素子に記憶されたキャリブレーションデータに対応するキャリブレーションデータ電圧を生成し、対応するキャリブレーション容量素子の前記他端に供給する手段とを有することを特徴とする液晶表示装置。

**【請求項 3】**

第 1 基板と、

第 2 基板と、

前記第 1 基板と前記第 2 基板との間に狭持される液晶とを有する液晶表示パネルを備え、マトリクス状に配置された複数の画素を有する液晶表示装置であって、

前記第 2 基板は、タッチパネルの検出電極を有し、

前記各画素は、画素電極と対向電極とを有し、

前記対向電極は、複数のブロックに分割されており、

前記分割された各ブロックの対向電極は、前記タッチパネルの走査電極を兼用し、前記各ブロックの対向電極には画像表示に用いられる対向電圧と、タッチ位置の検出に用いられるタッチパネル走査電圧が印加され、

前記各検出電極毎に設けられ、一端が前記各検出電極に接続されるキャリブレーション容量素子を有し、

タッチ位置検出処理前に、

前記検出電極に基準電圧がプリチャージされて、キャリブレーション容量の前記一端に基準電圧が印加され、かつ、前記キャリブレーション容量の他端に基準電圧が印加され、タッチ位置検出処理時に、

前記走査電極には、タッチパネル走査電圧が印加され、

かつ、前記各キャリブレーション容量素子の前記他端にキャリブレーション電圧を供給してタッチ位置を検出し、

互いに隣接する 2 つの検出電極の短絡試験時に、一端が奇数列の検出電極に接続される

10

20

30

40

50

キャリブレーション容量素子の他端に電荷が引き抜かれないキャリブレーション電圧Aを供給し、一端が偶数列の検出電極に接続されるキャリブレーション容量素子の他端に充分に電荷を引き抜けるキャリブレーション電圧Bを供給し、タッチ位置検出処理を実行する手段を有することを特徴とする液晶表示装置。

【請求項4】

第1基板と、

第2基板と、

前記第1基板と前記第2基板との間に狭持される液晶とを有する液晶表示パネルを備え、マトリクス状に配置された複数の画素を有する液晶表示装置であって、

前記第2基板は、タッチパネルの検出電極を有し、

10

前記各画素は、画素電極と対向電極とを有し、

前記対向電極は、複数のブロックに分割されており、

前記分割された各ブロックの対向電極は、連続する複数の表示ラインの各画素に対して共通に設けられており、

前記分割された各ブロックの対向電極は、前記タッチパネルの走査電極を兼用し、前記各ブロックの対向電極には画像表示に用いられる対向電圧と、タッチ位置の検出に用いられるタッチパネル走査電圧が印加され、

前記各検出電極毎に設けられ、一端が前記各検出電極に接続されるキャリブレーション容量素子と、

前記各検出電極と前記分割された各ブロックの対向電極との交点毎のキャリブレーションデータを記憶するメモリ素子とを有し、

20

タッチ位置検出処理前に、

前記検出電極に基準電圧がプリチャージされて、キャリブレーション容量の前記一端に基

準電圧が印加され、かつ、前記キャリブレーション容量の他端に基準電圧が印加され、

タッチ位置検出処理時に、

前記走査電極には、タッチパネル走査電圧が印加され、

かつ、前記各キャリブレーション容量素子の前記他端にキャリブレーション電圧を供給してタッチ位置を検出し、

互いに隣接する2つの検出電極の短絡試験時に、奇数列の検出電極と前記分割された各ブロックの対向電極との交点毎のキャリブレーションデータとして、電荷が引き抜かれないキャリブレーションデータAを記憶し、偶数列の検出電極と前記分割された各ブロックの対向電極との交点毎のキャリブレーションデータとして、充分に電荷を引き抜けるキャリブレーションデータBを記憶し、

30

前記互いに隣接する2つの検出電極の短絡試験時に、前記メモリ素子に記憶されたキャリブレーションデータAに対応するキャリブレーションデータ電圧Aを生成して、一端が奇数列の検出電極に接続されるキャリブレーション容量素子の他端に供給するとともに、前記メモリ素子に記憶されたキャリブレーションデータBに対応するキャリブレーションデータ電圧Bを生成して、一端が偶数列の検出電極に接続されるキャリブレーション容量素子の他端に供給し、タッチ位置検出処理を実行する手段を有することを特徴とする液晶表示装置。

40

【請求項5】

第1基板と、

第2基板と、

前記第1基板と前記第2基板との間に狭持される液晶とを有する液晶表示パネルを備え、マトリクス状に配置された複数の画素を有する液晶表示装置であって、

前記第2基板は、タッチパネルの検出電極を有し、

前記各画素は、画素電極と対向電極とを有し、

前記対向電極は、複数のブロックに分割されており、

前記分割された各ブロックの対向電極は、連続する複数の表示ラインの各画素に対して共通に設けられており、

50

前記分割された各ブロックの対向電極は、前記タッチパネルの走査電極を兼用し、前記各ブロックの対向電極には画像表示に用いられる対向電圧と、タッチ位置の検出に用いられるタッチパネル走査電圧が印加され、

前記各検出電極毎に設けられ、前記各検出電極に接続される複数の積分回路と、

前記各検出電極毎に設けられ、一端が前記各検出電極に接続されるキャリブレーション容量素子と、

前記各検出電極と前記分割された各ブロックの対向電極との交点毎のキャリブレーションデータを記憶するメモリ素子とを有し、

タッチ位置検出処理前に、

前記検出電極に基準電圧がプリチャージされて、キャリブレーション容量の前記一端に基準電圧が印加され、かつ、前記キャリブレーション容量の他端に基準電圧が印加され、タッチ位置検出処理時に、

前記走査電極には、タッチパネル走査電圧が印加され、

かつ、前記各キャリブレーション容量素子の前記他端にキャリブレーション電圧を供給してタッチ位置を検出し、

互いに隣接する2つの検出電極の短絡試験時に、奇数列の検出電極と前記分割された各ブロックの対向電極との交点毎のキャリブレーションデータとして、電荷が引き抜かれないキャリブレーションデータAを記憶し、偶数列の検出電極と前記分割された各ブロックの対向電極との交点毎のキャリブレーションデータとして、充分に電荷を引き抜けるキャリブレーションデータBを記憶し、

前記互いに隣接する2つの検出電極の短絡試験時に、前記メモリ素子に記憶されたキャリブレーションデータAに対応するキャリブレーションデータ電圧Aとして、V R E Fの基準電圧を生成して、一端が奇数列の検出電極に接続されるキャリブレーション容量素子の他端に供給するとともに、前記メモリ素子に記憶されたキャリブレーションデータBに対応するキャリブレーションデータ電圧Bとして、前記各積分回路に供給されるG N Dの電圧を生成して、一端が偶数列の検出電極に接続されるキャリブレーション容量素子の他端に供給し、タッチ位置検出処理を実行する手段を有することを特徴とする液晶表示装置。

#### 【請求項6】

前記各検出電極と前記各積分回路との間に接続される第1のスイッチ回路と、

前記各検出電極にV R E Fの基準電圧を供給する第2のスイッチ回路と、

前記各キャリブレーション容量素子の他端に、キャリブレーションデータ電圧あるいはV R E Fの基準電圧を供給する第3のスイッチ回路とを有し、

前記分割された各ブロックの対向電極にタッチパネル走査電圧を供給する前に、前記第1のスイッチ回路をオフ、前記第2のスイッチ回路をオンとし、前記第3のスイッチ回路により前記各キャリブレーション容量素子の他端に前記V R E Fの基準電圧を供給し、

前記分割された各ブロックの対向電極にタッチパネル走査電圧を供給している時に、前記第1のスイッチ回路をオン、前記第2のスイッチ回路をオフとし、前記第3のスイッチ回路により前記各キャリブレーション容量素子の他端に前記キャリブレーションデータ電圧を供給することを特徴とする請求項5に記載の液晶表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、液晶表示装置に係わり、特に、タッチパネルを内蔵したインセル方式の液晶表示装置に適用して有効な技術に関する。

##### 【背景技術】

##### 【0002】

表示画面に使用者の指またはペンなどを用いてタッチ操作（接触押圧操作、以下、単にタッチと称する）して情報を入力する装置（以下、タッチセンサ又はタッチパネルとも称する）を備えた表示装置は、P D Aや携帯端末などのモバイル用電子機器、各種の家電製

10

20

30

40

50

品、現金自動預け払い機（Automated Teller Machine）等に用いられている。

このようなタッチパネルとして、タッチされた部分の容量変化を検出する静電容量方式が知られている。

この静電容量方式タッチパネルとして、タッチパネル機能を液晶表示パネルに内蔵した、所謂、インセル方式の液晶表示装置が知られている。

インセル方式の液晶表示装置では、タッチパネルの走査電極として、液晶表示パネルを構成する第1基板（所謂、TFT基板）上に形成される対向電極（コモン電極ともいう）を分割して使用している。

#### 【先行技術文献】

##### 【特許文献】

10

##### 【0003】

##### 【特許文献1】特開2009-258182号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

インセル方式の液晶表示装置におけるタッチパネルは相互容量検出方式であり、液晶表示パネルの第1基板上に形成される走査電極と、液晶表示パネルの第2基板上に形成される検出電極との間の交差容量（ $C \times y$ ）を検出してタッチ位置を検出している。

交差容量（ $C \times y$ ）は、液晶層、第1および第2の基板を構成するガラス基板、偏光板、接着樹脂などの誘電率や厚みのばらつき、また不均一性のため、個体差や面内ばらつきを持っており、キャリブレーションが必須である。

20

また、インセル方式の液晶表示装置におけるタッチパネルの出荷検査では、タッチパネル全面を覆うことができる面積の金属プレートを乗せて、走査電極と検出電極の全交点のRawデータにおける、金属プレートを乗せた前後の差分値が規定範囲内にあると良品と判定する。

この金属プレート検査は、短時間で判定できる一方、互いに隣接する2つの検出電極の隣接ショート不良の検出は困難である。この隣接ショート不良には、互いに隣接する2つの検出電極に接続される、フレキシブル配線基板上の配線の隣接ショート不良も含まれる。

互いに隣接する2つの検出電極の隣接ショート不良の検出は、走査電極と検出電極の各交点毎の打点検査で可能であるが、検査に時間を要するため生産効率が著しく低下する。また、フレキシブル配線基板上の検出電極に接続される配線に、テストパッドを設けオープンショート検査をする方法は、ノイズや静電気に弱くなる、あるいは、フレキシブル配線基板が大きくなる等のデメリットがある。

30

##### 【0005】

本発明は、前記従来技術の問題点を解決するためになされたものであり、本発明の目的は、タッチパネル機能を内蔵した液晶表示装置において、交差容量のキャリブレーションを効率的に実行することが可能となる技術を提供することにある。

また、本発明の他の目的は、タッチパネル機能を内蔵した液晶表示装置において、交差容量のキャリブレーション回路を利用して、互いに隣接する2つの検出電極の隣接ショート不良を検出することが可能となる技術を提供することにある。

40

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

#### 【課題を解決するための手段】

##### 【0006】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

本発明は、検出電極のそれぞれに、他端にキャリブレーション電圧（V<sub>DAC</sub>）が印加されるキャリブレーション容量を配置し、キャリブレーション電圧（V<sub>DAC</sub>）を調整することで電荷引き抜き量を可変して、キャリブレーションを効率的に実行する。

50

さらに、本発明では、このキャリブレーション回路を利用して、フレキシブル配線基板上の配線を含めて、互いに隣接する2つの検出電極がショートしているか否かの隣接ショート不良の検査を行う。

隣接ショート不良の検査時、奇数番目の検出電極に接続されるキャリブレーション容量の他端に、電荷を引き抜かないキャリブレーション電圧（例えば、VREFの基準電圧）を印加し、偶数番目の検出電極には、十分に電荷を引き抜けるキャリブレーション電圧（例えば、GNDの電圧）を印加する。

これにより、互いに隣接する2つの検出電極がショートしていない場合は、奇数番目の検出電極から検出され、A/D変換器で変換されたRawデータが、例えば、10ビットで[0]となり、互いに隣接する2つの検出電極がショートしている場合は、奇数番目の検出電極から検出され、A/D変換器で変換されたRawデータが、例えば、10ビットで[1023]となるので、簡単かつ短時間に、検出電極の隣接ショート不良を検出することができる。

#### 【発明の効果】

#### 【0007】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

（1）本発明のタッチパネル機能を内蔵した液晶表示装置によれば、交差容量のキャリブレーションを効率的に実行することが可能となる。

（2）本発明のタッチパネル機能を内蔵した液晶表示装置によれば、交差容量のキャリブレーション回路を利用して、互いに隣接する2つの検出電極の隣接ショート不良を検出することが可能となる。

#### 【図面の簡単な説明】

#### 【0008】

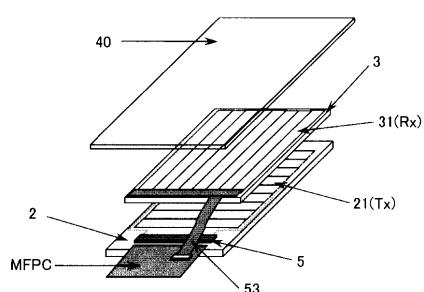

【図1（a）】液晶表示パネルの内部にタッチパネルを内蔵したインセル方式の液晶表示装置の一例の概略構成を示す分解斜視図である。

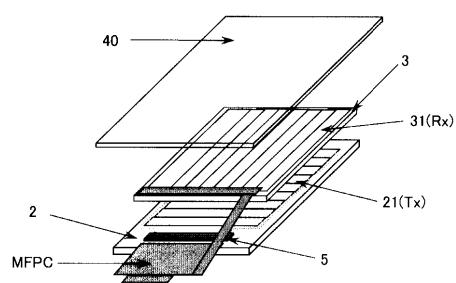

【図1（b）】液晶表示パネルの内部にタッチパネルを内蔵したインセル方式の液晶表示装置の他の例の概略構成を示す分解斜視図である。

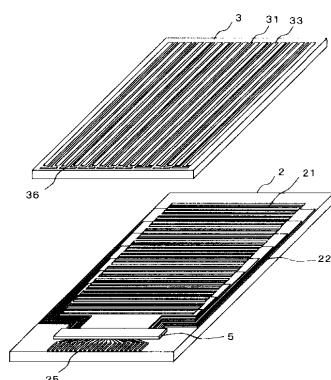

【図2】図1（a）,図1（b）に示す液晶表示装置における、対向電極と検出電極を説明する図である。

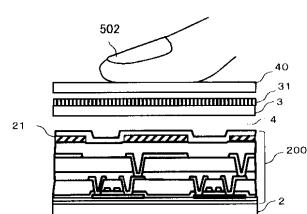

【図3】図1（a）,図1（b）に示す液晶表示装置の表示部の断面の一部を拡大して示す概略断面図である。

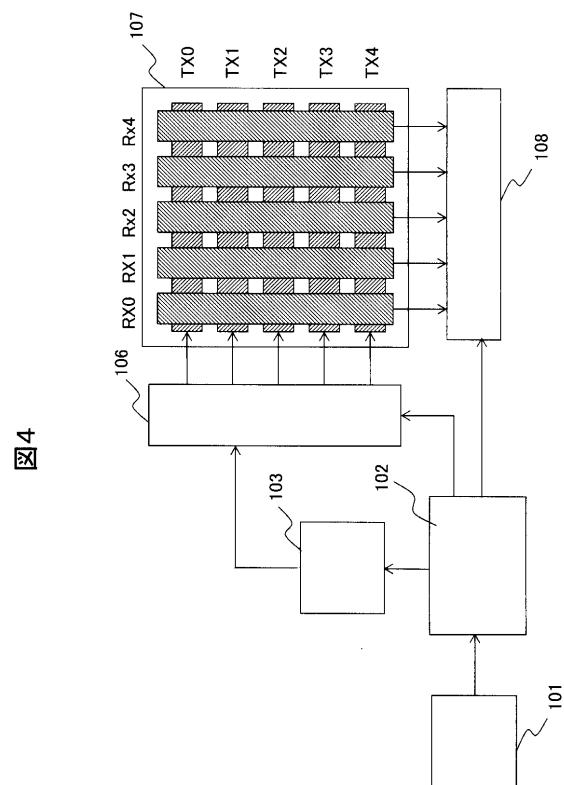

【図4】本発明の前提となるインセル方式の液晶表示装置における、タッチパネルの全体概略構成を示すブロック図である。

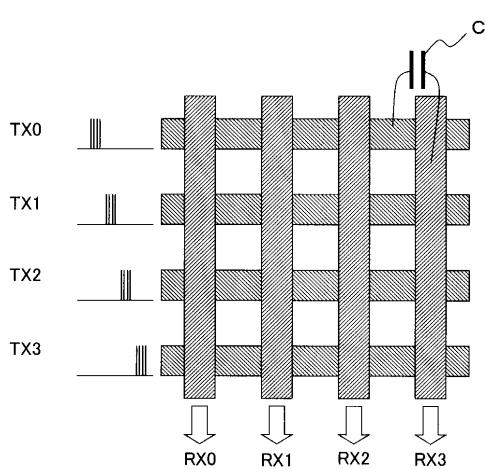

【図5】本発明の前提となるインセル方式の液晶表示装置における、タッチパネルの検出原理を説明するための図である。

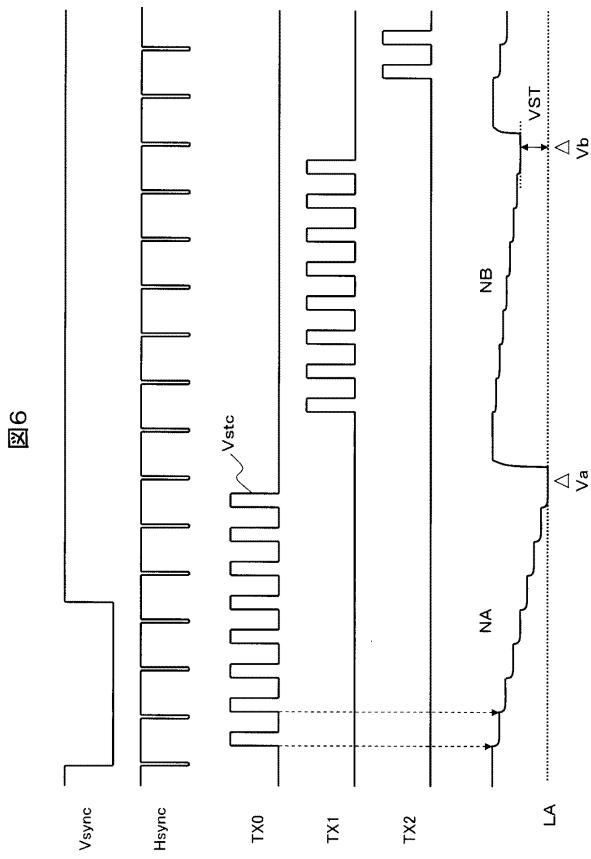

【図6】本発明の前提となるインセル方式の液晶表示装置における、タッチパネルのタッチ検出動作のタイミング図である。

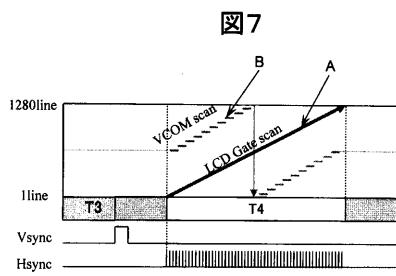

【図7】本発明の前提となるインセル方式の液晶表示装置における、タッチパネル検出時と、画素書き込み時のタイミングを説明するための図である。

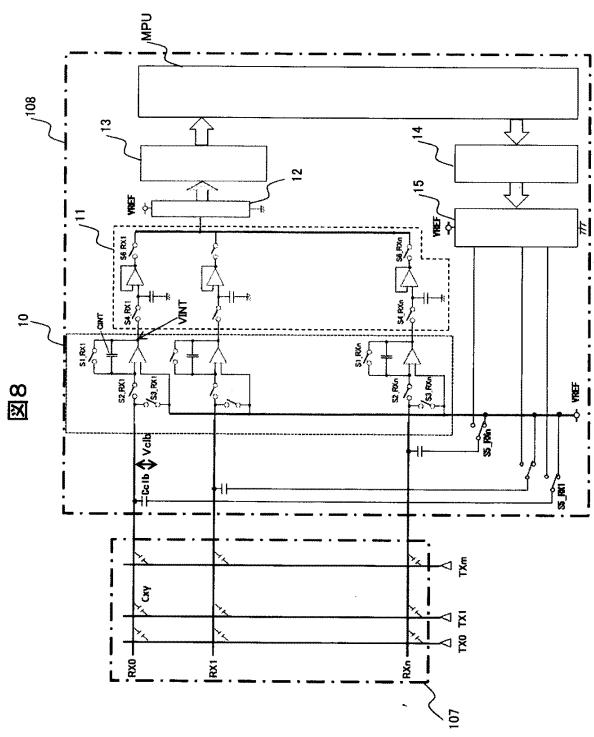

【図8】本発明の実施例のインセル方式の液晶表示装置の検出回路のより具体的な回路構成を示す回路図である。

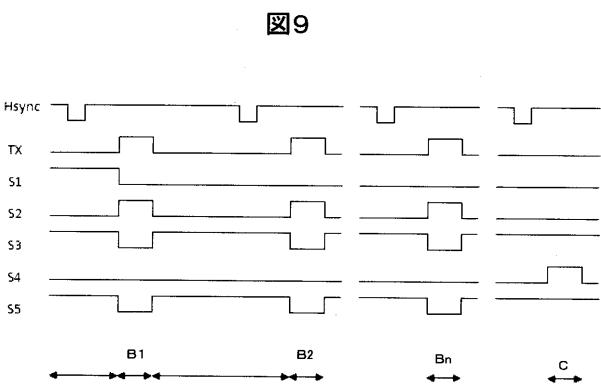

【図9】図8に示す回路の動作を説明するためのタイミングチャートである。

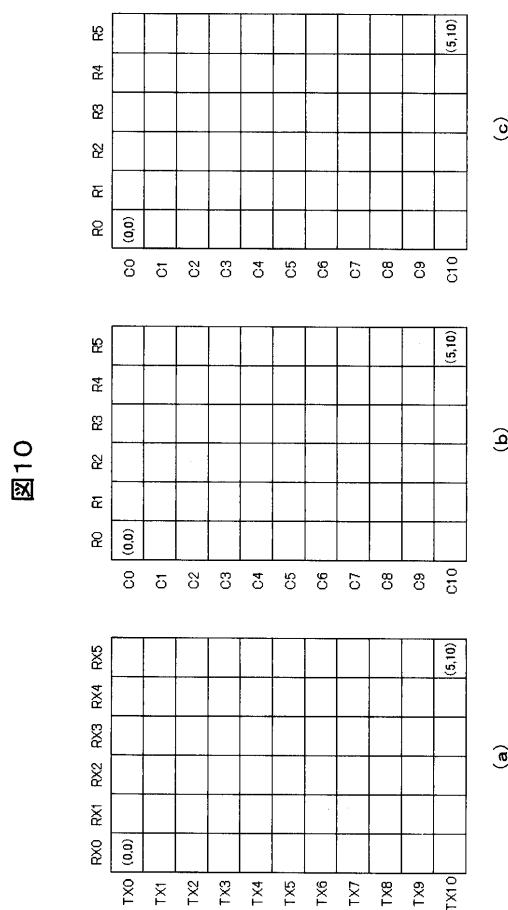

【図10】本発明の実施例のインセル方式の液晶表示装置のタッチパネル、検出RAM、および、キャリブレーションRAMのアドレスマップを示す図である。

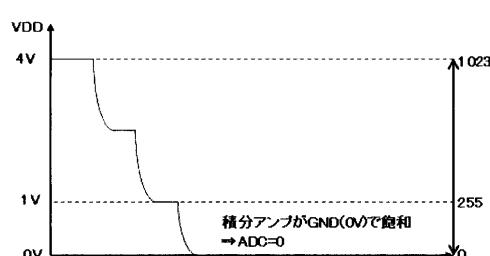

【図11】本発明の実施例のインセル方式の液晶表示装置のキャリブレーション時の積分回路での積分波形を示す図である。

【図12】本発明の実施例のインセル方式の液晶表示装置において、検出電極の隣接ショート不良検査時に、キャリブレーションRAMに設定されるキャリブレーションデータを示す図である。

10

20

30

40

50

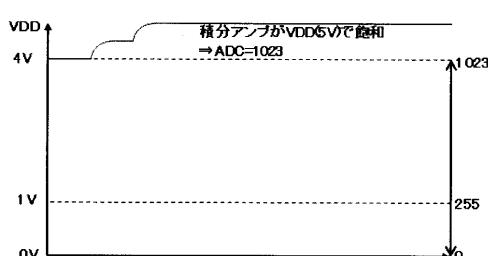

【図13】本発明の実施例のインセル方式の液晶表示装置において、検出電極の隣接ショート不良検査時に、キャリブレーションRAMに設定されるキャリブレーションデータが[00]の場合の積分回路での積分波形を示す図である。

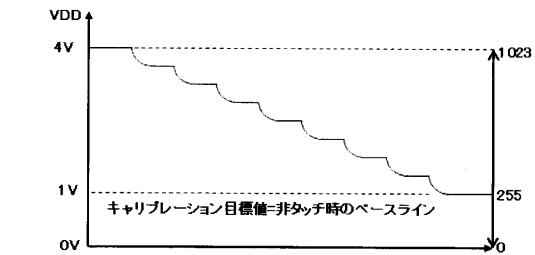

【図14】本発明の実施例のインセル方式の液晶表示装置において、検出電極の隣接ショート不良検査時に、キャリブレーションRAMに設定されるキャリブレーションデータが[FF]の場合の積分回路での積分波形を示す図である。

【図15】本発明の実施例のインセル方式の液晶表示装置において、互いに隣接する2つの検出電極がショートしていない場合と、互いに隣接する2つの検出電極がショートしている場合に、検出RAMに格納されるRawデータを示す図である。

【発明を実施するための形態】

10

【0009】

以下、図面を参照して本発明の実施例を詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。また、以下の実施例は、本発明の特許請求の範囲の解釈を限定するためのものではない。

図1(a)は、液晶表示パネルの内部にタッチパネルを内蔵したインセル方式の液晶表示装置の一例の概略構成を示す分解斜視図である。

図1(b)は、液晶表示パネルの内部にタッチパネルを内蔵したインセル方式の液晶表示装置の他の例の概略構成を示す分解斜視図である。

図1(b)に示すインセル方式の液晶表示装置は、低コスト化のために、図1(a)に示すメインフレキシブル配線基板(MFPC)と、接続用フレキシブル配線基板53とを一体化したものである。

図1(a)、図1(b)において、2は第1基板(以下、TFT基板という)、3は第2基板(以下、CF基板という)と、21は対向電極(共通電極ともいう)、5は液晶ドライバIC、MFPCはメインフレキシブル配線基板、40はフロントウィンドウ、53は接続用フレキシブル配線基板である。

図1(a)、図1(b)に示す液晶表示装置では、CF基板3上の裏面側透明導電膜(CD)を、帯状のパターンに分割して、タッチパネルの検出電極31となし、TFT基板2の内部に形成される対向電極21を帯状のパターンに分割、即ち、複数のブロックに分割して、タッチパネルの走査電極として兼用することにより、通常のタッチパネルで使用されるタッチパネル基板を削減している。また、図1に示す液晶表示装置では、タッチパネル駆動用の回路が、液晶ドライバIC(5)の内部に設けられる。

【0010】

20

次に、図2を用いて、図1に示す液晶表示装置の対向電極21と検出電極31について説明する。

前述したように、対向電極21はTFT基板2上に設けられているが、複数本の(例えば32本程度)対向電極21が両端で共通に接続され、対向電極信号線22と接続されている。

図2に示す液晶表示装置では、帯状の対向電極21が走査電極(TX)を兼用し、また、検出電極31が検出電極(RX)を構成する。

30

したがって、対向電極信号には、画像表示に用いられる対向電圧と、タッチ位置の検出に用いられるタッチパネル走査電圧とが含まれる。タッチパネル走査電圧が対向電極21に印加されると、対向電極21と一定の間隔を持って配置され容量を構成する検出電極31に検出信号が生じる。この検出信号は検出電極用端子36を介して外部に取り出される。

なお、検出電極31の両側にはダミー電極33が形成されている。検出電極31は一方の端部でダミー電極33側に向かい広がりT字状の検出電極用端子36を形成している。また、TFT基板2には対向電極信号線22以外にも駆動回路用入力端子25のような様々な配線、端子等が形成される。

【0011】

40

50

図1に示す液晶表示装置における、表示部の断面の一部を拡大した概略断面図を図3に示す。

図3に示すようにTFT基板2には画素部200が設けられており、対向電極21は画素の一部として画像表示に用いられる。また、TFT基板2とCF基板3との間には液晶組成物4が狭持されている。CF基板3に設けられた検出電極31とTFT基板に設けられた対向電極21とは容量を形成しており、対向電極21に駆動信号が印加されると検出電極31の電圧が変化する。

この時、図3に示すように、フロントウィンドウ40を介して指502等の導電体が近接または接触すると、容量に変化が生じ検出電極31に生じる電圧に、近接・接触が無い場合に比較して変化が生じる。

このように、液晶表示パネルに形成した対向電極21と検出電極31との間に生じる容量の変化を検出することで、液晶表示パネルにタッチパネルの機能を備えることが可能となる。

#### 【0012】

図4は、本発明の前提となるインセル方式の液晶表示装置における、タッチパネルの全体概略構成を示すブロック図である。

図4において、101はLCDドライバ、102はシーケンサ、103はタッチパネル走査電圧生成回路、106はデコーダ回路、107はタッチパネル、108は検出回路である。

タッチパネル107には、ユーザのタッチを検出するためのセンサ端子である電極パターン（TX0～TX4の走査電極、RX0～RX4の検出電極）が形成されている。

本発明の前提となるインセル方式の液晶表示装置は、タッチパネル機能が液晶表示パネルに内蔵されているため、図2に示す帯状の対向電極21が走査電極（TX）を兼用し、また、検出電極31が検出電極（RX）を構成する。

LCDドライバ101は、液晶表示パネルに画像を表示するための同期信号（垂直同期信号（Vsync）及び水平同期信号（Hsync））をシーケンサ102へ送出する。シーケンサ102は、タッチパネル走査電圧生成回路103、デコーダ106、及び検出回路108を制御して、タッチ検出動作のタイミングを制御する。

タッチパネル走査電圧生成回路103は、TX0～TX4の走査電極を駆動するためのタッチパネル走査電圧（Vstc）を生成して出力する。

デコーダ106は、シーケンサ102から入力される選択信号に基づいて、タッチパネル走査電圧（Vstc）を、TX0～TX4の走査電極の中1つの走査電極へ出力するアナログスイッチ（デマルチプレクサ）である。

検出回路108は、TX0～TX4の走査電極の中で、タッチパネル走査電圧（Vstc）が供給されている1つの走査電極と、RX0～RX4の各検出電極との交点における電極間容量（相互容量）を検出する。

#### 【0013】

図5は、本発明の前提となるインセル方式の液晶表示装置における、タッチパネルの検出原理を説明するための図である。

図6は、本発明の前提となるインセル方式の液晶表示装置における、タッチ検出動作のタイミング図である。

シーケンサ102は、タッチパネル走査電圧生成回路103等を制御し、垂直同期信号（Vsync）及び水平同期信号（Hsync）に同期しながら、TX0～TX4の走査電極へ順次タッチパネル走査電圧（Vstc）を供給する。ここで、図5、図6に示すように、各走査電極には、タッチパネル走査電圧（Vstc）が複数回（図6では8回）供給される。

図6に示すように、検出回路108は、RX0～RX4の各検出電極に流れる電流を積算し（図6では負方向への積算）、到達した電圧値（V<sub>a</sub>、V<sub>b</sub>）を記録する。

走査電極（TX）と検出電極（RX）との交点付近を、指（導体）がタッチしている場合、指へも電流が流れるため、積算結果の電圧値に変化が生じる。

例えば、図6において、走査電極(TX0)と検出電極(RXn)との交点付近に指が存在しない場合(図6のNAに示すタッチ無しの状態)、検出電極に流れる電流を積算した電圧は、非タッチレベル(LA)となる。

これに対して、走査電極(TX2)と検出電極(RXn)との交点付近には指が存在する場合(図6のNBに示すタッチ有りの状態)、指へも電流が流れ、検出電極に流れる電流を積算した電圧は、非タッチレベル(LA)よりも高電位の電圧となる。この変化量(タッチ信号)によりタッチ位置を検出することができる。

#### 【0014】

図7は、本発明の前提となるインセル方式の液晶表示装置における、タッチパネル検出時と、画素書き込み時のタイミングを説明するための図である。なお、図7において、T3は帰線期間、VSYNCは垂直同期信号、HSYNCは水平同期信号である 10

図7のAは、1フレームの画素書き込み期間(T4)に、1番目の表示ラインから1280表示ラインまでの画素書き込みタイミングを示し、図7のBが、20ブロックに分割された各ブロックの対向電極(CT1～CT20)におけるタッチパネル検出タイミングを示す。

図7に示すように、任意の表示ラインの対向電極を走査電極(TX)として機能させ、タッチパネル検出時のスキャン動作は、画素書き込みを行うゲートスキャンとは異なる箇所で行う。

図7で説明したように、ゲートスキャンと、タッチパネル走査は異なる表示ラインで実施しているが、映像線と対向電極(CT)との間、および、走査線と対向電極(CT)との間には寄生容量があるため、映像線上の電圧(VDL)の変動、あるいは、走査電圧(VGL)の立ち上がり、あるいは、立ち下り時に生じるノイズにより、タッチパネル検出時の検出感度が低下する。 20

そこで、本発明の前提となるインセル方式の液晶表示装置では、タッチ位置検出動作は、映像線上の電圧(VDL)の変動、あるいは、走査電圧(VGL)の立ち上がり、あるいは、立ち下りがない期間に実行される。

#### 【0015】

図8は、本発明の実施例のインセル方式の液晶表示装置の検出回路108のより具体的な回路構成を示す回路図である。

図9は、図8に示す回路の動作を説明するためのタイミングチャートである。 30

図8において、MPUはマイクロコンピュータ、CINTは積分容量、Cc1bはキャリブレーション容量、10は積分回路、11はサンプルホールド回路、12は10ビットのAD変換器、13はAD変換器12から出力されるデータ(以下、Rawデータ)を格納する検出RAM、14はキャリブレーションRAM、15は8ビットのDA変換器、107はタッチパネル、108検出回路である。

以下、図9を用いて、本実施例の検出回路108の動作を説明する。なお、図9において、Hsyncは水平同期信号である。

(1) 各検出電極(RX0～RXn)に流れる電流を検出(積分)前に、スイッチ(S1)をオンして、積分回路10をリセットするとともに、スイッチ(S3)をオンとして、各検出電極(RX0～RXn)をリセットする(図9のA1の期間)。基準電圧(VREF)を4V(VREF=4V)とすると、積分回路10の出力は4V、各検出電極(RX0～RXn)は、4Vにプリチャージされる。 40

また、スイッチ(S5)は、基準電圧(VREF)側に接続されており、キャリブレーション容量(Cc1b)の両端には、基準電圧(VREF)の4Vが印加されているため、キャリブレーション容量(Cc1b)の電荷は「0」である。

#### 【0016】

(2) 次に、スイッチ(S1)とスイッチ(S3)をオフとした後、TX0～TXmの走査電極の1つから、タッチパネル走査電圧(Vstc)を出力し、スイッチ(S5)を、DA変換器15側に切り替え、キャリブレーション容量(Cc1b)の一端に、DA変換器15から出力されるキャリブレーション電圧(VDAC)を印加し、電荷の引き抜きを 50

行った後に、スイッチ(S2)をオンとして残りの電荷を積分容量(CINT)に積分する(図9のB1の期間)。

これにより、TX0～TXmの走査電極の1つ 交差容量(Cxy) 積分容量(CINT)の経路で電流が流れ、積分回路10の出力電圧(VINT)が低下する。

ここで、(交差容量(Cxy)の電荷)-(キャリブレーション容量(Cc1b)の電荷)=積分容量(CINT)の電荷であり、

$$VINT = VREF - (Vstc * Cxy - Vc1b * Cc1b) / Cint$$

なお、Cintは積分容量(CINT)の容量値であり、また、Vc1bは、キャリブレーション容量(Cc1b)の両端に印加される電圧であり、(Vc1b = VREF - VDAC)である。

(3) 積分回路10での積分終了後、スイッチ(S2)をオフ、スイッチ(S3)をオンとし、かつ、スイッチ(S5)を基準電圧(VREF)側に接続して、各検出電極(RX0～RXn)を4Vにプリチャージするとともに、キャリブレーション容量(Cc1b)の電荷を「0」とする(図9のA2の期間)。

#### 【0017】

(4)(2)の積分回路10での積分動作を繰り返し、電圧を積み上げる(図9のB2, …の期間)。

(5) 積分回路10での積分完了後(図9のBnの期間後)、スイッチ(S4)をオンとして、サンプルホールド回路11でサンプル&ホールドし(図9のCの期間)、その後、スイッチ(S6)を順次オンとして、AD変換器13でAD変換し、検出RAM(13)に、RX0～RXnの走査電極分のRawデータを格納する。

AD変換器12が、10bitのAD変換器の場合、Rawデータは0(積分0V)～1023(積分4V)の範囲となる。

(6)(1)～(5)の処理を、全ての走査電極(TX0～TXm)について順次実行し、各走査電極(TX0～TXm)と各検出電極(RX0～RXn)の交点1面分のRawデータを検出RAM(13)に格納する。

(7) 交差容量(Cxy)は非タッチ時>タッチ時であるので、図6のVa、Vbに示すように、積分回路10での積分出力電圧(VINT)の降下に差が生じ、ここにしきい値を設けて、タッチ検出する。

#### 【0018】

図10は、本発明の実施例のインセル方式の液晶表示装置のタッチパネル107、検出RAM(13)、および、キャリブレーションRAM(14)のアドレスマップを示す図である。

同図(a)が、タッチパネル107のアドレスマップを、同図(b)が検出RAM(13)のアドレスマップを、同図(c)が後述するキャリブレーションRAM(14)のアドレスマップを示す。

図10に示すように、図10(a)に示す各走査電極(TX0～TXm)と各検出電極(RX0～RXn)の交点に対応する、積分回路10での積分出力電圧(VINT)をAD変換器12でAD変換し、交点1面分のRawデータを検出RAM(13)の当該交点のアドレス位置に格納する。

同様に、図10(a)に示す各走査電極(TX0～TXm)と各検出電極(RX0～RXn)の交点に対応するキャリブレーションデータを、キャリブレーションRAM(14)の当該交点のアドレス位置に格納する。

例えば、図10(a)に示すように、走査電極(TX0)と検出電極(RX0)の交点のアドレスが(0.0)の場合、走査電極(TX0)と検出電極(RX0)の交点の、積分回路10での積分出力電圧(VINT)は、検出RAM(13)の(0.0)のアドレス位置に格納され、走査電極(TX0)と検出電極(RX0)の交点のキャリブレーションデータは、キャリブレーションRAM(14)の(0.0)のアドレス位置に格納される。

#### 【0019】

10

20

30

40

50

次に、キャリブレーションについて説明する。

前述したように、各走査電極 (T X 0 ~ T X m) と各検出電極 (R X 0 ~ R X n) の交点の交差容量 (C x y) は、液晶層、ガラス基板、偏光板、接着樹脂などの誘電率や厚みのばらつき、また不均一性のため、個体差や面内ばらつきを持つため、キャリブレーションが必須である。

(7) 図11に示すように、非タッチ時Rawデータ動作点を255とし、マイクロコンピュータ(MPU)は、これをキャリブレーション目標値として、キャリブレーションRAM(14)のキャリブレーションデータを書き換え、DA変換器15から出力されるキャリブレーション電圧(VDAC)を可変しながら収束させる。

なお、非タッチ時のRawデータ動作点とは、非タッチ時の積分回路10での積分出力電圧(VINT)を、サンプルホールド回路11でサンプル&ホールドし、10ビットのAD変換器12でAD変換したときのRawデータであることは言うまでもない。

(8) キャリブレーションは動作点を移動させる作用のみで、検出感度には影響しない。

検出感度 = (C x y / Cint) \* Vstc

$$C x y = C x y\_u t \text{ (非タッチ時の交差容量)} - C x y\_t \text{ (タッチ時の交差容量)}$$

なお、通常、キャリブレーション範囲が、8ビットで[8'h80]の付近、即ち、基準電圧(VREF; 本実施例では、4V)とGND(0V)の電圧の中間付近の電圧となるように、キャリブレーション容量(Cc1b)を決定する。また、通常、キャリブレーション容量(Cc1b)は、ダイオード接続されたMOSトランジスタの接合容量を利用するので、キャリブレーション容量(Cc1b)の増減は、ダイオード接続されたMOSトランジスタが、並列に接続される個数で調整する。

#### 【0020】

次に、互いに隣接する2つの検出電極がショートしているか否かの検査(以下、RX隣接ショート検査という)について説明する。

本実施例では、RX隣接ショート検査に、前述したキャリブレーション容量(Cc1b)を利用する。

図12に示すように、RX隣接ショート検査時、キャリブレーションRAM(14)における、奇数番目の検出電極に対応するアドレス(図12のR0, R2, R4の列)には、電荷を引き抜かないキャリブレーションデータ(8ビットで[8'h00])を、キャリブレーションRAM(14)における、偶数番目の検出電極に対応するアドレス(図12のR1, R3, R5の列)には、十分に電荷を引き抜けるキャリブレーションデータ(8ビットで[8'hFF])を設定する。

キャリブレーションRAM(14)に、電荷を引き抜かないキャリブレーションデータ(8ビットで[8'h00])を設定すると、DA変換器15から出力されるキャリブレーション電圧(VDAC)は、基準電圧(VREF; 本実施例では、4V)となり、キャリブレーションRAM(14)に、十分に電荷を引き抜けるキャリブレーションデータ(8ビットで[8'hFF])を設定すると、DA変換器15から出力されるキャリブレーション電圧(VDAC)は、GND(0V)付近の電圧となる。

#### 【0021】

フレキシブル配線基板(図1(a)の53、図1(a)、(b)のMFP)上の配線を含めて、互いに隣接する2つの検出電極が、RX隣接ショートしていない場合、奇数番目の検出電極(RX)に接続されるキャリブレーション容量(Cc1b)の他端には、基準電圧(VREF)が印加されている。

そのため、走査電極(TX)から奇数番目の検出電極(RX)に流れる電流は、積分回路10に流れ、即ち、キャリブレーション容量(Cc1b)での電荷の引き抜きがないので、積分回路10の積分容量(CINT)で積分され、図13に示すように、積分回路10の出力は、GNDに飽和する。

したがって、積分回路10での積分出力電圧(VINT)を、サンプルホールド回路11でサンプル&ホールドし、AD変換器12でAD変換したときのRawデータは、Raw = 0となる。

10

20

30

40

50

また、互いに隣接する2つの検出電極が、RX隣接ショートしていない場合、偶数番目の検出電極(RX)に接続されるキャリブレーション容量(Cc1b)の他端には、GND(0V)付近の電圧が印加されている。

そのため、走査電極(TX)から奇数番目の検出電極(RX)に流れる全ての電流はキャリブレーション容量(Cc1b)に流れ、即ち、キャリブレーション容量(Cc1b)により、全電荷が引き抜かれ、また、積分回路10の積分容量(CINT)からも電荷が移動し、積分回路10の積分出力電圧(VINT)は上昇し、図14に示すように、VDD(5V)に飽和する。

したがって、積分回路10での積分出力電圧(VINT)を、サンプルホールド回路11でサンプル&ホールドし、AD変換器12でAD変換したときのRawデータは、Raw = 1023となる。

10

よって、図15(a)に示すように、検出RAM(13)に格納されるRawデータは、奇数番目の検出電極(RX)に対応する列が、10ビットで[1023]の値、偶数番目の検出電極(RX)に対応する列が、10ビットで[0]の値となる。

#### 【0022】

一方、フレキシブル配線基板(図1(a)の53、図1(a)、(b)のMFPc)上の配線を含めて、互いに隣接する2つの検出電極が、RX隣接ショートしている場合、走査電極(TX)から奇数番目の検出電極(RX)に流れる全ての電流は、他端にGND(0V)付近の電圧が印加されている、偶数番目の検出電極(RX)に接続されるキャリブレーション容量(Cc1b)に流れ、即ち、全電荷が引き抜かれ、また、積分回路10の積分容量(CINT)からも電荷が移動し、積分回路10の積分出力電圧(VINT)は上昇し、図14に示すように、VDD(5V)に飽和する。

20

したがって、積分回路10での積分出力電圧(VINT)を、サンプルホールド回路11でサンプル&ホールドし、AD変換器12でAD変換したときのRawデータは、Raw = 1023となる。

よって、図15(b)に示すように、検出RAM(13)に格納されるRawデータの中で、RX隣接ショートしている、互いに隣接する2つの検出電極に対応する列のRawデータは、10ビットで[1023]の値となる。

このように、本実施例によれば、簡単かつ短時間にRX隣接ショート不良を検出することができる。

30

#### 【0023】

なお、前述の説明から理解できるように、奇数番目の検出電極(RX)(または、偶数番目の検出電極(RX))に、スイッチ回路を介して、大きめの容量値を有する容量素子を接続し、かつ、GNDの電圧を出力する定電圧源を設け、RX隣接ショート検査に、スイッチ回路をオンとして、奇数番目の検出電極(RX)(または、偶数番目の検出電極(RX))に、他端に定電圧源からのGNDの電圧が印加されている容量素子を接続するようにも、簡単かつ短時間にRX隣接ショート不良を検出することができる。

この時、フレキシブル配線基板(図1(a)の53、図1(a)、(b)のMFPc)上の配線を含めて、互いに隣接する2つの検出電極が、RX隣接ショートしていない場合は、検出RAM(13)に格納されるRawデータは、スイッチ回路を介して、大きめの容量値を有する容量素子を接続される検出電極(RX)に対応する列が、10ビットで[1023]の値、それ以外の検出電極(RX)に対応する列が、キャリブレーション終了後の非タッチレベルの、10ビットで[255]の値となる。

40

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

#### 【符号の説明】

#### 【0024】

2 第1基板

3 第2基板

|         |                      |    |

|---------|----------------------|----|

| 4       | 液晶組成物                |    |

| 5       | 液晶ドライバ I C           |    |

| 1 0     | 積分回路                 |    |

| 1 1     | サンプルホールド回路           |    |

| 1 2     | A D 変換器              |    |

| 1 3     | 検出 R A M             |    |

| 1 4     | キャリブレーション R A M      |    |

| 1 5     | D A 変換器              |    |

| 2 1     | 対向電極                 |    |

| 2 2     | 対向電極信号線              | 10 |

| 2 5     | 駆動回路用入力端子            |    |

| 3 1     | 検出電極                 |    |

| 3 3     | ダミー電極                |    |

| 3 6     | 検出電極用端子              |    |

| 4 0     | フロントウィンドウ(又は、保護フィルム) |    |

| 5 3     | 接続用フレキシブル配線基板        |    |

| 1 0 1   | L C D ドライバ           |    |

| 1 0 2   | シーケンサ                |    |

| 1 0 3   | タッチパネル走査電圧生成回路       |    |

| 1 0 6   | デコーダ回路               | 20 |

| 1 0 7   | タッチパネル               |    |

| 1 0 8   | 検出回路                 |    |

| 2 0 0   | 画素部                  |    |

| 5 0 2   | 指                    |    |

| M P U   | マイクロコンピュータ           |    |

| M F P C | メインフレキシブル配線基板        |    |

| T X     | タッチパネルの走査電極          |    |

| R X     | タッチパネルの検出電極          |    |

【図1(a)】

図1(a)

【図1(b)】

図1(b)

【図2】

図2

【図3】

図3

【図4】

【図5】

図5

【図6】

【図7】

【図8】

【図9】

図9

【図10】

【図13】

図13

【図14】

図14

【図11】

図11

【図12】

図12

|     | R0 | R1 | R2 | R3 | R4 | R5 |

|-----|----|----|----|----|----|----|

| C0  | 00 | FF | 00 | FF | 00 | FF |

| C1  | 00 | FF | 00 | FF | 00 | FF |

| C2  | 00 | FF | 00 | FF | 00 | FF |

| C3  | 00 | FF | 00 | FF | 00 | FF |

| C4  | 00 | FF | 00 | FF | 00 | FF |

| C5  | 00 | FF | 00 | FF | 00 | FF |

| C6  | 00 | FF | 00 | FF | 00 | FF |

| C7  | 00 | FF | 00 | FF | 00 | FF |

| C8  | 00 | FF | 00 | FF | 00 | FF |

| C9  | 00 | FF | 00 | FF | 00 | FF |

| C10 | 00 | FF | 00 | FF | 00 | FF |

【図15】

図15

|     | R0   | R1   | R2   | R3 | R4   | R5 |

|-----|------|------|------|----|------|----|

| C0  | 1023 | 0    | 1023 | 0  | 1023 | 0  |

| C1  | 1023 | 0    | 1023 | 0  | 1023 | 0  |

| C2  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C3  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C4  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C5  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C6  | 1023 | 0    | 1023 | 0  | 1023 | 0  |

| C7  | 1023 | 0    | 1023 | 0  | 1023 | 0  |

| C8  | 1023 | 0    | 1023 | 0  | 1023 | 0  |

| C9  | 1023 | 0    | 1023 | 0  | 1023 | 0  |

| C10 | 1023 | 0    | 1023 | 0  | 1023 | 0  |

(a)

|     | R0   | R1   | R2   | R3 | R4   | R5 |

|-----|------|------|------|----|------|----|

| C0  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C1  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C2  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C3  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C4  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C5  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C6  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C7  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C8  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C9  | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

| C10 | 1023 | 1023 | 1023 | 0  | 1023 | 0  |

(b)

---

フロントページの続き

審査官 原 秀人

(56)参考文献 特開2009-258182(JP, A)

特開2012-234473(JP, A)

米国特許出願公開第2011/0267296(US, A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 3 / 041

G 06 F 3 / 044