(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5419659号

(P5419659)

(45) 発行日 平成26年2月19日(2014.2.19)

(24) 登録日 平成25年11月29日(2013.11.29)

(51) Int.Cl.

F 1

H04N 5/355 (2011.01)

H04N 5/335 550

H04N 5/374 (2011.01)

H04N 5/335 740

H04N 5/378 (2011.01)

H04N 5/335 780

請求項の数 10 (全 9 頁)

(21) 出願番号

特願2009-276703 (P2009-276703)

(22) 出願日

平成21年12月4日 (2009.12.4)

(65) 公開番号

特開2011-120087 (P2011-120087A)

(43) 公開日

平成23年6月16日 (2011.6.16)

審査請求日

平成24年11月20日 (2012.11.20)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 大屋 武

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 鈴木 肇

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換により画素信号を生成する一の画素と、

前記一の画素により生成された画素信号に対して複数のゲインで増幅し、前記複数のゲインに対応する複数の画素信号を出力する増幅部と、

前記増幅部により出力された画素信号の大きさに応じて、前記増幅部により出力された複数の画素信号のうちの1つを選択し、前記選択した画素信号に基づく信号を出力する合成部と、

前記合成部により選択された画素信号に対応する前記増幅部のゲインに応じて、前記合成部により出力された信号に対して信号処理する信号処理部と

を有し、

前記合成部は、前記増幅部により出力された画素信号と閾値とを比較し、前記比較の結果に応じて前記選択を行い、

前記信号処理部は、前記合成部により出力された信号及び前記閾値を比較し、前記比較の結果を前記増幅部のゲインの情報として、前記増幅部のゲインに応じて、前記合成部により出力された信号に対して信号処理することを特徴とする撮像装置。

## 【請求項 2】

前記合成部は、前記選択した画素信号に基づく信号に前記増幅部のゲインの情報を付加して前記信号処理部に出力することを特徴とする請求項1記載の撮像装置。

## 【請求項 3】

10

20

前記信号処理部は、前記合成功部により出力された信号に含まれる前記増幅部のゲインの情報に応じて、前記合成功部により出力された信号に対して信号処理することを特徴とする請求項1記載の撮像装置。

**【請求項4】**

前記増幅部のゲインの情報は、前記合成功部により出力された信号のうちの前記複数のゲインの倍率差に相当するビット数であることを特徴とする請求項3記載の撮像装置。

**【請求項5】**

前記合成功部は、前記閾値を前記信号処理部に出力することを特徴とする請求項1記載の撮像装置。

**【請求項6】**

前記信号処理部は、前記閾値を前記合成功部に出力することを特徴とする請求項1記載の撮像装置。

10

**【請求項7】**

さらに、前記閾値を前記合成功部及び前記信号処理部に出力するコントロール部を有することを特徴とする請求項1記載の撮像装置。

**【請求項8】**

前記増幅部の2つのゲインの設定値 $a_i$ 及び $b_i$ に対し、前記2つのゲインの実際値が $a_r$ 及び $b_r$ である場合、 $a_i > b_i$ であるとき、 $a_r < b_r \times a_i / b_i$ の関係が成立することを特徴とする請求項3～7のいずれか1項に記載の撮像装置。

**【請求項9】**

前記画素が行列状に複数設けられ、

前記増幅部が前記画素の各列に対応して複数設けられ、

さらに、前記複数の増幅部に対応して設けられ、前記複数の増幅部により出力される画素信号をアナログデジタル変換する複数のアナログデジタル変換部を有することを特徴とする請求項1～8のいずれか1項に記載の撮像装置。

20

**【請求項10】**

前記合成功部は、前記増幅部により出力された複数の画素信号が同じゲインの信号になるようにビットシフトにより正規化し、前記正規化された複数の画素信号のうちの1つを選択して出力することを特徴とする請求項1～9のいずれか1項に記載の撮像装置。

**【発明の詳細な説明】**

30

**【技術分野】**

**【0001】**

本発明は、撮像装置に関する。

**【背景技術】**

**【0002】**

撮像装置では、S/Nの改善やダイナミックレンジの拡大が求められている。それを実現する一つの方法として、特許文献1に開示されているような方法がある。この方法では、アナログ信号の大きさに応じて、A/D変換前にかけるゲインを切り替えている。小さなアナログ信号には大きなゲインをかけることで、その後に加わるノイズの影響を相対的に小さくし、その結果S/Nの改善を実現している。撮像装置においては、画像読み出し後に種々の画像処理を行う画像処理部がある。例えば、特許文献1の撮像装置の場合は、ノイズキャンセラ+ゲインミスマッチ回路の後段に接続されることになる。画像処理部において、ゲイン補正やシェーディング補正等の処理をする場合に、各画素データがどのゲインで読み出されたかという情報が必要になる場合がある。特許文献1においては、同文献の図1、図10に示されるように、A/D変換前にかけたゲイン情報については、出力データNビットと別に、Mビットの信号として後段に出力している。

40

**【先行技術文献】**

**【特許文献】**

**【0003】**

【特許文献1】特開2004-15701号公報

50

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

しかしながら、特許文献1のように画像データとゲイン情報を別々に後段に出力することは、出力線数の増加・システムの煩雑化につながる。

**【0005】**

本発明の目的は、簡素な構成で、ダイナミックレンジを拡大し、增幅部のゲインに応じて信号処理を行うことができる撮像装置を提供することである。

**【課題を解決するための手段】****【0006】**

本発明の撮像装置は、光電変換により画素信号を生成する一の画素と、前記一の画素により生成された画素信号に対して複数のゲインで増幅し、前記複数のゲインに対応する複数の画素信号を出力する増幅部と、前記増幅部により出力された画素信号の大きさに応じて、前記増幅部により出力された複数の画素信号のうちの1つを選択し、前記選択した画素信号に基づく信号を出力する合成部と、前記合成部により選択された画素信号に対応する前記増幅部のゲインに応じて、前記合成部により出力された信号に対して信号処理する信号処理部とを有し、前記合成部は、前記増幅部により出力された画素信号と閾値とを比較し、前記比較の結果に応じて前記選択を行い、前記信号処理部は、前記合成部により出力された信号及び前記閾値を比較し、前記比較の結果を前記増幅部のゲインの情報として、前記増幅部のゲインに応じて、前記合成部により出力された信号に対して信号処理することを特徴とする。

**【発明の効果】****【0007】**

本発明によれば、ダイナミックレンジを拡大することができ、簡素な構成で、増幅部のゲインに応じて信号処理を行うことができる。

**【図面の簡単な説明】****【0008】**

【図1】本発明の第1の実施形態による撮像装置のブロック図である。

【図2】ダイナミックレンジを拡大する動作を説明する図である。

【図3】固体撮像素子の内部構成の一例を示す図である。

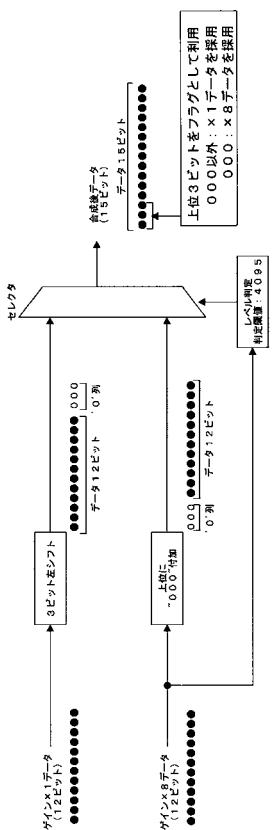

【図4】列合成部の動作方式の一例を示す図である。

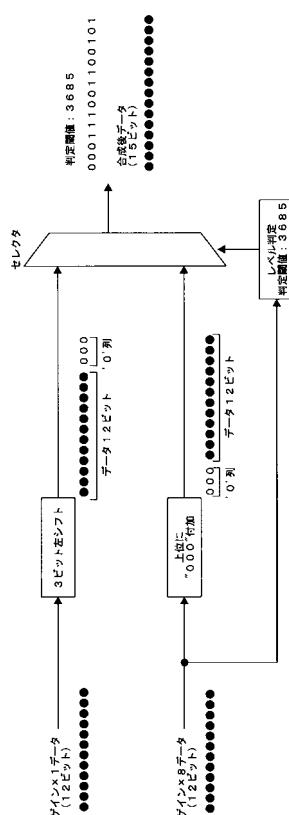

【図5】列合成部の動作方式の一例を示す図である。

【図6】列合成部の動作方式の一例を示す図である。

**【発明を実施するための形態】****【0009】****(第1の実施形態)**

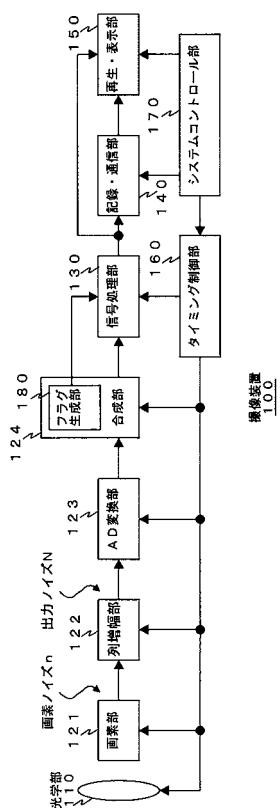

図1は、本発明の第1の実施形態による撮像装置100の構成例を示すブロック図である。光学部110を通って入射した被写体光は、画素部121上に結像される。画素部121は、例えば画素が2次元行列状に配置されており、入射した被写体光が結像されると、各画素により被写体光が電気信号(画素信号)に変換されて画像が撮像される。画素部121の各画素で変換された画像信号は、列増幅部122によって複数のゲインで増幅される。列増幅部122は、複数のゲインに対応する複数の画素信号を出力する。列増幅部122からのゲインの異なる複数の出力が、A/D変換部123でアナログデジタル(A/D)変換され、さらに合成部124で合成される。合成部124は、入力した画素信号の大きさに応じて、入力した複数の画素信号のうちの1つを選択し、選択した画素信号に基づく信号を出力する。合成の方法については後述する。信号処理部130は、合成部124により選択された画素信号に対応する列増幅部122のゲインに応じて、合成部124により出力された信号に対して、予め決められた方法によって信号処理を行う。そして、信号処理部130で信号処理された画像信号は、記録・通信部140によって記録媒体への記録や外部装置への出力が行われたり、あるいは、再生・表示部150に直接出力されて

10

20

30

40

50

再生や表示がなされたりする。また、記録・通信部 140 によって記録媒体に記録された画像信号は、必要に応じて、再生・表示部 150 に出力されて再生や表示がなされる。

#### 【0010】

タイミング制御部 160 は、システムコントロール部 170 による制御に基づき、光学部 110、画素部 121、列増幅部 122、A/D 変換部 123、合成部 124、及び信号処理部 130 の駆動タイミングを制御する。システムコントロール部 170 は、撮像装置 100 の動作を統括的に制御するものであり、記録・通信部 140、再生・表示部 150、及びタイミング制御部 160 の各構成部を制御する。また、システムコントロール部 170 は、タイミング制御部 160 を通じて、光学部 110、画素部 121、列増幅部 122、A/D 変換部 123、合成部 124、及び信号処理部 130 の駆動を制御する。フラグ生成部 180 は、合成部 124 で用いられた元データを特定するためのフラグを生成し、信号処理部 130 に出力する。フラグの付け方の詳細は、後述する。信号処理部 130 はそのフラグ情報により元データを判断し、信号処理をする。なお、ここでは、フラグ生成部 180 が合成部 124 の内部にある例を示しているが、この限りでなく、例えばタイミング制御部 160 やシステムコントロール部 170 内にある場合や、独立してある場合も考えられる。10

#### 【0011】

ダイナミックレンジを拡大するための原理及び合成部 124 の基本動作について説明する。本実施形態では、同一の画素データを複数のゲインで列増幅部 122 から読み出し、合成部 124 にて合成する。なお、以下では簡単のため  $\times 1$  と  $\times 8$  のゲインで増幅された信号を合成する場合を例にするが、この限りでなく、ゲインの組み合わせは例えば  $\times 1$  と  $\times 16$ 、 $\times 2$  と  $\times 16$  等、他の組み合わせであってもよい。また、以下では列増幅部 122 のゲインは固定として書いているが、当然、列増幅部 122 は可変でもよい。また合成するゲインの組み合わせは 2 組に限らず、3 組以上でもよい。20

#### 【0012】

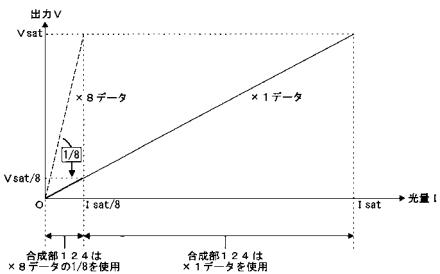

図 2 は、画素部 121 の画素に入射される光量  $I$  と、列増幅部 122 から出力されるデータ  $V$  の関係をグラフにしたものである。ゲインが  $\times 1$  のときのデータと、ゲインが  $\times 8$  の時のデータを示してある。ゲインが  $\times 1$  のデータは、光量  $I_{sat}$  で飽和出力  $V_{sat}$  に達する。一方、ゲインが  $\times 8$  のデータは、その  $1/8$  の光量  $I_{sat}/8$  で飽和出力  $V_{sat}$  に達する。この方法では、列増幅部 122 はゲインが  $\times 1$  とゲインが  $\times 8$  の 2 種類のデータを出力する。その 2 種類のデータは A/D 変換部 123 により A/D 変換され、合成部 124 に伝えられる。合成部 124 では、図 2 のグラフ下に示すように、例えば  $\times 8$  のデータが飽和していない場合には、 $\times 8$  のデータを  $1/8$  倍したデータを出力データとして採用する。それ以外の場合には、 $\times 1$  のデータを出力データとして採用する。30

#### 【0013】

このときのノイズ、及びダイナミックレンジについて説明する。信号には、画素部 121 から列増幅部 122 の手前までに画素ノイズ  $n$  が、列増幅部 122 から A/D 変換部 123 の手前までに出力ノイズ  $N$  が加重される。ゲインが  $\times 1$  のときの画素ノイズ  $n$  を “ $n_1$ ” とすると、ゲインが  $\times 8$  のときの画素ノイズ  $n$  はその 8 倍の “ $8 \times n_1$ ” である。一方、出力ノイズ  $N$  はゲインの影響を受けないため、ゲインが  $\times 1$  でも  $\times 8$  でも同等である。この出力ノイズ  $N$  を “ $N_0$ ” とする。ゲインが  $\times 1$  のときの全ノイズは “ $n_1 + N_0$ ” であり、ゲインが  $\times 8$  のときの全ノイズは “ $8 \times n_1 + N_0$ ” である。ここで、‘+’ はノイズの和を表しており、2 乗和の平方根を表す。以下の記述も同様である。40

#### 【0014】

ゲインが  $\times 8$  のデータを  $1/8$  にすると、ノイズも  $1/8$  となる。よって、ゲインが  $\times 8$  のデータを  $1/8$  倍したときの全ノイズは “ $n_1 + N_0/8$ ” となり、ゲインが  $\times 1$  の場合にくらべて、出力ノイズ  $N$  の影響が  $1/8$  に減少する。つまり、前述のように合成部 124 によって合成されたデータは、 $\times 1$  のデータに対して出力ノイズ  $N$  の影響が  $1/8$  になっている。一方、飽和出力は  $V_{sat}$  で変わらないので、“飽和出力 / 全ノイズ” を指標として表されるダイナミックレンジは大きくなる。50

## 【0015】

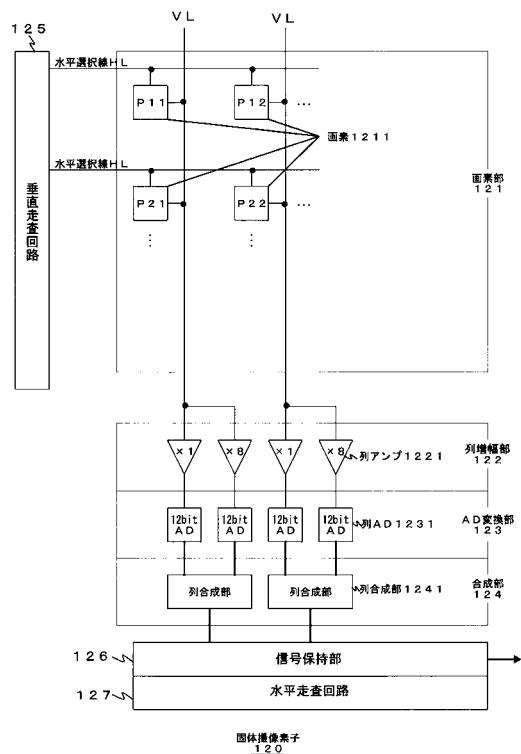

図3は、固体撮像素子120の内部構成の一例を示す図である。図3を用いて固体撮像素子120の動作を簡単に説明する。以下では固体撮像素子120がCMOSセンサの場合を例に説明するが、この限りでなく、固体撮像素子120がCCDセンサであってもよい。また、ここでは、画素部121、列増幅部122、AD変換部123、及び合成部124が、1つの固体撮像素子120の中にある場合を例に説明する。しかしながら、この限りでなく、例えば固体撮像素子120内には画素部121と列増幅部122があり、AD変換部123以降は固体撮像素子120外にあってもよい。

## 【0016】

画素部121には、画素1211が2次元マトリクス状に配列されている。画素1211は、光電変換により画素信号を生成する。垂直走査回路125の動作に応じて水平選択線HLの出力が定まり、水平方向の画素1211の行が順次選択される。選択された画素1211の行のデータが、垂直信号線VLを介して、列増幅部122内の列アンプ1221に伝えられる。列アンプ1221は、各列に対してゲインが×1倍のもの、ゲインが×8倍のものの2つが配置されている。列アンプ1221により×1倍及び×8倍されたデータは、AD変換部123内の列AD変換部1231によりAD変換される。以下では12ビットのAD変換が行われるものとするが、他のビット数のAD変換でもよく、またゲインごとに異なるビット数でもよい。その後、2種類のゲインのデータが、合成部124内の列合成部1241により合成される。合成後のデータは信号保持部126に一時保持され、水平走査回路127の動作に応じて一画素データずつ、固体撮像素子120の外部へ出力される。

## 【0017】

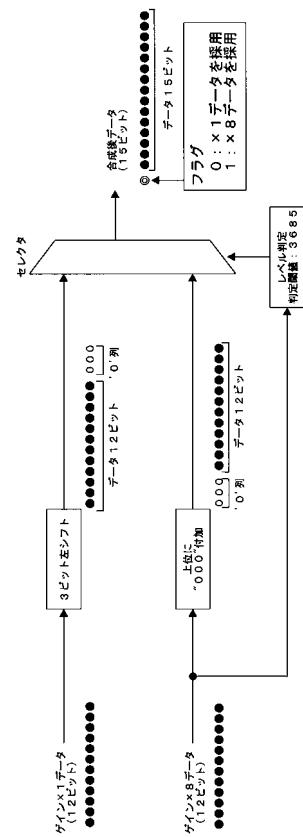

図4は、本発明の第1の実施形態による列合成部1241の動作を表す図である。列合成部1241は、列AD変換部1231より、ゲインが×1倍の12ビットデータ(画素信号)と、ゲインが×8倍の12ビットデータ(画素信号)を入力する。列合成部1241は、ゲインが×1倍の12ビットデータを左に3ビットシフト、つまり8倍して、15ビットデータとする。これによりゲインが×8倍のデータと、光量対出力の傾きが揃うことになる。ゲインが×8倍のデータには、上位の左側に‘0’を3ビット追加し、こちらも15ビットとする。ゲインが×8倍のデータの出力レベルを判定し、判定閾値より小さいレベルであれば、セレクタは元データのゲインが×8倍のデータを採用し、判定閾値以上のレベルであれば、セレクタは元データのゲインが×1倍のデータを採用するように動作する。判定閾値とは、例えば12ビットの最大値4095の9割に相当する3685、等といったように、システムによってあらかじめ定められたレベルである。すなわち、列合成部1241は、入力された複数のデータが同じゲインのデータになるようにビットシフトにより正規化し、正規化された複数のデータのうちの1つを選択して出力する。

## 【0018】

セレクタのデータ出力は15ビットである。列合成部124は、セレクタで選択されたデータの上位ビット(1ビット)として、セレクタがどちらのデータを採用したかを示すフラグを付加し、データとフラグを同一配線で信号処理部130に出力する。これにより、簡素な構成の撮像装置100を実現することができる。例えばフラグが0であれば元データのゲインは×1倍であり、フラグが1であれば元データのゲインは×8倍である、といったように定める。列合成部124は、ゲインが×8のデータの大きさに応じて、セレクタで選択するデータに対応するゲインのフラグ(情報)を付加する。すなわち、ゲインが×8のデータが判定閾値より小さければ1のフラグを付加し、判定閾値以上であれば0のフラグを付加する。後段の信号処理部130は、このフラグを観測することにより元データを判別することができる。例えば、信号処理部130は、フラグに応じて、ゲイン補正やシェーディング補正等の信号処理を行う。なお、ここに示した列合成部1241の方式は一例であり、合成方式や判定閾値、フラグの付け方等はこの限りでない。例えば、フラグは、必ずしもデータの上位ビット側に付加する必要はなく、下位ビット側等に付加してもよい。

10

20

30

40

50

## 【0019】

## (第2の実施形態)

図5は、本発明の第2の実施形態による列合成部1241の動作を表す図である。以下、本実施形態が第1の実施形態と異なる点を説明する。本実施形態の基本的な合成動作は第1の実施形態の場合と同様である。判定閾値とフラグのみが異なる。本実施形態では、12ビットの最大値4095を判定閾値とし、合成後のデータの15ビット中の上位3ビットをフラグとして利用する。元データのゲインが $\times 8$ 倍の場合、上位3ビットは必ず新たに付加された“000”である。また判定閾値はゲインが $\times 8$ 倍の場合で4095であり、これはゲインが $\times 1$ 倍の場合の512に相当する(4095/8)。ゲインが $\times 1$ 倍のデータは左3ビットシフト、つまり8倍されるので、セレクタへの入力は4096以上になる。つまり元データのゲインが $\times 1$ 倍の場合は、上位3ビットは必ず“000”以外となる。以上より、上位ビット(3ビット)をフラグ(ゲインの情報)として用い、後段の信号処理部130は、上位3ビットが“000”以外であれば元データのゲインは $\times 1$ 倍、“000”であれば元データのゲインは $\times 8$ 倍と判断することができる。なお、フラグに用いる‘0’のビットは、データのうちの複数のゲインの倍率差に相当するビット数の上位ビットを用いることが有効である(本実施形態の場合、8倍=3ビット)。また、フラグは、必ずしもデータの上位ビット側に付加する必要はなく、下位ビット側等に付加してもよい。

## 【0020】

## (第3の実施形態)

図6は、本発明の第3の実施形態による列合成部1241の動作を表す図である。以下、本実施形態が第1の実施形態と異なる点を説明する。本実施形態の基本的な合成方法は、第1の実施形態の場合と同様である。本実施形態ではフラグを用いず、全画素データに先立ち、判定閾値を合成部124から信号処理部130に出力する。これにより、信号処理部130では、その後に出てくる各画素データと、判定閾値とを比べることで、画素データが判定閾値以上であれば元データのゲインは $\times 1$ 倍、画素データが判定閾値より小さければ元データのゲインは $\times 8$ 倍と判断できる。すなわち、列合成部1241は、ゲインが $\times 8$ のデータと判定閾値とを比較し、その比較の結果に応じてセレクタで選択を行う。そして、合成部124は、先立って、判定閾値を信号処理部130に出力する。信号処理部130は、合成部124により出力されたデータ及び判定閾値を比較し、その比較の結果を列増幅部122のゲインの情報として、列増幅部122のゲインに応じて、合成部124により出力されたデータに対して信号処理する。なお、上記では全画素データの前のヘッダ情報として判定閾値を出力するとしたが、出力するタイミングはこの限りではない。また、他の例として、図1のシステムコントロール部170から、タイミング制御部160を介して、合成部124と信号処理部130の両方に判定閾値の情報を出力する方法もある。この方法でも、判定閾値を合成部124と信号処理部130で共有できるので、信号処理部130による元データのゲインの判別が可能となる。また、信号処理部130が合成部124に対して判定閾値を出力して指定する方法もある。

## 【0021】

## (第4の実施形態)

上記の第2の実施形態及び第3の実施形態では、ゲインが $\times 1$ 倍とゲインが $\times 8$ 倍の倍率差が、ぴったり8倍の場合を想定している。実際にはゲインは誤差を持ち、8倍からずれる可能性が大きい。本発明の第4の実施形態は、ゲイン誤差がある場合の解決策を示すものである。本発明の第4の実施形態の説明にも図6を用いる。例えば、列アンプ1221のゲインの $\times 8$ 倍の実際値が、設計値(設定値)に対して $\pm 2\%$ ばらつくとする。このときゲインの設計値が $\times 8$ 倍だと、最大で実際値は $\times 8.16$ 倍となる。実際のゲインが $\times 8.16$ 倍のとき、 $\times 8$ 倍の方のデータが3690であった場合を考える。判定閾値以上なので、 $\times 1$ 倍のデータが採用される。このとき、 $\times 1$ 倍のデータは、 $\times 8$ 倍のデータの“1/実ゲイン”的出力が、3ビットシフトで8倍されるので、(3690)/(8.16) $\times 8 = 3618$ である。これは判定閾値3685よりも小さい。よって後段の信号

10

20

30

40

50

処理部 130 は、元データを  $\times 8$  倍データだと判断してしまう。

【 0 0 2 2 】

このように、ゲインが $\times 8$ 倍を超えると、「合成部124から出力されるデータは判定閾値以下にも関わらず、元データが $\times 1$ 倍」という状況が発生してしまい、信号処理部130は正しく元データのゲインを判定できない。このようなことを避けるため、本実施形態では、例えば設計値を $\times 7.8$ 倍とし、 $\pm 2\%$ 誤差で最大 $\times 7.96$ 倍とすることで、最大でも $\times 8$ 倍を超えないように設定する。これにより、 $\times 1$ 倍のデータは必ず判定閾値を下回らないようにできる。なお、ここに挙げた数字は一例である。一般的には、列増幅部122の2つのゲインの設定値 $a_i$ 及び $b_i$ に対し、その2つのゲインの実際値が $a_r$ 及び $b_r$ である場合、 $a_i > b_i$ であるとき、 $a_r < b_r \times a_i / b_i$ の関係が成立するようすればよい。

【 0 0 2 3 】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

## 【符号の説明】

[ 0 0 2 4 ]

100 撮像装置、110 光学部、120 固体撮像素子、130 信号処理部、140 記録・通信部、150 再生・表示部、160 タイミング制御部、170 システムコントロール部、180 フラグ生成部

〔 四 1 〕

( 2 )

【図3】

【 四 4 】

( 5 )

( 6 )

---

フロントページの続き

(56)参考文献 特開2005-175517(JP,A)

国際公開第2009/108557(WO,A1)

特開2003-172611(JP,A)

特開2007-189537(JP,A)

特開2008-060708(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378