(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3838336号

(P3838336)

(45) 発行日 平成18年10月25日(2006.10.25)

(24) 登録日 平成18年8月11日(2006.8.11)

(51) Int.C1.

F 1

|             |             |                  |

|-------------|-------------|------------------|

| <b>H03B</b> | <b>5/32</b> | <b>(2006.01)</b> |

| <b>G04G</b> | <b>3/00</b> | <b>(2006.01)</b> |

| <b>H03B</b> | <b>5/04</b> | <b>(2006.01)</b> |

|        |      |

|--------|------|

| H 03 B | 5/32 |

| G 04 G | 3/00 |

| H 03 B | 5/04 |

|   |

|---|

| J |

| K |

| G |

請求項の数 7 (全 15 頁)

|            |                               |

|------------|-------------------------------|

| (21) 出願番号  | 特願2001-35694 (P2001-35694)    |

| (22) 出願日   | 平成13年2月13日 (2001.2.13)        |

| (62) 分割の表示 | 特願平8-339043の分割                |

| 原出願日       | 平成8年12月4日 (1996.12.4)         |

| (65) 公開番号  | 特開2001-257536 (P2001-257536A) |

| (43) 公開日   | 平成13年9月21日 (2001.9.21)        |

| 審査請求日      | 平成15年12月4日 (2003.12.4)        |

|           |                                               |

|-----------|-----------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (74) 代理人  | 100090387<br>弁理士 布施 行夫                        |

| (74) 代理人  | 100090398<br>弁理士 大渕 美千栄                       |

| (72) 発明者  | 矢部 宏<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内         |

| (72) 発明者  | 中宮 信二<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

最終頁に続く

(54) 【発明の名称】発振回路、電子回路、これらを備えた半導体装置、時計および電子機器

## (57) 【特許請求の範囲】

## 【請求項1】

主電源の電源電圧  $V_{ss}$  の絶対値より低い絶対値の定電圧  $V_{reg}$  で省電力駆動される発振回路において、

前記発振回路の信号路と前記定電圧  $V_{reg}$  側との間に接続され、信号路に侵入する第1の極性の静電圧を第1の半導体整流素子を介して選択的に前記定電圧  $V_{reg}$  側へバイパスさせる第1の静電保護回路と、

前記発振回路の信号路と基準電位側との間に接続され、信号路に侵入する第2の極性の静電圧を第2の半導体整流素子を介して選択的に前記基準電位側へバイパスさせる第2の静電保護回路と、

を含み、

前記第1の静電保護回路は、

前記発振回路の信号路と前記電源電圧  $V_{ss}$  との間に接続され、信号路に侵入する第1の極性の静電圧を選択的に前記電源電圧  $V_{ss}$  側へバイパスさせる第3の半導体整流素子を含むことを特徴とする発振回路。

## 【請求項2】

請求項1において、

前記第3の半導体整流素子の寄生容量値は、

前記第1の半導体整流素子の寄生容量値より小さな値に設定されたことを特徴とする発振回路。

**【請求項 3】**

請求項 1、2のいずれかにおいて、

前記各半導体整流素子の寄生容量を、

位相補償用コンデンサの一部または全部として用いることを特徴とする発振回路。

**【請求項 4】**

請求項 1 ~ 3のいずれかの発振回路を含むことを特徴とする電子回路。

**【請求項 5】**

請求項 1 ~ 4のいずれかの回路を含むことを特徴とする半導体装置。

**【請求項 6】**

請求項 1 ~ 4のいずれかの回路を備えたことを特徴とする時計。 10

**【請求項 7】**

請求項 1 ~ 4のいずれかの回路を備えたことを特徴とする電子機器。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、発振回路、電子回路、これらを備えた半導体装置、時計および電子機器に関する。

**【0002】****【背景技術および発明が解決しようとする課題】**

今日、携帯用の腕時計や電子機器は、主電源として電池や、充電可能な二次電池を用い、電子回路を駆動するものが多い。そして、このようなものに使用される前記電子回路は、発振回路の発振周波数  $f_s$  から基準クロックを作成するものが多い。 20

**【0003】**

通常、前記発振回路は、半導体基板上に構成されたその主要回路部分が、この半導体基板と別の箇所に設けられた水晶振動子と入出力端子を介して接続されている。このため、入出力端子を介して外部から侵入するサージ電圧から前記主要回路部分にを保護するために、前記主要回路部分の入出力端子側には静電保護回路が設けられている。

**【0004】**

このため、電子回路の負荷が増大し主電源の電圧  $V_{ss}$  に変動が生じると、これが前記静電保護回路の寄生容量値の変動を引き起こし、この結果、発振回路の発振周波数が変動してしまうという問題があった。 30

**【0005】**

すなわち、前記静電保護回路は、信号ラインとアース側との間に接続されたダイオードと、信号ラインと主電源  $V_{ss}$  側との間に接続されたダイオードとを含み、信号ラインに侵入するサージ電圧を、その極性に応じてアース側または電源電圧側へ選択的にバイパスすることで、内部回路の保護を図っている。

**【0006】**

ところで、前記静電保護回路では、ダイオードの P N 接合部分で、寄生容量が発生する。そして、この寄生容量の大きさは、負荷の変動などに起因して前記電源電圧  $V_{ss}$  が変動すると変化するという特性を有する。 40

**【0007】**

しかし、このように寄生容量値が変化すると、発振回路の発振定数が変化して、発振周波数そのものが変化してしまい、この結果、基準クロック周波数が変化し、電子回路各部の動作に悪影響が発生するという問題があった。

**【0008】**

特に、発振回路の発振出力を時計の基準クロックとして用いるような電子回路、例えば腕時計用の電子回路では、発振周波数が変化してしまうと、正確な時計動作そのものが損なわれてしまうという問題が生ずる。

**【0009】**

本発明の第 1 の目的は、主電源の電源電圧の変動の影響を受けることなく、安定した周波 50

数で発振することができる発振回路、電子回路、これらを備えた半導体装置、時計および電子機器を提供することにある。

#### 【0010】

本発明の第2の目的は、発振回路に設けられた静電保護回路の寄生容量を、発振回路を構成する位相補償用キャパシタの一部または全部として構成し、回路全体の構成をシンプルなものとし、その集積度を高めた発振回路、電子回路、これらを備えた半導体装置、時計および電子機器を提供することにある。

#### 【0011】

##### 【課題を解決するための手段】

(1) 本発明は、主電源の電源電圧  $V_{ss}$  の絶対値より低い絶対値の定電圧  $V_{reg}$  で省電力駆動される発振回路において、10

前記発振回路の信号路と前記定電圧  $V_{reg}$  側との間に接続され、信号路に侵入する第1の極性の静電圧を第1の半導体整流素子を介して選択的に前記定電圧  $V_{reg}$  側へバイパスさせる第1の静電保護回路と、

前記発振回路の信号路と基準電位側との間に接続され、信号路に侵入する第2の極性の静電圧を第2の半導体整流素子を介して選択的に前記基準電位側へバイパスさせる第2の静電保護回路と、

を含むことを特徴とする。

#### 【0012】

低消費電力型の電子回路では、主電源の電源電圧  $V_{ss}$  から、それより低い値をもつ定電圧  $V_{reg}$  を作成し、これを回路各部へ供給することが行われている。20

#### 【0013】

本発明の発振回路では、静電保護回路を、主電源の電源電圧  $V_{ss}$  側ではなく、この電源電圧  $V_{ss}$  から作成される定電圧  $V_{reg}$  側へ接続する構成を採用している。これにより、電源電圧  $V_{ss}$  が変動しても、静電保護回路に接続された定電圧  $V_{reg}$  が変動することがないため、静電保護回路を構成する半導体整流素子の寄生容量値の変動を効果的に抑制することができる。

#### 【0014】

このようにして、本発明によれば、主電源の電源電圧  $V_{ss}$  が変動しても、発振周波数が変動することのない発振回路を得ることができる。30

#### 【0015】

ここにおいて、前記静電保護回路に用いられる第1、第2の半導体整流素子としては、例えばダイオードや、バイポーラトランジスタ等を、必要に応じて用いることができる。

#### 【0016】

(2) 本発明は、(1)の発明において、

前記第1の静電保護回路は、

前記発振回路の信号路と前記電源電圧  $V_{ss}$  との間に接続され、信号路に侵入する第1の極性の静電圧を選択的に前記電源電圧  $V_{ss}$  側へバイパスさせる第3の半導体整流素子を含むことを特徴とする。

#### 【0017】

即ち、電源電圧  $V_{ss}$  を供給する主電源に比べ、その値より低い定電圧  $V_{reg}$  を作成する電源回路は、回路内部の容量成分が小さい。このため、定電圧  $V_{reg}$  側にのみ静電保護回路を接続すると、極めて大きなサージ電圧が侵入した場合には、その電圧に比し容量成分が小さすぎ、これに対処できない恐れがある。これに対し、本発明によれば、定電圧回路に比べ大きな容量成分を持つ主電源の電源電圧  $V_{ss}$  側へ、第3の半導体整流素子を接続する構成を採用する。これにより、大きなサージ電圧が侵入した場合でも、これを主電源側へ流すことができ、この結果、十分な静電破壊耐性を有し、しかも安定した発振出力を行う発振回路を得ることができる。40

#### 【0018】

(3) 本発明は、(2)の発明において、

50

前記第3の半導体整流素子の寄生容量値は、

前記第1の半導体整流素子の寄生容量値より小さな値に設定されたことを特徴とする。

#### 【0019】

ここにおいて、第3の半導体整流素子の寄生容量値は、第1の半導体整流素子の寄生容量値に比べ無視できる程度に小さい値に設定することが好ましい。

#### 【0020】

このようにすることにより、主電源の電源電圧Vssの変動により、第3の半導体整流素子の寄生容量値が変化した場合でも、これにほとんど影響を受けることなく、さらに安定した発振周波数の発振出力を得ることが可能となる。

#### 【0021】

10

(4) 本発明は、(1)～(3)の発明のいずれかにおいて、

前記各半導体整流素子の寄生容量を、

位相補償用コンデンサの一部または全部として用いることを特徴とする。

#### 【0022】

このようにすることにより、位相補償用コンデンサの一部又は全部を省略することができ、この結果、さらに回路全体の集積度を高めることが可能となる。

#### 【0023】

また、従来は、発振回路全体の容量成分を少なくして発振回路の消費電力を抑え、かつ半導体装置の面積を小さくするために、静電保護回路を構成する半導体整流素子として寄生容量値が小さく、かつサイズの小さなものが使用されていた。このため、半導体整流素子そのものを含めて回路全体の静電破壊耐性が十分でない場合もあった。これに対し、本発明によれば、寄生容量値の大きな半導体整流素子を積極的に用いて静電保護回路を構成することが可能となる。この結果、各半導体整流素子自体の静電破壊耐性を高め、静電保護回路としての機能をより充実することが可能となる。

20

#### 【0024】

(5) 本発明の電子回路は、(1)～(4)の発明に係るいずれかの発振回路を含むことを特徴とする。

#### 【0025】

これにより、発振回路から供給される安定した周波数出力を用い、良好に動作することができる電子回路を得ることが可能となる。

30

#### 【0026】

(6) 本発明の半導体装置は、(1)～(5)の発明に係るいずれかの回路を含むことを特徴とする。

#### 【0027】

即ち、水晶振動子を用いた発振回路や、この発振回路を用いた電子回路を半導体装置上に形成する場合には、所定回路基板上に形成された発振回路の主要回路部分と、この回路基板と異なるエリアに設けられた水晶振動子とを配線を介して接続する場合が多い。この場合に、水晶振動子と、主要回路部分との接続部分から、サージ電圧等の静電圧がノイズとして主要回路部分に侵入し、回路内部が破壊される恐れがある。

#### 【0028】

40

このような場合でも、本発明によれば、回路に侵入するサージ電圧等の静電圧を、静電保護回路を用いて良好に除去することができ、しかも安定した発振出力を用いて回路各部を良好に動作させることができ半導体装置を実現することができる。

#### 【0029】

(7) 本発明の時計は、(1)～(5)の発明に係る回路を備えたことを特徴とする。

#### 【0030】

本発明によれば、主電源の電源電圧が変動した場合でも、これに影響を受けることなく正確な計時動作を行うことができる時計を得ることができる。

#### 【0031】

(8) 本発明の電子機器は、(1)～(5)の発明に係る回路を備えたことを特徴と

50

する。

【0032】

本発明によれば、主電源の電源電圧が変動した場合でも、これに影響を受けることなく正確な発振出力を生成し、回路各部を動作させることができる電子機器を実現することができる。

【0033】

特に、(7)、(8)の発明は、交換可能な電池や充電可能な二次電池等を主電源として用いる携帯型の時計や、電子機器に適用する場合に極めて好適なものとなる。

【0034】

【発明の実施の形態】

本発明の好適な実施の形態を、本発明をアナログ表示型の腕時計に適用した場合を取り説く。

【0035】

(1) 全体構成

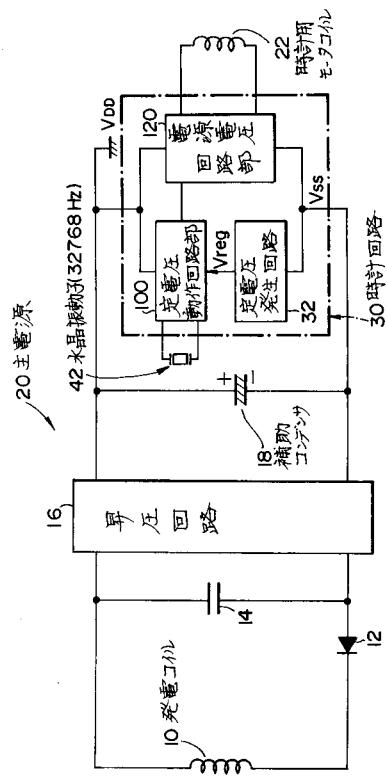

図1には、この腕時計に用いられる電子回路の一例が示されている。

【0036】

この腕時計は、図示しない発電機構を内蔵している。使用者が腕時計を装着し腕を動かすと、発電機構の回転錘が回転し、そのときの運動エネルギーにより発電ロータが高速回転され、発電ステータ側に設けられた発電コイル10から交流電圧が出力される。

【0037】

この交流電圧が、ダイオード12で整流され、二次電池14を充電する。この二次電池14は、昇圧回路16および補助コンデンサ18と共に主電源20を構成する。

【0038】

本実施の形態では二次電池14の電圧が低くて時計の駆動電圧に満たないときには、昇圧回路16により二次電池14の電圧を時計駆動可能な高電圧に変換し、補助コンデンサ18に蓄電する。そして、この補助コンデンサ18の電圧を電源電圧Vssとして時計回路30が動作する。

【0039】

この時計回路30は、半導体装置として構成されており、この半導体装置に端子を介して接続された水晶振動子42を用いて予め設定された発振周波数、ここで32765Hzの周波数の発振出力を生成し、この発振出力を分周することにより、一秒毎に極性の異なる駆動パルスを出力するように構成されている。この駆動パルスは、時計回路30に接続されたステップモータの駆動コイル22へ入力される。これにより、図示しないステップモータは、駆動パルスが通電される毎にロータを回転駆動し、図示しない時計の秒針、分針、時針を駆動し、時刻をアナログ表示することになる。

【0040】

ここにおいて、本実施の形態の時計回路30は、主電源から供給される電源電圧Vssにより駆動される電源電圧回路部120と、この電源電圧Vssからこの値より低い所定の一定電圧Vregを生成する定電圧発生回路32と、この定電圧Vregにより駆動される定電圧動作回路部100とを含んで構成される。

【0041】

(2) 時計回路

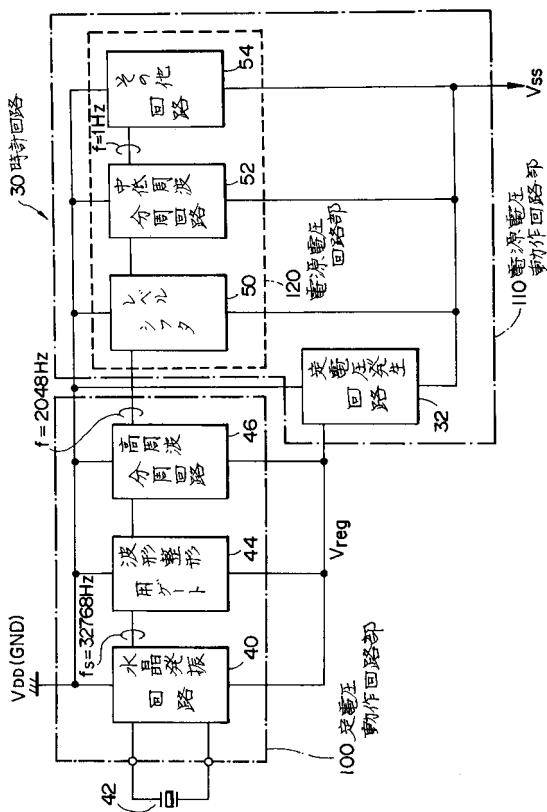

図2には、前記時計回路30のより詳細な機能ブロック図が示されている。

【0042】

前記定電圧動作回路部100は、外部接続された水晶振動子42を一部に含んで構成された水晶発振回路40と、波形整形ゲート44と、高周波分周回路46とを含んで構成される。

【0043】

前記電源電圧回路部120は、レベルシフタ50と、中低周波分周回路52と、その他の回路54とを含んで構成される。なお、本実施の形態の時計回路では、前記電源電圧回路

10

20

30

40

50

部 120 と、定電圧発生回路 32 とは、主電源 20 から供給される電源電圧 Vss により駆動される電源電圧動作回路部 110 を構成している。

【0044】

前記水晶発振回路 40 は、水晶振動子 42 を用いて基準周波数  $f_s = 32768 \text{ Hz}$  の正弦波出力を波形整形ゲート 44 に出力する。

【0045】

前記波形整形ゲート 44 は、この正弦波出力を矩形波に整形した後、高周波分周回路 46 へ出力する。

【0046】

前記高周波分周回路 46 は、基準周波数  $32768 \text{ Hz}$  を  $2048 \text{ Hz}$  まで分周し、その分周出力をレベルシフタ 50 を介して中低周波分周回路 52 へ出力する。 10

【0047】

前記中低周波分周回路 52 は、 $2048 \text{ Hz}$  まで分周された信号を、さらに  $1 \text{ Hz}$  まで分周し、その他の回路 54 へ入力する。

【0048】

前記その他の回路 54 は、 $1 \text{ Hz}$  の分周信号に同期してコイル 22 を通電駆動するドライバ回路を含んで構成され、この  $1 \text{ Hz}$  の分周信号に同期して時計駆動用ステップモータを駆動する。。

【0049】

本実施の形態の時計回路 30において、主電源 20 から供給される電圧 Vss により回路全体が駆動される電源電圧動作回路部 110 以外に、これにより低い一定電圧 Vreg で駆動される定電圧動作回路部 100 を設けたのは以下の理由による。 20

【0050】

すなわち、このような時計回路 30 では、長期間安定した動作を確保するために、その消費電力を低減することが必要となる。

【0051】

通常、回路の消費電力 P は、次式に示すように信号の周波数 f、回路の容量 C に比例し、さらに供給電源電圧 V の二乗に比例して増大する。

【0052】

【数 1】

$$P \propto fC V^2$$

30

【0053】

ここで、時計回路 30 に着目してみると、回路全体の消費電力 P を低減するためには、回路各部に供給する電源電圧 V を低い値、例えば Vreg に設定すればよい。しかし、単純にこのようにすると、定電圧発生回路 32 そのものを容量の大きなものとしなければならず、回路全体の高集積化、小型化という観点からみて好ましくない。

【0054】

次に、信号の周波数に着目してみると、時計回路 30 は、信号周波数が高い水晶発振回路 40、波形整形ゲート 44、高周波分周回路 46 と、それ以外の回路とに大別することができる。この信号の周波数は、前記数 1 からも明らかなように、回路の消費電力と比例関係がある。 40

【0055】

そこで、本実施の形態の定電圧発生回路 32 は、主電源 20 から供給される電源 Vss から、それより低い値の一定電圧 Vreg を生成し、これを高周波信号を扱う回路部 100、すなわち水晶発振回路 40、波形整形ゲート 44、高周波分周回路 46 へ供給している。このように、前記高周波信号を扱う回路 40、44、46 に対して供給する駆動電圧の値を下げてやることにより、定電圧発生回路 32 の負担をさほど増加させることなく、時計回路 30 全体の消費電力を効果的に低減することができる。

【0056】

50

なお、本実施の形態において、高周波分周回路 4 6 と中低周波分周回路 5 2 との間にレベルシフタ 5 0 を設けたのは、以下の理由による。

**【 0 0 5 7 】**

高周波分周回路 4 6 の出力波高値は、定電圧  $V_{reg}$  のレベルであり、主電源の電圧  $V_{ss}$  の波高値より小さい。このため、電源電圧  $V_{ss}$  で駆動されている中低周波分周回路 5 2 に、高周波分周回路 4 6 の定電圧  $V_{reg}$  レベルの出力をそのまま入力しても、この入力値が中低周波分周回路 5 2 の初段のロジックレベル電圧を越えないため、中低周波分周回路 5 2 が正常に動作しない。よって、中低周波分周回路 5 2 が正常に動作するように、レベルシフタ 5 0 を使い、高周波分周回路 4 6 の出力波高値を定電圧レベルから電源電圧レベルまで引き上げているのである。

10

**【 0 0 5 8 】**

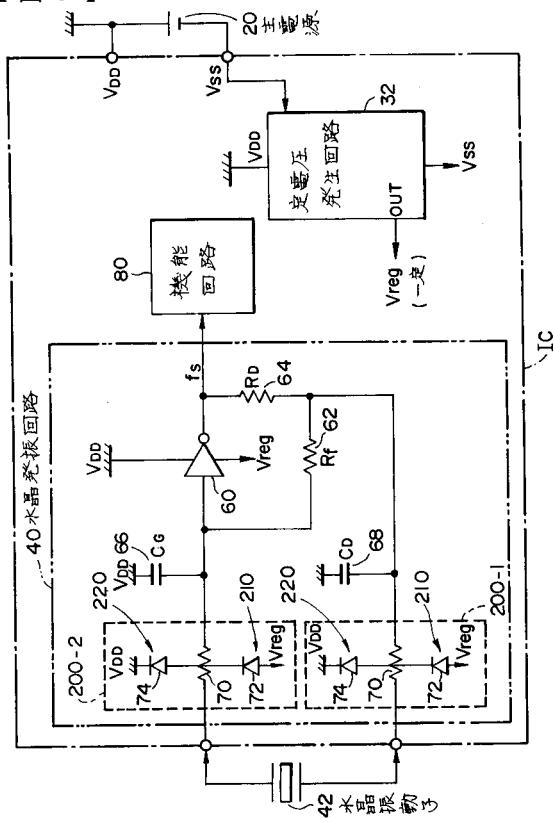

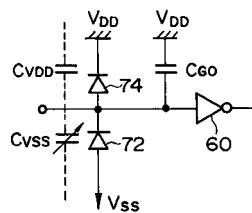

( 3 ) 水晶発振回路

図 3 には、本実施の形態の特徴である水晶発振回路 4 0 の具体的な回路構成が示されている。

**【 0 0 5 9 】**

この水晶発振回路 4 0 は、基本的には、インバータ 6 0 、フィードバック抵抗 6 2 、ドレン抵抗 6 4 、位相補償用コンデンサ 6 6 、6 8 を含んで構成され、発振周波数  $f_s$  の発振出力を、機能回路 8 0 へ向け出力する。この機能回路 8 0 は、波形整形ゲート 4 4 、高周波分周回路 4 6 、レベルシフタ 5 0 、中低周波分周回路 5 2 、その他の回路 5 4 を含んで構成されている。

20

**【 0 0 6 0 】**

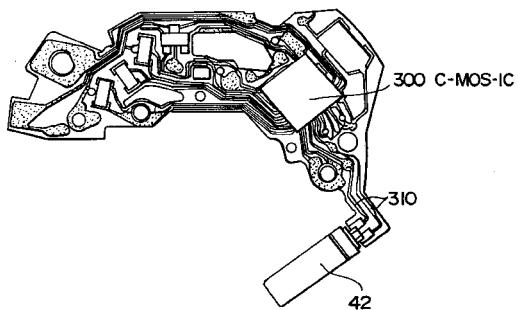

ところで、図 2 に示す時計回路 3 0 は、図 1 0 に示すように水晶振動子 4 2 を除いて基本的には半導体装置としての C - M O S - I C 3 0 0 として形成されており、発振回路主要部を構成する C - M O S - I C 3 0 0 と水晶振動子 4 2 は配線 3 1 0 を介して接続されている。

**【 0 0 6 1 】**

すなわち、水晶振動子 4 2 は、入出力端子を介して C - M O S - I C 3 0 0 の内部に構成された水晶発振回路 4 0 の主要回路部に接続されている。従って、この入出力端子から、サージ電圧が入力し内部回路を破壊する恐れがある。

**【 0 0 6 2 】**

30

このようなサージ電圧としては、例えば製品組付け時に治具から侵入するサージ電圧や、人間等のオペレータから侵入するサージ電圧などが考えられる。

**【 0 0 6 3 】**

このため、水晶発振回路 4 0 の内部には静電保護回路 2 0 0 - 1 、2 0 0 - 2 が設けられている。

**【 0 0 6 4 】**

これら各静電保護回路 2 0 0 - 1 、2 0 0 - 2 は、各入力端子に接続された信号路毎にそれぞれ設けられている。各静電保護回路 2 0 0 - 1 、2 0 0 - 2 は、同一の構成であるため、ここでは一方の静電保護回路 2 0 0 - 1 を例にとり説明する。

**【 0 0 6 5 】**

40

この静電保護回路 2 0 0 は、抵抗 7 0 と、発振回路の信号路に侵入するマイナス極性の静電圧を第 1 の半導体整流素子 7 2 を介して選択的に前記定電圧  $V_{reg}$  側へバイパスさせる第 1 の静電保護回路部 2 1 0 と、発振回路の信号路に侵入するプラス極性の静電圧を第 2 の半導体整流素子 7 4 を介して選択的にアース側へバイパスさせる第 2 の静電保護回路部 2 2 0 とを含んで構成されている。

**【 0 0 6 6 】**

前記抵抗 7 0 は、信号路に直列に接続され、サージ電圧から各整流素子 7 2 、7 4 を保護するものである。

**【 0 0 6 7 】**

前記第 1 、第 2 の半導体整流素子 7 2 、7 4 は、P N 接合型のダイオードを用いて構成さ

50

れてる。そして、第1の半導体整流素子72を構成するダイオードは、定電圧発生回路32の定電圧( $V_{reg}$ )出力端子側に逆方向接続されており、第二の半導体整流素子74を構成するダイオードは、アース側に順方向接続されている。

【0068】

これにより、外部から侵入したマイナス極性のサージ電圧は、定電圧端子 $V_{reg}$ 側へバイパスされ、プラス極性のサージ電圧はアース側へバイパスされることになり、半導体回路内部への侵入が防止される。

【0069】

本実施の形態の特徴は、前述したように第1の半導体整流素子72を、主電源20の電源電圧 $V_{ss}$ が変動してもその電圧の変動しない定電圧発生回路の $V_{reg}$ 側の端子へ接続したことにある。これにより、主電源20の電源電圧 $V_{ss}$ が変動してもこれら、各半導体整流素子72、74の寄生容量は変化せず、水晶発振回路40の発振周波数 $f_s$ は常に一定の値となる。10

【0070】

以下に、その詳細を説明する。

【0071】

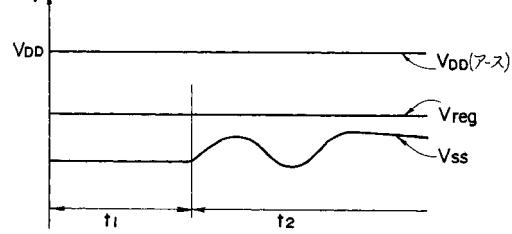

図4には、前記定電圧 $V_{reg}$ と、電源電圧 $V_{ss}$ の関係が示されている。主電源から供給される電源電圧 $V_{ss}$ (本実施の形態では負の値をとる)の絶対値は、常に定電圧発生回路32から出力される定電圧 $V_{reg}$ (本実施の形態では負の値をとる)の絶対値より大きな値をもつ。しかし、この電源電圧 $V_{ss}$ は、負荷の変動や、主電源20の充電状態等により図4に示すように変動することが多い。20

【0072】

これに対し、定電圧発生回路32から出力される定電圧 $V_{reg}$ は、この主電源の電圧 $V_{ss}$ が $V_{reg}$ の値を割り込まない限り、既に一定の電圧となる。

【0073】

本来、第1の半導体整流素子72は、容量の大きな主電源20側へ接続することが、高電圧サージ対策を行う上で好ましい。しかし、前述したように主電源20の電圧 $V_{ss}$ が変動すると、半導体で構成される第1、第2の半導体整流素子72、74の寄生容量の値が変動してしまう。

【0074】

I C内部のP N接合で作られている半導体整流素子72、74、特にダイオードのP、N接合部分の寄生静電容量Cは、通常次式で表される。30

【0075】

【数2】

$$C = A \sqrt{\frac{N_D}{V_A + V_B}}$$

但し、

A; 定数

$V_A$ ; 印加電圧

$N_D$ ; 不純物濃度

$V_B$ ; P-N接触電位差

【0076】

同式から、電源電圧 $V_A = V_{ss}$ が変化すると、この寄生容量Cが変化することが理解される。

【0077】

そして、この寄生容量Cが変化すると、結果的に発振回路40の発振周波数 $f_s$ も変動してしまう。以下にこれを説明する。

【0078】

(3 - 1) 発振周波数の変動対策

10

20

30

40

50

図5(A)には、発振回路40の等価回路が示されている。

【0079】

図5(B)には、水晶振動子42、図5(C)にはその等価回路が示されている。

【0080】

この図5(C)に示す等価回路を用いると、図5(A)に示す発振回路40は、図5(D)に示す回路として表される。

【0081】

そして、この図5(D)の等価回路で表されるLC発振回路40の発振周波数fsは、次式で表される。

【0082】

【数3】

$$f_s = \frac{1}{2\pi\sqrt{L' C_G'}} \cdot f_1(C_D')$$

【0083】

この式から、発振回路の内部容量CG'が変わると、発振周波数fsが変動することがわかる。すなわち、前記数3には、第1、第2の半導体整流素子72、74の寄生容量値CVD、CVSSが含まれるため、これらの値が変化すると、発振周波数fsが変動してしまう。

【0084】

これに対し、本実施の形態では、前記第1の半導体整流素子72を、電圧が変動しないVregに接続している。このため、電源電圧Vssの変動の影響を受けることなく、水晶発振回路40は常に一定周波数fsの発振出力を生成することが可能となる。

【0085】

さらに、このような構成とすることにより、前記第1及び第2の半導体整流素子72、74の寄生容量の値は常に一定の値となる。従って、この寄生容量の値を積極的に、位相補償用コンデンサ66、68として活用することができる。これにより、図3に示す位相補償用コンデンサ66、88の容量値を小さなものとすることができる、または場合によっては、これらのコンデンサ66、88を、省略することもできる。

【0086】

このようにすることにより、水晶発振回路40の部品点数を低減し、その集積度を高めることができるとなる。

【0087】

また、本実施の形態によれば、第1および第2の半導体整流素子72、74の寄生容量を、前記位相補償用コンデンサ66、68の一部または全部として活用することにより、半導体整流素子72、74自体の寄生容量値を大きなものとすることができます。

【0088】

すなわち、前記位相補償用コンデンサ66、68と、ダイオード72、74とを全く別に設ける場合には、回路40全体の容量を少なくし、その消費電力を低減するという観点から、ダイオード72、74は、寄生容量が小さなものを用いる必要がある。この場合には、この寄生容量値に応じて、静電破壊耐性も低下する。

【0089】

これに対し本実施の形態では、半導体整流素子72、74の寄生容量を前記位相補償用のコンデンサとして積極的に活用することにより、半導体素子として寄生容量値の大きなものを用いることができる。この結果、素子72、74自体の静電破壊耐性を高め、回路全体の静電保護能力を高めることができるようになる。

【0090】

(4)他の実施の形態

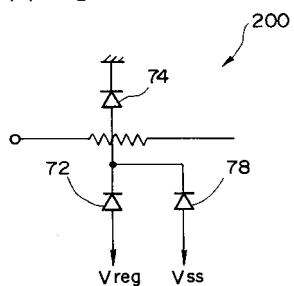

図6には、本発明の他の一例が示されている。この実施の形態の静電保護回路では、第3の半導体整流素子78を用い、これを主電源Vssに逆方向接続することを特徴とする。こ

10

20

30

40

50

れにより、容量の大きな主電源 20 側へサージ電圧のバイパス回路を構成することができるため、静電保護回路 200 の静電破壊耐性をさらに高めることができる。

【0091】

なお、この場合には電源電圧  $V_{SS}$  の変動の影響を受けて、第3の半導体整流素子 78 の寄生容量値が変動する。このため、第3の半導体整流素子 78 の寄生容量値に比べ、第1の半導体整流素子 72 の寄生容量値を一桁から二桁程度大きく設定することで、第3の半導体整流素子 78 の寄生容量値の変動量が、第1の半導体整流素子 72 および第3の半導体整流素子 78 の合成寄生容量値の変動量に対して数パーセント程度の影響に収まるようになることが望ましい。これにより、回路全体の静電容量の値を常に安定したものとし、より安定した発振出力を得ることができる。

10

【0092】

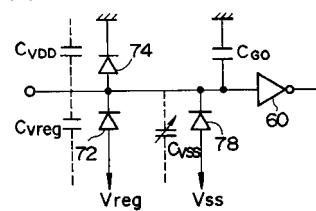

(5) 従来技術との対比

図7には、半導体整流素子 72 を主電源  $V_{SS}$  側へ接続した従来の静電保護回路の一例が示されている。図7に示す従来例では、電源電圧  $V_{SS}$  の変動する主電源に接続された第1の半導体整流素子 72 は、寄生容量値  $C_{VSS}$  が変動する素子として回路的に表現される。

【0093】

ここで、従来の静電保護回路を用いた水晶発振回路の一例について、周波数偏差の検討を以下に述べるように行った。

【0094】

図7の従来回路では、発振回路 40 のゲート 60 を構成するトランジスタのゲート端子およびドレイン端子から見た、静電保護回路 200 を含む IC (半導体装置) の内部回路の合成容量である  $C_G$ 、 $C_D$  の実測データは、次式で示す値となった。ここにおいて、抵抗 62 の抵抗値  $R_f$  は極めて大きいため、次式に示す  $C_G$  の値からは  $C_D$  の値は省略し、 $C_D$  の値からは  $C_{G0}$  の値は省略する。

20

【0095】

【数4】

$$C_G = C_{G0} + C_{VDD} + C_{VSS} + C_{GP} = 10.8 \text{ (PF)}$$

$$C_D = C_{D0} + C_{VDD} + C_{VSS} + C_{DP} = 6.1 \text{ (PF)}$$

30

【0096】

この従来回路において、電源電圧  $V_{SS}$  が 1.1 ボルトから 2.4 ボルトへ変動したとき、第1の半導体整流素子 72 の寄生容量値  $C_{VSS}$  の変動量は  $C_{VSS} = 0.07 \text{ (PF)}$  であった。

【0097】

次に、この寄生容量値の変動量が、水晶発振回路 40 の静電容量全体に占める割合の検討を行う。

【0098】

まず、数4に示す  $C_G$  に対する静電保護回路 200 - 2 の寄生容量値の変動量の比を求めると、その値は次式で示すようになる。

40

【0099】

【数5】

$$\frac{\Delta C_{VSS}}{C_{G0} + C_{VDD} + C_{VSS} + C_{GP}} \left( = \frac{7}{1080} \right)$$

【0100】

また、数4に示す  $C_D$  に対する静電保護回路 200 - 1 の寄生容量値の変動量の比を求めると、その値は次式で示すようになる。

【0101】

50

【数6】

$$\frac{\Delta C_{VSS}}{C_{DO} + C_{VDD} + C_{VSS} + C_{DP}} \left( = \frac{7}{610} \right)$$

【0102】

ここで、 $C_{GP}$ 、 $C_{DP}$ は、発振回路40の配線容量値をそれぞれ表すものである。

【0103】

このような寄生容量値の変動量から、発振回路の周波数偏差の値を求めるとき、その値は( $d f / d v$ ) = 3 (PPM)となる。これを月差に換算すると、8秒程度となる。例えば時計に許容される月差が15秒程度の場合には、この15秒のうち8秒が寄生容量値の変動によって引き起こされるということは到底許容されるものではない。10

【0104】

これに対し、図3に示すよう、第1の半導体整流素子72を、電圧が変動しない電源 $V_{reg}$ へ接続することにより、このような寄生容量値の変動分はほとんど無視できるようになり、水晶発振回路40自体の発振周波数の周波数偏差も、従来回路に比べ無視できる程度に改善することができる。

【0105】

また、同様な検証を、図6に示す第2実施の形態の静電保護回路を用いた水晶発振回路40について行った。図8は、この静電保護回路の等価回路図である。この場合には、第3の半導体整流素子78が、寄生容量値 $C_{VSS}$ が変化する素子となる。20

【0106】

図8に示す回路においても、第3の半導体整流素子78の寄生容量値は、第1の半導体整流素子72の寄生容量値に比べ十分小さく成形されているため、その寄生容量値 $C_{VSS}$ が変動した場合でも、回路全体の周波数偏差を図7に示す静電保護回路を用いた場合に比べ大幅に少なくできる。

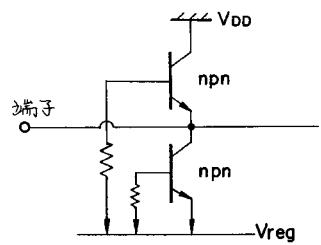

【0107】

なお、前記各実施の形態では、半導体整流素子として、ダイオードを用いるものを例にとり説明したが、これ以外にも必要に応じ各種の半導体整流素子を用いて保護回路を形成することができる。例えば図9に示すように、バイポーラトランジスタを半導体整流素子として用いて静電保護回路を形成してもよい。30

【0108】

また、前記実施の形態では、本発明を携帯用の腕時計に適用する場合を例にとり説明したが、本発明は、これ以外にも、例えば各種電子機器、例えば携帯電話、携帯用のコンピュータ端末等の電子機器に適用してもよい。

【図面の簡単な説明】

【図1】本発明が適用された腕時計用の電子回路の一例を示すブロック図である。

【図2】図1に示す電子回路の時計回路部分のブロック図である。

【図3】本実施の形態の水晶発振回路の具体的な構成を示す説明図である。

【図4】本実施の形態の回路で用いられる2種類の電源の電圧変動の様子を示す説明図である。40

【図5】図3に示す水晶発振回路の等価回路図であり、同図(A)は図3の水晶発振回路の等価回路図、同図(B)は水晶振動子の説明図、同図(C)は水晶振動子の等価回路図、同図(D)は水晶振動子の等価回路を考慮して作成された同図(A)の等価回路図である。

【図6】他の静電保護回路の説明図である。

【図7】従来用いられた静電保護回路の説明図である。

【図8】図6に示す静電保護回路の等価回路図である。

【図9】他の種類の半導体素子を用いて構成された静電保護回路の説明図である。

【図10】基板上における水晶振動子と発振回路主要部を構成するC-MOS-ICとの50

配置の説明図である。

【符号の説明】

- 20 主電源

- 32 定電圧発生回路

- 40 水晶発振回路

- 42 水晶振動子

- 72、74 半導体整流素子

- 200 静電保護回路

- 210 第1の静電保護回路部

- 220 第2の静電保護回路部

10

【図1】

【図2】

【図3】

【図4】

【図5】

$C_g'$ 、 $C_{go}$ 、 $C_o$ 、 $C_p$ 、 $C_{vdd}$

$C_d'$ 、 $C_{do}$ 、 $C_o$ 、 $C_p$ 、 $C_{vss}$

【図6】

【図7】

$C_{gp}$ 、 $C_{dp}$ ：配線容量

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 門脇 忠雄

長野県諏訪市大和3丁目3番5号 セイコーホームズ株式会社内

(72)発明者 牧内 佳樹

長野県諏訪市大和3丁目3番5号 セイコーホームズ株式会社内

審査官 桑江 晃

(56)参考文献 特開昭50-098263(JP,A)

特開平05-343919(JP,A)

特開平09-205325(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03B 5/00 - 5/42

G04G 3/00