República Federativa do Brasil

Ministério do Desenvolvimento, Indústria,

Comércio e Serviços

Instituto Nacional da Propriedade Industrial

**(11) BR 112017027873-1 B1**

**(22) Data do Depósito:** 06/06/2016

**(45) Data de Concessão:** 12/12/2023

**(54) Título:** TOPOLOGIAS DE ACIONADOR DE CAMADA FÍSICA DE BAIXA POTÊNCIA

**(51) Int.Cl.:** H04L 25/02; G06F 13/40; H04L 25/493.

**(30) Prioridade Unionista:** 03/06/2016 US 15/172,913; 22/06/2015 US 62/183,050.

**(73) Titular(es):** QUALCOMM INCORPORATED.

**(72) Inventor(es):** SHIH-WEI CHOU; CHULKYU LEE; DHAVAL SEJPAL.

**(86) Pedido PCT:** PCT US2016036073 de 06/06/2016

**(87) Publicação PCT:** WO 2016/209601 de 29/12/2016

**(85) Data do Início da Fase Nacional:** 22/12/2017

**(57) Resumo:** TOPOLOGIAS DE ACIONADOR DE CAMADA FÍSICA DE BAIXA POTÊNCIA. Trata-se de sistema, métodos e aparelho que facilitam a transmissão de dados, particularmente entre dois dispositivos em equipamento eletrônico. As linhas de transmissão são seletivamente terminadas em um transmissor codificado em polaridade de N fases quando as linhas de transmissão seriam, de outro modo, desacionadas. Os dados são mapeados para uma sequência de símbolos a ser transmitida em uma pluralidade de fios. A sequência de símbolos é codificada em três sinais. Um primeiro terminal dentre uma pluralidade de terminais pode ser acionado de maneira que transistores sejam ativados para acoplar o primeiro terminal ao primeiro e segundo níveis de tensão. O primeiro terminal pode adicionalmente ser acionado de maneira que um transistor dedicado seja ativado para acoplar o primeiro terminal a um nível de tensão intermediário. O transistor dedicado é ativado com base em um nível de tensão para acionar um segundo terminal dos três terminais e em um nível de tensão para acionar um terceiro terminal dos três terminais.

“TOPOLOGIAS DE ACIONADOR DE CAMADA FÍSICA DE BAIXA POTÊNCIA”

REFERÊNCIA CRUZADA A PEDIDOS REFERENTES

[0001] Este pedido reivindica a prioridade e o benefício do Pedido Provisório Número de Série U.S. 62/183.050, intitulado "LOW POWER PHYSICAL LAYER DRIVER TOPOLOGIES" depositado em 22 de junho de 2015, e do Pedido Não Provisório nº U.S. 15/172.913, intitulado "LOW POWER PHYSICAL LAYER DRIVER TOPOLOGIES" depositado em 3 de junho de 2016, cuja totalidade do conteúdo é incorporada no presente documento a título de referência.

ANTECEDENTES

CAMPO

[0002] A presente revelação refere-se geralmente a comunicações de dados de alta velocidade, e mais particularmente, a interfaces de linha para acionar fios de sinal em um sistema de multifase.

ANTECEDENTES

[0003] As interfaces de alta velocidade são frequentemente usadas entre circuitos e componentes de dispositivos móveis e outro aparelho complexo. Por exemplo, certos dispositivos podem incluir dispositivos de processamento, comunicações, armazenamento e/ou exibição que interagem uns com os outros através de enlaces de comunicações. Alguns desses dispositivos, inclusive memória de acesso aleatório dinâmico síncrono (SDRAM), podem ter capacidade para fornecer ou consumir dados e informações de controle em taxas de clock de processador. Outros dispositivos, tais como controladores de exibição, podem exigir quantidades variáveis de dados em taxas de

atualização de vídeo relativamente baixas.

[0004] As interfaces de alta velocidade são limitadas frequentemente por desvio de clock e são sujeitas a interferência. Sinais de alta frequência são frequentemente transmitidos com o uso de interfaces diferenciais para fornecer rejeição de modo comum para sinais críticos. Em dispositivos tais como dispositivos de memória, que transmitem e recebem grandes quantidades de dados através de barramentos amplos de dados e controle, as interfaces podem ser custosas e podem consumir potência significativa e espaço útil em uma placa de circuito.

#### SUMÁRIO

[0005] As modalidades reveladas no presente documento fornecem sistemas, métodos e aparelho para se comunicar entre dois dispositivos que podem ser colocalizados em um aparelho eletrônico e acoplados de modo comunicativo através de um ou mais enlaces de dados.

[0006] Em um aspecto da revelação, um método para transferência de dados inclui mapear dados para uma sequência de símbolos a ser transmitida em uma pluralidade de fios por meio de uma pluralidade de terminais, codificar a sequência de símbolos em três sinais, em que cada um dos três sinais está em uma das três fases para cada símbolo a ser transmitido, e em que os três sinais estão em fases diferentes entre si durante a transmissão de cada símbolo, e obter um sinal a ser transmitido por meio de um primeiro terminal dentre a pluralidade de terminais, em que o sinal é um dos três sinais. O método adicionalmente inclui acionar o primeiro terminal emitindo-se um primeiro nível de tensão de um primeiro acionador quando o sinal está em

uma primeira fase, acionar o primeiro terminal emitindo-se um segundo nível de tensão do primeiro acionador quando o sinal está em uma segunda fase, e acionar o primeiro terminal emitindo-se um terceiro nível de tensão de um segundo acionador quando o primeiro sinal está em uma terceira fase. O terceiro nível de tensão é emitido com base em um quarto nível de tensão para acionar um segundo terminal dentre a pluralidade de terminais, e com base em um quinto nível de tensão para acionar um terceiro terminal dentre a pluralidade de terminais.

[0007] Em um aspecto da revelação, o primeiro acionador inclui um primeiro transistor e um segundo transistor. Emitir o primeiro nível de tensão do primeiro acionador inclui ligar o primeiro transistor e desligar o segundo transistor para emitir o primeiro nível de tensão quando o sinal está na primeira fase. O primeiro terminal é acionado em direção ao primeiro nível de tensão quando o primeiro nível de tensão é emitido. Emitir o segundo nível de tensão do primeiro acionador inclui ligar o segundo transistor e desligar o primeiro transistor para emitir o segundo nível de tensão quando o sinal está na segunda fase. O primeiro terminal é acionado em direção ao segundo nível de tensão quando o segundo nível de tensão é emitido. O primeiro transistor e o segundo transistor são desligados quando o sinal está na terceira fase.

[0008] O método pode adicionalmente incluir acionar o segundo terminal dentre a pluralidade de terminais emitindo-se o quarto nível de tensão de um terceiro acionador e acionar o terceiro terminal dentre a pluralidade de terminais emitindo-se o quinto nível de

tensão de um quarto acionador. Em um aspecto da revelação, o segundo acionador inclui um terceiro transistor e um quarto transistor. Emitir o terceiro nível de tensão do segundo acionador quando o primeiro sinal está na terceira fase inclui receber a emissão de quarto nível de tensão do terceiro acionador e a emissão de quinto nível de tensão do quarto acionador, e ligar o terceiro transistor e o quarto transistor do segundo acionador de acordo com o quarto nível de tensão recebido e o quinto nível de tensão recebido para emitir o terceiro nível de tensão. O primeiro terminal é acionado em direção ao terceiro nível de tensão quando o terceiro nível de tensão é emitido.

[0009] Em um aspecto, o terceiro nível de tensão está em uma faixa de tensão limitada pelo primeiro nível de tensão e pelo segundo nível de tensão. Ademais, o terceiro transistor e o quarto transistor são desligados quando o primeiro sinal está na primeira fase ou na segunda fase.

[0010] Em um aspecto da revelação, um aparelho para transferência de dados inclui um meio para mapear dados para uma sequência de símbolos a ser transmitida em uma pluralidade de fios por meio de uma pluralidade de terminais, meio para codificar a sequência de símbolos em três sinais, em que cada um dos três sinais está em uma das três fases para cada símbolo a ser transmitido, e em que os três sinais estão em fases diferentes entre si durante a transmissão de cada símbolo, meio para obter um sinal a ser transmitido por meio de um primeiro terminal dentre a pluralidade de terminais, em que o sinal é um dos três sinais, meio para acionar o primeiro terminal emitindo-se um primeiro nível de tensão de um primeiro acionador quando

o sinal está em uma primeira fase, meio para acionar o primeiro terminal emitindo-se um segundo nível de tensão do primeiro acionador quando o sinal está em uma segunda fase, meio para acionar o primeiro terminal emitindo-se um terceiro nível de tensão de um segundo acionador quando o sinal está em uma terceira fase, em que o terceiro nível de tensão é emitido com base em um quarto nível de tensão para acionar um segundo terminal dentre a pluralidade de terminais, e com base em um quinto nível de tensão para acionar um terceiro terminal dentre a pluralidade de terminais, meio para acionar o segundo terminal emitindo-se o quarto nível de tensão de um terceiro acionador e um meio para acionar o terceiro terminal emitindo-se o quinto nível de tensão de um quarto acionador.

[0011] Em um aspecto da revelação, um transmissor inclui uma pluralidade de terminais acionados pelos acionadores de linha e um circuito de processamento configurado para mapear dados para uma sequência de símbolos a ser transmitida em uma pluralidade de fios por meio da pluralidade de terminais, codificar a sequência de símbolos em três sinais, em que cada um dos três sinais está em uma das três fases para cada símbolo a ser transmitido, e em que os três sinais estão em fases diferentes entre si durante a transmissão de cada símbolo, e obter um sinal a ser transmitido por meio de um primeiro terminal dentre a pluralidade de terminais, em que o sinal é um dos três sinais. O transmissor adicionalmente inclui um primeiro acionador de linha configurado para acionar o primeiro terminal emitindo-se um primeiro nível de tensão quando o sinal está em uma primeira fase, e acionar o

primeiro terminal emitindo-se um segundo nível de tensão quando o sinal está em uma segunda fase. O transmissor também inclui um segundo acionador de linha configurado para acionar o primeiro terminal emitindo-se um terceiro nível de tensão quando o sinal está em uma terceira fase, em que o terceiro nível de tensão é emitido com base em um quarto nível de tensão para acionar um segundo terminal dentre a pluralidade de terminais, e com base em um quinto nível de tensão para acionar um terceiro terminal dentre a pluralidade de terminais. O transmissor adicionalmente inclui um terceiro acionador de linha configurado para acionar o segundo terminal emitindo-se o quarto nível de tensão e um quarto acionador de linha configurado para acionar o terceiro terminal emitindo-se o quinto nível de tensão.

[0012] Em um aspecto da revelação, um meio de armazenamento legível por processador que tem uma ou mais instruções que, quando executada por pelo menos um circuito de processamento, faz com que o pelo menos um circuito de processamento mapeie dados para uma sequência de símbolos a ser transmitida em uma pluralidade de fios por meio da pluralidade de terminais, codificar a sequência de símbolos em três sinais, em que cada um dos três sinais está em uma das três fases para cada símbolo a ser transmitido, e em que os três sinais estão em fases diferentes entre si durante a transmissão de cada símbolo, obter um sinal a ser transmitido por meio de um primeiro terminal dentre a pluralidade de terminais, em que o sinal é um dos três sinais, acionar o primeiro terminal emitindo-se um primeiro nível de tensão quando o sinal está em uma primeira fase,

acionar o primeiro terminal emitindo-se um segundo nível de tensão quando o sinal está em uma segunda fase, acionar o primeiro terminal emitindo-se um terceiro nível de tensão quando o sinal está em uma terceira fase, em que o terceiro nível de tensão é emitido com base em um quarto nível de tensão para acionar um segundo terminal dentre a pluralidade de terminais, e com base em um quinto nível de tensão para acionar um terceiro terminal dentre a pluralidade de terminais, acionar o segundo terminal emitindo-se o quarto nível de tensão e acionar o terceiro terminal emitindo-se o quinto nível de tensão.

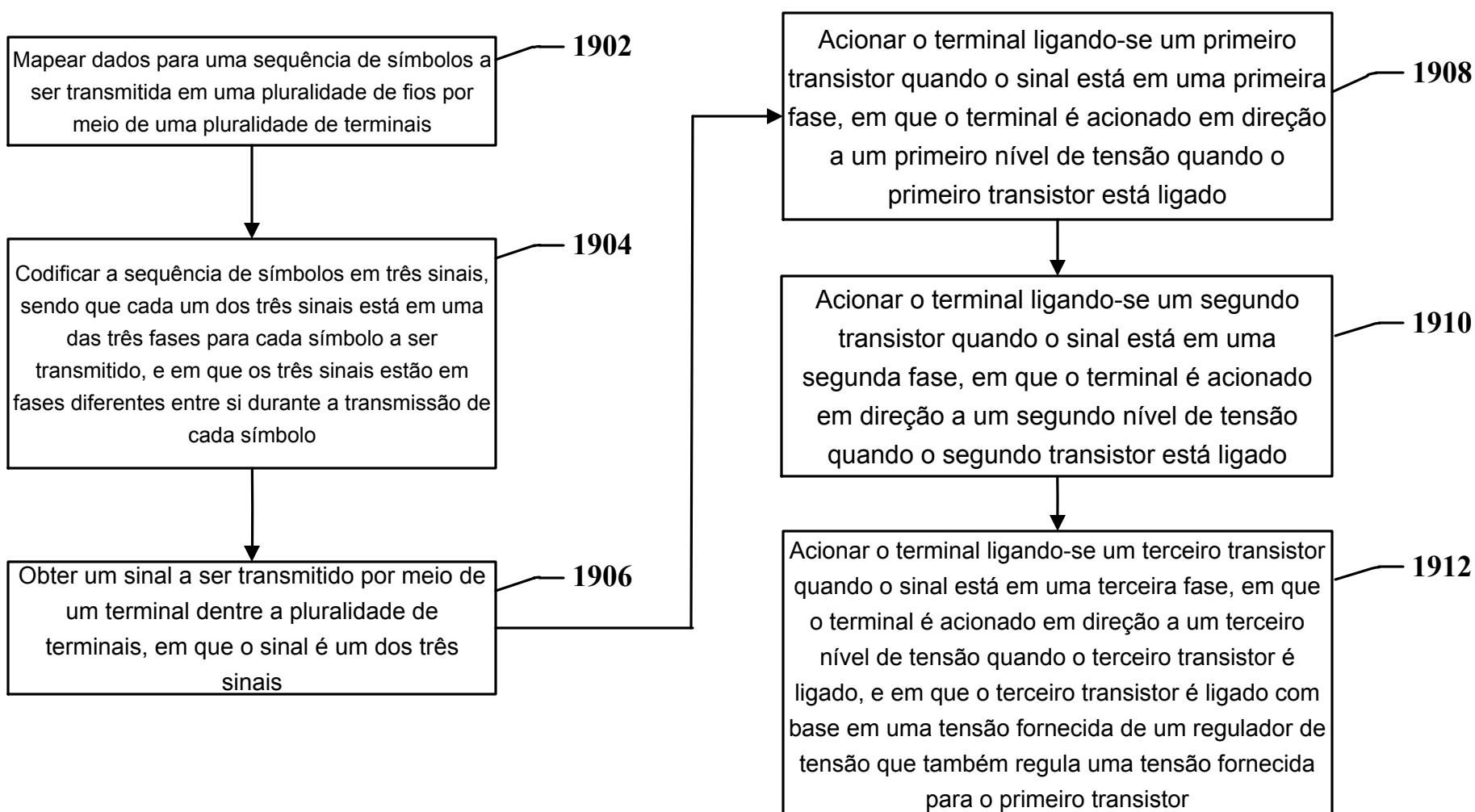

[0013] Em um aspecto da revelação, um método de transferência de dados inclui mapear dados para uma sequência de símbolos a ser transmitida em uma pluralidade de fios por meio de uma pluralidade de terminais, codificar a sequência de símbolos em três sinais, em que cada um dos três sinais está em uma das três fases para cada símbolo a ser transmitido, e em que os três sinais estão em fases diferentes entre si durante a transmissão de cada símbolo, e obter um sinal a ser transmitido por meio de um terminal dentre a pluralidade de terminais, em que o sinal é um dos três sinais. O método adicionalmente inclui acionar o terminal ligando-se um primeiro transistor quando o sinal está em uma primeira fase, em que o terminal é acionado em direção a um primeiro nível de tensão quando o primeiro transistor é ligado, acionar o terminal ligando-se um segundo transistor quando o sinal está em uma segunda fase, em que o terminal é acionado em direção a um segundo nível de tensão quando o segundo transistor é ligado, e acionar o terminal ligando-se um terceiro transistor quando o sinal

está em uma terceira fase. O terminal é acionado em direção a um terceiro nível de tensão quando o terceiro transistor é ligado. O terceiro nível de tensão está em uma faixa de tensão limitada pelo primeiro nível de tensão e pelo segundo nível de tensão. Ademais, o terceiro transistor é ligado com base em uma tensão fornecida de um regulador de tensão que também regula uma tensão fornecida para o primeiro transistor.

[0014] Em um aspecto, acionar o terminal quando o sinal está na primeira fase inclui desligar o segundo transistor e o terceiro transistor. Em outro aspecto, acionar o terminal quando o sinal está na segunda fase inclui desligar o primeiro transistor e o terceiro transistor. Em um aspecto adicional, acionar o terminal quando o sinal está na terceira fase inclui desligar o primeiro transistor e o segundo transistor.

[0015] Em um aspecto da revelação, um aparelho para transferência de dados inclui um meio para mapear dados para uma sequência de símbolos a ser transmitida em uma pluralidade de fios por meio de uma pluralidade de terminais, meio para codificar a sequência de símbolos em três sinais, em que cada um dos três sinais está em uma das três fases para cada símbolo a ser transmitido, e em que os três sinais estão em fases diferentes entre si durante a transmissão de cada símbolo, meio para obter um sinal a ser transmitido por meio de um terminal dentre a pluralidade de terminais, em que o sinal é um dos três sinais, meio para acionar o terminal ligando-se um primeiro transistor quando o sinal está em uma primeira fase, em que o terminal é acionado em direção a um primeiro nível de tensão quando o

primeiro transistor é ligado, meio para acionar o terminal ligando-se um segundo transistor quando o sinal está em uma segunda fase, em que o terminal é acionado em direção a um segundo nível de tensão quando o segundo transistor é ligado e um meio para acionar o terminal ligando-se um terceiro transistor quando o sinal está em uma terceira fase. O terminal é acionado em direção a um terceiro nível de tensão quando o terceiro transistor é ligado. O terceiro nível de tensão está em uma faixa de tensão limitada pelo primeiro nível de tensão e pelo segundo nível de tensão. Ademais, o terceiro transistor é ligado com base em uma tensão fornecida de um regulador de tensão que também regula uma tensão fornecida para o primeiro transistor.

[0016] Em um aspecto da revelação, um transmissor inclui uma pluralidade de terminais acionados pelos acionadores de linha, e um circuito de processamento configurado para mapear dados para uma sequência de símbolos a ser transmitida em uma pluralidade de fios por meio da pluralidade de terminais, codificar a sequência de símbolos em três sinais, em que cada um dos três sinais está em uma das três fases para cada símbolo a ser transmitido, e em que os três sinais estão em fases diferentes entre si durante a transmissão de cada símbolo, e obter um sinal a ser transmitido por meio de um terminal dentre a pluralidade de terminais, em que o sinal é um dos três sinais. O transmissor adicionalmente inclui um acionador de linha configurado para acionar o terminal ligando-se um primeiro transistor quando o sinal está em uma primeira fase, em que o terminal é acionado em direção a um primeiro nível de tensão quando o primeiro transistor

é ligado, acionar o terminal ligando-se um segundo transistor quando o sinal está em uma segunda fase, em que o terminal é acionado em direção a um segundo nível de tensão quando o segundo transistor é ligado, e acionar o terminal ligando-se um terceiro transistor quando o sinal está em uma terceira fase, em que o terminal é acionado em direção a um terceiro nível de tensão quando o terceiro transistor é ligado, e em que o terceiro transistor é ligado com base em uma tensão fornecida de um regulador de tensão que também regula uma tensão fornecida para o primeiro transistor.

[0017] Em um aspecto da revelação, um meio de armazenamento legível por processador que tem uma ou mais instruções que, quando executada por pelo menos um circuito de processamento, faz com que o pelo menos um circuito de processamento mapeie dados para uma sequência de símbolos a ser transmitida em uma pluralidade de fios por meio da pluralidade de terminais, codificar a sequência de símbolos em três sinais, em que cada um dos três sinais está em uma das três fases para cada símbolo a ser transmitido, e em que os três sinais estão em fases diferentes entre si durante a transmissão de cada símbolo, obter um sinal a ser transmitido por meio de um terminal dentre a pluralidade de terminais, em que o sinal é um dos três sinais, acionar o terminal ligando-se um primeiro transistor quando o sinal está em uma primeira fase, em que o terminal é acionado em direção a um primeiro nível de tensão quando o primeiro transistor é ligado, acionar o terminal ligando-se um segundo transistor quando o sinal está em uma segunda fase, em que o terminal é acionado em direção a um segundo nível

de tensão quando o segundo transistor é ligado, e acionar o terminal ligando-se um terceiro transistor quando o sinal está em uma terceira fase, em que o terminal é acionado em direção a um terceiro nível de tensão quando o terceiro transistor é ligado, e em que o terceiro transistor é ligado com base em uma tensão fornecida de um regulador de tensão que também regula uma tensão fornecida para o primeiro transistor.

#### BREVE DESCRIÇÃO DOS DESENHOS

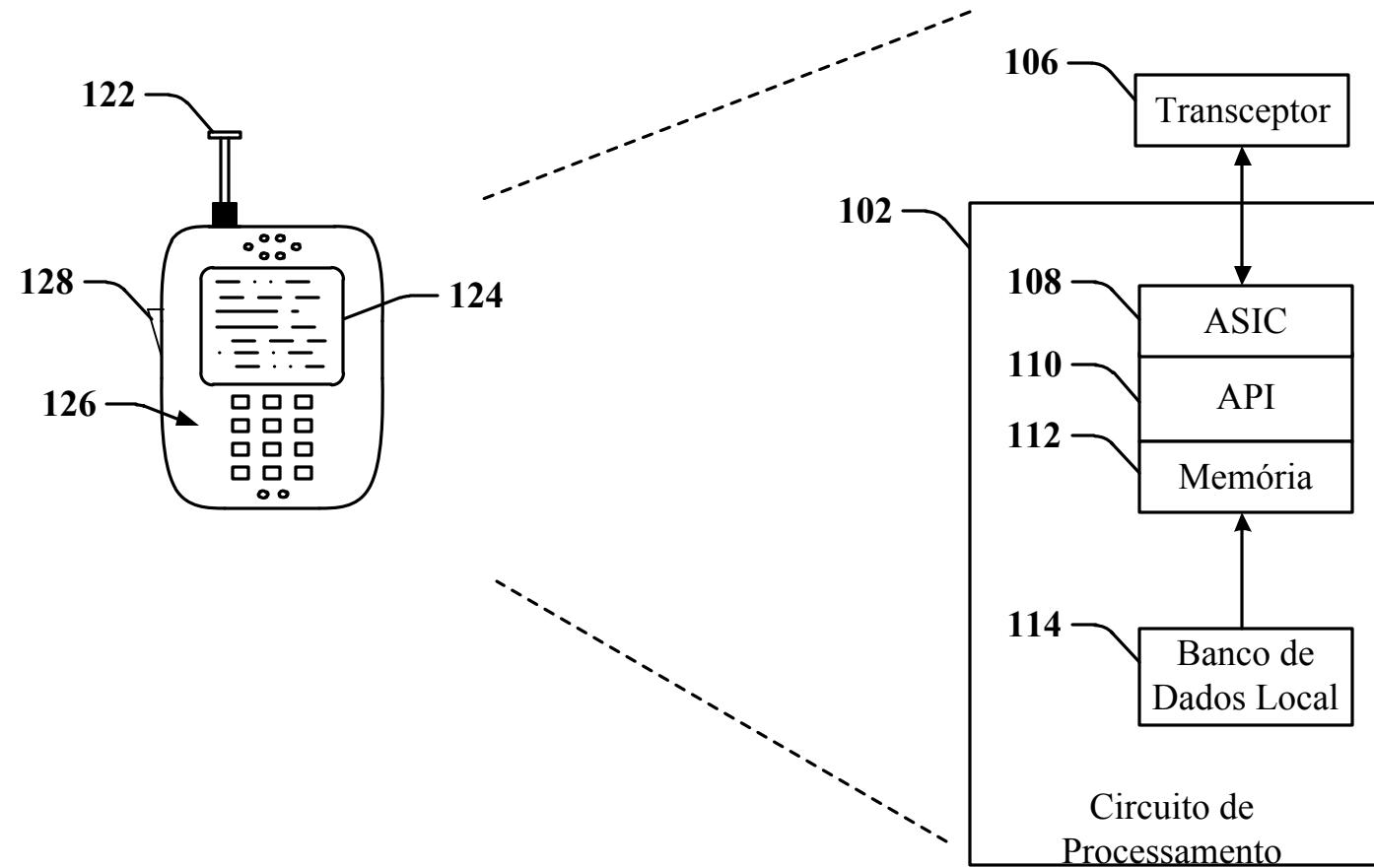

[0018] A Figura 1 representa um aparelho que emprega um enlace de dados codificado em polaridade de N fases entre dispositivos no aparelho.

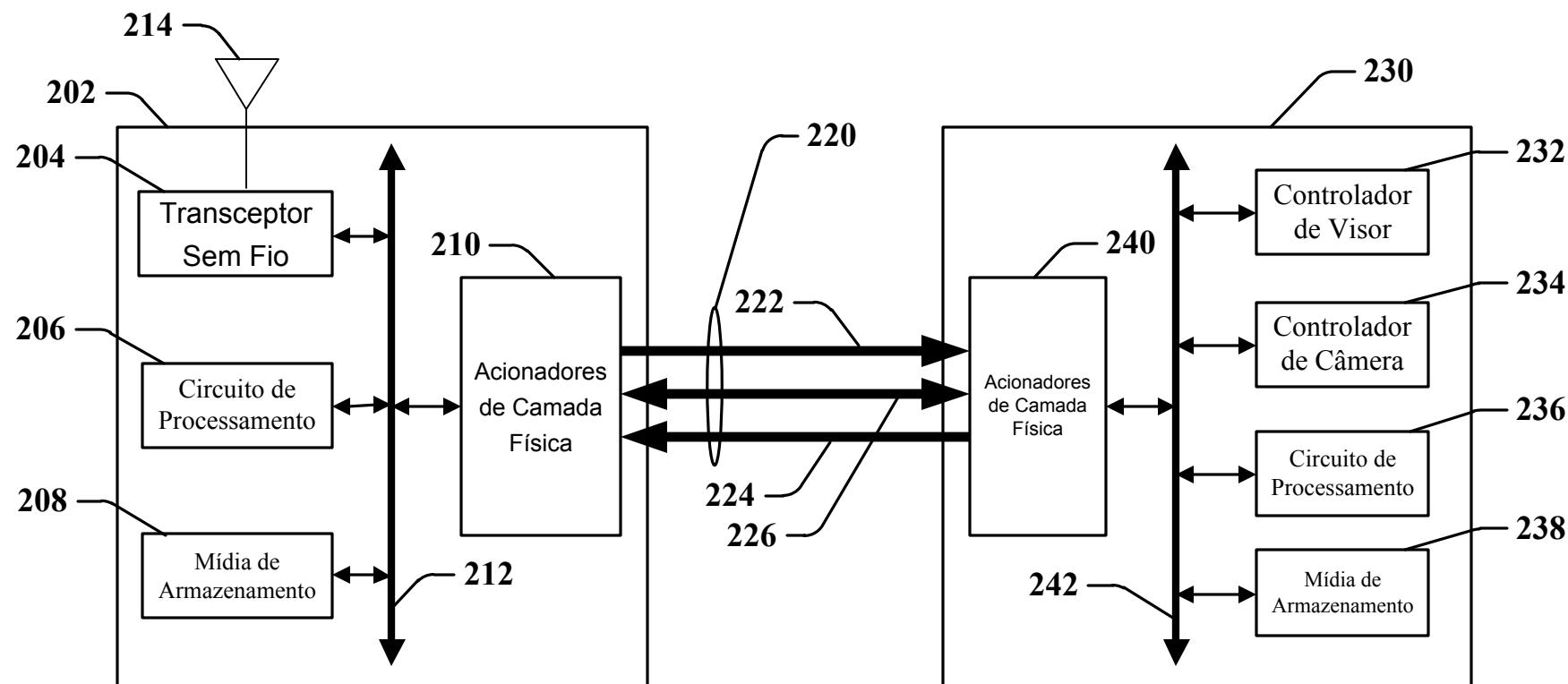

[0019] A Figura 2 ilustra uma arquitetura de sistema para um aparelho que emprega um enlace de dados codificado em polaridade de N fases.

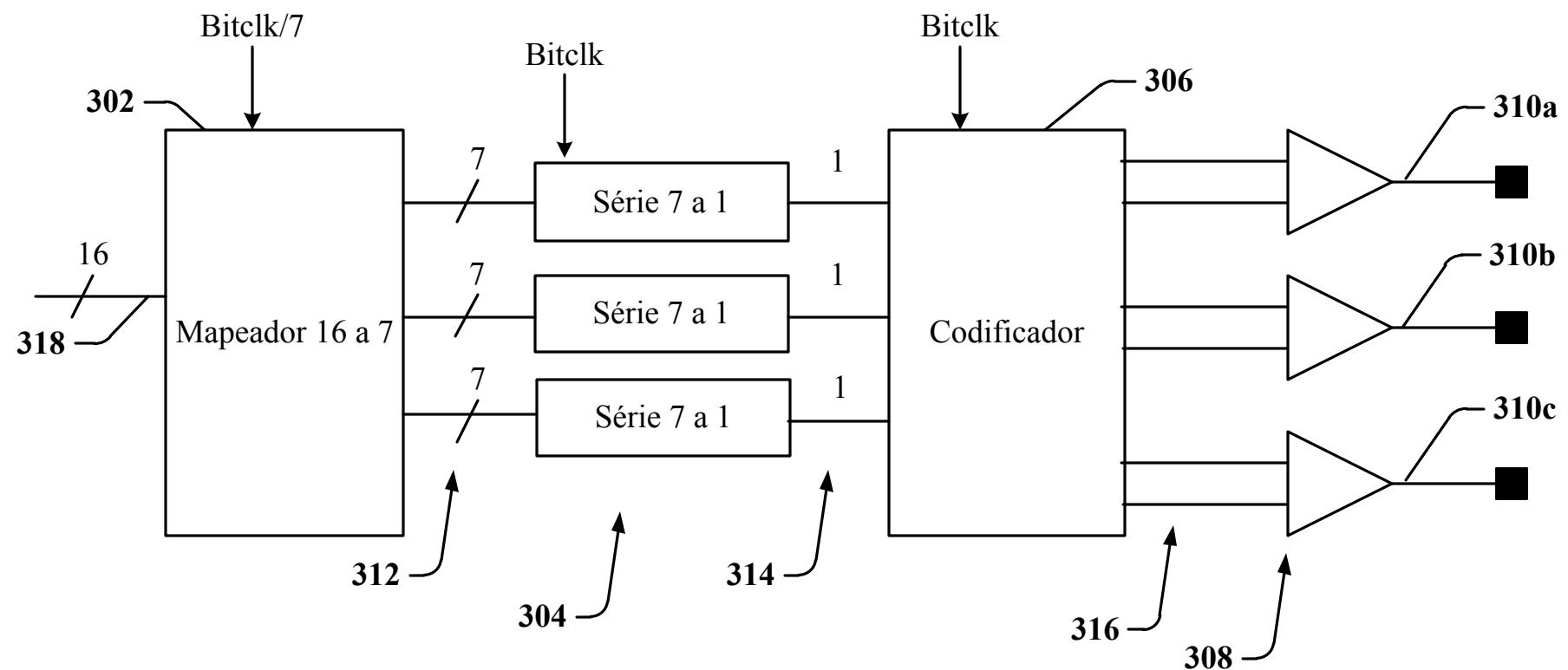

[0020] A Figura 3 ilustra um exemplo de um codificador de dados de polaridade de N fases.

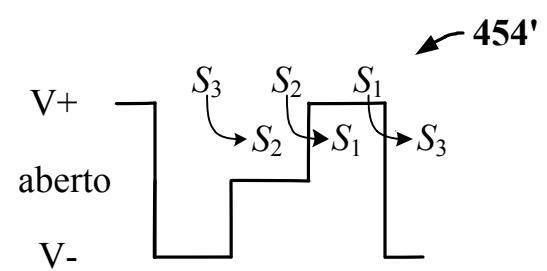

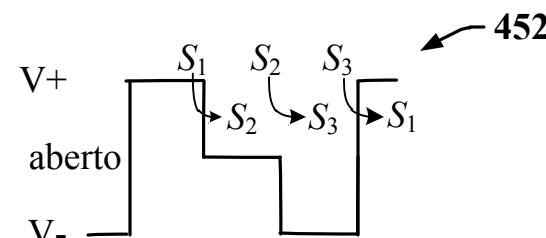

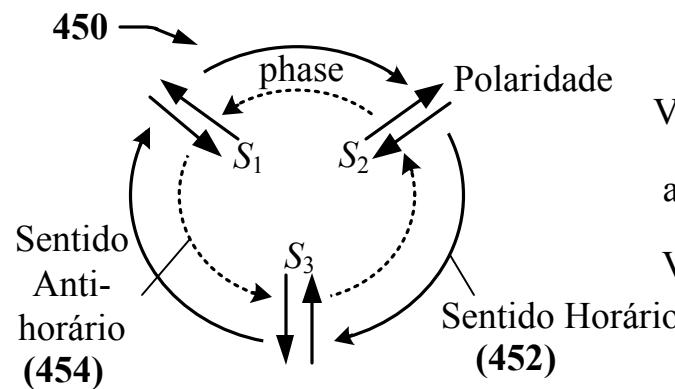

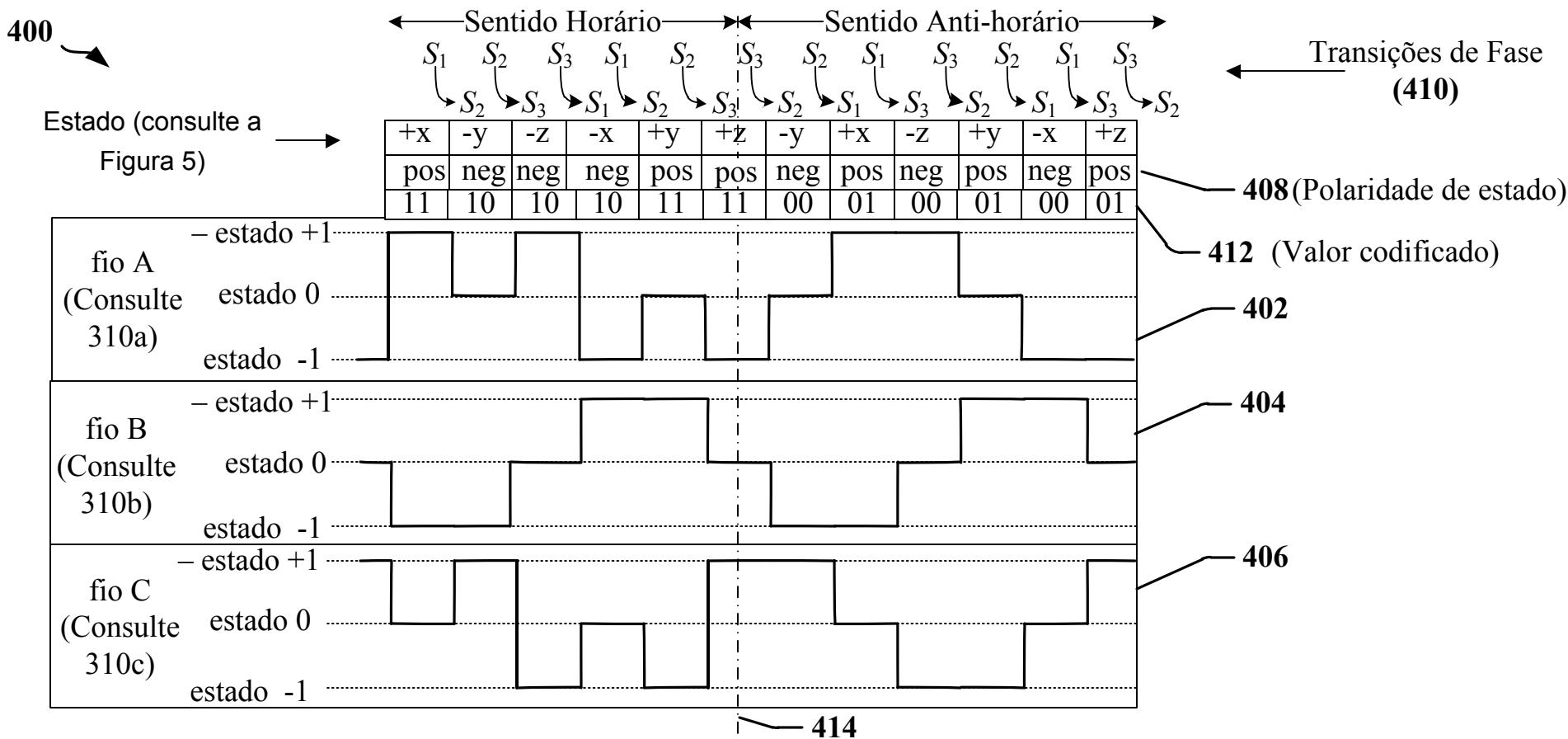

[0021] A Figura 4 ilustra sinalização em uma interface codificada em polaridade de N fases.

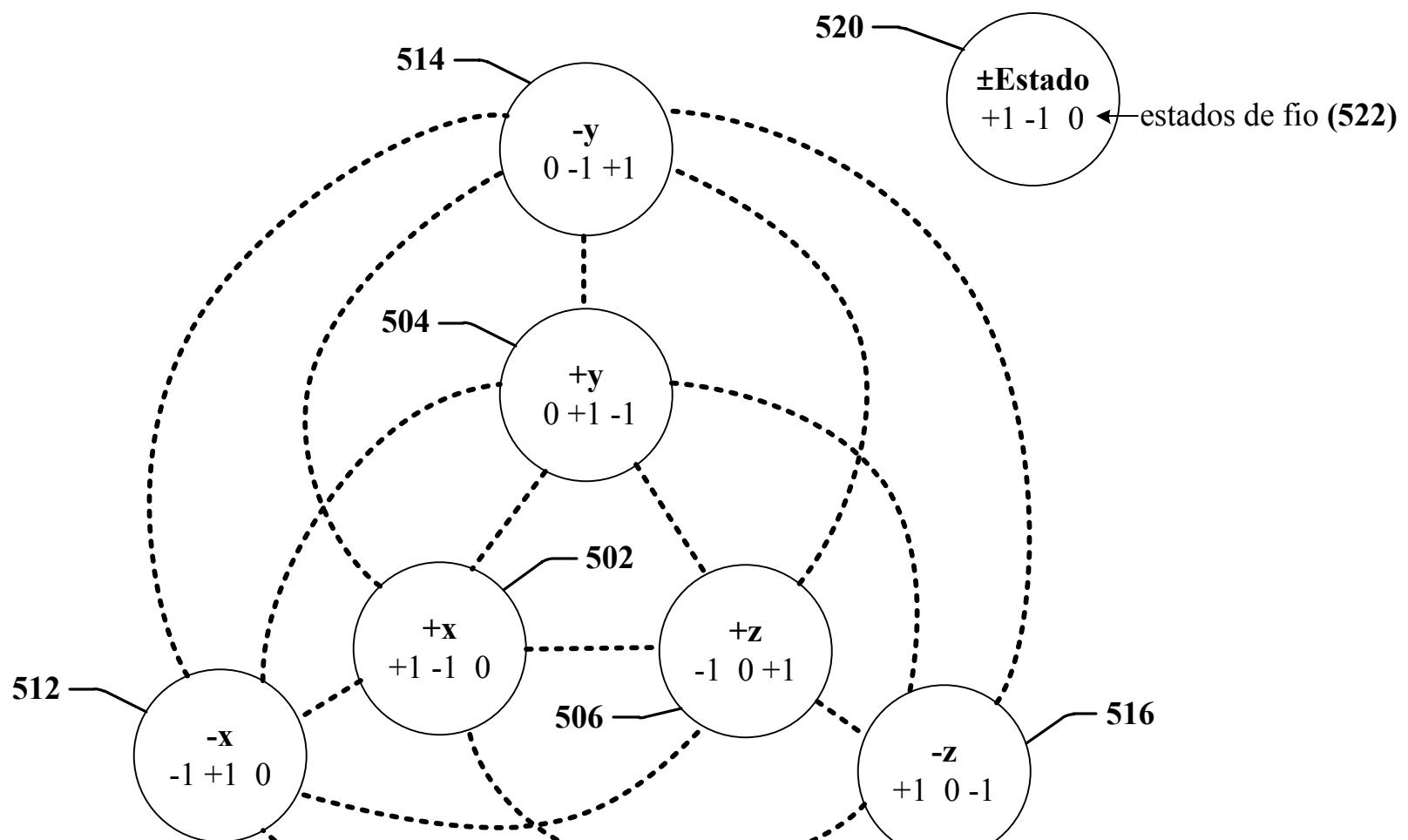

[0022] A Figura 5 é um diagrama de estado que ilustra transições de estado no exemplo de um enlace de comunicação de trifásico de 3 fios.

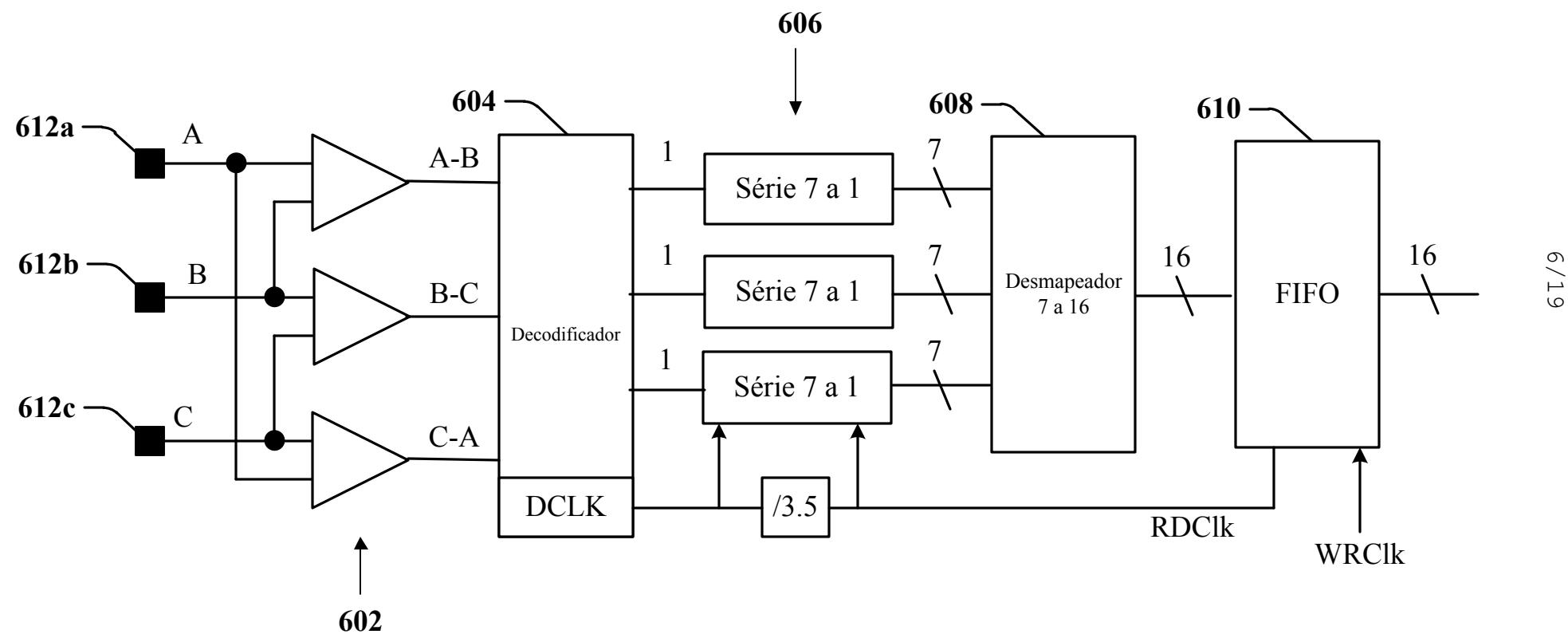

[0023] A Figura 6 ilustra um decodificador de dados de polaridade trifásico.

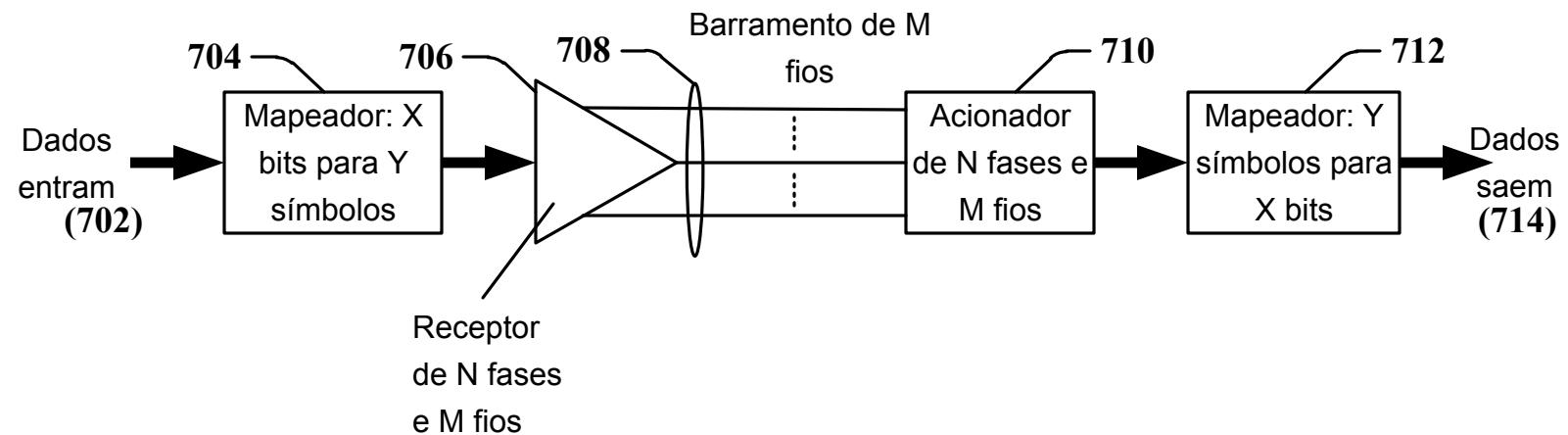

[0024] A Figura 7 ilustra um acionador para codificação de dados de polaridade de N fases e fio M.

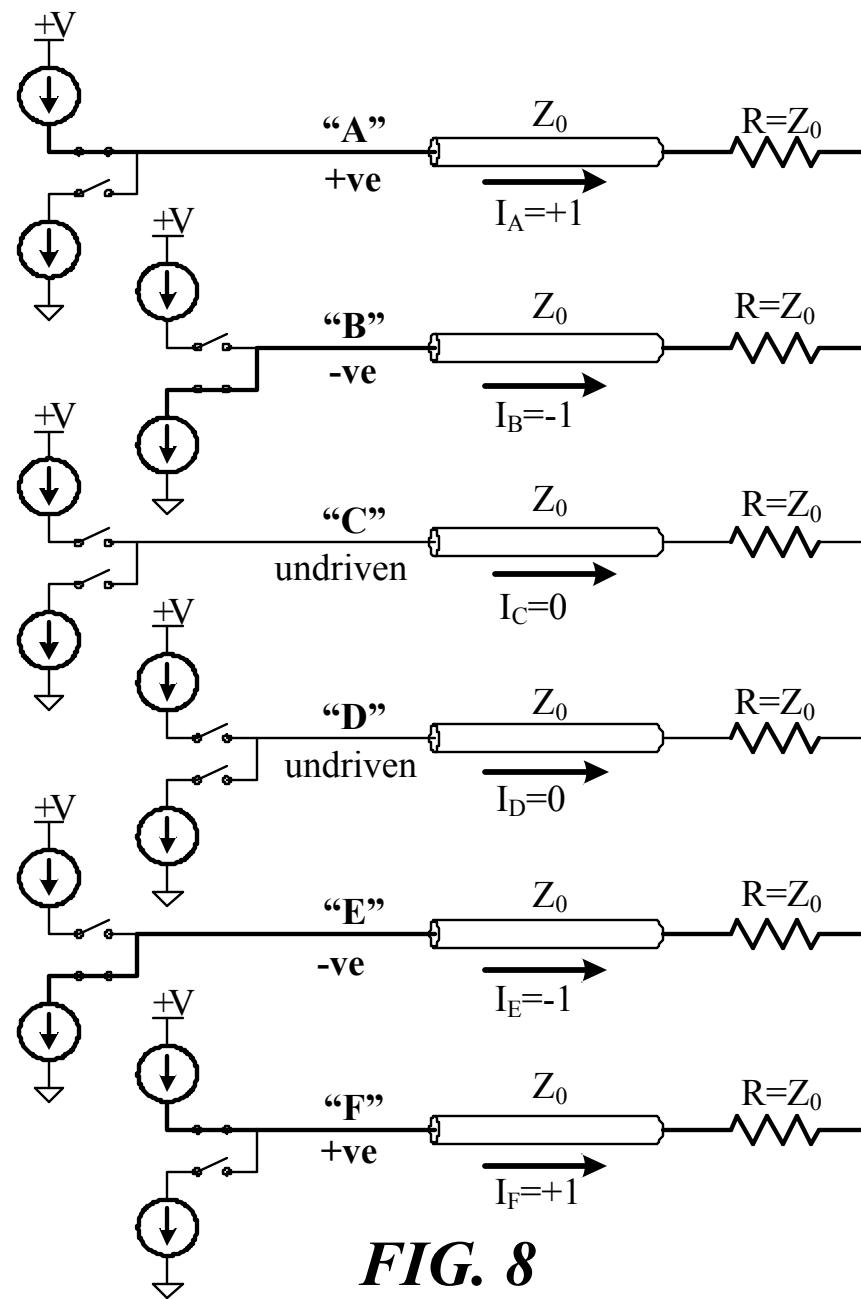

[0025] A Figura 8 é um desenho esquemático que mostra um modelo de um codificador que transmite símbolos com o uso de 6 fios com 2 pares de fios acionados para cada estado.

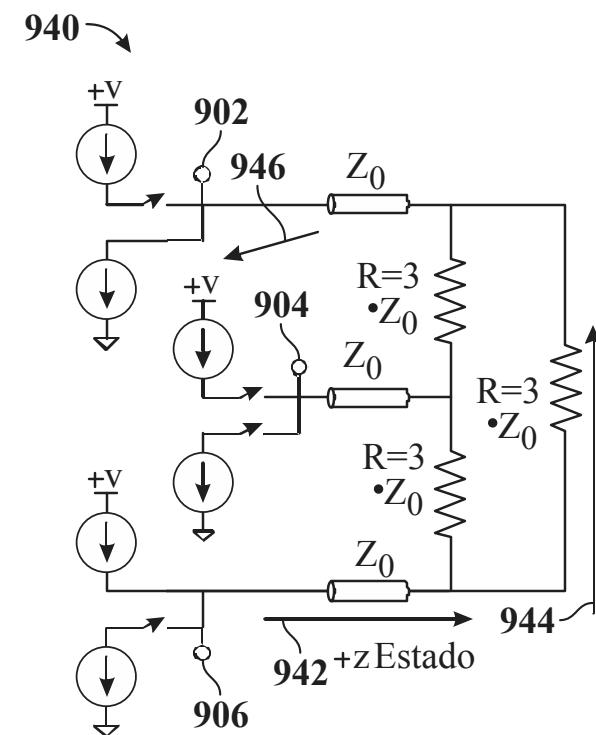

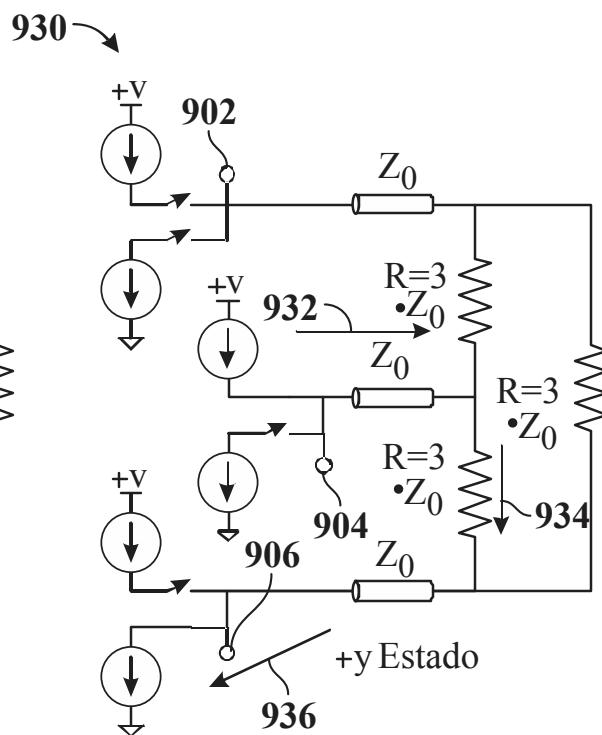

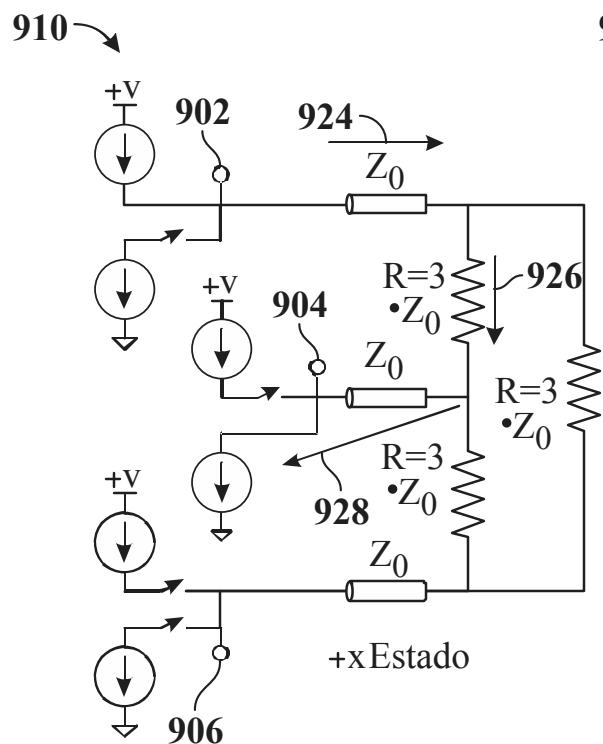

[0026] A Figura 9 é um desenho esquemático que mostra um modelo de um circuito de codificação de polaridade trifásico.

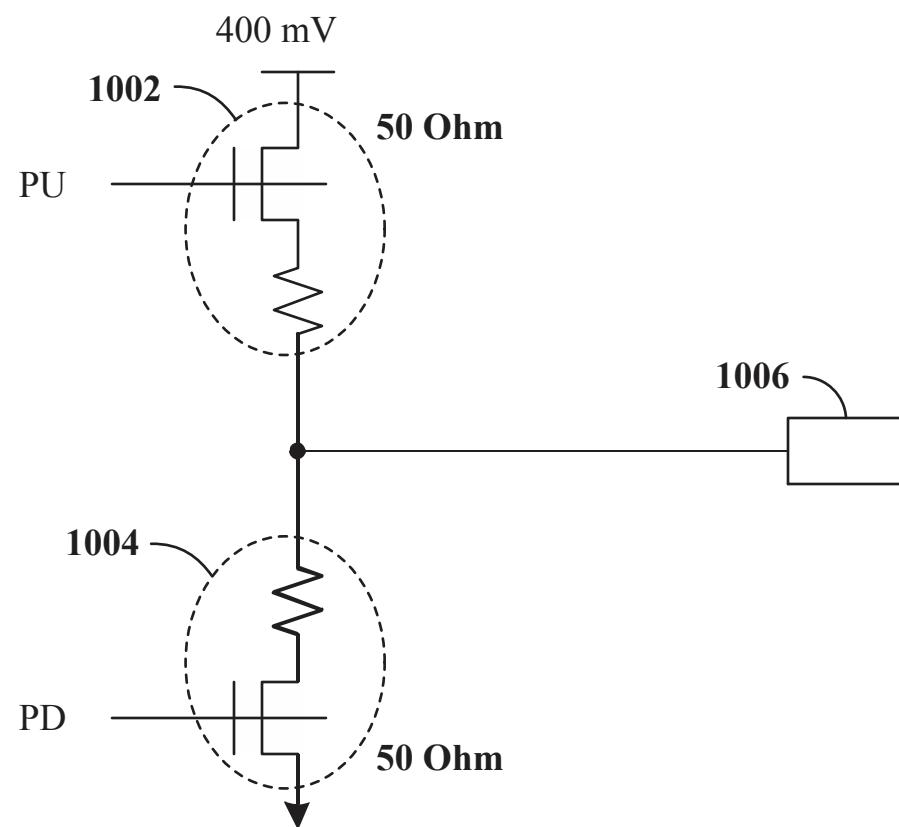

[0027] A Figura 10 ilustra um exemplo de uma interface de linha usada para acionar um fio de sinal em um sistema trifásico.

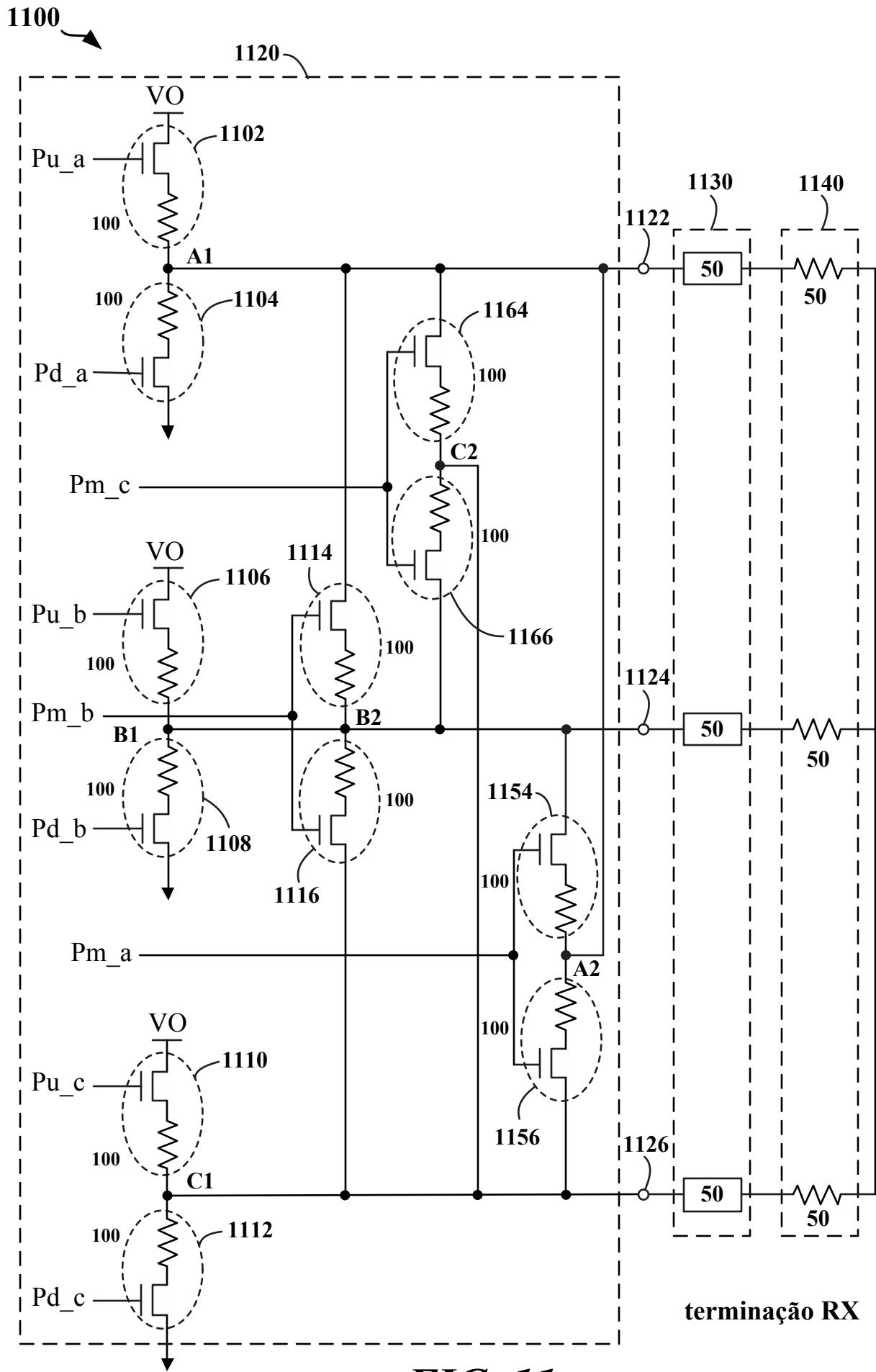

[0028] A Figura 11 ilustra um primeiro exemplo de interfaces de linha usadas para acionar três fios de sinal em um sistema trifásico.

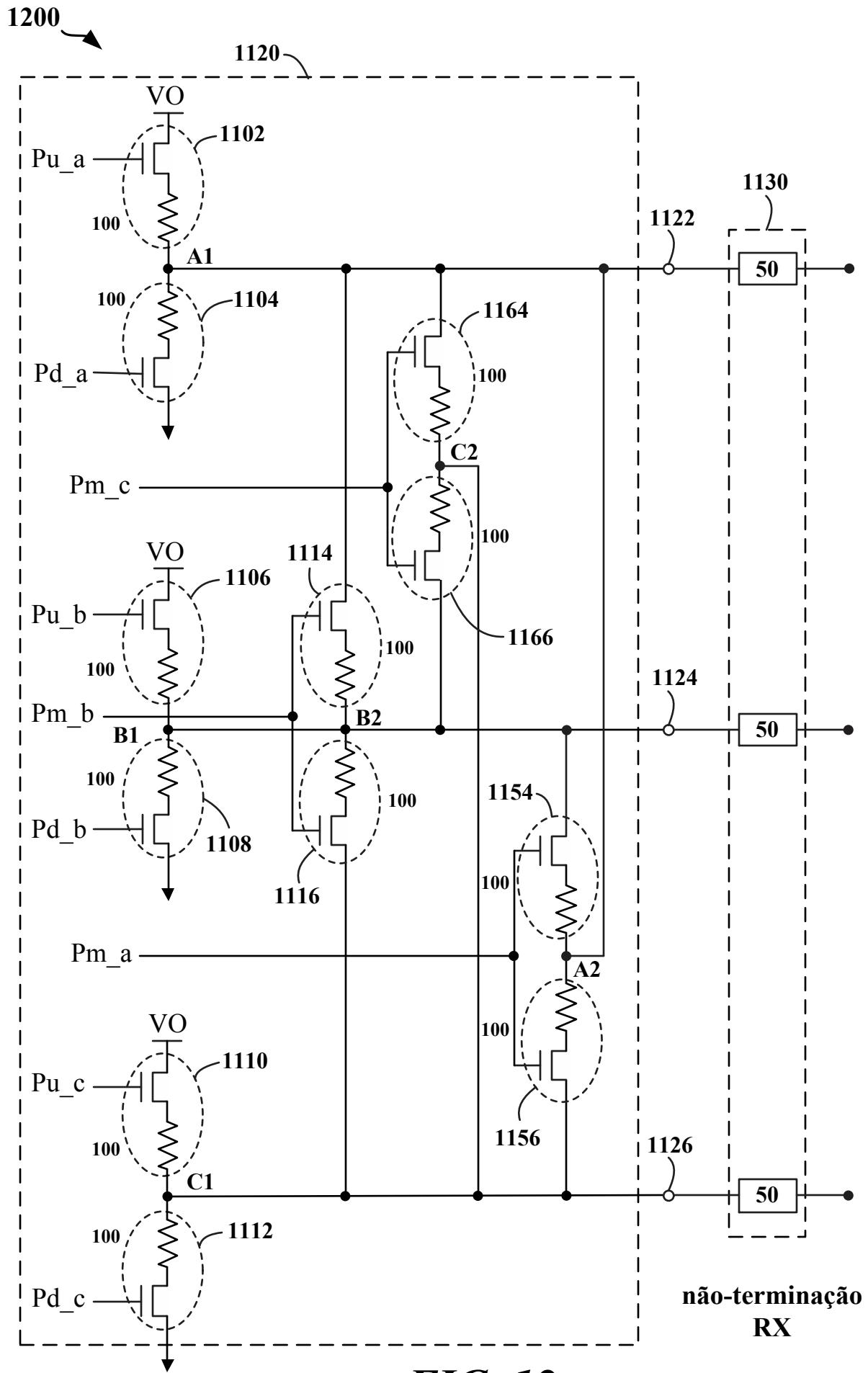

[0029] A Figura 12 ilustra um segundo exemplo de interfaces de linha usadas para acionar três fios de sinal em um sistema trifásico.

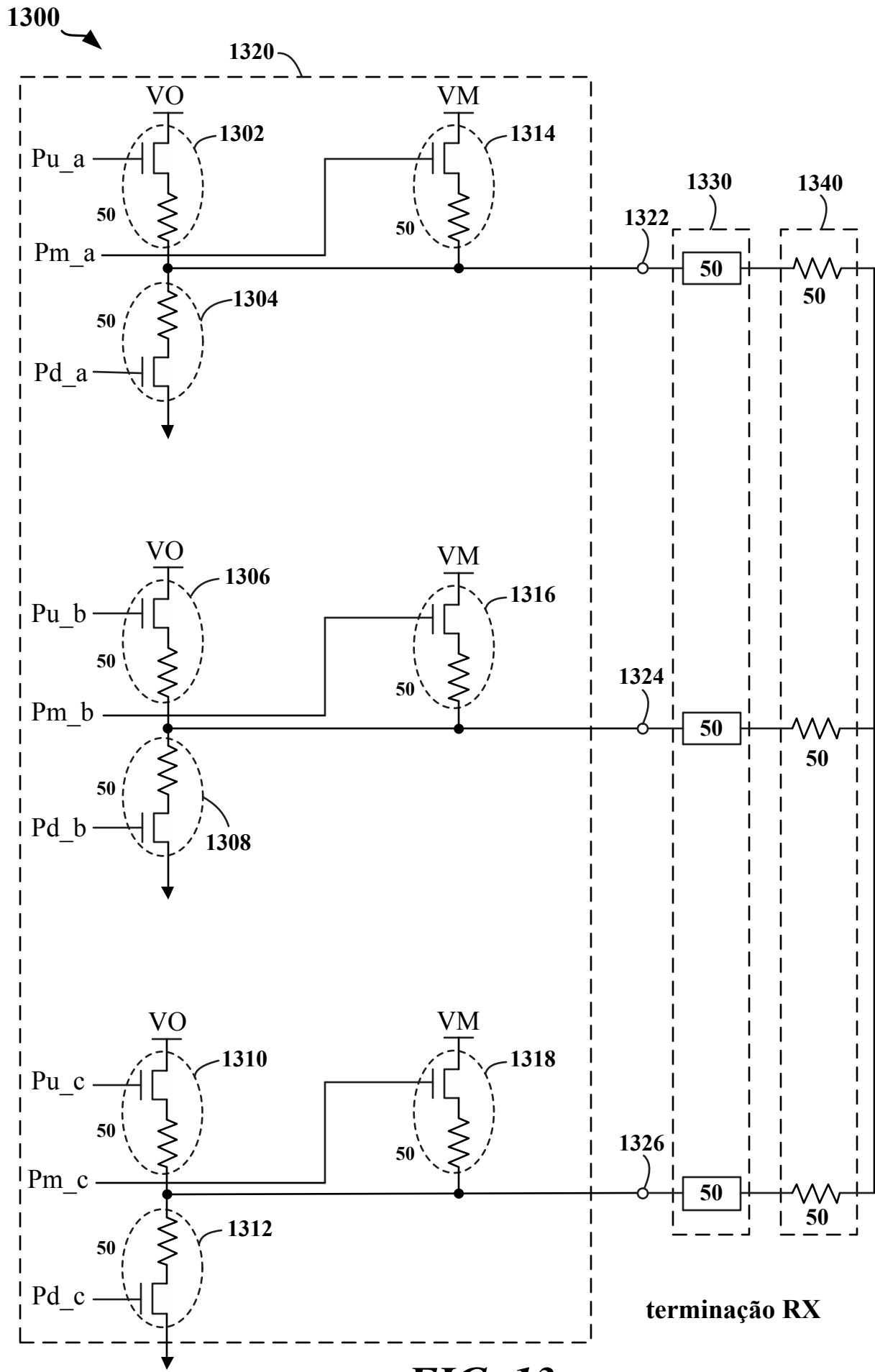

[0030] A Figura 13 ilustra um terceiro exemplo de interfaces de linha usadas para acionar três fios de sinal em um sistema trifásico.

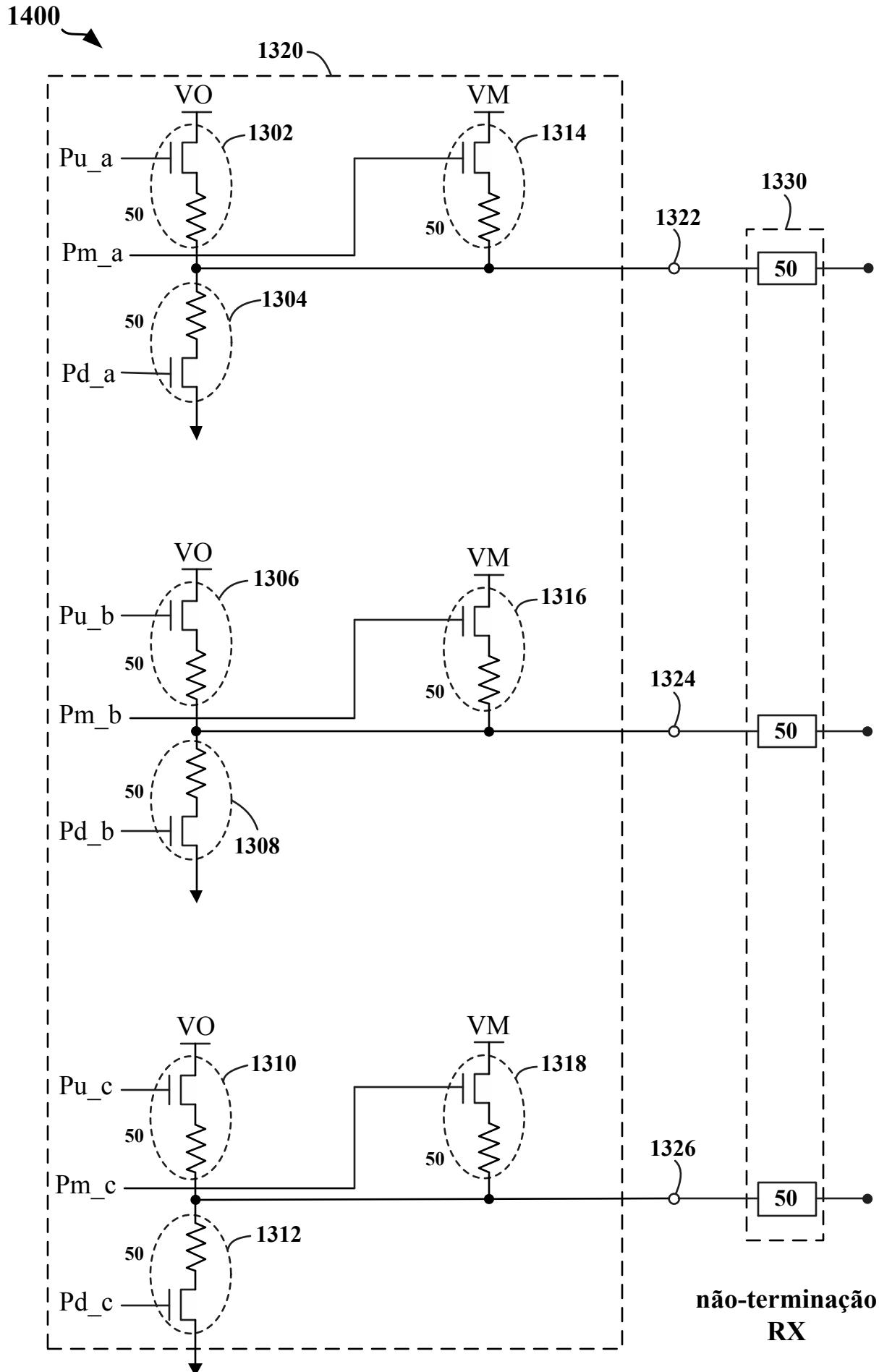

[0031] A Figura 14 ilustra um quarto exemplo de interfaces de linha usadas para acionar três fios de sinal em um sistema trifásico.

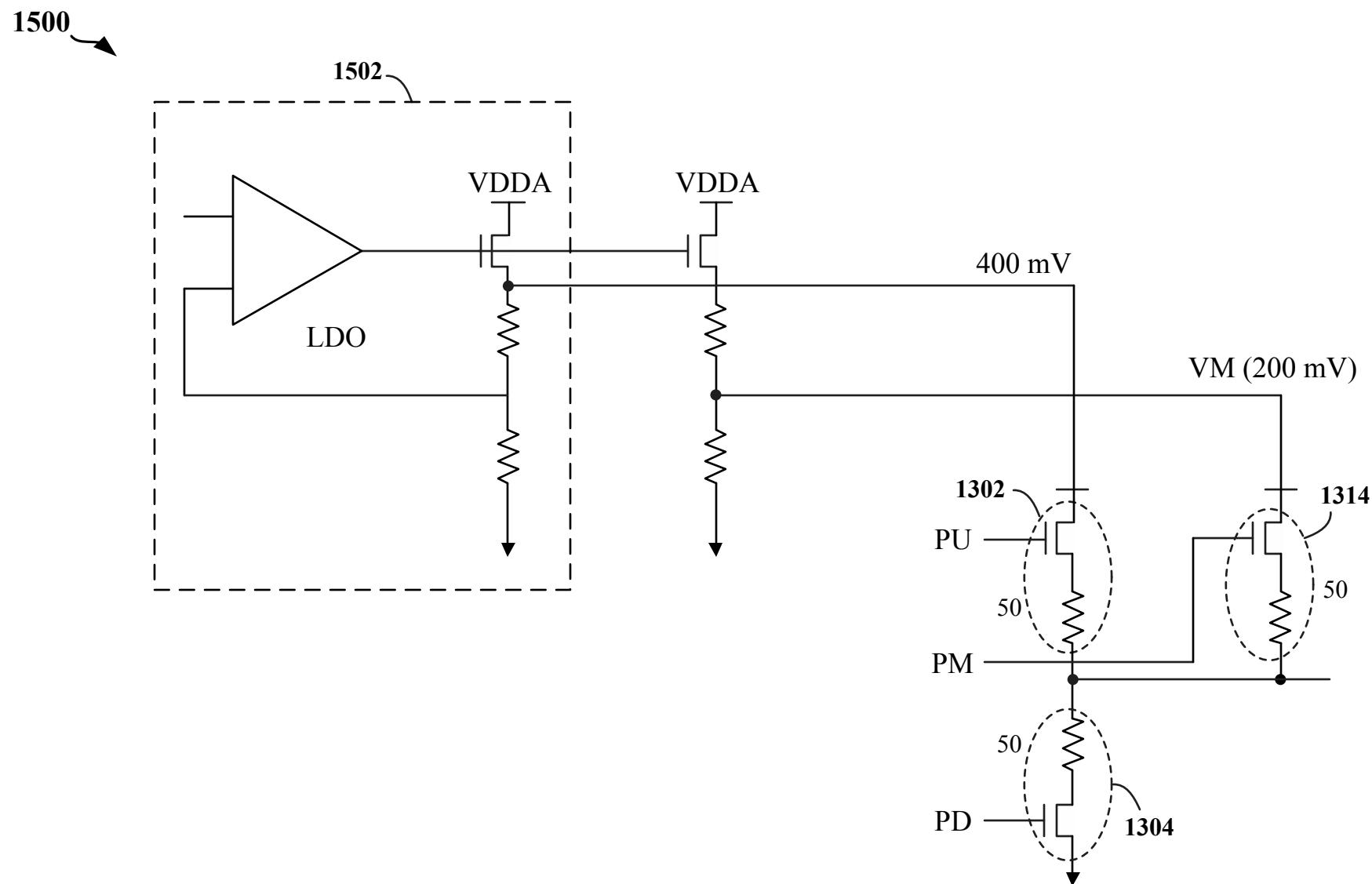

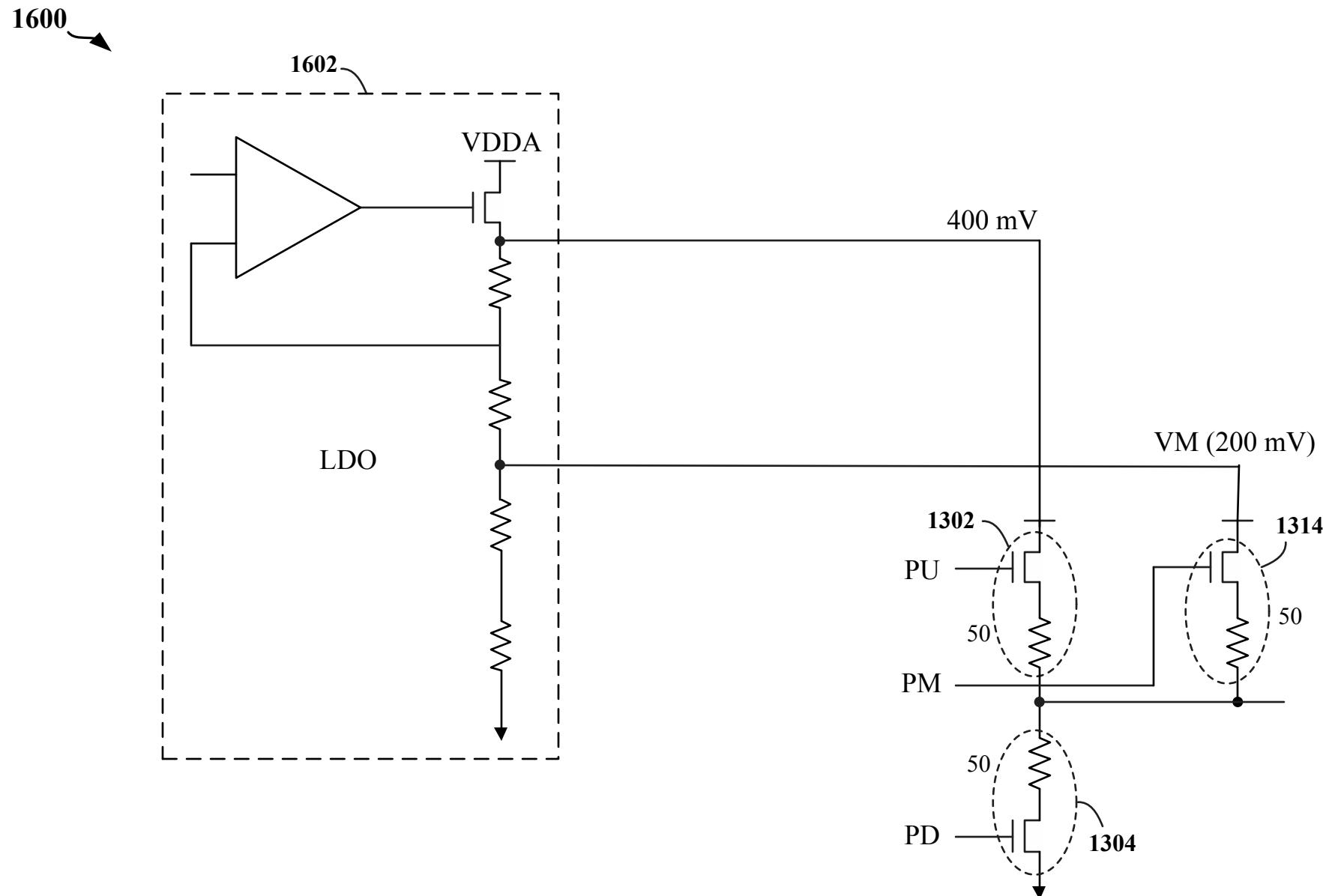

[0032] A Figura 15 ilustra um primeiro exemplo de um regulador de LDO em operação com um transistor pull-up e um transistor pull-middle.

[0033] A Figura 16 ilustra um segundo exemplo de um regulador de LDO em operação com um transistor pull-up e um transistor pull-middle.

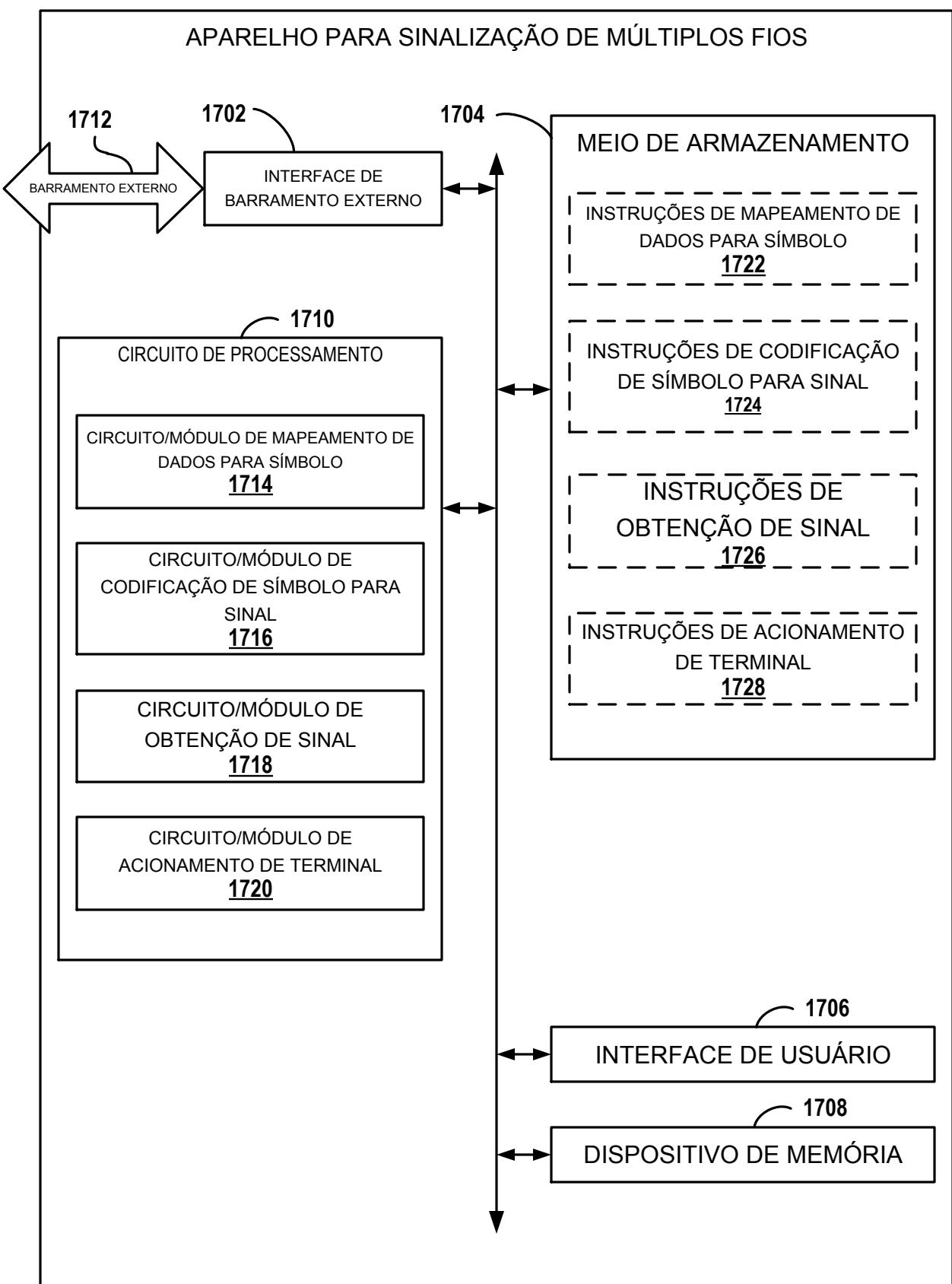

[0034] A Figura 17 é um diagrama que ilustra um exemplo de uma implantação de hardware para um transmissor de um sinal codificado de polaridade de N fases.

[0035] A Figura 18 é um fluxograma que ilustra um método de transferência de dados.

[0036] A Figura 19 é um fluxograma que ilustra

outro método de transferência de dados.

#### DESCRIÇÃO DETALHADA

[0037] Vários aspectos são descritos agora em referência aos desenhos. Na descrição a seguir, com propósitos de explicação, numerosos detalhes específicos são estabelecidos a fim de fornecer um entendimento completo de um ou mais aspectos. Pode ficar evidente, contudo, que tal (tais) aspecto(s) pode (podem) ser praticado(s) sem esses detalhes específicos.

[0038] Conforme usado neste pedido, os termos "componente", "módulo", "sistema" e semelhantes se destinam a incluir uma entidade relacionada a computador, tal como, mas não limitadamente, hardware, firmware, uma combinação de hardware e software, software, ou software em execução. Por exemplo, um componente pode ser, porém, sem limitação, um processo que é executado em um processador, um processador, um objeto, um executável, uma linha de execução, um programa e/ou um computador. A título de ilustração, tanto um aplicativo que é executado em um dispositivo de computação quanto o dispositivo de computação podem ser um componente. Um ou mais componentes podem permanecer dentro de um processo e/ou linha de execução, e um componente pode estar localizado em um dispositivo de computação e/ou distribuído dentre dois ou mais dispositivos de computação. Além disso, esses componentes podem executar de vários meios legíveis por computador que têm várias estruturas de dados armazenadas no mesmo. Os componentes podem se comunicar por meio de processos locais e/ou remotos, como, de acordo com um sinal que tem um ou mais pacotes de dados, como dados de um

componente que interage com outro componente em um sistema local, sistema distribuído e/ou através de uma rede, como, a Internet com outros sistemas por meio do sinal.

[0039] Além disso, o termo "ou" se destina a significar um "ou" inclusivo em vez de um "ou" exclusivo. Ou seja, a menos que especificado de outro modo, ou esteja claro a partir do contexto, a frase "X emprega A ou B" se destina a significar qualquer uma das permutações inclusivas naturais. Ou seja, a frase "X emprega A ou B" é satisfeita por qualquer um dos exemplos a seguir: X emprega A; X emprega B; ou X emprega tanto A quanto B. Além disso, os artigos "um" e "uma" conforme usados neste pedido e nas reivindicações anexas devem ser, geralmente, interpretados como significando "um ou mais", salvo especificação contrária ou clara a partir do contexto para ser direcionado para uma forma singular. Descrição Exemplificativa de codificação e Decodificação de Múltiplas Fases

[0040] Certos exemplos revelados se referem a sistemas e aparelho que empregam métodos de codificação e decodificação de dados de múltiplas fases que envolve uma pluralidade de condutores (isto é, M condutores ou fios). Os M condutores tipicamente incluem três ou mais condutores, e cada condutor pode ser denominado fio, embora os M condutores possam incluir traços condutivos em uma placa de circuito ou em uma camada condutora de um dispositivo de circuito integrado (IC) de semicondutor. Os M condutores podem ser divididos em uma pluralidade de grupos de transmissão, sendo que cada grupo codifica uma porção de um bloco de dados a ser transmitido. Um esquema

de codificação de  $N$  fases é definido em que bits de dados são codificados em transições de fase e mudanças de polaridade nos  $M$  condutores. Em um exemplo, um esquema de codificação de  $N$  fases para um sistema de 3 fios pode incluir três estados de fase e duas polaridades, e fornece 6 estados e 5 transições possíveis de cada estado. Mudanças determinísticas de tensão e/ou corrente podem ser detectadas e decodificadas para extrair dados dos  $M$  condutores. Decodificação não conta com condutores independentes, ou pares de condutores e informações de temporização podem ser derivados diretamente de transições de fase e/ou polaridade nos  $M$  condutores. Uma transferência de dados de polaridade de  $N$  fases pode ser aplicada a qualquer interface de sinalização, tal como interfaces elétrica, óptica e de radiofrequência (RF), por exemplo.

[0041] Certos aspectos da invenção podem ser aplicáveis a enlaces de comunicações instaladas entre componentes eletrônicos, que podem incluir subcomponentes de dispositivos tais como telefones, dispositivos de computação móvel, utensílios domésticos, eletrônicos de automóvel, sistemas aviônicos, etc. Em relação à Figura 1, por exemplo, um aparelho 100 que emprega codificação de  $N$  fases e  $M$  fio pode incluir um circuito de processamento 102 que é configurado para controlar operação do aparelho 100. O circuito de processamento 102 pode acessar e executar aplicativos de software e circuitos lógicos de controle e outros dispositivos no aparelho 100. Em um exemplo, o aparelho 100 pode incluir um dispositivo de comunicação que se comunica através de um transceptor de comunicações de RF 106 com uma rede de acesso de rádio (RAN), uma rede de

acesso principal, a Internet e/ou outra rede. O transceptor de comunicações 106 pode ser acoplado de modo operável a um circuito de processamento 102. O circuito de processamento 102 pode incluir um ou mais dispositivos de IC, tal como um IC específico para aplicativo (ASIC) 108. O ASIC 108 pode incluir um ou mais dispositivos de processamento, circuitos de lógica e assim por diante. O circuito de processamento 102 pode incluir e/ou ser acoplado a um armazenamento legível por processador 112 que pode manter instruções e dados que podem ser executados pelo circuito de processamento 102. O circuito de processamento 102 pode ser controlado por um ou mais dentre um sistema operacional e uma camada de interface de programação de aplicativo (API) 110 que suporte e permita execução de módulos de software que residem no armazenamento 112 do dispositivo. O armazenamento 112 pode incluir memória somente de leitura (ROM) ou memória de acesso aleatório (RAM), memória somente de leitura programável e eletricamente apagável (EEPROM), um dispositivo de memória flash ou qualquer dispositivo de memória que pode ser usado em processamento de sistemas e plataformas de computação. O circuito de processamento 102 pode incluir e/ou acessar um banco de dados local 114 que pode manter parâmetros operacionais e outras informações usadas para configurar e operar o aparelho 100. O banco de dados local 114 pode ser implantado com o uso de um ou mais dentre um módulo ou servidor de banco de dados, memória flash, mídia magnética, EEPROM, mídia óptica, fita, disco rígido ou flexível ou similares. O circuito de processamento também pode ser acoplado de modo operável aos dispositivos externos, como uma antena 122, um visor 124,

controles de operador, como um botão 128 e um teclado 126 dentre outros componentes.

[0042] A Figura 2 é um esquemática de blocos que ilustra certos aspectos de um aparelho 200 tal como um dispositivo móvel, um telefone móvel, um sistema de computação móvel, um computador do tipo notebook, um dispositivo de computação do tipo tablet, um reproduutor de mídia, um dispositivo de jogos, ou semelhantes. O aparelho 200 pode incluir uma pluralidade de dispositivos de IC 202 e 230 que trocam dados e informações de controle através de um enlace de comunicações 220. O enlace de comunicações 220 pode ser usado para conectar os dispositivos de IC 202 e 230, que podem estar localizados em proximidade estreita uns dos outros ou fisicamente localizados em partes diferentes do aparelho 200. Em um exemplo, o enlace de comunicações 220 pode ser fornecido em uma portadora de chip, um substrato ou uma placa de circuito que porta os dispositivos de IC 202 e 230. Em outro exemplo, um primeiro dispositivo de IC 202 pode estar localizado em uma seção de teclado numérico em um telefone do tipo flip enquanto um segundo dispositivo de IC 230 pode estar localizado em uma seção de visor do telefone do tipo flip. Uma porção do enlace de comunicações 220 pode incluir um cabo ou uma conexão óptica.

[0043] O enlace de comunicações 220 pode incluir múltiplos canais 222, 224 e 226. Um ou mais canais 226 podem ser bidirecionais e podem operar em modo de meio duplex e/ou modo de duplex completo. Um ou mais canais 222, 224 podem ser unidirecionais. O enlace de comunicações 220 pode ser assimétrico, o que fornece largura de banda maior

em uma direção. Em um exemplo descrito no presente documento, um primeiro canal de comunicações 222 pode ser denominado enlace progressivo 222 enquanto um segundo canal de comunicações 224 pode ser denominado enlace regressivo 224. O primeiro dispositivo de IC 202 pode ser atribuído como um host, mestre e/ou transmissor, enquanto o segundo dispositivo de IC 230 pode ser atribuído como um cliente, escravo e/ou receptor, mesmo se ambos os dispositivos de IC 202 e 230 são configurados para transmitir e receber no enlace de comunicações 220. Em um exemplo, o enlace progressivo 222 pode operar em uma taxa de dados maior quando comunica dados de um primeiro dispositivo de IC 202 para um segundo dispositivo de IC 230, enquanto o enlace regressivo 224 pode operar em uma taxa de dados menor quando comunica dados do segundo dispositivo de IC 230 para o primeiro dispositivo de IC 202.

[0044] Os dispositivos de IC 202 e 230 podem cada um incluir um processador ou outro dispositivo ou circuito de processamento e/ou computação 206, 236. Em um exemplo, o primeiro dispositivo de IC 202 pode realizar funções principais do aparelho 200, inclusive manter comunicações através de um transceptor 204 e uma antena 214, enquanto o segundo dispositivo de IC 230 pode suportar uma interface de usuário que gerencia ou opera um controlador de visor 232, e pode controlar operações de uma câmera ou um dispositivo de entrada de vídeo com o uso de um controlador de câmera 234. Outros recursos suportados por um ou mais dentre os dispositivos de IC 202 e 230 podem incluir um teclado, um componente de reconhecimento de voz e outros dispositivos de entrada ou saída. O controlador de

visor 232 pode incluir circuitos e unidades de software que suportam um visor tal como um painel de visor de cristal líquido (LCD), um visor de tela sensível ao toque, um indicador, e assim em diante. Os meios de armazenamento 208 e 238 podem incluir dispositivos de armazenamento transitórios e/ou não transitórios adaptados para manter instruções e dados usados pelos respectivos circuitos de processamento 206 e 236, e/ou outros componentes dos dispositivos de IC 202 e 230. Uma comunicação entre cada circuito de processamento 206, 236 e seus meios de armazenamento correspondentes 208 e 238 e outros módulos e circuitos pode ser facilitada por um ou mais barramentos 212 e 242, respectivamente.

[0045] O enlace regressivo 224 pode ser operado na mesma maneira que o enlace progressivo 222. O enlace progressivo 222 e o enlace regressivo 224 podem ter capacidade para transmitir em velocidades comparáveis ou em velocidades diferentes, sendo que velocidade pode ser expressa como uma taxa de transferência de dados e/ou uma taxa de relógio. As taxas de dados progressiva e regressiva podem ser substancialmente iguais ou podem diferir em ordens de magnitude, dependendo da aplicação. Em algumas aplicações um único enlace bidirecional 226 pode suportar comunicações entre o primeiro dispositivo de IC 202 e o segundo dispositivo de IC 230. O enlace progressivo 222 e/ou o enlace regressivo 224 pode ser configurável para operar em um modo bidirecional quando, por exemplo, os enlaces progressivo e regressivo 222 e 224 compartilham as mesmas conexões físicas e operam em uma maneira de meio duplex.

[0046] Em certos exemplos, o enlace regressivo 224 deriva um sinal de relógio do enlace progressivo 222 para finalidades de sincronização, para finalidades de controle, para facilitar gerenciamento de potência e/ou para simplicidade de projeto. O sinal de relógio pode ter uma frequência que é obtida dividindo-se a frequência de um símbolo de clock usado para transmitir sinais no enlace progressivo 222. O clock de símbolo pode ser sobreposto ou de outro modo codificado em símbolos transmitido no enlace progressivo 222. O uso de um sinal de relógio que é um derivado do símbolo de clock permite sincronização rápida de transmissores e receptores (transceptores 210, 240) e permite início e interrupção rápidos de sinais de dados sem a necessidade de enquadramento para permitir treinamento e sincronização.

[0047] Em certos exemplos, um único enlace bidirecional 226 pode suportar comunicações entre o primeiro dispositivo de processamento 202 e o segundo dispositivo de processamento 230. Em alguns casos, o primeiro dispositivo de processamento 202 e o segundo dispositivo de processamento 230 fornecem codificação e decodificação de dados, sinais de endereço e controle transmitidos entre um dispositivo de processamento e dispositivos de memória tais como memória de acesso aleatório dinâmico (DRAM).

[0048] Em um exemplo, um ou mais barramentos 212 e/ou 242 podem fornecer acesso a SDRAM de taxa dupla de dados (DDR) com o uso de uma técnica de codificação de N fases e M fio. Os dispositivos de codificação de polaridade de N fases 210 e/ou 240 podem codificar múltiplos bits por

transição, e múltiplos conjuntos de fios podem ser usados para transmitir e receber dados da SDRAM, sinais de controle, sinais de endereço, e assim em diante.

[0049] Em outro exemplo, o enlace de comunicações 220 inclui uma interface digital de alta velocidade, tal como uma interface digital de exibição móvel (MDDI), e um ou mais enlaces de dados 222, 224 e 226 podem usar codificação de polaridade de N fases. Os transceptores 210 e 240 podem codificar e decodificar dados transmitidos no enlace de comunicações 220. O uso de codificação de polaridade de N fases fornece transferência de dados de alta velocidade e pode consumir metade ou menos da potência de outras interfaces pelo fato de que menos acionadores estão ativos em enlaces de dados codificados de polaridade de N fases 220. Os dispositivos de codificação de polaridade de N fases 210 e/ou 240 podem codificar múltiplos bits por transição na interface, que pode incluir um barramento. Em um exemplo, uma combinação de codificação de polaridade e trifásica pode ser usada para suportar a uma IC de acionador de LCD de 80 quadros por segundo de Matriz Ampla de Gráfico de Vídeo (WVGA) sem um armazenamento temporário de quadro, o que entrega dados de pixel a 810 Mbps para atualização de exibição.

[0050] De acordo com certos aspectos revelados no presente documento, as características de um enlace de comunicações de polaridade de N fases e M fio podem ser modificadas de modo dinâmico para acomodar exigências e circunstâncias operacionais que mudam. Por exemplo, a quantidade de fios usada para transmitir um sinal de N fases pode ser aumentada a fim de obter uma largura de

banda disponível maior e/ou a quantidade de fios usada para transmitir um sinal de  $N$  fases pode ser diminuída para reduzir consumo de potência pelos dispositivos de IC 202 e 230. A quantidade de fios usada para transmitir um sinal de  $N$  fases em uma direção pode ser adaptada de modo independente da quantidade de fios usada para transmitir um sinal de  $N$  fases na outra direção. Os circuitos de recebimento e circuitos de transmissão nos acionadores de camada física 210 e 240 podem ser configurados com o uso de informações de controle transmitidas quando o enlace de comunicações 220 é ativado após hibernação ou energização. As informações de controle podem ser transmitidas de acordo com um protocolo predefinido, através do qual uma quantidade mínima de fios são ativados para portar uma mensagem de controle que especifica a configuração do enlace de comunicações 220, por exemplo. A mensagem de controle pode de modo alternativo ou adicional ser transmitida com um comando de desligamento, um comando de despertar, e/ou em um preâmbulo que precede cada transmissão. Em alguns exemplos, a configuração do enlace de comunicações 220 pode ser determinada durante uma sequência de treinamento e/ou sincronização, através da qual os acionadores de camada física de recebimento 210 ou 240 monitoram os fios disponíveis ou outros condutores para transições que correspondem a um sinal de  $N$  fases, a fim de determinar quais fios/condutores estão ativos.

[0051] A Figura 3 é um diagrama 300 que ilustra um exemplo de um transmissor de codificação de polaridade de  $N$  fases e  $M$  fio configurada para  $M=3$  e  $N=3$ . O exemplo de codificação trifásica de 3 fios é selecionado somente para

a finalidade de simplificar descrições de certos aspectos dessa revelação. Os princípios e as técnicas revelados para codificadores trifásicos de 3 fios podem ser aplicados em outras configurações de codificadores de polaridade de N fases e M fio.

[0052] Quando uma codificação de polaridade de N fases é usada, condutores tais como fios de sinal 310a, 310b e 310c em um barramento de M fio podem ser não acionados, acionados positivos, ou acionados negativos. Um fio de sinal não acionado 310a, 310b ou 310c pode estar em um estado de alta impedância. Um fio de sinal não acionado 310a, 310b ou 310c pode ser acionado para um nível de tensão que se situa substancialmente na metade entre os níveis de tensão positivo e negativo fornecidos em fios de sinal acionado. Um fio de sinal não acionado 310a, 310b ou 310c pode ter nenhuma corrente que flui através do mesmo. No exemplo ilustrado na Figura 3, cada fio de sinal 310a, 310b e 310c pode estar em um de três estados (denotados como +1, -1, e 0) com o uso de acionadores 308. Em um exemplo, os acionadores 308 podem incluir acionadores de modo de corrente de nível de unidade. Em outro exemplo, os acionadores 308 podem acionar tensões de polaridade opostas em dois sinais 310a e 310b enquanto o terceiro sinal 310c está em impedância alta e/ou empurrado para aterramento. Para cada intervalo de símbolo transmitido, pelo menos um sinal está no estado não ativado (0), enquanto a quantidade de sinais acionados positivos (estado +1) é igual à quantidade de sinais acionados negativos (estado -1), de modo que a soma de corrente que flui para o receptor seja sempre zero. Para cada par de intervalos de transmissão de

símbolo consecutivos, pelo menos um fio de sinal 310a, 310b ou 310c tem um estado diferente nos dois intervalos de transmissão de símbolo.

[0053] No exemplo retratado na Figura 3, dados de 16 bits 318 são inseridos em um mapeador 302, que mapeia os dados de entrada 318 por 7 símbolos 312 para transmitir sequencialmente através dos fios de sinal 310a, 310b e 310c. Os 7 símbolos 312 podem ser colocados em série, com o uso de conversores paralelo/série 304, por exemplo. Um codificador de N fases e M fio 306 recebe 7 símbolos 312 produzidos pelo mapeador um símbolo por vez e computa o estado de cada fio de sinal 310a, 310b e 310c para cada intervalo de símbolo. O codificador 306 seleciona os estados dos fios de sinal 310a, 310b e 310c com base no símbolo de entrada e os estados anteriores de fios de sinal 310a, 310b e 310c.

[0054] O uso de codificação de N fases e M fio permite que uma quantidade de bits seja codificada em uma pluralidade de símbolos em que os bits por símbolo não são um número inteiro. No exemplo simples de um sistema de 3 fios, existem 3 combinações disponíveis de 2 fios que podem ser acionados simultaneamente, e 2 combinações possíveis de polaridade no par de fios simultaneamente acionados, que rendem 6 estados possíveis. Visto que cada transição ocorre de um estado atual, 5 dos 6 estados estão disponíveis em todas as transições. O estado de pelo menos um fio é exigido para mudar em cada transição. Com 5 estados,  $\log_2(5) \approx 2,32$  bits pode ser codificado por símbolo. Consequentemente, um mapeador pode aceitar uma palavra de 16 bits e converter a mesma em 7 símbolos pelo fato de que

7 símbolos que portam 2,32 bits por símbolo podem codificar 16,24 bits. Em outras palavras, uma combinação de sete símbolos que codificam cinco estados tem  $5^7$  (78.125) permutações. Consequentemente, os 7 símbolos podem ser usados para codificar as  $2^{16}$  (65.536) permutações de 16 bits.

[0055] A Figura 4 ilustra um exemplo de sinalização 400 que emprega um esquema de codificação de dados de modulação trifásica com base no diagrama de transição de estado circular 450. De acordo com o esquema de codificação de dados, um sinal trifásico pode girar em duas direções e pode ser transmitido em três condutores 310a, 310b, e 310c. Cada um dos três sinais é acionado de modo independente nos condutores 310a, 310b, e 310c. Cada um dos três sinais inclui o sinal trifásico, sendo que cada sinal em cada condutor 310a, 310b, e 310c é 120 graus fora de fase em relação aos sinais nos outros dois condutores 310a, 310b, e 310c. Em qualquer ponto de tempo, cada um dos três condutores 310a, 310b, 310c está em um estado diferente dentre os estados {+1, 0, -1}. Em qualquer ponto de tempo, cada um dos três condutores 310a, 310b, 310c em um sistema de 3 fios está em um estado diferente do que os outros dois fios. Quando mais do que três condutores ou fios são usados, dois ou mais pares de fios podem estar no mesmo estado. O esquema de codificação ilustrado também codifica informações na polaridade dos dois condutores 310a, 310b e/ou 310c que sãoativamente acionados para os estados +1 e -1. A polaridade é indicada em 408 para a sequência de estados retratada.

[0056] Em qualquer estado de fase no exemplo de

três fios ilustrado, exatamente dois dos condutores 310a, 310b, 310c portam um sinal que é, de modo eficaz, um sinal diferencial para esse estado de fase, enquanto o terceiro condutor 310a, 310b ou 310c está não acionado. O estado de fase para cada condutor 310a, 310b, 310c pode ser determinado por diferença de tensão entre o condutor 310a, 310b ou 310c e pelo menos um outro condutor 310a, 310b e/ou 310c, ou pela direção de fluxo de corrente, ou falta de fluxo de corrente, no condutor 310a, 310b ou 310c. Conforme mostrado no diagrama de transição de estado 450, três estados de fase ( $S_1$ ,  $S_2$  e  $S_3$ ) são definidos. Um sinal pode fluir no sentido horário de estado de fase  $S_1$  para estado de fase  $S_2$ , estado de fase  $S_2$  para estado de fase  $S_3$ , e/ou estado de fase  $S_3$  para estado de fase  $S_1$  e o sinal pode fluir no sentido anti-horário de estado de fase  $S_1$  para estado de fase  $S_3$ , estado de fase  $S_3$  para estado de fase  $S_2$ , e/ou estado de fase  $S_2$  para estado de fase  $S_1$ . Para outros valores de  $N$ , transições entre os  $N$  estados pode opcionalmente ser definida de acordo com um diagrama de estado correspondente para obter giro circular entre transições de estado.

[0057] No exemplo de um enlace de comunicações trifásico de 3 fios, giros no sentido horário ( $S_1$  a  $S_2$ ), ( $S_2$  a  $S_3$ ), e/ou ( $S_3$  a  $S_1$ ) em uma transição de estado podem ser usados para codificar uma lógica 1, enquanto giros no sentido anti-horário ( $S_1$  a  $S_3$ ), ( $S_3$  a  $S_2$ ), e/ou ( $S_2$  a  $S_1$ ) na transição de estado podem ser usados para codificar uma lógica 0. Consequentemente um bit pode ser codificado em cada transição controlando-se se o sinal "gira" no sentido horário ou no sentido anti-horário. Por exemplo, uma lógica

1 pode ser codificada quando os três fios 310a, 310b, 310c realizam transição de estado de fase  $S_1$  para estado de fase  $S_2$  e uma lógica 0 pode ser codificada quando os três fios 310a, 310b, 310c realizam transição de estado de fase  $S_1$  para estado de fase  $S_3$ . No exemplo de três fios simples retratado, a direção de giro pode ser facilmente determinada com base em qual dos três fios 310a, 310b, e 310c está não acionado antes e depois da transição.

[0058] As informações podem também ser codificadas na polaridade dos condutores acionados 310a, 310b, e 310c ou direção de fluxo atual entre dois condutores 310a, 310b, e 310c. Os sinais 402, 404 e 406 ilustram níveis de tensão aplicados em condutores 310a, 310b e 310c, respectivamente em cada estado de fase em um enlace trifásico de 3 fios. Em qualquer momento, um primeiro condutor 310a, 310b, 310c é acoplado a uma tensão positiva (+V, por exemplo), um segundo condutor 310a, 310b, 310c é acoplado a uma tensão negativa (-V, por exemplo), enquanto o terceiro condutor 310a, 310b, 310c pode ter circuito aberto ou de outro modo ser não acionado. Sendo assim, um estado de codificação de polaridade pode ser determinado pelo fluxo de corrente entre o primeiro e o segundo condutores 310a, 310b, 310c ou as polaridades de tensão do primeiro e do segundo condutores 310a, 310b, 310c. Em algumas modalidades, dois bits de dados podem ser codificados em cada transição de fase. Um decodificador pode determinar a direção de giro de fase de sinal para obter o primeiro bit, e o segundo bit pode ser determinado com base na diferença de polaridade entre dois dos sinais 402, 404 e 406. O decodificador que determinou a direção de

giro pode determinar o estado de fase atual e a polaridade da tensão aplicada entre os dois condutores ativos 310a, 310b e/ou 310c, ou a direção de fluxo atual através dos dois condutores ativos 310a, 310b e/ou 310c.

[0059] No exemplo do enlace trifásico de 3 fios descrito no presente documento, um bit de dados pode ser codificado no giro, ou uma mudança de fase no enlace trifásico de três fios, e um bit adicional pode ser codificado na polaridade de dois fios acionados. Certas modalidades codificam mais do que dois bits em cada transição de um sistema de codificação trifásico de 3 fios permitindo-se uma transição para qualquer um dos estados possíveis de um estado atual. Dadas três fases de giro e duas polaridades para cada fase, 6 estados são definidos, de modo que 5 estados estejam disponíveis de qualquer estado atual. Consequentemente, pode haver  $\log_2(5) = 2,32$  bits por símbolo (transição) e o mapeador pode aceitar uma palavra de 16 bits e converter a mesma em 7 símbolos.

[0060] A Figura 5 é um diagrama de estado 500 que ilustra 6 estados e 30 transições de estado possíveis no exemplo de um enlace de comunicação de trifásico de 3 fios. A Figura 5 se expande no diagrama de transição de estado 450 na Figura 4 retratando-se todos os estados possíveis 502, 504, 506, 512, 514 e 516. Esses estados 502, 504, 506, 512, 514 e 516 incluem versões de polaridade positiva e polaridade negativa dos estados de fase S<sub>1</sub>, S<sub>2</sub> e S<sub>3</sub> ilustrados no diagrama de transição de fase 450 da Figura 4. A título de clareza, o conjunto de estados de fase/polaridade são rotulados de modo alfabético e inclui {+x, -x, +y, -y, +z, -z} sendo que, por exemplo, +x e -x

representam estados com o mesmo estado de fase, mas polaridade diferente. Conforme mostrado no elemento de estado modelo 520, cada estado 502, 504, 506, 512, 514 e 516 no diagrama de estado 500 inclui um campo de estados de fio 522 que mostra o estado de tensão de sinais 402, 404 e 406, que são transmitidos em fios 310a, 310b e 310c, respectivamente. Por exemplo, em estado 502 (+x), sinal 402 = +1, sinal 404 = -1 e sinal 406 = 0. Também são mostrados na Figura 5 os 5 caminhos de transição possíveis entre os estados 502, 504, 506, 512, 514 e 516, inclusive, a título de exemplo, o caminho de transição 524 entre estado -x 512 e estado -y 514.

[0061] A Figura 6 é um desenho de esquemática de blocos 600 que ilustra um exemplo que mostra certos componentes de camada física (PHY) em um receptor adaptado para se conectar a uma interface trifásica. Comparadores 602 e decodificador 604 são configurados para fornecer uma representação digital do estado de cada uma das três linhas de transmissão 612a, 612b e 612c, assim como a mudança no estado das três linhas de transmissão em comparação com o estado transmitido no período de símbolo anterior. Conforme pode ser visto do exemplo ilustrado, a tensão de cada condutor 612a, 612b ou 612c pode ser comparado às tensões dos outros dois condutores 612a, 612b e/ou 612c para determinar o estado de cada condutor 612a, 612b ou 612c, de modo que a ocorrência de uma transição possa ser detectada e decodificada pelo decodificador 604 com base nas emissões dos comparadores 602. Sete estados consecutivos são montados por conversores de série/paralelo 606, que produzem conjuntos de 7 símbolos a serem processados por um

desmapeador 608 para obter 16 bits de dados que podem ser colocados em armazenamento temporário no primeiro módulo primeiro a entrar primeiro a sair (FIFO) 610.

| Estado | Amplitude de fio |      |      | Saída Rx diferencial |      |      | Saída Digital de Receptor |       |       |

|--------|------------------|------|------|----------------------|------|------|---------------------------|-------|-------|

|        | A                | B    | C    | A-B                  | B-C  | C-A  | Rx_AB                     | Rx_BC | Rx_CA |

| +x     | +V               | 0    | +V/2 | +V                   | -V/2 | -V/2 | 1                         | 0     | 0     |

| -x     | 0                | +v   | +V/2 | -V                   | +V/2 | +V/2 | 0                         | 1     | 1     |

| +y     | +V/2             | +v   | 0    | -V/2                 | +V   | -V/2 | 0                         | 1     | 0     |

| -y     | +V/2             | 0    | +v   | +V/2                 | -V   | +V/2 | 1                         | 0     | 1     |

| +z     | 0                | +V/2 | +V   | -V/2                 | -V/2 | +V   | 0                         | 0     | 1     |

| -z     | +V               | +V/2 | 0    | +V/2                 | +V/2 | -V   | 1                         | 1     | 0     |

TABELA 1

[0062] Em referência também à Figura 5, a Tabela 1 ilustra as saídas dos receptores de diferencial 602 para cada estado de fio 522 no sistema de codificação de polaridade trifásico de 3 fios. No exemplo, os estados de fio 522 podem ser codificados na amplitude de tensão nos três fios 612a, 612b e 612c de modo que um estado +1 de um fio seja representado como uma tensão +V volts, um estado -1 do fio seja representado como 0 volts e o estado não acionado seja representado ou aproximado como +V/2 volts. Um receptor/decodificador pode ser configurado para emitir um código na saída digital do receptor para cada símbolo decodificado.

[0063] A Figura 7 inclui um diagrama de esquemática de blocos 700 que ilustra certos aspectos de um sistema de codificação de N fases e M fio e capacidades de codificação de bit para vários valores de M e configurações do sistema de codificação de N fases e M fio. Os dados

recebidos em um transmissor podem ser mapeados para uma quantidade de símbolos a ser sequencialmente transmitida por um barramento de M fio 708. O esquema de mapeamento pode determinar uma configuração para o barramento de M fio 708. Em um exemplo, uma pluralidade de conectores no barramento de M fio 708 pode portar o mesmo sinal de N fases, comutado por um ângulo de fase predeterminado. Em outro exemplo, o barramento de M fio 708 pode ser subdividido em grupos de G fios, sendo que cada grupo porta sinais de N fases diferentes. No último exemplo, um barramento de 9 fios 708 pode ser configurado com três segmentos diferentes de barramento de 3 fios. De acordo com certos aspectos, o mapeador 704 pode ser adaptado para definir dinamicamente o esquema de codificação, para reconfigurar o barramento de M fio 708 e para controlar a operação do acionador de N fases e M fio 706. Em um exemplo, o mapeador 704 pode ser adaptado para reconfigurar o sistema de codificação de N fases e M fio a fim de fornecer uma largura de banda desejada e/ou para limitar consumo de potência. Assim, o mapeador 704 pode habilitar e desabilitar de modo seletivo porções do barramento de M fio 708 quando uma demanda de largura de banda de dados é baixa, e o mapeador 704 pode habilitar porções adicionais do barramento de M fio 708 para obter largura de banda aumentada.

[0064] No receptor, os símbolos de N fases são recebidos e acumulados do barramento de M fio 708, tipicamente através de uma pluralidade de ciclos de clock de transmissão. Os símbolos acumulados podem então ser decodificados por um mapeador símbolo/bits 712. Clocks de

transmissão podem ser derivados de uma ou mais porções do barramento de M fio 708 e informações de configuração podem ser comunicadas com o uso de um grupo designado de condutores que fornecem um canal primário. No exemplo do barramento de 9 fios 708 configurado com três segmentos diferentes de barramento de 3 fios, um segmento de barramento pode ser identificado como o canal primário com um esquema de codificação padrão para ser usado durante energização e sincronização. Os comandos comunicados através do barramento podem fazer com que o transmissor e o receptor entrem em um estágio de hibernação em um ou mais dos segmentos de 3 fios.

[0065] Uma transferência de dados de N fases pode usar mais do que três fios de sinal ou outros condutores fornecidos em um meio de comunicação. O uso de fios de sinal adicionais que podem ser acionados simultaneamente fornece mais combinações de estados e polaridades e permite que mais bits de dados sejam codificados em cada transição entre estados. Isso pode aprimorar significativamente o rendimento do sistema, enquanto limita consumo de potência oposto aos enlaces de comunicações que usam múltiplos pares de diferencial para transmitir bits de dados, enquanto fornece largura de banda aumentada. Consumo de potência pode ser adicionalmente limitado configurando-se de modo dinâmico a quantidade de condutores ativos para cada transmissão.

[0066] A Figura 8 é um desenho esquemático que mostra um modelo de um codificador que transmite símbolos com o uso de 6 fios com 2 pares de fios acionados para cada estado. Os 6 fios podem ser rotulados A até F, de modo que

em um estado, fios A e F sejam acionados positivos, fios B e E negativos, e C e D não sejam acionados (ou não portem corrente). No exemplo o sinal de N fases pode ter 3 fases. Cada estado de fase pode ter uma polaridade positiva ou negativa. No modelo ilustrativo, cada fio pode ser conectado a uma fonte de corrente positiva, uma fonte de corrente negativa, ou nenhuma fonte de corrente. A corrente flui através de um fio que tem uma impedância  $Z_0$  que é tipicamente a impedância característica do fio de transmissão. Conforme mostrado na Figura 8, as correntes positivas são canceladas por duas correntes negativas.

[0067] Para seis fios, pode haver:

$$C(6,4) = \frac{6!}{(6-4)! \cdot 4!} = 15$$

[0068] combinações possíveis de fios acionados de modo ativo, com:

$$C(4,2) = \frac{4!}{(4-2)! \cdot 2!} = 6$$

[0069] combinações diferentes de polaridade para cada estado de fase.

[0070] As 15 combinações diferentes de fios acionados de modo ativo podem incluir:

|                |                |                |                |                |

|----------------|----------------|----------------|----------------|----------------|

| <b>A B C D</b> | <b>A B C E</b> | <b>A B C F</b> | <b>A B D E</b> | <b>A B D F</b> |

| <b>A B E F</b> | <b>A C D E</b> | <b>A C D F</b> | <b>A C E F</b> | <b>A D E F</b> |

| <b>B C D E</b> | <b>B C D F</b> | <b>B C E F</b> | <b>B D E F</b> | <b>C D E F</b> |

[0071] Dos 4 fios acionados, as combinações possíveis de dois fios acionados positivos (e os outros

dois precisam ser negativos). As combinações de polaridade podem incluir:

+ + - -      + - - +      + - + -      - + - +      - + + -      - - + +

Consequentemente, a quantidade total de estados diferentes pode ser calculada como  $15 \times 6 = 90$ . Para garantir uma transição entre símbolos sucessivos, 89 estados estão disponíveis para transição de qualquer estado atual, e a quantidade de bits que pode ser codificado em cada símbolo pode ser calculada como:  $\log_2(89) = 6,47$  bits por símbolo. Nesse exemplo, uma palavra de 32 bits pode ser codificada pelo mapeador em 5 símbolos, dado que  $5 \times 6,47 = 32,35$  bits.

[0072] A equação geral para a quantidade de combinações de fios que podem ser acionados para um barramento de qualquer tamanho, como uma função da quantidade de fios no barramento e a quantidade de fios simultaneamente acionados:

$$C(N_{wires}, N_{driven}) = \frac{N_{wires}!}{(N_{wires} - N_{driven})! \cdot N_{driven}!}$$

[0073] A equação para a quantidade de combinações de polaridade para os fios que são acionados é:

$$C\left(N_{driven}, \frac{N_{driven}}{2}\right) = \frac{N_{driven}!}{\left(\left(\frac{N_{driven}}{2}\right)!\right)^2}$$

[0074] A quantidade de bits por símbolo é:

$$\log_2 \left( C(N_{wires}, N_{driven}) \cdot C\left(N_{driven}, \frac{N_{driven}}{2}\right) - 1 \right)$$

[0075] A Figura 7 inclui um gráfico 720 que mostra codificação de bit para vários valores de M (isto é,

quantidades de fios) e configurações de fios e pares de fios.

[0076] Em algumas modalidades, um codificador pode ser configurado para aumentar a quantidade de fios usados para codificação de  $N$  fases quando largura de banda aumentada é exigida. A largura de banda pode mudar quando, por exemplo, um clipe de vídeo for exibido para um usuário do aparelho 100, ou quando uma rajada de dados for transferida entre circuitos de processamento e/ou dispositivos de memória. Mudanças em largura de banda também podem se corresponder ou relacionar com medidas de controle de potência assim como necessidades específicas de aplicação. Por exemplo, o aparelho da Figura 2 pode reconfigurar de modo dinâmico os enlaces 220 para iniciar medidas de economia de potência que pode conservar vida útil de bateria quando uma demanda por largura de banda é reduzida.

[0077] Quando uma largura de banda aumentada ou diminuída é exigida ou solicitada, um codificador pode aumentar ou diminuir a quantidade de condutores ativos para ser usado para codificação de  $N$  fases. Tal codificação adaptativa pode permitir a provisão de economia de potência de largura variável. Em um exemplo, fios adicionais podem ser adicionados em unidades atômicas. Uma unidade atômica pode incluir três fios que empregam codificação de polaridade trifásica (descrito no presente documento). Em outro exemplo, estados de codificação adicionais podem ser definidos adicionando-se pares de fios em um barramento de  $N$  fases e  $M$  fio. Em outro exemplo, estados de codificação adicionais podem ser obtidos adicionando-se um único fio,

através do qual dois fios não são acionados para cada estado. A adição de um fio não acionado pode aumentar consumo de potência menos do que adicionar um par de fios acionados.

[0078] A Figura 9 ilustra um modelo de um circuito de codificação de polaridade trifásico de 3 fios. Uma corrente é passada através de dois dentre três fios de sinal através de terminais correspondentes 902, 904 e/ou 906 que podem ser conectados a fios que têm uma impedância característica ( $Z^0$ ). Em um aspecto, nenhuma corrente é passada através do terceiro fio de sinal. No entanto, em outros aspectos, uma corrente pode ser passada através do terceiro fio de sinal. Conforme discutido no presente documento, cada estado de fase pode ser definido de modo a ter uma polaridade positiva ou uma polaridade negativa, embora o exemplo na Figura 9 retrate apenas a condição de polaridade positiva de cada estado de fase para simplificar a descrição. Para obter um estado "+x" 910, uma corrente é passada 924, 926, 928 de terminal 902 para terminal 904. Para obter um estado "+y" 930, uma corrente é passada 932, 934, 936 de terminal 904 para terminal 906. Para obter um estado "+z" 940, uma corrente é passada 942, 944, 946 de terminal 906 para terminal 902. O sinal não acionado pode ser puxado em direção a uma tensão neutra por resistores de terminação no receptor.

[0079] De acordo com certos aspectos revelados no presente documento, uma interface de camada física de N fases (PHY de N fases) e M fio é fornecida para suportar um canal multifásico. Referindo-se novamente à Figura 4, em um exemplo um sinal trifásico 402, 404, 406 fornecido em um

fio 310a, 310b, 310c é definido por dois sinais ativos de polaridade oposta e um sinal não acionado no qual nenhuma corrente é transmitida e/ou o fio 310a, 310b, 310c tem circuito aberto. Uma PHY trifásica pode codificar e decodificar o sinal trifásico fazendo com que o sinal não acionado realize transição para uma tensão neutra (por exemplo, 0 volts) em ambas as extremidades do circuito de linha de transmissão para impedir fluxo de corrente.

AMBIENTE OPERACIONAL EXEMPLIFICATIVO PARA ACIONAR UM FIO DE SINAL EM UM ENLACE DE COMUNICAÇÃO TRIFÁSICO

[0080] A Figura 10 ilustra um exemplo de uma interface de linha 1000 que pode ser usada para acionar um fio de sinal em uma PHY trifásica. Em um exemplo, um transistor 1002 recebe um sinal pull-up e um transistor 1004 recebe um sinal pull-down. Quando o terminal de saída 1006 for acionado para um estado de sinalização ativo (+1 ou -1), um dos transistores 1002 ou 1004 é ligado e o terminal de saída 1006 é acionado de modo ativo para um estado de sinalização ou o outro. Quando o terminal de saída 1006 for não acionado e em um estado de sinalização inativo (0), nem o controle pull-up nem o pull-down é ativo e ambos os transistores 1002 e 1004 são desligados. O terminal de saída 1006 se assenta tipicamente no nível de modo comum de linhas acionadas quando ambos os transistores 1002 e 1004 são desligados para obter um estado de sinalização inativo (0). No entanto, o tempo de assentamento pode resultar em tempos de desvio que não são mais para estados não acionados do que para estados que sãoativamente acionados por um transistor 1002 ou 1004. O tempo de assentamento e o tempo de desvio correspondente

podem ser aprimorados terminando-se a linha de transmissão ou o terminal 1006. Em um exemplo, um par de impedâncias, que pode ser resistivo, ou outras cargas podem ser fornecidas no transmissor ou no receptor para fazer com que um fio de sinal ou terminal 1006 adquira mais rapidamente um nível de tensão neutra e para manter o fio de sinal ou terminal 1006 na tensão neutra.

[0081] Uma interface de série de alta velocidade, tal como uma interface C-PHY (C-PHY), fornece alto rendimento através de canais limitados de largura de banda para se conectar a periféricos, inclusive visores e câmeras. C-PHY pode usar codificação trifásica e transmite símbolos através de faixas de três fios (ou trios) para render uma transferência eficaz de 2,28 bits por símbolo. Em um trio de três fios, dois dos três fios podem ser acionados para níveis opostos (por exemplo, nível alto e nível baixo) enquanto um terceiro fio pode ser terminado em um nível médio (nível de modo comum), e as tensões nas quais os fios são acionados muda em cada símbolo.

[0082] Topologias tradicionais de acionador de C-PHY, ou não acionam a tensão de nível médio, ou incorrem em penalidade de área e potência em acionar a tensão de nível médio com o uso de segmentos de circuito adicionais que continuam a consumir potência mesmo após a tensão de nível médio ser alcançada. Em um aspecto, um transmissor trifásico C-PHY pode exigir que um acionador possa acionar uma tensão de nível alto, baixo ou médio (modo comum) sobre o canal de transmissão. Se o acionador não pode acionar a tensão de nível médio (modo comum), as taxas de dados alcançáveis pelo acionador podem ser severamente limitadas.

Ademais, o acionador pode ser tornado não usável em aplicações de potência menor que não usam terminação de lado de receptor. No entanto, acionar a tensão de nível médio pode introduzir um fardo adicional no projeto do acionador e resulta em aumento de consumo de potência e área do acionador. Para aplicações de menos potência e desempenho, a potência adicional é indesejável. Consequentemente, para ajudar a aliviar esse fardo, a presente revelação fornece novas topologias de acionador de C-PHY que podem ser usadas com ou sem terminação de trio de lado de receptor. Utilizar as novas topologias de acionador de C-PHY com terminação de lado de receptor permite aplicações de taxa de dados maior enquanto diminui potência em comparação com abordagens tradicionais. Utilizar as novas topologias de acionador de C-PHY sem terminação de lado de receptor podem limitar taxas de dados, mas fornece economias adicionais de potência.

[0083] A Figura 11 ilustra um primeiro exemplo 1100 de interfaces de linha usadas para acionar três fios de sinal em um sistema trifásico. A Figura 12 ilustra um segundo exemplo 1200 de interfaces de linha usadas para acionar três fios de sinal em um sistema trifásico. No primeiro exemplo 1100 da Figura 11, um acionador de modo de tensão (transmissor) 1120 utiliza terminação de receptor (RX), em que impedâncias podem ser fornecidas em um receptor 1140 para fazer com que linhas de transmissão 1130 ou terminais de saída 1122, 1124 e 1126 a adquirir mais rapidamente uma tensão de nível médio e manter as linhas de transmissão 1130 ou os terminais de saída 1122, 1124, e 1126 na tensão de nível médio. Conforme mostrado na Figura

11, as linhas de transmissão 1130 podem ter impedâncias características de 50 Ohms, e o receptor 1140 pode terminar com as linhas de transmissão 1130 com o uso de impedâncias de 50 Ohm. No entanto, a terminação no receptor 1140 não é limitada ao uso de impedâncias de 50 Ohm visto que vários outros valores de impedância podem ser usados em concordância com a presente revelação. O segundo exemplo 1200 da Figura 12 pode ter uma arquitetura que é quase idêntica à arquitetura do primeiro exemplo 1100 exceto que o acionador de modo de tensão (transmissor) 1120 não utiliza terminação RX (denominada "não-terminação RX (RX-untermination)" na Figura 12). Por isso, no segundo exemplo 1200, as impedâncias não são fornecidas em um lado de receptor para fazer com que as linhas de transmissão 1130 (ou os terminais de saída 1122, 1124, e 1126) adquiram mais rapidamente uma tensão de nível médio e/ou mantenham as linhas de transmissão 1130 (ou os terminais de saída 1122, 1124, e 1126) na tensão de nível médio.

[0084] Tanto para o primeiro exemplo 1100 (caso de terminação RX) e o segundo exemplo 1200 (caso de não-terminação RX), as interfaces de linha que acionam os três fios de sinal (isto é, terminais de saída 1122, 1124, e 1126) operam em uma maneira similar. Portanto, a descrição abaixo em relação ao acionamento dos terminais de saída pelas interfaces de linha se aplica tanto ao primeiro exemplo 1100 quanto ao segundo exemplo 1200.

[0085] Em um aspecto, o acionador de modo de tensão 1120 usa um segmento de pull-up (ou acionador) e um segmento de pull-down (ou acionador) para acionar um terminal de saída associado em direção a uma tensão de

nível alto e uma tensão de nível baixo. O acionador de modo de tensão 1120 adicionalmente usa segmentos adicionais (ou acionadores) dedicados a acionar terminais de saída associados em direção a uma tensão de nível médio. Os segmentos adicionais puxam tensões para cima e/ou para baixo entre um primeiro sinal de tensão usado para acionar um primeiro terminal de saída que não seja um terminal de saída associado em direção a uma tensão de nível alto/baixo e um segundo sinal de tensão usado para acionar um segundo terminal de saída que não seja o terminal de saída associado em direção a uma tensão de nível alto/baixo.

[0086] O acionador de modo de tensão 1120 pode incluir um segmento (ou acionador) A1 para acionar um primeiro terminal de saída 1122 em direção a uma tensão de nível alto e uma tensão de nível baixo. O segmento A1 inclui um transistor pull-up 1102 configurado para receber um primeiro sinal pull-up (Pu\_a) e um transistor pull-down 1104 configurado para receber um primeiro sinal pull-down (Pd\_a). Quando o primeiro terminal de saída 1122 for acionado em direção à tensão de nível alto (por exemplo, estado de sinalização +1), o segmento A1 é configurado para emitir um sinal de tensão que corresponde à tensão de nível alto ligando-se o transistor pull-up 1102 e desligando-se o transistor pull-down 1104, e assim faz com que o primeiro terminal de saída 1122 seja acionado de modo ativo em direção à tensão de nível alto. Quando o primeiro terminal de saída 1122 for acionado em direção à tensão de nível baixo (por exemplo, estado de sinalização -1), o segmento A1 é configurado para emitir um sinal de tensão que corresponde à tensão de nível baixo ligando-se o transistor

pull-down 1104 e desligando-se o transistor pull-up 1102, e assim faz com que o primeiro terminal de saída 1122 seja acionado de modo ativo em direção à tensão de nível baixo. Quando o primeiro terminal de saída 1122 for acionado em direção à tensão de nível médio (por exemplo, estado de sinalização 0), tanto o transistor pull-up 1102 quanto o transistor pull-down 1104 são desligados.

[0087] O acionador de modo de tensão 1120 pode adicionalmente incluir um segmento (ou acionador) B1 para acionar um segundo terminal de saída 1124 em direção a uma tensão de nível alto e uma tensão de nível baixo. O segmento B1 inclui um transistor pull-up 1106 configurado para receber um segundo sinal pull-up ( $Pu_b$ ) e um transistor pull-down 1108 configurado para receber um segundo sinal pull-down ( $Pd_b$ ). Quando o segundo terminal de saída 1124 for acionado em direção à tensão de nível alto (por exemplo, estado de sinalização +1), o segmento B1 é configurado para emitir um sinal de tensão que corresponde à tensão de nível alto ligando-se o transistor pull-up 1106 e desligando-se o transistor pull-down 1108, e assim faz com que o segundo terminal de saída 1124 seja acionado de modo ativo em direção à tensão de nível alto. Quando o segundo terminal de saída 1124 for acionado em direção à tensão de nível baixo (por exemplo, estado de sinalização -1), o segmento B1 é configurado para emitir um sinal de tensão que corresponde à tensão de nível baixo ligando-se o transistor pull-down 1108 e desligando-se o transistor pull-up 1106, e assim faz com que o segundo terminal de saída 1124 seja acionado de modo ativo em direção à tensão de nível baixo. Quando o segundo terminal

de saída 1124 for acionado em direção à tensão de nível médio (por exemplo, estado de sinalização 0), tanto o transistor pull-up 1106 quanto o transistor pull-down 1108 são desligados.

[0088] O acionador de modo de tensão 1120 pode também incluir um segmento (ou acionador) C1 para acionar um terceiro terminal de saída 1126 em direção a uma tensão de nível alto e uma tensão de nível baixo. O segmento C1 inclui um transistor pull-up 1110 configurado para receber um terceiro sinal pull-up ( $P_{u\_c}$ ) e um transistor pull-down 1112 configurado para receber um terceiro sinal pull-down ( $P_{d\_c}$ ). Quando o terceiro terminal de saída 1126 for acionado em direção à tensão de nível alto (por exemplo, estado de sinalização +1), o segmento C1 é configurado para emitir um sinal de tensão que corresponde à tensão de nível alto ligando-se o transistor pull-up 1110 e desligando-se o transistor pull-down 1112, e assim faz com que o terceiro terminal de saída 1126 seja acionado de modo ativo em direção à tensão de nível alto. Quando o terceiro terminal de saída 1126 for acionado em direção à tensão de nível baixo (por exemplo, estado de sinalização -1), o segmento C1 é configurado para emitir um sinal de tensão que corresponde à tensão de nível baixo ligando-se o transistor pull-down 1112 e desligando-se o transistor pull-up 1110, e assim faz com que o terceiro terminal de saída 1126 seja acionado de modo ativo em direção à tensão de nível baixo. Quando o terceiro terminal de saída 1126 for acionado em direção à tensão de nível médio (por exemplo, estado de sinalização 0), tanto o transistor pull-up 1110 quanto o transistor pull-down 1112 são desligados.

[0089] O acionador de modo de tensão 1120 pode adicionalmente incluir segmentos adicionais (ou acionadores) dedicados a acionar respectivos terminais de saída em direção à tensão de nível médio. Por exemplo, o segmento (ou acionador) A2 aciona o primeiro terminal de saída 1122 em direção à tensão de nível médio, o segmento (ou acionador) B2 aciona o segundo terminal de saída 1124 em direção à tensão de nível médio, e o segmento (ou acionador) C2 aciona o terceiro terminal de saída 1126 em direção à tensão de nível médio.

[0090] Como um exemplo, uma operação para acionar um terminal de saída em direção à tensão de nível médio será primeiro descrito em relação ao segmento B2 configurado para acionar o segundo terminal de saída 1124 em direção à tensão de nível médio. Notavelmente, a operação para acionar o primeiro terminal de saída 1122 com o uso do segmento A2 e a operação para acionar o terceiro terminal de saída 1126 com o uso do segmento C2 é similar à operação descrita para acionar o segundo terminal de saída 1124 com o uso do segmento B2.

[0091] O segmento B2 é configurado para receber um sinal pull-middle (Pm\_b). O segmento B2 inclui um transistor 1114 configurado para emitir um sinal de tensão com base em um sinal de tensão recebido do segmento A1 e um transistor 1116 configurado para emitir um sinal de tensão com base em um sinal de tensão recebido do segmento C1. Quando o segundo terminal de saída 1124 for acionado em direção à tensão de nível médio (por exemplo, estado de sinalização 0), o transistor 1114 recebe do segmento A1 um sinal de tensão destinado a acionar o primeiro terminal de

saída 1122 em direção ao nível de tensão alto ou nível de tensão baixo. De modo concomitante, o transistor 1116 recebe do segmento C1 um sinal de tensão destinado a acionar o terceiro terminal de saída 1126 em direção ao nível de tensão alto ou nível de tensão baixo. Mediante recebimento dos sinais de tensão do segmento A1 e do segmento C1, o transistor 1114 e o transistor 1116 são respectivamente ativados (ligados) e juntos acionam o segundo terminal de saída 1124 em direção a um nível de tensão em uma faixa de tensão limitada pelo nível de tensão alto (relacionado ao primeiro terminal de saída 1122 ou ao terceiro terminal de saída 1126) e o nível de tensão baixo (relacionado ao primeiro terminal de saída 1122 ou ao terceiro terminal de saída 1126). Em um aspecto, o segmento B2 é desligado quando o segmento B1 aciona o segundo terminal de saída 1124 em direção a um nível de tensão alto ou um nível de tensão baixo.

[0092] O segmento A2 é configurado para receber um sinal pull-middle (Pm\_a). O segmento A2 inclui um transistor 1154 configurado para emitir um sinal de tensão com base em um sinal de tensão recebido do segmento B1 e um transistor 1156 configurado para emitir um sinal de tensão com base em um sinal de tensão recebido do segmento C1. Quando o primeiro terminal de saída 1122 for acionado em direção à tensão de nível médio (por exemplo, estado de sinalização 0), o transistor 1154 recebe do segmento B1 um sinal de tensão destinado a acionar o segundo terminal de saída 1124 em direção ao nível de tensão alto ou nível de tensão baixo. De modo concomitante, o transistor 1156 recebe do segmento C1 um sinal de tensão destinado a

acionar o terceiro terminal de saída 1126 em direção ao nível de tensão alto ou nível de tensão baixo. Mediante recebimento dos sinais de tensão do segmento B1 e o segmento C1, o transistor 1154 e o transistor 1156 são respectivamente ativados (ligados) e juntos acionam o primeiro terminal de saída 1122 em direção a um nível de tensão em uma faixa de tensão limitada pelo nível de tensão alto (relacionado ao segundo terminal de saída 1124 ou ao terceiro terminal de saída 1126) e pelo nível de tensão baixo (relacionado ao segundo terminal de saída 1124 ou ao terceiro terminal de saída 1126). Em um aspecto, o segmento A2 é desligado quando o segmento A1 aciona o primeiro terminal de saída 1122 em direção a um nível de tensão alto ou um nível de tensão baixo.

[0093] O segmento C2 é configurado para receber um sinal pull-middle (Pm\_c). O segmento C2 inclui um transistor 1164 configurado para emitir um sinal de tensão com base em um sinal de tensão recebido do segmento A1 e um transistor 1166 configurado para emitir um sinal de tensão com base em um sinal de tensão recebido do segmento B1. Quando o terceiro terminal de saída 1126 for acionado em direção à tensão de nível médio (por exemplo, estado de sinalização 0), o transistor 1164 recebe do segmento A1 um sinal de tensão destinado a acionar o primeiro terminal de saída 1122 em direção ao nível de tensão alto ou nível de tensão baixo. De modo concomitante, o transistor 1166 recebe do segmento B1 um sinal de tensão destinado a acionar o segundo terminal de saída 1124 em direção ao nível de tensão alto ou nível de tensão baixo. Mediante recebimento dos sinais de tensão do segmento A1 e o

segmento B1, o transistor 1164 e o transistor 1166 são respectivamente ativados (ligados) e juntos açãoam o terceiro terminal de saída 1126 em direção a um nível de tensão em uma faixa de tensão limitada pelo nível de tensão alto (relacionado ao primeiro terminal de saída 1122 ou ao segundo terminal de saída 1124) e pelo nível de tensão baixo (relacionado ao primeiro terminal de saída 1122 ou ao segundo terminal de saída 1124). Em um aspecto, o segmento C2 é desligado quando o segmento C1 açãoa o terceiro terminal de saída 1126 em direção a um nível de tensão alto ou um nível de tensão baixo.