(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6989552号

(P6989552)

(45) 発行日 令和4年1月5日(2022.1.5)

(24) 登録日 令和3年12月6日(2021.12.6)

(51) Int.Cl.

G06N 3/063 (2006.01)

F 1

G 06 N 3/063

請求項の数 12 (全 16 頁)

(21) 出願番号 特願2019-49872 (P2019-49872)

(22) 出願日 平成31年3月18日 (2019.3.18)

(65) 公開番号 特開2020-154412 (P2020-154412A)

(43) 公開日 令和2年9月24日 (2020.9.24)

審査請求日 令和2年8月21日 (2020.8.21)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 110002147

特許業務法人酒井国際特許事務所

(72) 発明者 丸亀 孝生

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 棚本 哲史

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 西 義史

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】 ニューラルネットワーク装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のニューロン回路を備えるニューラルネットワーク装置であって、

前記複数のニューロン回路のそれぞれは、

前段のニューロン回路から発生されたパルス信号に係数を乗算した値を表す入力信号を積分した積分信号を出力する積分回路と、

前記積分信号に応じて、後段のニューロン回路へと伝達される前記パルス信号を発生する発火回路と、

前記発火回路から前記パルス信号を発生させるための駆動電力を、前記発火回路に供給する二次電池と、

前記二次電池の電源電圧の増減に応じて、前記入力信号に対応する前記係数を更新する係数更新回路と、

を有するニューラルネットワーク装置。

## 【請求項 2】

前記ニューラルネットワーク装置は、複数のシナプス回路をさらに備え、

前記複数のニューロン回路のそれぞれは、前記複数のシナプス回路のうちの、2以上のシナプス回路が対応付けられ、対応付けられた前記2以上のシナプス回路から2以上の前記入力信号を取得し、

前記2以上のシナプス回路のそれぞれは、

前記係数が設定されており、

10

20

前記複数のニューロン回路のうちの何れか1つの前段のニューロン回路により発生された前記パルス信号を受け取り、

受け取った前記パルス信号と設定されている前記係数とを乗じた値を表す前記入力信号を生成し、

生成した前記入力信号を、対応する前記ニューロン回路に与える

請求項1に記載のニューラルネットワーク装置。

#### 【請求項3】

前記積分回路は、対応付けられた前記2以上のシナプス回路から取得した2以上の前記入力信号を積分する

請求項2に記載のニューラルネットワーク装置。

10

#### 【請求項4】

複数のニューロン回路と、

複数のシナプス回路と、

を備え、

前記複数のニューロン回路のそれぞれは、前記複数のシナプス回路のうちの、2以上のシナプス回路が対応付けられ、対応付けられた前記2以上のシナプス回路から2以上の入力信号を取得し、

前記2以上のシナプス回路のそれぞれは、

係数が設定されており、

前記複数のニューロン回路のうちの何れか1つの前段のニューロン回路により発生されたパルス信号を受け取り、

20

受け取った前記パルス信号と設定されている前記係数とを乗じた値を表す前記入力信号を生成し、

生成した前記入力信号を、対応する前記ニューロン回路に与え、

前記複数のニューロン回路のそれぞれは、

対応付けられた前記2以上のシナプス回路から取得した2以上の前記入力信号を積分した積分信号を出力する積分回路と、

前記積分信号に応じて、後段のニューロン回路へと伝達される前記パルス信号を発生する発火回路と、

前記発火回路から前記パルス信号を発生させるための駆動電力を、前記発火回路に供給する二次電池と、

30

係数更新回路と、

を有し、

前記二次電池は、前記発火回路から前記パルス信号が出力されたことに応じて、発生する電源電圧が減少し、

前記係数更新回路は、前記電源電圧の減少に応じて、対応付けられた前記2以上のシナプス回路のうちの前記入力信号を与えた対象のシナプス回路に設定されている前記係数を更新する

ニユーラルネットワーク装置。

#### 【請求項5】

前記係数更新回路は、前記電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、前記対象のシナプス回路に設定されている前記係数を更新する

請求項4に記載のニューラルネットワーク装置。

40

#### 【請求項6】

前記係数更新回路は、前記電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、前記対象のシナプス回路に前記電源電圧を印加する

請求項4に記載のニューラルネットワーク装置。

#### 【請求項7】

前記係数更新回路は、

更新回路内二次電池を含み、

50

前記電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、前記対象のシナプス回路に前記更新回路内二次電池から発生された電圧を印加する

請求項 4 に記載のニューラルネットワーク装置。

**【請求項 8】**

前記複数のシナプス回路のそれぞれは、印加された電圧に応じてコンダクタンスを変化させる抵抗変化メモリ素子を有し、

前記抵抗変化メモリ素子は、前記コンダクタンスが前記係数を表し、

前記抵抗変化メモリ素子は、前記前段のニューロン回路により発生された前記パルス信号のタイミングで電圧が印加され、

前記複数のシナプス回路のそれぞれは、前記抵抗変化メモリ素子に流れる電流を、前記入力信号として、対応する前記ニューロン回路に与える

請求項 4 に記載のニューラルネットワーク装置。

**【請求項 9】**

前記係数更新回路は、

前記電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、前記対象のシナプス回路が有する前記抵抗変化メモリ素子に、前記二次電池から発生される前記電源電圧を印加し、

前記電源電圧が予め定められた閾値以下または予め定められた閾値以上ではない場合、前記対象のシナプス回路が有する前記抵抗変化メモリ素子と、前記二次電池との間を切断する

請求項 8 に記載のニューラルネットワーク装置。

**【請求項 10】**

前記係数更新回路は、

更新回路内二次電池を含み、

前記電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、前記対象のシナプス回路が有する前記抵抗変化メモリ素子に、前記更新回路内二次電池から発生される電圧を印加し、

前記電源電圧が予め定められた閾値以下または予め定められた閾値以上ではない場合、前記対象のシナプス回路が有する前記抵抗変化メモリ素子と、前記更新回路内二次電池との間を切断する

請求項 8 に記載のニューラルネットワーク装置。

**【請求項 11】**

前記複数のニューロン回路のそれぞれが有する前記二次電池を充電する充電回路をさらに備える

請求項 1 から 10 の何れか 1 項に記載のニューラルネットワーク装置。

**【請求項 12】**

前記充電回路は、前記二次電池を定期的に充電する

請求項 11 に記載のニューラルネットワーク装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の実施形態は、ニューラルネットワーク装置に関する。

**【背景技術】**

**【0002】**

近年、ハードウェア化したニューラルネットワークを用いて、脳型プロセッサを実現する技術が提案されている。脳型プロセッサは、人工ニューロンを有する。人工ニューロンは、他のニューロンからシナプスを介して信号を受け取り、受け取った信号が閾値を超えると発火をする。人工ニューロンは、この発火をするために電力を消費する。

**【0003】**

人体のニューロンは、血液により運ばれた糖質および酸素によってエネルギーを作り出

10

20

30

40

50

す、と推定される。つまり、個々のニューロンは、電力を発生するエネルギー源としても機能している。脳型プロセッサは、人体のニューロンと同様の形態でエネルギー源を有することが脳を模擬するために好ましい、と考えられる。

#### 【0004】

また、脳は、スパイクタイミング依存シナプス可塑性（S T D P）と呼ばれる学習規則が存在する、と推定されている。S T D Pは、ニューロン発火のタイミングによってシナプス強度が変更される学習規則である。従来、このようなS T D Pを模擬する脳型プロセッサは、人工ニューロンとは別に、ニューロン発火のタイミングをシナプスにフィードバックするパスを有する。しかしながら、人体の脳には、ニューロンとは別のフィードバックパスは存在していない、と推定される。また、人工ニューロンとは別のフィードバックパスを備えた場合、脳型プロセッサは、回路規模が大きくなってしまう。10

#### 【先行技術文献】

##### 【特許文献】

##### 【0005】

【特許文献1】米国特許出願公開第2018/0247179号明細書

【特許文献2】特開2017-228295号公報

##### 【非特許文献】

##### 【0006】

【非特許文献1】Irem Boybat et al., “Neuromorphic computing with multi-memristive synapses”, Nature Communications volume 9 page 2514 (2018) 20

【非特許文献2】Abu Sebastian et al., “Brain-inspired computing using phase-change memory devices”, JOURNAL OF APPLIED PHYSICS 124, 111101 (2018)

【非特許文献3】Stanislaw Wozniak et al., “Neuromorphic Architecture With 1M Memristive Synapses for Detection of Weakly Correlated Inputs”, IEEE Transactions on Circuits and Systems II: Express Briefs, Volume: 64 Issue:11, Nov.2017

【非特許文献4】Wei Wang et al., “Learning of spatiotemporal patterns in a spiking neural network with resistive switching synapses”, Science Advances 2018:Vol.4:no.9:eaat4752, American Association for the Advancement of Science 30

【非特許文献5】Yusuke Nishitani et al., “Three-terminal ferroelectric synapse device with concurrent learning function for artificial neural networks”, Journal of Applied Physics 111, 124108 (2012)”, 22 June. 2012

【非特許文献6】Xinyu Wu et al., “A CMOS Spiking Neuron for Brain-Inspired Neural Networks With Resistive Synapses and In Situ Learning”, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, VOL. 62, NO. 11, November 2015

【非特許文献7】Atsuya Sasaki et al., “Fabrication of solid-state secondary battery using semiconductors and evaluation of its charge/discharge characteristics”, Japanese Journal of Applied Physics, 57, 041201 (2018), 3 March 2018 40

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0007】

本発明が解決しようとする課題は、人体のニューロンと同様の形態でエネルギー源を有することができるニューラルネットワーク装置を提供することにある。

#### 【課題を解決するための手段】

##### 【0008】

実施形態に係るニューラルネットワーク装置は、複数のニューロン回路を備える。前記複数のニューロン回路のそれぞれは、積分回路と、発火回路と、二次電池と、係数更新回路と、を有する。前記積分回路は、前段のニューロン回路から発生されたパルス信号に係数を乗算した値を表す入力信号を積分した積分信号を出力する。前記発火回路は、前記積分信号に応じて、後段のニューロン回路へと伝達される前記パルス信号を発生する。前記二次電池は、前記発火回路から前記パルス信号を発生させるための駆動電力を、前記発火回路に供給する。前記係数更新回路は、前記二次電池の電源電圧の増減に応じて、前記入力信号に対応する前記係数を更新する。

**【図面の簡単な説明】**

**【0009】**

10

【図1】実施形態に係るニューラルネットワーク装置の構成図。

【図2】演算部の構成図。

【図3】ニューロン回路およびシナップス回路の構成図。

【図4】ニューロン回路およびシナップス回路の信号波形図。

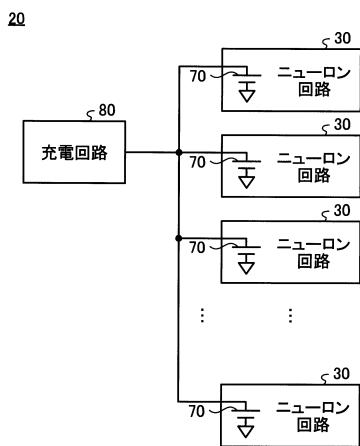

【図5】充電回路を備える演算部の構成図。

【図6】変形例に係るニューロン回路およびシナップス回路の構成図。

【図7】変形例に係るニューロン回路およびシナップス回路の信号波形図。

**【発明を実施するための形態】**

**【0010】**

20

以下、図面を参照しながら実施形態に係るニューラルネットワーク装置10について説明する。実施形態に係るニューラルネットワーク装置10は、人体のニューロンと同様の形態でエネルギー源を有することができる。さらに、実施形態に係るニューラルネットワーク装置10は、ニューロンとは別のフィードバックバスを有さずに、ニューロン発火のタイミングをフィードバックすることができる。

**【0011】**

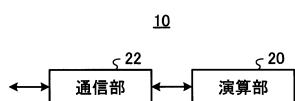

図1は、実施形態に係るニューラルネットワーク装置10の構成を示す図である。ニューラルネットワーク装置10は、演算部20と、通信部22とを備える。演算部20および通信部22は、1つの半導体装置に実装されてもよいし、複数の半導体装置に分散して実装されていてもよい。

**【0012】**

30

ニューラルネットワーク装置10は、外部装置から入力データを受信する。ニューラルネットワーク装置10は、受信した入力データに対してニューラルネットワークに従った演算処理を実行する。そして、ニューラルネットワーク装置10は、ニューラルネットワークに従った演算処理の結果である出力データを外部装置に送信する。

**【0013】**

演算部20は、ニューラルネットワークに基づく通常の演算処理をハードウェア回路により実行する。演算部20は、例えば、ニューラルネットワークに基づく通常の演算処理として、パターン認識処理、データ解析処理および制御処理等の様々な情報処理を実行する。

**【0014】**

40

また、演算部20は、通常の演算処理と並行して、学習処理を実行する。演算部20は、学習処理により、通常の演算処理をより適切に行うように、ニューラルネットワークに含まれる複数の係数（重み）を変更する。例えば、演算部20は、STDPの学習規則を模擬した学習処理により、複数の係数を変更する。

**【0015】**

通信部22は、外部装置とデータを送受信する。具体的には、通信部22は、外部装置から、演算対象となる入力データを受信する。また、通信部22は、外部装置へ、演算結果である出力データを送信する。

**【0016】**

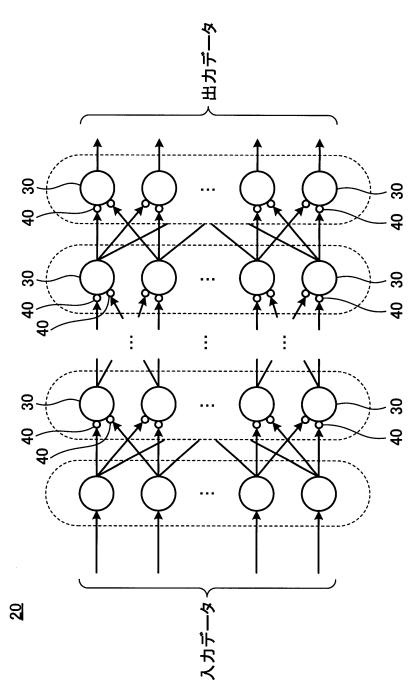

図2は、演算部20の構成を示す図である。演算部20は、受信した入力データに対し

50

てニューラルネットワークに従った演算処理を実行する。

**【0017】**

ニューラルネットワークは、複数の層を含む。複数の層のそれぞれは、受け取ったデータに対して所定の演算および処理をする。ニューラルネットワークに含まれる複数の層のそれぞれは、複数のノードを含む。複数のノードのそれぞれは、ニューロンに相当する。1つの層に含まれるノードの数は、層毎に異なってもよい。

**【0018】**

また、ニューラルネットワークは、前段の層に含まれる複数のノードのそれから、次段の層に含まれる複数のノードの全てへと信号を伝播する複数のリンクを含む。複数のリンクのそれぞれは、シナプスに相当する。また、複数のリンクのそれぞれは、係数が設定されている。係数は、信号の伝達のしやすさを表すシナプス強度に相当する。

10

**【0019】**

演算部20は、複数のノードに対応する機能として、ハードウェアにより実現された複数のニューロン回路30を備える。さらに、演算部20は、複数のリンクに対応する機能として、ハードウェアにより実現された複数のシナプス回路40も備える。

**【0020】**

複数のニューロン回路30のそれぞれは、複数のシナプス回路40のうちの2以上のシナプス回路40が、対応付けられている。1つのニューロン回路30に対応付けられている2以上のシナプス回路40は、前段の層に含まれる2以上のニューロン回路30と一一の一の関係となっている。つまり、1つのニューロン回路30に対応付けられているシナプス回路40の数は、前段の層に含まれるニューロン回路30の数と同一である。

20

**【0021】**

複数のニューロン回路30のそれぞれは、対応付けられた2以上のシナプス回路40から2以上の入力信号を取得する。そして、複数のニューロン回路30のそれぞれは、取得した2以上の入力信号に応じて、発火する。複数のニューロン回路30のそれぞれは、発火した場合、パルス信号を発生する。

**【0022】**

複数のシナプス回路40のそれぞれは、係数が設定されている。複数のシナプス回路40のそれぞれは、前段のニューロン回路30により発生されたパルス信号を受け取る。複数のシナプス回路40のそれぞれは、受け取ったパルス信号と、設定されている係数とを乗じた値を表す入力信号を生成する。そして、複数のシナプス回路40のそれぞれは、生成したパルス信号を、対応するニューロン回路30（後段のニューロン回路30）に与える。

30

**【0023】**

また、複数のニューロン回路30のそれぞれは、パルス信号の発生タイミングを内部においてフィードバックすることにより、対応するシナプス回路40に設定されている係数を更新する。例えば、複数のニューロン回路30のそれぞれは、パルス信号を発生した場合、対応付けられた2以上のシナプス回路40のうちの入力信号を与えた対象のシナプス回路40に設定されている係数を更新する。

40

**【0024】**

なお、ニューラルネットワークの初段の層は、外部装置から入力データを受け取り、受け取った入力データに応じた入力信号を、次の層に含まれる複数のニューロン回路30へと与える。従って、ニューラルネットワークの初段の層は、前段にシナプス回路40が対応付けられていないくてよい。また、ニューラルネットワークの初段の層は、演算および処理を実行しない。

**【0025】**

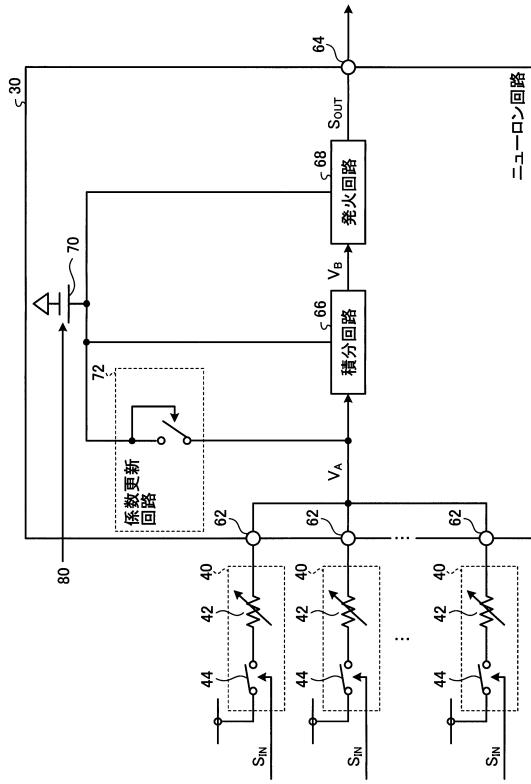

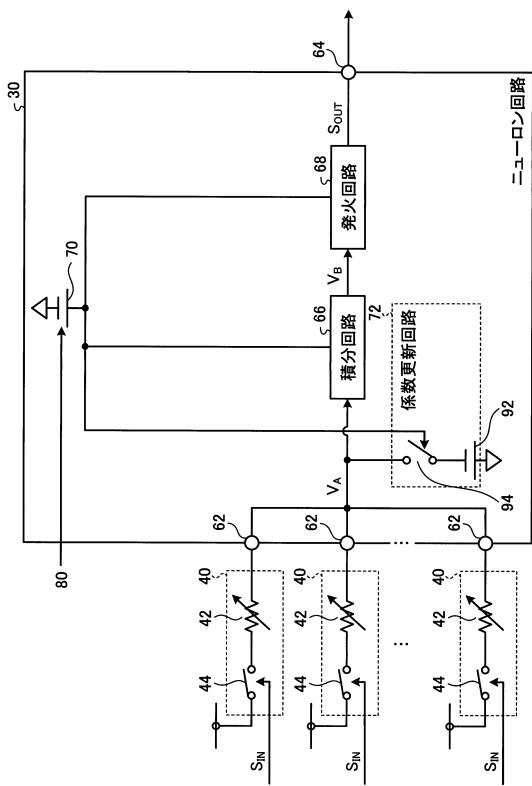

図3は、ニューロン回路30、および、ニューロン回路30に対応する2以上のシナプス回路40の回路構成を示す図である。

**【0026】**

1つのニューロン回路30の前段には、2以上のシナプス回路40が対応付けられてい

50

る。2以上のシナプス回路40のそれぞれは、さらに前段のニューロン回路30から受け取ったパルス信号と、設定されている係数とを乗じた値を表す入力信号を、対応するニューロン回路30へと与える。

#### 【0027】

例えば、シナプス回路40は、抵抗変化メモリ素子42と、スイッチ44とを含む。

#### 【0028】

抵抗変化メモリ素子42は、印加された電圧に応じてコンダクタンスを変化させる可変抵抗である。抵抗変化メモリ素子42のコンダクタンスは、シナプス回路40に設定されている係数を表す。抵抗変化メモリ素子42は、例えば、R e R A M (Resistive Random Access Memory)に用いられる抵抗素子であってもよいし、メモリストアであってもよい。

10

#### 【0029】

スイッチ44は、前段のニューロン回路30により発生されたパルス信号を受け取ったタイミングにおいて、抵抗変化メモリ素子42に所定の定電圧を印加する。例えば、スイッチ44は、パルス信号を受け取ったタイミングから所定期間、抵抗変化メモリ素子42に電圧を印加する。なお、スイッチ44により印加させる電圧は、抵抗変化メモリ素子42のコンダクタンスを変化させない程度の小さい電圧である。

#### 【0030】

このようなシナプス回路40は、抵抗変化メモリ素子42に流れる電流を、入力信号として、対応するニューロン回路30に与えることができる。抵抗変化メモリ素子42に流れる電流は、スイッチ44により抵抗変化メモリ素子42に印加された電圧と、抵抗変化メモリ素子42のコンダクタンスとを乗じた値を表す。従って、このようなシナプス回路40は、受け取ったパルス信号と設定されている係数とを乗じた値を表す入力信号を、対応するニューロン回路30に与えることができる。

20

#### 【0031】

ニューロン回路30は、2以上の入力端子62と、出力端子64と、積分回路66と、発火回路68と、二次電池70と、係数更新回路72とを有する。

#### 【0032】

2以上の入力端子62は、ニューロン回路30に対応付けられている2以上のシナプス回路40に接続される。2以上の入力端子62は、対応付けられた2以上のシナプス回路40から、2以上の入力信号を取得する。例えば、2以上の入力端子62のそれぞれは、対応するシナプス回路40の抵抗変化メモリ素子42に流れる電流を、入力信号として受け取る。この場合、2以上の入力端子62は、内部において接続される。

30

#### 【0033】

積分回路66は、2以上の入力端子62により取得された2以上の入力信号を積分する。例えば、積分回路66は、2以上の入力信号を加算して、時間積分する。そして、積分回路66は、積分値を表す積分信号を出力する。

#### 【0034】

例えば、積分回路66は、2以上の入力端子62から受け取った電流を加算し、加算した電流の時間積分をした値を表す積分信号を出力する。この場合、例えば、積分回路66は、抵抗、キャパシタおよび演算增幅器を接続したアナログ積分回路であってもよい。このアナログ積分回路は、2以上の入力端子62に流れる電流を加算した合計電流をキャパシタに蓄積し、キャパシタに発生した電圧を表す値を、積分信号として出力する。

40

#### 【0035】

発火回路68は、積分回路66から出力された積分信号に応じて、後段のニューロン回路30へと伝達されるパルス信号を発生する。例えば、発火回路68は、積分信号が予め定められた値以上または以下となった場合に、所定のパルス幅のパルス信号を発生する。例えば、積分信号が電圧信号である場合、発火回路68は、入力電圧と基準電圧とを比較するコンパレータであってもよい。

#### 【0036】

50

また、発火回路 6 8 は、積分信号の値が高い程、高い確率でパルス信号を発生する確率回路であってもよい。

#### 【 0 0 3 7 】

二次電池 7 0 は、内部に電力を蓄積し、電源電圧を発生する。二次電池 7 0 は、積分動作のための駆動電力を積分回路 6 6 に供給する。さらに、二次電池 7 0 は、パルス信号を発生させるための駆動電力を発火回路 6 8 に供給する。例えば、二次電池 7 0 は、電源電圧を、積分回路 6 6 および発火回路 6 8 に供給する。

#### 【 0 0 3 8 】

ここで、二次電池 7 0 は、それぞれのニューロン回路 3 0 に個別に設けられている。すなわち、演算部 2 0 は、複数のニューロン回路 3 0 に対して共通に設けられた 1 つの二次電池 7 0 を有していない。これにより、二次電池 7 0 は、人体のニューロンと同様の形態でエネルギー源として機能することができる。

10

#### 【 0 0 3 9 】

二次電池 7 0 は、積分回路 6 6 および発火回路 6 8 を十分に動作させることができ程度のエネルギー容量を有する。また、二次電池 7 0 は、発火回路 6 8 がパルス信号を発生した場合、所定量の電圧降下が生じる程度の放電特性を有する。すなわち、二次電池 7 0 は、発火回路 6 8 からパルス信号が出力されたことに応じて、発生する電源電圧が減少する。ただし、二次電池 7 0 は、発火回路 6 8 がパルス信号を発生した後も、少なくとも所定以上の電力を残存させることができるエネルギー容量を有する。より具体的には、二次電池 7 0 は、発火回路 6 8 がパルス信号を発生した後も、抵抗変化メモリ素子 4 2 のコンダクタンスを変化させることができる程度の電力を残存させる。

20

#### 【 0 0 4 0 】

例えば、二次電池 7 0 は、半導体基板上に作成される。例えば、二次電池 7 0 は、非特許文献 7 に示されるような、固体電解質と金属との積層薄膜を有する構成であってよい。

#### 【 0 0 4 1 】

また、二次電池 7 0 は、外部の充電回路 8 0 により充電がされる。なお、充電回路 8 0 による二次電池 7 0 に対する充電については、図 5 を参照して後述する。

#### 【 0 0 4 2 】

係数更新回路 7 2 は、発火回路 6 8 がパルス信号を発生したことによる二次電池 7 0 の電源電圧の減少に応じて、対応付けられた 1 以上のシナプス回路 4 0 のうちの入力信号を与えた対象のシナプス回路 4 0 に設定されている係数を更新する。入力信号を与えた対象のシナプス回路 4 0 は、例えば、前段のニューロン回路 3 0 からパルス信号を受け取った回路である。

30

#### 【 0 0 4 3 】

例えば、係数更新回路 7 2 は、電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、対象のシナプス回路 4 0 に設定されている係数を更新する。より具体的には、例えば、係数更新回路 7 2 は、電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、対象のシナプス回路 4 0 が有する抵抗変化メモリ素子 4 2 に電源電圧を印加する。

#### 【 0 0 4 4 】

40

抵抗変化メモリ素子 4 2 は、二次電池 7 0 から発生された電源電圧が印加された場合、所定量以上の電流（電荷）が流れる。この結果、抵抗変化メモリ素子 4 2 は、コンダクタンスが変化する。従って、係数更新回路 7 2 は、対象のシナプス回路 4 0 が有する抵抗変化メモリ素子 4 2 に電源電圧を印加することにより、対象のシナプス回路 4 0 に設定されている係数を更新することができる。

#### 【 0 0 4 5 】

例えば、係数更新回路 7 2 は、電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、二次電池 7 0 の電源電圧の発生端子と、入力端子 6 2 との間を、短絡させるスイッチング回路であってもよい。このスイッチング回路は、電源電圧が予め定められた閾値以下または予め定められた閾値以上ではない場合、二次電池 7 0 の電源

50

電圧の発生端子と、入力端子 6 2との間を切断させる。このような動作をするスイッチング回路は、ドレインとゲートの間を短絡したMOS-FETを、二次電池 7 0の電源電圧の発生端子と入力端子 6 2との間に設けることにより、実現することができる。これにより、係数更新回路 7 2は、電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、対象のシナップス回路 4 0が有する抵抗変化メモリ素子 4 2に電源電圧を印加することができる。

#### 【0046】

このような係数更新回路 7 2は、発火回路 6 8が発生したパルス信号のタイミングをニューロン回路 3 0の内部のパスを介して取得し、取得したタイミングに基づき、シナップス回路 4 0に設定されている係数を更新することができる。つまり、係数更新回路 7 2は、発火回路 6 8が発生したパルス信号のタイミングをニューロン回路 3 0の外部のパスを経由せずに取得することができる。これにより、係数更新回路 7 2は、ニューロンが発火したタイミングに応じてシナップス強度を更新する学習処理(STDP)を、簡易な回路で実行することができる。10

#### 【0047】

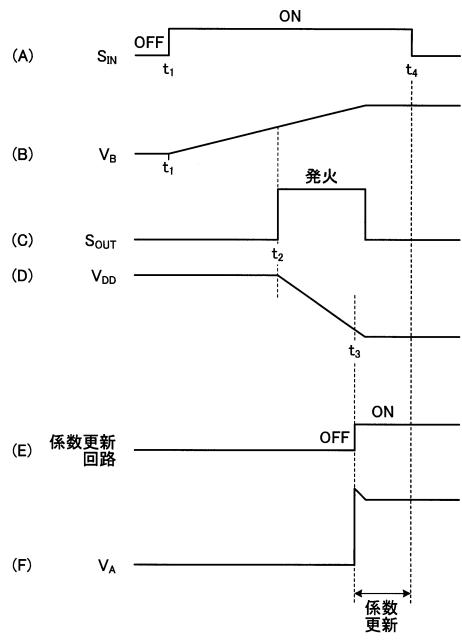

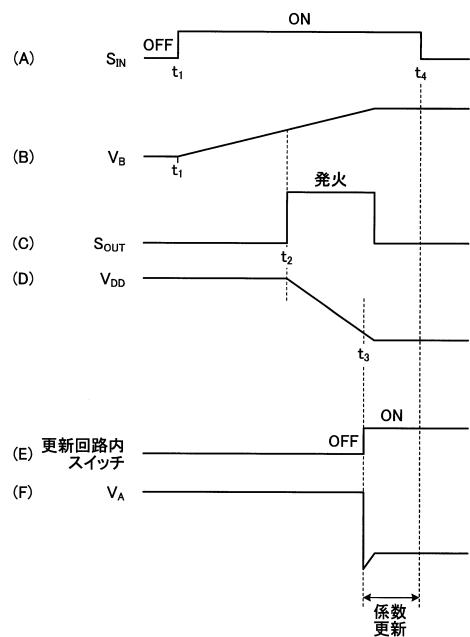

図4は、ニューロン回路 3 0およびシナップス回路 4 0の信号波形を示す図である。

#### 【0048】

図4(A)は、シナップス回路 4 0が受け取るスイッチング信号( $S_{IN}$ )を示す。図4(B)は、積分回路 6 6から出力される積分信号( $V_B$ )を示す。図4(C)は、発火回路 6 8から出力されるパルス信号( $S_{OUT}$ )を示す。図4(D)は、二次電池 7 0から出力される電源電圧( $V_{DD}$ )を示す。図4(E)は、係数更新回路 7 2の動作を表す。図4(F)は、入力端子 6 2の電圧( $V_A$ )を示す。20

#### 【0049】

まず、図4(A)に示すように、時刻  $t_1$ において、何れかのシナップス回路 4 0が受け取るスイッチング信号( $S_{IN}$ )は、オフからオンに変化する。例えば、スイッチング信号( $S_{IN}$ )は、前段のニューロン回路 3 0からパルス信号が発生されたタイミングにおいて、オフからオンに変化する。スイッチング信号( $S_{IN}$ )がオンとなった場合、スイッチ 4 4は、オンとなる。この結果、抵抗変化メモリ素子 4 2は、所定電圧が印加される。これにより、前段のニューロン回路 3 0からパルス信号を受け取った対象のシナップス回路 4 0は、抵抗変化メモリ素子 4 2に印加された電圧と、抵抗変化メモリ素子 4 2のコンダクタンスとを乗じた電流を、入力信号として積分回路 6 6に与えることができる。30

#### 【0050】

そして、時刻  $t_1$ から所定時間経過した時刻  $t_4$ において、スイッチング信号( $S_{IN}$ )は、オンからオフに変化する。スイッチング信号( $S_{IN}$ )がオフとなった場合、スイッチ 4 4は、オフとなる。

#### 【0051】

積分回路 6 6は、抵抗変化メモリ素子 4 2に印加された電圧と、抵抗変化メモリ素子 4 2のコンダクタンスとを乗じた電流を、入力信号として受け取る。この結果、図4(B)に示すように、積分回路 6 6は、時刻  $t_1$ から徐々に増加する積分信号( $V_B$ )を出力する。40

#### 【0052】

発火回路 6 8は、積分信号( $V_B$ )に応じて発火する。例えば、発火回路 6 8は、積分信号( $V_B$ )が予め定められた値に到達したタイミングで発火する。また、例えば、発火回路 6 8は、積分信号( $V_B$ )が予め定められた値を超えたタイミングで発火してもよい。本例では、図4(C)に示すように、時刻  $t_1$ の後の時刻  $t_2$ において、発火回路 6 8は、所定の時間幅のパルス信号( $S_{OUT}$ )を発生する。

#### 【0053】

二次電池 7 0は、発火回路 6 8がパルス信号( $S_{OUT}$ )を発生した場合、電源電圧( $V_{DD}$ )を徐々に低下させる。本例では、図4(D)に示すように、電源電圧( $V_{DD}$ )は、時刻  $t_2$ から低下を開始する。50

**【 0 0 5 4 】**

係数更新回路 7 2 は、電源電圧 ( $V_{DD}$ ) が所定の閾値以下となった場合、オフからオンに切り替わる。係数更新回路 7 2 は、オフの場合、二次電池 7 0 と入力端子 6 2 との間を切断する。係数更新回路 7 2 は、オンの場合、二次電池 7 0 と入力端子 6 2 との間を接続する。本例では、図 4 (E) に示すように、時刻  $t_2$  の後の時刻  $t_3$  において、係数更新回路 7 2 は、オフからオンに切り替わる。これにより、係数更新回路 7 2 は、時刻  $t_3$  から、入力端子 6 2 への電源電圧 ( $V_{DD}$ ) の印加を開始することができる。

**【 0 0 5 5 】**

入力端子 6 2 に電源電圧 ( $V_{DD}$ ) が印加された場合、対象のシナプス回路 4 0 (スイッチ 4 4 がオンとなっているシナプス回路 4 0) に含まれる抵抗変化メモリ素子 4 2 に、電源電圧 ( $V_{DD}$ ) が印加される。本例では、図 4 (F) に示すように、時刻  $t_3$  から時刻  $t_4$  までの間ににおいて、抵抗変化メモリ素子 4 2 は、電源電圧 ( $V_{DD}$ ) が印加される。

10

**【 0 0 5 6 】**

電源電圧 ( $V_{DD}$ ) は、抵抗変化メモリ素子 4 2 のコンダクタンスを書き換えることが可能な程度に大きな電圧である。従って、スイッチ 4 4 がオンとなっている期間において、入力端子 6 2 に電源電圧 ( $V_{DD}$ ) が印加された場合、抵抗変化メモリ素子 4 2 のコンダクタンスは、変化する。従って、図 4 (F) に示すように、時刻  $t_3$  から時刻  $t_4$  までの間ににおいて、係数更新回路 7 2 は、抵抗変化メモリ素子 4 2 のコンダクタンスを変化させることができる。すなわち、時刻  $t_3$  から時刻  $t_4$  までの間ににおいて、係数更新回路 7 2 は、対象のシナプス回路 4 0 に設定されている係数を更新することができる。

20

**【 0 0 5 7 】**

このようにニューロン回路 3 0 は、パルス信号 ( $S_{OUT}$ ) をフィードバックする外部パスを有さずに、シナプス回路 4 0 に設定された係数を更新することができる。

**【 0 0 5 8 】**

なお、パルス信号 ( $S_{OUT}$ ) が発生する時刻  $t_3$  が、スイッチング信号 ( $S_{IN}$ ) がオンからオフに変化する時刻  $t_4$  より前である場合、係数更新回路 7 2 は、対象のシナプス回路 4 0 に設定されている係数を更新する。しかし、時刻  $t_3$  が時刻  $t_4$  より後である場合、係数更新回路 7 2 は、対象のシナプス回路 4 0 に設定されている係数を更新しない。従って、このようなニューロン回路 3 0 は、ニューロン発火のタイミングによってシナプス強度が変更される学習規則である STD P を模擬した係数の更新をすることができる。

30

**【 0 0 5 9 】**

図 5 は、充電回路 8 0 を備える演算部 2 0 の構成を示す図である。演算部 2 0 は、充電回路 8 0 をさらに備える。充電回路 8 0 は、複数のニューロン回路 3 0 に対して共通に設けられる。

**【 0 0 6 0 】**

充電回路 8 0 は、複数のニューロン回路 3 0 のそれぞれが有する二次電池 7 0 を充電する。例えば、充電回路 8 0 は、二次電池 7 0 を定期的に充電する。これにより、パルス信号を発生することにより電力が消費された場合であっても、二次電池 7 0 は、新たに電力を蓄積することができる。従って、ニューロン回路 3 0 は、繰り返し動作をすることができる。

40

**【 0 0 6 1 】**

以上のように、本実施形態に係るニューラルネットワーク装置 1 0 は、複数のニューロン回路 3 0 のそれぞれが二次電池 7 0 を有する。これにより、ニューラルネットワーク装置 1 0 によれば、人体のニューロンと同様の形態でエネルギー源を有することができる。

**【 0 0 6 2 】**

さらに、本実施形態に係るニューラルネットワーク装置 1 0 は、複数のニューロン回路 3 0 のそれぞれが、二次電池 7 0 が発生する電源電圧の減少に応じて入力信号を与えた対象のシナプス回路 4 0 に設定されている係数を更新する。これにより、ニューラルネット

50

ワーク装置 10 によれば、ニューロン回路 30 とは別のフィードバックパスを有さずに、ニューロン発火のタイミングをフィードバックして、シナプス回路 40 に設定されている係数を更新することができる。

#### 【0063】

図 6 は、変形例に係るニューロン回路 30、および、変形例に係るニューロン回路 30 に対応する 2 以上のシナプス回路 40 の回路構成を示す図である。

#### 【0064】

変形例に係るニューロン回路 30 は、係数更新回路 72 の構成が、図 3 に示した回路構成と異なる。変形例に係るニューロン回路 30 については、図 3 に示した回路との共通点については詳細な説明を省略する。

10

#### 【0065】

変形例に係る係数更新回路 72 は、更新回路内二次電池 92 と、更新回路内スイッチ 94 とを有する。

更新回路内二次電池 92 は、内部に電力を蓄積し、電圧を発生する。更新回路内二次電池 92 は、抵抗変化メモリ素子 42 のコンダクタンスを変化させることができる程度の電力を蓄積する。更新回路内二次電池 92 は、二次電池 70 と同一構成であってよい。また、更新回路内二次電池 92 は、二次電池 70 と同様に外部の充電回路 80 により充電がされてもよい。

#### 【0066】

ただし、更新回路内二次電池 92 は、基準電位（例えばグランド）に対して、二次電池 70 とは逆方向の極性で接続される。従って、更新回路内二次電池 92 は、電源電圧に対してマイナスの電圧を発生する。

20

#### 【0067】

更新回路内スイッチ 94 は、二次電池 70 から発生された電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、対象のシナプス回路 40 が有する抵抗変化メモリ素子 42 に、更新回路内二次電池 92 から発生される電圧を印加する。例えば、更新回路内スイッチ 94 は、電源電圧が予め定められた閾値以下または予め定められた閾値以上となった場合、更新回路内二次電池 92 の電圧の発生端子と、入力端子 62 との間を、短絡させる。

#### 【0068】

30

また、更新回路内スイッチ 94 は、電源電圧が予め定められた閾値以下または予め定められた閾値以上ではない場合、対象のシナプス回路 40 が有する抵抗変化メモリ素子 42 と、更新回路内二次電池 92 との間を切断する。例えば、更新回路内スイッチ 94 は、二次電池 70 から発生された電源電圧が予め定められた閾値以下または予め定められた閾値以上ではない場合、更新回路内二次電池 92 の電圧の発生端子と、入力端子 62 との間を切断させる。

#### 【0069】

このような動作をする更新回路内スイッチ 94 は、例えば、MOS-FET のソース - ドレインを更新回路内二次電池 92 の電圧の発生端子と入力端子 62 と間に接続し、ゲートを二次電池 70 の電源電圧の発生端子に接続することにより、実現することができる。

40

#### 【0070】

図 7 は、変形例に係るニューロン回路 30 およびシナプス回路 40 の信号波形を示す図である。

#### 【0071】

図 7 (A) ~ 図 7 (D) は、図 4 (A) から図 4 (D) と同一の信号波形である。図 4 (E) は、係数更新回路 72 が有する更新回路内スイッチ 94 の動作を表す。図 4 (F) は、入力端子 62 の電圧 ( $V_A$ ) を示す。

#### 【0072】

係数更新回路 72 が有する更新回路内スイッチ 94 は、二次電池 70 により発生された電源電圧 ( $V_{DD}$ ) が所定の閾値以下となった場合、オフからオンに切り替わる。更新回

50

路内スイッチ 9 4 は、オフの場合、更新回路内二次電池 9 2 と入力端子 6 2との間を切斷する。更新回路内スイッチ 9 4 は、オンの場合、更新回路内二次電池 9 2 と入力端子 6 2との間を接続する。本例では、図 7 ( E ) に示すように、時刻  $t_3$  において、更新回路内スイッチ 9 4 は、オフからオンに切り替わる。

#### 【 0 0 7 3 】

本例においては、更新回路内二次電池 9 2 は、電源電圧 ( $V_{DD}$ ) とは極性が逆のマイナス電圧を発生する。これにより、更新回路内スイッチ 9 4 は、時刻  $t_3$  から、入力端子 6 2 に、更新回路内二次電池 9 2 から発生されたマイナス電圧の印加を開始することができる。

#### 【 0 0 7 4 】

入力端子 6 2 に更新回路内二次電池 9 2 から発生されたマイナス電圧が印加された場合、対象のシナップス回路 4 0 (スイッチ 4 4 がオンとなっているシナップス回路 4 0) に含まれる抵抗変化メモリ素子 4 2 に、更新回路内二次電池 9 2 から発生されたマイナス電圧が印加される。本例では、図 7 ( F ) に示すように、時刻  $t_3$  から時刻  $t_4$  までの間ににおいて、抵抗変化メモリ素子 4 2 は、マイナス電圧が印加される。

#### 【 0 0 7 5 】

更新回路内二次電池 9 2 から発生されたマイナス電圧は、抵抗変化メモリ素子 4 2 のコンダクタンスを書き換えることが可能な電圧である。従って、スイッチ 4 4 がオンとなっている期間において、入力端子 6 2 に更新回路内二次電池 9 2 から発生されたマイナス電圧が印加された場合、抵抗変化メモリ素子 4 2 のコンダクタンスは、変化する。従って、図 7 ( F ) に示すように、時刻  $t_3$  から時刻  $t_4$  までの間ににおいて、係数更新回路 7 2 は、抵抗変化メモリ素子 4 2 のコンダクタンスを変化させることができる。すなわち、時刻  $t_3$  から時刻  $t_4$  までの間ににおいて、係数更新回路 7 2 は、対象のシナップス回路 4 0 に設定されている係数を更新することができる。

#### 【 0 0 7 6 】

このように、変形例に係るニューロン回路 3 0 も、パルス信号 ( $S_{OUT}$ ) をフィードバックする外部パスを有さずに、シナップス回路 4 0 に設定された係数を更新することができる。

#### 【 0 0 7 7 】

このような変形例に係るニューロン回路 3 0 は、発火回路 6 8 が発生したパルス信号のタイミングを内部のパスを介して取得し、取得したタイミングに基づき、シナップス回路 4 0 に設定されている係数を更新することができる。つまり、変形例に係るニューロン回路 3 0 は、発火回路 6 8 が発生したパルス信号のタイミングを外部のパスを経由せずに取得することができる。これにより、変形例に係る係数更新回路 7 2 は、ニューロンが発火したタイミングに応じてシナップス強度を更新する学習処理 (STD P) を、簡易な回路で実行することができる。

#### 【 0 0 7 8 】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、請求の範囲に記載された発明とその均等の範囲に含まれる。

#### 【 符号の説明 】

#### 【 0 0 7 9 】

- 1 0 ニューラルネットワーク装置

- 2 0 演算部

- 2 2 通信部

- 3 0 ニューロン回路

- 4 0 シナップス回路

- 4 2 抵抗変化メモリ素子

10

20

30

40

50

4 4 スイッチ

6 2 入力端子

6 4 出力端子

6 6 積分回路

6 8 発火回路

7 0 二次電池

7 2 係数更新回路

8 0 充電回路

9 2 更新回路内二次電池

9 4 更新回路内スイッチ

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 野村 久美子

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 松崎 孝大

(56)参考文献 特開平06-309478(JP,A)

特開2015-195011(JP,A)

国際公開第2015/001697(WO,A1)

米国特許出願公開第2019/0042931(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 06 N 3 / 063