**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

*G11C 7/06* (2006.01)

(45) 공고일자

2006년06월19일

(11) 등록번호

10-0591346

(24) 등록일자

2006년06월12일

(21) 출원번호

10-2000-0010019

(65) 공개번호

10-2001-0066741

(22) 출원일자

2000년02월29일

(43) 공개일자

2001년07월11일

(30) 우선권주장

99-365661

1999년12월22일

일본(JP)

(73) 특허권자

소니 가부시끼 가이샤

일본국 도쿄도 시나가와쿠 기타시나가와 6쵸메 7반 35고

(72) 발명자

히라이리고지

일본국 도쿄도 시나가와쿠 기타시나가와 6쵸메 7반 35고 소니 가부시끼 가이

샤내

(74) 대리인

유미특허법인

김재만

(56) 선행기술조사문현

JP10117140 A

US5216295 A

US5841298 A

US6002270 A

\* 심사관에 의하여 인용된 문현

심사관 : 윤난영

**(54) 차동형 센스 증폭기 회로 및 이를 사용한 동적 논리 회로****요약**

쌍대(雙對) 논리 트리(tree)가 스위치를 통해 센스 증폭기에 접속된 동적(動的) 논리 회로는 센스 증폭기의 입력 및 출력 절점(節點) 전압에 의해 논리 트리와 센스 증폭기의 접속을 제어함으로써, 전력 소비를 절감하고 커플링 노이즈를 억제한다.

**대표도**

도 1

**색인어**

센스 앰프, 논리 출력 단자, NMOS 트랜지스터, 논리 입력 단자, 다이내믹 NOR 회로.

**명세서**

## 도면의 간단한 설명

도 1은 종래의 차동형 센스 증폭기 회로의 한 구성예를 나타낸 회로도.

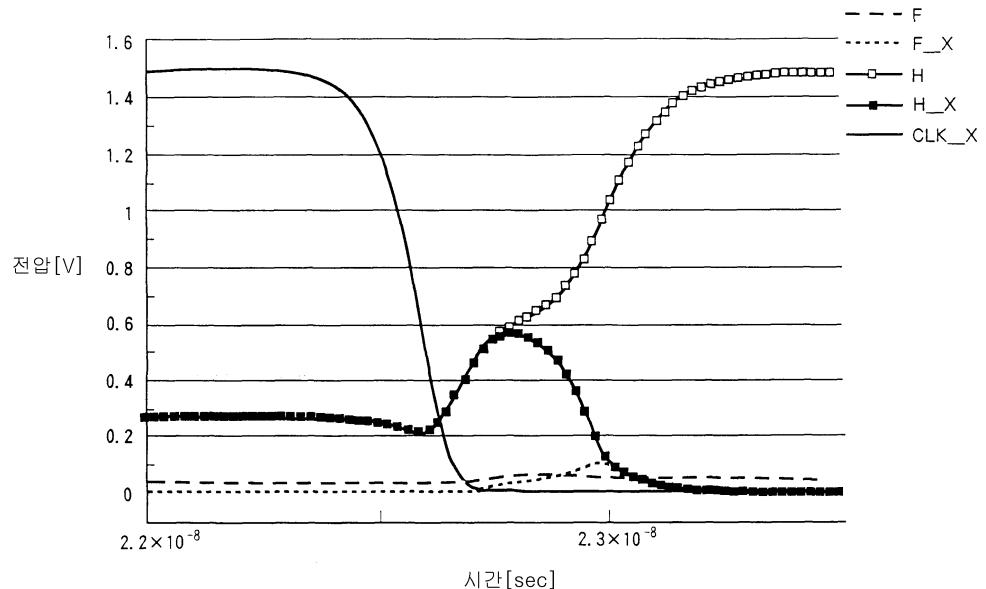

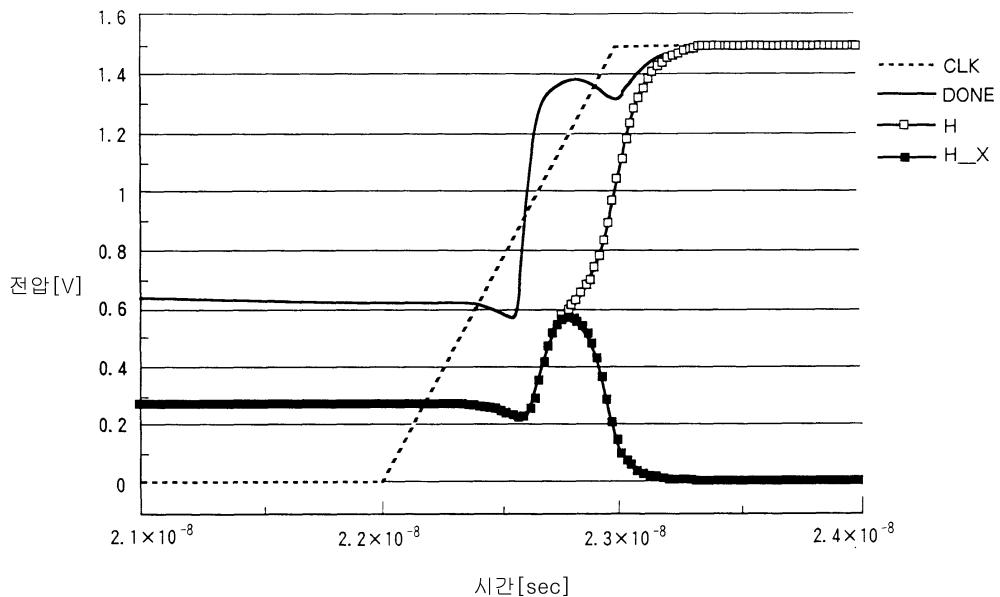

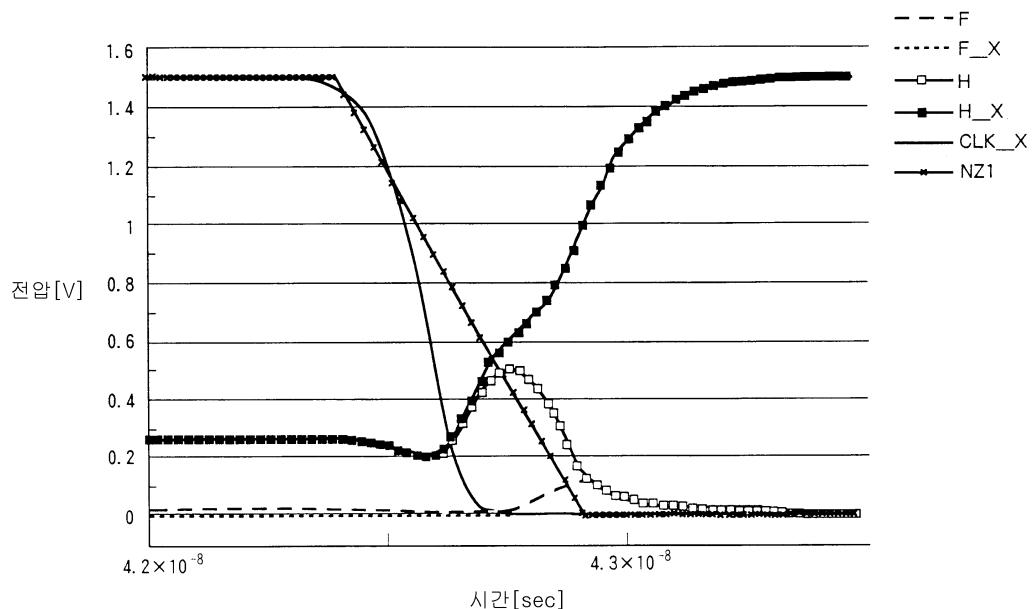

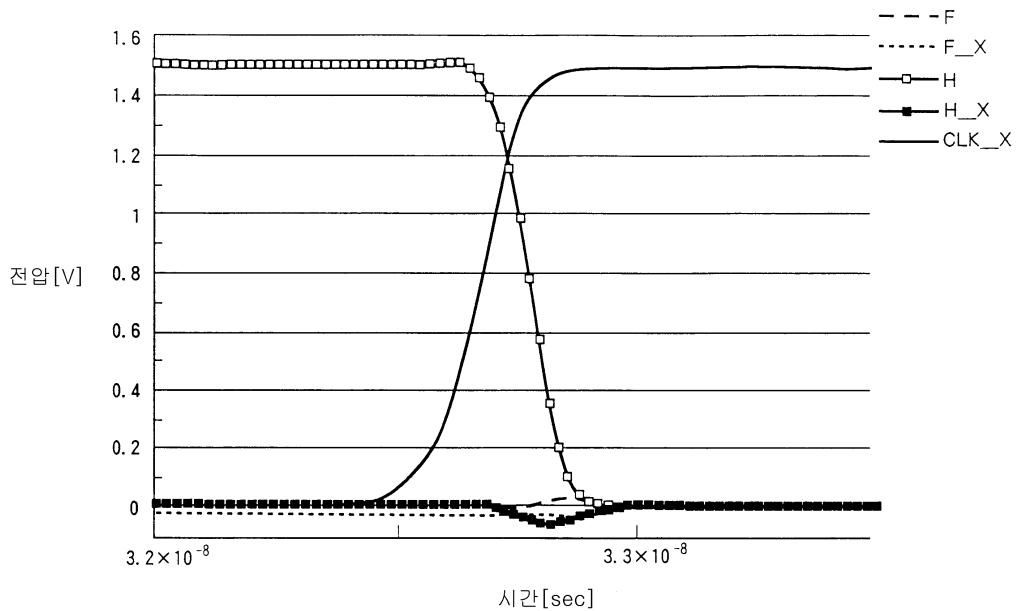

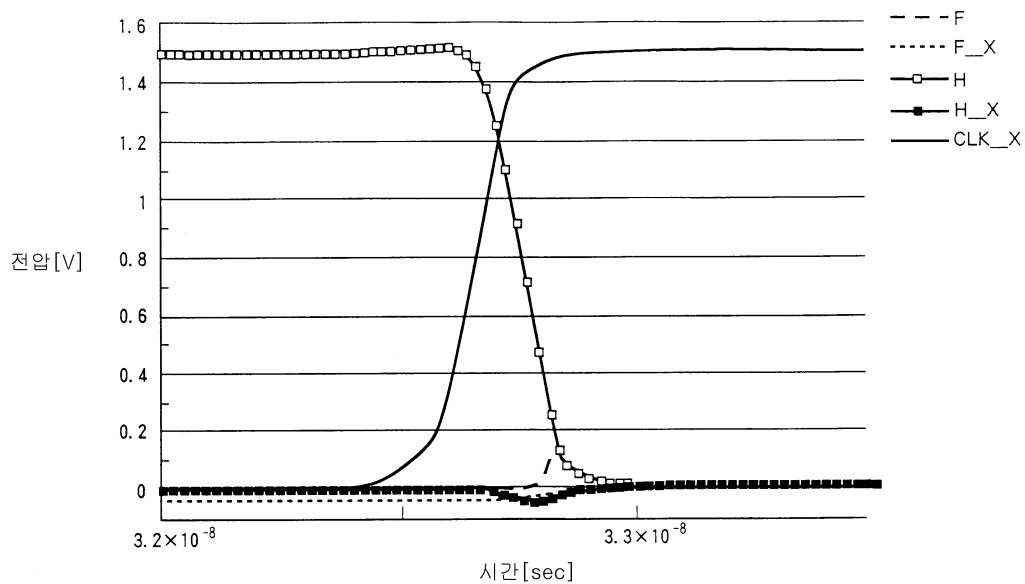

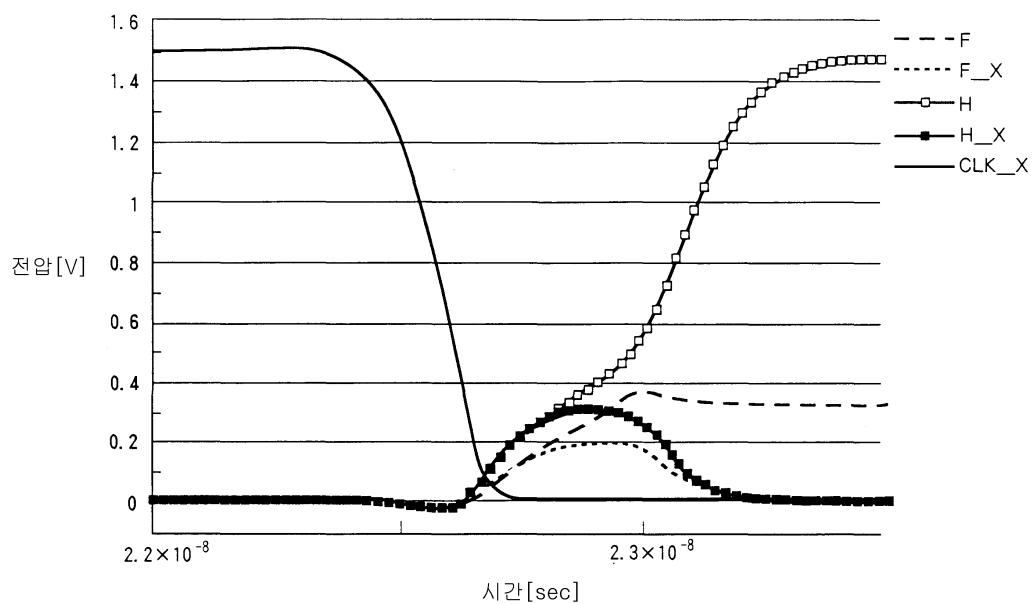

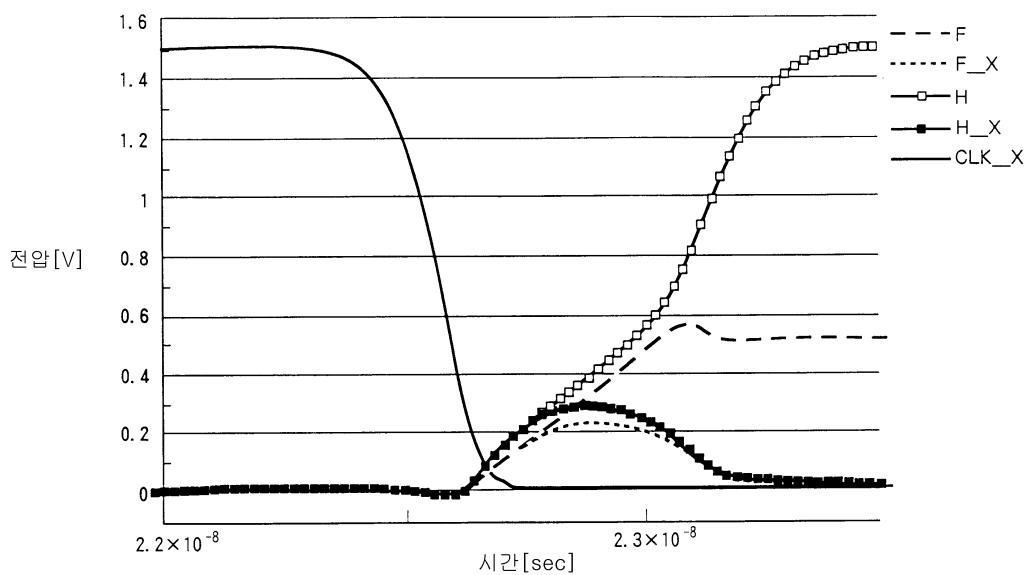

도 2는 DCSL3 방식의 센스 증폭기 회로의 클록(CLK) 상승, 즉 클록 반전 신호(CLK\_X)의 하강 시의 동작 과형(시뮬레이션 결과)을 나타낸 도면.

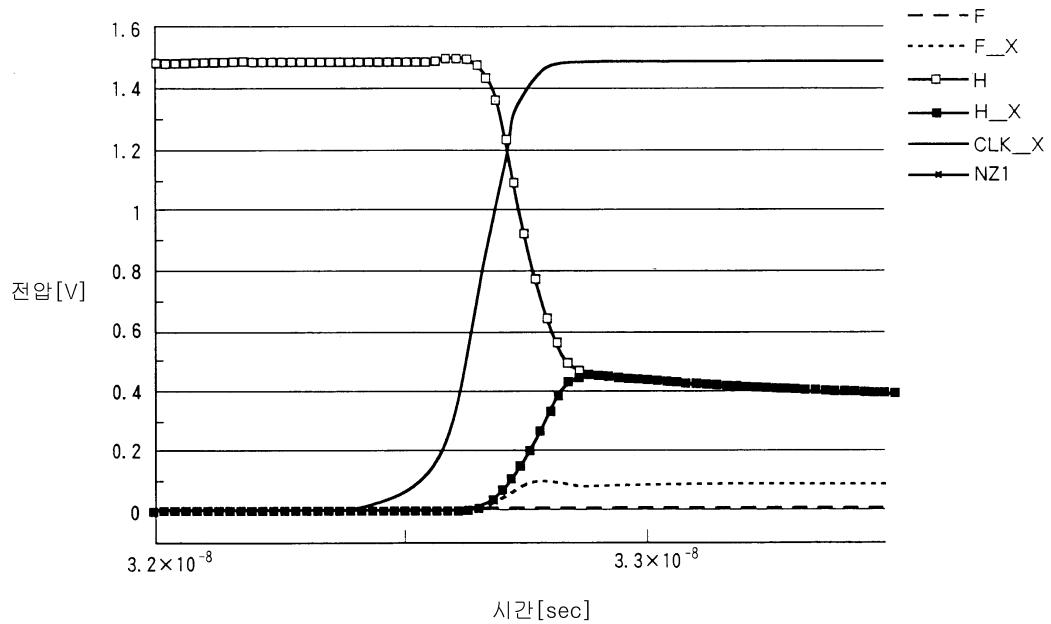

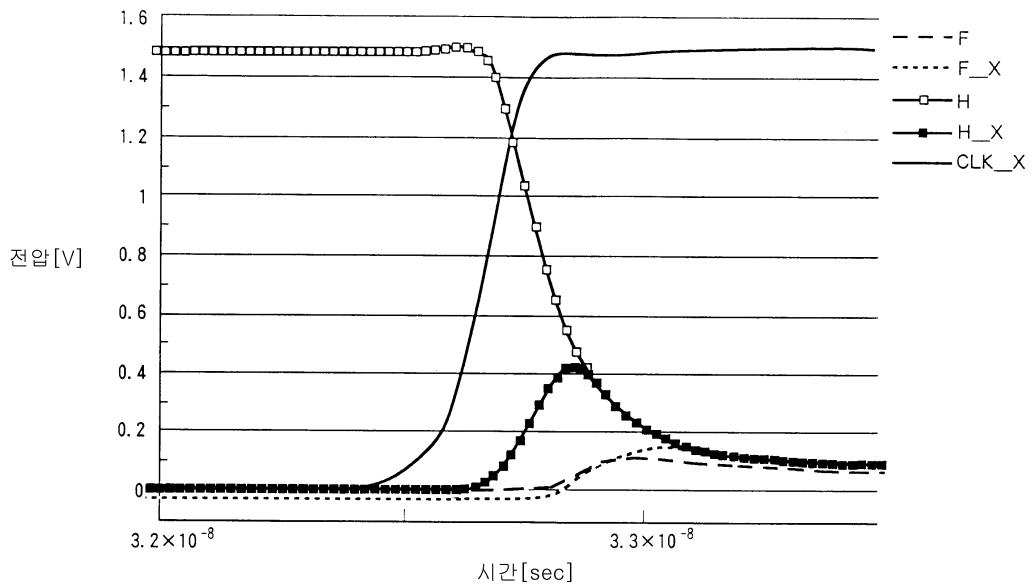

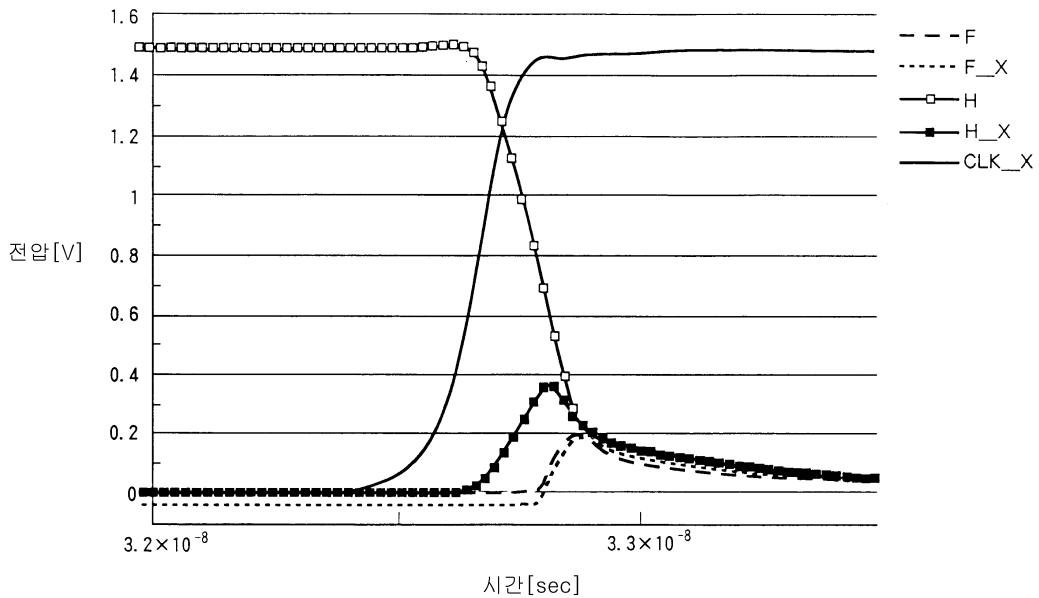

도 3은 DCSL3 방식의 센스 증폭기 회로의 클록(CLK) 하강, 즉 클록 반전 신호(CLK\_X)의 상승 시의 동작 과형(시뮬레이션 결과)을 나타낸 도면.

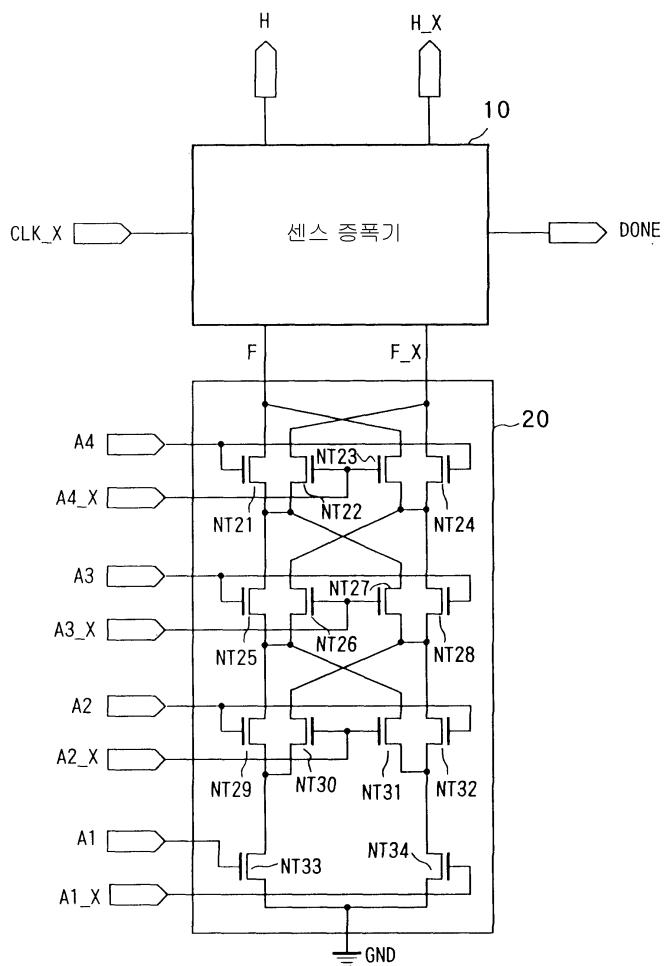

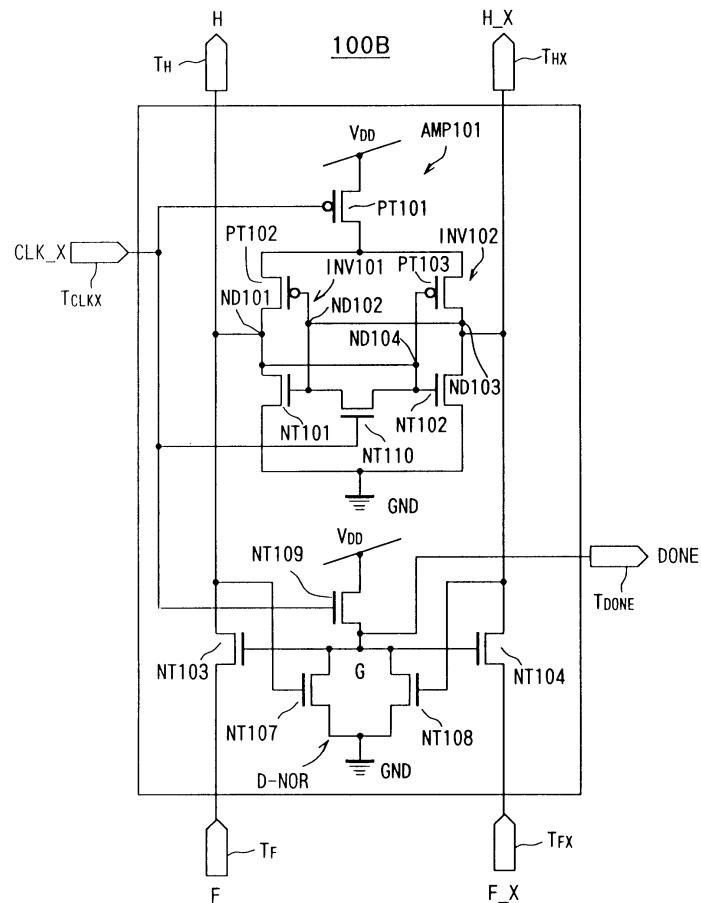

도 4는 DCSL3 방식의 차동형 센스 증폭기 회로의 논리 입력 단자(TF, TFX)에 대하여 NMOS 트랜지스터로 구성되는 쌍대(雙對) 논리 트리(tree)를 접속하여 구성한 동적 논리 회로를 나타낸 구성도.

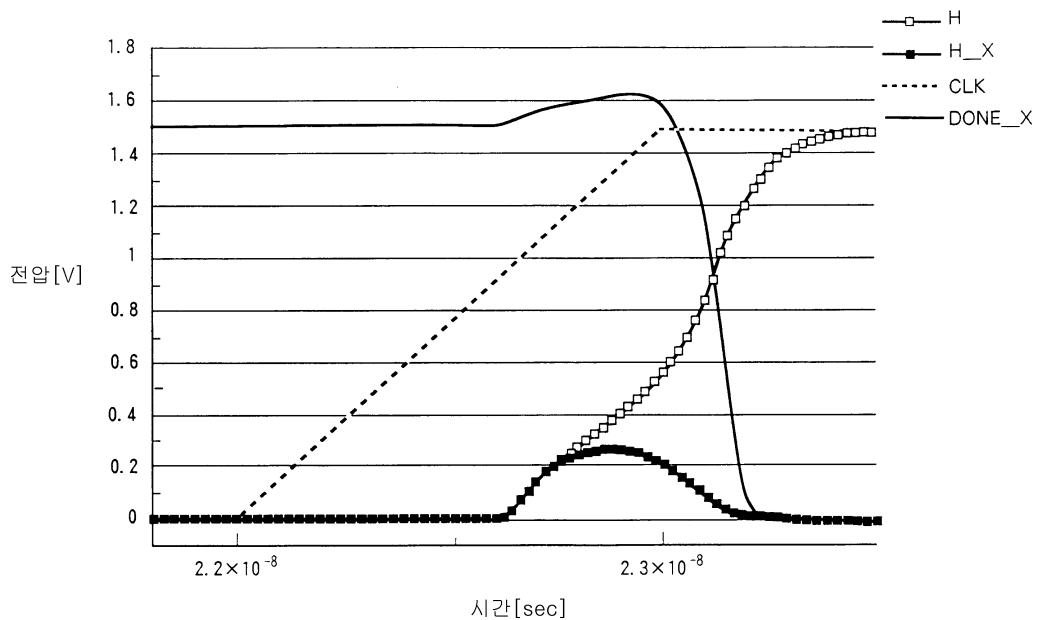

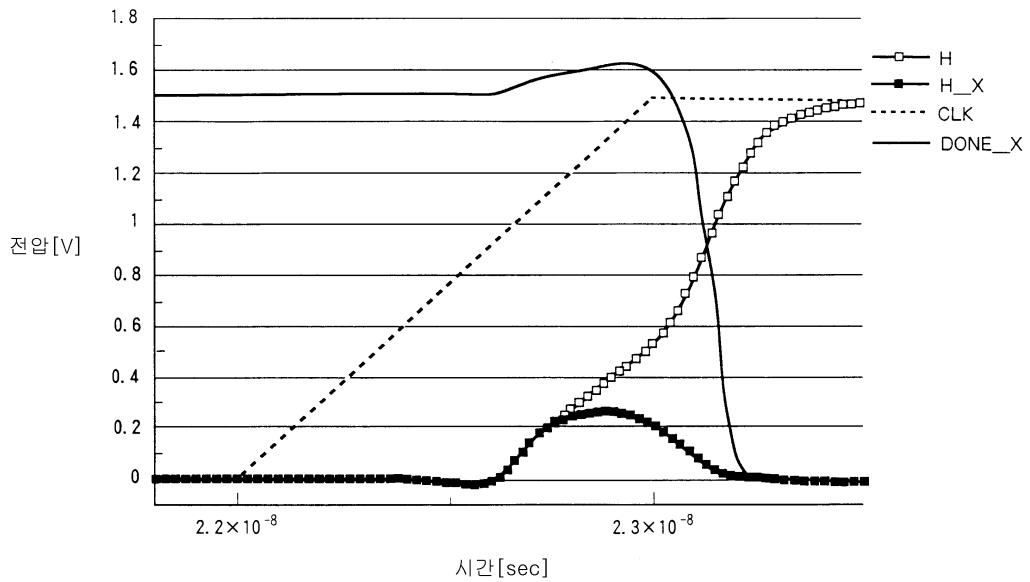

도 5는 DCSL3 방식의 센스 증폭기 회로에서 후지상으로부터 가동상으로 바뀔 때의 완료 신호(DONE)의 모양을 나타낸 도면.

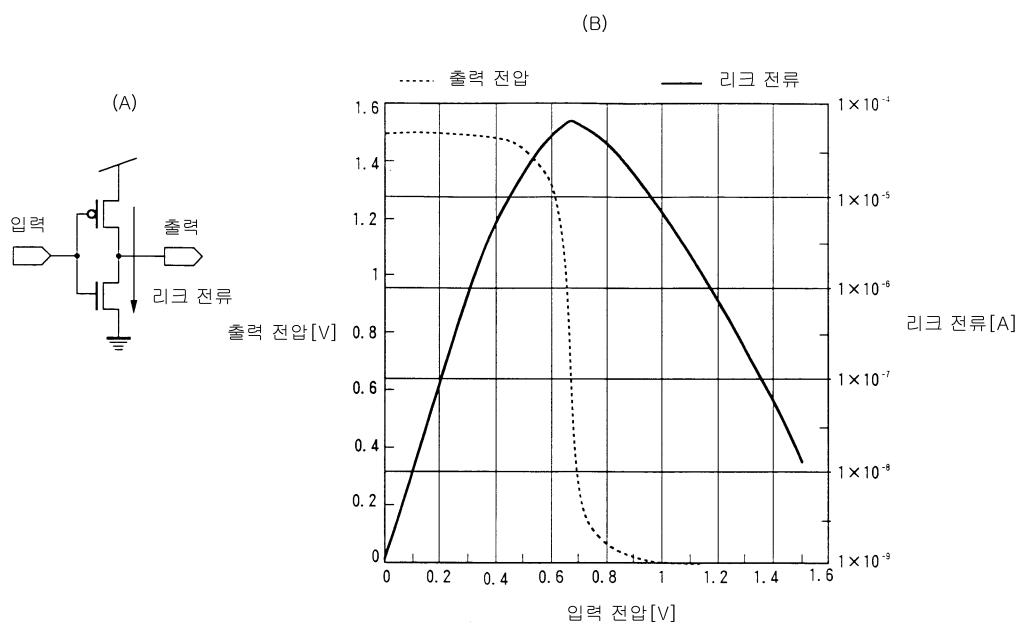

도 6 (A) 및 도 6 (B)는 COMS 인버터의 리크 전류에 대한 설명도이며, 도 6 (A)는 시뮬레이션 대상의 회로도, 도 6 (B)는 시뮬레이션 결과인 출력 전압, 리크 전류 대 입력 전압 특성을 나타낸 도면.

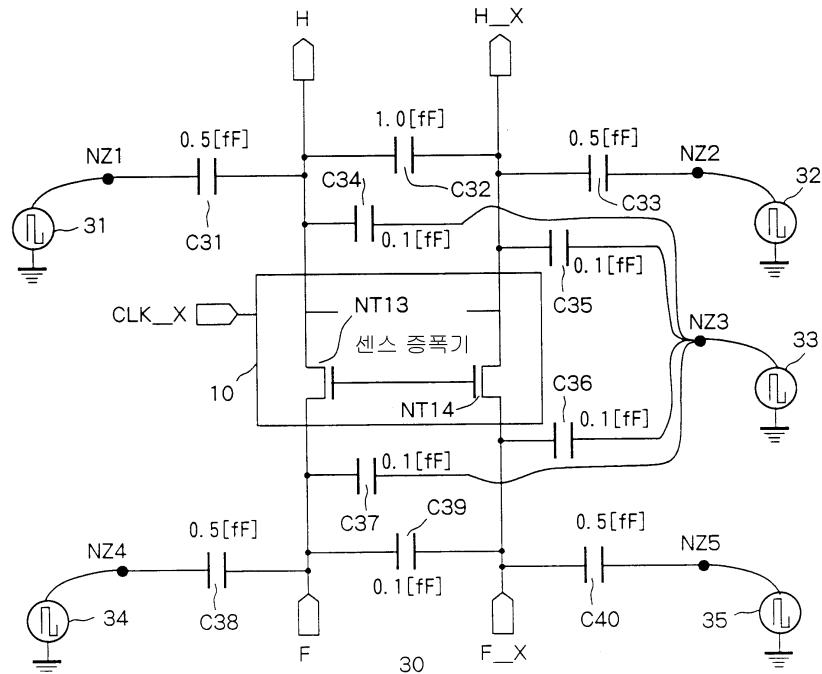

도 7은 커플링 노이즈 내성(耐性) 평가용 모델을 나타낸 도면.

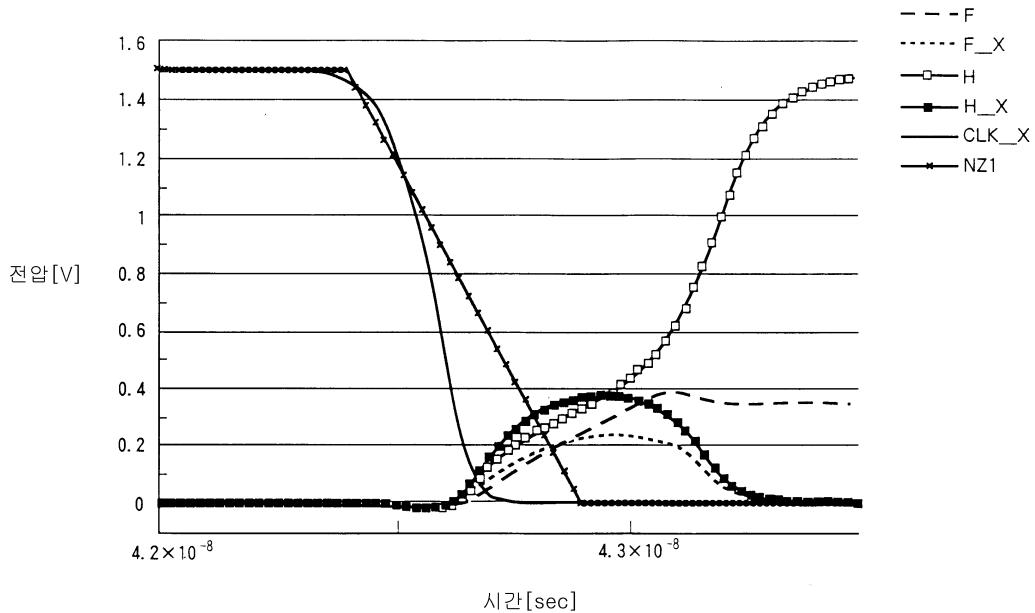

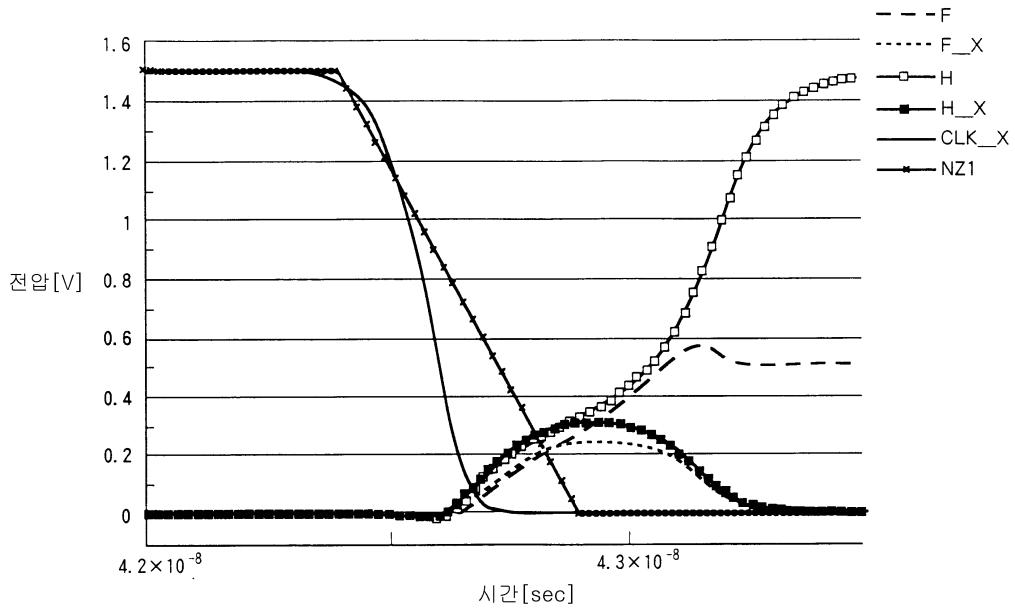

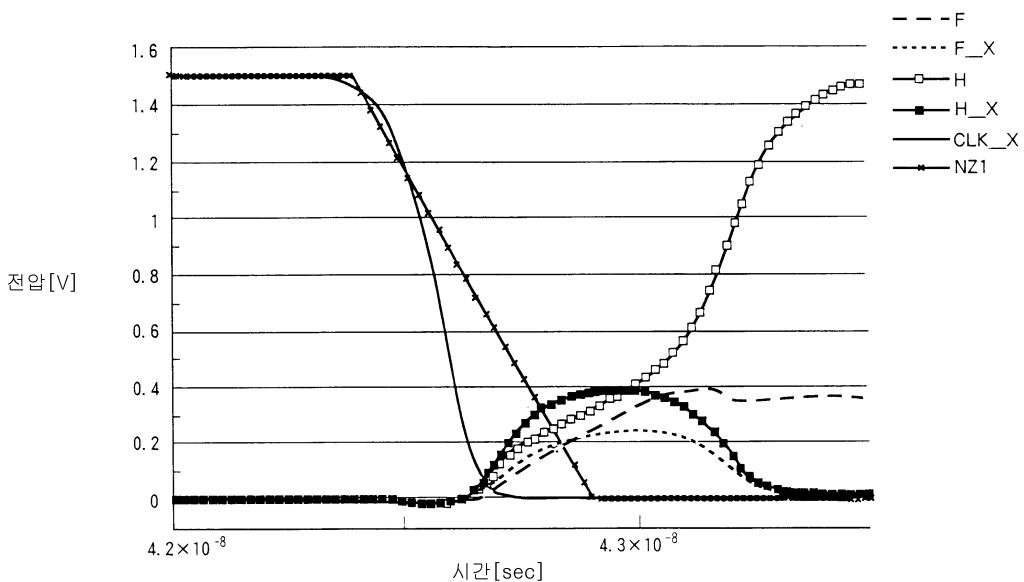

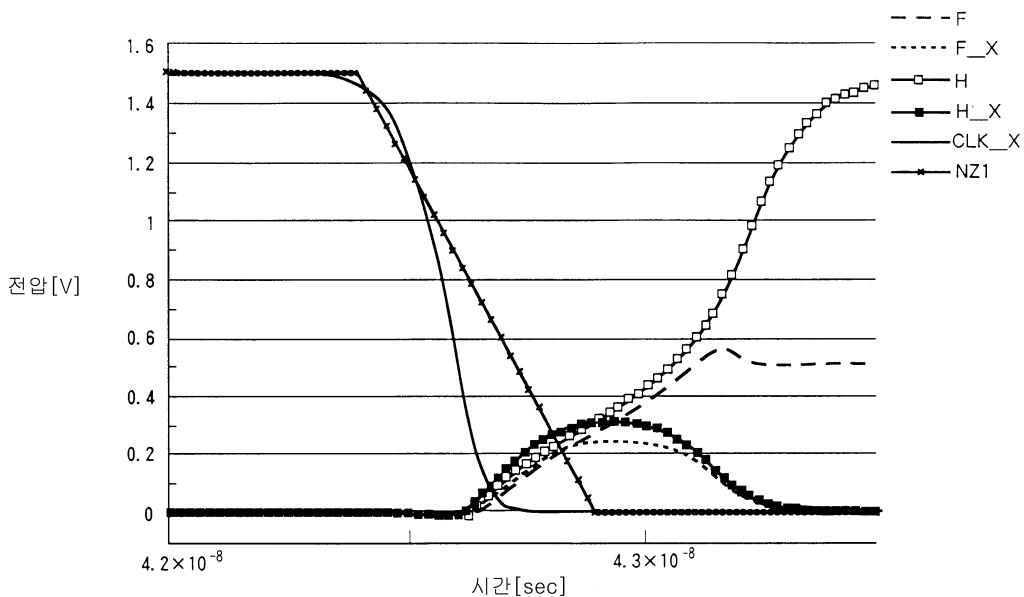

도 8은 DCSL3 방식의 센스 증폭기에 대하여 도 30의 커플링 노이즈 내성 평가용 모델을 적용하고, 클록 반전 신호(CLS\_X)의 하강과 동일한 정도의 타이밍으로 절점(節點)(NZ1)에 하강 신호를 부여한 경우의 동작 과형을 나타낸 도면.

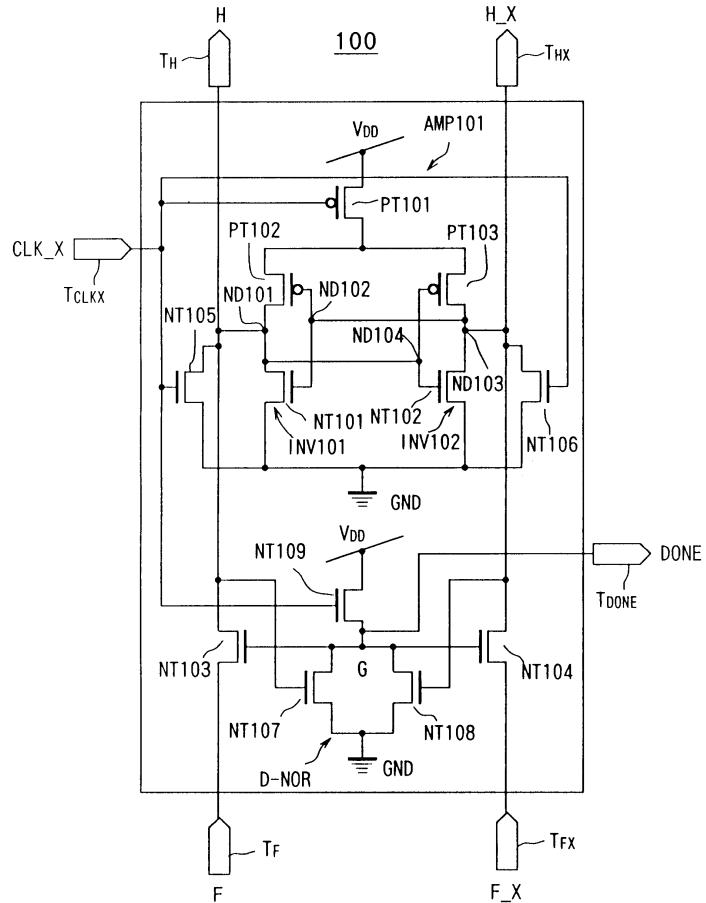

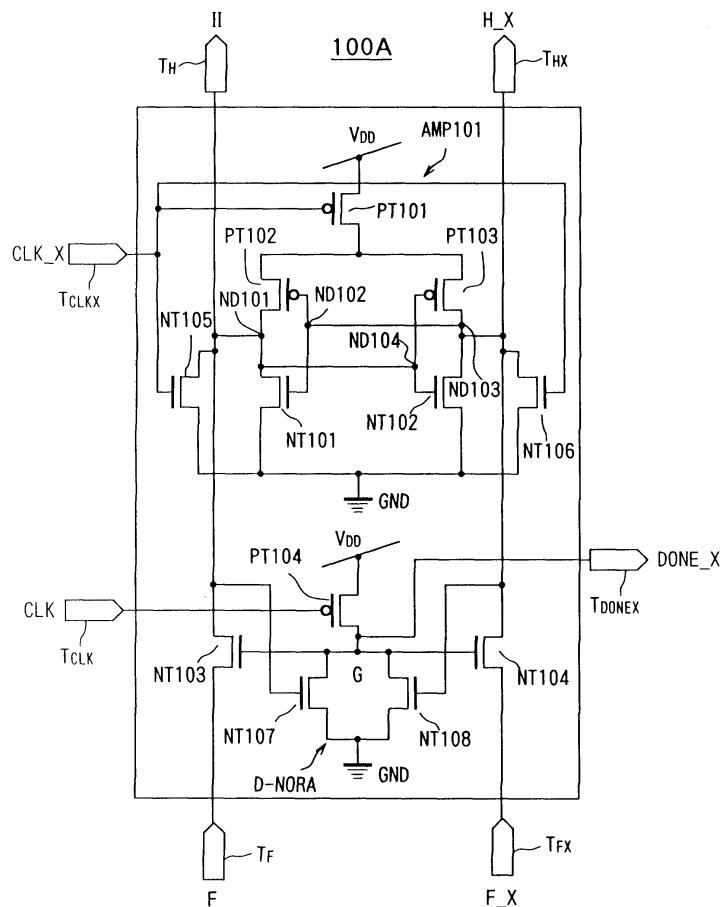

도 9는 본 발명에 관한 차동형(差動型) 센스 증폭기 회로의 제1 실시 형태를 나타낸 회로도.

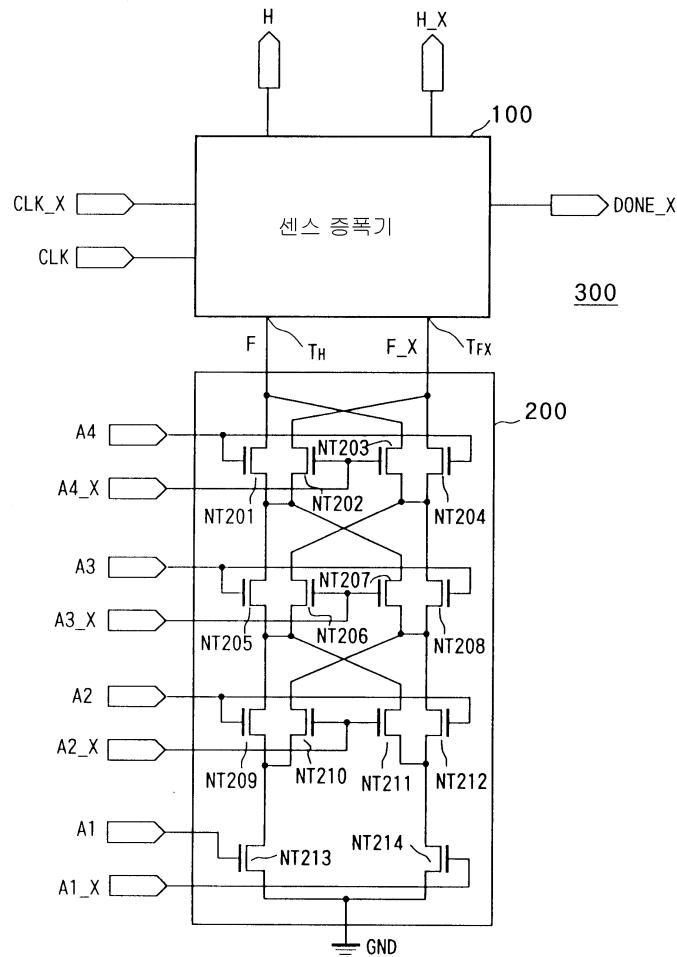

도 10은 본 발명에 관한 차동형 센스 증폭기 회로와, NMOS 쌍대(雙對) 논리 트리(2선식 논리 트리)를 조합하여 구성한 동적 논리 회로의 일예를 나타낸 도면.

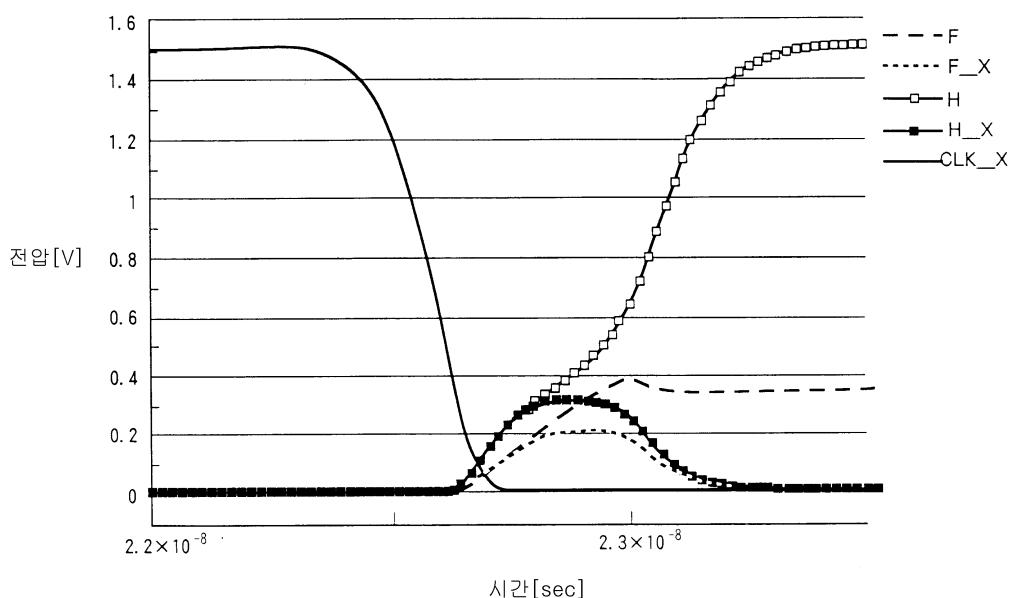

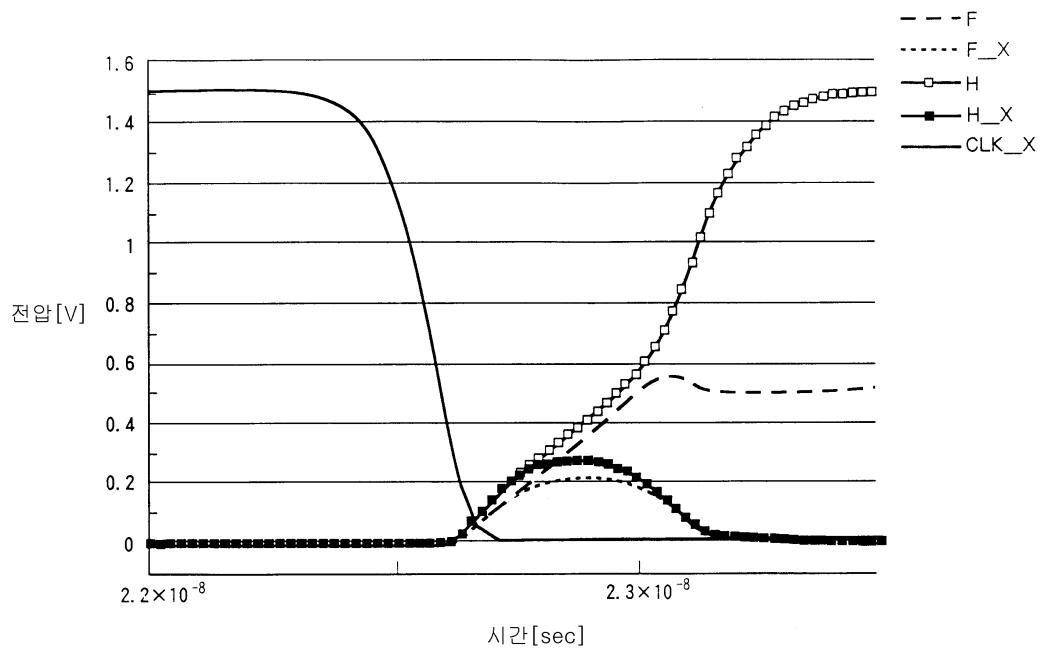

도 11은 노이즈를 부여하지 않은 경우의 도 1의 센스 증폭기 회로가 가동상(稼動相)(working phase)으로 바뀔 때의 과형(波形)을 나타낸 도면.

도 12는 노이즈를 부여하지 않은 경우의 도 1의 센스 증폭기 회로가 휴지상(休止相)(idle phase)으로 바뀔 때의 과형을 나타낸 도면.

도 13은 노이즈를 부여한 경우의 도 1의 센스 증폭기 회로가 가동상으로 바뀔 때의 과형을 나타낸 도면.

도 14는 커플링 노이즈(coupling noise)를 부여한 경우라도 정상 동작하는 최저 전원 전압을 나타낸 도면.

도 15는 본 발명에 관한 차동형 센스 증폭기 회로의 제2 실시 형태를 나타낸 회로도.

도 16은 노이즈를 부여하지 않은 경우의 도 7의 센스 증폭기 회로가 가동상으로 바뀔 때의 과형을 나타낸 도면.

도 17은 노이즈를 부여하지 않은 경우의 도 7의 센스 증폭기 회로가 휴지상으로 바뀔 때의 과형을 나타낸 도면.

도 18은 노이즈를 부여한 경우의 도 7의 센스 증폭기 회로가 가동상으로 바뀔 때의 과형을 나타낸 도면.

도 19는 도 7의 센스 증폭기 회로에서의 완료 신호(DONE\_X)의 과형을 나타낸 도면.

도 20은 본 발명에 관한 차동형 센스 증폭기 회로의 제3 실시 형태를 나타낸 회로도.

도 21은 노이즈를 부여하지 않은 경우의 도 12의 센스 증폭기 회로가 가동상으로 바뀔 때의 과형을 나타낸 도면.

도 22는 노이즈를 부여하지 않은 경우의 도 12의 센스 증폭기 회로가 휴지상으로 바뀔 때의 파형을 나타낸 도면.

도 23은 노이즈를 부여한 경우의 도 12의 센스 증폭기 회로가 가동상으로 바뀔 때의 파형을 나타낸 도면.

도 24는 본 발명에 관한 차동형 센스 증폭기 회로의 제4 실시 형태를 나타낸 회로도.

도 25는 노이즈를 부여하지 않은 경우의 도 16의 센스 증폭기 회로가 가동상으로 바뀔 때의 파형을 나타낸 도면.

도 26은 노이즈를 부여하지 않은 경우의 도 16의 센스 증폭기 회로가 휴지상으로 바뀔 때의 파형을 나타낸 도면.

도 27은 노이즈를 부여한 경우의 도 16의 센스 증폭기 회로가 가동상으로 바뀔 때의 파형을 나타낸 도면.

도 28은 도 24의 센스 증폭기 회로에서의 완료 신호(DONE\_X)의 파형을 나타낸 도면.

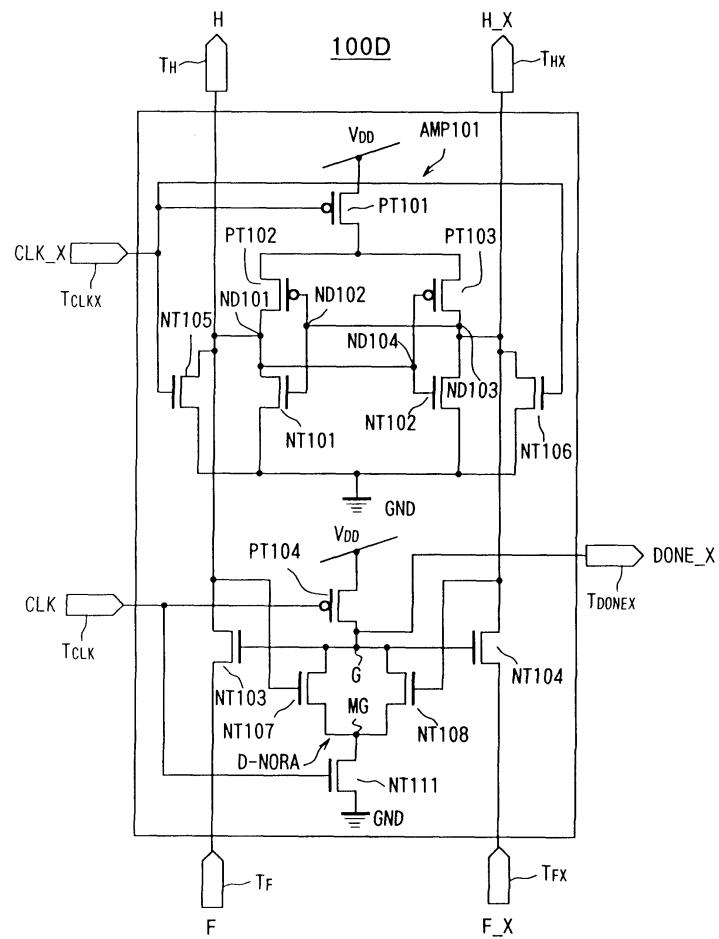

도 29는 본 발명에 관한 차동형 센스 증폭기 회로의 제5 실시 형태를 나타낸 회로도.

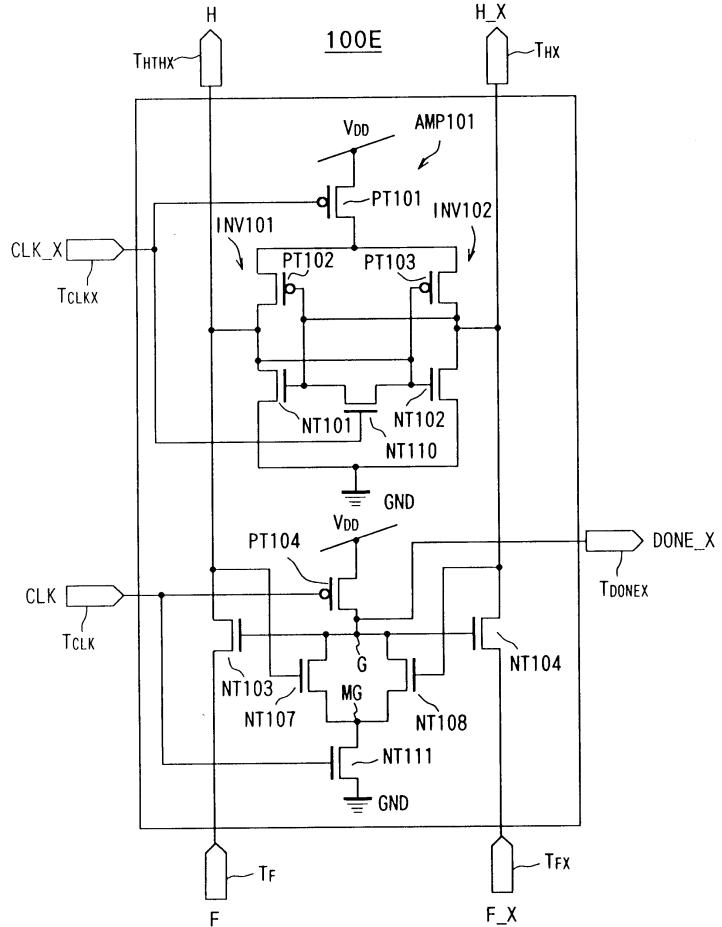

도 30은 본 발명에 관한 차동형 센스 증폭기 회로의 제6 실시 형태를 나타낸 회로도.

도 31은 본 발명에 관한 차동형 센스 증폭기 회로의 제7 실시 형태를 나타낸 회로도.

#### <도면의 주요 부분에 대한 부호의 설명>

100, 100A~100F: 차동형 센스 증폭기 회로, PT101~PT106: PMOS 트랜지스터, NT101~NT111: NMOS 트랜지스터, INV101, INV102: 인버터, AMP101: 센스 증폭기, D-NOR, D-NORA: 타이밍 NOR 회로, S-NOR: 스탠티 NOR 회로, G: 제어 절점, MG: 중간 절점.

#### 발명의 상세한 설명

##### 발명의 목적

##### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 CMOS 반도체 집적 회로에서의 차동(差動) 센스 증폭기와 이를 응용한 동적(動的) 논리 회로에 관한 것이다.

여기에서, "동적 논리 회로"란 내부 절점(節點)의 전위를 초기화하는 "휴지상(休止相)(idle phase)"과, 입력 신호에 따라 논리를 평가하고, 출력 절점의 전위를 확정하는 "가동상(稼動相)(working phase)"의 2개상을 클록(clock) 등의 제어 신호에 따라 교대하는 형식의 논리 회로를 말한다.

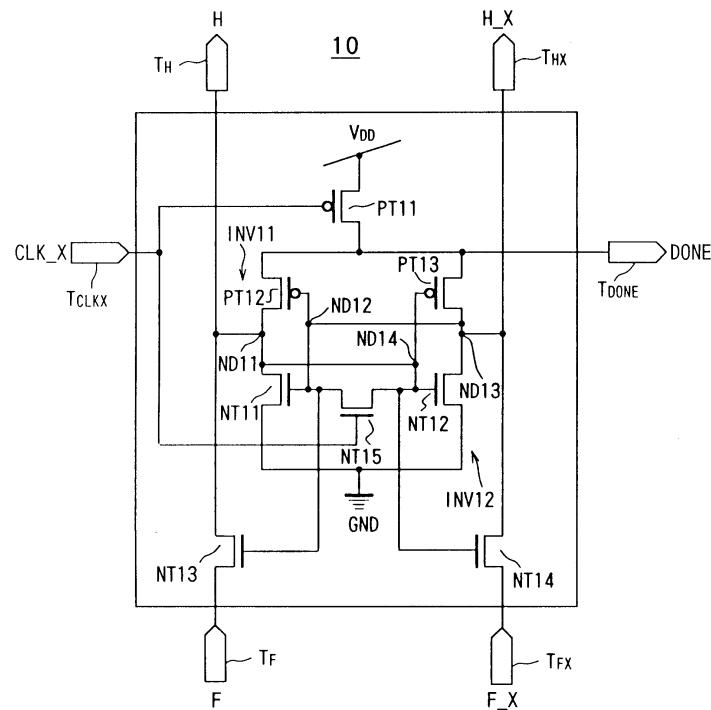

도 1은 종래의 차동형 센스 증폭기 회로의 한 구성예를 나타낸 회로도이다(문헌: Dinesh Somaseckhar and Kaushik Roy, "Differential Current Switch Logic: A Low Power DCVC Logic Family", IEEE JSSC, vol. 31, no. 7, pp. 981-991, July 1996. 참조).

이 차동형 센스 증폭기 회로(10)는, 도 1에 나타낸 바와 같이, p채널 MOS(PMOS) 트랜지스터(PT11~PT13, n채널 MOS(NMOS) 트랜지스터(NT11~NT15), 논리 입력 단자(TF, TFX), 논리 출력 단자(TH, THX), 클록 입력 단자(TCLKK), 및 논리 확정을 나타내는 완료 신호용 출력 단자(TDONE)를 가지고 있다.

PMOS 트랜지스터(PT11)의 소스가 전원 전압( $V_{DD}$ )의 공급 라인에 접속되고, 드레인(11)이 PMOS 트랜지스터(PT12, PT13)의 소스, 및 완료 신호용 출력 단자(TDONE)에 접속되어 있다.

PMOS 트랜지스터(PT12)와 NMOS 트랜지스터(NT11)의 드레인끼리 및 게이트끼리 접속되어 인버터(INV11)가 구성되어 있다.

PMOS 트랜지스터(PT12)와 NMOS 트랜지스터(NT11)의 드레인끼리의 접속점에 의해 인버터(INV11)의 출력 노드(ND11)가 구성되고, 게이트끼리의 접속점에 의해 인버터(INV11)의 입력 노드(ND12)가 구성되어 있다.

마찬가지로, PMOS 트랜지스터(PT13)와 NMOS 트랜지스터(NT12)의 드레인끼리 및 게이트끼리 접속되어 인버터(INV12)가 구성되어 있다.

PMOS 트랜지스터(PT13)와 NMOS 트랜지스터(NT12)의 드레인끼리의 접속점에 의해 인버터(INV12)의 출력 노드(ND13)가 구성되고, 게이트끼리의 접속점에 의해 인버터(INV12)의 입력 노드(ND14)가 구성되어 있다.

그리고, NMOS 트랜지스터(NT11 및 NT12)의 소스가 접지(接地)되어 있다.

인버터(INV11)의 출력 노드(ND11)가 인버터(INV12)의 입력 노드(ND14) 및 논리 출력 단자(TH)에 접속되고, 인버터(INV12)의 출력 노드(ND13)가 인버터(INV11)의 입력 노드(ND12) 및 논리 출력 단자(HX)에 접속되어 있다.

또, 인버터(INV11)의 입력 노드(ND12)와 인버터(INV12)의 입력 노드(ND14)와의 사이, 환연하면 NMOS 트랜지스터(NT11)의 게이트와 NMOS 트랜지스터(NT12)의 게이트와의 사이에 NMOS 트랜지스터(NT15)가 접속되어 있다.

또한, 논리 출력 단자(TH)와 논리 입력 단자(TF)와의 사이에 NMOS 트랜지스터(NT13)가 접속되고, 논리 출력 단자(THX)와 논리 입력 단자(TFX)와의 사이에 NMOS 트랜지스터(NT14)가 접속되어 있다.

그리고, PMOS 트랜지스터(PT11)의 게이트 및 NMOS 트랜지스터(NT15)의 게이트가 클록 입력 단자(TCLKX)에 접속되고, NMOS 트랜지스터(NT13)의 게이트가 인버터(INV11)의 입력 노드(ND12)에 접속되고, NMOS 트랜지스터(NT14)의 게이트가 인버터(INV12)의 입력 노드(ND14)에 접속되어 있다.

이상의 구성을 가지는 차동형 센스 증폭기 회로(10)는, 상기 문헌에 기재된 DCSL(Differential Current Switch Logic) 3 방식의 센스 증폭기 회로이다.

다음에 이 차동형 센스 증폭기 회로(10)의 동작 원리를, 시뮬레이션 파형(波形)을 나타낸 도 2 및 도 3과 연관시켜 설명한다.

그리고, 여기에서는, 휴지상에서 가동상으로 바뀌는 기점을 클록(CLK)의 상승으로 가정하고 있다. DCSL3 방식의 센스 증폭기 회로에서는, 제어 신호의 하강을 가동상에의 기점으로 하고 있으므로, 다음의 설명에서는 클록의 반전 신호(CLK\_X)를 도입하여, 설명에 이용한다.

도 2는 DCSL3 방식의 센스 증폭기 회로의 클록(CLK) 상승, 즉 클록 반전 신호(CLK\_X)의 하강 시의 동작 파형(시뮬레이션 결과)을 나타낸 도면이다. 다시 환연하면, 도 2는 클록(CLK-X)의 하강에서 휴지상으로부터 가동상으로 바뀌어, 논리가 확정되는 경과를 나타낸 것이다.

또, 도 3은 DCSL3 방식의 센스 증폭기 회로의 클록(CLK)의 하강, 즉 클록 반전 신호(CLK\_X)의 상승 시의 동작 파형(시뮬레이션 결과)을 나타낸 도면이다.

도 2 및 도 3에서, 횡축은 시간을 표시하고, 종축은 전압을 표시하고 있다.

도 2에 나타낸 바와 같이, 차동형 센스 증폭기(10)에서는, 클록 반전 신호(CLK\_X)가 논리 "1"에서 휴지상인 때, 논리 출력(H, H\_X)이 완전한 전위 OV로는 되지 않고, 대략 MOS의 임계값만큼 상승되어 있다.

이 논리 출력(H, H\_X)의 레벨, 즉 논리 출력 단자(TH, THX)의 전위는 NMOS 트랜지스터(NT13, NT14)의 게이트 전극에도 전달되어, 양 NMOS 트랜지스터(NT13, NT14)는 컷 오프(cut off)로 된다.

그러므로, 논리 입력 단자(TF, TFX)에 접속되는 도시하지 않은 논리 트리와 센스 증폭기 회로(10)가 전기적으로 분리된 상태로 되어 있다.

그리고, 클록 반전 신호(CLK\_X)가 논리 "0"으로 되어 가동상이 되면, PMOS 트랜지스터(PT11)가 온으로 되고, PMOS 트랜지스터(PT12, PT13)를 통해 전류가 흘러, 논리 출력 단자(TH, THX)의 전위가 상승되기 시작한다. 이 절점의 논리 출력 단자(TH, THX)의 전위는, NMOS 트랜지스터(NT13, NT14)의 게이트 전극에도 전달되고 있기 때문에, 양 NMOS 트랜지스터(NT13, NT14)는 온으로 되기 시작하여, 센스 증폭기로부터 논리 입력 단자(TF, TFX)로 전류를 흐르게 하기 시작한다.

그리고, 후술하는 바와 같이, 논리 입력 단자(TF, TFX)로 흘러 들어가는 전류에는 차가 있다. 이 차에 따라, PMOS 트랜지스터(PT11~PT13), 및 NMOS 트랜지스터(NT11, NT12)에 의해 구성되는 센스 증폭기는 논리 출력(H, H\_X)의 전위차를 확대하여 논리를 확정한다.

이 때, 논리 출력(H, H\_X)의 어느 한쪽은 반드시 논리 "0"으로 된다. 도면의 예에서는, 논리 출력(H\_X)이 논리 "0"으로 되어 있다.

그러므로, 논리 출력 단자(THX)에 대하여 접속 관계를 가지는 NMOS 트랜지스터(NT13)는 컷 오프로 된다. 이 NMOS 트랜지스터(NT13)는 논리 입력 단자(TF)에 대한 접속을 제어하는 스위치이다.

따라서, 논리 입력 단자(TF)로 흘러 들어가는 전류를 최소한의 필요로 억누를 수 있다.

클록 반전 신호(CLK\_K)가 논리 "1"로 되어 휴지상으로 되면, NMOS 트랜지스터(NT15)가 온으로 된다.

이에 따라, 논리 출력(H)의 단자(TH)를 포함하는 출력 라인 상에 존재하는 전하가 NMOS 트랜지스터(NT15)를 통해 논리 출력(H\_X)의 단자(THX)를 포함하는 출력 라인 상으로 흘러 들어가, 양 논리 출력 단자(TH, THX)의 전위는 동일하게 된다.

이 순간의 전위는 MOS의 임계값보다 약간 크기 때문에, NMOS 트랜지스터(NT11, NT12)는 약하게 온으로 된 상태가 된다. 그 결과, 이들을 통해 전류가 약간 방전된다. 따라서, 다음의 순간에는, 논리 출력 단자(TH, THX)의 전위는 MOS의 임계값과 거의 동일하게 된다.

이와 같은 구성, 기능을 가지는 DCSL3 방식의 차동형 센스 증폭기 회로(10)의 논리 입력 단자(TF, TFX)에 대하여 도 4에 나타낸 바와 같이, 예를 들면 NMOS 트랜지스터(NT21~NT34)로 구성되는 쌍대(雙對) 논리 트리(20)를 접속하여 동적(動的) 논리 회로가 실현된다.

"동적 논리 회로"란, 전술한 바와 같이, 내부 절점의 전위를 초기화하는 "휴지상"과, 입력 신호에 따라 논리 함수를 평가하고, 출력 절점의 전위를 확정하는 "가동상"의 2개 상을, 제어 신호에 따라 교대하는 형식의 논리 회로를 말한다. 제어 신호에는 일반적으로 클록이 사용된다.

전술한 바와 같이, DCSL3 방식의 센스 증폭기 회로(10)에서는, 이 휴지상에서 내부의 절점, 즉 논리 출력(H, H\_X)을 논리 "0"으로 초기화한다.

논리를 판정하는 가동상에서는, 도 1의 NMOS 트랜지스터(NT13, NT14)가 도통 상태로 되고, PMOS 트랜지스터(PT11~PT13)를 통해 전류가 논리 트리(20)로 흐른다.

이 때, 논리 입력(F와 F\_X)의 어느 한쪽은 반드시 그라운드(접지)에 이르는 경로를 가지며, 다른 한쪽은 경로 도중에서 컷 오프되어 있다.

따라서, 논리 입력 단자(TF)로 흘러 들어가는 전류와, 논리 입력 단자(TFX)로 흘러 들어가는 전류의 크기에 차가 생긴다.

도 1에서, PMOS 트랜지스터(PT11~PT13), 및 NMOS 트랜지스터(NT11, NT12)로 구성되는 센스 증폭기는 그 전류의 차에 따라 논리 출력(절점)(H, H\_X)의 전위차를 확대하여, 마침내는 논리 전위에 달하여 확정되기에 이른다.

### 발명이 이루고자 하는 기술적 과제

그런데, 전술한 DCSL3 방식의 차동형 센스 증폭기 회로(10)는 다음에 나타낸 3개의 과제가 있다.

DCSL3 방식의 제1 과제는, 논리 확정을 나타내는 완료 신호(DONE)가 완전하지 않은 것이다. 이 제1 과제에 대하여 도 5 와 연관시켜 설명한다.

도 5는 휴지상으로부터 가동상으로 바뀔 때의 완료 신호(DONE)의 모양을 나타낸 도면이다.

도 5에서 명백한 바와 같이, 휴지상에서의 완전 신호(DONE)는 NMOS 트랜지스터의 임계값보다 훨씬 커, 이미 논리 "0"을 의미하지 않는다.

또, 가동상으로 되어 완료 신호(DONE)가 상승하는 타이밍이 실제의 논리 출력(H, H\_X)의 확정 시기와 명백하게 상이하다.

따라서, 완료 신호(DONE)를 참조하도록 구성된 후단의 논리 회로는 오동작해 베릴 우려가 있다.

DCSL3 방식의 제2 과제는 휴지상에서의 논리 출력(H, H\_X)의 전위가 완전한 0V로는 되지 않는다고 하는 것이다. 전술한 바와 같이, 그 전위는 NMOS 트랜지스터의 임계값 근방으로 된다.

게이트 전극에 임계값 이하의 전위가 가해져, 컷 오프되어 있는 MOS라도, 실제로는 드레인 전류가 흐르고 있다. 일반적으로, 이것을 리크 전류(또는 컷 오프 리크)라고 한다. 그 전류의 양은 게이트 전위에 대하여 지수적(指數的)으로 변화되는 것이 알려지고 있다.

그 구체예를 도 6 (A) 및 6 (B)에 나타냈다.

도 6 (A) 및 6 (B)는 CMOS 인버터의 리크 전류에 대한 설명도이며, 도 6 (A)는 시뮬레이션 대상의 회로도, 도 6 (B)는 시뮬레이션 결과인 출력 전압, 리크 전류 대 입력 전압 특성을 나타낸 도면이다.

구체적으로는, 도 6 (B)는 동 도 6 (A)에 나타낸 바와 같은 CMOS 인버터에 대하여, 입력 단자의 전위를 0V로부터 전류 전압(1.5V)까지 변화시켰을 때의 출력 전위와 리크 전류에 대하여 정리한 것이다.

여기에서, 도 2 등으로부터, 휴지상에서의 출력(H, H\_X)의 전위를 0.2V 근방으로 본다.

도 6 (B)에 의하면, 입력 전압이 0.2V일 때 흐르는 리크 전류는 0.0V일 때의 그 100배이다.

따라서, DCSL3 방식의 차동형 센스 증폭기 회로에서는, 회로 정지(靜止) 시에서의 소비 전력이 커진다고 하는 문제가 있다.

DCSL3 방식의 제3 과제는 커플링 노이즈(coupling noise)에 의해 센스 증폭기가 오동작하는 것이다.

아주 가까운 거리에 있는 2개의 배선 간에는, 기생적(寄生的)인 용량 성분이 존재한다. 한쪽의 배선에 전위 변동이 생기면, 변동된 전위차의 시간 미분(微分)에 비례하는 변위 전류가 기생 용량을 통해 인접하는 배선으로 흘러 전위 변동을 발생시킨다. 이와 같이 부정한 전위 변동을 커플링 노이즈라고 한다.

도 7은 커플링 노이즈 내성(耐性) 평가용 모델을 나타낸 도면이다.

평가용 모델(30)에서는, 센스 증폭기 회로(10)의 주위에, 기생 용량(C31~C40)의 존재를 가정하고, 노이즈 전압원 (31~35)으로부터 절점(NZ1~NZ5)을 통해 센스 증폭기 내부의 절점(H, H\_X, F, F\_X)에 노이즈가 주어진다.

예를 들면, 절점(NZ1)에 상승 신호가 입력되면, 그 영향을 받아 절점(H)의 전위는 약간 상승한다.

도 8은 DCSL3 방식의 센스 증폭기 회로(10)에 대하여 그 모델을 적용하고, 클록 반전 신호(CLS\_X)의 하강과 동일한 정도의 타이밍으로, 절점(NZ1)에 하강 신호를 부여한 경우의 동작 파형을 나타낸 도면이다.

이 때의 입력 신호의 조건은 도 2의 경우와 동일하며, 정상으로 동작할 때에는 H=1, H\_X=0으로 된다.

그러나, 도 8에서는, H=0, H\_X=1로 되어 있다. 도면 중에서, 절점(NZ1)이 하강하는 기간 중, 논리 출력(H)의 전위가 논리 출력(H\_X)의 전위를 하회하는 현상이 보인다.

이는 노이즈를 부여하고 있지 않은 도 2 중에서는 일어나지 않는다. 도 2 중에서는, 논리 출력(H와 H\_X)의 전위가 동일하게 되어 있을 기간에, 도 8에서는, 절점(NZ1)의 영향을 받아 논리 출력(H)의 전위가 아주 적지만 낮게 되어 있다.

센스 증폭기 회로(10)는 이 부정으로 발생한 전위차를 확대해 버려, 잘못된 논리치를 확정해 버린다.

클록 반전 신호(CLD\_X)가 하강하는 것과 거의 동일 시기에, 외부로부터 하강 신호를 받으면 오동작한다고 하는 것은, 인근의 DCSL3 방식을 채용한 셀에서 발생한 클록 반전 신호(CLK\_X)의 하강에 의해 오동작을 일으킬 가능성을 시사하고 있다.

이와 같은 불안정한 회로는 실용적이 아니다.

본 발명은 이러한 사정을 감안하여 이루어진 것이며, 그 목적은 후단의 논리 회로를 오동작시키지 않는 완료 신호를 생성할 수 있고, 또 회로 정지 시에서의 소비 전력을 절감할 수 있고, 또 커플링 노이즈에 의해 오동작을 일으킬 우려가 없어, 실용적인 차동형 센스 증폭기 및 이를 사용한 동적 논리 회로를 제공하는 것에 있다.

### 발명의 구성 및 작용

상기 목적을 달성하기 위해, 본 발명은 제어 신호에 따라 휴지상 및 가동상 2개의 상(相)을 교대하는 차동형 센스 증폭기 회로로서, 제1 논리 입력 단자, 제2 논리 입력 단자, 제1 논리 출력 단자, 제2 논리 출력 단자, 제1 인버터, 및 제2 인버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차(差)에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기와, 휴지상을 나타내는 제어 신호를 받아 상기 제1 논리 입력 단자와 제2 논리 입력 단자를 기준 전위로 초기 설정하는 초기 설정 수단과, 상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단과, 상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단, 및 상기 휴지상을 나타내는 제어 신호를 받아 상기 제1 전환 수단과 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단, 및 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단을 가진다.

또, 본 발명에서는 상기 초기 설정 수단은 상기 제1 논리 출력 단자와 기준 전위와의 사이에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자와, 상기 제2 논리 출력 단자와 기준 전위와의 사이에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제2 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함하고, 상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제2 스위치 소자와, 상기 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제3 스위치 소자를 포함하고, 상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자와, 상기 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제5 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함하고, 상기 제2 설정 수단은 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제2 스위치 소자와, 상기 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 절점에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자와, 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 중간 절점 간에 접속되고, 상기 제1 스위치 소자가 도통될 때에는 비도통 상태로 유지되고, 상기 제1 스위치 소자가 비도통 상태로 유지될 때에는 도통되는 제4 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제3 스위치 소자를 포함하고, 상기 제2 설정 수단은 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자와, 상기 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 절점에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제5 스위치 소자와, 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 중간 절점 간에 접속되고, 상기 제3 스위치 소자가 도통될 때에는 비도통 상태로 유지되고, 상기 제3 스위치 소자가 비도통 상태로 유지될 때에는 도통되는 제6 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 제1 설정 수단의 제1 스위치 소자 또는 제3 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 n채널의 전하 효과 트랜지스터를 포함한다.

또, 본 발명에서는, 상기 제1 설정 수단의 제1 스위치 소자 또는 제3 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함한다.

또, 본 발명은 제어 신호에 따라 휴지상 및 가동상 2개의 상을 교대하는 차동형 센스 증폭기 회로로서, 제1 논리 입력 단자, 제2 논리 입력 단자, 제1 논리 출력 단자, 제2 논리 출력 단자, 제1 인버터, 및 제2 인버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기와, 휴지상을 나타내는 제어 신호를 받아 상기 제1 인버터의 입력과 제2 인버터의 입력을 접속하는 초기 설정 수단과, 상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단과, 상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단, 및 상기 휴지상을 나타내는 제어 신호를 받아 상기 제1 전환 수단과 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단, 및 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단을 가진다.

또, 본 발명에서는, 상기 초기 설정 수단은 상기 제1 인버터의 입력과 제2 인버터의 입력과의 사이에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함하고, 상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제2 스위치 소자와, 상기 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제2 스위치 소자를 포함하고, 상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2

전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자와, 상기 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함하고, 상기 제2 설정 수단은 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제2 스위치 소자와, 상기 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 절점에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자와, 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 중간 절점 간에 접속되고, 상기 제1 스위치 소자가 도통될 때에는 비도통 상태로 유지되고, 상기 제1 스위치 소자가 비도통 상태로 유지될 때에는 도통되는 제4 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제2 스위치 소자를 포함하고, 상기 제2 설정 수단은 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자와, 상기 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 절점에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자와, 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 중간 절점 간에 접속되고, 상기 제2 스위치 소자가 도통될 때에는 비도통 상태로 유지되고, 상기 제2 스위치 소자가 비도통 상태로 유지될 때에는 도통되는 제5 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 제1 설정 수단의 제1 스위치 소자 또는 제2 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 n채널의 전하 효과 트랜지스터를 포함한다.

또, 본 발명에서는, 상기 제1 설정 수단의 제1 스위치 소자 또는 제2 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함한다.

또, 본 발명에서는, 제어 신호에 따라 휴지상 및 가동상 2개의 상을 교대하는 차동형 센스 증폭기 회로로서, 제1 논리 입력 단자, 제2 논리 입력 단자, 제1 논리 출력 단자, 제2 논리 출력 단자, 제1 인버터, 및 제2 인버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기와, 휴지상을 나타내는 제어 신호를 받아 상기 제1 인버터의 입력과 제2 인버터의 입력을 접속하는 초기 설정 수단과, 상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단과, 상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단, 및 상기 휴지상 시, 상기 제1 논리 출력 단자 및 제2 논리 출력 단자 중 최소한 한쪽의 전위를 받아 상기 제1 전환 수단과 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단, 및 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단을 가진다.

또, 본 발명은, 상기 초기 설정 수단은 상기 제1 인버터의 입력과 제2 인버터의 입력과의 사이에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 직렬로 접속되고, 각각 휴지상 시의 제1 논리 출력 단자의 전위 및 제2 논리 출력 단자의 전위를 제어 단자에 받아 도통되는 제1 스위치 소자 및 제2 스위치 소자를 포함하고, 상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자와, 상기 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 직렬로 접속되고, 각각 휴지상 시의 제1 논리 출력 단자의 전위 및 제2 논리 출력 단자의 전위를 제어 단자에 받아 도통되는 제2 스위치 소자 및 제3 스위치 소자를 포함하고, 상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자와, 상기 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제5 스위치 소자를 포함한다.

또, 본 발명에서는, 상기 제1 설정 수단의 제1 및 제2 스위치 소자는, 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜ジ스터를 포함한다.

또, 본 발명에서는, 상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력한다.

또, 본 발명은 제어 신호에 따라 휴지상 및 가동상 2개의 상을 교대하는 동적(動的) 논리 회로로서, 제1 논리 입력 단자, 제2 논리 입력 단자, 제1 논리 출력 단자, 제2 논리 출력 단자, 제1 인버터와 제2 인버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기와, 휴지상을 나타내는 제어 신호를 받아 상기 제1 논리 입력 단자와 제2 논리 입력 단자를 기준 전위로 초기 설정하는 초기 설정 수단과, 상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단과, 상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단과, 상기 휴지상을 나타내는 제어 신호를 받아 상기 제1 전환 수단 및 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단과, 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제1 전환 수단 및 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단을 가지는 차동형 센스 증폭기 회로, 및 각각 상기 차동 센스 증폭기 회로의 제1 논리 입력 단자 및 제2 논리 입력 단자에 접속된 2선(線)을 가지고, 입력 신호에 따라 한쪽 선만이 기준 전위에 이르는 경로를 형성하는 2선식 논리 트리를 가진다.

또, 본 발명은 제어 신호에 따라 휴지상 및 가동상 2개의 상을 교대하는 동적 논리 회로로서, 제1 논리 입력 단자, 제2 논리 입력 단자, 제1 논리 출력 단자, 제2 논리 출력 단자, 제1 인버터와 제2 인버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기와, 휴지상을 나타내는 제어 신호를 받아 상기 제1 인버터의 입력과 제2 인버터의 입력을 접속하는 초기 설정 수단과, 상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단과, 상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단과, 상기 휴지상을 나타내는 제어 신호를 받아 상기 제1 전환 수단 및 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단과, 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제1 전환 수단 및 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단을 가지는 차동형 센스 증폭기 회로, 및 각각 상기 차동 센스 증폭기 회로의 제1 논리 입력 단자 및 제2 논리 입력 단자에 접속된 2선을 가지고, 입력 신호에 따라 한쪽 선만이 기준 전위에 이르는 경로를 형성하는 2선식 논리 트리를 가진다.

또, 본 발명은 제어 신호에 따라 휴지상 및 가동상 2개의 상을 교대하는 동적 논리 회로로서, 제1 논리 입력 단자, 제2 논리 입력 단자, 제1 논리 출력 단자, 제2 논리 출력 단자, 제1 인버터와 제2 인버터버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기와, 휴지상을 나타내는 제어 신호를 받아 상기 제1 인버터의 입력과 제2 인버터의 입력을 접속하는 초기 설정 수단과, 상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단과, 상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접

속 또는 분리하는 제2 전환 수단과, 상기 휴지상 시에 상기 제1 논리 출력 단자 및 제2 논리 출력 단자 중 최소한 한쪽의 전위를 받아 상기 제1 전환 수단 및 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단과, 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단을 가지는 차동형 센스 증폭기 회로, 및 각각 상기 차동 센스 증폭기 회로의 제1 논리 입력 단자 및 제2 논리 입력 단자에 접속된 2선을 가지고, 입력 신호에 따라 한쪽 선만이 기준 전위에 이르는 경로를 형성하는 2선식 논리 트리를 가진다.

본 발명에 의하면, 휴지상을 나타낸 제어 신호가 공급되면, 센스 증폭기 회로의 제1 논리 출력 단자 및 제2 논리 출력 단자가 기준 전위, 예를 들면 0V(제2 레벨)로 초기 설정된다.

이에 따라, 접속 설정 수단의 제2 설정 수단에 의한 제2 전원 전위에의 설정은 억지되고, 제1 설정 수단에 의해 제어 절점이 대략 제1 전원 전위로 설정된다. 그 결과, 제1 전환 수단에 의해 제1 논리 입력 단자와 제2 논리 출력 단자가 전기적으로 접속되고, 또한 제2 전환 수단에 의해 제2 논리 입력 단자와 제2 논리 출력 단자가 전기적으로 접속된다.

여기에서, 가동상으로 전환되면, 접속 설정 수단의 제1 설정 수단에 의한 제1 전원 전위에의 설정은 억제되고, 제2 설정 수단에 의해 제어 절점이 제2 전원 전위로 설정된다.

그리고, 센스 증폭기에서, 제1 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 전위와 제2 논리 출력의 논리 전위가 (제1 레벨, 제2 레벨)이거나 (제2 레벨, 제1 레벨)로 확정된다.

### 제1 실시 형태

도 9는 본 발명에 관한 차동형 센스 증폭기 회로의 제1 실시 형태를 나타낸 회로도이다.

이 차동형 센스 증폭기 회로(100)는 도 9에 나타낸 바와 같이, PMOS 트랜지스터(PT101~PT103), NMOS 트랜지스터(NT101~NT109), 제1 논리 입력 단자(TF), 제2 논리 입력 단자(TFX), 제1 논리 출력 단자(TH), 제2 논리 출력 단자(THX), 클록 입력 단자(TCLKX), 및 논리 확정을 나타내는 완료 신호용 출력 단자(TDONE)를 가지고 있다.

PMOS 트랜지스터(PT101)의 소스가 전원 전압( $V_{DD}$ )의 공급 라인에 접속되고, 드레인이 PMOS 트랜지스터(PT102, PT103)의 소스에 접속되어 있다.

PMOS 트랜지스터(PT102)와 NMOS 트랜지스터(NT101)의 드레인끼리 및 게이트끼리 접속되어 인버터(INV101)가 구성되어 있다.

PMOS 트랜지스터(PT102)와 NMOS 트랜지스터(NT101)의 드레인끼리의 접속점에 의해 인버터(INV101)의 출력 노드(ND101)가 구성되고, 게이트끼리의 접속점에 의해 인버터(INV101)의 입력 노드(ND102)가 구성되어 있다.

마찬가지로, PMOS 트랜지스터(PT103)와 NMOS 트랜지스터(NT102)의 드레인끼리 및 게이트끼리 접속되어 인버터(INV102)가 구성되어 있다.

PMOS 트랜지스터(PT103)와 NMOS 트랜지스터(NT102)의 드레인끼리의 접속점에 의해 인버터(INV102)의 출력 노드(ND103)가 구성되고, 게이트끼리의 접속점에 의해 인버터(INV102)의 입력 노드(ND104)가 구성되어 있다.

그리고, NMOS 트랜지스터(NT101 및 NT102)의 소스가 접지되어 있다.

인버터(INV101)의 출력 노드(ND101)가 인버터(INV102)의 입력 노드(ND104) 및 논리 출력 단자(TH)에 접속되고, 인버터(INV102)의 출력 노드(ND103)가 인버터(INV101)의 입력 노드(ND102) 및 논리 출력 단자(HX)에 접속되어 있다.

이상의 접속 관계에 있는 PMOS 트랜지스터(PT101~PT103, 및 NT101, NT102)에 의해 센스 증폭기(AMP101)가 구성되어 있다.

논리 출력 단자(TH)와 논리 입력 단자(TF)와의 사이에 제1 전환 수단으로서의 NMOS 트랜지스터(103)가 접속되고, 논리 출력 단자(THX)와 논리 입력 단자(TFX)와의 사이에 제2 전환 수단으로서의 NMOS 트랜지스터(NT104)가 접속되어 있다.

또, 논리 출력 단자(TH)와 접지와의 사이에 초기 설정 수단의 제1 스위치 소자로서의 NMOS 트랜지스터(NT105)가 접속되고, 논리 출력 단자(THX)와 접지와의 사이에 제2 스위치 소자로서의 NMOS 트랜지스터(NT106)가 접속되어 있다.

이들 NMOS 트랜지스터(NT105, NT106)는 휴지상(CLK\_X=1)인 때 논리 출력(H, H\_X)을 0V로 내리는, 즉 기준 전위로 초기 설정하기 위해 이용된다.

또한, NMOS 트랜지스터(NT107 및 NT108)의 소스는 접지되고, 이들의 드레인은 NMOS 트랜지스터(NT103 및 NT104)의 게이트, NMOS 트랜지스터(NT109)의 드레인, 및 완료 신호용 출력 단자(TDONE)에 공통으로 접속되어 있다. 또, NMOS 트랜지스터(NT109)의 소스가 전원 전압( $V_{DD}$ )의 공급 라인에 접속되어 있다.

그리고, PMOS 트랜지스터(PT101)의 게이트, NMOS 트랜지스터(NT105, NT106, 및 NT109)의 클록 입력 단자(TCLKX)에 접속되어 있다.

NMOS 트랜지스터(NT107)의 게이트가 논리 입력 단자(TH)와 NMOS 트랜지스터(NT103)의 접속점에 접속되고, NMOS 트랜지스터(NT108)의 게이트가 논리 입력 단자(THX)와 NMOS 트랜지스터(NT104)의 접속점에 접속되어 있다.

그리고, 상기한 접속 관계를 가지는 NMOS 트랜지스터(NT107~NT109)에 의해 다이내믹 NOR 회로가 구성되어, 논리 트리 분리의 접속 제어 수단으로서 기능한다.

다음에, 상기 구성에 의한 동작을 설명한다.

먼저, 휴지상에서는 클록 신호(CLK)가 논리 "0", 즉 로크 반전 신호(CLK\_X)가 논리 "1"에서 클록 입력 단자(TCLKX)를 통해, PMOS 트랜지스터(PT101)의 게이트, 및 NMOS 트랜지스터(NT105, NT106, NT109)의 게이트에 공급된다.

이에 따라, PMOS 트랜지스터(PT101)는 오프 상태로 유지되고, 센스 증폭기(AMP101)는 비가동 상태에 있다.

한편, NMOS 트랜지스터(NT105, 및 NT106)가 오프로 되고, 논리 출력 단자(TH, THX)의 전위는 완전히 0V까지 내려간다.

그 결과, 이 논리 출력 단자(TH, THX)에 게이트가 접속된 NMOS 트랜지스터(NT107, 및 NT108)는 컷 오프된다.

이 때, 논리 "1"의 클록 반전 신호(CLK\_X)를 받은 NMOS 트랜지스터(NT109)는 온으로 된다. 그 결과, 논리 트리 분리용의 NMOS 트랜지스터(NT103, NT104)의 게이트에 접속된 제어 절점(G)이 대략 전원 전압( $V_{DD}$ ) 레벨까지 프리차지(precharge)된다. 실제로는,  $V_{DD} - V_{th}$ ( $V_{th}$ 는 NMOS 트랜지스터의 임계값)까지 프리차지된다. 이 프리차지 전위는 NMOS 트랜지스터(NT103, NT104)를 전류를 통과시키는데 충분한 정도로 온 하는 데 가능한 전위이다.

이에 따라, NMOS 트랜지스터(NT103, NT104)가 전류를 통과시킬 정도로 온되어, 센스 증폭기(AMP101)와 논리 입력 단자(TF, TFX)에 접속되는 도시하지 않은 논리 트리가 전기적으로 접속된다.

즉, 휴지상에서 센스 증폭기(AMP101)와 논리 트리가 전기적으로 접속된다.

이 상태에서 가동상으로 되어, 클록 신호(CLK)가 논리 "1", 즉 로크 반전 신호(CLK\_X)가 논리 "0"에서 로크 입력 단자(TCLKX)를 통해, PMOS 트랜지스터(PT101)의 게이트, 및 NMOS 트랜지스터(NT105, NT106, NT109)의 게이트에 공급된다.

이에 따라, PMOS 트랜지스터(PT101)가 온되고, NMOS 트랜지스터(NT105, NT106)가 컷 오프로 되어, 센스 증폭기(AMP101)가 가동된다.

이 때, NMOS 트랜지스터(NT103, NT104)는 휴지상으로부터 온으로 되어 있기 때문에, 논리 입력 단자(TF, TFX)로 향해 곧 전류가 흐르기 시작하여, 논리 평가가 개시된다.

이 전류의 차가 센스 증폭기(AMP101)에 의해 전위차로서 확대되어, 마침내 논리가 확정된다.

이 도중, 논리 출력(H)이 논리 "1"에 근접하고 있는 경우에는, 게이트가 논리 출력 단자(TH)에 접속된 다이내믹 NOR 회로(D-NOR)의 NMOS 트랜지스터(NT107)가 온으로 된다.

또는, 논리 출력(H\_X)이 논리 "1"에 근접하고 있는 경우에는, 게이트가 논리 출력 단자(THX)에 접속된 다이내믹 NOR 회로(D-NOR)의 NMOS 트랜지스터(NT108)가 온으로 된다.

어느 경우라도, 제어 절점(C)에 있던 전하는 방전되어, 그 전위는 0V로 된다.

이에 따라, NMOS 트랜지스터(NT103, NT104)는 컷 오프로 되어, 센스 증폭기와 논리 트리는 전기적으로 분리된다.

이 움직임에 의해, 센스 증폭기(AMP101)로부터 논리 트리로 흘러 들어가는 전류가 최소한의 필요로 억제된다.

또, 도 10에 나타낸 바와 같이, 전술한 바와 같은 차동형 센스 증폭기 회로(100)와, NMOS 쌍대 논리 트리(2선식 논리 트리)(200)를 조합함으로써, 그 논리 트리가 실현하는 논리 함수에 따른 동적 논리 회로(300)를 실현할 수 있다.

도 10의 예에서는, NMOS 쌍대 논리 트리(2선식 논리 트리)(200)를 NMOS 트랜지스터(NT201~NT214)로 이루어지는 4 입력 EXOR에 의해 구성하여, 동적 논리 회로(300)를 실현하고 있다.

NMOS 쌍대 논리 트리(200)에서, NMOS 트랜지스터(NT201, NT205, NT209, NT213)가 센스 증폭기 회로(100)의 논리 입력 단자(TF)와 접지와의 사이에 직렬로 접속되어 있다.

또, NMOS 트랜지스터(NT204, NT208, NT212, NT214)가 센스 증폭기 회로(100)의 논리 입력 단자(TFX)와 접지와의 사이에 직렬로 접속되어 있다.

논리 입력 단자(TFX)와, NMOS 트랜지스터(NT201 및 NT205)의 접속점과의 사이에 NMOS 트랜지스터(NT202)가 접속되고, 논리 입력 단자(TF)와, NMOS 트랜지스터(NT204 및 NT208)의 접속점과의 사이에 NMOS 트랜지스터(NT203)가 접속되어 있다.

그리고, NMOS 트랜지스터(NT201 및 NT204)의 게이트에 신호(A4)가 공급되고, NMOS 트랜지스터(NT202 및 NT203)의 게이트에 신호(A4)의 반전 신호(A4\_X)가 공급된다.

NMOS 트랜지스터(NT203 및 NT204)의 접속점과 NMOS 트랜지스터(NT205 및 NT209)의 접속점과의 사이에 NMOS 트랜지스터(NT206)가 접속되고, NMOS 트랜지스터(NT201 및 NT202)의 접속점과 NMOS 트랜지스터(NT208 및 NT212)의 접속점과의 사이에 NMOS 트랜지스터(NT207)가 접속되어 있다.

그리고, NMOS 트랜지스터(NT205 및 NT208)의 게이트에 신호(A3)가 공급되고, NMOS 트랜지스터(NT206 및 NT207)의 게이트에 신호(A3)의 반전 신호(A3\_X)가 공급된다.

NMOS 트랜지스터(NT207 및 NT208)의 접속점과 NMOS 트랜지스터(NT209 및 NT213)의 접속점과의 사이에 NMOS 트랜지스터(NT210)가 접속되고, NMOS 트랜지스터(NT205 및 NT206)의 접속점과 NMOS 트랜지스터(NT212 및 NT214)의 접속점과의 사이에 NMOS 트랜지스터(NT211)가 접속되어 있다.

그리고, NMOS 트랜지스터(NT209 및 NT212)의 게이트에 신호(A2)가 공급되고, NMOS 트랜지스터(NT210 및 NT211)의 게이트에 신호(A2)의 반전 신호(A2\_X)가 공급된다.

또, NMOS 트랜지스터(NT213)의 게이트에 신호(A1)가 공급되고, NMOS 트랜지스터(NT214)의 게이트에 신호(A1)의 반전 신호(A1\_X)가 공급된다.

2선식 논리 트리(200)에서는, 센스 증폭기 회로(100)에의 논리 입력(F)의 라인과 논리 입력(F\_X)의 라인 중 어느 한쪽이 반드시 접지에 이르는 경로를 가지며, 다른 쪽은 경로 도중에서 컷 오프된다.

그리고, 도 9의 센스 증폭기 회로(100)를 사용하여 도 10에 나타낸 바와 같은, 4입력 EXOR 동적 논리 회로(300)로서 구성 하여, 시뮬레이션을 행하였다. 또, 노이즈 내성 평가도 동일하게 행하였다.

또 11은 노이즈를 부여하지 않은 경우의 도 9의 센스 증폭기 회로(100)가 가동상으로 바뀔 때의 파형을 나타낸 도면이며, 도 12는 노이즈를 부여하지 않은 경우의 도 9의 센스 증폭기 회로(100)가 휴지상으로 바뀔 때의 파형을 나타낸 도면이며, 도 13은 노이즈를 부여한 경우의, 도 9의 센스 증폭기 회로(100)가 가동상으로 바뀔 때의 파형을 나타낸 도면이다.

도 11, 도 12, 및 도 13에서, 횡축은 시간을 표시하고, 종축은 전압을 표시하고 있다.

먼저, 도면에는 표시되어 있지 않지만, 도 9의 차동형 센스 증폭기 회로(100)에서, 논리가 확정된 것을 나타내는 완료 신호(DONE)는 0V에서 대략 전원 전압 레벨까지 진폭(振幅)했다.

따라서, 도 9의 차동형 센스 증폭기 회로(100)에 의하면, 종래 기술의 제1 과제는 해결되었다.

도 11을 보면 명백한 바와 같이, 가동상으로 바뀌기 직전의 휴지상에서, 논리 출력(H, H\_X)은 이상적인 0V로 되어 있다.

또, 도 12에 나타낸 바와 같이, 도 9의 차동형 센스 증폭기 회로(100)에서는, 휴지상으로 바뀌면 신속하게 0V로 내려간다.

따라서, 도 9의 차동형 센스 증폭기 회로(100)에 의하면, 휴지상에서 논리 출력(H, H\_X)이 0V로 되지 않고, NMOS 임계 값 전압만큼 상승하므로, 리크 전류가 커진다고 하는, 종래 기술의 제2 과제는 해결되었다.

또, 도 13을 보면 명백한 바와 같이, 본 발명에서는 오동작은 보이지 않는다.

도 7의 평가용 모델(30)에서의 노이즈(NZ1)의 하강 영향을 받아 논리 출력(H)의 전위가 논리 출력(H\_X)보다 낮아지고 있는 기간이 존재한다.

DCSL3 방식의 센스 증폭기 회로에서는, 이대로 전위차가 확대되어 버렸다.

그러나, 도 9의 센스 증폭기 회로에서는, 도 13에 나타낸 바와 같이, 이 노이즈의 전위차를 역전하여, 옳바른 논리치로 향해 논리 출력(H, H\_X)의 전위가 수속(收束)되어 가는 모양이 묘사되어 있다.

이 현상은 센스 증폭기 회로(100)가 가지는, NMOS 트랜지스터(NT107~NT109)에 의해 구성된 다이내믹 NOR 회로(D-NOR)에 의한 논리 트리 분리 제어 기구의 움직임에 의해 실현되고 있다.

따라서, 도 9의 차동형 센스 증폭기 회로(100)에 의하면, 커플링 노이즈에 의해 센스 증폭기가 잘못된 값으로 확정되어 버린다고 하는, 종래 기술의 제3 과제는 해결되었다.

커플링 노이즈에 의한 오동작은, 논리 트리의 높이와 전원 전압에 의존한다.

일반적으로, 전원 전압이 낮고, 논리 트리가 높아질수록, 커플링 노이즈에 의해 오동작되기 쉽게 된다.

도 14는 커플링 노이즈를 부여한 경우라도 정상 동작하는 최저 전원 전압을 나타낸 도면이다. 그리고, 도 14에서는, 도 9의 센스 증폭기 회로(100)는 N2형으로서 나타내고 있다.

EXOR의 논리 트리의 높이는 그 입력 차수(次數)와 동일하다.

도 14에서 명백한 바와 같이, 종래의 DCSL3 방식의 센스 증폭기 회로에서는, 전원 전압이 높고, 논리 트리가 낮아도 오동작을 일으킨다.

한편, 본 발명에 관한 N2형의 센스 증폭기 회로(100)를 사용한 EXOR 논리에서는, 조건에도 의하지만 대체로 1.5V보다 낮은 전압에서도 동작 가능하다.

따라서, 도 9의 센스 증폭기 회로(100)를 사용하여 동적 논리 회로를 구성하면, 저전원 전압에서 안정된 동작을 하는 동적 논리 회로를 실현할 수 있다.

일반적으로, CMOS 논리 회로의 소비 전력은 전원 전압의 2승(乘)에 비례한다. 예를 들면, 전원 전압을 1/2로 하면, 소비 전력은 1/4로 된다.

즉, 도 9의 센스 증폭기 회로(100)에 의하면, CMOS 반도체 집적 회로의 소비 전력을 대폭 절감하는 데 기여하는 것이다.

이상 설명한 바와 같이, 본 제1 실시 형태에 의하면, 휴지상에서 센스 증폭기(AMP101)의 논리 출력 단자(TH, THX)의 전위를 0V(논리 "0")로 초기 설정하는 NMOS 트랜지스터(NT105, NT106)와, 논리 출력 단자(TH, THX)와 논리 입력 단자(TF, TFX)를 작동적으로 접속하는 NMOS 트랜지스터(NT103, NT104)와, 휴지상에서는 NMOS 트랜지스터(NT103, NT104)를 도통시키고, 가동상에서는 논리 입력(F, F\_X)가 가지는 도통 저항의 차에 따라 논리 출력(H, H\_X)의 논리 전위를 (0, 1)이거나 (1, 0)으로 확정시키는 논리 트리 분리 수단으로서의 다이내믹 NOR 회로(D-NOR)를 형성했으므로, 후단의 논리 회로를 오동작시키지 않는 완료 신호를 생성할 수 있고, 또 회로 정지 시에서의 소비 전력을 절감할 수 있다.

또, 커플링 노이즈에 의해 오동작을 일으킬 우려가 없어, 실용적인 차동형 센스 증폭기 및 이를 사용한 동적 논리 회로를 실현할 수 있다.

## 제2 실시 형태

도 15은 본 발명에 관한 차동형 센스 증폭기 회로의 제2 실시 형태를 나타낸 회로도이다.

본 제2 실시 형태가 전술한 제1 실시 형태와 상이한 점은, 다이내믹 NOR 회로의 전원 전압(V<sub>DD</sub>)의 공급 라인과 제어 절점(G)을 프리차지용 NMOS 트랜지스터에 대신하여 프리차지용 PMOS 트랜지스터(PT104)에 의해 접속하고, PMOS 트랜지스터(PT104)의 게이트를 클록 반전 신호(CLK\_X)의 클록 입력 단자(TCLKX) 대신에, 클록 신호(CLK)의 클록 입력 단자(TCLK)에 접속한 것에 있다.

그 밖의 구성 및 작용은 전술한 제1 실시 형태와 동일하여, 그 상세한 설명은 생략한다.

도 15의 센스 증폭기 회로(100A)를 사용하여, 도 10에 나타낸 바와 같은, 4입력 EXOR 동적 논리 회로(300)로서 구성하고, 시뮬레이션을 행하였다. 또 노이즈 내성 평가도 동일하게 행하였다.

또 16은 노이즈를 부여하지 않은 경우의 도 15의 센스 증폭기 회로(100A)가 가동상으로 바뀔 때의 과형을 나타낸 도면이며, 도 17은 노이즈를 부여하지 않은 경우의 도 15의 센스 증폭기 회로(100A)가 휴지상으로 바뀔 때의 과형을 나타낸 도면이며, 도 18은 노이즈를 부여한 경우의, 도 15의 센스 증폭기 회로(100A)가 가동상으로 바뀔 때의 과형을 나타낸 도면이다.

또, 도 19는 도 15의 센스 증폭기 회로(100A)에서의 완료 신호(DONE\_X)의 과형을 나타낸 도면이다.

도 16, 도 17, 및 도 18에서, 횡축은 시간을 표시하고, 종축은 전압을 표시하고 있다.

먼저, 도 19에서 명백한 바와 같이, 도 15의 차동형 센스 증폭기 회로(100A)에서, 논리가 확정된 것을 나타내는 완료 신호(DONE\_X)는 0V에서 전원 전압 레벨까지 완전히 진폭하고 있다.

또, 논리 출력(H)의 과형과 진폭의 중앙치에 가까운 곳에서 교차되고 있어, 천이(遷移)되는 타이밍도 이상적인 것이라고 할 수 있다.

따라서, 도 15의 차동형 센스 증폭기 회로(100A)에 의하면, 종래 기술의 제1 과제는 해결되었다.

도 16을 보면 명백한 바와 같이, 가동상으로 바뀌기 직전의 휴지상에서, 논리 출력(H, H\_X)은 이상적인 0V로 되어 있다.

또, 도 17에 나타낸 바와 같이, 도 15의 차동형 센스 증폭기 회로(100A)에서는, 휴지상으로 바뀌면 신속하게 0V로 내려간다.

따라서, 도 15의 차동형 센스 증폭기 회로(100A)에 의하면, 휴지상에서 논리 출력(H, H\_X)이 0V로 되지 않고, NMOS 임계값 전압만큼 상승하므로, 리크 전류가 커진다고 하는, 종래 기술의 제2 과제는 해결되었다.

또, 도 18을 보면 명백한 바와 같이, 본 발명에서는 오동작은 보이지 않는다.

도 7의 평가용 모델(30)에서의 노이즈(NZ1)의 하강 영향을 받아 논리 출력(H)의 전위가 논리 출력(H\_X)보다 낮아지고 있는 기간이 존재한다.

DCSL3 방식의 센스 증폭기 회로에서는, 이대로 전위차가 확대되어 버렸다.

그러나, 도 15의 센스 증폭기 회로에서는, 도 18에 나타낸 바와 같이, 이 노이즈의 전위차를 역전하여, 옳바른 논리치로 향해 논리 출력(H, H\_X)의 전위가 수속되어 가는 모양이 묘사되어 있다.

이 현상은 센스 증폭기 회로(100A)가 가지는, PMOS 트랜지스터(PT104) 및 NMOS 트랜지스터(NT107, NT108)에 의해 구성된 다이내믹 NOR 회로(D-NORA)에 의한 논리 트리 분리 제어 기구의 움직임에 의해 실현되고 있다.

따라서, 도 15의 차동형 센스 증폭기 회로(100A)에 의하면, 커플링 노이즈에 의해 센스 증폭기가 잘못된 값으로 확정되어 버린다고 하는, 종래 기술의 제3 과제는 해결되었다.

전술한 바와 같이, 커플링 노이즈에 의한 오동작은, 논리 트리의 높이와 전원 전압에 의존한다.

일반적으로, 전원 전압이 낮고, 논리 트리가 높아질수록, 커플링 노이즈에 의해 오동작되기 쉽게 된다.

또, 커플링 노이즈를 부여한 경우라도 정상 동작하는 최저 전원 전압을 나타낸 도 14에서는, 도 15의 센스 증폭기 회로(100A)는 P2형으로서 나타내고 있다.

전술한 바와 같이, EXOR의 논리 트리의 높이는 그 입력 차수(次數)와 동일하다.

도 14에서 명백한 바와 같이, 종래의 DCSL3 방식의 센스 증폭기 회로에서는, 전원 전압이 높고, 논리 트리가 낮아도 오동작을 일으킨다.

한편, 본 발명에 관한 P2형의 센스 증폭기 회로(100A)를 사용한 EXOR 논리에서는, 조건에도 의하지만 대체로 1.5V보다 낮은 전압에서도 동작 가능하다. 또한, 이 P2형의 센스 증폭기 회로(100A)에서는, 0.7V 부근에서 조차도 오동작을 일으키지 않는다.

따라서, 도 15의 센스 증폭기 회로(100A)를 사용하여 동적 논리 회로를 구성하면, 저전원 전압에서 안정된 동작을 하는 동적 논리 회로를 실현할 수 있다.

그리고, 도 9의 센스 증폭기 회로와 마찬가지로, 도 15의 센스 증폭기 회로(100A)에 의하면, CMOS 반도체 집적 회로의 소비 전력을 대폭 절감하는 데 기여하는 것이다.

이상 설명한 바와 같이, 본 제2 실시 형태에 의하면, 전술한 제1 실시 형태의 효과와 동일한 효과를 얻을 수 있다.

### 제3 실시 형태

도 20은 본 발명에 관한 차동형 센스 증폭기 회로의 제3 실시 형태를 나타낸 회로도이다.

본 제3 실시 형태가 전술한 제1 실시 형태와 상이한 점은, 휴지상(CLK\_X=1)인 때 논리 출력(H, H\_X)을 0V로 내리는 디스차지 수단으로서의 NMOS 트랜지스터(NT105, NT106) 대신에, 센스 증폭기(AMP101)를 구성하는 인버터(INV101)의 입력 노드(ND102)와 인버터(INV102)의 입력 노드(ND104)와의 사이, 환연하면 NMOS 트랜지스터(NT101)의 게이트와 NMOS 트랜지스터(NT102)의 게이트와의 사이를 NMOS 트랜지스터(NT110)에 의해 접속하고, NMOS 트랜지스터(NT110)의 게이트를 클록 반전 신호(CLK\_X)의 클록 입력 단자(TCLKX)에 접속한 것에 있다.

이 차동형 센스 증폭기 회로(100B)의 가동상에서의 행동은, NMOS 트랜지스터(NT110)에 관한 것 이외는 도 9의 센스 증폭기 회로와 동일하므로, 그 설명은 생략한다.

다음에, 도 20의 센스 증폭기 회로(100B)의 동작을, 도 9의 센스 증폭기 회로의 동작과 상이한 점을 중심으로 설명한다.

가동상으로부터 휴지상으로 바뀌면, 클록 반전 신호(CLK\_X)가 논리 "0"으로부터 논리 "1"로 바뀌고, NMOS 트랜지스터(NT110)가 온으로 된다. 그 결과, 논리 출력 단자(TH와 THX)가 전기적으로 접속되어, 전하의 평형 상태가 형성된다.

따라서, 논리 출력(H, H\_X)의 전위는 NMOS 트랜지스터(NT101, NT102)의 임계값 근방으로 된다.

이에 따라, 다이내믹 NOR 회로를 구성하는 D-NOR의 NMOS 트랜지스터(NT107, NT108)는 컷 오프된다.

이 때, 프리차지용 NMOS 트랜지스터(NT109)는 클록 반전 신호(CLK\_X)가 논리 "0"으로부터 논리 "1"로 전환됨에 따라 온으로 된다.

NMOS 트랜지스터(NT109)를 통해 제어 절점(G)에 전하가 공급된다.

그 결과, 논리 트리 분리용의 NMOS 트랜지스터(NT103, NT104)의 게이트에 접속된 제어 절점(G)이 대략 전원 전압( $V_{DD}$ ) 레벨까지 프리차지된다. 실제로는,  $V_{DD} - V_{th}$ ( $V_{th}$ 는 NMOS 트랜지스터의 임계값)까지 프리차지된다. 이 프리차지 전위는 NMOS 트랜지스터(NT103, NT104)를 전류를 통과시키는데 충분한 정도로 온 하는 것이 가능한 전위이다.

이에 따라, NMOS 트랜지스터(NT103, NT104)가 전류를 통과시킬 정도로 온되어, 센스 증폭기(AMP101)와 논리 입력 단자(TF, TFX)에 접속되는 도시하지 않은 논리 트리가 전기적으로 접속된다.

즉, 휴지상에서 재차, 센스 증폭기(AMP101)와 논리 트리가 전기적으로 접속된다.

그리고, 논리 입력 단자(TF, TFX) 중 어느 한쪽은 반드시 그라운드에 이르는 경로를 가지며, NMOS 트랜지스터(NT103, NT104) 중 어느 한쪽을 통해, 논리 출력 단자(TH, THX)에 남아 있던 전하를 뽑아낸다.

이 결과, 논리 출력(H, H\_X)의 전위는 0V까지 내려가게 된다. 예를 들면, 논리 입력(F) 쪽이 그라운드에 이르는 경로를 갖고 있는 경우, 논리 출력(H)의 전하는 NMOS 트랜지스터(NT103)를 통해 뽑혀진다.

한편, 논리 출력(H\_X)의 전하는 NMOS 트랜지스터(NT110)를 경유한 다음, NMOS 트랜지스터(NT103)를 통해 뽑혀진다.

도 20의 센스 증폭기 회로(100B)를 사용하여, 도 10에 나타낸 바와 같은, 4입력 EXOR 동적 논리 회로(300)로서 구성하고, 시뮬레이션을 행하였다. 또, 노이즈 내성 평가도 동일하게 행하였다.

또 21은 노이즈를 부여하지 않은 경우의 도 20의 센스 증폭기 회로(100B)가 가동상으로 바뀔 때의 파형을 나타낸 도면이며, 도 22는 노이즈를 부여하지 않은 경우의 도 20의 센스 증폭기 회로(100B)가 휴지상으로 바뀔 때의 파형을 나타낸 도면이며, 도 23은 노이즈를 부여한 경우의, 도 20의 센스 증폭기 회로(100B)가 가동상으로 바뀔 때의 파형을 나타낸 도면이다.

도 21, 도 22, 및 도 23에서, 횡축은 시간을 표시하고, 종축은 전압을 표시하고 있다.

먼저, 도면에 표시하고 있지 않지만, 도 20의 차동형 센스 증폭기 회로(100B)에서, 논리가 확정된 것을 나타내는 완료 신호(DONE\_X)는 0V에서 전원 전압 레벨까지 진폭한다.

따라서, 도 20의 차동형 센스 증폭기 회로(100B)에 의하면, 종래 기술의 제1 과제는 해결되었다.

도 21을 보면 명백한 바와 같이, 가동상으로 바뀌기 직전의 휴지상에서, 논리 출력(H, H\_X)은 이상적인 0V로 되어 있다.

또, 도 22에 나타낸 바와 같이, 도 20의 차동형 센스 증폭기 회로(100B)에서는, 휴지상으로 바뀌면 신속하게 0V로 내려간다.

따라서, 도 20의 차동형 센스 증폭기 회로(100B)에 의하면, 휴지상에서 논리 출력(H, H\_X)이 0V로 되지 않고, NMOS 임계값 전압만큼 상승하므로, 리크 전류가 커진다고 하는, 종래 기술의 제2 과제는 해결되었다.

또, 도 23을 보면 명백한 바와 같이, 본 발명에서는 오동작은 보이지 않는다.

도 7의 평가용 모델(30)에서의 노이즈(NZ1)의 하강 영향을 받아 논리 출력(H)의 전위가 논리 출력(H\_X)보다 낮아지고 있는 기간이 존재한다.

DCSL3 방식의 센스 증폭기 회로에서는, 이대로 전위차가 확대되어 버렸다.

그러나, 도 20의 센스 증폭기 회로에서는, 도 23에 나타낸 바와 같이, 이 노이즈의 전위차를 역전하여, 옳바른 논리치로 향해 논리 출력(H, H\_X)의 전위가 수속되어 가는 모양이 묘사되어 있다.

이 현상은 센스 증폭기 회로(100B)가 가지는, NMOS 트랜지스터(NT107~NT109)에 의해 구성된 다이내믹 NOR 회로(D-NOR)에 의한 논리 트리 분리 제어 기구의 움직임에 의해 실현되고 있다.

따라서, 도 20의 차동형 센스 증폭기 회로(100B)에 의하면, 커플링 노이즈에 의해 센스 증폭기가 잘못된 값으로 확정되어 버린다고 하는, 종래 기술의 제3 과제는 해결되었다.

전술한 바와 같이, 커플링 노이즈에 의한 오동작은, 논리 트리의 높이와 전원 전압에 의존한다.

일반적으로, 전원 전압이 낮고, 논리 트리가 높아질수록, 커플링 노이즈에 의해 오동작되기 쉽게 된다.

또, 커플링 노이즈를 부여한 경우라도 정상 동작하는 최저 전원 전압을 나타낸 도 14에서는, 도 20의 센스 증폭기 회로(100B)는 N3형으로서 나타내고 있다.

전술한 바와 같이, EXOR의 논리 트리의 높이는 그 입력 차수와 동일하다.

도 14에서 명백한 바와 같이, 종래의 DCSL3 방식의 센스 증폭기 회로에서는, 전원 전압이 높고, 논리 트리가 낮아도 오동작을 일으킨다.

한편, 본 발명에 관한 N3형의 센스 증폭기 회로(100A)를 사용한 EXOR 논리에서는, 조건에도 의하지만 대체로 1.5V보다 낮은 전압에서도 동작 가능하다.

따라서, 도 20의 센스 증폭기 회로(100B)를 사용하여 동적 논리 회로를 구성하면, 저전원 전압에서 안정된 동작을 하는 동적 논리 회로를 실현할 수 있다.

그리고, 도 9의 센스 증폭기 회로와 마찬가지로, 도 20의 센스 증폭기 회로(100B)에 의하면, CMOS 반도체 집적 회로의 소비 전력을 대폭 절감하는 데 기여하는 것이다.

이상 설명한 바와 같이, 본 제3 실시 형태에 의하면, 전술한 제1 실시 형태의 효과와 동일한 효과를 얻을 수 있다.

#### 제4 실시 형태

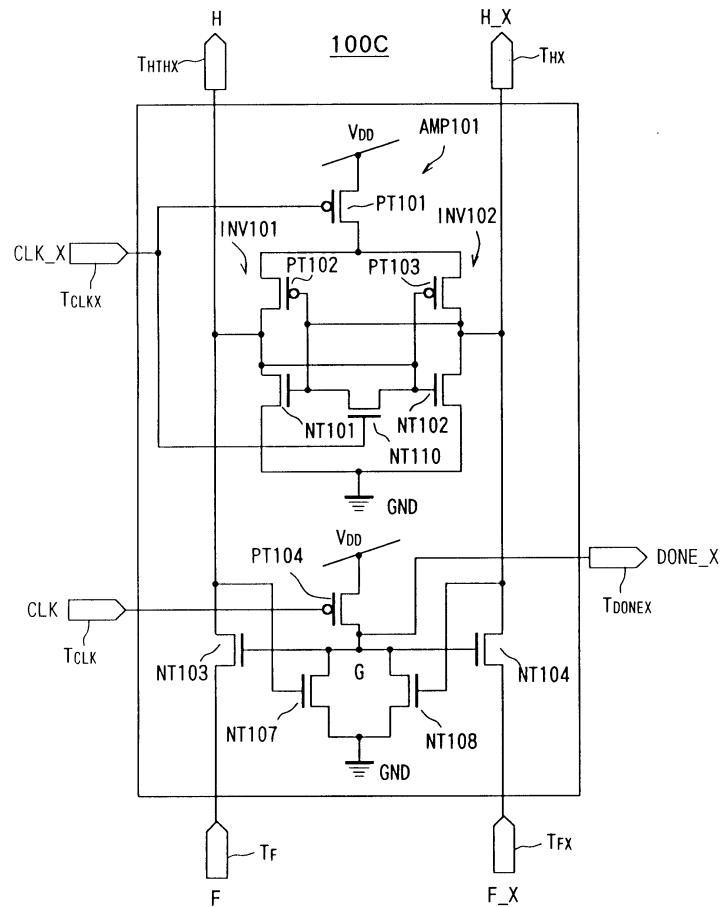

도 24는 본 발명에 관한 차동형 센스 증폭기 회로의 제4 실시 형태를 나타낸 회로도이다.

본 제4 실시 형태가 제3 실시 형태와 상이한 점은, 다이내믹 NOR 회로의 전원 전압( $V_{DD}$ )의 공급 라인과 제어 절점(G)을 프리차지용 NMOS 트랜지스터에 대신하여 프리차지용 PMOS 트랜지스터(PT104)에 의해 접속되고, PMOS 트랜지스터(PT104)의 게이트를 클록 반전 게이트(CLK\_X)의 클록 입력 단자(TCLKX) 대신에, 클록 신호(CLK)의 클록 입력 단자(TCLK)에 접속된 것에 있다.

그 밖의 구성 및 작용은 전술한 제3 실시 형태와 동일하여, 그 상세한 설명은 생략한다.

도 24의 센스 증폭기 회로(100C)를 사용하여, 도 10에 나타낸 바와 같은, 4입력 EXOR 동적 논리 회로(300)로서 구성하고, 시뮬레이션을 행하였다. 또, 노이즈 내성 평가도 동일하게 행하였다.

또 25는 노이즈를 부여하지 않은 경우의 도 20의 센스 증폭기 회로(100C)가 가동상으로 바뀔 때의 파형을 나타낸 도면이며, 도 26은 노이즈를 부여하지 않은 경우의 도 20의 센스 증폭기 회로(100C)가 휴지상으로 바뀔 때의 파형을 나타낸 도면이며, 도 27은 노이즈를 부여한 경우의, 도 20의 센스 증폭기 회로(100B)가 가동상으로 바뀔 때의 파형을 나타낸 도면이다.

또, 도 28은 도 24의 센스 증폭기 회로(100C)에서의 완료 신호(DONE\_X)의 파형을 나타낸 도면이다.

도 25, 도 26, 및 도 28에서, 횡축은 시간을 표시하고, 종축은 전압을 표시하고 있다.

먼저, 도 28에서 명백한 바와 같이, 도 20의 차동형 센스 증폭기 회로(100C)에서, 논리가 확정된 것을 나타내는 완료 신호(DONE\_X)는 0V에서 전원 전압 레벨까지 진폭하고 있다.

또, 논리 출력(H)의 파형과 진폭의 중앙치에 가까운 곳에서 교차되고 있어, 천이되는 타이밍도 이상적이라고 할 수 있다.

따라서, 도 24의 차동형 센스 증폭기 회로(100C)에 의하면, 종래 기술의 제1 과제는 해결되었다.

도 25를 보면 명백한 바와 같이, 가동상으로 바뀌기 직전의 휴지상에서, 논리 출력(H, H\_X)은 이상적인 0V로 되어 있다.

또, 도 26에 나타낸 바와 같이, 도 24의 차동형 센스 증폭기 회로(100C)에서는, 휴지상으로 바뀌면 신속하게 0V로 내려간다.

따라서, 도 24의 차동형 센스 증폭기 회로(100C)에 의하면, 휴지상에서 논리 출력(H, H\_X)이 0V로 되지 않고, NMOS 임계값 전압만큼 상승하므로, 리크 전류가 커진다고 하는, 종래 기술의 제2 과제는 해결되었다.

또, 도 27을 보면 명백한 바와 같이, 본 발명에서는 오동작은 보이지 않는다.

도 7의 평가용 모델(30)에서의 노이즈(NZ1)의 하강 영향을 받아 논리 출력(H)의 전위가 논리 출력(H\_X)보다 낮아지고 있는 기간이 존재한다.

DCSL3 방식의 센스 증폭기 회로에서는, 이대로 전위차가 확대되어 버렸다.

그러나, 도 24의 센스 증폭기 회로에서는, 도 27에 나타낸 바와 같이, 이 노이즈의 전위차를 역전하여, 옳바른 논리치로 향해 논리 출력(H, H\_X)의 전위가 수속되어 가는 모양이 묘사되어 있다.

이 현상은 센스 증폭기 회로(100C)가 가지는, PMOS 트랜지스터(PT104), 및 NMOS 트랜지스터(NT107, NT108)에 의해 구성된 다이내믹 NOR 회로(D-NOR)에 의한 논리 트리 분리 제어 기구의 움직임에 의해 실현되고 있다.

따라서, 도 24의 차동형 센스 증폭기 회로(100C)에 의하면, 커플링 노이즈에 의해 센스 증폭기가 잘못된 값으로 확정되어 버린다고 하는, 종래 기술의 제3 과제는 해결되었다.

전술한 바와 같이, 커플링 노이즈에 의한 오동작은, 논리 트리의 높이와 전원 전압에 의존한다.

일반적으로, 전원 전압이 낮고, 논리 트리가 높아질수록, 커플링 노이즈에 의해 오동작되기 쉽게 된다.

또, 커플링 노이즈를 부여한 경우라도 정상 동작하는 최저 전원 전압을 나타낸 도 14에서는, 도 24의 센스 증폭기 회로(100C)는 P3형으로서 나타내고 있다.

전술한 바와 같이, EXOR의 논리 트리의 높이는 그 입력 차수와 동일하다.

도 14에서 명백한 바와 같이, 종래의 DCSL3 방식의 센스 증폭기 회로에서는, 전원 전압이 높고, 논리 트리가 낮아도 오동작을 일으킨다.

한편, 본 발명에 관한 P3형의 센스 증폭기 회로(100C)를 사용한 EXOR 논리에서는, 조건에도 의하지만 대체로 1.5V보다 낮은 전압에서도 동작 가능하다. 또한, 이 P3형의 센스 증폭기 회로(100C)에서는, 0.7V 부근에서 조차도 오동작을 일으키지 않는다.

따라서, 도 24의 센스 증폭기 회로(100C)를 사용하여 동적 논리 회로를 구성하면, 저전원 전압에서 안정된 동작을 하는 동적 논리 회로를 실현할 수 있다.

그리고, 도 9의 센스 증폭기 회로와 마찬가지로, 도 24의 센스 증폭기 회로(100C)에 의하면, CMOS 반도체 집적 회로의 소비 전력을 대폭 절감하는 데 기여하는 것이다.

이상 설명한 바와 같이, 본 제4 실시 형태에 의하면, 전술한 제1 실시 형태 및 제2 실시 형태의 효과와 동일한 효과를 얻을 수 있다.

#### 제5 실시 형태

도 29는 본 발명에 관한 차동형 센스 증폭기 회로의 제5 실시 형태를 나타낸 회로도이다.

본 제5 실시 형태가 전술한 제2 실시 형태와 상이한 점은, 논리 트리 분리의 접속 제어 수단을 구성하는 NMOS 트랜지스터(107, 및 108)의 소스 접속점인 중간 절점(MG)과 접지와의 사이에, NMOS 트랜지스터(NT111)를 접속하고, 이 NMOS 트랜지스터(NT111)의 게이트를 클록 입력 단자(TCLK)에 접속한 것에 있다.

기본적인 동작 원리는 도 15에 나타낸 제2 실시 형태와 동일하게 된다. 그러므로, 상세한 설명을 생략한다.

NMOS 트랜지스터(NT111)를 부가함으로써 동작이 약간 상이한 것은, 가동상으로부터 휴지상으로 천이되는 과정에 있다.

이 천이 과정에서, PMOS 트랜지스터(PT104)가 온으로 되는 것과, NMOS 트랜지스터(NT107, NT108)가 컷 오프되는 것은 동시에 일어나지 않는다.

NMOS 트랜지스터(NT107, NT108)가 컷 오프되는 데는, 절점(TH, TH\_X) 상의 전하 평형 분배와 NMOS 다이오드에 의한 전하 유출이라고 하는 과정이 필요하게 된다.

그러므로, 도 15의 제2 실시 형태에서는, PMOS 트랜지스터(PT104)가 온으로 되고 나서 NMOS 트랜지스터(NT107, NT108) 중 어느 한쪽을 통해 관통 전류가 흐르는 순간이 존재한다.

이에 대하여, 도 29에 나타낸 본 제5 실시 형태에서는, 이상과 같은 관통 전류는 발생하지 않는다.

PMOS 트랜지스터(PT104)가 온으로 됨과 동시에, 동일 클록 신호(CLK)에 동기하여, NMOS 트랜지스터(NT111)가 컷 오프되기 때문이다.

제5 실시 형태에 의하면, 전술한 제2 실시 형태의 효과에 더하여, 저소비 전력화를 도모할 수 있는 이점이 있다.

또, 도 29의 센스 증폭기 회로(100D)를 사용하여, 도 10에 나타낸 바와 같은 동적 논리 회로를 실현할 수 있음은 물론이다.

#### 제6 실시 형태

도 30은 본 발명에 관한 차동형 센스 증폭기 회로의 제6 실시 형태를 나타낸 회로도이다.

본 제6 실시 형태가 제4 실시 형태와 상이한 점은, 논리 트리 분리의 접속 제어 수단을 구성하는 NMOS 트랜지스터(NT107, 및 NT108)의 소스 접속점인 중간 절점(MG)과 접지와의 사이에, NMOS 트랜지스터(NT111)를 접속하고, 이 NMOS 트랜지스터(NT111)의 게이트를 클록 입력 단자(TCKL)에 접속한 것에 있다.

기본적인 동작 원리는 도 24에 나타낸 제4 실시 형태와 동일하게 된다. 그러므로, 상세한 설명을 생략한다.

NMOS 트랜지스터(NT111)를 부가함으로써 동작이 약간 상이한 것은, 가동상으로부터 휴지상으로 천이되는 과정에 있다.

이 천이 과정에서, PMOS 트랜지스터(PT104)가 온으로 되는 것과, NMOS 트랜지스터(NT107, NT108)가 컷 오프되는 것은 동시에 일어나지 않는다.

NMOS 트랜지스터(NT107, NT108)가 컷 오프되는 데는, 절점(TH, TH\_X) 상의 전하 평형 분배와 NMOS 다이오드에 의한 전하 유출이라고 하는 과정이 필요하게 된다.

그러므로, 도 24의 제4 실시 형태에서는, PMOS 트랜지스터(PT104)가 온으로 되고 나서 NMOS 트랜지스터(NT107, NT108) 중 어느 한쪽을 통해 관통 전류가 흐르는 순간이 존재한다.

이에 대하여, 도 30에 나타낸 본 제6 실시 형태에서는, 이상과 같은 관통 전류는 발생하지 않는다.

PMOS 트랜지스터(PT104)가 온으로 됨과 동시에, 동일 클록 신호(CLK)에 동기하여, NMOS 트랜지스터(NT111)가 컷 오프되기 때문이다.

제6 실시 형태에 의하면, 전술한 제4 실시 형태의 효과에 더하여, 저소비 전력화를 도모할 수 있는 이점이 있다.

또, 도 30의 센스 증폭기 회로(100E)를 사용하여, 도 10에 나타낸 바와 같은 동적 논리 회로를 실현할 수 있음은 물론이다.

#### 제7 실시 형태

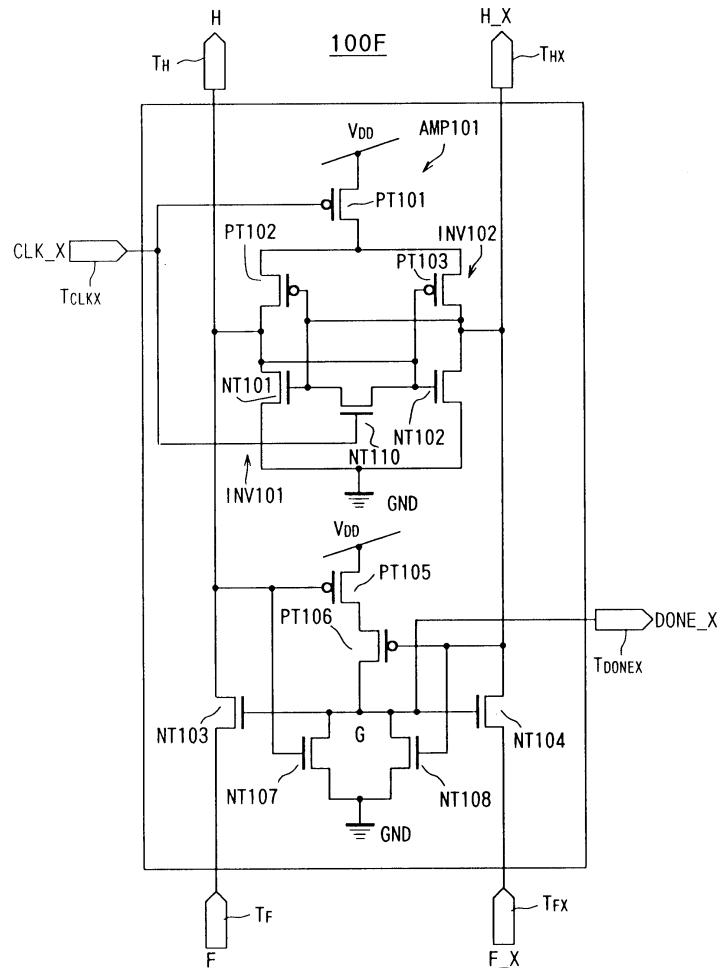

도 31은 본 발명에 관한 차동형 센스 증폭기 회로의 제7 실시 형태를 나타낸 회로도이다.

본 제7 실시 형태가 전술한 제3 실시 형태와 상이한 점은, 다이내믹 NOR 회로의 전원 전압( $V_{DD}$ )의 공급 라인과 제어 절점(G)를 프리차지용 NMOS 트랜지스터에 대신하여 직렬로 접속한 2개의 PMOS 트랜지스터(PT105, PT106)에 의해 접속하고, PMOS 트랜지스터(PT105)의 게이트를 논리 출력 단자(TH)에 접속하고, PMOS 트랜지스터(PT106)의 게이트를 논리 출력 단자(THX)에 접속하고, 논리 트리 분리용의 제어 기구를 스테틱 NOR 회로(S-NOR)에 의해 구성한 것에 있다.

그 밖의 구성 및 작용은 전술한 제3 실시 형태와 동일하다.

본 제7 실시 형태에서는, 클록 신호(CLK)에 의하지 않고, 절점(TH, TH\_X)의 논리 전위를 보아 제어 절점(G)의 전위를 결정하고, 논리 트리의 분리를 제어한다.

즉, 휴지상에서는 절점(TH, TH\_X)이 함께 논리 "0"이기 때문에, 제어 절점(G)을 논리 "1"로 하고, 가동상에서 절점(TH, TH\_X) 중 어느 한쪽이 논리 "1"로 된 시점에서 제어 절점(G)을 논리 "0"으로 한다.

PMOS 트랜지스터(PT105, PT106)가 직렬 접속으로 되어 있기 때문에, 절점(TH, TH\_X)이 함께 논리 "0"으로 되돌아 올 때까지 전류는 흐르지 않아, 관통 전류는 발생하지 않는다.

본 제7 실시 형태에 의하면, 전술한 제3 실시 형태의 효과에 더하여, 저소비 전력화를 도모할 수 있는 이점이 있다.

또, 본 제7 실시 형태에 의하면, 논리 트리 분리의 제어에 클록 신호(CLK)를 필요로 하지 않기 때문에, 클록 신호(CLK)에 대한 부가를 경감할 수 있다.

또, 도 31의 센스 증폭기 회로(100F)를 사용하여, 도 10에 나타낸 바와 같은 동적 논리 회로를 실현할 수 있음은 물론이다.

### 발명의 효과

이상 설명한 바와 같이, 본 발명에 의하면, 후단의 논리 회로를 오동작시키지 않는 완료 신호를 생성할 수 있고, 또 회로 정지 시에서의 소비 전력을 절감할 수 있다.

또, 본 발명에 의하면, 커플링 노이즈에 의해 오동작을 일으킬 우려가 없어, 실용적인 차동형 센스 증폭기 및 이를 사용한 동적 논리 회로를 실현할 수 있다.

상기한 바와 같이, 본 발명에 대하여 실시 형태를 참조하여 상세히 설명했으나, 이 기술 분야에서 숙련된 사람은 본 발명의 기본 개념 및 범위를 일탈하지 않고 여러 가지 변경이 가능함을 이해할 수 있을 것이다.

### (57) 청구의 범위

#### 청구항 1.

제어 신호에 따라 휴지상(休止相)(idle phase) 및 가동상(稼動相)(working phase) 2개의 상(相)을 교대하는 차동형(差動型) 센스 증폭기 회로로서,

제1 논리 입력 단자,

제2 논리 입력 단자,

제1 논리 출력 단자,

제2 논리 출력 단자,

제1 인버터, 및 제2 인버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차(差)에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기,

휴지상을 나타내는 제어 신호를 받아 상기 제1 논리 입력 단자와 제2 논리 입력 단자를 기준 전위로 초기 설정하는 초기 설정 수단,

상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단,

상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단, 및

상기 휴지상을 나타내는 제어 신호를 받아 상기 제1 전환 수단과 제2 전환 수단의 제어 단자에 접속된 제어 절점(制御節點)의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단, 및 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단

을 가지는 차동형 센스 증폭기 회로.

## 청구항 2.

제1항에 있어서,

상기 초기 설정 수단은 상기 제1 논리 출력 단자와 기준 전위와의 사이에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자와, 상기 제2 논리 출력 단자와 기준 전위와의 사이에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제2 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

## 청구항 3.

제1항에 있어서,

상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함하고,

상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제2 스위치 소자와, 상기 제2 전원 전압과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

## 청구항 4.

제2항에 있어서,

상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제3 스위치 소자를 포함하고,

상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전압과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자와, 상기 제2 전원 전압과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제5 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

## 청구항 5.

제1항에 있어서,

상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함하고,

상기 제2 설정 수단은 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제2 스위치 소자와, 상기 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 절점에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자와, 상기 제1 전환

수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 중간 절점 간에 접속되고, 상기 제1 스위치 소자가 도통될 때에는 비도통 상태로 유지되고, 상기 제1 스위치 소자가 비도통 상태로 유지될 때에는 도통되는 제4 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

### 청구항 6.

제2항에 있어서,

상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제3 스위치 소자를 포함하고,

상기 제2 설정 수단은 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자와, 상기 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 절점에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제5 스위치 소자와, 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 중간 절점 간에 접속되고, 상기 제3 스위치 소자가 도통될 때에는 비도통 상태로 유지되고, 상기 제3 스위치 소자가 비도통 상태로 유지될 때에는 도통되는 제6 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

### 청구항 7.

제3항에 있어서,

상기 제1 설정 수단의 제1 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 n채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 8.

제3항에 있어서,

상기 제1 설정 수단의 제1 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 9.

제4항에 있어서,

상기 제1 설정 수단의 제3 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 n채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 10.

제4항에 있어서,

상기 제1 설정 수단의 제3 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 11.

제5항에 있어서,

상기 제1 설정 수단의 제1 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 n채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 12.

제6항에 있어서,

상기 제1 설정 수단의 제3 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 13.

제1항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 14.

제2항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 15.

제3항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 16.

제7항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 17.

제8항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 18.

제11항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 19.

제어 신호에 따라 휴지상 및 가동상 2개의 상을 교대하는 차동형 센스 증폭기 회로로서,

제1 논리 입력 단자,

제2 논리 입력 단자,

제1 논리 출력 단자,

제2 논리 출력 단자,

제1 인버터, 및 제2 인버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기,

휴지상을 나타내는 제어 신호를 받아 상기 제1 인버터의 입력과 제2 인버터의 입력을 접속하는 초기 설정 수단,

상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단,

상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단, 및

상기 휴지상을 나타내는 제어 신호를 받아 상기 제1 전환 수단과 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단, 및 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단

을 가지는 차동형 센스 증폭기 회로.

### 청구항 20.

제19항에 있어서,

상기 초기 설정 수단은 상기 제1 인버터의 입력과 제2 인버터의 입력과의 사이에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

## 청구항 21.

제19항에 있어서,

상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함하고,

상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제2 스위치 소자와, 상기 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

## 청구항 22.

제20항에 있어서,

상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제2 스위치 소자를 포함하고,

상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자와, 상기 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

## 청구항 23.

제19항에 있어서,

상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함하고,

상기 제2 설정 수단은 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제2 스위치 소자와, 상기 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 절점에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자와, 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 중간 절점 간에 접속되고, 상기 제1 스위치 소자가 도통될 때에는 비도통 상태로 유지되고, 상기 제1 스위치 소자가 비도통 상태로 유지될 때에는 도통되는 제4 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

## 청구항 24.

제20항에 있어서,

상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제2 스위치 소자를 포함하고,

상기 제2 설정 수단은 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자와, 상기 중간 절점과 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 절점에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자와, 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 중간 절점 간에 접속되고, 상기 제2 스위치 소자가 도통될 때에는 비도통 상태로 유지되고, 상기 제2 스위치 소자가 비도통 상태로 유지될 때에는 도통되는 제5 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

### 청구항 25.

제21항에 있어서,

상기 제1 설정 수단의 제1 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 n채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 26.

제21항에 있어서,

상기 제1 설정 수단의 제1 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 27.

제22항에 있어서,

상기 제1 설정 수단의 제2 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 n채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 28.

제22항에 있어서,

상기 제1 설정 수단의 제2 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 29.

제23항에 있어서,

상기 제1 설정 수단의 제1 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 30.

제24항에 있어서,

상기 제1 설정 수단의 제2 스위치 소자는 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

### 청구항 31.

제19항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 32.

제20항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 33.

제21항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 34.

제25항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 35.

제26항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 36.

제29항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

### 청구항 37.

제어 신호에 따라 휴지상 및 가동상 2개의 상을 교대하는 차동형 센스 증폭기 회로로서,

제1 논리 입력 단자,

제2 논리 입력 단자,

제1 논리 출력 단자,

제2 논리 출력 단자,

제1 인버터, 및 제2 인버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기,

휴지상을 나타내는 제어 신호를 받아 상기 제1 인버터의 입력과 제2 인버터의 입력을 접속하는 초기 설정 수단,

상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단,

상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단, 및

상기 휴지상 시, 상기 제1 논리 출력 단자 및 제2 논리 출력 단자 중 최소한 한쪽의 전위를 받아 상기 제1 전환 수단과 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단, 및 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단

을 가지는 차동형 센스 증폭기 회로.

### 청구항 38.

제37항에 있어서,

상기 초기 설정 수단은 상기 제1 인버터의 입력과 제2 인버터의 입력과의 사이에 접속되고, 휴지상을 나타내는 제어 신호를 제어 단자에 받아 도통되는 제1 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

### 청구항 39.

제37항에 있어서,

상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 직렬로 접속되고, 각각 휴지상 시의 제1 논리 출력 단자의 전위 및 제2 논리 출력 단자의 전위를 제어 단자에 받아 도통되는 제1 스위치 소자 및 제2 스위치 소자를 포함하고,

상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제3 스위치 소자와, 상기 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

**청구항 40.**

제38항에 있어서,

상기 접속 제어 수단의 제1 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 접속 상태로 하는 것이 가능한 제1 전원 전위와 상기 제어 절점 간에 직렬로 접속되고, 각각 휴지상 시의 제1 논리 출력 단자의 전위 및 제2 논리 출력 단자의 전위를 제어 단자에 받아 도통되는 제2 스위치 소자 및 제3 스위치 소자를 포함하고,

상기 제2 설정 수단은 상기 제1 전환 수단 및 제2 전환 수단을 분리 상태로 하는 것이 가능한 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제1 논리 출력 단자에 접속되고, 제1 논리 출력 전위가 제1 레벨인 때 도통되는 제4 스위치 소자와, 상기 제2 전원 전위와 상기 제어 절점 간에 접속되고, 제어 단자가 상기 제2 논리 출력 단자에 접속되고, 제2 논리 출력 전위가 제1 레벨인 때 도통되는 제5 스위치 소자를 포함하는 차동형 센스 증폭기 회로.

**청구항 41.**

제39항에 있어서,

상기 제1 설정 수단의 제1 및 제2 스위치 소자는, 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

**청구항 42.**

제40항에 있어서,

상기 제1 설정 수단의 제2 및 제3 스위치 소자는, 게이트가 제어 신호의 입력 단자에 접속된 p채널의 전하 효과 트랜지스터를 포함하는 차동형 센스 증폭기 회로.

**청구항 43.**

제37항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

**청구항 44.**

제38항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

**청구항 45.**

제39항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

#### 청구항 46.

제40항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

#### 청구항 47.

제41항에 있어서,

상기 접속 제어 수단은 상기 제어 절점으로부터 논리가 확정된 것을 나타내는 완료 신호를 출력하는 차동형 센스 증폭기 회로.

#### 청구항 48.

제어 신호에 따라 휴지상 및 가동상 2개의 상을 교대하는 동적(動的) 논리 회로로서,

제1 논리 입력 단자, 제2 논리 입력 단자, 제1 논리 출력 단자, 제2 논리 출력 단자, 제1 인버터와 제2 인버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기와, 휴지상을 나타내는 제어 신호를 받아 상기 제1 논리 입력 단자와 제2 논리 입력 단자를 기준 전위로 초기 설정하는 초기 설정 수단과, 상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단과, 상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단과, 상기 휴지상을 나타내는 제어 신호를 받아 상기 제1 전환 수단 및 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단과, 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단을 가지는 차동형 센스 증폭기 회로, 및

각각 상기 차동 센스 증폭기 회로의 제1 논리 입력 단자 및 제2 논리 입력 단자에 접속된 2선(線)을 가지고, 입력 신호에 따라 한쪽 선만이 기준 전위에 이르는 경로를 형성하는 2선식 논리 트리(tree)

를 가지는 동적 논리 회로.

#### 청구항 49.

제어 신호에 따라 휴지상 및 가동상 2개의 상을 교대하는 동적 논리 회로로서,

제1 논리 입력 단자, 제2 논리 입력 단자, 제1 논리 출력 단자, 제2 논리 출력 단자, 제1 인버터와 제2 인버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기와, 휴지상을 나타내는 제어 신호를 받아 상기 제1 인버터의 입

력과 제2 인버터의 입력을 접속하는 초기 설정 수단과, 상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단과, 상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단과, 상기 휴지상을 나타내는 제어 신호를 받아 상기 제1 전환 수단 및 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단과, 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단을 가지는 차동형 센스 증폭기 회로, 및

각각 상기 차동 센스 증폭기 회로의 제1 논리 입력 단자 및 제2 논리 입력 단자에 접속된 2선을 가지고, 입력 신호에 따라 한쪽 선만이 기준 전위에 이르는 경로를 형성하는 2선식 논리 트리

를 가지는 동적 논리 회로.

## 청구항 50.

제어 신호에 따라 휴지상 및 가동상 2개의 상을 교대하는 동적 논리 회로로서,

제1 논리 입력 단자, 제2 논리 입력 단자, 제1 논리 출력 단자, 제2 논리 출력 단자, 제1 인버터와 제2 인버터버터를 가지고, 제1 인버터의 출력과 제2 인버터의 입력이 접속되고, 그 접속점이 상기 제1 논리 출력 단자에 접속되고, 제1 인버터의 입력과 제2 인버터의 출력이 접속되고, 그 접속점이 상기 제2 논리 출력 단자에 접속되고, 가동상을 나타내는 제어 신호를 받아 가동되고, 제1 논리 입력 및 제2 논리 입력이 가지는 도통 저항의 차에 따라 제1 논리 출력 및 제2 논리 출력의 논리 전위를 상이한 제1 레벨 및 제2 레벨로 확정시키는 센스 증폭기와, 휴지상을 나타내는 제어 신호를 받아 상기 제1 인버터의 입력과 제2 인버터의 입력을 접속하는 초기 설정 수단과, 상기 제1 논리 입력 단자와 제1 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제1 전환 수단과, 상기 제2 논리 입력 단자와 제2 논리 출력 단자를 제어 단자의 전위에 따라 전기적으로 접속 또는 분리하는 제2 전환 수단과, 상기 휴지상 시에 상기 제1 논리 출력 단자 및 제2 논리 출력 단자 중 최소한 한쪽의 전위를 받아 상기 제1 전환 수단 및 제2 전환 수단의 제어 단자에 접속된 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 접속 가능하게 하는 전위로 설정하는 제1 설정 수단과, 가동상 시에 상기 제1 논리 출력 단자 또는 제2 논리 출력 단자의 전위에 따라 상기 제어 절점의 전위를, 제1 및 제2 전환 수단이 접속된 각 2 단자 간을 최소한 분리 가능하게 하는 전위로 설정하는 제2 설정 수단을 가지는 접속 제어 수단을 가지는 차동형 센스 증폭기 회로, 및

각각 상기 차동 센스 증폭기 회로의 제1 논리 입력 단자 및 제2 논리 입력 단자에 접속된 2선을 가지고, 입력 신호에 따라 한쪽 선만이 기준 전위에 이르는 경로를 형성하는 2선식 논리 트리

를 가지는 동적 논리 회로.

**도면**

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

|       | 논리목의 형식<br>(논리목의 높이) |               |               |               |

|-------|----------------------|---------------|---------------|---------------|

|       | 2- 입력<br>EXOR        | 3- 입력<br>EXOR | 4- 입력<br>EXOR | 5- 입력<br>EXOR |

| DCSL3 | > 1.50               | > 1.50        | > 1.50        | > 1.50        |

| N2 형  | 0.97                 | 1.08          | 1.20          | 1.46          |

| P2 형  | ≤ 0.70               | ≤ 0.70        | ≤ 0.70        | 0.72          |

| N3 형  | 1.04                 | 1.13          | 1.23          | > 1.50        |

| P3 형  | ≤ 0.70               | ≤ 0.70        | ≤ 0.70        | ≤ 0.70        |

도면15

도면16

도면17

도면18

도면19

도면20

도면21

도면22

도면23

도면24

도면25

도면26

도면27

도면28

도면29

도면30

도면31