(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5451332号

(P5451332)

(45) 発行日 平成26年3月26日(2014.3.26)

(24) 登録日 平成26年1月10日(2014.1.10)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| HO 1 S 5/343 | (2006.01) |

| HO 1 S 5/12  | (2006.01) |

| HO 1 S 5/125 | (2006.01) |

| HO 1 S 5/50  | (2006.01) |

| HO 1 S 5/026 | (2006.01) |

HO 1 S 5/343

HO 1 S 5/12

HO 1 S 5/125

HO 1 S 5/50

HO 1 S 5/026 610

請求項の数 16 (全 33 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2009-263472 (P2009-263472)  |

| (22) 出願日     | 平成21年11月19日 (2009.11.19)      |

| (65) 公開番号    | 特開2010-157691 (P2010-157691A) |

| (43) 公開日     | 平成22年7月15日 (2010.7.15)        |

| 審査請求日        | 平成24年9月13日 (2012.9.13)        |

| (31) 優先権主張番号 | 特願2008-306963 (P2008-306963)  |

| (32) 優先日     | 平成20年12月2日 (2008.12.2)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 301005371<br>日本オクラロ株式会社<br>神奈川県相模原市中央区小山四丁目1番5<br>5号 |

| (74) 代理人  | 110000154<br>特許業務法人はるか国際特許事務所                        |

| (74) 代理人  | 100100310<br>弁理士 井上 学                                |

| (74) 代理人  | 100098660<br>弁理士 戸田 裕二                               |

| (72) 発明者  | 北谷 健<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所中央研究所内       |

最終頁に続く

(54) 【発明の名称】光半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型InP層上に半絶縁性InP層が積層された半絶縁性基板上に、半導体積層体が積層され、

前記第1導電型InP層は、亜鉛又は硫黄がドーピングされており、

前記半絶縁性InP層は、ルテニウム又はオスミウムがドーピングされ、

前記半導体積層体は、

前記半絶縁性基板上に配置されたn型半導体層と、

前記n型半導体層上に積層されている活性層と、

前記活性層上に積層されているp型半導体層と、

を備えていることを特徴とする光半導体装置。

## 【請求項 2】

請求項1において、

ルテニウムがドーピングされた半絶縁性InP層の膜厚は、0.5 μm以上150 μm以下とする光半導体装置。

## 【請求項 3】

請求項2において、

第1導電型のキャリアを供給する第1電極と、前記第1導電型とは異なる第2導電型のキャリアを供給する第2電極とを前記半絶縁性基板の一方の面に備えている光半導体装置。

## 【請求項 4】

10

20

請求項 1 において、

第1光機能素子と第2光機能素子を備え、

前記第1光機能素子は、第1導電型のキャリアを供給する第1電極と、前記第1導電型とは異なる第2導電型のキャリアを供給する第2電極とを前記半絶縁性基板の一方の面に備え、

前記第2光機能素子は、第1導電型のキャリアを供給する第3電極と、前記第1導電型とは異なる第2導電型のキャリアを供給する第4電極とを前記半絶縁性基板の一方の面に備え、

前記第1電極と前記第3電極とは連結されており、

前記第2電極と前記第4電極とは分離されていることを特徴とする光半導体装置。 10

【請求項 5】

請求項 1 において、

前記半絶縁性InP層の上に下部クラッド層、活性層及び上部クラッド層の積層体を有し、

分布帰還型(DFB)レーザ、分布反射型(DBR)レーザ、半導体光增幅器(SOA)のいずれかが構成されていることを特徴とする光半導体装置。

【請求項 6】

請求項 4 において、

前記第1光機能素子は、分布帰還型(DFB)レーザ、分布反射型(DBR)レーザ、半導体光增幅器(SOA)のいずれかであることを特徴とする光半導体装置。 20

【請求項 7】

請求項 1 において、

PIN型フォトダイオード(PD)、雪崩型フォトダイオード(APD)のどちらかが構成されていることを特徴とする光半導体装置。

【請求項 8】

請求項 1 において、

パッシブ導波路、多モード干渉器(MMI)、アレイ型導波路回折格子(AWG)のいずれかが構成されていることを特徴とする光半導体装置。

【請求項 9】

少なくとも表面にルテニウム(Ru)或いはオスニウム(0s)がドーピングされた半絶縁性InPを有する半絶縁性InP基板と、 30

前記半絶縁性InP基板上に配置されたn型半導体層と、

前記n型半導体層上に積層されている活性層と、

前記活性層上に積層されているp型半導体層と、

前記p型半導体層に接続された第1電極と、

前記n型半導体層に接続された第2電極とを備えた光半導体装置。

【請求項 10】

請求項 9 において、

前記半絶縁性InP基板は、Ruがドーピングされた半絶縁性InPで構成されていることを特徴とする光半導体装置。 40

【請求項 11】

請求項 9 において、

前記半絶縁性InP基板は、Ruがドーピングされた半絶縁性InP層が、導電性InP基板上に積層されていることを特徴とする光半導体装置。

【請求項 12】

請求項 9 において、

前記半絶縁性InP基板は、Ruがドーピングされた半絶縁性InP層が、Feドープ半絶縁性InP基板上に積層されていることを特徴とする光半導体装置。

【請求項 13】

請求項 9 において、

50

前記光半導体装置は、少なくとも半導体レーザ、或いは半導体光増幅器を含むことを特徴とする光半導体装置。

【請求項 1 4】

請求項 1 3 において、

前記半絶縁性基板のルテニウム、或いはオスニウムのドーピング濃度は $5 \times 10^{15} \text{ cm}^{-3}$ から $1 \times 10^{19} \text{ cm}^{-3}$ の範囲であることを特徴とする光半導体装置。

【請求項 1 5】

請求項 1 4 において、

前記半絶縁性基板中の亜鉛(Zn)、ベリリウム(Be)、マグネシウム(Mg)、炭素(C)、シリコン(Si)、硫黄(S)、錫(Sn)の濃度が $1 \times 10^{16} \text{ cm}^{-3}$ 未満であることを特徴とする光半導体装置。

10

【請求項 1 6】

請求項 1 5 において、

前期基板主表面が(100)面であって、該基板面が-0.05度以上-0.2度以下の角度で微傾斜していることを特徴とする光半導体装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、半絶縁性基板上に形成された半導体層で構成された光半導体装置に関する。

20

【背景技術】

【0 0 0 2】

プロードバンドネットワークの急激な普及に伴い、光通信用デバイスの高速化、小型化、高機能化が重要な課題となっている。こうした背景のもと、従来は単独の素子として用いられていた半導体レーザ光源、変調器、受光器などの光機能素子を、一つの基板上にモノリシックに集積した光電子集積回路(OEIC: Optical Electrical Integrated Circuit)を備えた光半導体装置(OEICデバイス)の必要性が高まっている。OEICデバイスには、異なる、あるいは同様の機能を有する複数の光機能素子をひとつの基板上に形成することによる小型化、単独素子間の光結合に関わる手間と部品点数の削減による低コスト化、複数の異なる機能を有する機能素子の集積による高機能化・多機能化など多くのメリットがある。こうしたOEICデバイスでは、アレイ化した複数の光機能素子や、電気特性が異なる複数の光機能素子を同時に駆動させるため、光機能素子間の電気的な絶縁が極めて重要なとなる。

30

素子の両面に電極を配置する光半導体装置で用いるInP基板は、n型又はp型の導電性基板か、絶縁性基板を用いる。

【0 0 0 3】

しかし、通信用光ファイバの低分散、低光損失波長帯となる $1.3 \mu\text{m}$ 帯、 $1.55 \mu\text{m}$ 帯に好適な光通信用のOEICデバイスは、その製造の容易さから、半絶縁性(Semi-Insulating: SI)を有するInP(インジウムリン)基板上に形成され、片面に電極を集約することが好ましい。このようなSI-InP基板として、Fe(鉄)-InP(Fe(鉄))がドープされたInP基板を用いるものが、特許文献1に開示されている。具体的には、特許文献1には、Fe(鉄)-InP基板の上にp型半導体層としてZn-InP層(Zn(亜鉛)がドープされたInP)を積層した場合に、Fe-InP基板のFeとZn-InPのZnとの相互拡散により、SI-InP基板としての抵抗率が低下することを防止するために、Fe-InP基板上に、Ru-InP(Ru(ルテニウム)がドープされた半絶縁性InP)層を設け、続いてp型半導体層/活性層/n型半導体層の順に積層した積層体を設け、p型のキャリアをp型半導体層に供給するp電極と、n型キャリアをn型半導体層に供給するn電極とを、共にFe-InP基板の一方の面(半導体層の積層面)に備えた構造が開示されている。

40

【先行技術文献】

【特許文献】

【0 0 0 4】

50

【特許文献 1】特開2002-344087号公報

【特許文献 2】特開2000-332287号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

上記特許文献1に開示された半絶縁性基板を用いた光半導体装置では、十分な特性を得ることができなかった。

【0006】

本発明の目的は、従来の半絶縁性基板を用いた光半導体装置の特性を改善することにある。

10

【課題を解決するための手段】

【0007】

本発明者らは、上記特性劣化の原因を検討し、2つの原因を見出した。

【0008】

第1の原因は、Fe-InP基板自体のエッチピット密度 (EPD: Etch pit density) が高いことである。第2の原因は、p型ドーパントであるZnと半絶縁性ドーパントであるFeとが直接接触しておらず、間にRu-InP層を挟んでいても、相互拡散の影響を完全に抑制することはできないという新たな劣化モードによるものである。

【0009】

そこで、第1の原因による特性劣化を解消するために、基板側からp型半導体層/活性層/n型半導体層という積層順は同様にしたまま、半絶縁性基板自体を多層化し、導電性InP基板の上にRu-InP層を設けた多層半絶縁性基板にすることとした。

20

【0010】

さらに、第2の原因による特性劣化を解消するために、素子構造を変えて、基板側からn型半導体層/活性層/p型半導体という積層順とし、該積層体が積層される半絶縁性基板自体をRu-InP基板とするか、半絶縁性基板自体を多層化し、Fe-InP基板の上にRu-InP層を設けた多層半絶縁性基板とした。なお、第1の原因による特性劣化を解消した手段と同様に、導電性InP基板の上にRu-InP層を設けた多層半絶縁性基板を用いても同様の効果が得られる。

【発明の効果】

30

【0011】

本発明によれば、従来の半絶縁性基板を用いた光半導体装置の特性を改善することができる。

【図面の簡単な説明】

【0012】

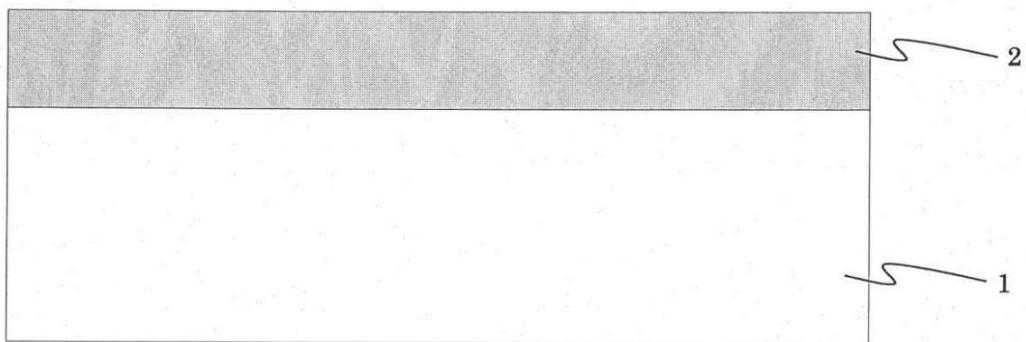

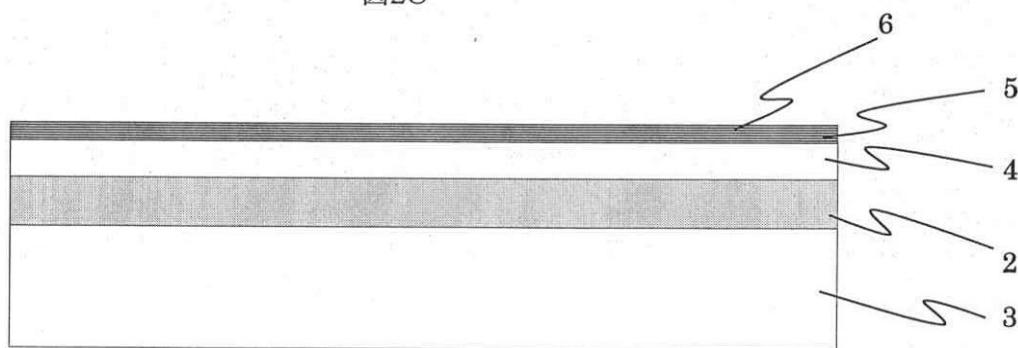

【図1A】Znがドープされた導電性InP基板上にRuがドープされたSI-InP層を有する多層半絶縁性基板の断面図である。

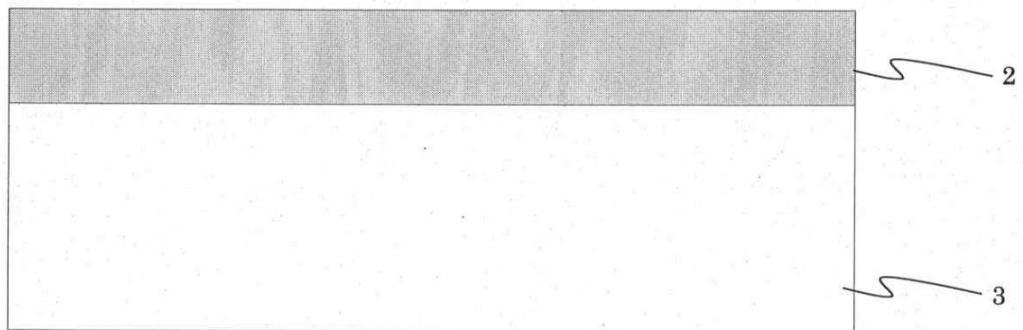

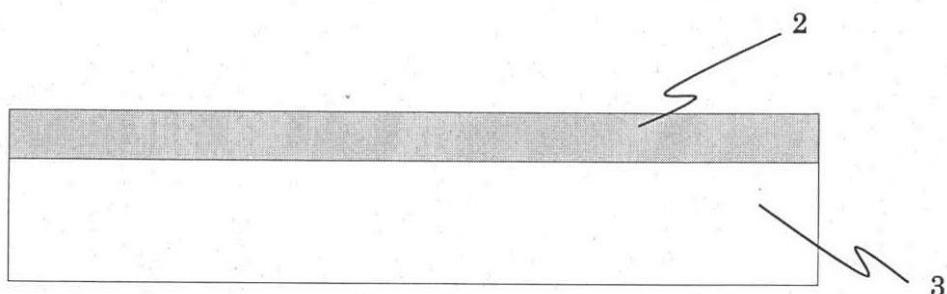

【図1B】Sがドープされた導電性InP基板上にRuがドープされたSI-InP層を有する多層半絶縁性基板の断面図である。

【図2A】実施例1の光半導体装置の製作過程を表す図である。

40

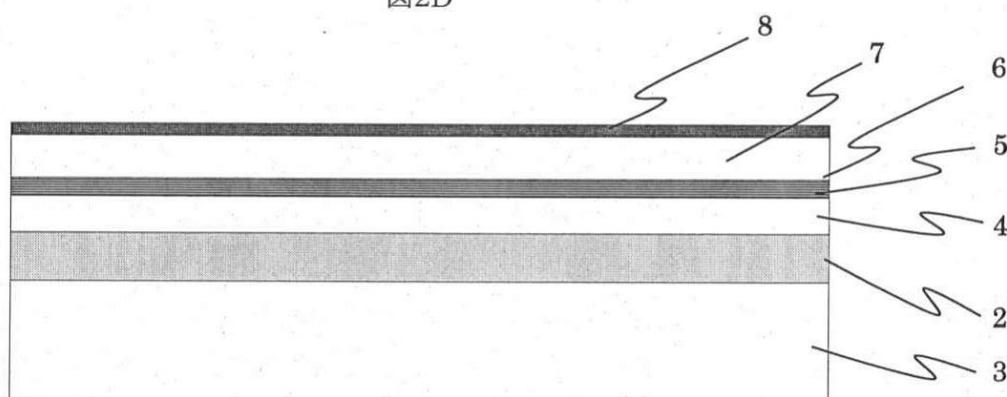

【図2B】実施例1の光半導体装置の製作過程を表す図である。

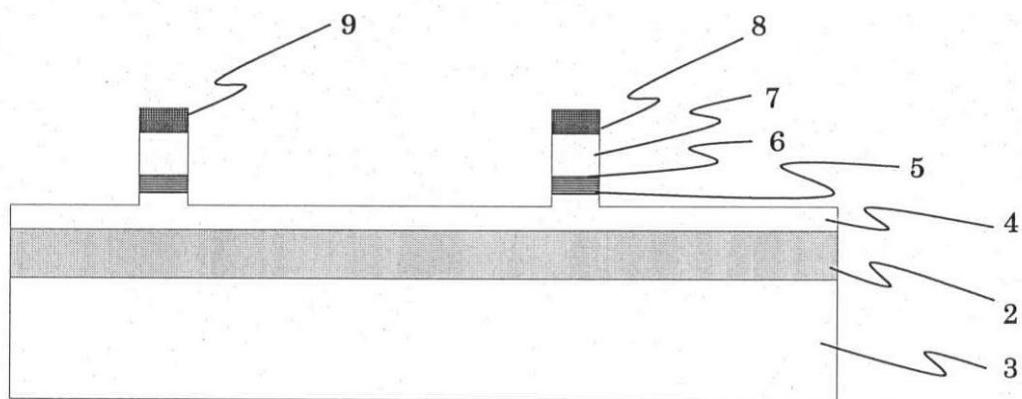

【図2C】実施例1の光半導体装置の製作過程を表す図である。

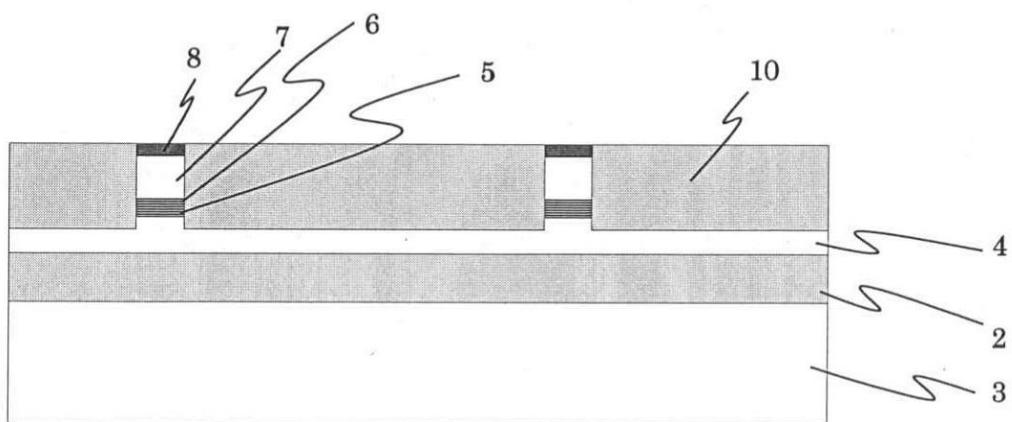

【図2D】実施例1の光半導体装置の製作過程を表す図である。

【図2E】実施例1の光半導体装置の製作過程を表す図である。

【図2F】実施例1の光半導体装置の製作過程を表す図である。

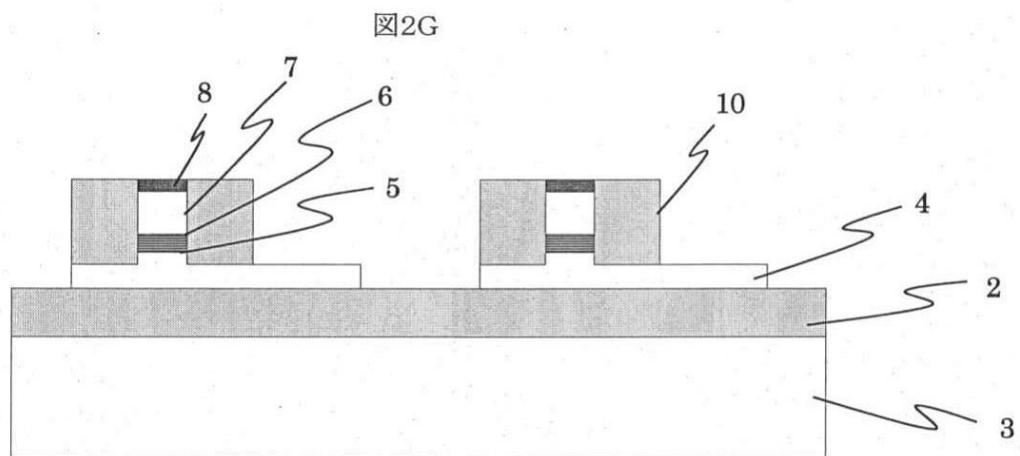

【図2G】実施例1の光半導体装置の製作過程を表す図である。

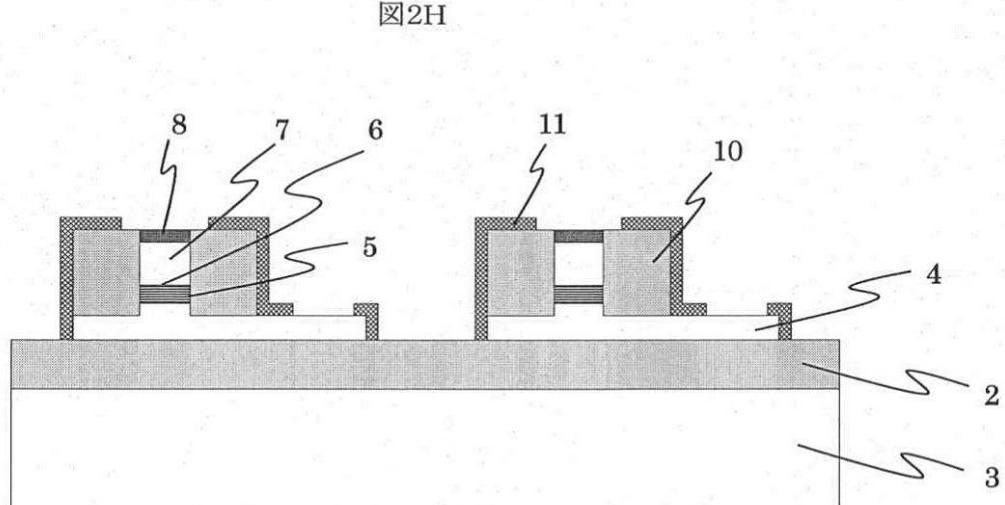

【図2H】実施例1の光半導体装置の製作過程を表す図である。

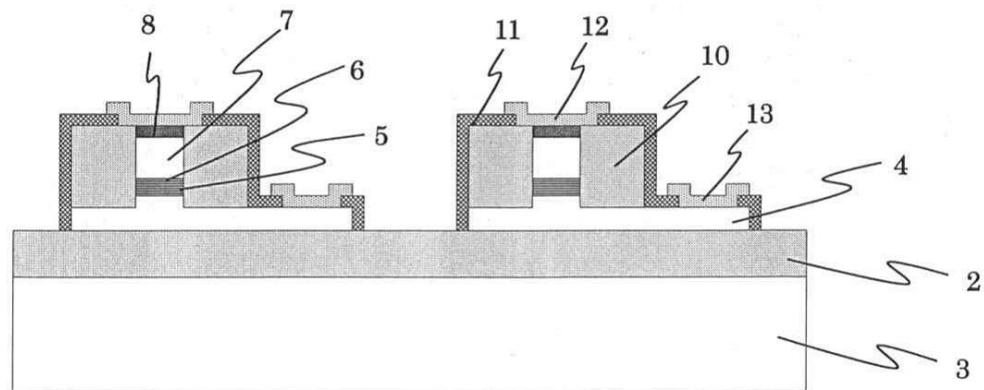

【図2I】実施例1の光半導体装置の製作過程を表す図である。

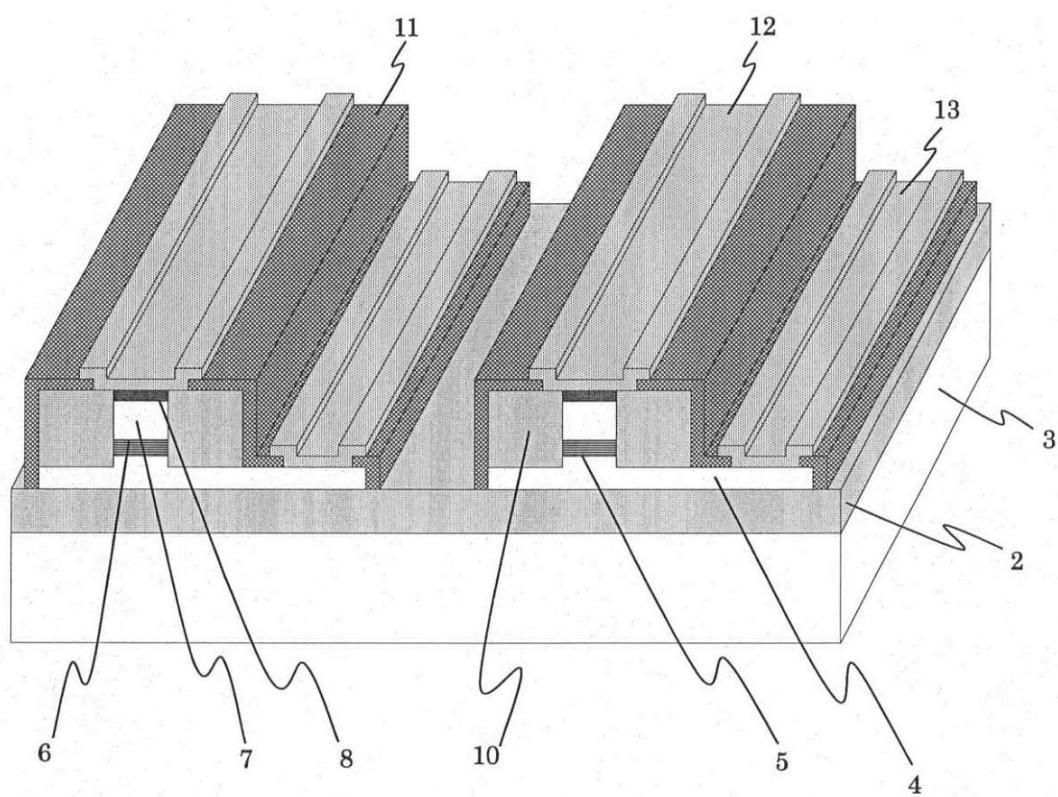

【図3】実施例1の光半導体装置の斜視図である。

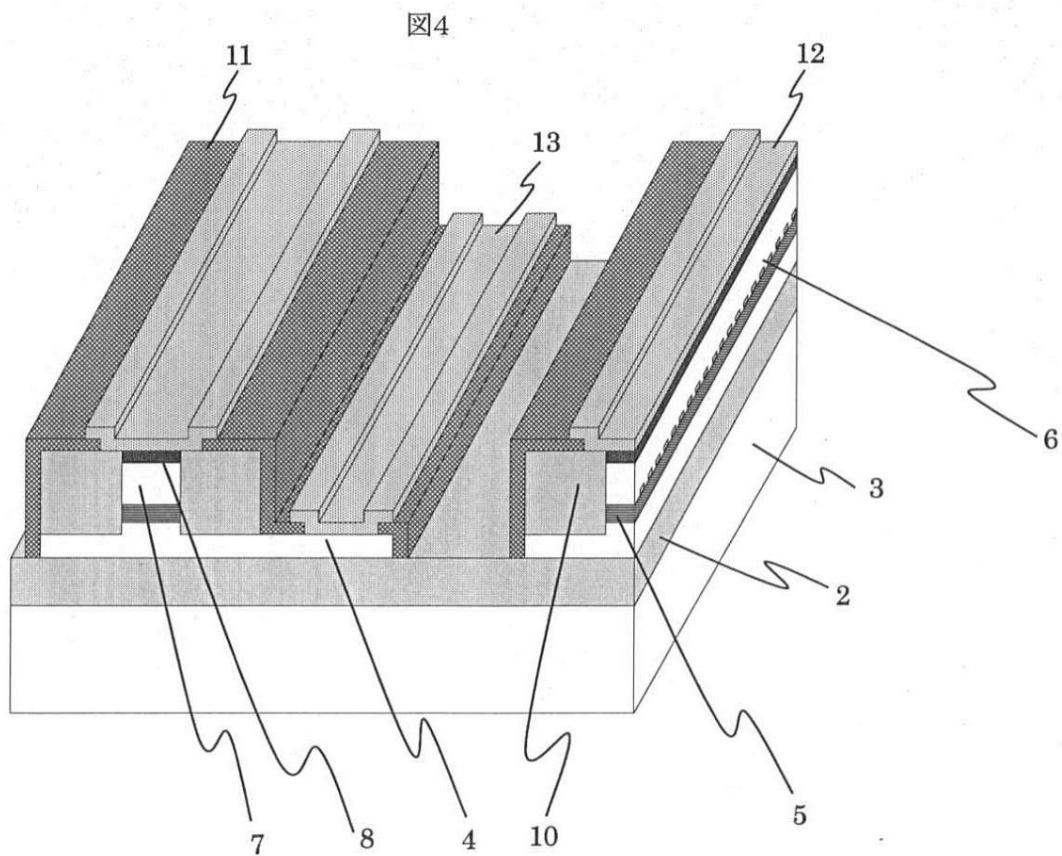

【図4】実施例1の光半導体装置の斜視図の光軸方向の部分断面図である。

50

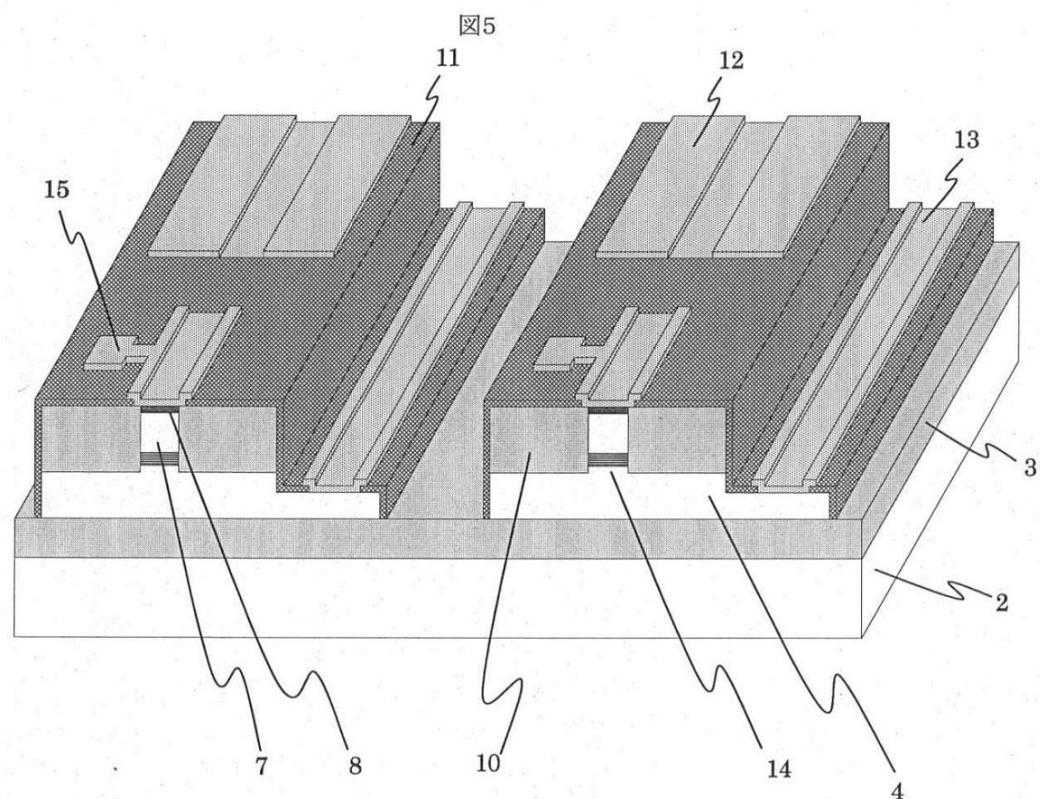

【図5】実施例2の光半導体装置（光半導体集積デバイス：OEIC）の斜視図である。

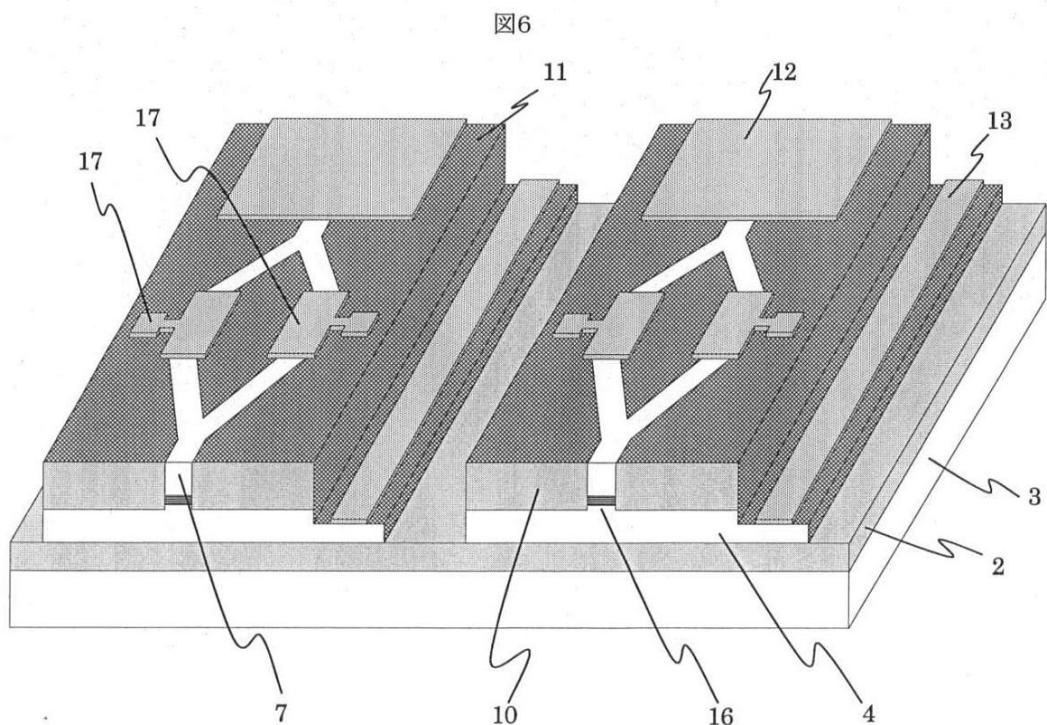

【図6】実施例3の光半導体装置（光半導体集積デバイス：OEIC）の斜視図である。

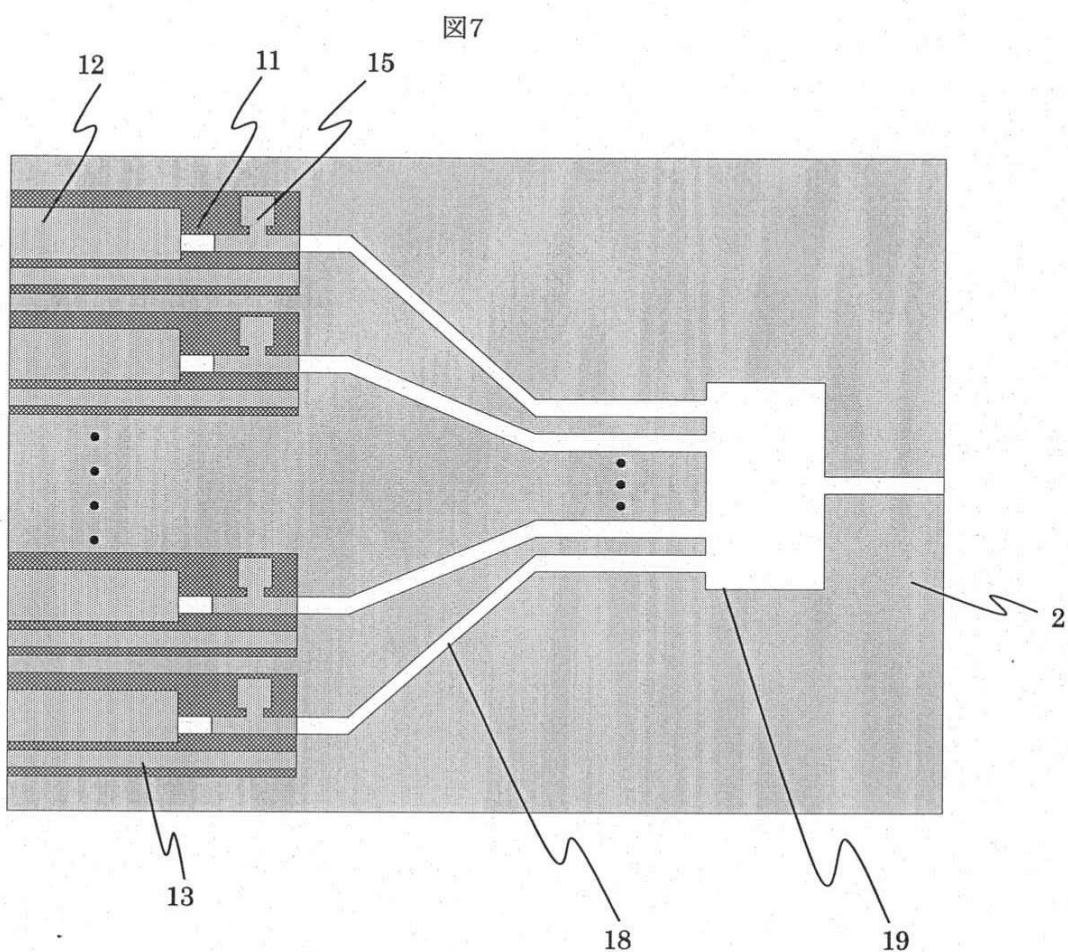

【図7】実施例4の光半導体装置（光半導体集積デバイス：OEIC）の斜視図である。

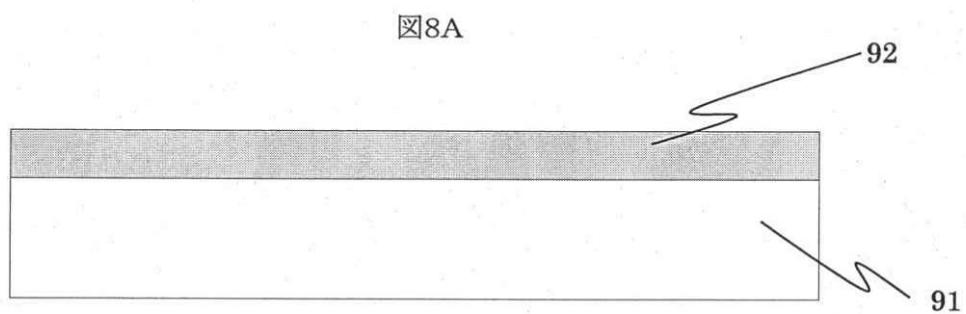

【図8A】実施例5の光半導体装置の製作過程を表す図である。

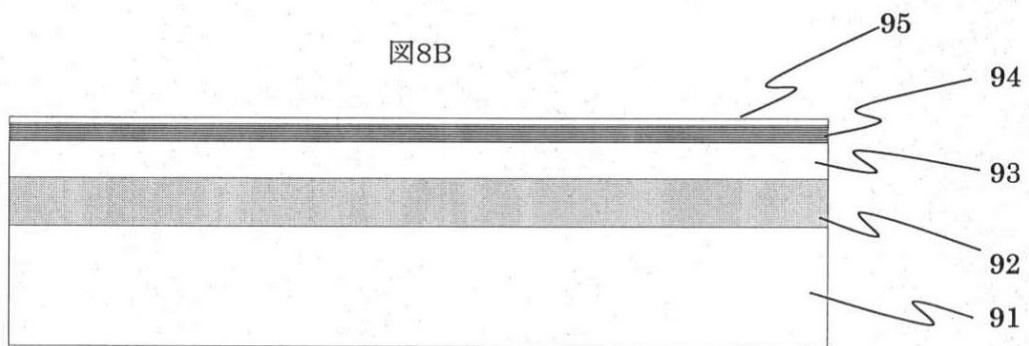

【図8B】実施例5の光半導体装置の製作過程を表す図である。

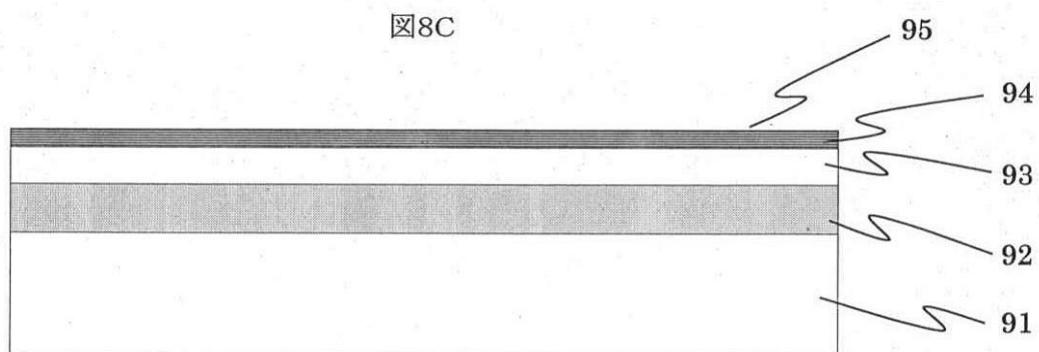

【図8C】実施例5の光半導体装置の製作過程を表す図である。

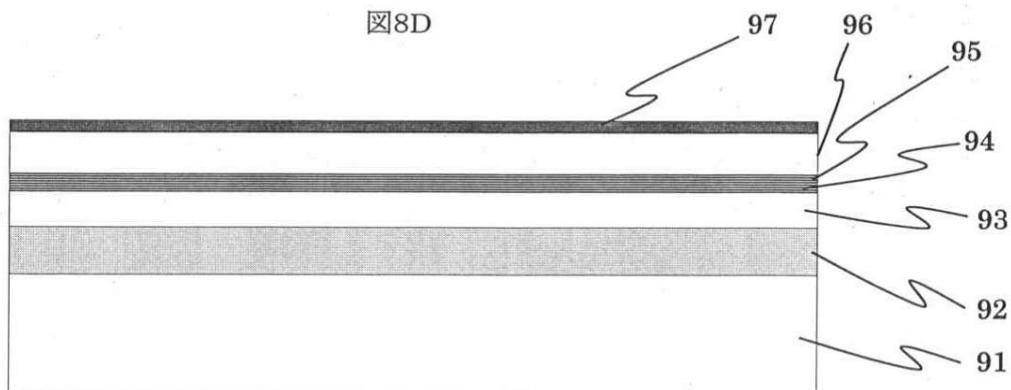

【図8D】実施例5の光半導体装置の製作過程を表す図である。

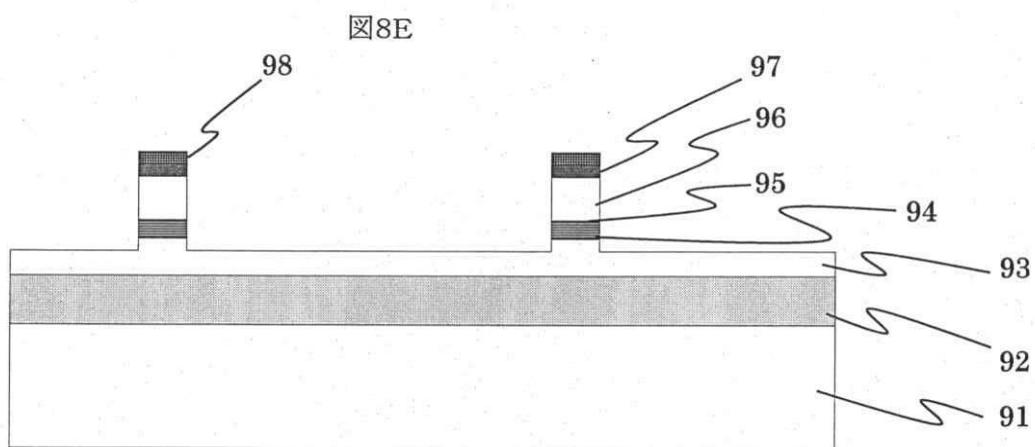

【図8E】実施例5の光半導体装置の製作過程を表す図である。

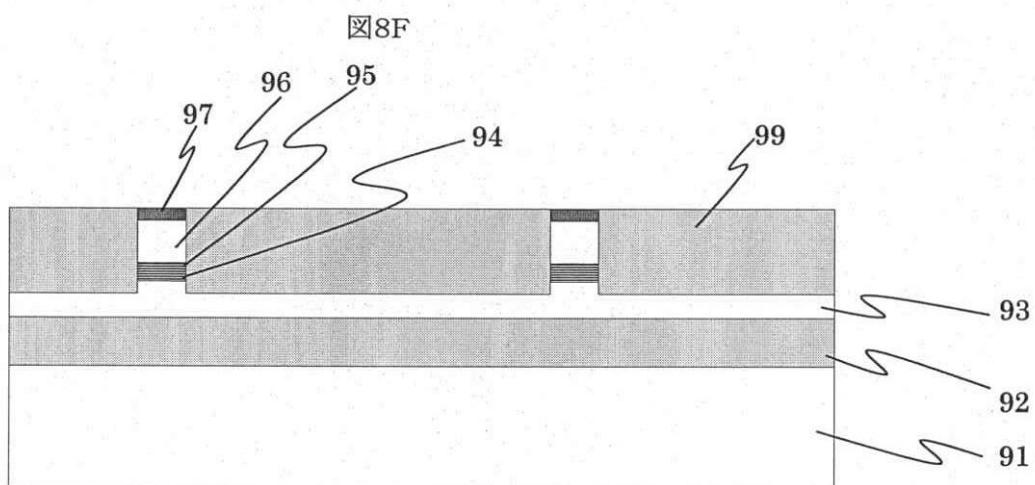

【図8F】実施例5の光半導体装置の製作過程を表す図である。

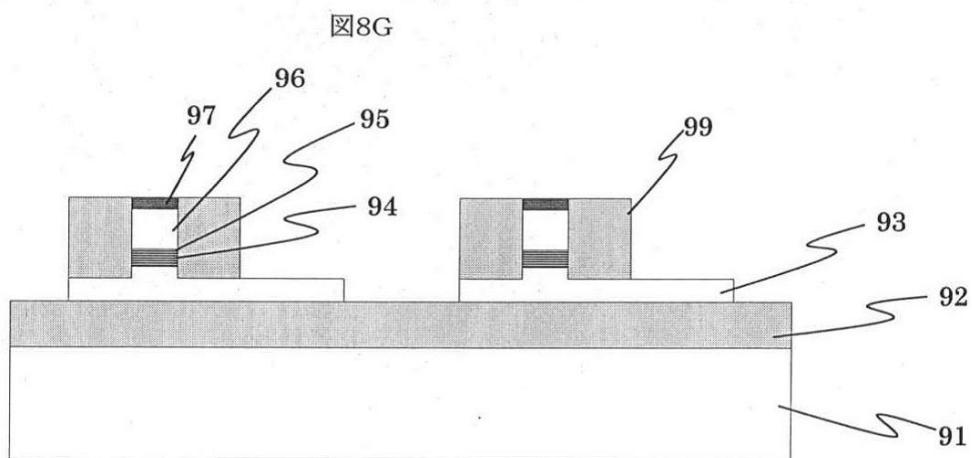

【図8G】実施例5の光半導体装置の製作過程を表す図である。

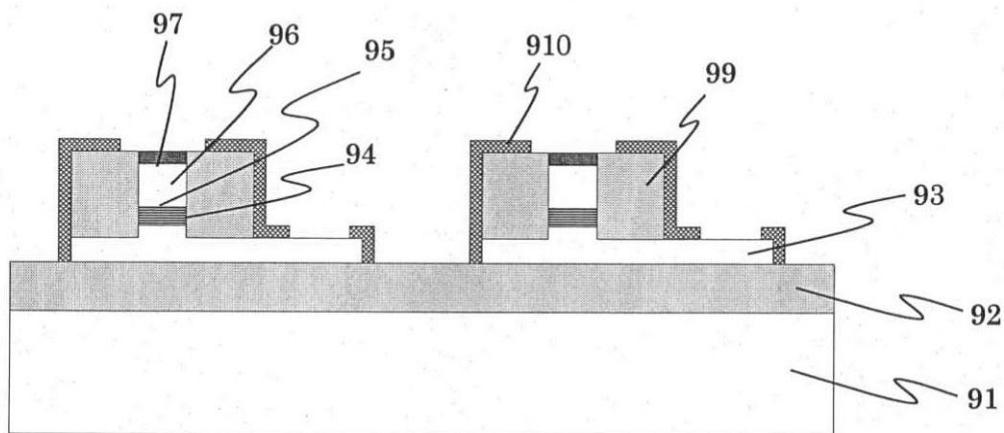

【図8H】実施例5の光半導体装置の製作過程を表す図である。

【図8I】実施例5の光半導体装置の製作過程を表す図である。

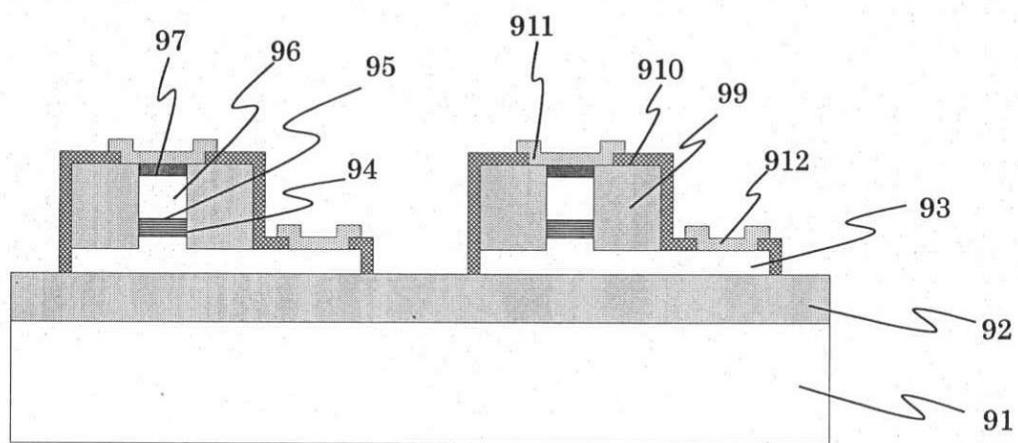

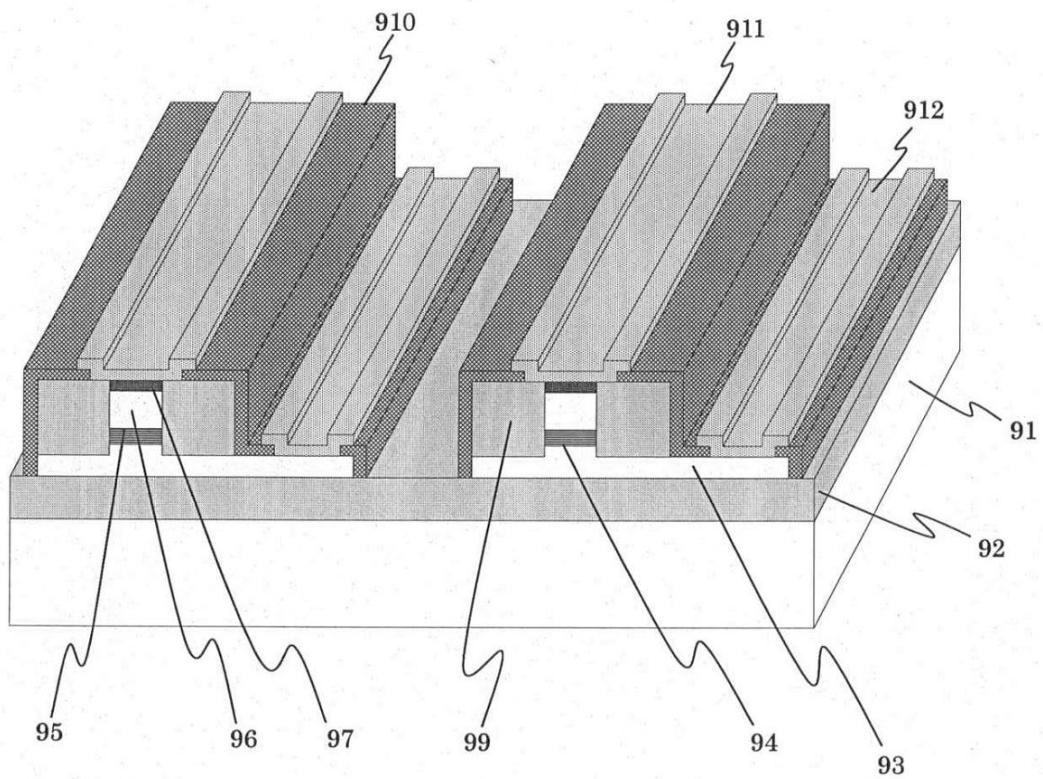

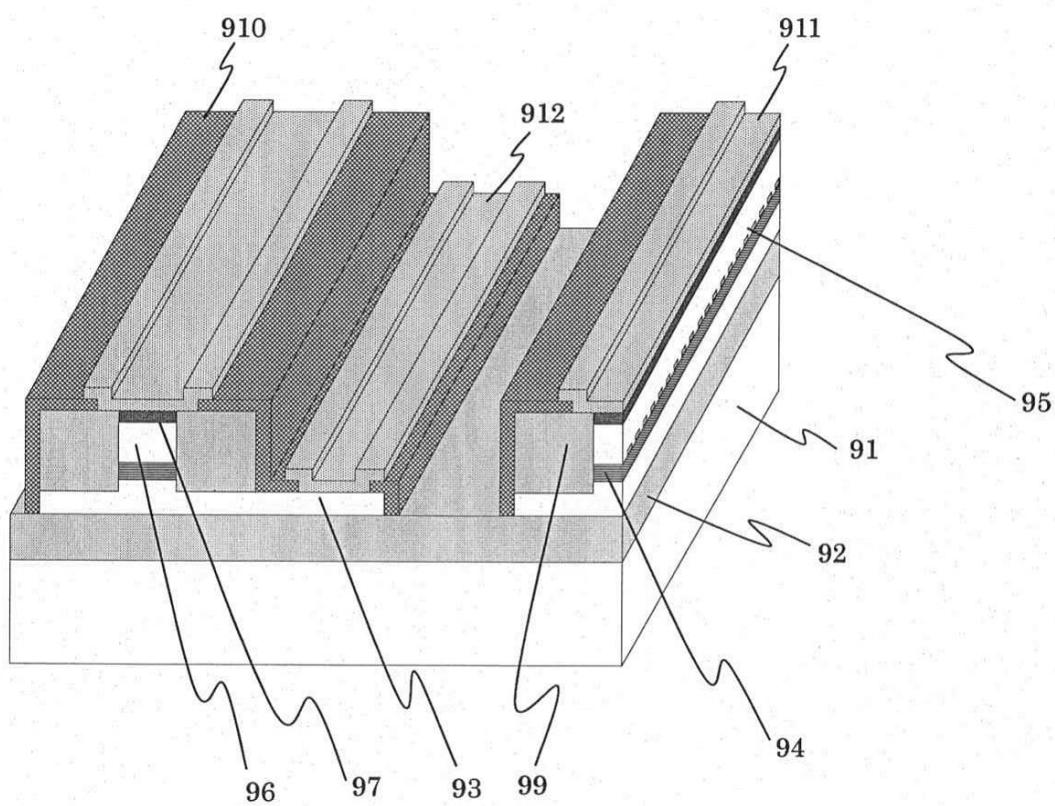

【図9】実施例5の光半導体装置の斜視図である。

【図10】実施例5の光半導体装置の斜視図の光軸方向の部分断面図である。

【図11】実施例6の光半導体装置（光半導体集積デバイス：OEIC）の斜視図である。

【図12】実施例7の光半導体装置（光半導体集積デバイス：OEIC）の斜視図である。

【図13】実施例8の光半導体装置（光半導体集積デバイス：OEIC）の斜視図である。

【図14】3dB帯域と抵抗、容量の関係を示す図である。

【図15】OEIC素子のn電極の面積を $100\mu\text{m} \times 100\mu\text{m}$ としたときのRu-InPバッファー層容量のRu-InP膜厚依存性を示す図である。

【発明を実施するための形態】

【0013】

以下、実施例を挙げて本願に含まれる各発明を説明するが、最初にその概要を説明する。

【0014】

まず、本発明者らは、従来の半絶縁性基板を用いた光半導体装置の特性を改善する方法を検討するに当たり、第1に、基板自体の絶縁性に着目した。製造効率を改善するため、大型3インチ径のウェハを用いた場合、所望の特性が得られなかったり、安定した特性を得ることができない場合があったからである。

【0015】

特許文献1のFe(鉄)-InP基板は、Zn(亜鉛)がドーピングされたp型導電性InP基板（Zn-InP基板）、あるいはS(硫黄)がドーピングされたn型導電性InP基板（S-InP基板）基板に比べ、格子欠陥の原因となるEPD密度が高い。例えば、Zn(亜鉛)ドープされた2インチ径p-InP基板のEPDは約 $200\text{cm}^{-2}$ 、S(硫黄)ドープされた2インチ径n-InP基板のEPDは約 $400\text{cm}^{-2}$ であるのに対して、Fe(鉄)がドープされたSI-InP基板のEPDは約 $5000\text{cm}^{-2}$ と、導電性基板に対してEPD密度が一桁以上高い。EPDの高さは、信頼性だけでなく、拡散現象と深く相關している結晶欠陥を増大させるため、光半導体装置の電気特性の低下を招きやすい。

【0016】

従って、SI-InP基板を用いて片面のみから電極を取り出す光半導体装置において、導電性基板を用いて両面電極取り出しの光半導体装置並みの特性を求めるのには、さらなる工夫が必要になる。

【0017】

そこで、本発明者らは、まず、半絶縁性材料のみでInP基板自体を構成しようとするコンセプトではない、異なるコンセプトで解決することを考えた。これが第1のアプローチである。具体的には、導電性InP層の表面に半絶縁InP層を設けた多層半絶縁性基板を採用することにした。その結果、格子欠陥が少なく（低EPD）安定した絶縁性を備えたSI-InP基板を実現することができた。また、同時に、低EPDにより大型基板の採用も可能になつたので、製造効率を改善することができた。そして、この基板をOEICデバイスに用いることで、光機能素子の間の絶縁特性が改善し、電気特性の優れたOEICデバイスを備えた半導体装置が実現可能になった。さらに、具体的には、n型InP基板であるS-InP基板又はp型

10

20

30

40

50

InP基板であるZn-InP基板上に半絶縁性層であるRu-InP層又はOs(オスニウム)-InP層を積層した。EPDが低いZn(亜鉛)あるいはS(硫黄)がドープされたp型又はn型導電性InP基板上にRu-InP層を形成した場合、3インチ径においても数100cm<sup>-2</sup>のEPDが実現でき、低EPDかつ半絶縁性機能を有する大口径InP基板の供給が容易になった。そして、この低EPDのSI-InP基板を用いて光半導体装置を製造することにより、相互拡散等に起因する特性劣化を抑制できるようになった。

【0018】

なお、特許文献1(特開2002-344087号公報)における、Ru-InP層の配置目的は、SI-InP基板のドーパントであるFe(鉄)との相互拡散を防ぐためである。従って、SI-InPであるFe-InP基板の上にp型InP層であるZn-InP層を用いた構造で生じたFeとZnの相互拡散を解決する目的で、Ru-InP層が挿入されているので、FeとZnの相互拡散がなくても、Ru-InP層がなければ半絶縁性基板として成り立たない上記発明と特許文献1とは明らかに異なるものである。

【0019】

次に、本発明者らは、半絶縁性材料のみでInP基板自体を構成しようとするコンセプトの中で別の解がないか検討した。これが第2のアプローチである。

【0020】

半絶縁性基板の上にp型半導体層を配置するこれまでの半絶縁性基板を用いた光半導体装置では、SI-InP基板であるFe-InP基板上に、Ru-InP層を介してp型半導体層としてZn-InP層を配置していた。これは特許文献1でも開示されていたように、Fe-InP層とZn-InP層との接触起因による相互拡散の知見によるものであったが、それでも十分な特性は得られなかった。

【0021】

そこで、本発明者らは、相互拡散の影響をさらに防止するために、基板側からn型半導体層/活性層/p型半導体層という積層順としたFe-InP基板を用いた半導体レーザの試作を行った。これはFe-InP層とZn-InP層間の距離を増大させると共に、n型半導体層による拡散防止効果を期待したものである。

【0022】

その結果、従来の積層順よりも相互拡散の影響は大幅に軽減された。しかし、依然として導電性基板を用いた半導体レーザに比べて、試作した半導体レーザの素子特性や信頼性に問題があった。そこで、本発明者らは、原因を探るべく半導体層各層の分析を行った。その結果、基板に含まれるFeとp型半導体層に含まれるZnが、数μmの半導体層やn型層を挟んでいるにも関わらず相互拡散し、僅かに活性層内に侵入することで特性を劣化させていることが判った。

【0023】

また、この特性の劣化現象は、受光素子などに比べて、素子動作時の電流値(数mA~数十mA)の高い半導体レーザや半導体光増幅器等において顕著であることも判った。それは、高い動作電流下では、FeとZnの相互拡散と、その相互拡散に深く相關している結晶転位の増殖が急激に促進されるからであると推測された。

【0024】

前述のように、Feを含む半絶縁層とZnを含むp型層との界面で、Fe-Zn相互拡散現象による素子特性への影響があることは特許文献1のように従来から知られていたが、上記分析により判明した、活性層を挟んで反対側にあるp型半導体層との相互拡散現象により特性が劣化することは新規な知見である。

【0025】

本発明者らは、この新たな知見から、SI-InP基板上にn型半導体層/活性層/p型半導体層の順に積層された積層体を備えた光半導体装置において、第2のアプローチとして、最下層の基板自体をSI基板としたままSI-InP基板を工夫するアプローチを考えた。

【0026】

具体的には、Ru-InP基板上に、n型半導体層/活性層/p型半導体層の順に積層した積層

10

20

30

40

50

体を備えた構造とすることで、前述の離れた層の間で生じるFeとZnとの相互拡散に起因する素子特性や信頼性の劣化をも抑制した。これは、RuドープInP基板は、実質的に半絶縁性といえるが、弱いn型に近い特性を示すため、n型層と積層することでFeやZnの拡散防止効果が増強されるからである。そのため、Fe-InP基板上にRu-InP層を形成した基板上に、n型半導体層／活性層／p型半導体層を順に積層成長させた構造でも良い。さらに、Ru-InP基板の代わりに、第1のアプローチで記載した導電性基板上にRu-InP層を積層した構造を用いても、上記問題を解決することができる。つまり、Fe-InP基板を用いず、Ru-InP層で絶縁性を確保した（単層又は多層）半絶縁性基板に対して、n型半導体層、活性層、p型半導体層を順に積層成長させる構造でもよい。その結果、従来、相互拡散現象により活性層に向かって拡散していたZnや半絶縁性ドーパント(Ru、Fe)の混入を抑制でき、半導体レーザや光増幅器の特性や信頼性の劣化が極めて軽減される。

#### 【0027】

なお、特許文献2（特開2000-332287号公報）には、SI-InP基板として、Ru-InP基板に関する記述がある。しかし、この場合、Ru-InP基板上に直接p型半導体層を形成した素子構造に関するもので、Ru-InP基板を用いても、やはりp型層との積層界面では相互拡散を完全には抑制できないため、低濃度のバッファー層を挿入する必要があることを示している。しかし、本発明は、Ru-InP基板上にn型半導体層を形成する素子構造を用いるもので、課題や解決手段が異なるものである。

#### 【0028】

さらに、本発明者らは、以下の条件を満たすRuドープSI-InP基板を用いることが好ましいことも見出した。

#### 【0029】

最初に、基板にドーピングするRuの好ましいドーピング濃度は、 $5 \times 10^{15} \text{ cm}^{-3}$ から $1 \times 10^{19} \text{ cm}^{-3}$ の範囲である。「 $5 \times 10^{15} \text{ cm}^{-3}$ 以上」は、好ましい絶縁性能が得られる濃度である。「 $1 \times 10^{19} \text{ cm}^{-3}$ 以下」は、Ruの析出が抑えられた低EPD及び高抵抗なSI-InP基板としての好ましい範囲である。

#### 【0030】

また、Ru-InP基板中のZn、Mg、Be、C、Si、S、Snの濃度を $1 \times 10^{16} \text{ cm}^{-3}$ 以下とすることが好ましい。これらの原子が過剰に混入すると偏析してEPDを劣化させる可能性がある。また、格子内に位置した場合であっても、InP基板中で導電性のドーパントとなり、Ru-InP基板の絶縁性能を低下させる。よって、これらの元素を先に述べた値以下にすることが好ましい。

#### 【0031】

さらに、Ru基板主表面を(100)としたとき、基板表面を微傾斜させることが好ましい。これにより、結晶層のEPDが低減できることがわかったからである。その際、最も効果が得られる傾斜角度は、-0.05度から-0.2度の範囲である。傾斜する方位は、好ましくは[110]方向であるが、この方向でなければならない訳ではない。本傾斜に関する要件は、Ru基板のEPDが若干高い場合にも、その上に結晶成長する素子の能動層における実効的なEPDを低減するために有効である。

#### 【0032】

本発明は、半導体レーザを含む集積素子や半導体増幅器、及びそれを含む集積デバイスにも有効であることは言うまでもない。

#### 【0033】

なお、本願明細書では、半絶縁性ドーパントして、Ruを用いた実施態様について説明しているが、Ruに代えて、Os（オスニウム）を用いても、同様の効果が得られる。

#### 【実施例1】

#### 【0034】

図1A、Bは、実施例1で用いるSI-InP基板の断面図である。図1Aは、導電性InP基板としてZnをドープしたZn-InP基板の上に、Ru-InP層を積層した構造である。図1Bは、導電性InP基板としてS（硫黄）をドープしたInP基板の上にRu-InP層を積層した構造であ

10

20

30

40

50

る。

【0035】

図3は、実施例1の光半導体装置の斜視図で、図4は、図3で説明した光半導体装置の斜視図の光軸方向の部分断面図である。

【0036】

図1A、BのSI-InP基板を用いた実施例1の光半導体装置の製作過程を図2Aから図2Iを用いて説明する。ただし図はあくまで本実施例を説明するものであって、図の大きさと本実施例記載の縮尺や曲率などは必ずしも一致するものではない。

【0037】

ここではS-InPで構成されたn型InP基板を用いて説明するが、Zn-InPで構成されたp型InP基板を用いることができる。また、導電性InP基板上のSI-InP層として、Ru-InPを用いた例を説明するが、Os-InP層でもよい。

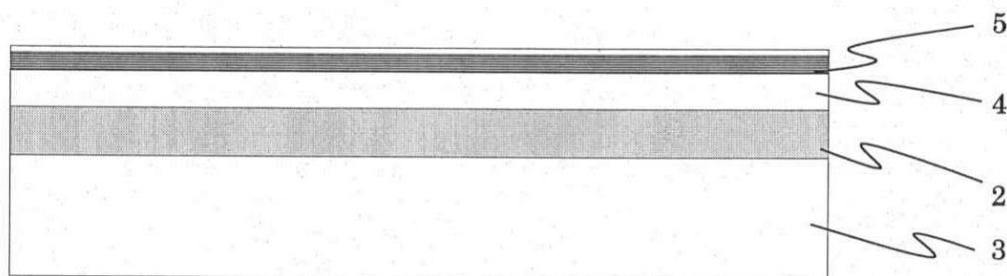

【0038】

まず、n型InP基板3であるS-InP基板上へ、MOCVD法によりSI-InP層2としてRu-InP層を形成することで多層半絶縁性基板を形成する(図2A)。続いて、S-InPで構成されたn型InPクラッド層4、アンドープの量子井戸構造5を順次積層する(図2B)。量子井戸構造としては、例えばIn、Ga、Al、Asからなる量子井戸層と障壁層を10層程度交互に積層することにより、レーザ発振に好適な活性層を形成できる。続いて、干渉露光とエッチングの組み合わせにより回折格子構造6を形成する(図2C)。続いて、Zn-InPで構成されたp型InPクラッド層7および高濃度にp型にドープされた電極コンタクト層8を順次積層する(図2D)。続いて、多層誘電体マスク9をパターンとし、フォトリソグラフィーとエッチングの組み合わせにより、メサを形成する(図2E)。続いて、半絶縁InP埋め込み層10の再成長により埋め込みヘテロ構造を形成する(図2F)。続いて、フォトリソグラフィーとエッチングの組み合わせにより、SI-InP層2上のn型InPクラッド層4のS-InP層が隣接する素子間で完全に分離するようにSI-InP層2よりも上の半導体積層体をエッチングし、かつ、n側の電極コンタクトのために、図2Fでメサを埋め込んだ半絶縁InP埋め込み層10をエッチングにより除去する。このとき、所望の厚さのn型InP層が残るよう

10

20

30

エッチングの深さを調節する必要がある(図2G)。続いて、ウェハの全面に絶縁膜11を形成した後、p側、n側それぞれの電極コンタクト位置のコンタクト層8のみ露出するよう、フォトリソグラフィーとエッチングの組み合わせにより絶縁膜11にコンタクト用のスルーホールを形成する(図2H)。このときの絶縁膜11としては、例えば酸化シリコンが適している。続いて、図2Hで形成したスルーホールに、公知の材料であるTi/Auなどのp電極12、n電極13を形成する(図2I、図4)。最後に、ウェハをバー状態にへき開し、両端面に所望の反射率を有する多層誘電体膜をコーティングし、隣接素子間が電気的に分離されたDFBレーザアレイを実現できる。これは個変化すれば、DFBレーザとなる。

【0039】

本実施例では、埋め込みヘテロ型導波路を有する素子について説明したが、リッジ導波路を初め、他の導波路構造全般に適用することができる。

【0040】

40

また、本実施例では分布帰還型(DFB)レーザの構成例について説明したが、前述の通り、導電性InP基板上にRu-InP層を備えた構造を採用して、次の(A)～(D)の光機能素子から選択された任意の光機能素子を形成しても、低E.P.Dで特性の優れた光半導体装置を、大型のウェハで製造できる。

【0041】

- (A)分布帰還型(DFB)レーザ、分布反射型(DBR)レーザ、半導体光増幅器(SOA)

- (B)電界吸収型(EA)変調器、マッハツエンダ型(MZ)変調器、方向性結合型光(DC)変調器

- (C)PIN型フォトダイオード(PD)、雪崩型フォトダイオード(APD)

- (D)パッシブ導波路、多モード干渉器(MMI)、アレイ型導波路回折格子(AWG)

50

## 【実施例 2】

## 【0042】

図5は、実施例2の光半導体装置（光半導体集積デバイス：OEIC）の斜視図である。この光半導体装置は、EA変調器とDFBレーザが集積されたEA/DFBレーザである。ただし図は飽くまで本実施例を説明するものであって、図の大きさと本実施例記載の縮尺や曲率などは必ずしも一致するものではない。ここではS-InPで構成されたn型InP基板を用いて説明するが、Zn-InPで構成されたp型InP基板を用いることができる。また、導電性InP基板上のSI-InP層として、Ru-InPを用いた例を説明するが、Os-InP層でもよい。

## 【0043】

まず、n型InP基板3上へ、MOCVD法によりRuをドープしたSI-InP層2を形成する。続いて、n型InPクラッド4、アンドープの量子井戸構造を順次積層する。量子井戸構造としては、例えばIn、Ga、Al、Asからなる量子井戸層と障壁層を10層程度交互に積層することにより、レーザ発振に好適な多重量子井戸構造5を形成できる。続いて、フォトリソグラフィーとエッチングの組み合わせにより所望の長さの活性層のみを残し、アンドープ量子井戸層5を除去する。このとき、エッチングのマスクとして誘電体マスク9を用いる。続いて、パッシブ光導波路となるアンドープInGaAsPバルク層を再成長する。続いて、先に成長したDFBレーザに相当する領域と、所望の長さのパッシブ導波路を残して、フォトリソグラフィーとエッチングの組み合わせにより、アンドープInGaAsPバルク層をエッチング除去する。続いて、電界吸収型(EA)変調器の光吸収層14となるアンドープ量子井戸層を再成長する。このとき、量子井戸構造としては、例えばIn、Ga、Al、Asからなる量子井戸層と障壁層を10層程度交互に積層することにより、電界吸収型光変調器の光吸収層14に好適な量子井戸構造を形成できる。また、各光機能部の再成長順序は、上記に限るものではない。続いて、干渉露光とエッチングの組み合わせにより、DFBレーザに相当する領域にのみ回折格子構造を形成する。続いて、ウェハ全面にp型InPクラッド層7および高濃度にp型にドープされたp<sup>+</sup>電極コンタクト層8を順次積層する。続いて、フォトリソグラフィーとエッチングの組み合わせにより、メサを形成する。続いて、半絶縁InP埋め込み層10の再成長により埋め込みヘテロ構造を形成する。続いて、フォトリソグラフィーとエッチングの組み合わせにより、RuがドープされたSI-InP上のn型InP層が、隣接する素子間で完全に分離するようにエッチングし、かつ、n側の電極コンタクトのために、先に形成したSI-InP層をエッチングにより除去する。このとき、所望の厚さのn型InP層が残るようエッチングの深さを調節する必要がある。続いて、ウェハの全面に絶縁膜を形成した後、DFBレーザのp電極12、EA変調器のp電極15、DFBレーザとEA変調器共通のn電極13を形成する。最後に、ウェハをバー状態にへき開し、両端面に所望の反射率を有する多層誘電体膜をコーティングし、隣接素子間が電気的に分離されたEA/DFBレーザアレイを実現できる。これは個変化すれば、EA/DFBレーザとなる。

## 【0044】

本実施例では、埋め込みヘテロ型導波路を有する素子について説明したが、リッジ導波路を初め、他の導波路構造全般に適用した場合でも、同様に隣接した光機能素子間が電気的に分離されたOEICデバイスを備えた光半導体装置を実現できる。

## 【0045】

また、本実施例では図面の煩雑さを避けるためEA変調器とDFBレーザのみのOEICデバイスを示しているが、次の(A)～(D)の光機能素子から選択された任意の複数の光機能素子で構成しても、光半導体装置(OEICデバイス)の特性改善を実現できる。また、大型のウェハで製造しても、低EPDな多層半絶縁性基板を採用しているので、歩留まりも高くなる。

## 【0046】

- (A) 分布帰還型(DFB)レーザ、分布反射型(DBR)レーザ、半導体光増幅器(SOA)

- (B) 電界吸収型(EA)変調器、マッハツェンダ型(MZ)変調器、方向性結合型光(DC)変調器

- (C) PIN型フォトダイオード(PD)、雪崩型フォトダイオード(APD)

10

20

30

40

50

(D) パッシブ導波路、多モード干渉器(MMI)、アレイ型導波路回折格子(AWG)

また、レーザ部が熱的、あるいは電気的な手段で発振波長を可変する機能を有していても、本発明の効果は本質的に変わるものではない。

【実施例3】

【0047】

図6は、実施例3の光半導体装置(光半導体集積デバイス:OEIC)の斜視図である。MZ/DFBレーザアレイである。ただし図は飽くまで本実施例を説明するものであって、図の大きさと本実施例記載の縮尺や曲率などは必ずしも一致するものではない。ここではS-InPで構成されたn型InP基板を用いて説明するが、Zn-InPで構成されたp型InP基板を用いることができる。また、導電性InP基板上のSI-InP層として、Ru-InPを用いた例を説明するが、Os-InP層でもよい。なお、実施例3の光集積デバイスの作成法は実施例2から容易に推測可能であるため、ここでは詳細な説明は割愛する。

10

【0048】

本発明を適用することにより、マッハ-ツェンダ型変調器とDFBレーザをモノリシックに集積した半導体集積デバイスアレイの特性を改善できる。

【0049】

本実施例では、埋め込みヘテロ型導波路を有する素子について説明したが、リッジ導波路を初め、他の導波路構造全般に適用した場合でも、同様に隣接した光機能素子間が電気的に分離されたOEICデバイスを備えた光半導体装置を実現できる。

20

【0050】

また、本実施例では図面の煩雑さを避けるためEA変調器とDFBレーザのみの集積図を示しているが、前述の通り、導電性InP基板上にRu-InP層を備えた構造を採用して、次の(A)～(D)の光機能素子から選択された複数の光機能素子で構成しても、低EPDで特性の優れた光半導体装置を実現できる。大型のウェハで製造できる。

(A) 分布帰還型(DFB)レーザ、分布反射型(DBR)レーザ、半導体光増幅器(SOA)

(B) 電界吸収型(EA)変調器、マッハツェンダ型(MZ)変調器、方向性結合型光(DC)変調器

(C) PIN型フォトダイオード(PD)、雪崩型フォトダイオード(APD)

(D) パッシブ導波路、多モード干渉器(MMI)、アレイ型導波路回折格子(AWG)

また、レーザ部が熱的、あるいは電気的な手段で発振波長を可変する機能を有していても、本発明の効果は本質的に変わるものではない。

30

【実施例4】

【0051】

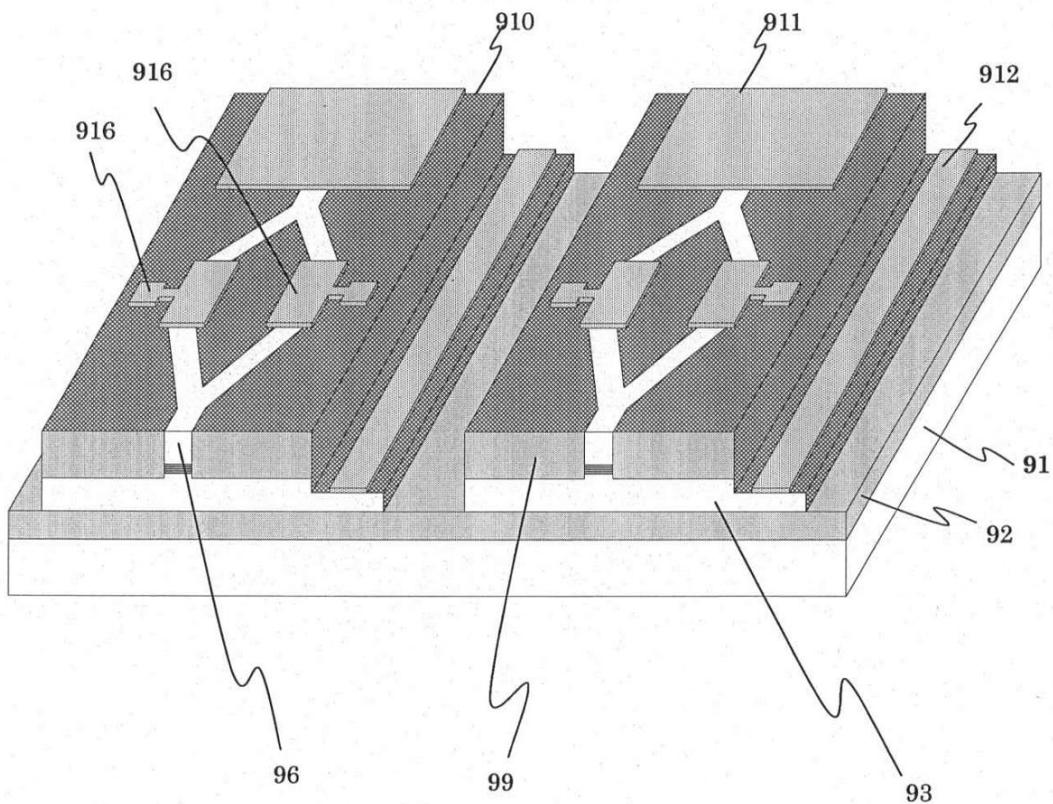

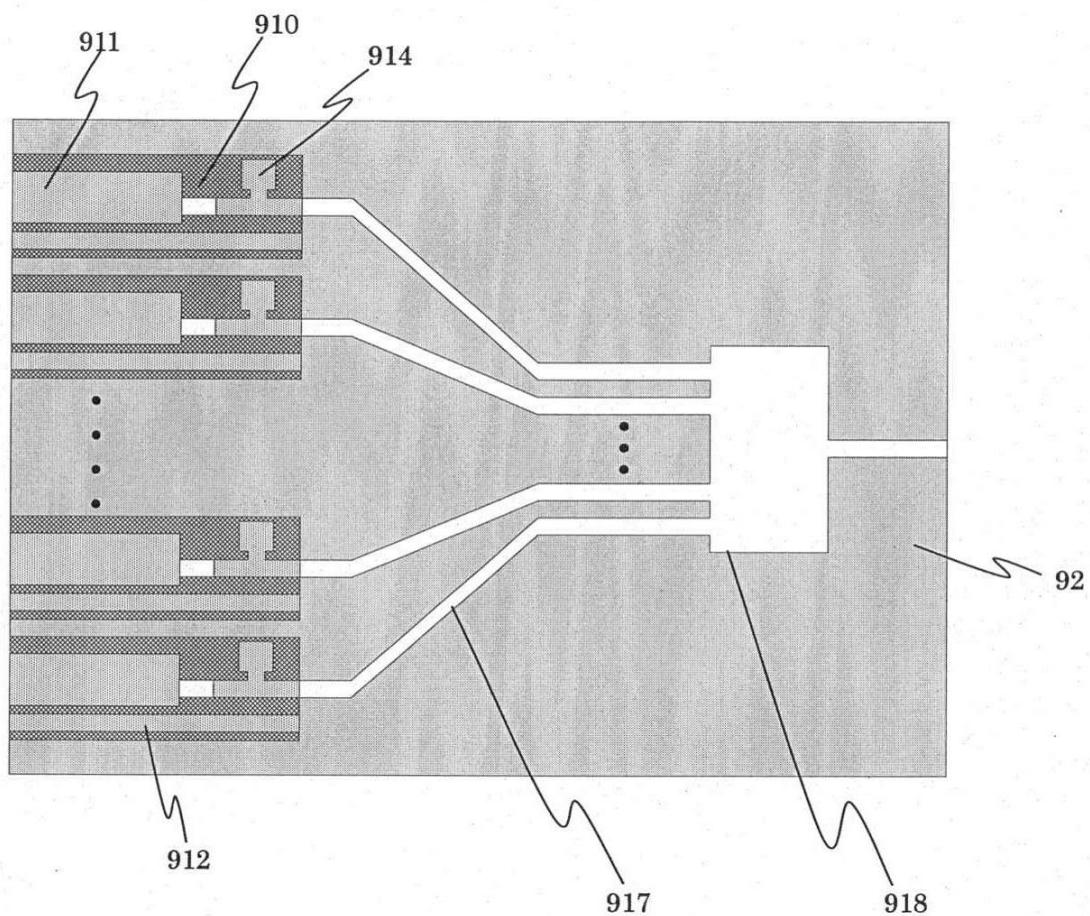

図7は、実施例4の光半導体装置(光半導体集積デバイス:OEIC)の斜視図である。EA/DFBレーザアレイと多モード干渉器(MMI)とが集積されている。ただし図は飽くまで本実施例を説明するものであって、図の大きさと本実施例記載の縮尺や曲率などは必ずしも一致するものではない。ここではS-InPで構成されたn型InP基板を用いて説明するが、Zn-InPで構成されたp型InP基板を用いることができる。また、導電性InP基板上のSI-InP層として、Ru-InPを用いた例を説明するが、Os-InP層でもよい。なお、実施例4の光集積デバイスの作成法は実施例2から容易に推測可能であるため、ここでは詳細な説明は割愛する。

40

【0052】

本実施例では、アレイ状EA/DFBレーザの光出力を、多モード干渉器(MMI)を用いて一つの導波路に集光することが可能な構成になっている。

【0053】

本実施例では、埋め込みヘテロ型導波路を有する素子について説明したが、リッジ導波路を初め、他の導波路構造全般に適用した場合でも、同様に隣接した光機能素子間が電気的に分離されたOEICデバイスを備えた光半導体装置を実現できる。

【0054】

また、本実施例では図面の煩雑さを避けるためEA/DFBレーザと多モード干渉器(MMI)の

50

みの集積図を示しているが、次の(A)～(D)の光機能素子から選択された複数の光機能素子で構成しても、大型のウェハで製造できる。

【0055】

(A)分布帰還型(DFB)レーザ、分布反射型(DBR)レーザ、半導体光増幅器(SOA)

(B)電界吸収型(EA)変調器、マッハツェンダ型(MZ)変調器、方向性結合型光(DC)変調器

(C)PIN型フォトダイオード(PD)、雪崩型フォトダイオード(APD)

(D)パッシブ導波路、多モード干渉器(MMI)、アレイ型導波路回折格子(AWG)

また、レーザ部が熱的、あるいは電気的な手段で発振波長を可変する機能を有していても、本発明の効果は本質的に変わるものではない。

10

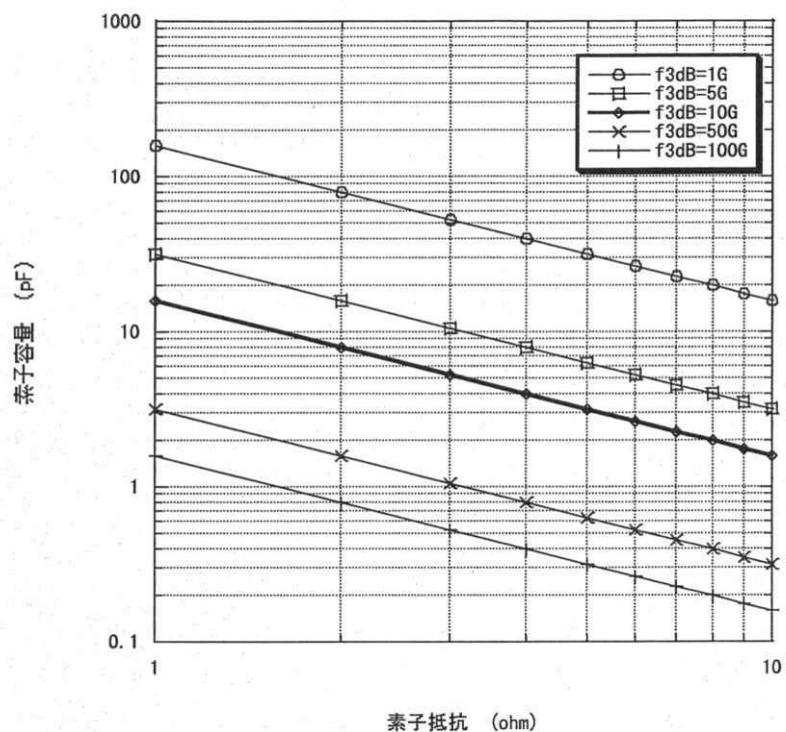

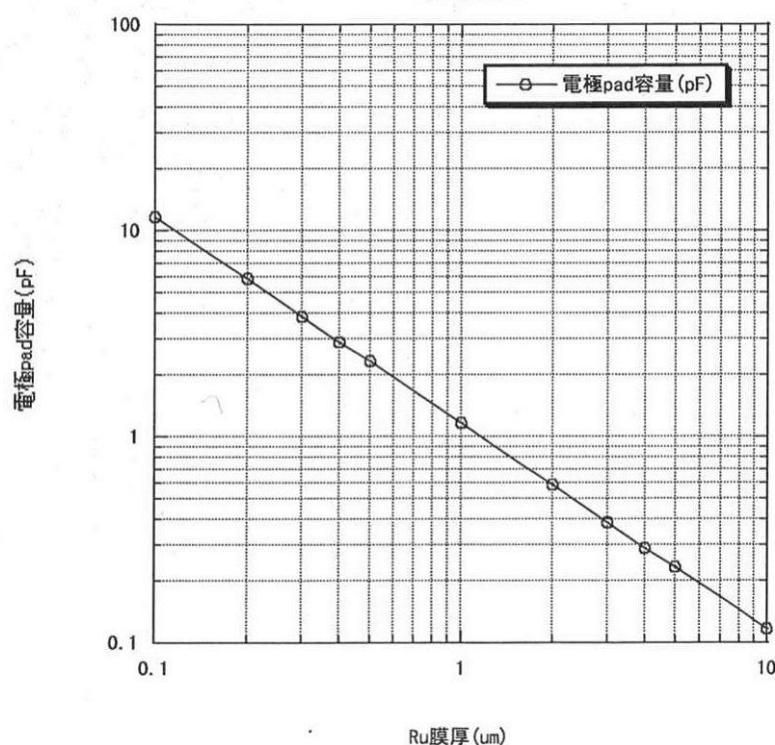

【0056】

<実施例1乃至4におけるRu-InP膜の好ましい膜厚>

なお、実施例1乃至4に記載したRu-InP膜の好ましい膜厚について、以下説明する。

【0057】

図14に、3dB帯域と抵抗、容量の関係を示す。10GB/s以上の変調動作において、素子抵抗を5以下とすると、素子容量を3pF以下にすることが必要であることがわかる。

【0058】

図15にOEIC素子のn電極の面積を100  $\mu\text{m} \times 100 \mu\text{m}$ としたときのRu-InPバッファー層容量のRu-InP膜厚依存性を示す。容量を3pF以下にするには、Ru-InP膜厚が0.5  $\mu\text{m}$ 以上あれば良い。よって、膜厚の下限は0.5  $\mu\text{m}$ である。一方、素子は最終的に研磨を行い、素子厚15  $\mu\text{m}$ 程度まで薄くする。よって、Ru-InPバッファー層の膜厚は150  $\mu\text{m}$ あれば十分であり、これが上限となる。従って、尚、成長速度の観点から、150  $\mu\text{m}$ の膜厚を実現するためには、MOCVD法よりも、ハイドライドVPE法など成長速度が数10  $\mu\text{m}/\text{h}$ と早い成膜方法を用いることが製造上好ましい。

20

【実施例5】

【0059】

本発明を適用した半導体光集積素子の実施例5の製作過程を、図8を用いて説明する。ただし図はあくまで本実施例を説明するものであって、図の大きさと本実施例記載の縮尺や曲率などは必ずしも一致するものではない。ここではRu-InP基板を用いた例を説明するが、Os-InP基板でもよい。

30

【0060】

まず、先に述べた手法により作製したRu-InP基板91上へ、MOCVD法によりRuをドープしたSI-InP層92を形成する(図8A)。続いて、S-InPで構成されたn型InPクラッド93、アンドープの量子井戸構造94を順次積層する(図8B)。量子井戸構造94としては、例えばIn、Ga、Al、Asからなる量子井戸層と障壁層を10層程度交互に積層することにより、レーザ発振に好適な活性層を形成できる。続いて、干渉露光とエッチングの組み合わせにより回折格子構造95を形成する(図8C)。続いて、Zn-InPで構成されたp型InPクラッドおよび高濃度にp型にドープされたp<sup>+</sup>コンタクト層97を順次積層する(図8D)。続いて、フォトリソグラフィーとエッチングの組み合わせにより、誘電体マスク98でメサを形成する(図8E)。続いて、再成長により半絶縁InP埋め込み層99でメサを埋め込み、埋め込みヘテロ構造を形成する(図8F)。続いて、フォトリソグラフィーとエッチングの組み合わせにより、RuがドープされたSI-InP上のS-InPで構成されたn型InP層が、隣接する素子間で完全に分離するようにエッチングし、かつ、n側の電極コンタクトのために、図8Fで形成したSI-InP層をエッチングにより除去する。このとき、所望の厚さのn型InP層が残るようにエッチングの深さを調節する必要がある(図8G)。続いて、ウェハの全面に絶縁膜を形成した後、p側、n側それぞれの電極コンタクト位置の半導体部のみ露出するように、フォトリソグラフィーとエッチングの組み合わせによりスルーホールを形成する(図8H)。このときの絶縁膜(パッシベーション膜)としては、例えば酸化シリコンなどが適している。続いて、図8Hで形成したスルーホール部に、公知の材料であるTi/Auなどの電極(DFBレーザp電極911、n電極912)を形成する(図8

40

50

I)。最後に、ウェハをバー状態にへき開し、両端面に所望の反射率を有する誘電体膜をコーティングすることにより、隣接素子間が電気的に分離されたDFBレーザアレイを実現できる。本光半導体装置の斜視図を図9に、図9の光軸方向の部分断面図を図10に示す。

#### 【0061】

本実施例では、埋め込みヘテロ型導波路を有する素子について説明したが、リッジ導波路を初め、他の導波路構造全般に適用することができる。

#### 【0062】

また、本実施例では分布帰還型(DFB)レーザの構成例について説明したが、半導体レーザのみならず、半導体光増幅器でも同様であり、またそれらを含む光集積素子に対しても有効であることは言うまでも無い。光集積素子に含まれる部品としては、例えば下記の(A)- (D)が挙げられる。

#### 【0063】

- (A) 分布帰還型(DFB)レーザ、分布反射型(DBR)レーザ、半導体光増幅器(SOA)

- (B) 電界吸収型(EA)変調器、マッハツエンダ型(MZ)変調器、方向性結合型光(DC)変調器

- (C) PIN型フォトダイオード(PD)、雪崩型フォトダイオード(APD)

- (D) パッシブ導波路、多モード干渉器(MMI)、アレイ型導波路回折格子(AWG)

#### 【実施例6】

#### 【0064】

実施例6の半導体光集積素子の製作過程を図11で説明する。ただし図はあくまで本実施例を説明するものであって、図の大きさと本実施例記載の縮尺や曲率などは必ずしも一致するものではない。ここではRu-InP基板を用いた例を説明するが、Os-InP基板でもよい。

#### 【0065】

まず、先に述べた手法により作製したRu-InP基板上へ、MOCVD法によりRuをドープしたSI-InP層を形成する。続いて、n型の導電性を有するInPクラッド、アンドープの量子井戸構造を順次積層する。量子井戸構造としては、例えばIn、Ga、Al、Asからなる量子井戸層と障壁層を10層程度交互に積層することにより、レーザ発振に好適な活性層を形成できる。続いて、フォトリソグラフィーとエッチングの組み合わせにより所望の長さの活性層のみを残し、アンドープ量子井戸層を除去する。このとき、エッチングのマスクとして誘電体を用いる。続いて、パッシブ光導波路となるアンドープInGaAsPバルク層を再成長する。続いて、先に成長したDFBレーザに相当する領域と、所望の長さのパッシブ導波路を残して、フォトリソグラフィーとエッチングの組み合わせにより、アンドープInGaAsPバルク層をエッチング除去する。続いて、電界吸収型(EA)変調器の光吸収層となるアンドープ量子井戸層を再成長する。このとき、量子井戸構造としては、例えばIn、Ga、Al、Asからなる量子井戸層と障壁層を10層程度交互に積層することにより、電界吸収型光変調器の光吸収層に好適な量子井戸構造を形成できる。また、各光機能部の再成長順序は上記に限るものではない。続いて、干渉露光とエッチングの組み合わせにより、DFBレーザに相当する領域にのみ回折格子構造を形成する。続いて、ウェハ全面にp型の導電性を有するInPクラッドおよび高濃度にp型にドープされた電極コンタクト層を順次積層する。続いて、フォトリソグラフィーとエッチングの組み合わせにより、メサを形成する。続いて、再成長により埋め込みヘテロ構造を形成する。続いて、フォトリソグラフィーとエッチングの組み合わせにより、RuがドープされたSI-InP上のn型InP層が、隣接する素子間で完全に分離するようにエッチングし、かつ、n側の電極コンタクトのために、先に形成したSI-InP層をエッチングにより除去する。このとき、所望の厚さのn型InP層が残るようにエッチングの深さを調節する必要がある。続いて、ウェハの全面に絶縁膜を形成した後、EA変調器およびDFBレーザのp側、n側それぞれの電極コンタクト位置の半導体部のみが露出するように、フォトリソグラフィーとエッチングの組み合わせによりスルーホールを形成する。このときの絶縁膜としては、例えば酸化シリコンなどが好適である。続いて、先に形

10

20

30

40

50

成したスルーホール部に、公知の材料であるTi/Auなどの電極を形成する。最後に、ウェハをバー状態にへき開し、両端面に所望の反射率を有する誘電体膜をコーティングすることにより、隣接素子間が電気的に分離されたEA/DFBレーザアレイを実現できる。

#### 【0066】

本実施例では、埋め込みヘテロ型導波路を有する素子について説明したが、リッジ導波路を初め、他の導波路構造全般に適用した場合でも、同様に隣接した光機能素子間が電気的に分離されたOEICデバイスを備えた光半導体装置を実現できる。

#### 【0067】

また、本実施例では図面の煩雑さを避けるためEA変調器とDFBレーザのみの集積図を示しているが、半導体レーザのみならず、半導体光増幅器でも同様であり、またそれらを含む光集積素子に対しても有効であることは言うまでも無い。光集積素子に含まれる部品としては、例えば下記の(A)-(D)が挙げられる。

#### 【0068】

- (A) 分布帰還型(DFB)レーザ、分布反射型(DBR)レーザ、半導体光増幅器(SOA)

- (B) 電界吸収型(EA)変調器、マッハツエンダ型(MZ)変調器、方向性結合型光(DC)変調器

- (C) PIN型フォトダイオード(PD)、雪崩型フォトダイオード(APD)

- (D) パッシブ導波路、多モード干渉器(MMI)、アレイ型導波路回折格子(AWG)

#### 【実施例7】

#### 【0069】

本発明を適用した半導体光集積デバイスの実施例7を図12に示す。ただし図はあくまで本実施例を説明するものであって、図の大きさと本実施例記載の縮尺や曲率などは必ずしも一致するものではない。光集積デバイスの作成法は実施例6から容易に推測可能であるため、ここでは詳細な説明は割愛する。

#### 【0070】

本発明を適用することにより、図12のようにマッハ-ツエンダ(MZ)型変調器とDFBレーザをモノリシックに集積した半導体集積デバイスアレイを実現できる。

#### 【0071】

本実施例では、埋め込みヘテロ型導波路を有する素子について説明したが、リッジ導波路を初め、他の導波路構造全般に適用した場合でも、同様に隣接した光機能素子間が電気的に分離されたOEICデバイスを備えた光半導体装置を実現できる。

#### 【0072】

また、本実施例では図面の煩雑さを避けるためMZ変調器とDFBレーザのみの集積図を示しているが、半導体レーザのみならず、半導体光増幅器でも同様であり、またそれらを含む光集積素子に対しても有効であることは言うまでも無い。光集積素子に含まれる部品としては、例えば下記の(A)-(D)が挙げられる。

#### 【0073】

- (A) 分布帰還型(DFB)レーザ、分布反射型(DBR)レーザ、半導体光増幅器(SOA)

- (B) 電界吸収型(EA)変調器、マッハツエンダ型(MZ)変調器、方向性結合型光(DC)変調器

- (C) PIN型フォトダイオード(PD)、雪崩型フォトダイオード(APD)

- (D) パッシブ導波路、多モード干渉器(MMI)、アレイ型導波路回折格子(AWG)

また、レーザ部が熱的、あるいは電気的な手段で発振波長を可変する機能を有していても、本発明の効果は本質的に変わるものではない。

#### 【実施例8】

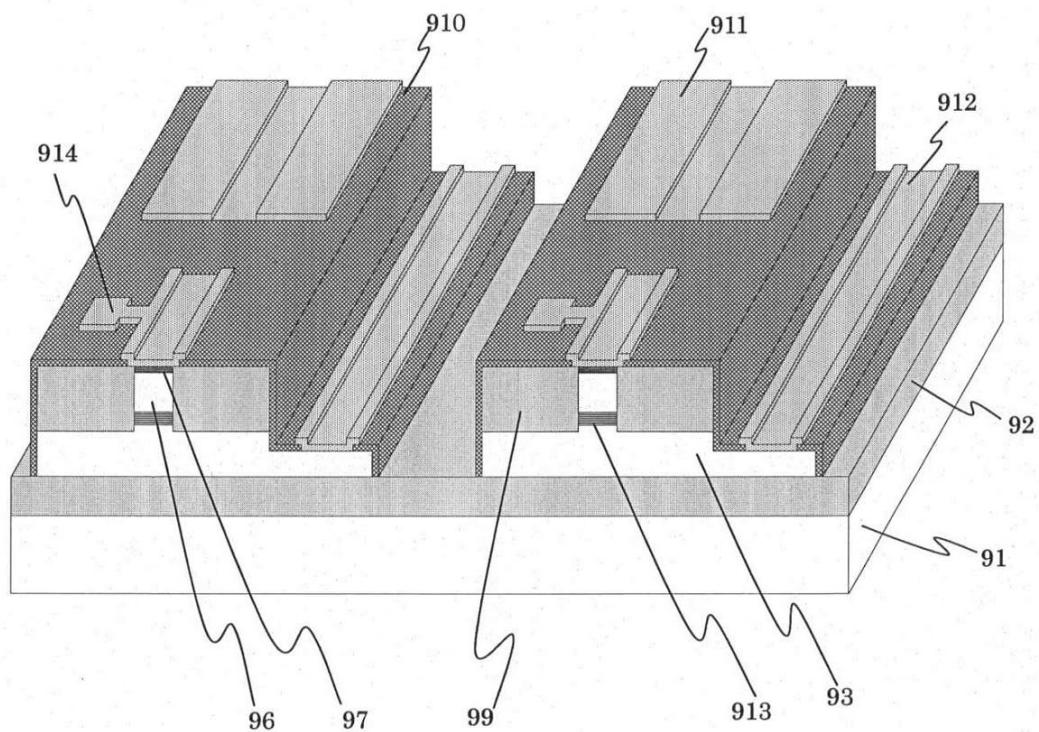

#### 【0074】

本発明を適用した半導体光集積デバイスの実施例8を図13に示す。ただし図はあくまで本実施例を説明するものであって、図の大きさと本実施例記載の縮尺や曲率などは必ずしも一致するものではない。ここではRu-InP基板を用いた例を説明するが、Os-InP基板でもよい。

10

20

30

40

50

## 【0075】

なお、実施例8の光集積デバイスの作成法は実施例6から容易に推測可能であるため、ここでは詳細な説明は割愛する。

## 【0076】

本実施例では、図13のようにアレイ上に配置されたEA/DFBレーザの光出力を、多モード干渉器(MMI)を用いて一つの導波路に集光することが可能である。

## 【0077】

本実施例では、埋め込みヘテロ型導波路を有する素子について説明したが、リッジ導波路を初め、他の導波路構造全般に適用した場合でも、同様に隣接した光機能素子間が電気的に分離されたOEICデバイスを備えた光半導体装置を実現できる。

10

## 【0078】

また、本実施例では図面の煩雑さを避けるためEA変調器とDFBレーザのみの集積図を示しているが、半導体レーザのみならず、半導体光増幅器でも同様であり、またそれらを含む光集積素子に対しても有効であることは言うまでも無い。光集積素子に含まれる部品としては、例えば下記の(A)-(D)が挙げられる。

## 【0079】

(A)分布帰還型(DFB)レーザ、分布反射型(DBR)レーザ、半導体光増幅器(SOA)

(B)電界吸収型(EA)変調器、マッハツエンダ型(MZ)変調器、方向性結合型光(DC)変調器

(C)PIN型フォトダイオード(PD)、雪崩型フォトダイオード(APD)

20

(D)パッシブ導波路、多モード干渉器(MMI)、アレイ型導波路回折格子(AWG)

尚、実施例5乃至8におけるRu-InP基板91は、既に述べた別の発明コンセプトに基づき、Fe-InP基板で置き換えても良い。

## 【符号の説明】

## 【0080】

1...p型InP基板、2...Ru-InP層、3...n型InP基板、4...n型InPクラッド層、5...多重量子井戸構造、6...回折格子層、7...p型InPクラッド層、8...コンタクト層、9...誘電体マスク、10...半絶縁InP埋め込み層、11...絶縁膜、12...p電極、13...n電極、14...光吸収層、15...EA変調器p電極、16...位相変調層、17...位相調整領域p電極、18...光導波路、19...多モード干渉器

91...RuドープInP基板、92...RuドープInPバッファー層、93...n型InPクラッド層、94...多重量子井戸、95...回折格子層、96...p型InPクラッド層、97...p+型コンタクト層、98...誘電体マスク、99...半絶縁InP埋め込み層、910...パッシベーション膜、911...DFBレーザp電極、912...n電極、913...光吸収層、914...EA変調器p電極、916...位相調整領域p電極、917...光導波路、918...多モード干渉器

30

## 【図1A】

図1A

## 【図1B】

図1B

## 【図2A】

図2A

【図2B】

図2B

【図2C】

図2C

【図2D】

図2D

【図2E】

図2E

【図2F】

図2F

【図2G】

【図2H】

【図2I】

図2I

【図3】

図3

【図4】

【図5】

【図6】

【図7】

【図8A】

【図8B】

【図8C】

【図8D】

【図 8 E】

【図 8 F】

【図 8 G】

【図8H】

図8H

【図8I】

図8I

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図14】

図14

## CRの関係

【図15】

図15

Ru厚と容量

## フロントページの続き

| (51)Int.Cl. |                  | F I     |         |

|-------------|------------------|---------|---------|

| H 0 1 L     | 31/10 (2006.01)  | H 0 1 L | 31/10 A |

| H 0 1 L     | 31/107 (2006.01) | H 0 1 L | 31/10 B |

| G 0 2 B     | 6/122 (2006.01)  | G 0 2 B | 6/12 A  |

(72)発明者 土屋 朋信

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

(72)発明者 牧野 茂樹

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

審査官 日夏 貴史

(56)参考文献 特開平04-007873 (JP, A)

特開2008-098297 (JP, A)

特開平09-064459 (JP, A)

特開昭62-090969 (JP, A)

特開昭62-092386 (JP, A)

特開2002-344087 (JP, A)

A. van GEELEN et al., Ruthenium doped high power 1.48μm SIPBH laser, 11th International Conference on Indium Phosphide and Related Materials 1999 (IPRM 1999), 1999年5月, p.203-206

LEALMAN I. et al., Reliable 1550nm SI BH lasers fabricated using an improved Ru precursor, 20th International Conference on Indium Phosphide and Related Materials 2008 (IPRM 2008), 2008年5月

(58)調査した分野(Int.Cl., DB名)

|         |           |   |             |

|---------|-----------|---|-------------|

| H 0 1 S | 5 / 1 2   | - | 5 / 5 0     |

| H 0 1 L | 3 1 / 1 0 | - | 3 1 / 1 0 9 |

| G 0 2 B | 6 / 1 2   | - | 6 / 1 3 8   |

| H 0 1 L | 2 7 / 1 5 |   |             |